# **Durham E-Theses**

# Wideband harmonic radar detection

Farrukh Aslam, S. M.

#### How to cite:

Farrukh Aslam, S. M. (2008) Wideband harmonic radar detection, Durham theses, Durham University. Available at Durham E-Theses Online: http://etheses.dur.ac.uk/2334/

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

# Wideband Harmonic Radar Detection

By

S. M. Farrukh Aslam

A thesis submitted to the

University of Durham, Durham, United Kingdom,

For the degree of MSc

June 2008

The copyright of this thesis rests with the author or the university to which it was submitted. No quotation from it, or information derived from it may be published without the prior written consent of the author or university, and any information derived from it should be acknowledged.

0 1 SEP 2008

## **Abstract**

Radio sites consist naturally of metallic structures. Metals are always covered by an oxide film due to the metal reacting chemically with the oxygen in air. The rate of this oxide formation depends largely on the environment. Any oxide film between metallic contacts will cause non-linearity. RF currents passing through these junctions would generate harmonics. When RF signals at two frequencies f1 and f2 pass through a non-linearity they create signals at their sum and difference frequencies. These are known as 'inter-modulation products'. This generation of inter-modulation products when radio waves interact with rusty parts is called as the 'Rusty Bolt Effect'. Radio spectrum is carefully controlled for optimal usage of the available frequencies so that different services operate in well-defined frequency channels. Of com has set some standards for radio site engineering. This set of standards is given in the document 'MPT 1331: Code of Practice for Radio Site Engineering'. Any transmission site which is not following these codes would likely cause interference to other users. It is important that radio engineers should check the sites for their compliance with these codes. If a particular radio site is causing interference due to the rusty-bolt effect, the corroded points must be located to minimize their effect using a Harmonic Radar.

A 'Harmonic Radar' is a device that illuminates a region of space with RF waves and receives the harmonics of the transmitted frequencies. The received data can then be processed to find the exact location and mobility of the points causing the generation of these harmonics. It works on the principle of radar transmitting a chirp signal and receiving harmonics of the transmitting frequency. Work is currently being carried out at the 'Centre for Communication Systems' in Durham University funded by HMGCC on the design and implementation of a novel Wideband Harmonic Radar system. The radar system would employ advanced sub-systems i.e. a suitable waveform and multiple antenna arrays processing super-resolution algorithms for angular information.

# Declaration

No portion of the work referred to in this report has been submitted in support of an application for another degree or qualification at this or any other university, or institution of learning.

# Acknowledgements

I would like to sincerely thank my supervisor, Professor Sana Salous for her help and guidance throughout the duration of my PhD. I would also like to express my gratitude to Dr. Feeney, who on many occasions provided me with constructive discussions and guidance. Furthermore, I would like to give my thanks to the HMGCC for funding my studies and giving me the opportunity to undertake research in this field.

# List of Abbreviations

|      | <del></del>                                            |

|------|--------------------------------------------------------|

| AOA  | Angle of Arrival                                       |

| DOA  | Direction of Arrival                                   |

| DSP  | Digital Signal Processing                              |

| EIRP | Effective Isotropic Radiated Power                     |

| EM   | Expectation Maximization                               |

| FFT  | Fast Fourier Transform                                 |

| FMCW | Frequency Modulated Continuous Wave                    |

| MIMO | Multiple Input Multiple Output                         |

| ML   | Maximum Likelihood                                     |

| NLJD | Non-Linear Junction Detector                           |

| PIM  | Passive Intermodulation                                |

| RCS_ | Radar Cross Section                                    |

| RF   | Radio Frequency                                        |

| Rx   | Receiver                                               |

| SAGE | Space Alternating Generalized Expectation-Maximization |

| SIMO | Single Input Multiple Output                           |

| Tx   | Transmitter                                            |

| UCA  | Uniform Circular Array                                 |

| ULA  | Uniform Linear Array                                   |

| VFO  | Variable Frequency Oscillator                          |

| WRF  | Waveform Repition Frequency                            |

# Table of Contents

| 1. | Introduction                                                 |      |

|----|--------------------------------------------------------------|------|

|    | 1.1. Introduction                                            | 1-1  |

|    | 1.2. Review of chapter contents                              | 1-3  |

|    | 1.3. References                                              | 1-4  |

| 2. | FMCW Harmonic Radar                                          |      |

|    | 2.1. Radar Theory & Principles                               | 2-1  |

|    | 2.2. FMCW/Chirp Waveform                                     | 2-2  |

|    | 2.3. Harmonic Radar – Historical Development                 | 2-6  |

|    | 2.3.1. Non-Linear Junction Detector                          | 2-8  |

|    | 2.3.2. Issues related to NLJD Operation                      | 2-10 |

|    | 2.3.2.1.Null Range                                           |      |

|    | 2.3.2.2.Target dependence on frequency                       |      |

|    | 2.3.2.3.Frequency Interference                               | 2.1. |

|    | 2.3.3. Further Applications                                  | 2-11 |

|    | 2.4. Harmonic Radar Range Equation 2.5. References           | 2-11 |

|    | 2.3. References                                              | 2-15 |

| 3. | Rusty Bolt Effect                                            |      |

|    | 3.1. Introduction                                            | 3-1  |

|    | 3.2. Passive Intermodulation                                 | 3-2  |

|    | 3.2.1. Mathematical Representation                           | 3-2  |

|    | 3.2.2. MPT 1331: Code of Practice for Radio Site Engineering | 3-3  |

|    | 3.3. Localisation Techniques                                 | 3-4  |

|    | 3.4. References                                              | 3-5  |

| 4. | System Description                                           |      |

|    | 4.1. Introduction                                            | 4-1  |

|    | 4.2. System Design                                           | 4-2  |

|    | 4.2.1. Transmitter                                           | 4-2  |

|    | 4.2.2. Harmonic Receiver                                     | 4-3  |

|    | 4.2.3. Antenna Array                                         | 4-4  |

|    | 4.3. Chirp Generator 4.3.1. DDFS Board – AD9854              | 4-5  |

|    | 4.3.1. DDFS Board – AD9834 4.3.1.1. Different Waveforms      | 4-5  |

|    | 4.3.1.2.Phase Coherency                                      |      |

|    | 4.3.2. Digital Programmer                                    | 4-14 |

|    | 4.3.2.1. C based Design                                      | 7-17 |

|    | 4.3.2.2. Gate Array Design                                   |      |

|    | 4.4 References                                               | 4-21 |

| 5  | Signal Processing                                            |      |

| ٠. | 5.1. Heterodyne Detection                                    | 5-1  |

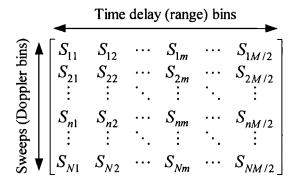

|    | 5.2. Double FFT Processing                                   | 5-3  |

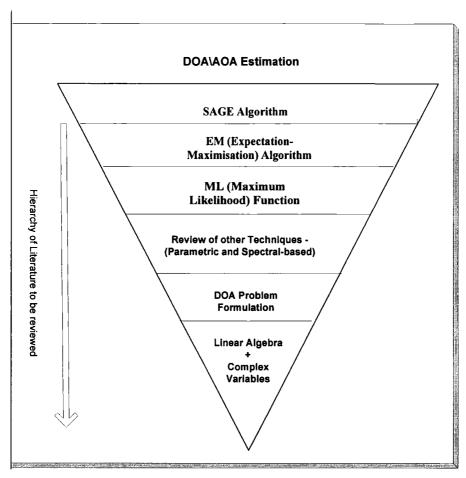

|    | 5.3. SAGE Algorithm - DOA Estimation                         | 5-5  |

5.4. References 5-12

### 6. Conclusions & Further Work

6-1

## Appendices

A-1: Gate Array Design - Schematics

A – 2 : Gate Array Design – VHDL Code

A - 3 : DDS Programmer - C Code

A-4: Chirp Parameter Calculator

A-5: Publications and Outputs

# Chapter 1

#### 1.1 Introduction

A Radar system uses electromagnetic waves to identify the range, direction, or speed of moving and fixed objects such as aircraft, ships, vehicles, and landscape. The term RADAR is an acronym for **Ra**dio **D**etection and **R**anging. Radar can be regarded as an all-weather day/night performing sensor that can measure target range accurately and precisely.

Radar system was developed during World War II as a way to detect enemy aircrafts. Enemy airplanes could be detected because they reflected some of the transmitted energy. Crude radar images were obtained on the displays of airborne radar systems. Over the many decades radar techniques and technology have been developed. The enormous advances that have been made in radar since the 1950s are mainly due to the development of fast, high-performance digital processing hardware and algorithms [1]. Radar systems continue to find applications in diverse areas like Detection and Ranging of ground, sea and air targets, Air Traffic Control (ATC), Meteorological applications, Collision avoidance, Speed measurement and Remote sensing.

Much work has been done in developing radar systems having a high bandwidth. The distinguishing characteristic of a wideband radar is its fine range resolution, which is inversely proportional to the operating bandwidth. Wideband radar systems help to accurately pin-point the intended target. The Lincoln Laboratory in the United States has done pioneering work in the development of high-power wideband radar. Since 1970 the Laboratory has developed and fielded several wideband radars for use in ballistic-missile-defence research and space-object identification. [2]

One main advancement has been in the different types of radar transmit waveforms. The type and quality of information received by a radar depends in part on the waveform it transmits. FMCW – Frequency Modulated Continuous Waveform is one example that has been successfully employed in practical systems. [3]

Chapter I Introduction

An interesting class of radar systems is a harmonic radar whereby the radar system receives the harmonics of the fundamental frequency transmitted. The aim is to locate and identify the target(s) that are generating these harmonics. Harmonic radars have been put to great use in the field of Entomology where they have been instrumental in tracking the movement of insects. Such systems are now being developed to be used in other areas where non-linear or harmonic generating elements are the intended targets. One such application is to locate the junctions producing passive intermodulation frequencies commonly at transmission sites [4]. These rusty-bolt joints can be located using a wideband harmonic detector and counter-measures can then be performed.

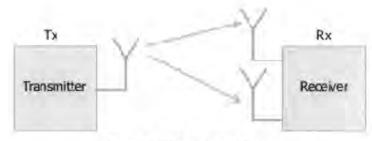

Figure 1.1 SIMO Channel System

Antenna technology has proved to be a very important component of radar and other communication systems. Recent research work has been on 'smart antenna' systems which make use of antenna arrays. One such system is the SIMO system as shown in Figure 1.1. SIMO (single input, multiple output) is an antenna technology for wireless communications in which multiple antennas are used at the receiver. The antennas are combined to minimize errors and optimize data speed. The data henceforth received can be processed using algorithms to extract useful information. Advancement in signal processing techniques has made it possible to employ super-resolution algorithms to precisely locate the targets.

The project undertaken aims to utilize the strengths of various systems, techniques and methodologies mentioned above to develop a highly effective 'Wideband Harmonic Radar system' with appropriate antenna arrays employing high resolution signal processing algorithms.

## 1.2 Review of Chapter Contents

Chapter 2 describes the FMCW Harmonic radar system in detail. It explains the theory behind an FMCW waveform and gives an overview of the historical development of harmonic radar system.

Chapter 3 provides an overview of the Rusty-bolt Effect. It describes the reason behind its occurrence and mentions the counter-measures available in literature.

Chapter 4 provides a system level overview of the harmonic radar. It also explains the work done so far and gives an understanding of its various components.

Chapter 5 deals with signal processing algorithms. Two techniques are mentioned and their underlying principle is explained.

Chapter 6 is the conclusion of the report. It describes the work accomplished so far and the requirements needed in order to carry out developing the rest of the radar system.

## 1.3 References

- [1] H. D. Griffiths, Chris J. Baker, "Radar Imaging for Combating Terrorism", Department of Electronic and Electrical Engineering, University College London, London, UK

- [2] W. W. Camp, J. T. Mayhan, R. M. O'Donnell, "Wideband Radar for Ballistic Missile Defense and Range-Doppler Imaging of Satellites", Lincoln Laboratory Journal volume 12, number 2, 2000

- [3] M. I. Skolnik, Introduction to Radar Systems, 2<sup>nd</sup> ed: McGraw Hill, 1988

- [4] "MPT 1331 : Code of Practice for Radio Site Engineering", June 2001, Flyde Microsystems Ltd

# Chapter 2

#### **FMCW Harmonic Radars**

#### 2.1 Radar Theory & Principles

Radar measurement is based on the principles of properties of radiated electromagnetic energy. Electromagnetic energy travels through air at approximately the speed of light. This energy is transmitted to and reflected from the reflecting object. A small portion of the reflected energy returns to the radar set. This returned energy is called an 'echo'. Radar sets use the echo to determine primarily the direction and distance of the reflecting object.

One of the most important relations used to define the working of a radar system is the radar range equation. It relates the transmit power from the radar to the received power in terms of range, antenna and target dimensions. The fundamental form of the radar range equation is

$$P_{\rm r} = \frac{P_{\rm r}G}{4\pi R^2} \frac{\sigma}{4\pi R^2} A_e \tag{2.1}$$

where

- P<sub>t</sub> Transmit Power

- P<sub>r</sub> Receive Power

- G Antenna Gain

- R Target Range

- $\sigma$  RCS Radar Cross Section i.e. measure of size of target as seen by the radar. Its units are that of area.

- $A_e$  Effective Aperture of receiving antenna

Two important parameters for radar performance is its resolution and sensitivity.

#### Resolution

The range resolution tells us how far apart two targets have to be to be distinguished as two separate entities. If the time delay between the reflected signals from two

objects is greater than the pulse duration, then the two objects are seen separately. [21] If the targets are closer than this duration, then the receiver will not be able to distinguish between the two.

#### Sensitivity

The range sensitivity or accuracy indicates uncertainty in a measurement of the absolute distance to an object. Intuitively, accuracy of a range measurement should depend on the 'sharpness' of the pulse shape. However, the crucial factor determining range accuracy is bandwidth. Consider a single wavelength being used to locate a target. The target phase measured will be ambiguous every wavelength. A second wavelength added to the transmission will aide in locating the target. It reduces ambiguities and sharpens the position of the target. Adding more wavelengths means increasing bandwidth. Therefore, adding more bandwidth leads to greater accuracy and the system becomes more sensitive [21].

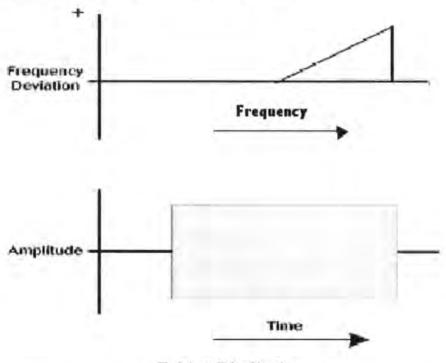

#### 2.2 FMCW / Chirp Waveform

FMCW or Frequency Modulated Continuous Wave work on the principle of 'pulse compression' or 'pulse coding'. It is a processing technique that maximises the sensitivity and resolution of radar systems. Chirp signals derive their name from the fact that if the signal was audible it would sound like the chirp or tweet of a bird. The chirp of a bird increases monotonically over a frequency interval.

Chirp waveform was first classified by Klauder et al. [1] as published in the Bell Labs Technical Journal in 1960. However, the basic idea was presented earlier by Oliver in 1951 in a Bell Telephone Laboratory internal memorandum which was interestingly titled "Not with a bang but a Chirp" [2].

Increase in radar sensitivity can be achieved by two methods.

- 1. By increasing the average transmitting power

- 2. By increasing the pulse length

Average transmitted power is the peak power multiplied by the transmitter duty cycle. The peak power can be as high as several hundred kilowatts. However, a pulse radar transmits short burst of pulses where the average transmit power might be 1% of the peak transmit power. This makes such a system very inefficient. Increasing the pulse length can increase the average transmitted power without decreasing efficiency but this has an adverse effect of degrading the range resolution. The radio pulse is too long and can not distinguish between two closely spaced targets.

This conflict in user requirements can be resolved in designing such a transmit waveform that would maximise both sensitivity and resolution. As described above, the range resolution does not necessarily depend upon the pulse length but on the pulse bandwidth. The bandwidth can be altered by manipulating the amplitude and/or phase within the pulse without changing its duration. Thus, the radar resolution can be increased without having to change its duration. This manipulation of pulse is called 'pulse coding'. The types of pulses that involve changing the frequency of the transmitted pulses are called 'chirp' pulses. This is an electronic method to boost the apparent signal strength as perceived by the radar receiver. The outgoing radar pulses are chirped, that is, the frequency of the carrier is varied within the pulse, much like the sound of a cricket chirping.

The timing mark is the changing frequency. The transit time is proportional to the difference in frequency between the echo and the transmitter signal. The greater the transmitter frequency deviation in a given time interval, the more accurate the measurement of the transit time and the greater will be the transmitted spectrum.

In FMCW radar, the transmitter frequency is changed as a function of time in a known manner. This known manner can be linear or non-linear in nature.

A linear chirp waveform modulated signal can be defined by the following equations:

$$x_T(t) = A_0 \cos[\phi_T(t)] \tag{2.2}$$

where

$$\phi_T(t) = 2\pi \left( f_c t + \frac{kt^2}{2} \right)$$

(2.3)

and

$$A_{T} = \begin{cases} E_{o} \text{ for } 0 \le t \le t' \\ 0 \text{ otherwise} \end{cases}$$

(2.4)

Here, the subscript T stands for transmitting,  $f_0$  is the carrier frequency at t = 0, k is the linear chirp rate and  $\phi_T(t)$  is the instantaneous transmitted phase. The time value t' represents the length of the transmitted chirp signal. It is known that the instantaneous transmitted frequency is specified by:

$$f_{\tau}(t) = \left(\frac{1}{2\pi}\right) \frac{d\phi(t)}{dt} \tag{2.5}$$

which implies

$$f_T(t) = f_e + kt$$

(2.6)

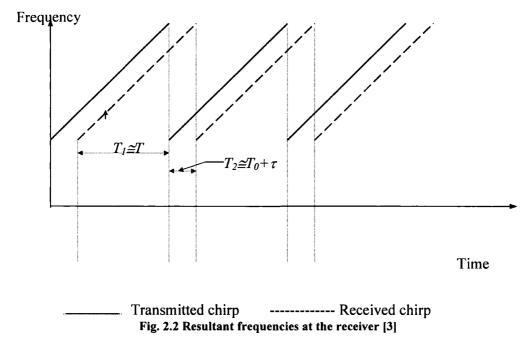

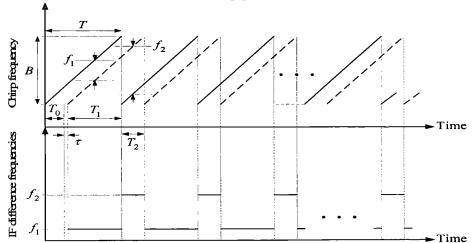

It is evident from the equation that the frequency increases linearly with time. Therefore, the transmitted signal exhibits linear frequency modulation commonly referred to as the saw-tooth signal shown in figure 2.1

Fig 2.1 A Chirp Signal

This signal is generated repetitively a fixed quantity of times in a second. This quantity is known as the Wave Repetition Frequency (WRF).

Figure 2.2 shows the resultant frequency at the receiver. Here it is possible to see graphically all the parameters involved in the preceding sections. The solid line represents the transmitted signal the dotted line shows the received signal. The received signal is delayed by a time  $\tau$ , with respect to the transmitted signal. If a signal that is a replica of the transmitted signal is combined with the received signal, then the resultant difference frequency will be a train pulse and the pulse width has a frequency  $f_D$ . This can be used to extract useful information using a signal processing technique. More of it is explained in Chapter 6.

For a linear chirp, the sweep rate is the slope of y-axis (frequency) to x-axis (time) over a single chirp. Therefore, the sweep rate 'k' is

$$k = \frac{B}{T} \tag{2.7}$$

and equation (2.2) becomes

$$x_T(t) = A_T \cos[\phi_T(t)] = A_T \cos\left(2\pi f_c t \pm \pi \frac{B}{T} t^2\right)$$

(2.8)

where  $f_c$  is the carrier frequency

A<sub>T</sub> is the amplitude of the transmitted signal and is constant

B is the sweep bandwidth T is the sweep period.

The instantaneous frequency of this signal is:

$$f_T(t) = \frac{1}{2\pi} \frac{d\phi_T(t)}{dt} = f_c \pm \frac{B}{T}t \tag{2.9}$$

For a linearly increasing chirp,

$$f_T(t) = f_c + \frac{B}{T}t \tag{2.10}$$

In this case,  $f_c$  is the lower frequency of the bandwidth.

#### 2.3 Harmonic Radar – Historical Development

Harmonic Radar is a device that illuminates a region of space with RF waves and receives the harmonics of the transmitted frequencies. The received data can then be processed to find the exact locations of the points causing the generation of these harmonics. It works on the principle of radar transmitting a chirp signal and receiving harmonics of the transmitting frequency.

Radars were the earliest applications of chirp waveform. Barrick [4], Poole [5], Klauder et al. [1] presented valuable works related to the theory of the FMCW signals and its radar applications. With the development of electronic circuit techniques and signal processing algorithms, this principle found new applications - one of them being in area of mobile radio channel characterisation as presented by Salous [6-7].

An early commercial FMCW Harmonic Radar system was METRRA – Metal Target Re-Radiation developed for the US Army in the late 70's. [8] Its intended use was to detect stationary military targets e.g. tanks, vehicles, and weapon caches etc. which are hidden by foliage. The system transmitted a 400 MHz signal and received its third harmonic (120 MHz) signal. It is reported to be successfully demonstrated at a range of 1 kilometre. [8]

Another harmonic radar system was developed by the U.S. 'Strategic Environmental Research and Development Program (SERDP)' which is the Department of Defense's (DoD) environmental science and technology program. This system developed in the late 90's third harmonics and used for Unexploded Ordinance (UXO) Detection. This project built a prototype system that demonstrated capability to detect and locate buried UXO remotely. [9]

Harmonic radars have also been an area of interest in academia. One such system was developed at the Electromagnetic Laboratory at Michigan State University. Its intended use was in etymology. This radar was a bi-static CW system. The transmit frequency was 800 – 900 MHz and the receiver could be tuned to from 1232 MHz to 1862 MHz. The system was intended to detect harmonic radar tags in high-clutter environments. [10]

Recent developments in non-linear junction detectors (NLJD) have shown the advancement and sophistication of new devices coming up. A number of patents have been issued in the past few years.

Jones et al. [11] developed a non-linear junction detector for counter surveillance measures. Its main feature is the use of a circularly polarized Tx/Rx antenna. Using linearly polarized antenna, one has to scan the target area twice in a horizontal and vertical position. This ensures that the surveillance device returning polarized harmonic return do not go un-detected. Using a NLJD with circularly polarized antenna allows successful detection regardless of which angle the scan is made. Barsumian et al. [12] have developed an interesting NLJD that transmits a series of pulses as the transmit signal. The transmit power of pulses is varied. The received harmonics of all pulses are compared to each other as well as to a set of standard data. The harmonic signals are analysed if they correspond to a known set of non-linear device. The receive harmonics are also demodulated to the audible frequency range where they are detected by an audio circuit. Some NLJDs have a feed back control system in them such as developed by Holmes et al. [13]. The feed back control maintains a pre-determined minimum threshold value of the received signals. So the control system has two parts – one to determine the signal strength and other to vary

the power output level of the transmitter. Advantage of this invention is improved system efficiency.

All of the systems mentioned above transmit at a single frequency and receive at multiple harmonics. An innovative method is to transmit at multiple frequencies and then try to receive different combination of its harmonics. One such invention is the CWER (Concealed Weapon and Electronics Radar) system developed at John Hopkins University by Jablonski et al. [14]. This system transmits two frequencies at  $f_1$  and  $f_2$  from separate antenna systems. This creates received signals of the order of  $\inf_1 \pm \inf_2$ , where n and m are integers. A single frequency transmit has adequate detection capability but it has very limited capability with respect to classifying different types of targets. This Dual Frequency Scanning Harmonic Radar has the ability to distinguish objects of different types and to distinguish them from nearby clutter. Another recently patented invention was by Rafael-Armament Development Authority Ltd. [15] This NLJD transmits more than two frequencies  $f_1$ ,  $f_2$ ,  $f_3$  .... towards the area of interest. The receiving unit then tunes to receive at intermodulation products  $nf_1 + mf_2 + qf_3$  ...., wherein n, m, q are non-zero integers.

#### 2.3.1 Non-Linear Junction Detector

The use of a Harmonic Detector, also called as a 'Non-Linear Junction Detector' is dependent on the fact that electronic devices and metallic objects that come in contact with one another create a non-linear junction. What a non-linear junction detector does is detect these non-linear junctions. In doing so, active or inactive junctions can be detected. One should keep in mind that these non-linear junctions can be anything from electronic circuits like eavesdropping equipment (bugs, microphones etc) to various corroded metal junctions. Various methods of analysis and algorithms can be used to distinguish between the targets.

The two main functions of a sweep using Non Linear Junction Detectors are:

- 1. The Detection of non-linear junctions

- 2. The Discrimination between junctions so as to differentiate between electronics and other forms of junctions

The RF sweep would be useless without the second step as there would be many false alarms.

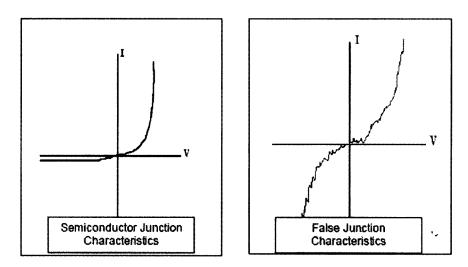

The junctions in electronic devices are different than those in other junctions. The harmonic returns of electronics are well defined but that of non-electronics are not. Electronic components will have a strong second harmonic signal and a weak third harmonic signal. Other junctions will have a weak second harmonic signal and a strong third harmonic signal [16]. The 3<sup>rd</sup>, 5<sup>th</sup> and other odd harmonic reflections are reflected by any conductive or metallic surface. Fig. 2.3 shows graph of current and voltage characteristics of a semi-conductor junction and a false junction.

Fig. 2.3 IV- graphs for non-linear junctions [17]

The non-linear characteristics of semiconductor junctions differ from false junctions: the 2nd and 3rd harmonic signals will have different intensities. When a NLJD radiates a semiconductor junction, it results in a 2nd harmonic stronger than the 3rd harmonic. A false junction returns a 3rd harmonic that is stronger than the 2nd harmonic.

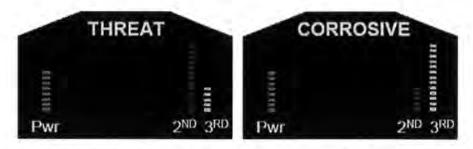

Fig. 2.4 User Interface Graph for a commercial NLJD [17]

NLJD's should have the capability to compare the received signal strength of both the 2nd and 3rd harmonic which will enable to discriminate between true semiconductor junctions and false junctions. It is also very important that NLJD's with both 2nd and 3rd harmonic receiving capabilities provide good RF isolation because the receiving functions must not interfere with each other. If it is not the case then a pure semiconductor junction may still appear to have a fairly strong 3rd harmonic and a pure false junction may appear to have a fairly strong 2nd harmonic which will lead to erroneous results. Fig. 2.4 shows the display of ORION – a commercially available Non-Linear Junction detector which displays the relative harmonic levels of both a semi-conductor and a false junction.

#### 2.3.2 Issues related to NLJD Operation

Most NLJDs on the market today transmit on a single frequency or are limited to a small frequency range. This creates three problems.

#### 2.3.2.1 Null Range Effect

If the distance between the NLJD and the target is equal to ½ the wavelength of the transmit frequency then there is a null effect in the RF transmit signal. This reduces the detection sensitivity associated with that specific range and frequency. Usually this effect is not a problem because the user is constantly moving the NLJD and therefore the range to the target is constantly changing.

#### 2.3.2.2 Target Dependence on Frequency

It is often observed that NLJD's perform differently for different targets. This is because detection range is dependent on frequency. Consider a cellular phone as a potential target. If an NLJD operates at a frequency that is within the operational band of the cellular phone, then the detection range of the phone will be large, however, if the NLJD operates at a frequency range that is outside of the operational band of the cellular phone, then the built-in filters within the phone will attenuate the NLJD signal and the detection range will be greatly reduced.

#### 2.3.2.3 Frequency Interference

If the NLJD is operating on a frequency that may also be occupied by another transmitter, the NLJD may have very erratic and unreliable readings. As more wireless devices are being assigned to more frequencies, the performance of these limited NLJD units can suffer. NLJD should be frequency agile and automatically search for quiet channels on which to operate to avoid frequency interference from other devices.

One commercial NLJD ORION<sup>TM</sup> [20] addresses the above mentioned problems using two methods: Quiet Channel Search and Frequency Hopping. In normal search mode, the ORION<sup>TM</sup> automatically searches for the quietest channels on which to operate in the ambient environment. The new frequency hopping search method employs an algorithm that constantly changes the transmit frequency over the full legal range to increase the target hit rate.

A list of popular NLJD's used in the commercial market is given in a tabular format below listing their main parameters:-

| Company           | Product    | Frequency          | Power  | Antenna       |  |

|-------------------|------------|--------------------|--------|---------------|--|

|                   |            | (MHz)              |        | Polarization  |  |

| AudioTel, U.K.    | SuperBroom | Tx - 888.5         | EIRP - | Tx - Linear   |  |

|                   |            | Rx1 - 1777         | +40dBm | Rx - Circular |  |

|                   |            | Rx2 - 2665.5       |        |               |  |

| Research          | ORION      | Tx - 850 -         |        |               |  |

| Electronics, U.K. |            | 1005               |        |               |  |

|                   |            | <b>Rx1</b> – 1700- | 1.4W   | Tx - Circular |  |

|                      |           | 2010<br><b>Rx2</b> – 2550-<br>3015 |        | Rx – Circular |

|----------------------|-----------|------------------------------------|--------|---------------|

| Surveillance         | Eclipse   | Tx - 890 - 895                     | 2 W    |               |

| Consulting Group,    |           | Rx1 - 1780 -                       |        | Tx – Circular |

| Switzerland          |           | 1790                               |        | Rx – Circular |

|                      |           |                                    |        |               |

|                      |           | Rx2 - 2670 -                       |        |               |

|                      |           | 5370                               |        |               |

| Information Security | Boomerang | Tx - 915                           | 100mW, | Tx – Linear   |

| Associates, U.S.A.   |           | Rx1 - 1830                         | 500mW  | Rx - Linear   |

|                      |           | Rx2 - 2745                         |        |               |

#### 2.3.3 Further Applications

FMCW Harmonic Radars can also be used in many other different applications such as:-

- 1. Radar Entomology i.e. tracking of insects' movements e.g. Butterflies, Bees, and Snails etc.

- 2. Unexploded Ordinance Detection (Third Harmonic Detection)

- 3. Electronic counter surveillance i.e. Detection of 'bugs' implanted by enemy agents. Professional investigators or "spies" sometimes use many electronic devices that do not utilize radio frequency transmissions. The NLJD will detect and locate any electronic device regardless of whether or not the device is powered.

- 4. Measurement of thickness of ionizing layer in space and upper atmosphere

#### 2.4 Harmonic Radar Range Equation

The basic radar range equations can be used to develop the range equation for harmonic radar. This can be subsequently used to calculate the power link budget.

Colpitts & Boiteau [18] developed the range equation for harmonic radar to be used for insect tracking. The target was a harmonic 'tag' (a dipole and an inductive loop) which would be planted on insects to track them.

The Friis Transmission equation is given as

$$P_{r} = P_{t} \frac{G_{t} G_{r} \lambda^{2}}{\left(4\pi R\right)^{2}} \tag{2.11}$$

The Harmonic Radar Range Equation can be developed in a similar manner as the conventional radar except that a harmonic cross-section should be replaced for radar cross-section. The harmonic cross-sectional area of the tag is described as follows:

$$\sigma_h = \frac{P_{dth}G_{dh}}{W_{df}} \tag{2.12}$$

where  $P_{dth}G_{dh}$  - Effective isotropic radiated power (EIRP) from the tag at the second harmonic. Its units are Watts.

$W_{df}$  - Fundamental frequency power density incident upon the tag in units of W / m<sup>2</sup>

The power density incident upon the tag is given by

$$W_{df} = \frac{P_{stf}G_{sf}}{4\pi R^2} \tag{2.13}$$

where  $P_{stf}$  - Radar transmit power

$G_{sf}$  - Gain of the transmit antenna

R - Distance between radar and tag

The EIRP of the illuminated tag is the power transmitted from the tag at the second harmonic multiplied by the antenna gain of the tag at the second harmonic.

$$(EIRP)_{tag} = P_{dth}G_{dth} = \frac{\sigma_h P_{stf}G_{sf}}{4\pi R^2}$$

(2.14)

The received second harmonic power from the tag back to the radar can be calculated as

$$P_{srh} = P_{dth} \frac{G_{dh} G_{sh} \lambda_h^2}{(4\pi R^2)} \tag{2.15}$$

where  $G_{sh}$  - Receive radar antenna gain at the second harmonic frequency

$\lambda_h$  - Harmonic wavelength

The ratio of the received second harmonic power to the radar transmit power at the fundamental frequency is given as

$$\frac{P_{srh}}{P_{stf}} = \frac{\sigma_h G_{sf} G_{sh}}{4\pi} \left[ \frac{\lambda_h}{4\pi R^2} \right]^2 \tag{2.16}$$

Jenn [19] developed a generalised harmonic radar range equation for the third harmonic given as

$$P_{r} = \frac{(P_{r}G_{r})^{\alpha}G_{r}\lambda_{3}^{2}\sigma_{h}}{(4\pi)^{\alpha+2}R^{2\alpha+2}}$$

(2.17)

where  $\alpha \approx 2.5$  is a non linear parameter determined experimentally. It varies slightly from target to target.

#### 2.5 References

- [1] Klauder J. R., Price A. C., Darlington S., and Albersheim W. J., "The Theory and Design of Chirp Radars", *The Bell System Technical Journal*, July 1960, Vol. 39, No. 4, pp 745-815

- [2] B.M. Oliver, Bell Telephone Laboratories Technical Memorandum, MM51-150-10, Case 33089, March 8, 1951

- [3] V. M. Hinostroza, "Indoor Wideband Mobile Radio Channel Characterisation System", UMIST PhD Thesis, 2002

- [4] Barrick D. E. "FMCW radar signals and digital processing". NOAA technical report, ERL 283-wpl26

- [5] Poole A. W. V., "Advanced sounding. The FMCW alternative", *Radio Science*, December 1985, Vol. 20, No. 6, pp 1609-1619.

- [6] Salous S., and Nickandrou N. "Architecture for Advanced FMCW Sounding", *International Journal in Electronics*, 1998, Vol. 84, No. 5, pp. 429-436.

- [7] Salous S., Nikandrou N., and Bajj N.F., "Digital techniques for mobile radio chirp sounders", *IEE proceedings Communications*, June 1998, Vol. 145, No. 3, pp. 191-196.

- [8] The Field Artillery Journal, March-April 1977 pp. 50-51, http://sill-www.army.mil/famag/1977/ [accessed 17<sup>th</sup> Feb. 2008]

- [9] J. Kositsky, (2001), Unexploded Ordnance (UXO) Detection by Enhanced Harmonic Radar, <a href="http://www.p2pays.org/ref/20/19401.pdf">http://www.p2pays.org/ref/20/19401.pdf</a> [accessed 17<sup>th</sup> Feb. 2008]

- [10] Gregory L. Charvat, Edward J. Rothwell, Leo C. Kempel, "Harmonic Radar Tag measurement", Michigan State University, (2003)

- [11] THOMAS H. JONES. 2000. Non-Linear Junction Detector. US006057765A.

- [12] BRUCE R. BARSUMIAN. 2000. Pulse Transmitting Non-Linear Junction Detector. US006163259A

- [13] STEVEN JOHN HOMES. 2005. Non-linear junction detector. US006897777B2

- [14] DANIEL G. JABLONSKI. 2004. System and method of radar detection of non-linear interfaces. US006765527B2

- [15] ITZHAK SCHNITZER, 2007. Radar system and method for locating and identifying objects by their non-linear echo signals

- [16] Ralph D. Thomas, (1999), The Detection of Active and Non-Active Eavesdropping Devices Buried In Walls and Furniture, http://www.pimall.com/nais/n.junction.html [accessed 17th Feb. 2008]

- [17] Thomas H. Jones, (1999), An Overview of Non-Linear Junction Detection Technology for Countersurveillance, www.reiusa.net/system/products/NJE-4000/NLJDTech.pdf [accessed 17th Feb. 2008]

- [18] Bruce G. Colpitts and Gilles Boiteau, "Harmonic Radar Transceiver Design: miniature Tags for Insect Tracking", IEEE Transactions on Antennas and Propagation, Nov. 2004, Vol. 52, No. 11, pp 2825 2831

- [19] Professor David Jenn, "Microwave Devices & Radar", Lecture Notes, Volume IV, Naval Postgraduate School, <a href="www.dcjenn.com/EC4610/VolIV(v4.7.2).pdf">www.dcjenn.com/EC4610/VolIV(v4.7.2).pdf</a> [accessed 17th Feb. 2008]

- [20] "ORION™, Non-Linear Junction Evaluator: Operating Manual" Version 2.1, (2005), Research Electronics International

- [21] S. Kingsley, S. Quegan, "Understanding Radar Systems", McGraw-Hill, 1992

# Chapter 3

## **Rusty Bolt Effect**

#### 3.1 Introduction

Radio transmission sites are vulnerable to corrosion and rusting with the passage of time. These deteriorations can appear randomly at different locations which can be scattered over the entire site. They can result in erroneous frequency transmissions. The main reason of the appearance of these impairments is a phenomenon called as the 'Rusty Bolt Effect'.

Radio sites consist naturally of metallic structures. Metals are always covered by an oxide film due to the metal reacting chemically with the oxygen in air. The rate of this oxide formation depends largely on the environment. Any oxide film between metallic contacts will cause non-linearity.

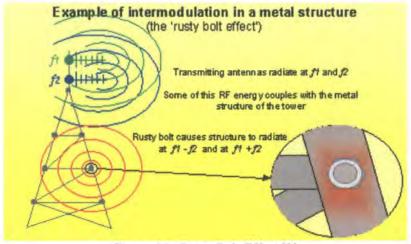

RF currents passing through these junctions would generate harmonics. When RF signals at two frequencies  $f_1$  and  $f_2$  pass through a non-linearity they create signals at their sum and difference frequencies  $(f_1 - f_2)$  and  $(f_1 + f_2)$ . These are known as 'intermodulation products'. This generation of inter-modulation products when radio waves interact with rusty parts is called as the 'Rusty Bolt Effect'. It is also known as passive inter-modulation abbreviated as PIM.

Figure 3.1: Rusty Bolt Effect [1]

Radio spectrum is carefully controlled for optimal usage of the available frequencies so that different services operate in well-defined frequency channels. Inter-modulation creates frequencies that can be difficult to control and would cause interference in channels reserved for other uses. Studies have shown that PIM distortion has caused problems in naval and land communication systems. [2]

PIM distortion was first identified during the early 1940's [3]. Studies were done on systems with antennas containing rusty-bolt parts. The detailed understanding of the phenomenon was not present at that time but the idea of rust prevention to reduce PIM was known.

#### 3.2 Passive Intermodulation

#### 3.2.1 Mathematical Representation

PIM components can be represented using mathematical equations. Consider current passing through a rusty point. The relationship between current and voltage will not be completely linear. It will contain harmonic frequencies and their linear combinations.

The voltage transfer characteristic of a non-linear system can be described as

$$v_i(t) = a_1 v_i(t) + a_2 v_i^2(t) + a_3 v_i^3(t) + \dots$$

(3.1)

Consider an input signal consisting of two sinusoidal frequencies  $\omega_1$  and  $\omega_2$  represented as

$$V_i(t) = A_1 \cos(\omega_1 t) + A_2 \cos(\omega_2 t) \tag{3.2}$$

where  $\omega = 2\pi f$

The contribution from the second term is given as

$$a_{2}v_{i}^{2}(t) = a_{2}[A_{1}cos(\omega_{1}t) + A_{2}cos(\omega_{2}t)]^{2}$$

$$= a_{2}[A_{2}cos^{2}(\omega_{1}t) + B_{2}cos^{2}(\omega_{2}t)] + 2A_{1}A_{2}cos(\omega_{1}t)cos(\omega_{2}t)]$$

(3.3)

Using the trigonometric relation

$$\cos^2\theta = (1 + \cos 2\theta)/2$$

we can reduce Eq. (3.3) to

$$a_{2}v_{i}^{2}(t) = a_{2}(A_{1}^{2}/2 + A_{2}^{2}/2 + 1/2A_{1}^{2}\cos 2\omega_{1}t + 1/2A_{2}^{2}\cos 2\omega_{2}t + 2A_{1}A_{2}\cos \omega_{1}t\cos \omega_{2}t]$$

(3.4)

Using the trigonometric relation,

$$cos(\theta_1 + \theta_2) + cos(\theta_1 - \theta_2) = 2cos\theta_1 cos\theta_2$$

Eq. (3.4) can be converted to

$$a_{2}v_{1}^{2}(t) = a_{2}[1/2(A_{1}^{2} + A_{2}^{2}) + 1/2(A_{1}^{2}\cos 2\omega_{1}t + A_{2}^{2}\cos 2\omega_{2}t) + A_{1}A_{2}\{\cos(\omega_{1} + \omega_{2})t\cos(\omega_{1} - \omega_{2})t\}]$$

(3.5)

We can see the output contains dc component, second harmonics of the input frequencies and intermodulation products at the sum and difference frequencies. Consequently, from Equation (3.5) third, fourth and higher harmonics will be present depending on the non-linear characteristic.

#### 3.2.2 MPT 1331: Code of Practice for Radio Site Engineering

In order to assist radio system designers to minimise such interferences, Ofcom has set some standards for radio site engineering. This set of standards is given in the document 'MPT 1331: Code of Practice for Radio Site Engineering'.

Sections of the code emphasize on different aspects of radio engineering to make the sites operate effectively. Section (3.1) deals with the sources of generation of unwanted inter-modulation products, Section (3.4) describes the Corrosion & Climatic effects on the radio sites and Section (5) describes some recommendations to control inter-modulation and unwanted products. [6]

Any transmission site which is not following these codes would likely cause interference to other users. It is important that radio engineers should check the sites for their compliance with these codes.

If a particular radio site is causing interference due to the rusty-bolt effect, the corroded points must be located to minimize their effect.

#### 3.3 Localization Techniques

#### 3.3.1 Audio Detector – Laboratory Model

An audio detection technique can be used to demonstrate the presence of PIM products. One such system was developed by Bailey [4] as a 'rusty-bolt simulator'.

The system consists of two oscillators of known frequencies representing two signals. These are then mixed using a diode. The resultant frequency is then mixed with another frequency provided by a variable frequency oscillator (VFO). The VFO can be tuned so that the output of the mixer remains between 2 and 8 kHz. This can then be detected using a speaker.

In the lab demonstrating kit mentioned above, two oscillator frequencies were 4 and 6 MHz, the intermodulation frequency was 10 MHz and the VFO was 9.992-9.998 MHz.

#### 3.3.2 Microwave Holographic Imaging

Microwave Holographic Imaging is a well established and an efficient technique to locate PIM sources.

Aspden et al. [5] have used this technique to image intermodulation product sources on reflector antennas. Two signal sources at 7.2GHz and 7.7GHz illuminate a parabolic reflector. It is then scanned for the third order IMP at 8.2GHz. This was done by trying to lock the received signal with a reference signal. The reference IMP signal is generated by a non-linear diode.

#### 3.4 References

- [1] Preventing Intermodulation, Radio communications Agency: EMC Awareness, www.ofcom.org.uk/static/archive/ra/topics/research/RAwebPages/Radiocomms/pages/mittech/install/intermod.htm [accessed 2<sup>nd</sup> May, 2007]

- [2] P. L. Lui, "Passive intermodulation interference in communication systems," *Electron. Commun. Eng. J.*, vol. 2, pp. 109–118, June 1990.

- [3] Reuven Shavit, (2003) "Intermodulation Distortion in Metal Space Frame Radomes", www.l-3com.com/essco/resources/IMP-MSF.pdf [accessed 20th Feb. 2008]

- [4] Brandt Bailey, John Schneider (1999), Rusty Bolt Simulator, www.ece.ndsu.nodak.edu/~glower/design/projects/sp99/90\_rust.pdf, [accessed 20th Feb. 2008]

- [5] Aspden, P.L. Anderson, A.P. Bennett, J.C., "Microwave holographic imaging of intermodulation product sourcesapplied to reflector antennas", *Antennas and Propagation*, 1989. ICAP 89., Sixth International Conference on , 463-467 vol., Apr 1989

- [6] "MPT 1331 : Code of Practice for Radio Site Engineering", June 2001, Flyde Microsystems Ltd.

# Chapter 4

## System Description

#### 4.1 Introduction

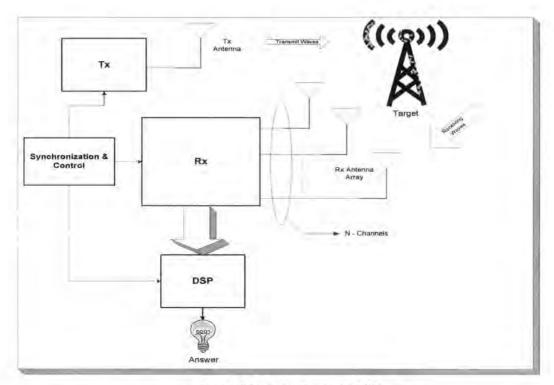

The Harmonic Radar envisioned for the project is a mono-static wideband FMCW radar system with a suitable receive antenna array. The received waves would then be processed using super-resolution algorithms to accurately locate the target. A conceptual diagram of such a system is shown in Fig 4.1.

Figure 4.1 System Conceptual Diagram

The 'Tx' block represents the transmitter which transmits a frequency at 1GHz. The 'Rx' block represents the receiver. It can receive the harmonic frequencies at 2GHz, 3GHz and so on through an antenna array. The DSP represents the digital signal processing block which processes the data. There is also a need for a separate subsystem that would control and synchronize between the three distinct blocks.

## 4.1 System Design

Figure 4.1: Detailed System Diagram

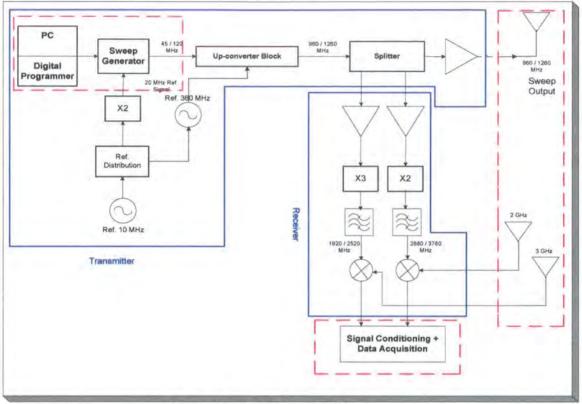

Figure 4.2 shows a detailed system diagram of the transmitter and receiver described in the previous section. The blue lines clearly mark their respective outlines.

#### 4.1.1 Transmitter

The transmitter can be broadly described in two main sub-systems.

- 1. Chirp Generator

- 2. Up conversion Block

The chirp generator is the block that produces the sweep wave output. It works on a reference signal of 20MHz and produces an output frequency sweep of 45-120 MHz. More on this part is described in section 4.3. The sweep generator works on a reference frequency of 20 MHz. The system reference signal is produced by a 10 MHz oscillator. This signal is then fed to a reference distribution board that provides this reference signal to different components. Two of these signals are shown in the

diagram. The first is multiplied with a 'times two' multiplier to provide the reference signal for the sweep generator. The second provides the reference signal for the PLL synthesizer that produces a signal of 360 MHz which is then used in the upconversion block.

The up conversion block is a complex sub-system required to up-convert the sweep frequencies coming from the chirp generator to the required transmit sweep centring at 1 GHz. The required output sweep from the up-converter block is 960 – 1260 MHz. This would realistically require stages of up-conversion from the lower frequency to intermediate levels and then to the RF level. This would translate to the use of components of mixers, LO's (local oscillators), multipliers, amplifiers and band-pass filters to remove the spurious frequencies. The RF frequency is then split into three parts. One is transmitted after amplifying through a high power amplifier. The other two are then passed onto to the receiver to be used in the channels for superheterodyne down-conversion.

#### 4.2.2 Harmonic Receiver

The harmonic receiver primarily consists of two main channels. It will receive the harmonics of the transmit frequency at 2GHz and 3GHz through a receive antenna array. The two down-conversion channels coming from the transmitter are amplified and then up-converted using 'times two' and 'times three' multipliers. The output is then filtered to give a clean signal at 1920 - 2520 MHz and 2880 - 3780 MHz respectively. These two channels are needed to perform super heterodyne down conversion on the receiving harmonic waves. This down-conversion is performed using two mixers.

The output of the mixers would be converted to digital data. It can then be digitally processed using advanced algorithms to obtain useful information. A detailed description on the signal processing can be found in Chapter 5.

#### 4.2.3 Antenna Array

The radar antenna array is an important part of the system. The system requires one transmit antenna and two or more receive antennas. The important factors deciding the selection of antenna are:-

- Bandwidth, and

- Directivity

Bandwidth of any antenna can be defined as the maximum frequency range over which the antenna meets a defined specification. [1] Therefore, the system requirements are a directional antenna covering a wide bandwidth for transmitter (960-1260 MHz) and receiver array (1920-2520 MHz and 2880-3780MHz). Different antennas were studied in literature that would satisfy these two main conditions. A good option would be horn antennas which have been mentioned in literature. [2]

Figure 4.3: Log-Periodic Antennas (900-2600 MHz) [4]

The candidate wideband directional antennas are:-

- 1. Horn

- 2. Log-Periodic

- 3. Discone

- 4. Modified Patch Antennas

- 5. Conical Spiral with cavity

- 6. Log Spiral with cavity

Log-periodic antennas were ordered as shown in Figure 4.3 depending on the availability and price.

#### 4.3 Chirp Generator

The chirp or sweep generator produces a signal that varies in frequency from 45 MHz to 120 MHz and remains constant in amplitude. It consists of two main parts:-

- 1. DDFS (Direct Digital Frequency Synthesizer) Board

- 2. Digital Programmer

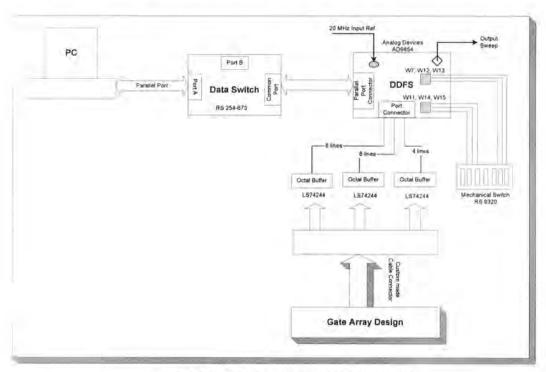

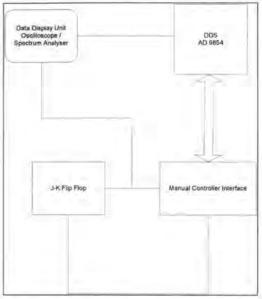

A block diagram of the digital programmer with the DDFS board is shown in Fig. 4.4

Figure 4.4 Digital Programmer with DDFS board

#### 4.3.1 DDFS Board - AD9854

DDFS - Direct Digital Frequency synthesis is a method to create arbitrary waveforms and frequencies from a single, fixed source frequency using digital processing blocks. The DDS board used in the chirp generator is Analog Devices AD 9854. The AD9854 can generate highly stable, frequency-phase, amplitude-programmable sine and cosine

outputs that can be used in many applications. Some of the available features of this board are:-

| Programmable Ref. CLK Multiplier | - | 4 to 20 |

|----------------------------------|---|---------|

| Control Register Data            | - | 8 bits  |

| Control Register Address         | - | 6 bits  |

| Frequency Resolution             | - | 48 bits |

| Frequency Step Resolution        | - | 48 bits |

The AD9854 has five programmable operational modes. Three bits in the control register called as Mode 0, Mode 1 and Mode 2 must be programmed to select the type of operation. The different mode bits selections and their result are shown in table below:

| Mode 2 | Mode 1 | Mode 0 | Result      |

|--------|--------|--------|-------------|

| 0      | 0      | 0      | Single Tone |

| 0      | 0      | 1      | FSK         |

| 0      | 1      | 0      | Ramped FSK  |

| 0      | 1      | 1      | Chirp       |

| 1      | 0      | 0      | BPSK        |

The AD9854 supports linear as well as nonlinear FM sweep patterns. The different parameters needed to program the chirp mode are:-

- Start Frequency Tuning Word (FTW 1)

- Time steps (Ramp rate)

- Frequency steps (Delta frequency)

- I/O UD Clock

- Clear Accumulator 1 Bit (CLR ACC1)

Other controlling parameters present on the DDS board are:-

- Clear Accumulator 2 Bit (CLR ACC2)

- FSK bit (Frequency Shift Keying)

- BPSK bit (Binary Phase Shift Keying)

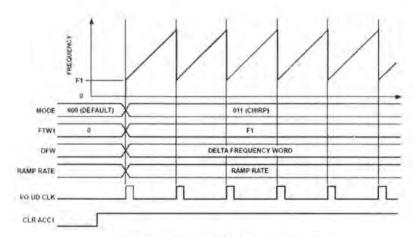

Figure 4.5 Chirp Mode Operation [3]

Fig. 4.5 illustrates the functioning of a simple chirp mode. It is important to note that FTW1 is only a starting point for FM chirp. There is no built-in restraint requiring a return to FTW1. However, instant return to FTW1 can be achieved by interrupting the current chirp, reset the frequency back to FTW1, and continue the chirp at the previously programmed rate and direction.

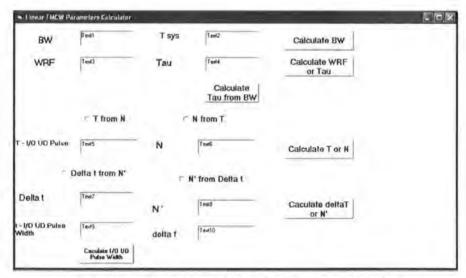

A program was developed in Visual Basic that would calculate all the required Chirp mode parameters. The user interface of this program is shown in Figure 4.6

Figure 4.6: User Interface of Chirp Mode Parameter Calculator

This program uses a set of standard equations available in literature to calculate the required parameters. The equations are described below:

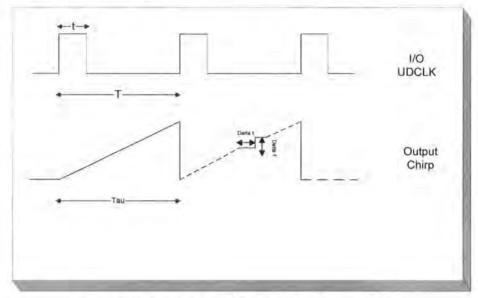

Figure 4.7: Relationship of I/OUDCLK and Output Chirp

All the equations that follow refer to figure 4.7 above.

The time period T of the chirp is related to the system clock by the relation

$$T = (N+1)(T_{sys} \times 2) \tag{4.1}$$

where  $T_{sys}$  is the DDFS system clock.

The time step value in Fig. 4.5 is  $\Delta t$ . It is related to the system clock with a counter N'. Their relation is given as

$$\Delta t = (N'+1)(T_{sys}) \tag{4.2}$$

The width of the I/O UDCLK pulse is related to the system clock by

$$t = 8T_{sys} \tag{4.3}$$

By definition of BW,

$$BW = n\Delta f \tag{4.4}$$

The relation of time period and step-time for the chirp is given as

$$n = \frac{\tau}{\Delta t} \tag{4.5}$$

Replacing Eq. (4.5) into Eq. (4.4) gives us

$$BW = \tau \frac{\Delta f}{\Delta t} \tag{4.6}$$

But since

$$\tau = T \tag{4.7}$$

Therefore we have,

$$\frac{BW}{T} = \frac{\Delta f}{\Delta t} \tag{4.8}$$

These equations have been used in the VB program to calculate the required parameters to generate a chirp depending on the parameters entered by the user.

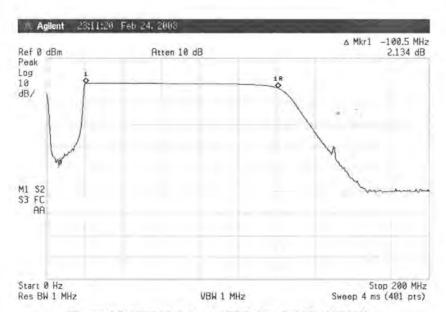

Figure 4.8 AD9854 Output - Wide Bandwidth (100 MHz)

AD9854 is capable of producing a wide bandwidth clean signal. Fig 4.8 shows the output from the DDS board on a spectrum analyzer. It has constant amplitude from 10 to 110 MHz giving a clean bandwidth of around 100 MHz.

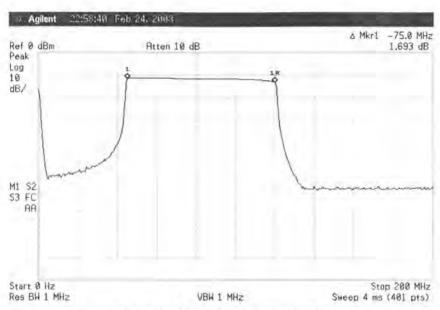

Figure 4.9 AD9854 Output - 45/120 MHz

Fig 4.9 shows the output from AD9854 when operating in the sweep generator. It produces a sweep from 45 MHz to 120 MHz with almost constant amplitude. The bandwidth thus achieved is 75 MHz.

#### 5.3.1.1 Waveform Designing

Waveform designing is an important area of research in radar signals. The type and quality of information received by radar depend in part on the waveform it transmits. Efficient waveforms minimize the ambiguities present in FMCW radar system. One such practical solution has been presented by Salous [5] where a multiple WRF signal was introduced as a solution to range/Doppler ambiguity. This goes back to the pioneering work by Poole [6] where he introduced a multi-cell waveform.

More advanced waveforms than the basic linear chirp signal were studied to be implemented with the DDS AD9854. The result has been summarized in the table below:-

| Waveforms                | AD9854 Signals Used             |  |  |

|--------------------------|---------------------------------|--|--|

| 1. Linear Chirp          | I/O UDCLK, CLRACC1              |  |  |

| 2. Triangular Modulation | I/O UDCLK, FSK/BPSK bit (Ramped |  |  |

|                        | FSK Mode)                                                                                                                                                               |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3. Linear FM Ranging   | I/O UDCLK, CLRACC2 (A variant of Chirp Mode)                                                                                                                            |

| 4. Segmented Linear FM | I/O UDCLK, FSK/BPSK bit, CLRACC2                                                                                                                                        |

| 5. Multi-cell Chirp    | Not possible without adding external hardware circuit                                                                                                                   |

| 6. Staggered WRF       | This can be programmed in the Chirp mode using the signals I/O UDCLK, CLRACC1. The critical part would be programming new Δf and/or Δt values after every single chirp. |

| 7. Multiple WRF        | This is the same as above except that new $\Delta f$ and/or $\Delta t$ values must be programmed after a number of individual chirps as defined by the WRF.             |

#### 5.3.1.2 Phase Coherency

An important consideration is the phase component of the transmitting signal. The Chirp mode by default has an internal problem for our applications. The CLR ACC1 signal only clears the Frequency Accumulator. It does not affect the Phase Accumulator value. The frequency changes of the DDS become phase continuous, but not phase coherent. When a new frequency is programmed into the DDS, the next phase will simply be incremental with respect to the last phase value in the phase accumulator, and therefore the output sine wave will be phase continuous.

This phase continuity will cause a problem in the harmonic detector. There will always be a phase component present in the transmitting signal and therefore in the receiving signal. This phase component will appear as a Doppler or a movement / velocity in the end data. Thus, if the DDS is used as such, it will show a Doppler component of an object without any actual movement present.

Some modifications either in the source code of the program or with some additional external hardware circuitry is needed to clear the phase accumulator along with the frequency accumulator.

The CLR ACC2 control bit (Register Address 1F hex) is available to clear both the frequency accumulator (ACC1) and the phase accumulator (ACC2). When this bit is set high, the output of the phase accumulator results in 0 Hz output from the DDS. As long as this bit is set high, the frequency and phase accumulators are cleared, resulting in 0 Hz output. To return to the previous DDS operation, CLR ACC2 must be set to logic low. This bit can be used to clear the phase of the signal along with the amplitude.

However, we cannot afford to keep the CLR ACC2 bit high for a long duration. Otherwise it will result in an ON/OFF Keying pattern.

Solutions were designed so as to clear the ACC2 bit before the start of the next chirp. This would require a number of steps as follows:

- The DDS board should be programmed from a circuitry controlled by the user. For this, a cable was built to connect the junction pins on the board with a test board. These pins can then be used to control the DDS by sending in appropriate control commands at the correct addresses.

- The CLR ACC2 bit requires a signal that would clear the output in between the end of the first chirp and start of the next chirp. This 'high' time should be as low as possible so as not to severely distort the shape of the end waveform.

Figure 4.10: Block diagram of external hardware Figure 4.11: Block diagram of external to generate the CLR ACC2 signal

hardware to generate the CLR ACC2 signal

The circuit performs the following functions:

- All the signals provided in the junction J10 on the DDS board are connected to a test board via a cable.

- 2. The Manual Controller allows the user to send control words at appropriate addresses.

- 3. The I/O Update Clock is then sent to a mono stable multi-vibrator (74121) which generates a longer version of the UD CLK pulse width depending on the resistor and capacitor values selected.

- 4. This longer pulse was then sent as CLR ACC2 signal back to the DDS board through the manual controller.

This solution did not work. The reason for this was that the output of the multivibrator occurs after a certain amount of delay from the input UD CLK signal. For the phase accumulator to be cleared, the two signals I/O UD CLK and CLR ACC2 must start at exactly the same time.

A slight modification in the circuit can achieve this quite easily. An additional OR gate was added to the circuit as shown in Fig. 4.10

- 1. One input to the OR gate is the I/O UD CLK signal.

- 2. The other input is the output of the multi vibrator signal.

- 3. The output signal from the OR gate would be a wider pulse that starts at exactly the same time as the I/O UD CLK. This signal was then sent as the CLR ACC2 signal to the DDS board through the manual controller.

This solution also failed to clear the phase accumulator.

In order to diagnose the problem, an attempt was made to provide such signals which are the exact replica as that in Fig 4.11. The CLR ACC2 signal has a period that is the exact twice of the I/O UD CLK period. Such a signal can be generated using a J-K Flip Flop. The block diagram of such a circuit is shown in Fig. 4.11.

- 1. The I/O UD CLK signal is sent from the manual controller to a J-K Flip Flop.

- 2. The J-K Flip Flop is set in a toggle mode.

- 3. It then generates a signal that has a period exact twice that of the I/O UD CLK.

- 4. This signal is then sent as the CLR ACC2 signal to the DDS board via the manual controller.

This design does clear the phase at the start of every chirp. However, it also clears the amplitude for the whole pulse duration and there is no chirp during this time. A gate array design has been envisioned to solve this problem. Further details of it are given in section 4.3.2.

#### 4.3.2 Digital Programmer

The digital programmer is supposed to program the DDFS board according to the parameters selected by the user. A further task in this sweep generator is to reset the phase after every sweep as identified in section 4.3.1.

There can be two variants to this digital programmer. One based on a 'C' program being controlled through a PC or the other being a gate array design. Efforts were made on both variants of the design. Both designs are explained below:-

#### 5.3.2.1 C based Design

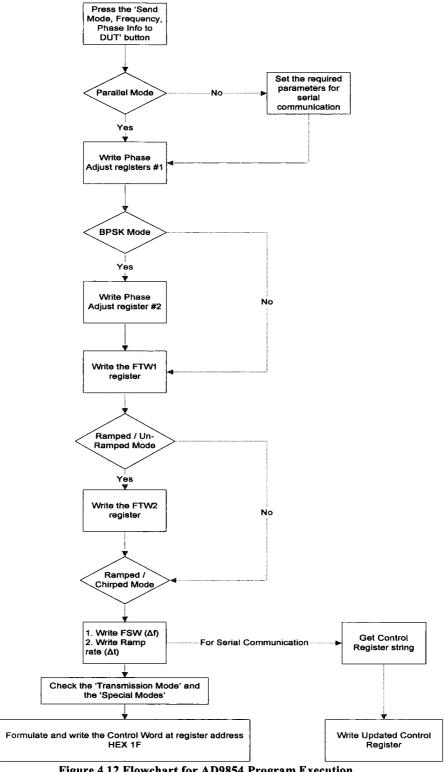

The 'C' code should emulate the entire program execution of the DDS AD9854. A flowchart of the steps carried out to program the DDS board is shown in Figure 4.12. There are three main parts to program the DDFS

- Accessing the parallel port

- Calculating the chirp parameters

- Sending appropriate data with address and control signals to program the DDFS.

Such a 'C' language code was written using the DOS based C-compiler TC++v3. The code listing of this is provided in A 3.1

Figure 4.12 Flowchart for AD9854 Program Execution

The code has limited success in its limitation. The data send by the programmer (laptop) can be traced on the registers and buffers on the DDFS board but it is not being read by the AD9854 chip. One possible reason might be the RD (read) and WR (write) signals. Their timing is crucial in writing any data to the chip. The code controls these signals and is using an arbitrary 'delay' value. It has been decided that the gate array design would be pursued to completion.

#### 5.3.2.2 Gate Array Design

There are two variants of the Gate Array Design.

Full Extensive VHDL code design

The VHDL code was designed by another worker. The design consists of 7 functional modules, each concerned with a specific task. Each module carries out its task in consequence to external inputs or from one or more of the other modules. Many of the individual block modules work but some modules and their integrated simulation are not entirely correct.

Some reasons attributed to this are as follows:-

- a. Code was previously developed for Xilinx compiler tools

- b. Some commands were specific for the Xilinx FPGAs which are not valid in Altera's Quartus compiler

- c. Some of the numerical factors used in the design are specific to the board and the clock frequency being tested for. It was mistakenly taken as absolute values.

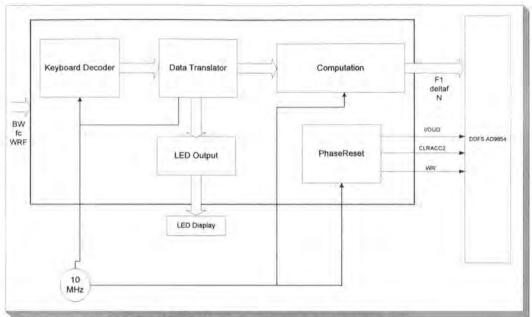

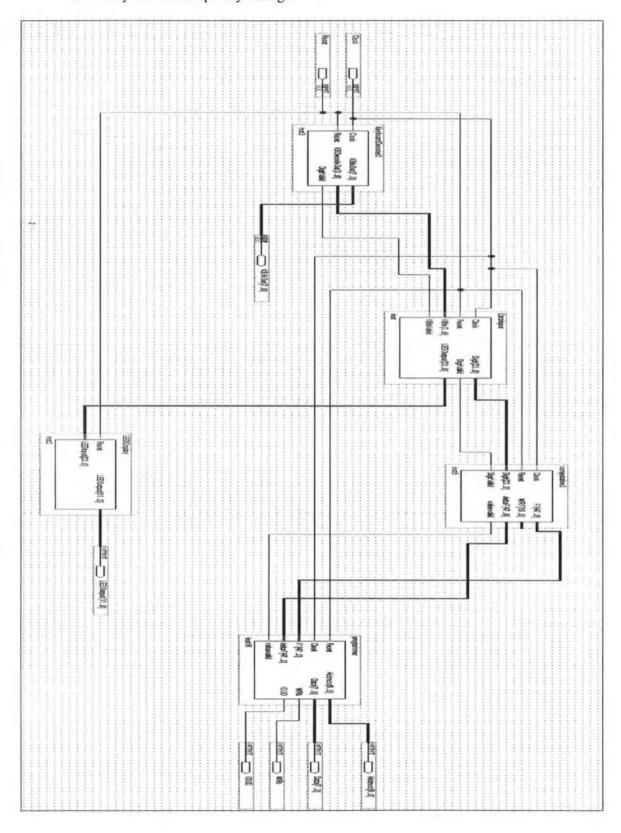

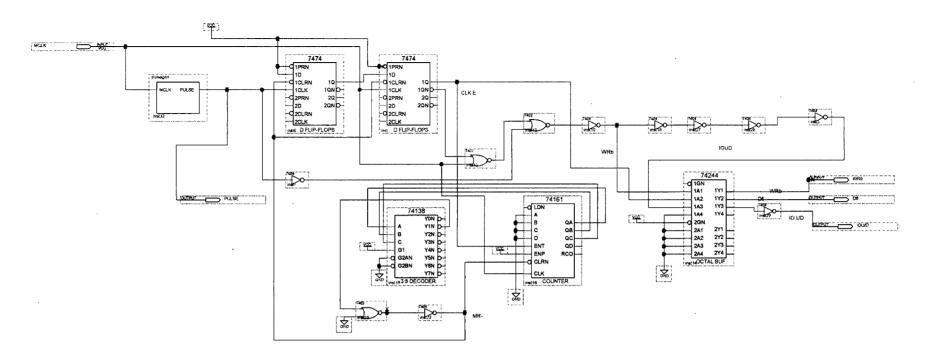

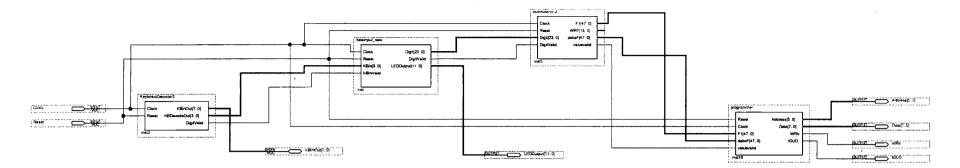

Figure 4.13 Modular Representation of Gate Array Design

Simpler Design (VHDL + Schematics)

Figure 4.13 shows a design that is almost in state of completion at the time of writing this document. This gate array design consists of a mixture of VHDL code and hardware schematics. They can be viewed in Appendices 1-2.

The modules 'keyboard decoder', 'data translator' and 'LED Output' were designed by another worker. They were tested successfully with the new compiler and simulated. The two blocks 'PhaseReset' and 'Computation' were designed. They are described as follows:-

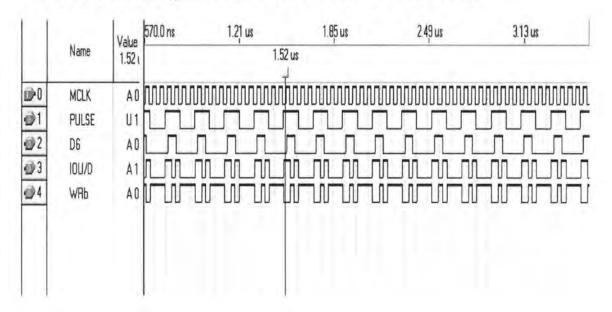

#### Phase Reset Module

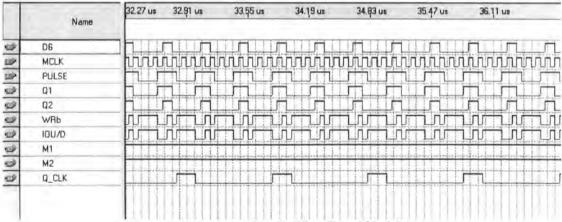

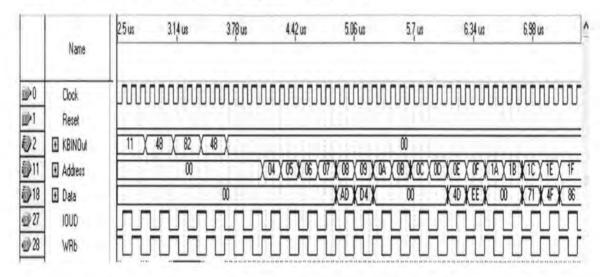

Figure 4.14 Simulation Result: 'PhaseReset' Module

The 'PhaseReset' module is designed using a hardware schematic as shown in Appendix A1.1. Its simulation result is shown in Figure 4.14 above. The three output signals going to the DDFS are I/OUD, WRb and D6 (CLRACC2). The other outputs shown in the simulation were tapped to observe the behaviour of the circuit.

#### Computation Module

The computation module is supposed to calculate the values required to program the DDFS. It takes the values coming from the Data Translator module and is supposed to output to the DDFS. The schematic is shown in A1.2

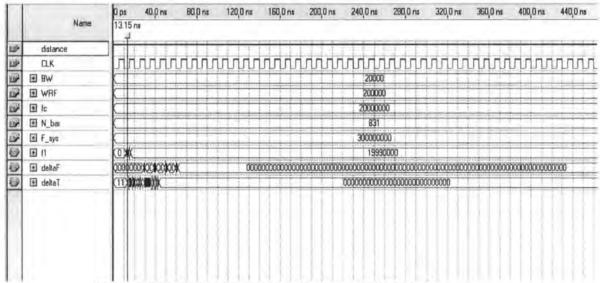

Figure 4.15 Simulation Result: 'compnew' module (Real values)

Figure 4.15 shows the simulation result of this module when the input numerals are actual values for the board. The zero result shows either the circuit is not working or the values are going out of range for the present design. To check the validity of the circuit, it was simulated for simpler values. The simulation result is shown in Fig. 4.16 below.

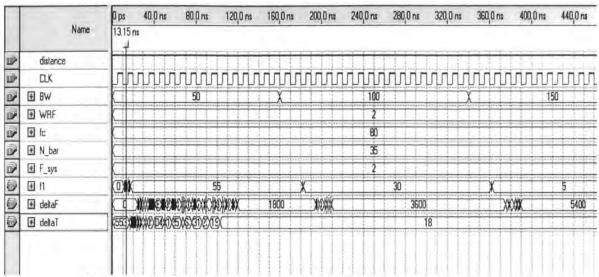

Figure 4.16 Simulation Result: 'compnew' module (Simpler values)

The output signals are correct which validates the working of the circuit. An attempt was also made to design this module using VHDL code given in Appendix A2.1. There is a numerical factor that goes outside the 'integer' range as defined by the compiler. It is a probable reason for a zero output.

'PULSE' Control Signal Generation for Phase-Reset Module

#### Comments:

1. The simulation is for 10 MHz clock.

- 2. A MAX7000 family device is sufficient to compile this design.

- 3. The 'Pulse' generator block has been added which is a VHDL code for a 'divide-by-4 clock frequency' design.

#### Simulation Results

The final simulation result for the design is shown below.

To clarify the inputs and outputs, a test output "KBDecodeOut" is added to the result. The output is shown in the following figures:-

| <u>m</u> >0              | Clock            |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------|------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>D</u> 1               | Reset            |                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <b>⊉</b> 1<br><b>₽</b> 2 | <b>⊞</b> KBINOut | (\(14\)\(41\)\(48\)\(82\)\(22\)\(48\)\(82\)\(11\)\(48\)\(82\)\(48\) | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |