## **Durham E-Theses**

# Organic transistors based on pentacene and dibenzothiophene derivatives

Kolb, Daniel

#### How to cite:

Kolb, Daniel (2008) Organic transistors based on pentacene and dibenzothiophene derivatives, Durham theses, Durham University. Available at Durham E-Theses Online: <a href="http://etheses.dur.ac.uk/2189/">http://etheses.dur.ac.uk/2189/</a>

#### Use policy

The full-text may be used and/or reproduced, and given to third parties in any format or medium, without prior permission or charge, for personal research or study, educational, or not-for-profit purposes provided that:

- a full bibliographic reference is made to the original source

- a link is made to the metadata record in Durham E-Theses

- the full-text is not changed in any way

The full-text must not be sold in any format or medium without the formal permission of the copyright holders.

Please consult the full Durham E-Theses policy for further details.

The copyright of this thesis rests with the author or the university to which it was submitted. No quotation from it, or information derived from it may be published without the prior written consent of the author or university, and any information derived from it should be acknowledged.

## Organic Transistors based on Pentacene and Dibenzothiophene derivatives

by

Daniel Kolb, BA (Oxon) MSc (Lond)

Submitted in conformity with the requirements for the degree of Doctor of Philosophy School of Engineering University of Durham

Copyright © 2008 by Daniel Kolb, BA (Oxon) MSc (Lond)

### **Declaration**

I hereby declare that the work reported in this thesis has not previously been submitted for any degree and is not being currently submitted in candidature for any other degree.

The work in this thesis was carried out by the candidate

Signed. McPetty.

Director of Studies

## Copyright Notice

The copyright of this thesis rests with the author. No quotation from it should be published without their prior written consent and information derived from it should be acknowledged.

### Acknowledgements

There are a number of people without whom this thesis would not have been possible. Firstly, my supervisor Prof. Mike Petty, for his support and guidance throughout this project. His enthusiasm and insight have been fundamental to the success of this work. From the Molecular Electronics and Microsystems group, I would like to thank Chris Pearson, Andrew Gallant and Mark Rosamond for training me to use the laboratory apparatus, and Mohammed Mabrook for his help with some of the experimental work. For the X-Ray Photoelectron Spectroscopy measurements I thank Prof. Jas Pal Badyal, and Wayne Schofield, of the Department of Chemistry.

The work on PMMA dielectrics would not have been possible without the assistance of Ben Shuler, a final-year project student. The hafnium oxide depositions would not have taken place without the collaboration between the University of Durham and the National Technical University of Athens — for this I thank Prof. Dimitris Tsoukalas, Emanuele Verrelli and Panos Dimitrakis of the NTUA.

Finally, I would like to thank Prof. Martin Bryce and Changsheng Wang, of the Department of Chemistry, and Igor Perepichka and Irene Perepichka, formerly of the Department of Chemistry, for synthesising the dibenzothiophenebased molecules used in this work.

#### Abstract

## Organic Transistors based on Pentacene and Dibenzothiophene derivatives

Daniel Kolb, BA (Oxon) MSc (Lond)

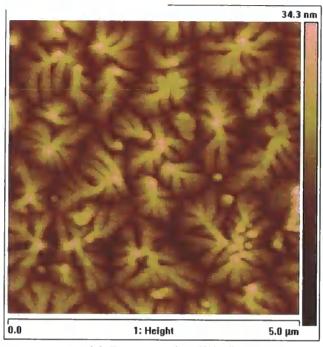

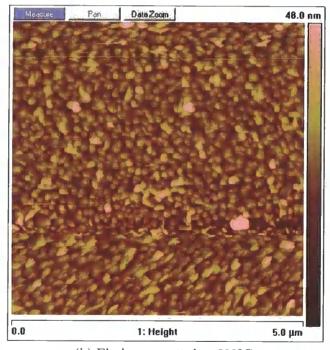

This thesis is concerned with the fabrication and characterisation of organic thin film transistors. Initially, pentacene thin films were investigated, with results comparable to those found in published literature. Initial studies of pentacene transistors revealed a poor hole mobility of  $6.3 \times 10^{-3}$  cm<sup>2</sup>/V/s. Improvements in the fabrication process (using a more conductive silicon wafer as the gate, and treating the silicon oxide surface with a silanising agent) increased the mobility to around 0.1 cm<sup>2</sup>/V/s. Better pentacene deposition conditions allowed a polycrystalline structure to form, with dendritic grains of the order of 2–3 µm in size. This increased the mobility of the transistor further, to 0.54 cm<sup>2</sup>/V/s.

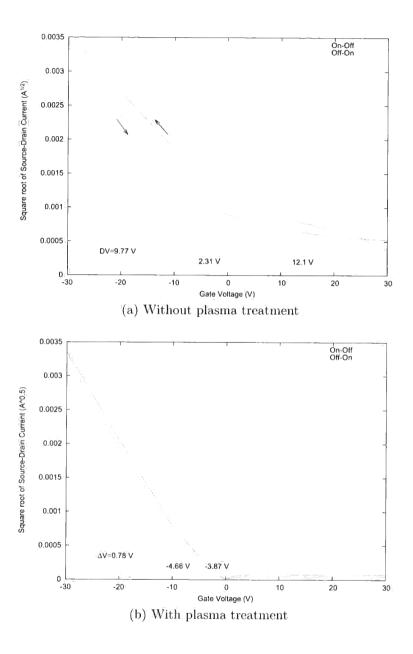

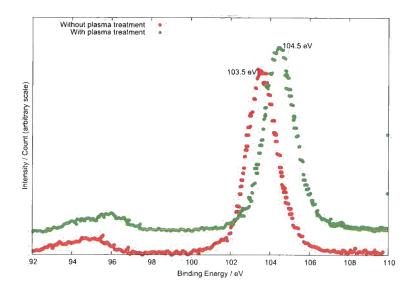

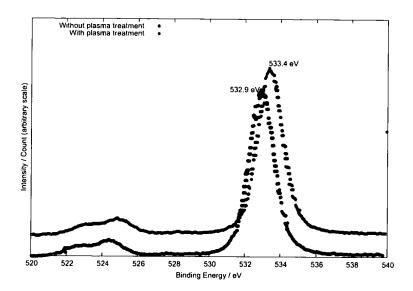

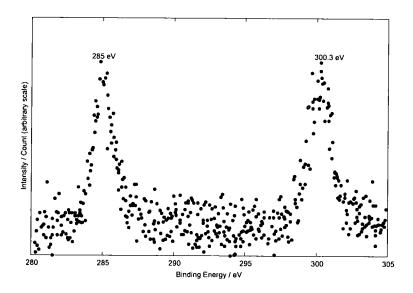

Treatment of the silicon oxide surface prior to pentacene deposition was found to affect significantly the hysteresis in the transfer characteristics. Removal of photoresist with acetone and propan-2-ol prior to pentacene deposition resulted in fairly large threshold voltages, with an average shift between the off-on and on-off threshold voltages of 9.7 V. Application of an oxygen plasma prior to deposition resulted in decreased threshold voltages, and a reduced threshold voltage shift of 3.8 V. The hysteresis was attributed to charge trapping on the oxide surface due to organic contamination; the oxygen plasma served to reduce this. X-Ray Photoelectron Spectroscopy measurements confirmed this — following a plasma treatment, the carbon content on the surface was reduced significantly. Incorporation of a layer of gold nanoparticles between the oxide and pentacene was found to provide charge traps — this might be exploited in memory devices.

Replacing the silicon oxide with PMMA produced favorable results. Negative threshold voltages with low hysteresis were observed for all the devices. Mobilities of up to 0.21 cm<sup>2</sup>/V/s were recorded for devices with a 124 nm PMMA layer; a thinner (80 nm) layer of PMMA resulted in reduced mobility, as did a thicker (350 nm) layer.

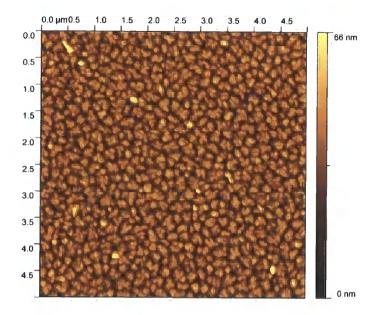

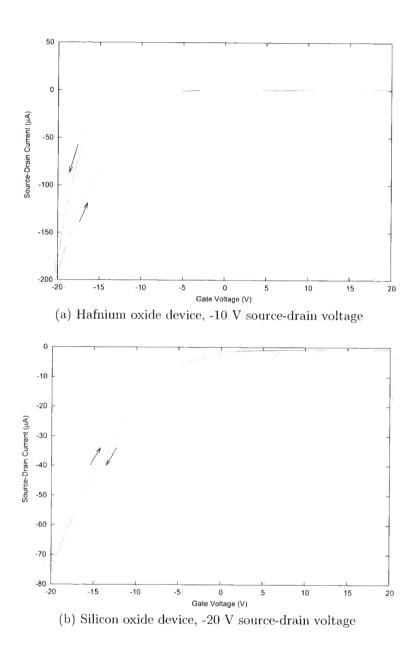

Replacing the silicon oxide with sputtered hafnium oxide produced devices with a large number of defects. Deposited pentacene did not form optimal crystal structures, and the output characteristics of a number of devices showed no significant variation with source-drain voltage. These output characteristics were therefore assumed to be the result of leakage through the oxide. The measured device that showed reasonable output characteristics was found to have a mobility of  $0.59~\rm cm^2/V/s$ , demonstrating that hafnium oxide could have good potential as a dielectric, if deposited in a manner not resulting in a leaky oxide.

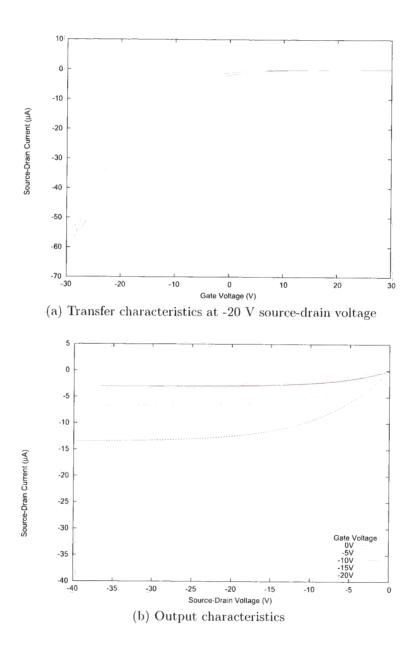

Three dibenzothiophene-based molecules, synthesised in the University of Durham, were characterised and thin film transistors fabricated. 3,7-bis(dibenzothiophene-4-yl)-dibenzothiophene-S,S-dioxide exhibited the characteristics of an air-stable n-type device, with a mobility of  $3.5 \times 10^{-6}$  cm<sup>2</sup>/V/s. A related molecule, 3,7-bis(4-(ethylsulfonyl)phenyl)dibenzo[b,d]thiophene, incorporating additional electron-deficient groups, did not exhibit any field-effect-modified behaviour. A third molecule, that did not contain electron-deficient groups, exhibited p-type behaviour, and transistors showed good output characteristics, but only possessed a mobility of  $3.7 \times 10^{-5}$  cm<sup>2</sup>/V/s; the low mobility was attributed to the lack of long-range order in the structure of the deposited film.

## **Contents**

| 1 | Inti                                   | Introduction |                                      |    |  |

|---|----------------------------------------|--------------|--------------------------------------|----|--|

| 2 | Organic Semiconductors and Transistors |              |                                      | 3  |  |

|   | 2.1                                    | Introd       | uction                               | 3  |  |

|   | 2.2                                    | Electro      | onic structure of atoms              | 4  |  |

|   |                                        | 2.2.1        | Hybridised orbitals and bonding      | E  |  |

|   | 2.3                                    | Inorga       | nic semiconductors                   | 8  |  |

|   |                                        | 2.3.1        | Nearly-Free Electron Model           | 8  |  |

|   | 2.4                                    | Organ        | ic semiconductors                    | 11 |  |

|   |                                        | 2.4.1        | History                              | 11 |  |

|   |                                        | 2.4.2        | Band structure of molecular crystals | 13 |  |

|   | 2.5                                    | Transi       | ${f stors}$                          | 14 |  |

|   |                                        | 2.5.1        | Field-effect transistor              | 14 |  |

|   |                                        | 2.5.2        | Thin-film transistor                 | 23 |  |

|   |                                        | 2.5.3        | Grain-boundary barrier model         | 23 |  |

|   |                                        | 2.5.4        | Organic TFT                          | 25 |  |

|   | 2.6                                    | Organ        | ic TFT dielectric surface treatments | 27 |  |

|   | 2.7                                    | Recent       | t research                           | 27 |  |

|   |                                        | 2.7.1        | Organic semiconducting materials     | 28 |  |

|   |                                        | 2.7.2        | OTFTs                                | 29 |  |

|   | 2.8                                    | Summ         | ary                                  |    |  |

| 3 | Thi | n Film  | Technologies                                | 42         |  |  |  |  |  |

|---|-----|---------|---------------------------------------------|------------|--|--|--|--|--|

|   | 3.1 | Introd  | uction                                      | . 42       |  |  |  |  |  |

|   | 3.2 | Thin f  | ilms                                        | . 42       |  |  |  |  |  |

|   | 3.3 | Therm   | al oxidation                                | 43         |  |  |  |  |  |

|   | 3.4 | Deposi  | ition techniques                            | . 47       |  |  |  |  |  |

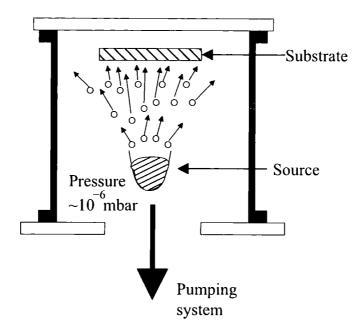

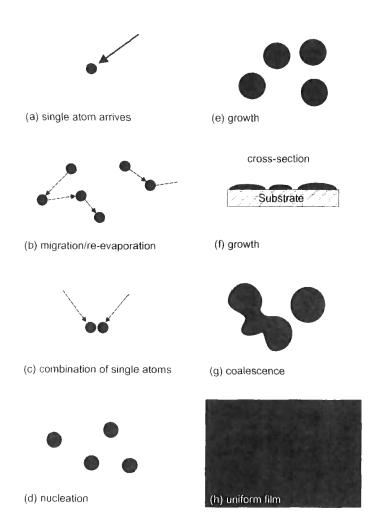

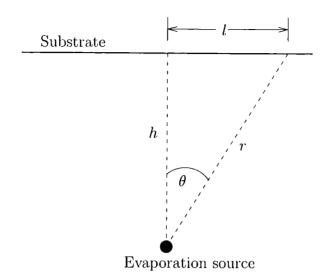

|   |     | 3.4.1   | Vacuum sublimation / thermal evaporation    | . 47       |  |  |  |  |  |

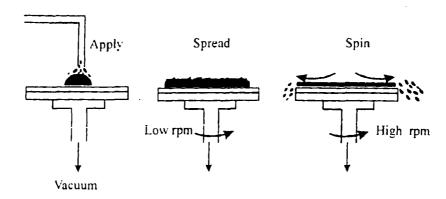

|   |     | 3.4.2   | Spin-coating                                | . 55       |  |  |  |  |  |

|   |     | 3.4.3   | Sputter coating                             | . 58       |  |  |  |  |  |

|   |     | 3.4.4   | Langmuir-Blodgett deposition                | . 59       |  |  |  |  |  |

|   |     | 3.4.5   | Self-assembly and Layer-by-Layer deposition | 60         |  |  |  |  |  |

|   |     | 3.4.6   | Other deposition techniques                 | 60         |  |  |  |  |  |

|   | 3.5 | Summ    | ary                                         | 63         |  |  |  |  |  |

| 4 | Exp | erimer  | ntal Methods                                | 67         |  |  |  |  |  |

|   | 4.1 | Introd  | $\operatorname{uction}$                     | 67         |  |  |  |  |  |

|   | 4.2 |         |                                             |            |  |  |  |  |  |

|   |     | 4.2.1   | Substrate preparation                       | 67         |  |  |  |  |  |

|   |     | 4.2.2   | Dielectric preparation                      | 68         |  |  |  |  |  |

|   |     | 4.2.3   | Semiconductor deposition                    | . 70       |  |  |  |  |  |

|   |     | 4.2.4   | Contacts                                    | 70         |  |  |  |  |  |

|   |     | 4.2.5   | Lithography                                 | 72         |  |  |  |  |  |

|   |     | 4.2.6   | Plasma etching                              | . 72       |  |  |  |  |  |

|   | 4.3 | Standa  | urd device layout                           | 72         |  |  |  |  |  |

|   | 4.4 |         |                                             |            |  |  |  |  |  |

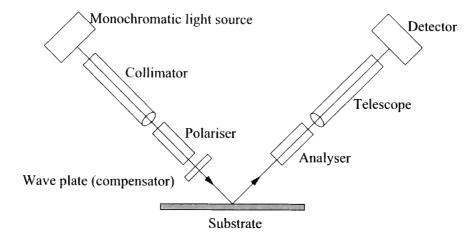

|   |     | 4.4.1   | Ellipsometry                                | 73         |  |  |  |  |  |

|   |     | 4.4.2   | Absorption Spectroscopy                     | 73         |  |  |  |  |  |

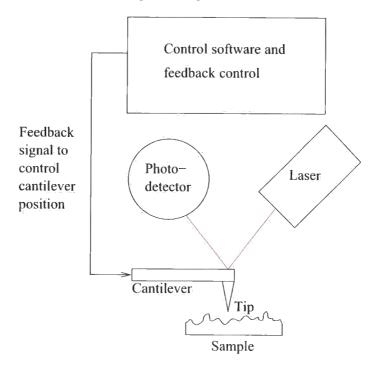

|   |     | 4.4.3   | Atomic Force Microscopy                     | 75         |  |  |  |  |  |

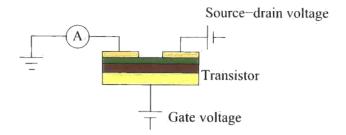

|   | 4.5 | Electri | cal characterisation                        | 76         |  |  |  |  |  |

|   | 4.6 | Summa   | ary                                         | 77         |  |  |  |  |  |

| 5 | Pen | tacene  | $/\mathrm{SiO}_2$ -based OTFTs              | <b>7</b> 9 |  |  |  |  |  |

|   | 5.1 | Introdu | uction                                      | 79         |  |  |  |  |  |

|   | 5.2 | Physic  | al characterisation of pentacene            | 80         |  |  |  |  |  |

|   |     | -       | Chemical structure                          |            |  |  |  |  |  |

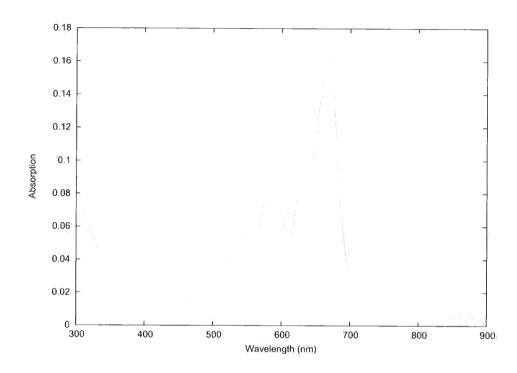

|   |      | 5.2.2   | Absorption spectrum                           | 0 |

|---|------|---------|-----------------------------------------------|---|

|   |      | 5.2.3   | Film morphology                               | Э |

|   | 5.3  | Electr  | ical characterisation                         | 2 |

|   | 5.4  | Transi  | stor measurements                             | 5 |

|   |      | 5.4.1   | Initial experiments                           | 5 |

|   |      | 5.4.2   | Silane treatment                              | 5 |

|   |      | 5.4.3   | Improving the gate                            | 7 |

|   |      | 5.4.4   | Effect of grain size                          | 7 |

|   |      | 5.4.5   | Improving the gate contact                    | 9 |

|   |      | 5.4.6   | SiO <sub>2</sub> surface treatment            | Э |

|   |      | 5.4.7   | A transistor with an improved gate contact 97 | 7 |

|   |      | 5.4.8   | Gold nanoparticles                            | 9 |

|   | 5.5  | Summ    | ary                                           | 2 |

| 6 | Alte | ernativ | ve gate dielectrics 105                       | 5 |

|   | 6.1  | Introd  | uction                                        | 5 |

|   | 6.2  | PMM.    | A dielectric                                  | ŝ |

|   | 6.3  | Hafniu  | ım oxide dielectric                           | 3 |

|   | 6.4  | A trar  | nsistor on a flexible substrate               | 1 |

|   | 6.5  | Summ    | ary                                           | 3 |

| 7 | Dib  | enzoth  | niophene-based OTFTs 126                      | 3 |

|   | 7.1  | Introd  | uction                                        | 3 |

|   | 7.2  | IR-35I  | For the second section $126$                  | 3 |

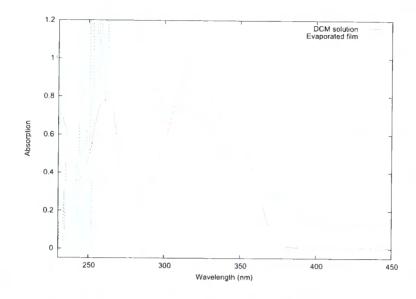

|   |      | 7.2.1   | Physical characterisation                     | 3 |

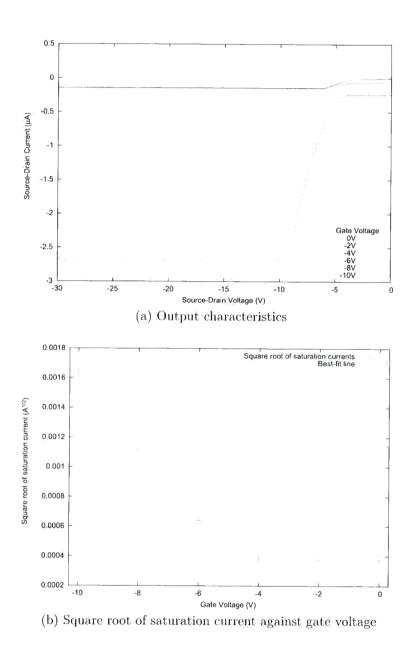

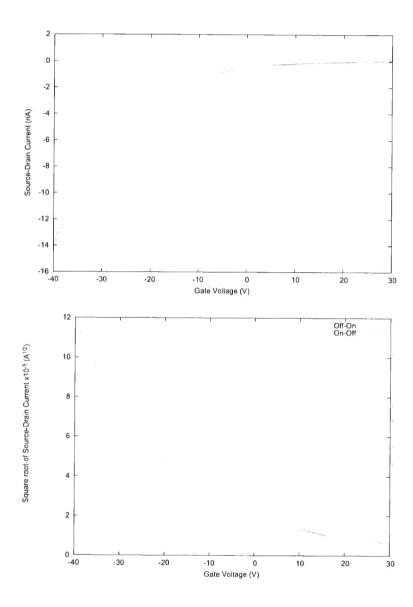

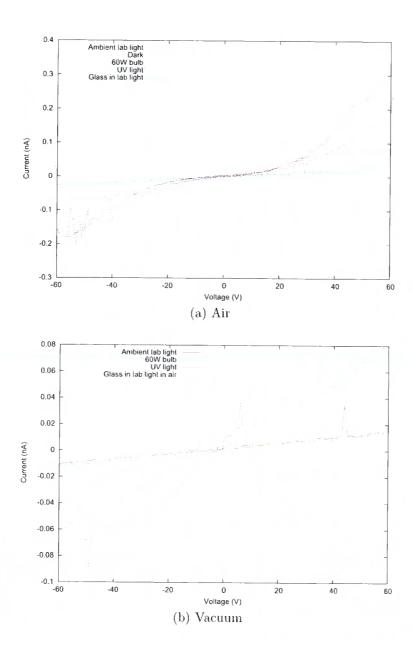

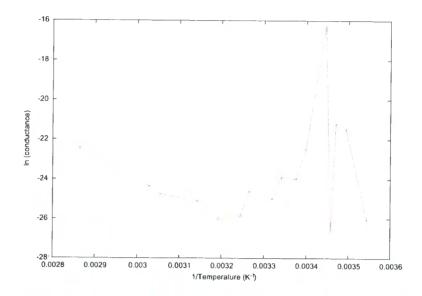

|   |      | 7.2.2   | Electrical characterisation                   | 9 |

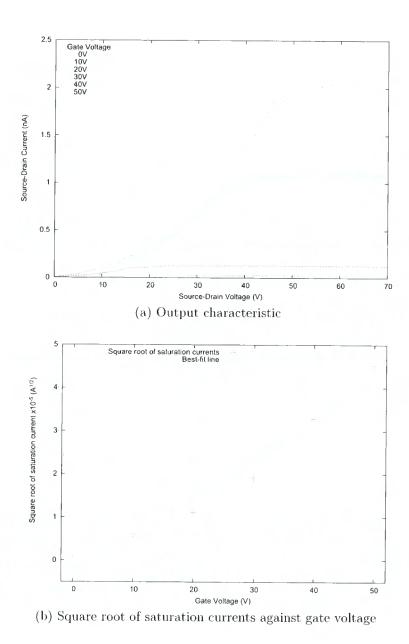

|   |      | 7.2.3   | Transistor device                             | ) |

|   | 7.3  | EC-08   | A                                             | 4 |

|   |      | 7.3.1   | Physical characterisation                     | 4 |

|   |      | 7.3.2   | Electrical characterisation                   | 5 |

|   |      | 7.3.3   | Transistor device                             | 3 |

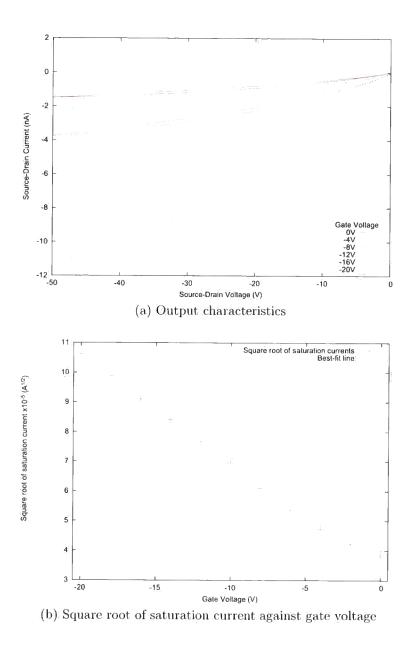

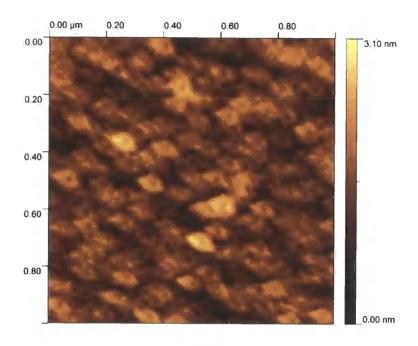

|   | 7.4  | CSW-    | $652 \ldots \ldots \ldots \ldots \ldots 138$  | 3 |

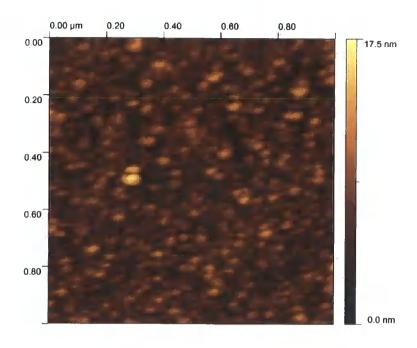

|   |      | 7.4.1   | Physical characterisation                     | 3 |

|   |      | 7.4.2   | Transistor device                             | 9 |

|              | 7.5 | Summary                      | . 143 |

|--------------|-----|------------------------------|-------|

| 8            | Con | nclusions and further work   | 145   |

|              | 8.1 | Conclusions                  | . 145 |

|              | 8.2 | Suggestions for further work | . 148 |

| A            | Pub | olication List               | 153   |

| В            | Tra | nsistor summary              | 154   |

| $\mathbf{C}$ | HfC | ). AFM images                | 161   |

## List of Figures

| Z.1  | Schematic representations of s and p orbitals                  | ·  |  |  |  |

|------|----------------------------------------------------------------|----|--|--|--|

| 2.2  | Combining s and p orbitals giving two sp hybrids               | 7  |  |  |  |

| 2.3  | Bonding in ethene                                              |    |  |  |  |

| 2.4  | Energy versus wavevector for a free electron, and in a monato- |    |  |  |  |

|      | mic linear lattice                                             | 10 |  |  |  |

| 2.5  | Energy bands of an insulator, semiconductor and conductor      | 11 |  |  |  |

| 2.6  | Perylene molecule                                              | 12 |  |  |  |

| 2.7  | BEDT-TTF molecule                                              | 12 |  |  |  |

| 2.8  | trans-isomer of polyacetylene                                  | 13 |  |  |  |

| 2.9  | Photograph of first MOSFET                                     | 15 |  |  |  |

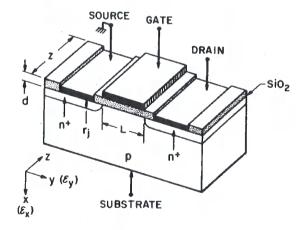

| 2.10 | Perspective view of the MOSFET                                 | 15 |  |  |  |

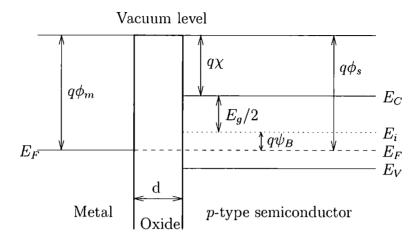

| 2.11 | Energy band diagram of ideal MOS diode at zero bias            | 16 |  |  |  |

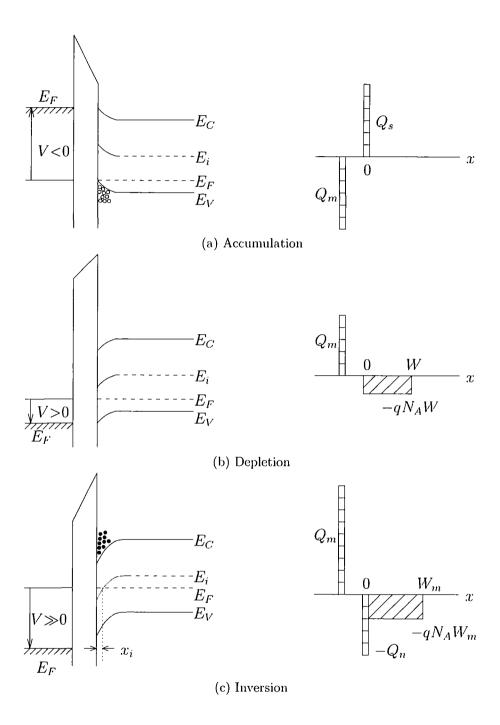

| 2.12 | Energy band diagrams and charge distributions of an idea MOS   |    |  |  |  |

|      | $\ diode. \ \ldots \ldots \ldots \ldots \ldots \ldots$         | 17 |  |  |  |

| 2.13 | Operations and output characteristics of the MOSFET            | 20 |  |  |  |

| 2.14 | Grain boundary barrier model schematic                         | 24 |  |  |  |

| 2.15 | Treatment of $SiO_2$ surface with silanising agent             | 27 |  |  |  |

| 3.1  | Basic thermal oxidation setup                                  | 43 |  |  |  |

| 3.2  | Model for oxidation of silicon                                 | 44 |  |  |  |

| 3.3  | Schematic of a thermal evaporation system                      | 48 |  |  |  |

| 3.4  | Stages of growth of an evaporated film                                  | 53 |

|------|-------------------------------------------------------------------------|----|

| 3.5  | Evaporation geometry from a point thermal source onto a plane substrate | 54 |

| 3.6  | Schematic representation of spin-coating.                               | 55 |

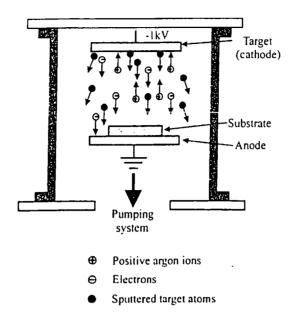

| 3.7  | Schematic of a sputtering system                                        | 58 |

| 0.1  | Schematic of a sputtering system                                        | JO |

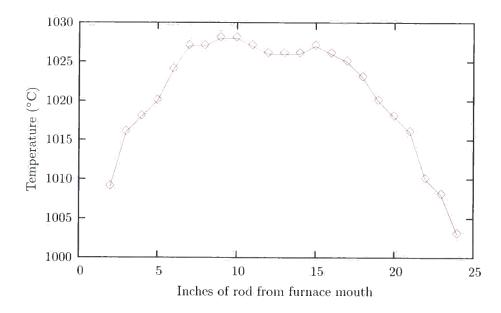

| 4.1  | Furnace temperature profile at nominal temperature of 1030°C.           | 68 |

| 4.2  | Photograph of Edwards Auto306 evaporator                                | 71 |

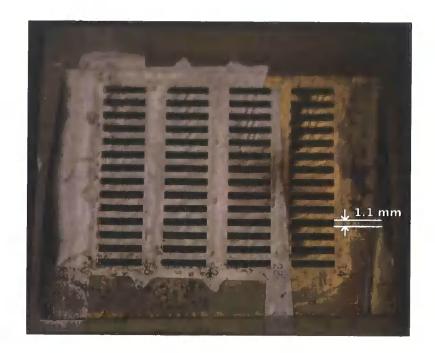

| 4.3  | Shadow mask for patterning transistors                                  | 71 |

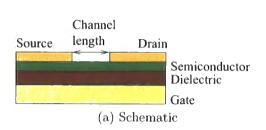

| 4.4  | Schematic and photograph of transistor                                  | 73 |

| 4.5  | Schematic representation of an ellipsometer                             | 74 |

| 4.6  | Schematic diagram of an AFM                                             | 75 |

| 4.7  | Schematic of the three-terminal transistor measurement setup.           | 76 |

| 4.8  | Photograph of the measurement sample chamber                            | 77 |

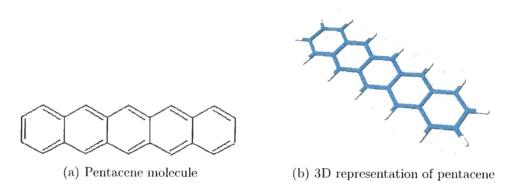

| 5.1  | The pentacene molecule                                                  | 80 |

| 5.2  | Absorption spectrum of a 90 nm thin film of pentacene between           |    |

|      | 300 and 900 nm                                                          | 81 |

| 5.3  | Photograph of pentacene on glass                                        | 81 |

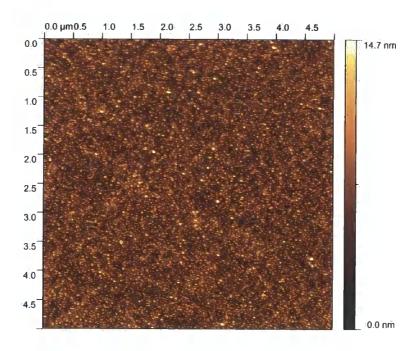

| 5.4  | $5 \ \mu m \times 5 \ \mu m$ AFM scans of evaporated pentacene          | 83 |

| 5.5  | I-V characteristics for pentacene in various environments, and          |    |

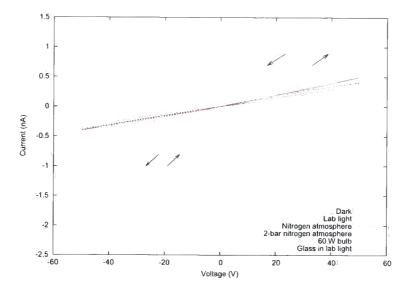

|      | for a glass slide in ambient light.                                     | 84 |

| 5.6  | Characteristics of initial devices fabricated                           | 86 |

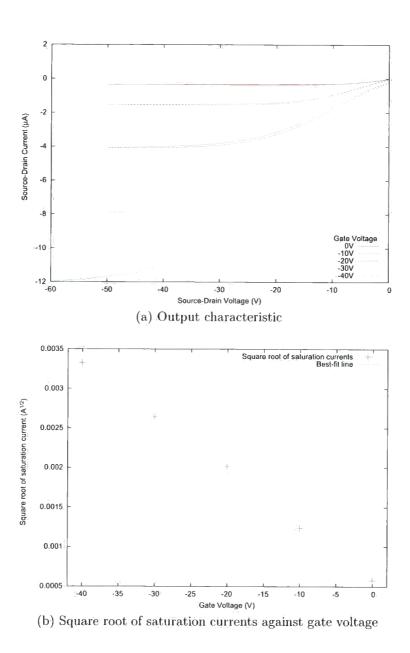

| 5.7  | Characteristics of device fabricated on pentacene with 2–3 µm           |    |

|      | crystal size                                                            | 88 |

| 5.8  | Levinson plot for linear region of transistor                           | 89 |

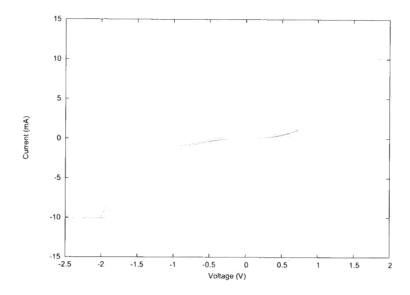

| 5.9  | I-V characteristic for silver paste contacts on silicon                 | 90 |

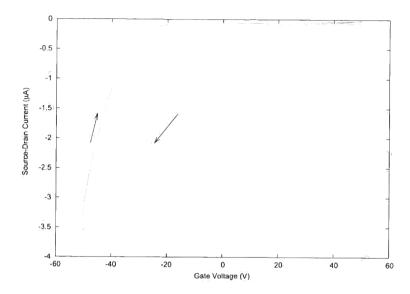

| 5.10 | Transfer characteristics at -20 V source-drain voltage for RIE-         |    |

|      | etched wafer.                                                           | 91 |

| 5.11 | Transfer characteristics for devices where the photoresist was          |    |

|      | removed with acetone and propanol, optionally followed by an            |    |

|      | oxygen plasma treatment                                                 | 92 |

| 5.12 | Si(2p) spectra for samples cleaned in acetone and isopropanol,          |    |

|      | optionally followed by an oxygen plasma.                                | 95 |

| 5.13 | optionally followed by an oxygen plasma                                                  |

|------|------------------------------------------------------------------------------------------|

| 5.14 | C(1s) spectrum for sample cleaned in acetone and isopropanol,                            |

|      | followed by an oxygen plasma                                                             |

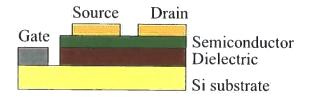

| 5.15 | Schematic of transistor with gate contact on top of substrate 97                         |

| 5.16 | Characteristics of a device fabricated with a gate on top of the                         |

|      | substrate                                                                                |

| 5.17 | Transfer characteristics for devices incorporating nanoparticles                         |

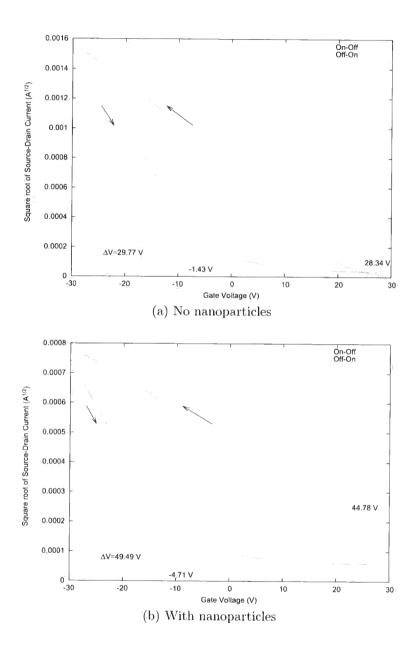

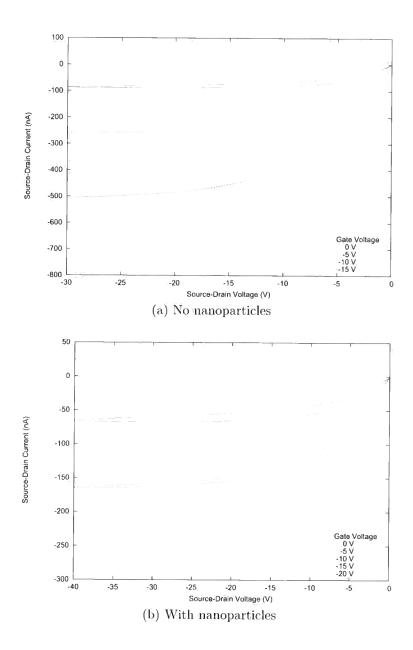

|      | and without nanoparticles, source-drain voltage of -20 V $100$                           |

| 5.18 | Output characteristics for devices with and without nanoparticles. 101                   |

| 6.1  | The PMMA molecule                                                                        |

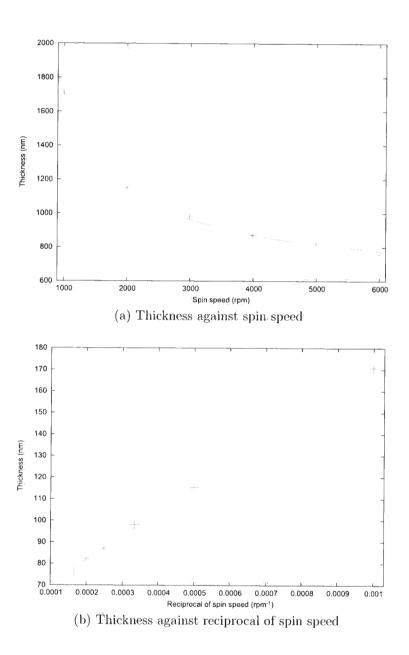

| 6.2  | Spin curve for 2.5% PMMA (93k) in anisole 107                                            |

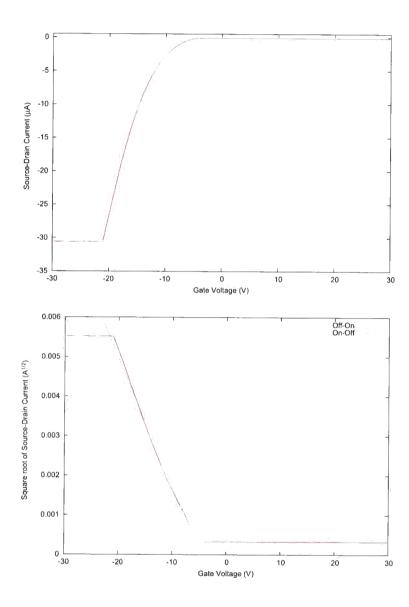

| 6.3  | Transfer characteristics at -20 V source-drain voltage of transis-                       |

|      | tor on 124 nm PMMA dielectric                                                            |

| 6.4  | Output characteristics of transistor on 124 nm PMMA dielec-                              |

|      | tric                                                                                     |

| 6.5  | Transfer characteristics at -20 V source-drain voltage of transis-                       |

|      | tor on 350 nm PMMA dielectric                                                            |

| 6.6  | Output characteristics of transistor on 350 nm PMMA dielec-                              |

|      | tric                                                                                     |

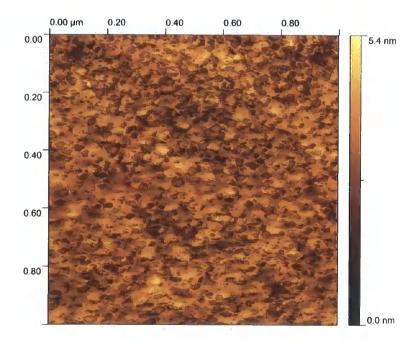

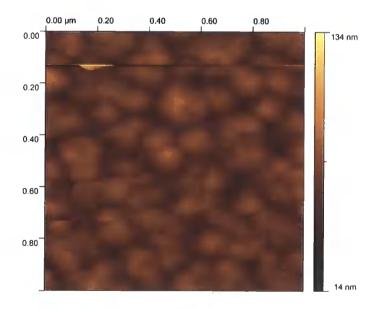

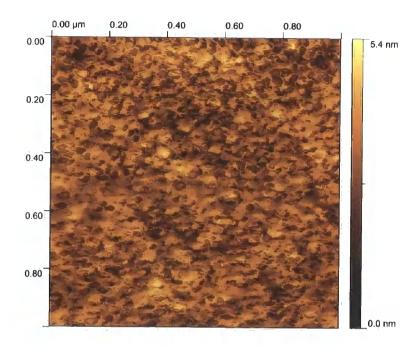

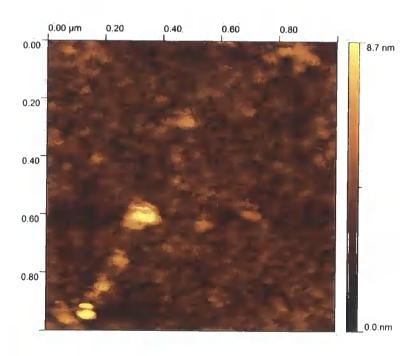

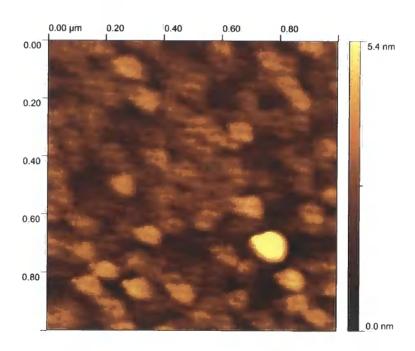

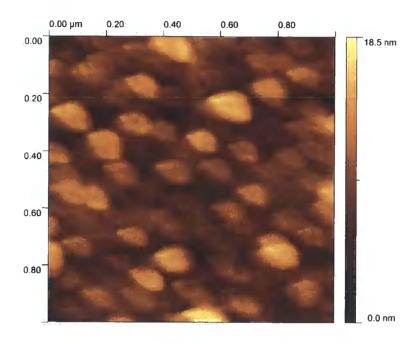

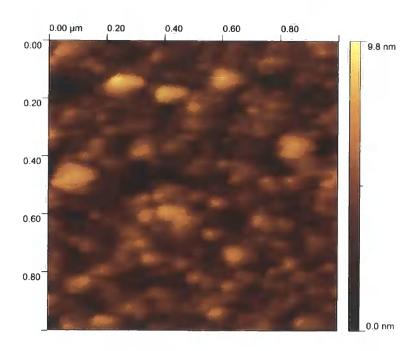

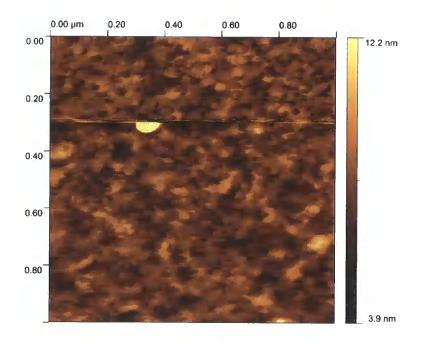

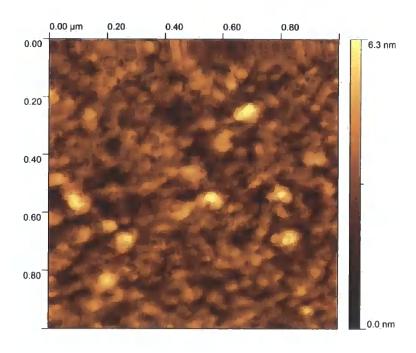

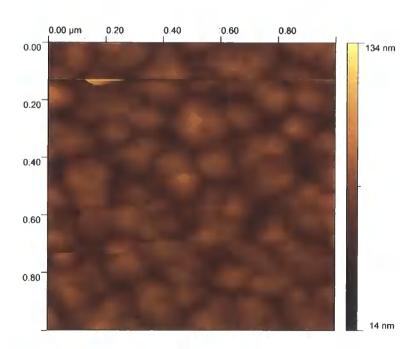

| 6.7  | 1 $\mu m$ $\times$ 1 $\mu m$ AFM image of hafnium oxide, from sample P1 $_{\odot}$ . 114 |

| 6.8  | $1~\mu m \times 1~\mu m$ AFM image of hafnium oxide, from sample P2 $_{\odot}$ .<br>.114 |

| 6.9  | 1 $\mu m \times 1 \mu m$ AFM image of silicon oxide                                      |

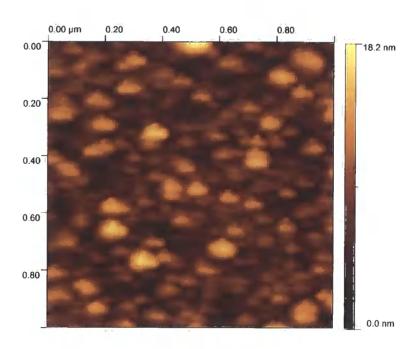

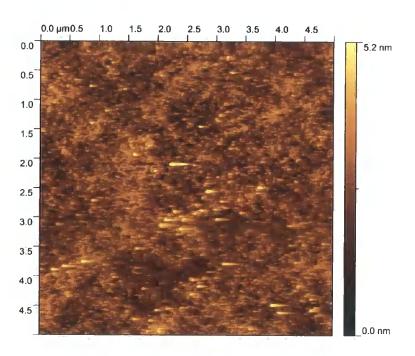

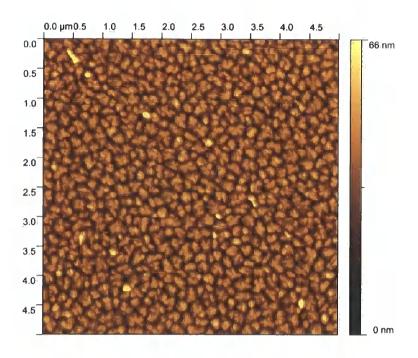

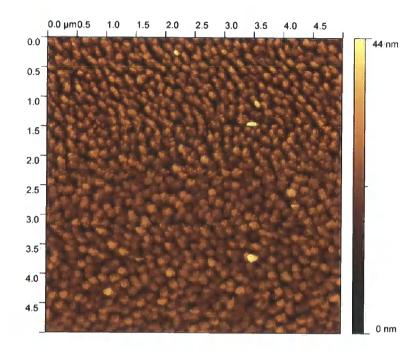

| 6.10 | 1 μm $\times$ 1 μm AFM image of pentacene deposited on hafnium                           |

|      | oxide, from sample P1                                                                    |

| 6.11 | 5 $\mu m$ $\times$ 5 $\mu m$ AFM image of pentacene deposited on hafnium                 |

|      | oxide, from sample P1                                                                    |

| 6.12 | Transfer characteristics of a pentacene device on $HfO_2$ and $SiO_2$ . 118              |

| 6.13 | Output characteristics of $HfO_2$ device fabricated on $N2119$                           |

| 6.14 | Characteristics of transistor on 40 nm $HfO_2$ dielectric 120                            |

| 6.15 | Characteristics of transistor fabricated on polyimide substrate $122$                    |

| 6.16 | Photograph of a transistor on a polyimide substrate                                      |

| 7.1  | The IR-35F molecule                                                         |

|------|-----------------------------------------------------------------------------|

| 7.2  | AFM image of thermally evaporated IR-35F on glass 127                       |

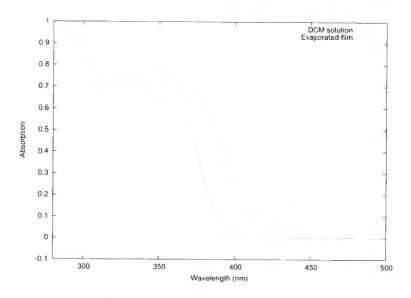

| 7.3  | Absorption spectra of IR-35F in DCM and evaporated film 128                 |

| 7.4  | Photograph of IR-35F on glass slide (75 $\times$ 25.4 mm each) 129          |

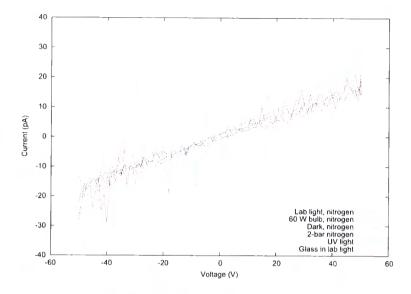

| 7.5  | I-V characteristics for IR-35F in various environments, and for             |

|      | a glass slide in ambient light                                              |

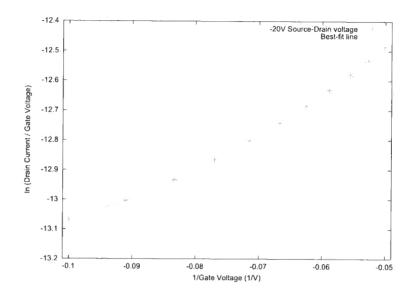

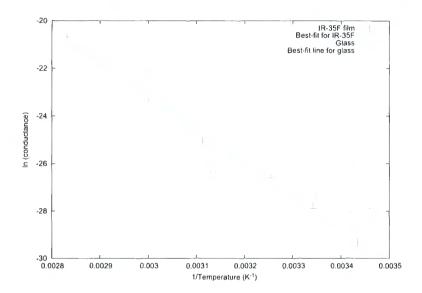

| 7.6  | ln(conductance) against temperature reciprocal for IR-35F film              |

|      | and glass                                                                   |

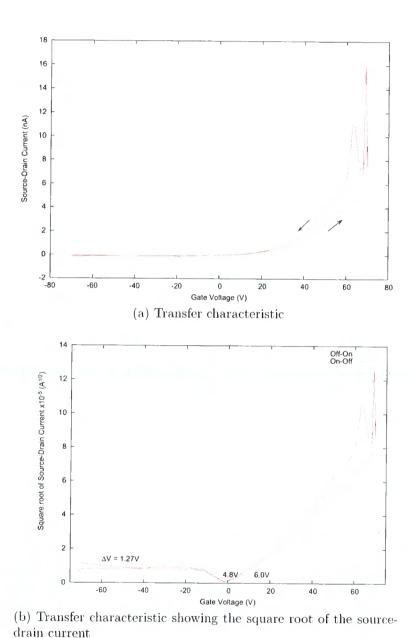

| 7.7  | Transfer characteristics of IR-35F transistor at $+70$ V source-            |

|      | drain voltage                                                               |

| 7.8  | Output characteristics of IR-35F transistor                                 |

| 7.9  | The EC-08A molecule                                                         |

| 7.10 | Absorption spectra of EC-08A in DCM and evaporated film. $$ . 135           |

| 7.11 | I-V characteristics for EC-08A in various environments 136 $$               |

| 7.12 | $\ln(\text{conductance})$ against temperature reciprocal for EC-08A film    |

|      | in air                                                                      |

| 7.13 | The CSW-652 molecule                                                        |

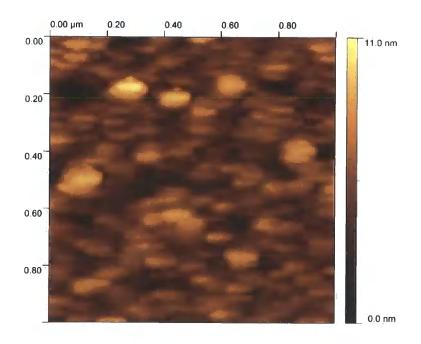

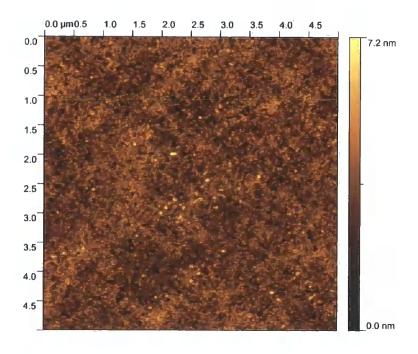

| 7.14 | 1 µm $\times$ 1 µm atomic force micrograph of CSW-652 on SiO <sub>2</sub> , |

|      | and $SiO_2$                                                                 |

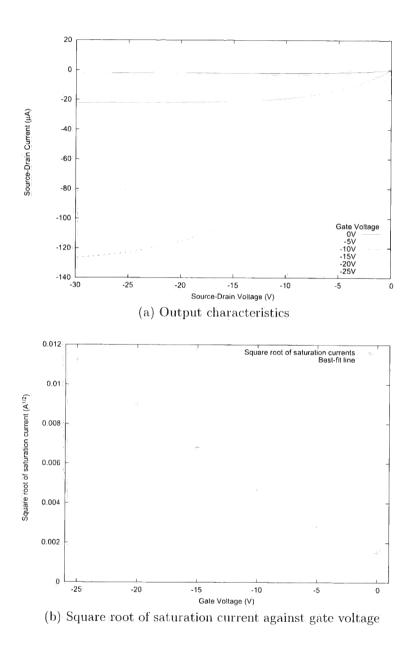

| 7.15 | Transfer characteristics of CSW-652 transistor at -40 V source-             |

|      | drain voltage                                                               |

| 7.16 | Output characteristics of CSW-652 transistor                                |

## **List of Tables**

| 2.1 | Summary of quantum numbers of electrons in atoms                   | 4   |

|-----|--------------------------------------------------------------------|-----|

| 2.2 | Field effect mobilities of OTFTs 1986–1997                         | 26  |

| 2.3 | Structure and results of OTFTs published in recent years           | 31  |

| 5.1 | Average hysteresis and threshold voltages for various photoresist  |     |

|     | strippers                                                          | 93  |

| 5.2 | XPS summary for plasma-cleaned and non-plasma cleaned ${ m SiO_2}$ |     |

|     | surfaces                                                           | 95  |

| 5.3 | Threshold voltages and shifts for devices incorporating gold       |     |

|     | nanoparticles and without nanoparticles                            | 99  |

| 6.1 | Summary of hafnium oxide depositions                               | 113 |

#### Introduction

Organic transistors are currently the subject of substantial international research, with many potential commercial applications. Compared to traditional silicon devices, they have low production costs; much of the processing can be performed at or near room temperature; and the techniques involved tend to be simpler than those for silicon.

Since the first postulation of organic conductors in 1911 [1] and particularly since they were first discovered in 1954 [2], research has progressed to the point where, today, organic devices are appearing in commercial products in increasing volume. Whilst organic transistors will never fully replace silicon due to speed issues, there are a multitude of applications, such as flexible displays, where their particular qualities far outweigh the speed benefits of silicon. The ability to fabricate organic transistors on flexible substrates allows for the fabrication of "paper" displays: the transistors are used as the driving circuitry for an organic LED display.

The aim of the research in this thesis is threefold. Firstly, to characterise pentacene and pentacene transistors fabricated on a silicon oxide dielectric, and to investigate the effect of various surface treatments of the SiO<sub>2</sub> on the transistors. Secondly, to compare the characteristics of pentacene-based transistors with different dielectrics to those made on SiO<sub>2</sub>. Thirdly, to investigate the properties of some new materials, based on the dibenzothiophene moiety, synthesised in the Department of Chemistry in the University of Durham.

REFERENCES 2

Chapter 2 gives an introduction to organic semiconductors, with a brief outline of how semiconducting behaviour arises in organic molecules. An overview of the materials used in research is provided, including some current research into new semiconducting molecules. Chapter 3 introduces thin films and their formation techniques: the techniques relevant to this work are described, and other formation techniques are summarised. Chapter 2 covers transistors, describing the operation of a field effect transistor and introducing organic thin film transistors. Dielectric surface treatments are briefly covered, and a summary of recent OTFT research is also provided.

Details of the experimental techniques used in this research are given in chapter 4. The methods used to fabricate the transistors are described, along with a discussion of the techniques used to characterise the devices and materials. Results for pentacene films and transistors made from pentacene on silicon oxide are given in chapter 5. The effects of the pentacene film morphology, and the effect of various silicon oxide surface treatments, on the characteristics and performance of the transistors are reported. Chapter 6 compares the characteristics of pentacene transistors on poly(methyl methacrylate) and hafnium oxide dielectrics, and hence provides a contrast between these dielectric materials and SiO<sub>2</sub>. Chapter 7 focuses on the characterisation and FET performance of three new materials, all based on the dibenzothiophene moiety, which were synthesised at the University of Durham.

Chapter 8 offers conclusions drawn from the work reported, and provides some suggestions for further work.

#### References

- [1] H. N. McCoy and W. C. Moore, "Organic amalgams: Substances with metallic properties composed in part of non-metallic elements," *Journal of the American Chemical Society*, vol. 33, pp. 273–292, March 1911.

- [2] H. Akamatu, H. Inokuchi, and Y. Matsunaga, "Electrical conductivity of the perylene-bromine complex," *Nature*, vol. 173, pp. 168–169, January 1954.

### **Organic Semiconductors and Transistors**

#### 2.1 Introduction

This chapter provides an introduction to organic semiconductors and transistors. Sections 2.2 and 2.2.1 summarise the electronic structure of atoms and bonding within organic compounds. Section 2.3 gives a brief introduction to inorganic semiconductors; section 2.4.2 provides the analogue for organic molecules. A short history and important research milestones of organic semiconductors are outlined in section 2.4.1. The operation of a metal-oxide-semiconductor field effect transistor (MOSFET) is given in section 2.5.1, the model yields the equation for source-drain currents in the linear and saturation regions. Section 2.5.2 compares the MOSFET to a thin film transistor, and introduces the grain boundary barrier model. A brief history of the organic thin film transistor is given in section 2.5.4.

The research in this thesis concentrates on the effect of surface treatments on silicon oxide / pentacene-based organic thin film transistors, the effect of replacing silicon oxide with alternative dielectrics, and the characterisation of some new materials. Surface treatments affecting OTFT performance are outlined in section 2.6. Sections 2.7.1 and 2.7.2 summarise some recent research in the fields of organic semiconducting materials and OTFTs, respectively.

| Name                  | Symbol         | Permitted values                 | Property              |

|-----------------------|----------------|----------------------------------|-----------------------|

| Principal             | $\overline{n}$ | Positive integers (1,            | Orbital energy (size) |

|                       |                | $2,3,\dots)$                     |                       |

| Angular mo-           | l              | Integers from 0 to $n-$          | Orbital shape         |

| mentum                |                | 1                                |                       |

| Magnetic              | $m_l$          | Integers from $-l$ to 0          | Orbital orientation   |

|                       |                | to $+l$                          |                       |

| $\operatorname{Spin}$ | $m_s$          | $+\frac{1}{2}$ or $-\frac{1}{2}$ | Direction of electron |

|                       |                |                                  | spin                  |

Table 2.1: Summary of quantum numbers of electrons in atoms.

#### 2.2 Electronic structure of atoms

During the latter part of the 19th century, it was found that many phenomena involving electrons in solids could not be explained in terms of classical mechanics. Quantum mechanics was thus developed to explain the observations. One of the early outcomes of quantum mechanics was the development of the Bohr atomic model, in which electrons were assumed to revolve around the atomic nucleus in discrete orbitals. An assumption in the Bohr model is that only certain orbits with fixed radii are stable around the nucleus [1]. The Bohr model was found to have significant limitations, and several improvements and enhancements were proposed. A significant improvement was regarding the electron as a charge contained within a spherical shell at a given radius, instead of a small finite particle moving around an orbit.

An electronic orbital, therefore, is a region of space in an atom or molecule where an electron with a given energy may be located. Due to the requirement of stable orbits, the electrons occupy well-defined spherical regions, distributed in various shells and subshells. In the quantum mechanical model, the shells and subshells are spatial regions around the nucleus where the electrons are most likely to be located. Each electron is characterised by a set of quantum numbers (principal, angular moment, magnetic and spin) which specify the size, shape and orientation of an electron's probability density function: the quantum numbers are summarised in table 2.1. The principal quantum number specifies the main shell where an electron is located, which gives the total energy of the electron. The angular momentum (orbital) number specifies the

magnitude of the orbital momentum; the l values 0, 1, 2, 3 indicate the electron subshell, corresponding to s, p, d, and f orbitals, respectively. The number of energy states for each subshell is determined by  $m_l$ : for an s subshell, there is a single energy state, whereas for p, d and f subshells there exist three, five and seven states. Each electron additionally has a spin direction,  $m_s$ , associated with it.

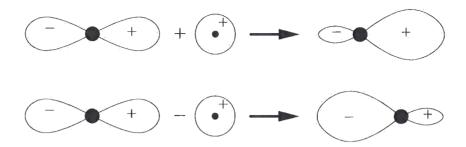

An atomic orbital is defined as a one-electron wavefunction  $\psi(x,y,z,t)$ . The corresponding probability distribution function  $|\psi|^2$ , defines the probability of finding an electron per unit volume at x,y,z and at time t.  $|\psi|^2$  has wave-like properties: its amplitude can be positive, corresponding to a wave crest, or negative, corresponding to a wave trough; a node is formed when a crest and trough meet. In three-dimensional waves, the nodes are two-dimensional surfaces at which  $\psi=0$ . Consequently, atomic orbitals may be characterised by their corresponding nodes, related to the quantum numbers: the 1s orbital has no nodes, its wavefunction is spherically symmetrical and its numerical value decreases exponentially from the nucleus; the 2s orbital has one spherical node; and the  $2p_{x,y,z}$  orbitals have nodes in the yz, xz and xy planes respectively. Figure 2.1 schematically depicts s and p orbitals; the + and - signs represent the arithmetic sign of the wavefunction — the signs determine how wavefunctions will combine when they interact (see section 2.2.1). The dashed lines represent nodal surfaces.

Electron states are filled according to the Pauli Exclusion Principle\*. When all the electrons occupy the lowest possible energies, the atom is in its ground state. The outermost filled shell is occupied by the valence electrons, which participate in bonding between atoms and are responsible for many of the physical and chemical properties of the resulting molecule.

#### 2.2.1 Hybridised orbitals and bonding

The electron configuration for carbon is  $1s^22s^22p^2$  — i.e. the inner s shell is filled and of the four valence electrons, two are in the outer s orbital and two in p orbitals. As the s orbital is spherically symmetrical, it can form a

<sup>\*</sup>No two fermions can have identical quantum numbers

Figure 2.1: Schematic representations of s and p orbitals (from [1]).

Figure 2.2: Mathematical combination of s and p orbitals to give two sp hybrids.

bond in any direction, whereas the p orbitals tend to form bonds along their axes. When two or more valence electrons are involved in bonding with other atoms, hybrid orbitals are constructed by combining the wavefunctions of the 2s and 2p orbitals. In the simplest case, the 2s orbital hybridises with a single p orbital, resulting in two sp hybrids, 180° apart; two p orbitals remain. The sp hybrids resulting from the sum and difference of the two wavefunctions are shown in figure 2.2.

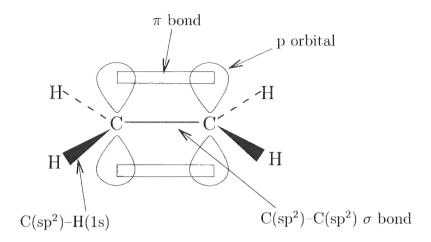

Other combinations of orbitals lead to different hybrids. With three groups bonded to a central atom, three  $\mathrm{sp^2}$  hybrids are constructed from one s and two p orbitals — the hybrid lies in the plane of the two p orbitals, and the remaining p orbital is perpendicular to that plane. Similarly, four  $\mathrm{sp^3}$  hybrids can be derived from an s orbital and three p orbitals; in this case the hybrids form a tetrahedron: this is demonstrated in the structure of methane, which consists of four  $\mathrm{C}(\mathrm{sp^3})\mathrm{-H}(1\mathrm{s})$  bonds.

Although carbon tends to form four covalent bonds (with four sp<sup>3</sup> hybrids), it can also form double and triple bonds with itself using sp<sup>2</sup> and sp hybrids, respectively. Ethene, for example, contains two  $C(sp^2)$ –H(1s) bonds on each carbon; a third sp<sup>2</sup> hybrid forms a single  $C(sp^2)$ – $C(sp^2)$  bond in the plane of the molecule: a  $\sigma$  bond. A p orbital is 'left over' on the carbons, which lies perpendicular to the plane of the six atoms; the two p orbitals are parallel to each other and have regions of overlap above and below the molecular plane — the overlapping regions form sideways bonding  $\pi$  bonds. Figure 2.3 illustrates the bonding in ethene.

Figure 2.3: Bonding in ethene.

When a number of atoms are in close proximity, their atomic orbitals tend to overlap — in the case of overlapping p orbitals, the  $\pi$  electrons are able to localise over the whole molecule (see section 2.4.2).

#### 2.3 Inorganic semiconductors

Solid state materials can be grouped into three classes — insulators, semiconductors and conductors, broadly defined by their conductivities. Insulators have conductivities in the order of  $10^{-18}$  to  $10^{-8}$  S/cm; conductors have conductivities above  $10^4$  S/cm; semiconductors have conductivities between these values [2]. This wide range of conductivities can be attributed to the arrangement of electrons in the solids' crystal structures.

### 2.3.1 Nearly-Free Electron Model

Although the free electron model of metals<sup>†</sup> gives a good insight into a number of properties of the material, including thermal and electrical conductivity, the model falls down on a number of points, such as the distinction between metals

<sup>&</sup>lt;sup>†</sup>Valence electrons in a metal crystal structure are assumed to be completely detached from their ions (an electron 'gas'); electron-electron interactions are neglected; and the crystal lattice is not taken into account

and insulators, and many transport properties. Extending the free electron model to take into account a periodic potential of a solid crystal lattice causes new properties to emerge, the most important of which is the possibility of an energy band gap arising between valence and conduction band electrons [3].

A full derivation of the origin of electron bands and bandgaps is out of the scope of this thesis, as it is readily found in most solid state physics books. However, some important stages to the derivation are outlined below:

For a free electron gas in three dimensions, the Schrödinger equation is

$$-\frac{\hbar^{2}}{2m}\nabla^{2}\psi_{\mathbf{k}}(\mathbf{r}) = \epsilon_{\mathbf{k}}\psi_{\mathbf{k}}(\mathbf{r})$$

$$\Rightarrow -\frac{\hbar^{2}}{2m}\left(\frac{\partial^{2}}{\partial x^{2}} + \frac{\partial^{2}}{\partial y^{2}} + \frac{\partial^{2}}{\partial z^{2}}\right)\psi_{\mathbf{k}}(\mathbf{r}) = \epsilon_{\mathbf{k}}\psi_{\mathbf{k}}(\mathbf{r})$$

(2.1)

where  $\nabla$  is the gradient operator,  $\hbar$  the reduced Planck constant, m the mass of an electron,  $\psi_{\mathbf{k}}$  the electron wavefunction, and  $\epsilon_{\mathbf{k}}$  the electron energy.

If the electrons are confined to a cube of edge L, the resulting wavefunction is the standing wave

$$\psi_n(\mathbf{r}) = A \sin\left(\frac{\pi n_x x}{L}\right) \sin\left(\frac{\pi n_y y}{L}\right) \sin\left(\frac{\pi n_z z}{L}\right)$$

(2.2)

where  $n_x$ ,  $n_y$ ,  $n_z$  are positive integers, and the origin is at one corner of the cube. The wavefunctions also need to satisfy periodic boundary conditions with period L, thus

$$\psi(x+L,y,z) = \psi(x,y,z) \tag{2.3}$$

and similarly for y and z. Hence equation 2.2 will only hold true when

$$\psi_n(\mathbf{r}) = A\sin(k_x x)\sin(k_y y)\sin(k_z z) \tag{2.4}$$

$$\psi_n(\mathbf{r}) = A \sin(k_x x) \sin(k_y y) \sin(k_z z)$$

$$k \equiv \frac{2n\pi}{L}$$

(2.4)

where n is any positive or negative integer, or 0.

To explain band structure, this free electron model needs to be extended slightly.

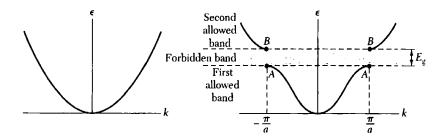

Figure 2.4: Plot of energy  $\epsilon$  versus wavevector k for a free electron, and for an electron in a monatomic linear lattice of lattice constant a (image taken from [3]).

Bragg reflection<sup>‡</sup> is a characteristic of waves travelling in a crystal — this reflection of electron waves is the cause of energy (band) gaps: at Bragg reflection, wavelike solutions to the Schrödinger equation do not exist.

Figure 2.4 shows the energy versus wavevector for a free electron, and for a nearly-free electron with an energy gap at  $k = \pm \pi/a$ ; other energy gaps occur at integer multiples of  $\pm \pi/a$  — i.e. conditions required for Bragg scattering. At these points, the wavefunctions of the electrons are not travelling waves, but are standing waves: they are continually Bragg reflected between  $+\pi/a$  and  $-\pi/a$ . These standing waves can be formed from two travelling waves:

$$\exp\left(\pm i\pi\frac{x}{a}\right) = \cos\left(\frac{\pi x}{a}\right) \pm i\sin\left(\frac{\pi x}{a}\right) \tag{2.6}$$

so the standing waves are

$$\psi(+) = \exp\left(i\frac{\pi x}{a}\right) + \exp\left(-i\frac{\pi x}{a}\right) = 2\cos\frac{\pi x}{a}$$

(2.7)

$$\psi(-) = \exp\left(i\frac{\pi x}{a}\right) - \exp\left(-i\frac{\pi x}{a}\right) = 2\sin\frac{\pi x}{a}$$

(2.8)

The two waves cause an accumulation of electrons at different regions, and hence have different values of potential energy in the field of the ions of the lattice — this is the origin of the energy gap. The magnitude of the energy gap and the occupation of the energy bands determines whether the crystal acts as an insulator, semiconductor, or conductor.

<sup>&</sup>lt;sup>‡</sup>Reflection from crystal planes

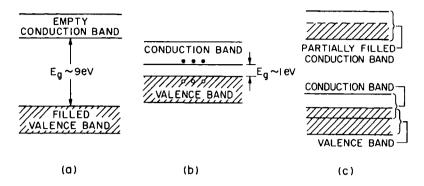

Figure 2.5: Schematic energy band representations of an insulator, a semiconductor, and a conductor (taken from [2]).

Figure 2.5 shows schematic representations of these properties. In an insulator, the valence electrons (section 2.2) completely fill the valence band, and there is a large gap between this and the conduction band. In a conductor, the conduction band is partially filled, or overlaps with the valence band so there is no band gap. In these cases, the electrons can easily move to higher energy levels when they gain kinetic energy, and hence current conduction readily occurs. In a semiconductor, the valence band is filled; however, the band gap is sufficiently small that thermal excitation can give electrons enough energy to jump to the conduction band, leaving a hole in the valence band. When an electric field is applied, both the electrons and holes will gain energy and conduct electricity.

#### Organic semiconductors 2.4

#### 2.4.1History

Most organic materials are electrical insulators with values of room temperature electrical conductivity in the range  $10^{-9} - 10^{-14} \text{ Scm}^{-1}$  [4]  $(10^9 - 10^{14} \text{ scm}^{-1})$  $\Omega$ cm resistivity). However, it was predicted in 1911 that certain organic solids may exhibit an electrical conductivity comparable to that of metals [5]; this was later confirmed in 1954 when Akamatu et al. reported a room temperature conductivity of around  $10^{-1}$  Scm<sup>-1</sup> for a bromine/perylene complex [6]; perylene (see figure 2.6) itself being an insulator with a room temperature

Figure 2.6: Perylene molecule.

Figure 2.7: BEDT-TTF molecule.

conductivity of around  $10^{-15} - 10^{-17}$  Scm<sup>-1</sup>. Considerable further work was done in synthesising and investigating properties of both donor and acceptor molecules; a major milestone was the synthesis of the acceptor molecule tetracyano-p-quinodimethane (TCNQ) and the donor molecule tetrathiafulvalene (TTF), which were combined in 1972 to form the charge transfer salt (TTF)(TCNQ). This was the first organic solid to show metallic conductivity over an extended temperature range [7].

As further work was undertaken into organic conductors, it was found that some TTF derivatives exhibited superconducting properties; a notable one is a charge-transfer salt of bisethylenedithiotetrathiofulvalene (BEDT-TTF; figure 2.7,  $\kappa$ -(BEDT-TTF)<sub>2</sub>Cu(NCS)<sub>2</sub> ( $\kappa$  denoting the packing arrangement of the BEDT-TTF molecules), which has a critical temperature of 10.4 K [8, pages 76, 107].

Meanwhile, in 1977, Shirakawa, MacDiarmid and Heeger (Nobel Prize in Chemistry, 2000) discovered that oxidation of one of the polyacetylene film isomers (trans-isomer, shown in figure 2.8, is the thermodynamically stable form at room temperature) with halogens made the films  $\sim 10^6$  times more conductive than the unhalogenated films [9]. This paper lead to a large amount

Figure 2.8: *trans*-isomer of polyacetylene.

of research into conducting polymers, distinct from the research into conductive low molecular weight organic materials.

The work in this thesis is based on small molecule semiconductors, and thus following sections will only concentrate on these.

#### 2.4.2Band structure of molecular crystals

A molecular crystal may be regarded as a miniature lattice with a precisely spaced series of atoms in close proximity to each other, giving rise to a good overlap of their atomic orbitals. The intramolecular interactions between the atoms lead to a splitting of the  $2p_z$  orbitals and to a localisation of the  $\pi$ electrons over the whole molecule. As a result, bonding orbitals take up the electrons whereas the antibonding orbitals remain empty [1]. Thus there is a highest occupied molecular orbital (HOMO) energy level and a lowest unoccupied molecular orbital (LUMO) energy level, analogous to the valence and conduction bands in inorganic semiconductors (section 2.3).

Most organic solids are insulators due to there being a large energy difference between the HOMO and LUMO levels, with the HOMO level being completely filled, and the solids are usually molecular, not possessing a system of covalent bonds extending over macroscopic distances, hence quantum mechanical interactions between the HOMOs of adjacent molecules are small and the valence band formed by these interactions is very narrow. Similarly, the conduction band arising from the interactions between the LUMOs is also

<sup>§</sup> The wavefunction formed from the sum  $\psi_A + \psi_B$  of two single electron wavefunctions  ${}^\P{}$ The wavefunction formed from the difference  $\psi_A - \psi_B$  of two single electron wavefunctions

small, so the band gap is essentially that of the free molecule. This is also true for any  $\sigma$ -bonded polymers (e.g. polyethylene).

To obtain a larger conductivity and hence semiconducting behaviour, the HOMO-LUMO gap needs to be reduced; this can be achieved by including heteroatoms with lone pair electrons (e.g. polyaniline or polyaromatics), or with extensive  $\pi$ -bonding [7]. With pentacene, for example (see section 2.7.1), incorporating the molecule into a larger crystal structure drastically changes the HOMO and LUMO levels: from around 1.2 eV (for the single molecule) to around 2.8 eV (for the crystal) for the LUMO level, and from 6.5 eV to 5 eV for the HOMO level. In the acene series, from benzene to pentacene, as the number of benzene rings increase, the size of the  $\pi$  electron system increases, and the HOMO-LUMO bandgap correspondingly decreases [1].

A large number of small-molecule semiconductors exist; a summary of some of these materials can be found in section 2.7.1.

#### 2.5 Transistors

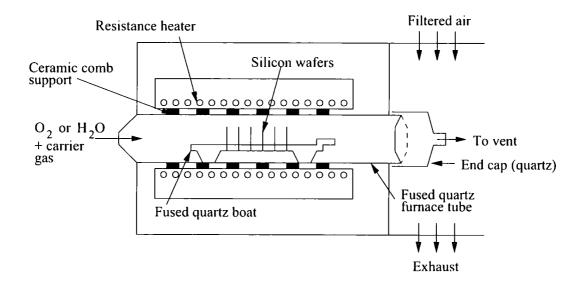

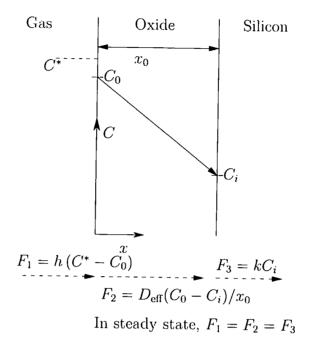

#### 2.5.1Field-effect transistor

A field effect transistor is a unipolar device (currents are carried predominantly by either electrons or holes), in which the conductivity of the semiconductor is modulated by a transverse electric field [10]. Figure 2.9 shows a photograph of the first MOSFET (Metal-Oxide-Semiconductor FET), fabricated in 1960 with a thermally oxidised silicon substrate (over 100 nm) and a channel length of over 20 µm [2]. A perspective view of a silicon MOSFET is shown in figure 2.10; it consists of a p-type semiconductor substrate in which two n-type regions (the source and the drain) are formed; the gate is formed by direct metal contact to the oxide. The remainder of this section will describe n-channel FETs.

When no voltage is applied to the gate, the source-to-drain electrodes correspond to two p-n junctions connected back-to-back; the only current that can flow is a reverse leakage current (this is the case for an enhancement mode device; a depletion mode device continues to have a small conductive channel, and requires a negative gate voltage to turn the transistor 'off'). When a

Figure 2.9: First MOSFET fabricated using a thermally oxidised silicon substrate (taken from [2]).

Figure 2.10: Perspective view of the MOSFET (taken from [2]).

Figure 2.11: Energy band diagram of an ideal MOS diode at V = 0 (from [2]).

large enough positive voltage is applied to the gate (greater than the threshold voltage), an n-type channel (surface inversion layer) is formed between the two n-type regions, so the source and drain are connected by a conducting n-channel. The conductance of the channel can be modified by varying the gate voltage.

The formation of the inversion layer can be explained by looking at the case of a MOS diode (the gate contact of the MOSFET is essentially a MOS diode). For an ideal MOS diode, the following assumptions are made:

- 1. At zero applied bias, the energy difference between the metal work function and semiconductor work function is zero.

- 2. The only charges that exist in the diode under any biasing conditions are those in the semiconductor and those with equal but opposite sign on the metal surface adjacent to the oxide

- 3. There is no carrier transport through the oxide under DC biasing conditions

The energy band diagram for an ideal MOS diode at zero bias is shown in figure 2.11.  $q\phi_m$  and  $q\phi_s$  are the metal and semiconductor work functions,  $q\chi$  the semiconductor electron affinity,  $q\psi_B$  the energy difference between the

Figure 2.12: Energy band diagrams and charge distributions of an ideal MOS diode (from [2]).

Fermi level  $E_F$  and the intrinsic Fermi level  $E_i$ . When the diode is biased with positive or negative voltages, three cases may exist at the semiconductor surface: the energy band diagrams and charge distributions for these are shown in figure 2.12. In the ideal diode, no current flows in the device (assumption 3), thus the Fermi level in the semiconductor will remain constant. In figure 2.12a, a negative voltage is applied to the metal, thus the bands near the semiconductor surface are bent upward. The carrier density in the semiconductor depends on the difference between  $E_i$  and  $E_F$  in the relation

$$p_p = n_i e^{(E_i - E_F)/kT} (2.9)$$

where  $n_i$  is the intrinsic carrier concentration. The upward bending increases  $E_i - E_F$ , and hence increases the carrier concentration close to the oxide surface — i.e. an accumulation of holes.

When a small positive voltage is applied (figure 2.12b), the energy bands bend downward, and thus the hole concentration is reduced — i.e. a depletion of holes. The space charge per unit area,  $Q_{sc}$ , in the semiconductor is given by the charge within the depletion region:

$$Q_{sc} = -qN_AW (2.10)$$

where W is the width of the depletion region and  $N_A$  is the substrate doping.

Figure 2.12c shows the case when a larger positive voltage is applied: the bands bend more so that  $E_i$  crosses over  $E_F$ . The electron concentration, similar to the hole concentration given in equation 2.9, is given by

$$n_p = n_i e^{(E_F - E_i)/kT} (2.11)$$

When  $E_F > E_i$ , as is the case with the large positive voltage, the electron concentration at the surface is larger than  $n_i$ , which in turn is larger than the hole concentration. As  $n_p > p_p$ , the surface is thus inverted. As the bands are bent further, the conduction band edge approaches the Fermi level; at this point the electron concentration increases rapidly. After this point most of the additional negative charges in the semiconductor consist of the charge  $Q_n$

due to the electrons in a narrow n-type inversion layer. The width of this inversion layer tends to range from 1-10 nm [2]. Once an inversion layer is formed, the surface depletion layer width reaches a maximum — an increase in potential will result in a large charge increase in the inversion layer, and thus not have an effect on the depletion layer. Thus the charge per unit area in the semiconductor is given by

$$Q_s = Q_n + Q_{sc} (2.12)$$

where  $Q_{sc}$  corresponds to the space charge per unit area at  $W = W_{max}$ .

When a potential is applied, this voltage will appear partly across the oxide and partly across the semiconductor. Thus

$$V = V_{ox} + \psi_s \tag{2.13}$$

where  $\psi_s$  is the semiconductor potential and  $V_{ox}$  is the potential across the oxide (thickness d) given by

$$V_{ox} = \mathcal{E}_{ox}d = \frac{|Q_s| d}{\epsilon_0 \epsilon_{ox}} \equiv \frac{|Q_s|}{C_{ox}}$$

(2.14)

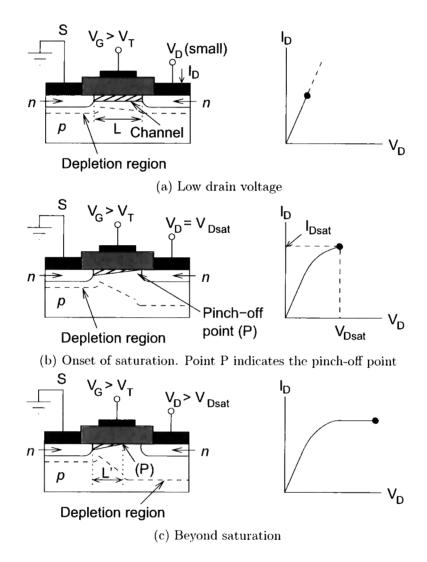

Figure 2.13 shows a schematic of the MOSFET operation, and output I-V characteristics when the gate voltage is above the threshold voltage (i.e. an inversion layer has been formed). If a small drain voltage is applied (figure 2.13a), electrons will flow from source to drain through the conducting channel. Thus the channel simply acts as a resistance, and  $I_D$  is proportional to  $V_D$  the linear region of operation. The total charge induced in the semiconductor per unit area,  $Q_s$ , at a distance y from the source is given from equations 2.13 and 2.14 by

$$Q_s(y) = -[V_G - \psi_s(y)] C_{ox}$$

(2.15)

where  $C_{ox} = \epsilon_0 \epsilon_{ox}/d$  is the gate capacitance per unit area and  $\psi_s(y)$  is the surface potential at y.

Figure 2.13: Operations of the MOSFET and output I-V characteristics (from [2]).

\_

The charge in the inversion layer, from equations 2.12 and 2.15 is

$$Q_n(y) = Q_s(y) - Q_{sc}(y)$$

= - [V\_G - \psi\_s(y)] C\_{ox} - Q\_{sc}(y) (2.16)

$\psi_s(y)$  at inversion can be approximated by  $2\psi_B + V(y)$ , where V(y) is the potential at a point y away from the source.  $Q_{sc}(y)$  can be formulated by

$$Q_{sc} = -qN_aW_{max} \simeq -\sqrt{2\epsilon_s qN_A \left[V(y) + 2\psi_B\right]}$$

(2.17)

Substituting equation 2.17 into 2.16 gives

$$Q_n(y) \simeq -\left[V_G - V(y) - 2\psi_B\right] C_{ox} + \sqrt{2\epsilon_s q N_A \left[V(y) + 2\psi_B\right]}$$

(2.18)

The conductivity of the channel at position y can be approximated by

$$\sigma(x) = qn(x)\mu(x) \tag{2.19}$$

For a constant mobility, the channel conductance is then given by

$$g = \frac{w}{L} \int_0^{x_i} \sigma(x) dx = \frac{w\mu}{L} \int_0^{x_i} qn(x) dx$$

(2.20)

where w is the channel width and L the channel length. The integral corresponds to the total charge per unit area in the inversion layer, and is therefore equal to  $|Q_n|$ . The channel resistance of a section dy is

$$dR = \frac{dy}{gL} = \frac{dy}{w\mu |Q_n(y)|} \tag{2.21}$$

and thus the voltage drop is

$$dV = I_D dR = \frac{I_D dy}{w\mu |Q_n(y)|} \tag{2.22}$$

where the drain current is independent of y. Substituting equation 2.18 into

The derivation is out of the scope of this thesis but may be found in section 5.4.1 of [2].

2.22 and integrating from source  $(V=0,\,y=0)$  to drain  $(V=V_D,\,y=L)$  yields

$$I_D \simeq \frac{w}{L} \mu C_{ox} \left\{ \left( V_G - 2\psi_B - \frac{V_D}{2} \right) V_D - \frac{2}{3} \frac{\sqrt{2\epsilon_s q N_A}}{C_{ox}} \left[ \left( V_D + 2\psi_B \right)^{3/2} - \left( 2\psi_B \right)^{3/2} \right] \right\}$$

(2.23)

In the case of small  $V_D$  (transistor operating in the linear mode), this equation reduces to

$$I_D \simeq \frac{w}{L} \mu C_{ox} \left( V_G - V_T \right) \qquad V_D \ll V_G - V_T \tag{2.24}$$

where  $V_T$  is the threshold voltage given by

$$V_T \simeq \frac{\sqrt{2\epsilon_s q N_A (2\psi_B)}}{C_{cor}} + 2\psi_B \tag{2.25}$$

The derivation of  $V_T$  is outside the scope of this thesis, but can be found in section 5.4.1 of [2].

As the drain voltage increases, it reaches a point at which the width of the inversion layer at y = L is reduced to zero (figure 2.13b). The charge,  $Q_n(y)$  at y = L, therefore becomes zero, and the number of mobile electrons at the drain are reduced drastically; the drain current and voltage at this point are designated  $I_{Dsat}$  and  $V_{Dsat}$ . Beyond this 'pinch-off' point, the drain current remains essentially the same because for  $V_D > V_{Dsat}$ , at point P the voltage  $V_{Dsat}$  remains the same. Thus the number of carriers arriving at P from the source, and hence source-drain current, remains the same. The major change is a decrease in L to L', as in figure 2.13c.

The value of  $V_{Dsat}$  can be obtained from equation 2.18 under the condition  $Q_n(L) = 0$ :

$$V_{Dsat} \simeq V_G - 2\psi_B + K^2 \left(1 - \sqrt{1 + \frac{2V_G}{K^2}}\right)$$

(2.26)

where  $K \equiv \sqrt{\epsilon_s q N_A}/C_{ox}$ . Substituting equation 2.26 into 2.23 gives the saturation current

$$I_D \simeq \frac{w\mu\epsilon_0\epsilon_{ox}}{2dL} \left(V_G - V_T\right)^2 \equiv \frac{\mu w}{2L} C_{ox} \left(V_G - V_T\right)^2 \qquad V_D > V_G - V_T \quad (2.27)$$

In the saturation region, the mobility can be obtained (graphically) by plotting the square root of the saturation current against gate voltage and obtaining the gradient:

$$gradient = \sqrt{\frac{1}{2}\mu \frac{w}{L}C_{ox}}$$

(2.28)

which can be rearranged to obtain a mobility

$$\mu = \frac{2(\text{gradient})^2 L}{wC_{ox}} \tag{2.29}$$

### 2.5.2 Thin-film transistor

A thin film transistor (TFT) is a field effect transistor made by depositing thin films of dielectric, semiconductor, and contacts over a supporting substrate. In comparison, in the MOSFET, the semiconductor also doubles as the substrate for the *n*-type regions and the dielectric. Probably the most common use of TFTs is in liquid crystal displays; these transistors are usually fabricated on glass substrates.

The transistors reported on in this work are all thin-film transistors, using organic semiconductors as the active layer. The substrates are almost all silicon wafers; conductive silicon was chosen due to its ability to act directly as the transistor gate, and the relative ease of growing a good quality oxide as the dielectric.

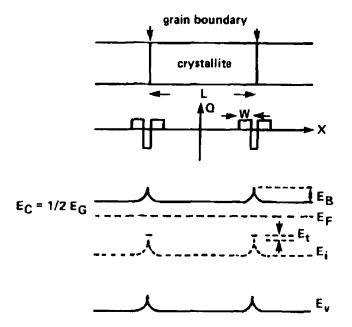

# 2.5.3 Grain-boundary barrier model

The semiconducting layers in TFTs are commonly amorphous or polycrystalline silicon; in organic TFTs pentacene, which tends to form a polycrystalline structure when deposited, is a common material. With a polycrystalline material, a grain-boundary barrier model (illustrated in figure 2.14) can be applied. This model assumes that carriers are transported at inter-poly-grains

Figure 2.14: Grain structure, charge distribution and band diagram assumed in the grain boundary trapping model (taken from [11]).

by thermionic emission over the grain boundary barrier and that no scattering is taking place in the grains [11]. The trap density  $N_t$  can be determined from a Levinson plot of  $\ln(I_D/V_G)$  against  $1/V_G$ . The Levinson model is based on the predicted transistor drain current in the linear regime [12], given by

$$I_D = \mu_0 V_D C_{ox} \left(\frac{W}{L}\right) V_G \exp\left(-\frac{E_B}{kT}\right)$$

$$\equiv \mu_0 V_D C_{ox} \left(\frac{W}{L}\right) V_G \exp\left(-\frac{s}{V_G}\right)$$

(2.30)

where  $E_B$  is the potential barrier height,  $\mu_0$  is the trap-free mobility, and the thermally activated mobility is

$$\mu = \mu_0 \exp\left(-\frac{E_B}{kT}\right) \equiv \mu_0 \exp\left(-\frac{s}{V_G}\right)$$

(2.31)

Screening causes  $E_B$  to fall as  $V_G$  increases, hence  $N_t$  can be estimated from the slope s of the Levinson plot using the formula

$$s = \frac{q^3 N_t^2 t}{8\epsilon k T C_{ox}} \tag{2.32}$$

where t represents the thickness of the semiconducting layer, and  $\epsilon$  is the dielectric constant of the semiconductor (which can be taken as 4 for pentacene [12]).

# 2.5.4 Organic TFT

Replacing the silicon in a TFT with an organic semiconductor has been an area of active research for the last 20 years. Compared to silicon, organic devices have relatively low mobilities, and so are not suitable for applications requiring high switching speeds. However, they have advantages over silicon for applications that require large-area coverage, structural flexibility, low-temperature processing and low cost; such applications include the driving circuitry for "paper" displays, or low end data storage such as RFID tags [13]. Table 2.2 lists the highest reported mobility for organic FETs published between 1986 and 1997 (more recent developments are given in section 2.7.2).

| Year | Mobility ( $cm^2/V/s$ ) | Material                                 |

|------|-------------------------|------------------------------------------|

|      |                         |                                          |

| 1986 | $10^{-5}$               | polythiophene                            |

| 1988 | $10^{-4}$               | polyacetylene                            |

|      | $10^{-4}$               | phthalocyanine                           |

|      | $10^{-4}$               | poly(3-hexylthiophene)                   |

| 1989 | $10^{-3}$               | poly(3-alkylthiophene)                   |

|      | $10^{-3}$               | $\alpha, \omega$ -hexathiophene          |

| 1992 | 0.02                    | $\alpha,\omega$ -hexathiophene           |

|      | $2 \times 10^{-3}$      | pentacene                                |

| 1993 | 0.05                    | $\alpha, \omega$ -di-hexyl-hexathiophene |

| 1994 | 0.06                    | $\alpha, \omega$ -di-hexyl-hexathiophene |

| 1995 | 0.03                    | $\alpha, \omega$ -hexathiophene          |

|      | 0.038                   | pentacene                                |

|      | 0.3                     | $\mathrm{C}_{60}$                        |

| 1996 | 0.02                    | phthalocyanine                           |

|      | 0.045                   | poly(3-hexyxthiophene)                   |

|      | 0.13                    | $\alpha, \omega$ -di-hexyl-hexathiophene |

|      | 0.6                     | pentacene                                |

| 1997 | 1.3                     | pentacene                                |

Table 2.2: Field effect mobilities of early OTFTs (taken from [14]).

Figure 2.15: Treatment of SiO<sub>2</sub> surface with silanising agent.

### Organic TFT dielectric surface treatments 2.6

For organic FETs using a silicon oxide dielectric, a number of studies have shown that the oxide surface is very important to the mobility and characteristics of the transistors ([15–18], also sections 5.4.2, 5.4.6 and 5.4.8). Reduction in mobility, or increase in hysteresis in the transfer or output characteristics have been attributed to charge trapping at the oxide surface. Two surface treatments are commonly used to minimise these trapping states: firstly, an oxygen plasma ([17,18]; section 5.4.6) is used to remove residual organic contamination; this procedure is primarily performed after stripping photoresist from the oxide surface. Secondly, a silane treatment (section 5.4.2) can be applied to modify chemically the SiO<sub>2</sub> surface: normally, the surface is terminated with -OH groups, which act as good charge traps; the silanising agent substitutes these groups with (CH<sub>3</sub>)<sub>3</sub>-Si- groups [15], which render the oxide surface hydrophobic. Figure 2.15 illustrates this group substitution. Two silane-based surface treatments are used in the course of this work: dicholorodimethylsilane (DMDS; (CH<sub>3</sub>)<sub>2</sub>Cl<sub>2</sub>Si) and hexamethyldisilazane (HMDS; (CH<sub>3</sub>)<sub>3</sub>Si-NH- $Si(CH_3)_3$ , reported in [15]).

### Recent research 2.7

There exists a large body of published literature about organic semiconductors and thin film transistors [19]. A summary of some of the research is given below.

## 2.7.1 Organic semiconducting materials

There exist a large number of small-molecule semiconductors, which can be broadly grouped into a few different types.

Linear acenes, such as anthracene, tetracene, or pentacene (see chapter 5) consist of a number of benzene molecules arranged in a straight line. They are important materials in electrical applications because the band gap is controllable by selecting the number of aromatic rings [20]: the more rings, the smaller the band gap. Most published work on acenes concerns devices made out of pentacene, such as transistors or diodes [21], as pentacene is a well-established, reliable semiconducting material with good carrier mobility. There has been investigation into doping the pentacene films with iodine and alkaline metals [20, 22, 23]; achieving maximum conductivity of 150 Scm<sup>-1</sup> for highly ordered films heavily doped with iodine, and 2.8 Scm<sup>-1</sup> for a rubidium-doped film, which turned the film into an n-type semiconductor. A derivative of a linear acene, 5,6,11,12-tetraphenyltetracene (rubrene) has been reported to have a carrier mobility of  $\sim 20$  cm<sup>2</sup>/V/s at room temperature, increasing to  $\sim 30$  cm<sup>2</sup>/V/s at around 150 K [24]. This appears to be one of the highest mobilities reported for an organic semiconductor.

Thiophene-based molecules (see also chapter 7) are a popular alternative to acenes. A large body of published work exists on the synthesis and properties of thiophene-based materials — reported improvements over pentacene include better resistance to oxidation [25]. Transistor mobilities reported are not as high as those for pentacene; nevertheless they have reasonable values:  $0.15 \text{ cm}^2/\text{V/s}$  [25, 26], increasing up to  $1.0 \text{ cm}^2/\text{V/s}$  [27].

There have been reports of other materials used as semiconductors, for example copper phthalocyanines [28] or azurin proteins [29]. A number of other materials have been reported with n-type behaviour: some of these are summarised in the section below. Section 2.7.2 contains more details on transistor performances of various materials.

### *n*-type organic semiconductors

A characteristic feature of most organic semiconductors is strong trapping of electrons but not holes — i.e. the materials exhibit p-type conduction [30]. However, in order to make complementary FETs it is necessary to obtain ntype materials with electron mobilities of the same order as hole mobilities in p-type materials. Although there has been a large amount of research into n-type semiconductors in recent years, many n-type materials only work in a vacuum or inert atmosphere because ambient oxygen and moisture can act as electron traps [31].

It has been shown that by incorporating electron deficient groups into normally p-type materials, it is possible to improve the electron transport properties, thus obtaining n-type behaviour [32]. Thiophenes are common materials to incorporate electron deficient groups in due to the ease of functionalising the group [33]; mobilities of these materials have been found to be reasonable: incorporation of a trifluoromethylphenyl derivative into a dithiazolylbenzothiadiazole derivative yielded a field effect mobility of 0.068 cm<sup>2</sup>/V/s [33], while incorporating the trifluoromethylphenyl group onto a thiazolothiazole unit yielded a mobility of up to 0.30 cm<sup>2</sup>/V/s [34].

Naphthalenetetracarboxylic diimide compounds have been used in the fabrication of n-channel FETs: it was found that an unfluorinated compound exhibited a mobility of 0.16 cm<sup>2</sup>/V/s under vacuum, but the device rapidly deactivated on exposure to air; fluorinated compounds, however, were relatively stable in air but at a reduced mobility ( $\sim 0.01 \text{ cm}^2/\text{V/s}$ ) [35]. One of the highest reported mobilities for n-type devices was for the compound N, N'bis(2,2,3,3,4,4,4-heptafluorobutyl)-perylene tetracarboxylic diimide, which exhibited a field-effect mobility of 0.75 cm<sup>2</sup>/V/s in nitrogen, reducing to 0.56  $cm^2/V/s$  in air but remaining stable for more than 50 days [31].

#### 2.7.2OTFTs

Given the large volume of research into organic TFTs, a summary of a selection of papers published in the last few years is given in table 2.3.

Two main approaches to OTFT research are evident. One aspect involves investigating the semiconducting and FET behaviour of newly synthesised molecules; these transistors tend to be fabricated on silicon / silicon oxide with gold contacts, as this is a common configuration that has produced reliable devices. A significant number of these molecules are based on thiophenes; mobilities of these molecules, where semiconducting behaviour was evident, varied between around  $0.05 \text{ cm}^2/\text{V/s}$  and  $>1 \text{ cm}^2/\text{V/s}$ . Halik et al. [27] found, when investigating sexithiophene-based molecules, that the length of alkyl chains in alkyl-substituted molecules had a significant effect on the mobility of the transistors: reducing the alkyl chain length from ten to six units increased the mobility (for top contact devices) from 0.1 to  $1.0 \text{ cm}^2/\text{V/s}$ . This was attributed to the alkyl chains forming an intrinsic barrier separating the thiophene backbone from the contacts, thus increasing the effective contact resistance. Removing the alkyl chains entirely reduced the carrier mobility to 0.07 cm<sup>2</sup>/V/s; this was attributed to the presence of optimised alkyl chains resulting in enhanced molecular ordering and improved  $\pi$ – $\pi$  stacking in the active layer. Molecules exhibiting n-type behaviour (see also section 2.7.1) typically contained electron-deficient fluorine groups; although these were airstable, mobilities tended to be  $< 0.1 \text{ cm}^2/\text{V/s}$ . Higher mobility n-type devices tended to work only in vacuum, degrading rapidly in air. Only recently have high-mobility, air-stable n-type molecules been synthesised [31].

Another aspect of the research investigates the optimisation of the fabrication methods and conditions of OTFTs. Usually, pentacene is used due to its air-stability, reliability as a semiconductor and potential for high mobilities. It has been found that two major factors contribute to the performance of the transistors: pentacene deposition conditions and dielectric surface treatment. The rate of pentacene deposition affects the crystal size [36] (see also sections 5.2.3 and 5.4.4) — the larger crystal sizes result in fewer inter-grain boundaries, and thus a corresponding increasing in mobility is observed. Depositing the pentacene onto a substrate held at an elevated temperature also resulted in increased mobility [12, 16, 17]. Treating a silicon oxide dielectric (see section 2.6) with silane-based surface treatments was found to increase the mobility of transistors [15] (see also section 5.4.2), due to chemical modification of the oxide surface to remove charge traps. Oxygen plasmas have been found to increase mobility and reduce hysteresis in the devices [17] (see also section 5.4.6); these have been attributed to a physical reduction in trapping states on the dielectric surface: the oxygen plasma removing carbon contamination from the surface. Replacing silicon dioxide with other dielectric materials has shown promise: organic dielectrics such as PMMA [37] or polyimide [38] have resulted in devices with reasonable mobilities, low hysteresis and negative threshold voltages. An Atomic Layer Deposition deposited Al<sub>2</sub>O<sub>3</sub> / HfO<sub>2</sub> bilayer [39] was found to reduce the threshold voltage compared to silicon oxide, but also reduced the mobility by an order of magnitude. Using a titanium gate electrode with TiO<sub>2</sub> dielectric, capped with a styrene-based layer [40] resulted in a transistor with a low threshold voltage (-0.48 V) and a high mobility (0.8  $cm^2/V/s$ ).

Table 2.3: Structure and results of OTFTs published in recent years.

| Structure                                           | Results                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Polyethylene naphthalate                            | Mobility: $1.2 \text{ cm}^2/\text{V/s}$ ; on-                                                                                                                                                                                                                                                                                                           |

| (PEN) film substrate,                               | off current ratio: $10^8$                                                                                                                                                                                                                                                                                                                               |

| Ni gate, SiO <sub>2</sub> dielectric,               |                                                                                                                                                                                                                                                                                                                                                         |

| Pd electrodes, pentacene                            |                                                                                                                                                                                                                                                                                                                                                         |

| semiconductor                                       |                                                                                                                                                                                                                                                                                                                                                         |

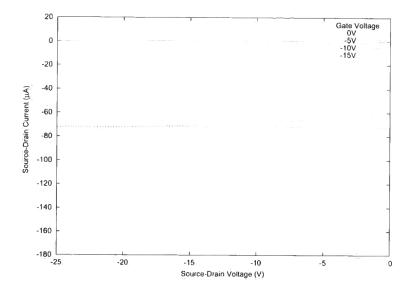

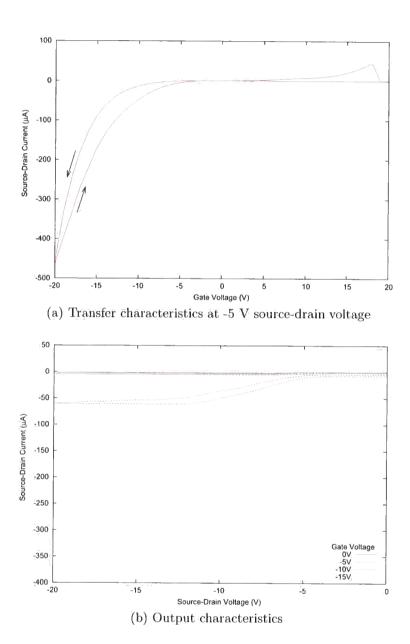

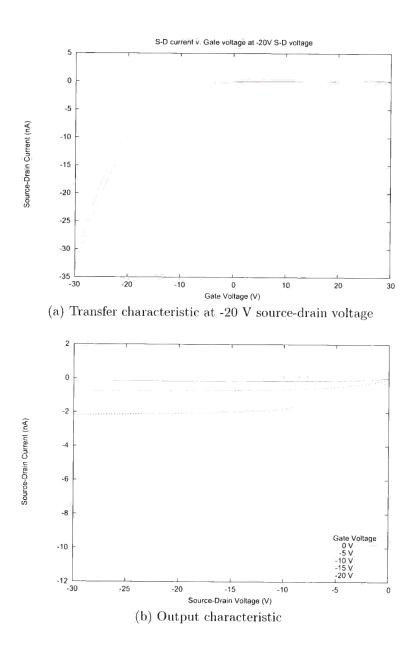

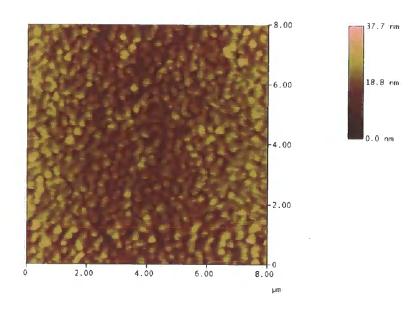

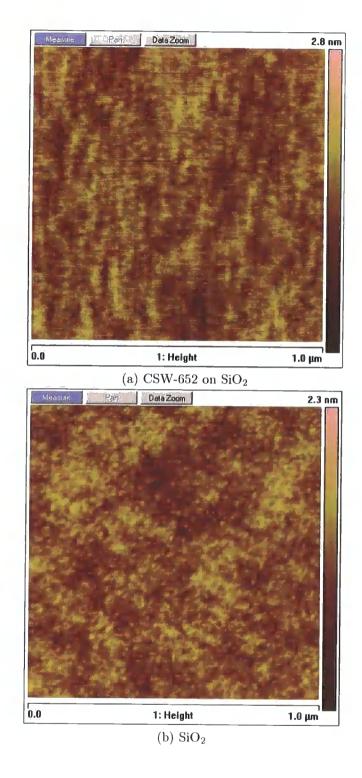

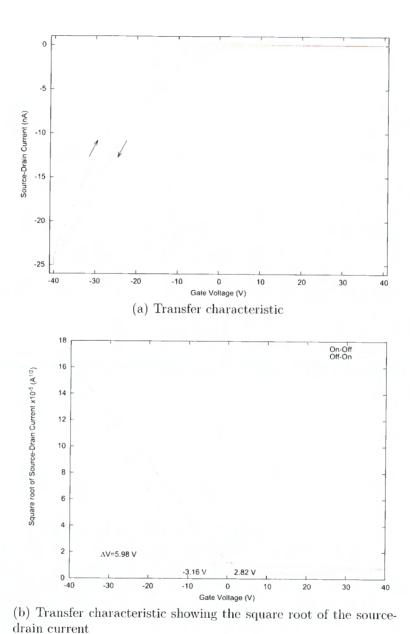

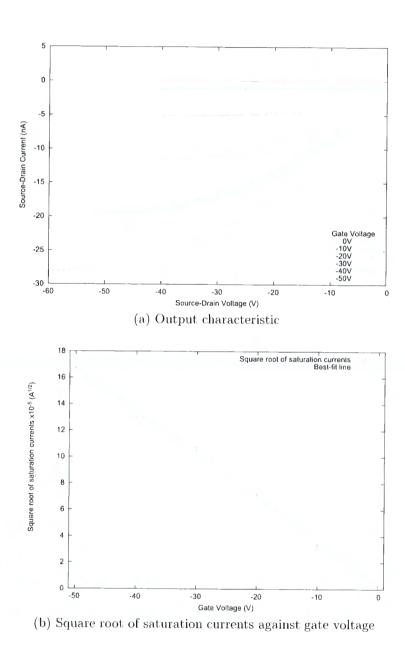

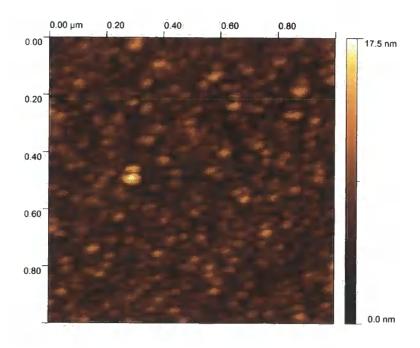

| Glass substrate, Ti/Au                              | Mobility: $1.5 \text{ cm}^2/\text{V/s}$ ;                                                                                                                                                                                                                                                                                                               |