1743

# Bifurcation Behavior of SPICE Simulations of Switching Converters: A Systematic Analysis of Erroneous Results

Xiaoqun Wu, Siu-Chung Wong, Member, IEEE, Chi K. Tse, Fellow, IEEE, and Junan Lu

Abstract—The SPICE simulation program is widely used as a brute force simulator for analyzing and designing switching power converters. Results from SPICE are mostly useful, but their integrity is sometimes questionable as erroneous results could be obtained which may not reflect the true behavior of the circuits being simulated. Various parameters in SPICE are crucial in controlling the convergence and accuracy of the simulated results, e.g., relative error tolerance and maximum integration step size. In this paper, we study the system consisting of the SPICE simulation algorithm and the circuit being simulated. Specifically, we describe the generation of flawed solutions in terms of bifurcation of the system under parameter variations. Erroneous results have been collected for different relative error tolerances, maximum integration step sizes, and parasitic inductance and capacitance. These flawed solutions can be analyzed in terms of the manifestation of period-doubling bifurcation and chaotic behavior under variation of selected simulation parameters. This paper provides a systematic approach to rationalizing the behavior of the SPICE simulator, its practical significance being in the identification of the ranges of simulation parameters for which flawed solutions can be produced.

*Index Terms*—Bifurcation, circuit simulation, power electronics, SPICE, switching converters.

## I. INTRODUCTION

ROPER models and reliable simulations are indispensable to the analysis and design of power electronics circuits [1]. SPICE is among the most widely used simulation tools which provide design information such as circuit operation, stability, transient performance, device stresses, etc. [1]–[5]. Transient analysis using SPICE is the most popular method for studying the large-signal behavior of switching converters. Switching converters, being nonlinear and time-varying, can be difficult to simulate using SPICE [6]–[8], the most commonly encountered problem being *convergence*. To overcome the

Manuscript received February 5, 2006; revised February 16, 2007. This work was supported by the Hong Kong Research Grants Council under a competitive earmarked research grant (PolyU 5289/05E). This paper was previously presented at the IEEE Power Electronics Specialists Conference, Jeju, Korea, June 2006. Recommended for publication by Associate Editor K. Smedley.

- X. Wu was with the Department of Electronic and Information Engineering, Hong Kong Polytechnic University, Hunghom, Hong Kong, China, while this work was performed. She is now with the Department of Mathematics and Statistics, Wuhan University, Hubei 430072, China.

- S.-C. Wong and C. K. Tse are with the Department of Electronic and Information Engineering, Hong Kong Polytechnic University, Hunghom, Hong Kong, China (e-mail: encktse@polyu.edu.hk).

- $\rm J.\,Lu$  is with the Department of Mathematics and Statistics, Wuhan University, Hubei 430072, China.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPEL.2007.904207

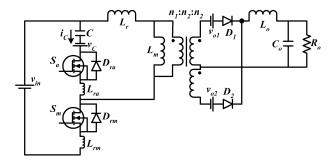

Fig. 1. Asymmetrical half-bridge forward converter.

TABLE I SIMULATION TIMES FOR DIFFERENT VALUES OF RELTOL AND TMAX

| RELTOL | TMAX    | Simulation time |

|--------|---------|-----------------|

| 0.005  | default | 5.780 s         |

| 0.02   | 10 ns   | 17.766 s        |

| 0.002  | 1 ns    | 151.904 s       |

convergence problems, engineers often resort to trial-and-error types of adjustment of simulation parameters, such as relaxing the relative error tolerance and increasing the maximum step size. Furthermore, flawed or erroneous results may be generated, giving wrong or misleading design information [9]. It is thus of interest to study the way in which the SPICE simulator fails to give correct results. So far, very little work has been reported to address the dynamics of the simulation process from a system viewpoint (i.e., treating the simulator that imitates the dynamics of the switching converter as a dynamical system and its parameters as system/bifurcation parameters), and to study the effects on the integrity of the results obtained. In this paper we investigate the SPICE simulator and its dynamical behavior in terms of possible bifurcations from stable operation. (See [10]–[15] for some previous study of bifurcations in power electronics, and [16]-[18] for a survey of the recent research in nonlinear dynamics of power converters.) We wish to know what parameters control the integrity of the results and how flawed results normally develop as system parameters are changed. The purpose is to understand the dynamics of SPICE simulations, leading to a more informed use of SPICE in the design of switching converters.

In Section II, we first describe a switching converter and some typical simulation results from SPICE. We will give three sets of simulation results in Section II-B. These results show different behaviors of the same circuit, under the same circuit condition

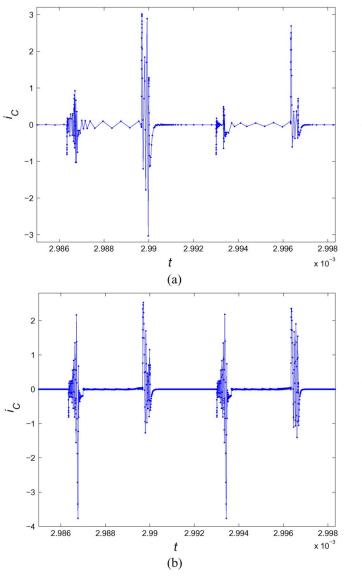

Fig. 2. Flawed simulation results of  $i_C$  with: (a) RELTOL = 0.005 and default TMAX and (b) RELTOL = 0.02 and TMAX = 10 ns.

Fig. 3. Improved simulation result of  $i_C$  with  ${\tt RELTOL}=0.002$  and  ${\tt TMAX}=1$  ns.

Fig. 4. (a) "Correct" simulation of  $i_C$  with RELTOL = 0.001, TMAX = 1 ns and METHOD = Gear. (b)–(c) Close-up views.

(c)

2.9966

2.9968

2.997

2.9964

2.9962

2.996

but with different simulator's parameters. We treat the SPICE algorithm and the switching converter as a nonlinear dynamical system [19] and study the effects of the simulator's parameters, relative error tolerance (RELTOL), maximum

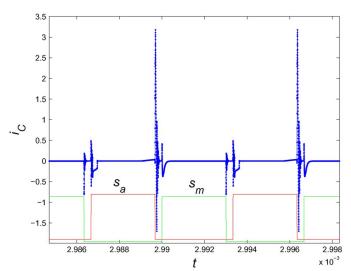

Fig. 5. (a) Flawed periodic operation of  $i_C$  with RELTOL = 0.001 and (b) close-up view.

Fig. 6. (a) Flawed periodic operation of  $i_C$  with RELTOL = 0.01 and (b) close-up view.

step size (TMAX), parasitic inductors  $L_{ra}$ ,  $L_{rm}$ , and parasitic capacitance  $C_{jo}$ , on the simulator's outputs. One of the circuit variables is chosen as the output. The simulated outputs of the system for different values of RELTOL are reported in Section III-A, those for different values of TMAX are reported in Section III-B, and those for varying parasitic inductance and capacitance are reported in Section III-C. We illustrate in Section IV the different operation boundaries in the system parameter space within which correct or flawed results are produced. Finally, we conclude our findings in Section V.

#### II. SPICE SIMULATION OF SWITCHING CONVERTERS

We consider the half-bridge forward converter shown in Fig. 1, [20], [21]. SPICE has been found very useful in identifying the number of states of operation, zero-voltage switching conditions, device stresses, and sensitivity of this circuit. In the following study, we will use SPICE to verify the operational waveforms of the circuit and our purpose is to find out whether SPICE would faithfully reproduce the correct information and

under what conditions it would fail to do so. Furthermore, as we are interested in knowing the integrity of SPICE in simulating the correct waveforms, we are not concerned here with the problem of convergence associated with the presence of a feedback loop. We thus omit such a feedback loop and focus on openloop simulations which are often performed by engineers in order to inspect the operational waveforms.

## A. Circuit Description

The circuit in Fig. 1 can be described in a SPICE netlist file, as shown in the Appendix. Dummy sources  $v_C$ ,  $V_{o1}$  and  $V_{o2}$  are added for the measurement of current. The transformer is assumed ideal. Parasitic source-pin-inductors  $L_{ra}$  and  $L_{rm}$  of the MOS switches are added for more accurate waveform calculations.  $D_{ra}$  and  $D_{rm}$  are body diodes of the MOS transistors. The two diodes can also be shunted by external fast switching diodes to improve the efficiency.

Steady-state (or near steady-state) waveforms can be obtained by running transient analysis in SPICE for a sufficiently long period of time. Usually, steady-state waveforms can be assumed when there is no significant change of the waveforms in two

Fig. 7. (a) Flawed periodic operation of  $i_C$  of longer period with RELTOL = 0.1 and (b) close-up view.

consecutive switching periods. A typical transient analysis command is as follows:

#### TRAN TSTEP TSTOP ( TSTART ( TMAX ))

where TMAX is the maximum step size used by SPICE. As a default, the program chooses either TSTEP or (TSTOP-TSTART)/50.0, whichever is smaller. The calculation of steady-state waveforms can be speeded up by using the optional UIC (use initial conditions) keyword at the end of the .TRAN statement. Also, near steady-state voltages and currents values are inserted using "IC = ..." at the end of the elements or using the .IC control line for various initial node voltages obtained from previous solutions.

# B. Erroneous Simulation Results: Beyond Speed-Accuracy Tradeoff

It is generally believed that simulation speed and convergence can be improved dramatically by relaxing the requirement of simulation tolerance [6]. We have measured the simulation time for three sets of simulation tolerances and controls,

Fig. 8. (a) Flawed chaotic operation of  $i_C$  with RELTOL = 0.2 and (b) close-up view.

as shown in Table I. Figs. 2 and 3 show the corresponding simulated waveforms.

For comparison, we also present in Fig. 4 the "correct" (practically consistent) waveforms of  $i_C$  with a tighter simulation control, i.e., RELTOL = 0.001, TMAX = 1 ns and the integration method is Gear. We observe a rather large discrepancy in the simulated results for different simulator's parameters. This clearly shows that the simulator's parameters do not only control the speed-accuracy tradeoff, but may also be crucial in determining whether correct or flawed results would be produced. It is thus useful to study the dynamics of the system consisting of the SPICE simulation algorithm that imitates the dynamics of the switching converter.

Since we are primarily concerned with system stability in relation to the SPICE parameters (RELTOL and TMAX), and the circuit parameters (parasitic inductors  $L_{ra}$ ,  $L_{rm}$  and capacitance  $C_{jo}$  of body diodes  $D_{ra}$  and  $D_{rm}$ ), we will focus on variation of these parameters. From the simulation results based on the netlist shown in the Appendix, we observe period-doubling bifurcation and chaotic behavior in some intervals of time during a switching cycle. In the following, we choose the current  $i_C$ , as shown in Fig. 1, as the system output for the purpose of identifying the instability phenomena.

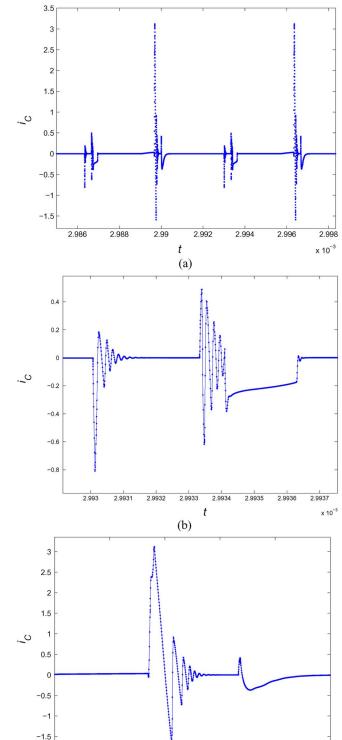

Fig. 9. (a) "Correct" simulation of  $i_C$  with TMAX = 0.5 ns; (b) flawed period-2 operation of  $i_C$  with TMAX = 2 ns; (c) flawed period-4 operation of  $i_C$  with TMAX = 5 ns; (d) flawed periodic operation of  $i_C$  with TMAX = 10 ns.

#### III. PERIOD-DOUBLING BIFURCATION OF SPICE RESULTS

## A. Varying RELTOL

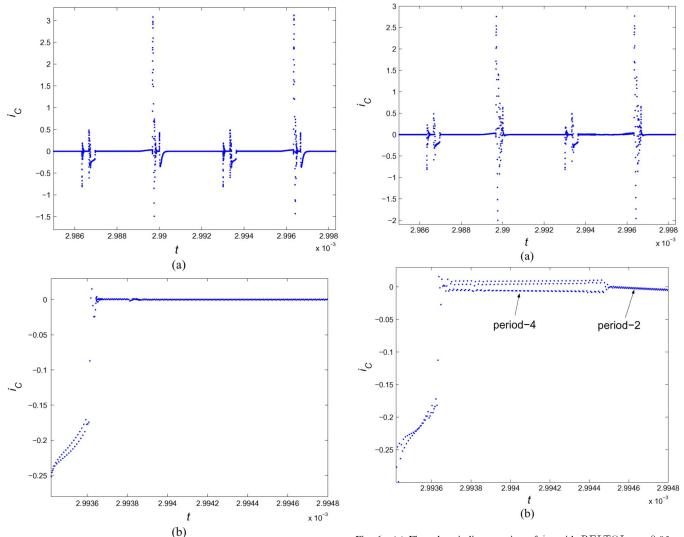

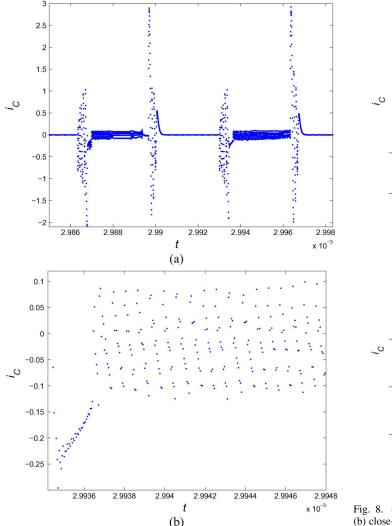

In this section, we present a detailed inspection of the effect of varying RELTOL. In these simulations, TMAX is fixed at 5 ns. The simulated results with varying RELTOL are shown in Figs. 5 to 8.

Fig. 5 plots the waveform of  $i_C$  in two switching cycles with RELTOL = 0.001. An erroneous period-2 subharmonic operation is observed, as shown in the close-up view in Fig. 5(b). Fig. 6 shows period-2 and period-4 operation (also erroneous) in some intervals of a switching cycle with RELTOL = 0.01. Also, Fig. 7 shows erroneous periodic operation of longer periods with a larger RELTOL. Finally, Fig. 8 displays erroneous chaotic operation with RELTOL = 0.2.

In general, we observe that the simulation results become more "unstable" (in the sense that more erroneous answers are produced) as we increase RELTOL.

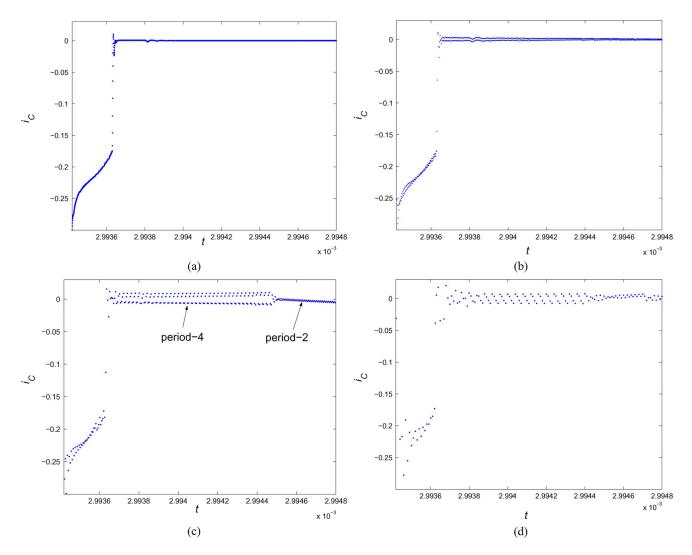

#### B. Varying TMAX

We now look at the effect of varying TMAX. For simplicity, we keep RELTOL at 0.01, and display the close-up views in some interval of a switching cycle.

Fig. 9(a) displays the "correct" simulated operation of  $i_C$  with TMAX = 0.5 ns. When TMAX is relaxed to 2 ns, an erroneous period-2 operation is observed, as shown in Fig. 9(b). When we further increase TMAX, we observe period-2 and period-4 operations, as shown in Fig. 9(c) and (d).

Thus, we observe that the simulation results again become progressively more "unstable" as TMAX is increased. Again, by "unstable" we mean that the simulation results do not converge to the correct results.

#### C. Varying Parasitic Inductance and Capacitance

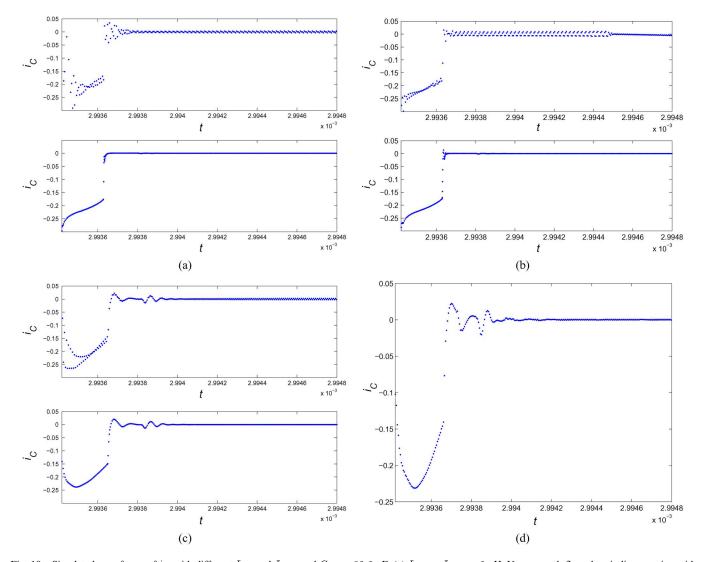

Since parasitic inductors  $L_{ra}$ ,  $L_{rm}$  and parasitic capacitance  $C_{jo}$  of the body diodes of the MOS transistors may also affect the simulated results, we now look at the effect of varying these parasitic elements. In the following simulations, TMAX is fixed

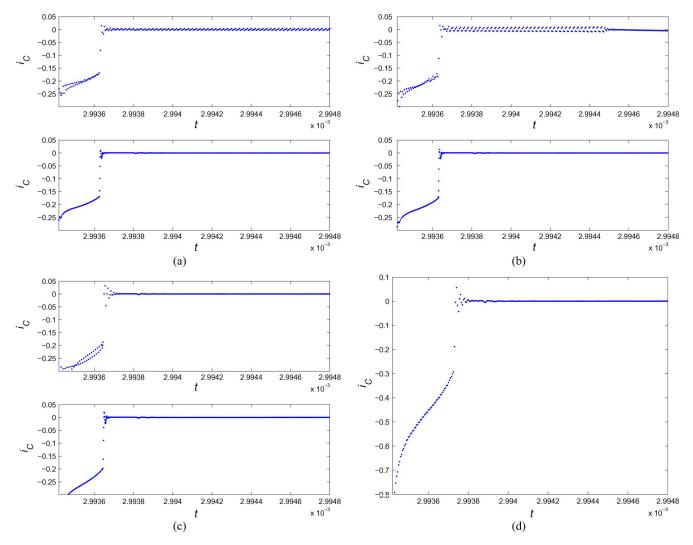

Fig. 10. Simulated waveforms of  $i_C$  with different  $L_{ra}$  and  $L_{rm}$ , and  $C_{jo}=83.2$  pF. (a)  $L_{ra}=L_{rm}=1$  nH. Upper panel: flawed periodic operation with RELTOL = 0.01; lower panel: "correct" result with RELTOL = 0.001 and METHOD = Gear. (b)  $L_{ra}=L_{rm}=5$  nH. Upper panel: flawed periodic operation with RELTOL = 0.01; lower panel: "correct" result with RELTOL = 0.001 and METHOD = Gear. (c)  $L_{ra}=L_{rm}=80$  nH. Upper panel: flawed periodic operation with RELTOL = 0.01; lower panel: correct result with RELTOL = 0.001 and METHOD = Gear. (d) "Correct" simulation with  $L_{ra}=L_{rm}=150$  nH and RELTOL = 0.01.

at 5 ns. For simplicity, we only display the close-up views in some intervals of a switching cycle.

Fig. 10 shows the simulated results for different values of  $L_{ra}$  and  $L_{rm}$ , and  $C_{jo}=83.2$  pF. The upper panels of Fig. 10(a) to (c) display erroneous period-2 and period-4 waveforms of  $i_C$  for relatively small values of inductance with RELTOL = 0.01. For comparison, we also show in the lower panels the "correct" simulated results with a tighter numerical control, i.e., RELTOL = 0.001 and METHOD = Gear. Increasing the parasitic inductance to 150 nH, we obtain the "correct" result, as shown in Fig. 10(d). Thus, we observe that the simulation results become more "stable" as  $L_{ra}$  and  $L_{rm}$  are increased.

Fig. 11 shows the simulated results for different values of parasitic capacitance  $C_{jo}$ , while  $L_{ra}$  and  $L_{rm}$  are kept at 5 nH. The upper panels of Fig. 11(a) to (c) display erroneous periodic waveforms of  $i_C$  for relatively small values of  $C_{jo}$  with RELTOL = 0.01. Increasing the capacitance to 400 pF,

period-2 operation is observed, as shown in Fig. 11(c). The corresponding "correct" results for different values of  $C_{jo}$  are also presented in the lower panels in Fig. 11(a) and (c) for the purpose of comparison. Further increasing  $C_{jo}$  to 2400 pF, we obtain the "correct" result, as shown in Fig. 11(d). Thus, the simulation results again become more "stable" as the parasitic capacitance is increased.

# IV. APPLICATION: IDENTIFICATION OF OPERATION BOUNDARIES

Of engineering importance is the ranges of parameters that correspond to different types of results, flawed and correct. To address this issue, we need to identify the operation boundaries in some appropriate parameter space. We have performed a large number of simulations for different sets of parameters, which enable operation boundaries to be identified. It should be noted

Fig. 11. Simulated waveforms of  $i_C$  with different  $C_{jo}$ , and  $L_{ra}=L_{rm}=5$  nH. (a)  $C_{jo}=15$  pF. Upper panel: flawed periodic operation with RELTOL = 0.01; lower panel: "correct" result with RELTOL = 0.001 and METHOD = Gear. (b)  $C_{jo}=83.2$  pF. Upper panel: flawed periodic operation with RELTOL = 0.01; lower panel: "correct" result with RELTOL = 0.001 and METHOD = Gear. (c)  $C_{jo}=400$  pF. Upper panel: flawed periodic operation with RELTOL = 0.01; lower panel: "correct" result with RELTOL = 0.001 and METHOD = Gear. (d) "Correct" simulation with  $C_{jo}=2400$  pF and RELTOL = 0.01.

that although numerical results are presented here for a particular circuit, the general procedure is applicable to any circuit to yield similar information.

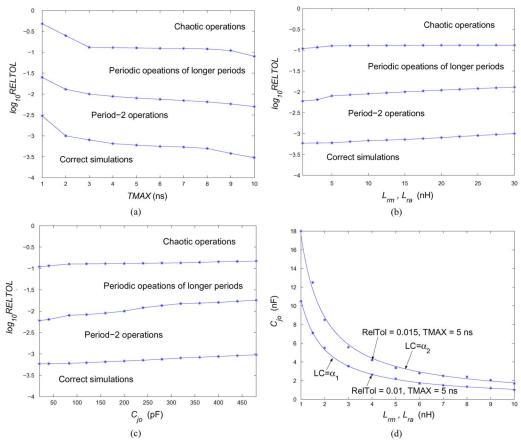

Fig. 12(b) and (c) displays the boundaries of operations in the 2-D parameter space of  $log_{10}RELTOL$  versus  $L_{ra}, L_{rm}$ and  $C_{io}$ . Here, we observe that the simulated results become generally more "stable" as the parasitic inductance and capacitance are increased. The correct-flawed simulation boundaries in the space of parasitic capacitance versus parasitic inductance for different values of RELTOL are shown in Fig. 12(d), where TMAX is fixed at 5 ns. For a certain value of RELTOL, we find that the numerically obtained boundary curves are generally consistent with the curve  $LC = \alpha_i$ , where  $\alpha_i$  is a constant. The correct simulated results should then correspond to the region Fig. 12(a) displays the boundaries of operations in the 2-D parameter space of  $log_{10}$ RELTOL versus TMAX. It can be observed that the simulated results become more "unstable" as TMAX and RELTOL are increased, which is consistent with the observations made earlier in Sections III-A and III-B

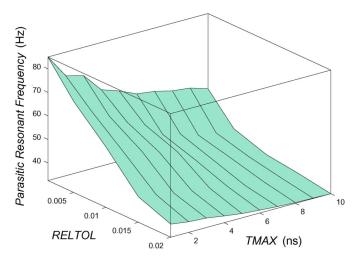

defined by  $LC > \alpha_i$ . Since the parasitic resonant frequency is given by

$$f = \frac{1}{2\pi\sqrt{LC}}\tag{1}$$

the above observation clearly indicates that for given values of RELTOL and TMAX, there is a critical parasitic resonant frequency  $f_c$  below which the simulated results are correct. Fig. 13 displays the 3-D boundary surface in the 3-D space of the parasitic resonant frequency, RELTOL and TMAX. In this figure, correct simulations correspond to the region below the surface and erroneous simulations correspond to system parameters above the surface.

From the above results, we clearly see that correct simulation results can only be obtained if the simulation parameters are chosen within the region where the system (SPICE) does not bifurcate into period-2, other longer periodic or chaotic or-

Fig. 12. Boundaries of operations in 2-D parameter space of (a)  $\log_{10}$  RELTOL versus TMAX; (b)  $\log_{10}$  RELTOL versus parasitic inductance; (c)  $\log_{10}$  RELTOL versus parasitic capacitance; (d) parasitic capacitance versus parasitic inductance for two different values of RELTOL. Simulation of "correct" results corresponds to region above the curves.

Fig. 13. Correct-flawed simulation boundary surface. "Correct" simulated results correspond to the area below the surface.

bits. It should be noted that although the boundary curves will be different if different circuit parameters are used, the general trend of the stability behavior should remain unchanged. Thus, an effective strategy for obtaining correct answers from SPICE is to choose TMAX and RELTOL appropriately in conjunction with the sizes of the circuit parasitics, as explained earlier.

#### V. CONCLUSION

The SPICE simulator, along with the switching converter it imitates, has been studied in terms of the bifurcation behavior of the simulated results. A dynamical system viewpoint is taken to examine the SPICE simulated results for different parameter values. It has been found that SPICE exhibits period-doubling bifurcation and chaos when parameters are not properly chosen, giving erroneous results which do not reflect the true behavior of the circuits being simulated. Our main conclusion is that SPICE is itself a dynamical system which is controlled by a number of parameters whose variations cause the simulated results to manifest various behaviors. We also find that the system's behavior is affected by the parasitic resonant frequency of the circuit. In this paper, we have considered four parameters in particular, namely, relative error tolerance, maximum step size, parasitic inductance, and parasitic capacitance. We have performed a thorough investigation which identifies various system parameters that affect the integrity of the simulation results and the parameter boundaries that define a region in which trustworthy results can be guaranteed. The results obtained here can facilitate parameter selection for guaranteeing correct operations. Finally, it should be noted that our study has explained the convergence problem of SPICE from a system's viewpoint, treating SPICE itself as a system which may exhibit complex behavior when its parameters are changed. In particular, for the given circuit under study, we have observed period-doubling bifurcation as the key mechanism through which SPICE loses stability and bifurcates into period-2 orbits. When the circuit being simulated is a different one, SPICE may exhibit other bifurcation behaviors. The possibilities, like in any other nonlinear system, are rich. This remains the key difficulty in deriving a universal solution for solving SPICE's stability problems.

# APPENDIX SPICE NETLIST

| .PARAM | f = 150 e3                                                      |

|--------|-----------------------------------------------------------------|

| .PARAM | T = 1/f                                                         |

| .PARAM | d = 0.45                                                        |

| .PARAM | dT = T*d                                                        |

| .PARAM | $fT = T^*(d)$                                                   |

| .PARAM | f1T = (T + dT - fT)/2                                           |

| .PARAM | rise = T/1e3                                                    |

| .PARAM | n = 19                                                          |

| *      | Please note that original spice3 does not support .PARAM macro, |

| *      | we use .PARAM macro here for better readability.                |

| Vin    | nss 0 DC 120                                                    |

| Vc1    | nc1 0 DC 0 Pulse 0 12 0 {rise}                                  |

|        | $+{\rm rise}$                                                   |

|        | $+\{dT\}$                                                       |

|        | $+\{T\}$                                                        |

| Rc1    | nc1 nc11 5                                                      |

| Vc2    | nc2 n2 DC 0 Pulse 0 12 {f1T}                                    |

|        | $+\{rise\}$                                                     |

|        | $+{\rm rise}$                                                   |

|        | $+\{f\Gamma\}$                                                  |

|        | $+\{T\}$                                                        |

| Rc2    | nc2 nc22 5                                                      |

| C      | nss n1c 165n                                                    |

| Vc     | n1 n1c 0                                                        |

| Lr     | nss n3 30u                                                      |

| Lm     | n3 n2 150u IC = 1                                               |

| RLm    | n3 n2 10k                                                       |

| Mm     | n2 nc11 n2m n2m Sma $L=2uW=.64$                                 |

| Ma     | n1 nc22 n2a n2a Sma $L=2uW=.64$                                 |

| Drm    | n2m n2 Dma                                                      |

| Dra    | n2a n1 Dma                                                      |

```

Lra

n2 n2a 5n

0 n2m 5n

Lrm

n3 \ n2 \ i = i(Vo1)/\{n\}

B<sub>p</sub>1

Bp2

n3 \ n2 \ i = -i(Vo2)/\{n\}

Bout1

0 \text{ n4 } v = (v(n3) - v(n2))/\{n\}

0 \text{ n5 } v = (v(n2) - v(n3))/\{n\}

Bout2

n6 n4 0

Vo<sub>1</sub>

Vo<sub>2</sub>

n7 n5 0

D1

n6 n8 Dout

D2

n7 n8 Dout

Lo

n8 \text{ no } 4u \text{ IC} = 16

Co

no 0.990u IC = 5

no 0 0.32

Ro

.MODEL

Sma NMOS level = 3VTO = 3.697KP =

20.68u \text{ GAMMA} = 0PHI = .6RD =

.02108RS = .4508IS = 202.9f JS = 0

+PB = .8CBD = 366.5pCJ = 0CJSW =

0CGSO = 950pCGDO = 300pCGBO =

0 + TOX = 100 \text{nXJ} = 0DELTA =

0ETA = 0U0 = 0

.MODEL

Dma D IS = 7.27pRS = 22.4mBV =

200 \text{IBV} = 10.0 \text{uCJO} = 83.2 \text{pM} =

0.333N = 0.700TT = 36.0n

.MODEL

Dout D IS = 0.5fCJO = 1400pBV =

100M = 0.5VJ = 0.2TT = 1n

.TRAN

10n 3000u 2980u TMAX UIC

.OPTION

RELTOL = * * *

.END

.CON-

TROL

RUN

.ENDC

```

#### REFERENCES

- [1] D. Maksimovic, A. M. Stankovic, V. J. Thottuvelil, and G. C. Verghese, "Modeling and simulation of power electronic converters," *Proc. IEEE*, vol. 89, no. 6, pp. 898–912, Jun. 2001.

- [2] T. L. Quarles, SPICE3 Version 3C1 User's Guide Univ. of California. Berkeley, Apr. 1989, ERL Memo No. UCB/ERL M89/46.

- [3] J. Xu and M. Grotzbach, "Time-domain analysis of half-wave zerocurrent switch quasi-resonant converters by using SPICE," *IEEE Trans. Ind. Electron.*, vol. 40, no. 6, pp. 577–579, Dec. 1993.

- [4] A. M. Nassar, A. M. Moselhy, and M. A. El-Gazzar, "Comparison study between a computer aided analysis program using state space technique and SPICE program," in *Proc. URSI Int. Symp. Signals, Sys*tems, and Electronics, Oct. 1995, pp. 477–480.

- [5] J. F. Dawson, D. Bozec, D. R. Cullen, L. M. McCormack, and B. W. Flynn, "Simulation of harmonic and conducted interference levels from switched-mode power supplies and phase controllers," in *Proc. Int. Symp. Electromagnetic Compatibility*, Santa Clara, CA, Aug. 2004, pp. 598–603.

- [6] R. D. Castro, "Solving SPICE problems," *IEE Proc. Pt. G*, vol. 135, no. 4, pp. 177–178, Aug. 1988.

- [7] Z. Q. Shang, "SPICE: Surviving problems in circuit evaluation," IEE Colloq. Convergence Problem in SPICE, pp. 10/1–10/5, Jun. 30, 1993.

- [8] E. Yilmaz and M. M. Green, "Some standard SPICE DC algorithms revisited: Why does SPICE still not converge?," in *Proc. IEEE Int. Symp. Circuits and Systems*, 1999, pp. 286–289.

- [9] K. G. Nichols, T. J. Kazmierski, M. Zwolinski, and A. D. Brown, "Overview of SPICE-like circuit simulation algorithms," in *IEE Proc. Circuits, Devices and Systems*, Aug. 1994, vol. 141, no. 4, pp. 242–250.

- [10] J. H. B. Deane and D. C. Hamill, "Instability, subharmonics and chaos in power electronic systems," in *Proc. IEEE Power Electron. Specialists Conf. Rec.*, Jun. 1989, pp. 34–42.

- [11] C. K. Tse, "Flip bifurcations and chaos in a three-state boost switching regulator," *IEEE Trans. Circuits Syst. I*, vol. 41, no. 1, pp. 16–23, Jan. 1994

- [12] K. Chakrabarty, G. Poddar, and S. Banerjee, "Bifurcation behavior of the buck converter," *IEEE Trans. Power Electron.*, vol. 11, no. 3, pp. 439–447, May 1996.

- [13] S. Banerjee, E. Ott, J. A. Yorke, and G. H. Yuan, "Anomalous bifurcations in DC-DC converters: Borderline collisions in piecewise smooth maps," in *Proc. IEEE Power Electronics Specialists Conf. Rec.*, Jun. 1997, pp. 1337–1344.

- [14] H. H. C. Iu and C. K. Tse, "Study of low-frequency bifurcation phenomena of a parallel-connected boost converter system via simple averaged models," *IEEE Trans. Circuits Syst. I*, vol. 50, no. 5, pp. 679–685, May 2003.

- [15] D. Dai, C. K. Tse, and X. Ma, "Symbolic analysis of switching systems: Application to bifurcation analysis of dc/dc switching converters," *IEEE Trans. Circuits Syst. I*, vol. 52, no. 8, pp. 1632–1643, Aug. 2005.

- [16] S. Banerjee and G. Verghese, Eds., Nonlinear Phenomena in Power Electronics. New York: IEEE Press, 2000.

- [17] C. K. Tse and M. Di Bernardo, "Complex behavior of switching power converters," *Proc. IEEE*, vol. 90, no. 5, pp. 768–781, May 2002.

- [18] C. K. Tse, Complex Behavior of Switching Power Converters. Boca Raton, FL: CRC, 2003.

- [19] K. T. Alligood, T. D. Sauer, and J. A. Yorke, Chaos: An Introduction to Dynamical Systems. New York: Springer-Verlag, 1996.

- [20] Y. H. Leu and C. L. Chen, "Improved asymmetrical half-bridge converter using a tapped output inductor filter," *IEE Proc. Electrical Power Applications*, vol. 150, no. 4, pp. 417–424, Apr. 2003.

- [21] Y. H. Leu, C. L. Chen, and T. M. Chen, "Analysis and design of twotransformer asymmetrical half-bridge converter," in *Proc. IEEE Power Electronics Specialists Conf. Rec.*, Jun. 2002, pp. 943–948.

**Siu-Chung Wong** (M'01) received the B.Sc. degree in physics from the University of Hong Kong in 1986, the M.Phil. degree in electronics from the Chinese University of Hong Kong in 1989, and the Ph.D. degree from the University of Southampton, Southampton, U.K., in 1997.

He is currently an Assistant Professor in the Department of Electronic and Information Engineering, Hong Kong Polytechnic University, Hunghom, Hong Kong. His research interests include modeling of power converters, nonlinear analysis of power

electronics, LED lighting systems, automobile lighting systems, and Internet traffic analysis.

Dr. Wong is a member of the Electrical College, The Institution of Engineers, Australia.

Chi K. Tse (M'90–SM'97–F'06) received the B.Eng. degree (with first-class honors) in electrical engineering in 1987 and the Ph.D. degree in 1991 from the University of Melbourne, Melbourne, Australia

He is presently Chair Professor and Head of Department of Electronic and Information Engineering, Hong Kong Polytechnic University, Hunghom, Hong Kong, and is a Guest Professor with Wuhan University, Heibei, China. His research interests include nonlinear systems, complex networks and

power electronics. He is the author of *Linear Circuit Analysis* (London, U.K.: Addison-Wesley, 1998) and *Complex Behavior of Switching Power Converters* (Boca Raton: CRC Press, 2003), co-author of *Chaos-Based Digital Communication Systems* (Heidelberg, Germany: Springer-Verlag, 2003), *Communications with Chaos* (London: Elsevier, 2006) and *Signal Reconstruction With Applications to Chaos-Based Communications* (Beijing, China: Tsinghua University Press, 2007), and co-holder of a U.S. patent.

Dr. Tse was awarded the L.R. East Prize by the Institution of Engineers, Australia, in 1987. He won the IEEE TRANSACTIONS ON POWER ELECTRONICS Prize Paper Award for 2001 and the International Journal of Circuit Theory and Applications Best Paper Award for 2003. In 2005, he was named an IEEE Distinguished Lecturer. While with Hong Kong Polytechnic University, he twice received the President's Award for Achievement in Research, the Faculty's Best Researcher Award, the Research Grant Achievement Award, and a few other teaching awards. From 1999 to 2001, he served as an Associate Editor for the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS PART I—FUNDAMENTAL THEORY AND APPLICATIONS, and since 1999 he has been an Associate Editor for the IEEE TRANSACTIONS ON POWER ELECTRONICS. He currently also serves as the Editor-in-Chief of the IEEE Circuits and Systems Society Newsletter, an Associate Editor for the International Journal of Systems Science, a Guest Associate Editor of the IEICE Transactions on Fundamentals of Electronics, Communications and Computers, and a Guest Editor of Circuits, Systems and Signal Processing.

**Xiaoqun Wu** was born in Hubei, China, in 1978. She received the B.Sc. degree in applied mathematics and the Ph.D. degree in computational mathematics from Wuhan University, Hubei, China, in 2000 and 2005, respectively.

She was a Research Assistant from February 2004 to March 2005 and a Research Associate from August 2005 to October 2006, with the Department of Electronic and Information Engineering, Hong Kong Polytechnic University, Hong Kong. Since May 2005, she has been a Lecturer with the School

of Mathematics and Statistics, Wuhan University, Hubei. Her research interests include complex networks, nonlinear dynamics, chaos control and synchronization, and bifurcation analysis in power electronics.

**Junan Lu** received the B.Sc. degree in geophysics from Peking University, Peking, China, and the M.Sc. degree in applied mathematics from Wuhan University, Wuhan, China, in 1968 and 1982, respectively.

He is currently a Professor with the School of Mathematics and Statistics, Wuhan University, Hubei, China. His research interests include nonlinear systems, chaos control and synchronization, complex networks, and scientific and engineering computing. He is the coauthor of *An Introduction to Chaotic Dynamics* (Wuhan, China: Wuhan Univ.

Hydraulic and Electrical Engineering Press, 1998), *Matlab Solutions of Partial Differential Equations* (Wuhan, China: Wuhan Univ. Press, 2001) and *Analysis of Chaotic Time Series and Its Applications* (Wuhan: Wuhan Univ. Press, 2002). He has also published more than 100 journal papers.