# Control Design of VSIs to Enhance Transient Performance in Microgrids

Federico, de Bosio; Antonio DeSouza Ribeiro, Luiz; Savaghebi, Mehdi; Quintero, Juan Carlos Vasquez; Guerrero, Josep M.

Published in: Proceedings of 18th European Conference on Power Electronics and Applications (EPE'16 - ECCE Europe)

DOI (link to publication from Publisher): 10.1109/EPE.2016.7695496

Publication date: 2016

Aalborg Universitet

**Document Version** Early version, also known as pre-print

Link to publication from Aalborg University

Citation for published version (APA):

Federico, D. B., Antonio DeSouza Ribeiro, L., Savaghebi, M., Quintero, J. C. V., & Guerrero, J. M. (2016). Control Design of VSIs to Enhance Transient Performance in Microgrids. In Proceedings of 18th European Conference on Power Electronics and Applications (EPE'16 - ECCE Europe) IEEE. DOI: 10.1109/EPE.2016.7695496

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- ? Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- ? You may not further distribute the material or use it for any profit-making activity or commercial gain ? You may freely distribute the URL identifying the publication in the public portal ?

Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

## **Control Design of VSIs to Enhance Transient Performance in Microgrids**

| Federico de Bosio            |

|------------------------------|

| Energy Department            |

| Politecnico di Torino        |

| Corso Duca degli Abruzzi, 24 |

| 10129 Torino, Italy          |

| federico.debosio@polito.it   |

Luiz Antonio de Souza Ribeiro Institute of Electrical Energy Federal University of Maranhao Av. Dos Portugueses, 1966 65072010 Sao Luis MA, Brazil I.a.desouzaribeiro@ieee.org

Mehdi Savaghebi, Juan C. Vasquez, Josep M. Guerrero Department of Energy Technology Aalborg University Pontoppidanstraede 111 9220 Aalborg, Denmark {mes, juq, joz}@et.aau.dk www.microgrids.et.aau.dk

# **Keywords**

«Current regulator», «Voltage Regulator», «Power Quality», «Microgrids».

## Abstract

This paper discusses the control design for an islanded microgrid in order to ensure acceptable performance in terms of voltage quality and load sharing by focusing on transient conditions. To this aim, state feedback decoupling approach has been applied. Experimental tests have been performed to demonstrate the effectiveness of the proposed approach.

# Introduction

Distributed Generators (DGs) often consist of power sources connected through a power-electronic interface converter (e.g. an inverter in the case of dc-to-ac conversion) to a utility grid or microgrid. Microgrid is a local grid consisting of DGs, energy storage systems and dispersed loads which may operate in grid-connected or islanded mode [1],[2].

The main role of the DG interface converter is to control power injection. Moreover, mitigation of voltage quality problems such as harmonics and unbalance can be achieved through proper control strategies. Another important point in microgrids is the load sharing among DGs especially when the distribution lines are not symmetric [3]-[5]. In order to share fundamental positive sequence load component among inverters, droop control has been extensively applied. In this case, the accuracy of the power control is affected by the output impedance of the DG units as well as the line impedances. By including virtual impedance at fundamental frequency, the effect of the line impedances can be mitigated [6]. Furthermore, the virtual impedance can improve the sharing of nonlinear and unbalanced loads [4],[7],[8]. Recent approaches in control of power converters for stand-alone applications demonstrated the benefits introduced by decoupling the controlled states, i.e. the inductor current and capacitor voltage [9]. Higher damping of the system is achieved improving the response of the regulators during transients.

However, in the present literature, voltage quality and load sharing in transient conditions (e.g. load steps) are not well explored. Based on this, the paper applies a state feedback decoupling approach to ensure minimized voltage distortion and load sharing errors during transient conditions. A general case in which unbalanced nonlinear loads are supplied in the microgrid is considered. The control design is validated through experimental tests.

### **Control Structure of DGs Interface Converters**

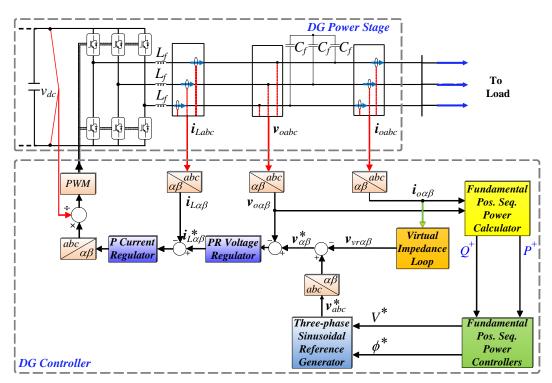

Fig. 1 shows the power stage and control system of a three-phase Voltage Source Inverter (VSI) which acts as a DG interface converter in the microgrid. The inverter is terminated by an LC filter and the control structure mainly consists of controllers for fundamental positive sequence powers (droop controllers), virtual impedance block and voltage and current inner control loops.

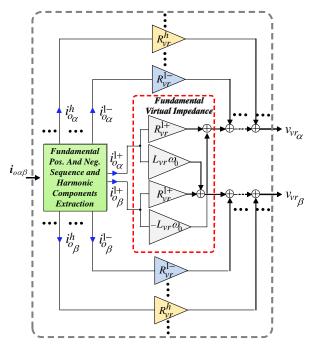

The details of power calculation and droop control can be found in [10]. The structure of virtual impedance block is depicted in Fig. 2 where the components of the inverter output current are extracted and then fed to a selective structure. In other words, fundamental positive sequence components are fed to an RL impedance block and other components (fundamental negative sequence as well as harmonic components, here  $3^{rd}$ ,  $5^{th}$  and  $7^{th}$ ) pass through virtual resistances [4].

Voltage controller is Proportional-Resonant (PR) whereas current controller is only formed by a Proportional (P) gain according to the following equations:

$$G_{\nu}(s) = k_{pV} + \sum_{h=1,3,5,7} \frac{k_{ih}[scos(\varphi) - h\omega_1 \sin(\varphi)]}{s^2 + (h\omega_1)^2}$$

(1)

$$G_i(s) = k_{pI} \tag{2}$$

The inner current and voltage loops are cascaded and designed using serial tuning. The bandwidth of the inner current loop is set to a value that provides fast dynamic performance, and avoids interactions with the voltage loop. In practical applications the maximum allowed bandwidth for the inner current loop is mainly limited by the transport and sampling delays.

In islanded microgrids, the VSI operates in voltage mode where the capacitor voltage and inductor currents are the controlled states [11]. With reference to Fig. 1, the voltage and current are measured and transformed to the stationary reference frame ( $\alpha\beta$ ), being  $i_{L\alpha\beta}$  and  $v_{o\alpha\beta}$  the inductor current and capacitor voltage vectors, respectively.

The voltage loop, with the limitations imposed by its bandwidth, controls the converter output voltage by fixing the current reference. The inner current loop controls the inverter states in order to follow the current reference.

Fig. 1. DG power stage and control system

Fig. 2. Virtual impedance scheme [4]

## **Design of Voltage and Current Regulators**

It is expected from any current or voltage regulator: i) to provide zero steady-state error; ii) accurately track the commanded reference during transients; iii) have a bandwidth as higher as possible; and iv) decrease or minimize the total harmonic distortion.

The general approach to design the inner current loop is to neglect the coupling between the inductor current and the capacitor voltage. This is the basic assumption in AC drives and grid connected applications, as the electromotive force is strong, and acts as a disturbance to the current regulator.

The proportional gain of the current regulator is selected to achieve the desired bandwidth of approximately  $f_{bw} = 1 kHz$ . For the delay of the system  $T_d = 1.5/f_s = 150 \mu s$ , and the system parameters (see Table I), the controller gain is approximately  $k_{pI} = 5.61$  (see Table II).

| Table I. System parameters |                                    | Table II. Current |                           | Table IV. Droop control |       |                                       |          |                    |

|----------------------------|------------------------------------|-------------------|---------------------------|-------------------------|-------|---------------------------------------|----------|--------------------|

| Parameter                  | Symbol                             | Value             | regulator control         |                         |       | parameters                            |          |                    |

| Switching frequency        | $f_s$                              | 10 kHz            | 0                         | meters                  |       | Parameter                             | Symbol   | Value              |

| Filter inductance          | $L_f$                              | 1.8 mH            | Parameter                 | Symbol                  | Value | Proportional gain<br>(active power)   | $k_{pP}$ | 1×10 <sup>-6</sup> |

| Filter capacitance         | $C_f$                              | 27 µF             | Proportional              | 1,                      | 5 6 1 | Integral gain (active                 | 1-       | 1×10 <sup>-4</sup> |

| Inductor ESR               | $R_{f}$                            | 0.1 Ω             | gain w/o<br>decoupling    | $k_{pI}$ 5.61           | 3.01  | power)                                | $k_{iP}$ | 1×10               |

| Rated linear load          | R <sub>l</sub><br>C <sub>NL</sub>  | 68 Ω<br>235 μF    | Proportional<br>gain with | lr.                     | 6.42  | Proportional gain<br>(reactive power) | $k_{pQ}$ | 5×10 <sup>-4</sup> |

| Nonlinear load             | R <sub>NL</sub><br>L <sub>NI</sub> | 155 Ω<br>0.084 mH | decoupling                | k <sub>pI</sub>         | 0.42  |                                       |          |                    |

Table III. Voltage

| Table | V. | Virtual | l iı | mped | ance |

|-------|----|---------|------|------|------|

|       | I  | oaramet | tei  | rs   |      |

| regulator control                   |                    |       | Parameter                                   | Symbol        | Value  |

|-------------------------------------|--------------------|-------|---------------------------------------------|---------------|--------|

| parameters                          |                    |       | Virtual inductance                          | $L_{vr}$      | 2.5 mH |

|                                     |                    |       | Fund. pos.                                  | $R_{vr}^{1+}$ | 0.3 Ω  |

| Parameter                           | Symbol             | Value | sequence                                    |               | 0.5 == |

| Proportional gain                   | $k_{pV}$           | 0.05  | Fund. neg.                                  | $R_{wr}^{1-}$ | 1.5 Ω  |

| Integral gain                       | $k_{iV}$           | 100   | sequence                                    | vr            | 1.0 == |

| Integral gain 3 <sup>rd</sup><br>HC | k <sub>iV,h3</sub> | 10    | Pos. and neg. sequence 3 <sup>rd</sup> H    | $R_{vr}^3$    | 2 Ω    |

| Integral gain 5 <sup>th</sup><br>HC | k <sub>iV,h5</sub> | 10    | Pos. and neg. sequence 5 <sup>th</sup> H    | $R_{vr}^5$    | 4 Ω    |

| Integral gain 7 <sup>th</sup><br>HC | k <sub>iV,h7</sub> | 10    | Pos. and neg.<br>sequence 7 <sup>th</sup> H | $R_{vr}^7$    | 4 Ω    |

|                                     |                    |       |                                             |               |        |

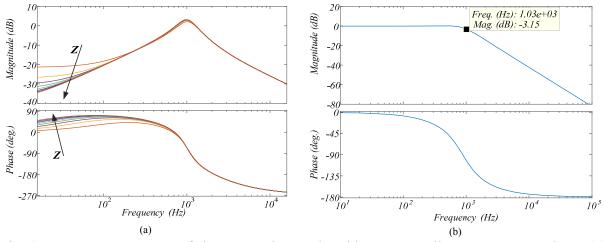

The effect of decoupling the controlled states is clearly shown by the frequency response analysis of the system with a P controller as current regulator. The frequency response as a function of the load impedance is shown in Fig. 3(a). In this case, the range of variation is from rated to no-load condition, with arrows indicating increase in the load impedance. The system has a strong load dependency with low gain at low frequencies. For this reason, an integral term is needed to achieve zero steady-state error if voltage decoupling is not performed.

On the other hand, if the controlled states are decoupled, the system has much higher damping and less overshoot for the same bandwidth, as shown in the frequency response of Fig. 3(b). Moreover, the inner current loop becomes independent of the load. The magnitude at low frequencies is almost 0 dB, thus allowing the use of a P controller in the current loop when voltage decoupling is performed.

Fig. 3. Frequency response of the current loop only with a P controller as current regulator: (a) without decoupling; (b) with decoupling

The design of the voltage regulator is based on the procedure illustrated in [9]. According to the open loop trajectories on the Nyquist diagram it is possible to determine the leading angles in (1) at each harmonic frequency. The parameters for the voltage loop are shown in Table III.

#### **Experimental Results**

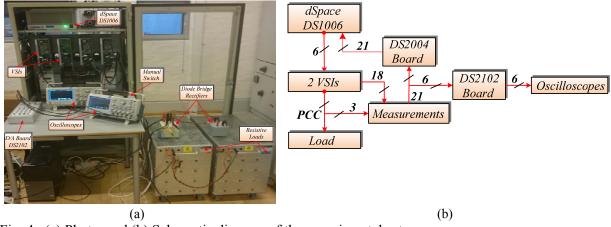

The theoretical analysis is validated through experimental results. For this purpose, a low scale test bed made up of two Danfoss power converters of 2.2 kW each has been built. The control platform is based on dSPACE DS1006. An Analog-to-Digital DS2004 board is used to digitalize the analog signals sensed via LEM current and voltage transducers. A Digital-to-Analog conversion 16-bit high resolution board DS2102 has been used to record the data on two oscilloscopes.

The photo and schematic diagram of the experimental setup are shown in Fig. 4(a) and Fig. 4(b), respectively. The PWM signals for each VSI are sent from dSPACE DS1006 platform, based on the implemented control law. Three-phase inductor currents, capacitor voltage and output current are measured for each VSI, as well as the voltage at the Point of Common Coupling (PCC). The measured variables are sent to the A/D board DS2004. Only the reference, measured and error values of capacitor voltage in  $\alpha$ -axis from each VSI are sent to the D/A board DS2102 and then to the oscilloscopes.

Fig. 4. (a) Photo and (b) Schematic diagram of the experimental setup

All the following experimental results are performed using a P controller as current regulator and with state feedback cross-coupling decoupling of the capacitor voltage. Resonant regulators tuned at specific harmonic orders are used in the outer voltage loop. The two parallel power converters are droop-controlled and operate in voltage control mode. Two diode bridge rectifiers are used as nonlinear loads, with unbalance created opening one phase on the AC side of the loads. The system and control parameters are shown in Table I-V. In particular, the design of the virtual impedance and droop control parameters is based on [4] and [10].

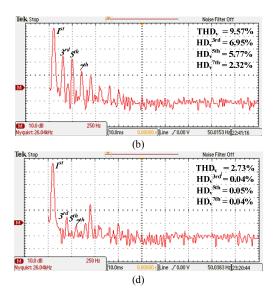

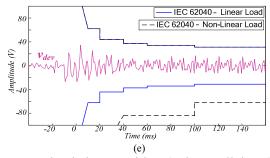

In Fig. 5(a), a 100% unbalanced nonlinear step load change (from open circuit to full rated load) is performed, without activating the harmonic compensators (HC) in the voltage loop for both power converters. As expected from the FFT analysis [see Fig. 5(b)], harmonics are present in the capacitor voltage, mainly a  $3^{rd}$  harmonic component due to unbalanced nonlinear load. Performing the step load change with HC activated at the  $3^{rd}$ ,  $5^{th}$  and  $7^{th}$  harmonic orders [see Fig. 5(c)] reduces significantly the THDv, without interfering with the transient response. Still the system reaches steady-state in less than one cycle and a half after the load step change. Since the bandwidth of the voltage loop has been set to 100 Hz, a  $3^{rd}$  HC is needed. The transient response complies with the standards imposed by IEC 62040 for UPS systems, as shown in Fig. 5(e). Similar results are obtained for the other power converter, referred to as DG<sub>2</sub>.

Fig. 5. Unbalanced nonlinear step load change with DGs in parallel: DG<sub>1</sub> with output impedance of  $L_1 = 1.8$  mH; DG<sub>2</sub> with output impedance of  $L_2 = 1.8$  mH - (a) Transient response without HC, reference (200 V/div), real (200 V/div) and capacitor voltage error (50 V/div) ( $\alpha$ -axis); (b) FFT of the capacitor voltage (250 Hz/div); (c) Transient response with 3<sup>rd</sup>, 5<sup>th</sup>, 7<sup>th</sup> HC, reference (200 V/div) and capacitor voltage error (50 V/div) ( $\alpha$ -axis); (d) FFT of the capacitor voltage (250 Hz/div); (e) 100% Step load change, Dynamic characteristics according to IEC 62040 standard for linear and nonlinear loads

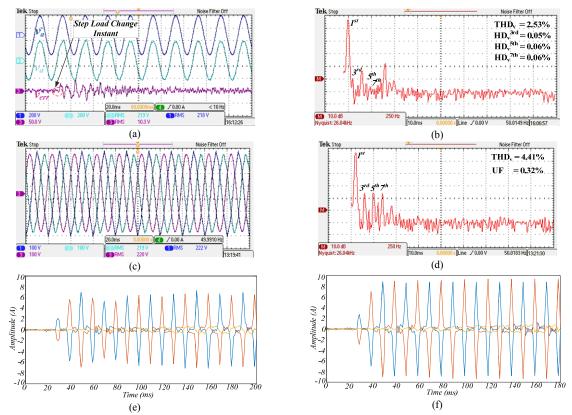

Unbalance between the two lines supplying the loads is created doubling the line impedance at the output of DG<sub>1</sub>. Again, a 100% unbalanced nonlinear step load change is performed [see Fig. 6(a)]. Both power converters have the HC at  $3^{rd}$ ,  $5^{th}$  and  $7^{th}$  harmonic activated. The steady-state voltage at PCC between the two VSIs is shown in Fig. 6(b), which results in an Unbalance Factor (UF) of 0.32%, in compliance with the standards which set the upper limit to 2%. However, the load is not equally shared between the DGs as can be seen comparing Fig. 6(e) and Fig. 6(f). These last data have been plotted in MATLAB after have been recorded in dSPACE ControlDesk scopes.

Fig. 6. Unbalanced nonlinear step load change with DGs in parallel:  $DG_1$  with output impedance of  $L_1 = 3.6$  mH;  $DG_2$  with output impedance of  $L_2 = 1.8$  mH; virtual impedance not activated - (a) Transient response, reference (200 V/div), real (200 V/div) and capacitor voltage error (50 V/div) ( $\alpha$ -axis); (b) FFT of the capacitor voltage (250 Hz/div); (c) Voltage at PCC; (d) FFT of voltage at PCC (250 Hz/div); (e) Transient conditions, output current from  $DG_1$ ; (f) Transient conditions, output current from  $DG_2$

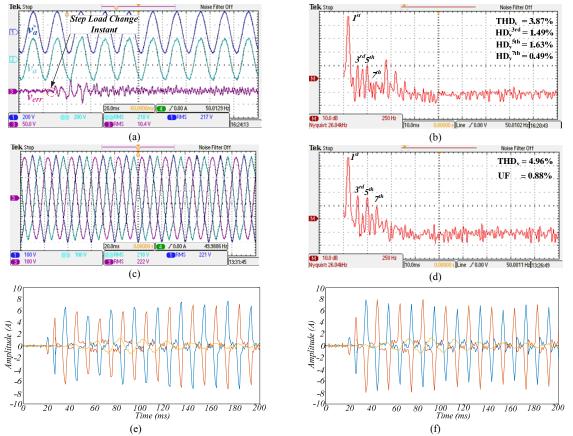

When the Virtual Impedance outer loop is activated, the current sharing improves noticeably [see Fig. 7(e) and Fig. 7(f)]. This improvement is achieved by decrease/increase of  $DG_2/DG_1$  current components. In addition, fundamental positive sequence component of load current is still shared, properly. However, it can be seen that the current sharing improvement is achieved at the expense of increasing all voltage distortions: slight increase in THD and the UF at PCC [see Fig. 7(c) and Fig. 7(d)] as well as DGs terminal [see Fig. 7(a) and Fig. 7(b)].

Fig. 7. Unbalanced nonlinear step load change with DGs in parallel:  $DG_1$  with output impedance of  $L_1 = 3.6$  mH;  $DG_2$  with output impedance of  $L_2 = 1.8$  mH; virtual impedance activated - (a) Transient response, reference (200 V/div), real (200 V/div) and capacitor voltage error (50 V/div) ( $\alpha$ -axis); (b) FFT of the capacitor voltage (250 Hz/div); (c) Voltage at PCC; (d) FFT of voltage at PCC (250 Hz/div); (e) Transient conditions, output current from  $DG_1$ ; (f) Transient conditions, output current from  $DG_2$

#### Conclusion

Design and experimental validation of control for inverter-based microgrids have been addressed. It is demonstrated that a significant increase in performance for both steady state and transient conditions can be achieved by proper design of inner voltage and current control loops of DGs interface converters. The system is much more damped when the controlled states are decoupled, allowing the use of a proportional controller as current regulator.

## References

- [1] IEEE Guide for Design, Operation, and Integration of Distributed Resource Island Systems with Electric Power Systems, IEEE Standard 1547.4-2011, 2011.

- [2] J. M. Guerrero, P. C. Loh, M. Chandorkar, and T.-L. Lee, "Advanced control architectures for intelligent MicroGrids, Part I: Decentralized and Hierarchical Control," *IEEE Trans. Ind. Electron.*, vol. 60, pp. 1254-1262, Apr. 2013.

- [3] M. M. Hashempour, M. Savaghebi, J. C. Vasquez, and J. M. Guerrero, "A control architecture to coordinate distributed generators and active power filters coexisting in a microgrid," *IEEE Trans. Smart Grid*, Early Access, 2015.

- [4] M. Savaghebi, A. Jalilian, J. C. Vasquez, and J. M. Guerrero, "Secondary control for voltage quality enhancement in microgrids,", *IEEE Trans. Smart Grid*, vol. 3, no. 4, pp. 1893-1902, Dec. 2012.

- [5] J. He, Y. W. Li, and M. S. Munir, "A flexible harmonic control approach through voltage controlled DGgrid interfacing converters," *IEEE Trans. Ind. Electron.*, vol. 59, no. 1, pp. 444-455, Jan. 2012.

- [6] J. M. Guerrero, J. C. Vasquez, J. Matas, L. G. de Vicuña, and M. Castilla, "Hierarchical control of droopcontrolled AC and DC microgrids—a general approach toward standardization," *IEEE Trans. Ind. Electron.*, vol. 58, no. 1, pp. 158-172, Jan. 2011.

- [7] J. M. Guerrero, J. Matas, L. G. de Vicuña, M. Castilla, and J. Miret, "Decentralized control for parallel operation of distributed generation inverters using resistive output impedance," *IEEE Trans. Ind. Electron.*, vol. 54, no. 2, pp. 994-1004, Apr. 2007.

- [8] D. De, and V. Ramanarayanan, "Decentralized parallel operation of inverters sharing unbalanced and nonlinear loads," *IEEE Trans. Power Electron.*, vol. 25, no. 12, pp. 3015-3025, Dec. 2010.

- [9] F. de Bosio, L. A. de S. Ribeiro, F. D. Freijedo, M. Pastorelli, and J. M. Guerrero, "Effect of state feedback coupling and system delays on the transient performance of stand-alone VSI with LC output filter", *IEEE Trans. Ind. Electron.*, Early Access, 2016.

- [10]J. C. Vasquez, J. M. Guerrero, M. Savaghebi, J. Eloy-Garcia, and R. Teodorescu, "Modeling, analysis, and design of stationary-reference-frame droop-controlled parallel three-phase voltage source inverters," *IEEE Trans. Ind. Electron.*, vol. 60, no. 4, pp. 1271-1280, Apr. 2013.

- [11]F. de Bosio, L. A. de S. Ribeiro, M. S. Lima, F. D. Freijedo, J. M. Guerrero, and M. Pastorelli, "Current control loop design and analysis based on resonant regulators for microgrid applications," in *IEEE Conf. Rec. IECON*, Yokohama, Japan, Nov. 2015, pp. 5322 - 5327.