Aalborg Universitet

### PhD thesis: Modulation and Circulating Current Suppression for Parallel Interleaved Voltage Source Converters

Gohil, Ghanshyamsinh Vijaysinh

Published in:

Modulation and Circulating Current Suppression for Parallel Interleaved Voltage Source Converters

Publication date: 2016

**Document Version** Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Gohil, G. V. (2016). PhD thesis: Modulation and Circulating Current Suppression for Parallel Interleaved Voltage Source Converters. In Modulation and Circulating Current Suppression for Parallel Interleaved Voltage Source Converters

**General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- ? Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

? You may not further distribute the material or use it for any profit-making activity or commercial gain

? You may freely distribute the URL identifying the publication in the public portal ?

Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

## Modulation and Circulating Current Suppression for Parallel Interleaved Voltage Source Converters

Ph.D. Dissertation Ghanshyamsinh Gohil

Dissertation submitted to Faculty of Engineering and Science at Aalborg University in partial fulfillment of the requirements for the degree of

> Doctor of Philosophy in Electrical Engineering

February 17, 2016

| Thesis submitted:         | February 17, 2016                             |

|---------------------------|-----------------------------------------------|

| PhD Supervisor:           | Prof. Remus Teodorescu                        |

|                           | Aalborg University                            |

| Assistant PhD Supervisor: | Assoc. Prof. Tamas Kerekes                    |

|                           | Aalborg University                            |

| PhD Committee:            | Prof. Paolo Mattavelli, University of Padova  |

|                           | Prof. Maryam Saeedifard, Georgia Institute of |

|                           | Technology                                    |

|                           | Prof. Francesco Iannuzzo, Aalborg University  |

| PhD Series:               | Faculty of Engineering and Science, Aalborg   |

|                           | University                                    |

ISSN: 2246-1248 ISBN: 978-87-7112-511-5

Published by: Aalborg University Press Skjernvej 4A, 2nd floor DK 9220 Aalborg Ø Phone: +45 99407140 aauf@forlag.aau.dk forlag.aau.dk

© Copyright: Ghanshyamsinh Gohil

Printed in Denmark by Rosendahls, 2016

### **Copyright Statement**

This present report combined with the scientific papers which are listed in §1.3.2 and §1.3.3 has been submitted for assessment in partial fulfilment of the PhD degree. The scientific papers are not included in this version due to copyright issues. Detailed publication information is provided in §1.3.2 and §1.3.3 and the interested reader is referred to the original published papers. As part of the assessment, co-author statements have been made available to the assessment committee and are also available at the Faculty of Engineering and Science, Aalborg University. Dedicated to my mother Pushpa for her endless love and encouragement and to my wife Vandana and son Meghdattsinh for their sacrifice and reminding me that there is life outside the office

## Curriculum Vitae

## Ghanshyamsinh Gohil

The author received Bachelor's degree in Electrical Engineering from the South Gujarat University and received Master of technology degree in electrical engineering with specialization in power electronics and power systems from the Indian Institute of Technology-Bombay, Mumbai, in 2011.

Since May 2013, He has been working towards the Ph.D. degree at the Department of Energy Technology, Aalborg University, Denmark. Prior to joining the Ph.D. studies, he was employed at Siemens Technology and Services, where he was involved in the research activities in the hybrid micro-grid. He also worked on the power quality issues and photo-voltaic converters during his employment at the Crompton Greaves Global R&D Center.

His research interests include parallel operation of voltage source converters, pulsewidth modulation techniques, packaging and the novel topologies for the wide band-gap semiconductor devices, medium voltage dc-dc converters, and energy internet.

Curriculum Vitae

## Abstract

The two-level Voltage Source Converters (VSCs) are often connected in parallel to increase the current handling capability. In such systems, the multi-level voltage waveforms can be obtained by interleaving the carrier signals of the parallel connected two-level VSCs. The multi-level voltage waveform facilitates reduction in both the switching frequency and the size of the harmonic filter components. This leads to the improvement in both the system efficiency and power density. However, when VSCs are connected in parallel and share the same dc-link, the circulating current flows through the closed path due to the control asymmetry and the impedance mismatch. When the carriers are interleaved, the pole voltages (switched output voltage of the VSC leg) of the interleaved parallel legs are phase shifted and it creates instantaneous potential difference across the closed path, formed due to the parallel connection. This instantaneous potential difference further aggravates the circulating current, which results in increased losses and unnecessary oversizing of the components present in the circulating current path. Therefore, the circulating current should be suppressed to realize the full potential of the carrier interleaving.

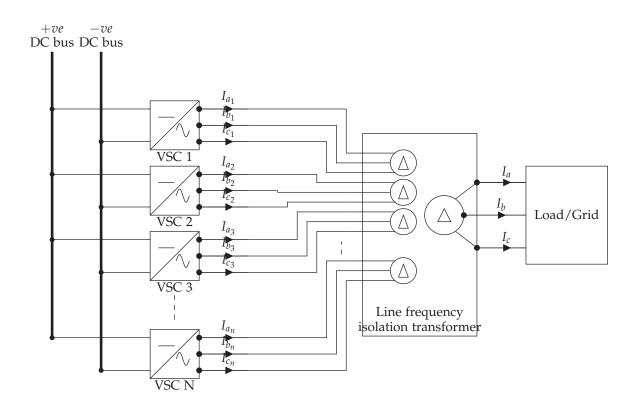

The formation of the circulating current path can be avoided by using the line frequency isolation transformer. However, it increases the overall size of the system and should be avoided. The use of the Common-Mode (CM) inductor in series with the line filter inductor for each of the VSCs is proposed in literature. Another approach proposes the use of the Coupled Inductor (CI) to suppress the circulating current by providing magnetic coupling between the parallel interleaved legs of the corresponding phases. Although the interleaved carrier signals lead to the reduction in the value of the harmonic filter components, additional filter components (CIs) are often required to suppress the circulating current. The volume of these inductive components can be reduced by integrating both of these functionalities into a single magnetic component. Different integrated inductor solutions are presented in this thesis with an objective to reduce the overall size of the magnetic component, so that the power density can be further improved or for the given filter size, the switching frequency can be further reduced. The advantages achieved by

the magnetic integration is highlighted by comparing the volume and losses with that of the separate inductor case.

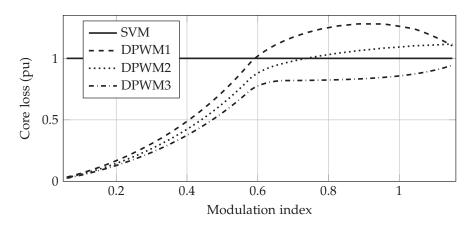

The modulation scheme has significant impact on the core losses in the CI, the harmonic performance, and the switching losses. These performance parameters for the conventional Pulse Width Modulation (PWM) schemes are evaluated and compared. The PWM schemes for the size reduction of the CM and core losses reduction in the CI is also proposed. For the multi-level converter, the Phase Disposition (PD) PWM scheme results in optimal harmonic performance. However it can not be applied to the parallel VSCs in its original form as it may lead to the saturation of the CI. A modified PD modulator is proposed, which ensures flux balancing in the CI, while ensuring the use of the nearest three vectors to synthesize the reference space voltage vector in each sampling interval.

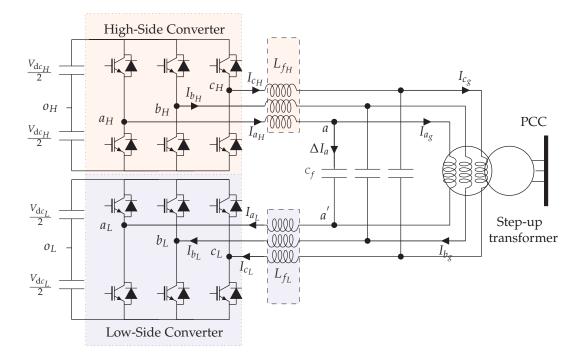

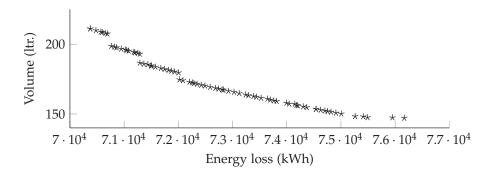

A 3.3 kV medium voltage converter using the two-level VSCs, configured in open-end transformer topology has been studied. An integrated inductor for this topology is also proposed. The multi-objective design optimization has been performed, where the energy loss and the volume are optimized. A non-inferior (Pareto optimal) solution is obtained. The optimization process takes into account the yearly load profile and it is used to minimize the energy loss, rather than minimizing the losses at a specific operating point.

In a dual converter fed open-end transformer topology, each of the VSCs has to process the rated current. In many high power applications, single two-level VSC may not be able to handle the rated current. To overcome this problem, parallel connection of the two-level VSCs for the open-end transformer topology is proposed. Using this topology, both the voltage and the current handling capability of the converter can be increased. The carrier signals of the parallel VSCs are interleaved to improve the harmonic performance. The integrated inductor for suppressing the circulating current between the parallel VSCs and for improving the line current quality is also proposed.

## Resumé

To niveau spændingskilde konverterne (VSC) er ofte forbundet I parallel for at øge strømbelastningsevnen. I sådanne systemer kan flere-niveau spændingskurve opnås ved at indflette bærersignalet af de parallelt forbundne toniveau spændingskilde konvertere. Flere-niveau spændingskurven muliggør reduktion af både switchfrekvensen og størrelsen af de harmoniske filter komponenter. Det leder til forbedring af både systemeffektiviteten og effektdensiteten. For parallelkoblede spændingskildekonvertere, der deler den samme mellemkreds, løber der cirkulerende strøm gennem den lukkede bane pga. kontrol asymmetri og impedans mismatch. Når bæresignalet er indflettet, er polspændingerne (skiftede udgangsspænding af VSCens ben) af de indflettede parallelle ben faseforskudte, hvilket skaber øjeblikkelig potentialeforskel over den lukkede bane dannet af parallelforbindelsen. Denne øjeblikkelige potentiale forskel forværrer den cirkulerende strøm yderligere. Derfor bør den cirkulerende strøm blive undertrykket for at udnytte det fulde potentiale af at indflette bærersignalet.

Dannelsen af den cirkulerende strømbane kan undgås ved hjælp af en grundtone isolations transformer. Men det øger den samlede størrelse af systemet og bør undgås. Brug af en Common Mode (CM) spole is serie med net filter spolen for hver VSC er forslået i litteraturen. En anden metode foreslår anvendelse af en koblet spole (CI) for at undertrykke den cirkulerende strøm, ved at skabe en magnetisk kobling mellem de parallelle indflettede ben af de tilsvarende faser. Selvom de indflettede bæresignaler føre til en reduktion i værdien af de harmoniske filter komponenter, er yderligere filter komponenter (CIer) ofte nødvendig for at undertrykke den cirkulerende strøm. Volumen af disse induktive komponenter kan reduceres ved at integrere begge disse funktionaliteter i en enkelt magnetisk komponent. Forskellige integrerede spole løsninger præsenteres i denne afhandling med en målsætning om at reducere den samlede størrelse af den magnetiske komponent, så effekttætheden kan forbedres yderligere, eller for den givne filter størrelse, kan switchfrekvensen reduceres yderligere. De fordele, der opnås ved den magnetiske integration er fremhævet ved at sammenligne volumen og tabet med det separate spole tilfælde.

Modulationsmetode har betydelig indvirkning på kernetabet i den CI, den harmoniske ydeevne, og switchtabene. Disse resultatparametre for de konventionelle pulsbreddemodulation (PWM) metoder evalueres og sammenlignes. Der foreslås også PWM metoder til størrelsesreduktion af CM strøm og reduktion af kernetab i den CI. For Multiniveaukonverter resulterer fase disposition (PD) PWM metoder i optimal harmonisk ydelse. Dog kan det ikke anvendes på de parallelle VSC'er i sin oprindelige form, da det kan føre til mætning af CI. Der foreslås en modificeret PD modulation, som sikrer fluxafbalancering i CI, samtidig med at brugen af de nærmeste tre vektorer til at syntetisere reference spænding rumvektoren i hvert samplingsinterval.

En 3,3 kV mellemspændingkonverter er, ved hjælp af de to- niveau VSC'er konfigureret i åben ende transformer topologi, blevet undersøgt. Der foreslås også en integreret spole for denne topologi. Mmult-iobjektiv design optimering er blevet udført, hvor energitabet og volumen er optimeret. En ikke-inferiør (Pareto optimal) løsning er opnået. Optimeringsproces tager hensyn til den årlige belastningsprofil, og den bruges til at minimere energitabet, snarere end at minimere tabene i et bestemt arbejdspunkt. I en dobbelt konverter fødet åben ende transformer topologi, skal hver behandle hver af VSC'erne behandle mærkestrømmen. I mange højeffekt applikationer kan en enkelt to-niveau VSC ikke være i stand til at håndtere mærkestrømmen. For at overvinde dette problem, foreslås der parallelkobling af to-niveau VSC'erne for åben ende transformer topologi. Ved hjælp af denne topologi, kan både spænding- og strømhåndteringskapaciteten af konverteren øges. Bæresignalerne af de parallelle VSC'er er indflettet for at forbedre den harmoniske ydeevne. Den integrerede spole er også foreslået for at undertrykke den cirkulerende strøm mellem de parallelle VSC'er og for at forbedre netstrømskvaliteten.

| Cι | urricu    | <b>lum V</b> i | itae                                  |                                           | v   |  |  |  |

|----|-----------|----------------|---------------------------------------|-------------------------------------------|-----|--|--|--|

| Al | Vii       |                |                                       |                                           |     |  |  |  |

| Re | kesumé ix |                |                                       |                                           |     |  |  |  |

| Pr | eface     |                |                                       |                                           | xxi |  |  |  |

| Ι  | Su        | mmar           | y                                     |                                           | 1   |  |  |  |

| Su | ımma      | iry            |                                       |                                           | 3   |  |  |  |

|    | 1         | Introd         | uction .                              |                                           | 3   |  |  |  |

|    |           | 1.1            | Backgro                               | und and Motivation                        | 3   |  |  |  |

|    |           |                | 1.1.1                                 | Applications                              | 3   |  |  |  |

|    |           |                | 1.1.2                                 | Overview of the Parallel Interleaved VSCs | 4   |  |  |  |

|    |           | 1.2            | Research                              | h Objectives and Contributions            | 14  |  |  |  |

|    |           |                | 1.2.1                                 | Research Challenges and Objectives        | 14  |  |  |  |

|    |           |                | 1.2.2                                 | Contributions                             | 15  |  |  |  |

|    |           | 1.3            | Thesis C                              | Overview                                  | 17  |  |  |  |

|    |           |                | 1.3.1                                 | Summary Overview                          | 17  |  |  |  |

|    |           |                | 1.3.2                                 | Appended Publications                     | 17  |  |  |  |

|    | _         |                | 1.3.3                                 | Other Publications                        | 19  |  |  |  |

|    | 2         |                |                                       | r Design                                  | 20  |  |  |  |

|    |           | 2.1            |                                       | the Carrier Interleaving                  | 20  |  |  |  |

|    |           |                | 2.1.1                                 | Design constraint                         | 21  |  |  |  |

|    |           |                | 2.1.2                                 | Filter Design Procedure                   | 23  |  |  |  |

|    |           |                | 2.1.3                                 | Comparative Evaluation                    | 24  |  |  |  |

|    |           | 2.2            | 0                                     | der Harmonic Filters                      | 25  |  |  |  |

|    |           |                | 2.2.1                                 | LC Trap Filter                            | 26  |  |  |  |

|    | 2         |                | 2.2.2                                 | LCL Filter with LC Trap Branch            | 28  |  |  |  |

|    | 3         | wodu           | dulation of Parallel Interleaved VSCs |                                           |     |  |  |  |

|   |       | 3.1      | Compar      | ative Evaluation of the Conventional Schemes .   | 29       |

|---|-------|----------|-------------|--------------------------------------------------|----------|

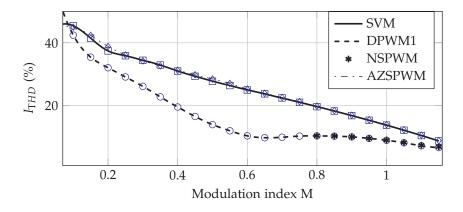

|   |       |          | 3.1.1       | Harmonic Performance                             | 29       |

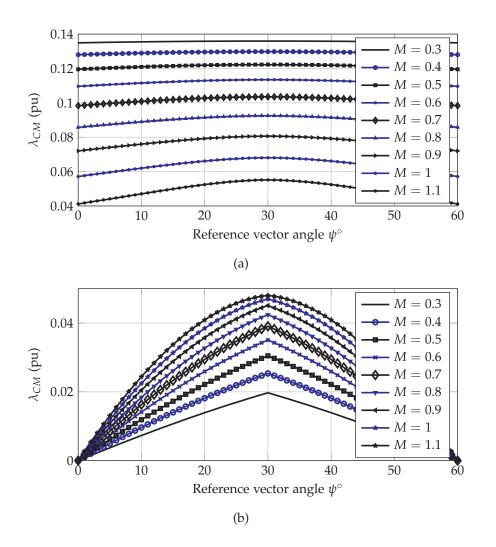

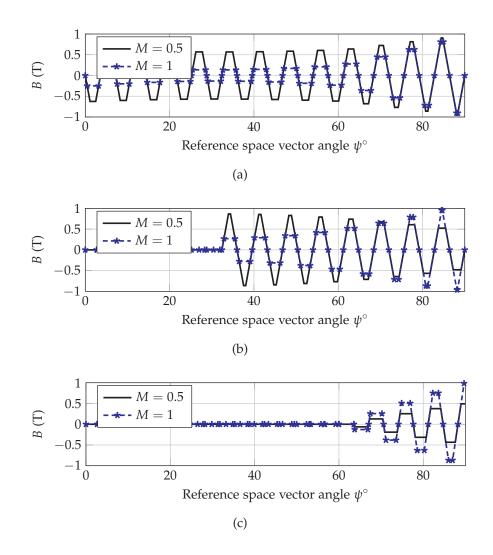

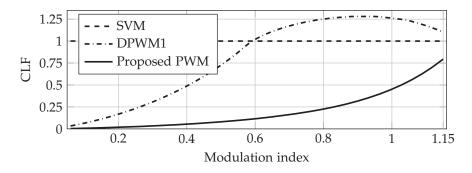

|   |       |          | 3.1.2       | Core Losses of the Coupled Inductor              | 31       |

|   |       |          | 3.1.3       | Switching losses                                 | 33       |

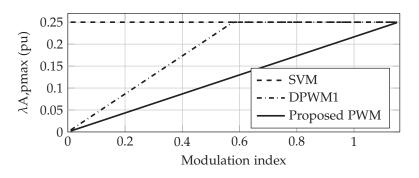

|   |       | 3.2      | Size Red    | uction of the Circulating Current Filter         | 34       |

|   |       |          | 3.2.1       | Coupled Inductor                                 | 34       |

|   |       |          | 3.2.2       | Common Mode Inductor                             | 37       |

|   |       |          | 3.2.3       | Harmonic Performance and Switching Losses .      | 38       |

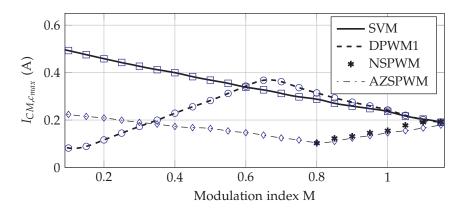

|   |       |          | 3.2.4       | Reduced CM Voltage PWM Schemes                   | 39       |

|   |       | 3.3      | Nearest     | Three Vector Modulation                          | 43       |

|   | 4     | Magne    | etic Integi | ration                                           | 47       |

|   |       | 4.1      | Integrate   | ed Inductor                                      | 47       |

|   |       | 4.2      | Integrate   | ed Inductor for Whiffletree Configuration        | 50       |

|   |       | 4.3      | Integrate   | ed Inductor for Medium Voltage Converters        | 56       |

|   |       |          | 4.3.1       | Design Optimization                              | 57       |

|   |       |          | 4.3.2       | Volumetric comparison                            | 59       |

|   |       | 4.4      |             | Voltage Converters with Parallel VSCs            | 59       |

|   |       |          | 4.4.1       | Magnetic Structure of Integrated Inductor        | 60       |

|   | 5     |          |             | d Outlook                                        | 65       |

|   |       | 5.1      |             | ons                                              | 65       |

|   |       |          | 5.1.1       | Harmonic Filter Design                           | 65       |

|   |       |          | 5.1.2       | Modulation Scheme                                | 66       |

|   |       |          | 5.1.3       | Integrated Inductor                              | 68       |

|   |       | 5.2      | Outlook     |                                                  | 69       |

|   |       |          | 5.2.1       | Core Loss Modeling of the Integrated Inductor    | 69       |

|   |       |          | 5.2.2       | Modulation                                       | 69<br>70 |

|   | Defe  |          | 5.2.3       | Advance Control of the Circulating Current       | 70       |

|   | Kefe  | erences  | • • • • •   |                                                  | 70       |

|   |       |          |             |                                                  |          |

| Π | Aı    | opend    | ed Publ     | ications                                         | 79       |

|   | 1     | ſ        |             |                                                  |          |

| Α | Des   | ign of t | he Trap I   | Filter for the High Power Converters with Paral- | ,        |

|   | lel I |          | ved VSCs    |                                                  | 81       |

|   | 1     |          |             |                                                  | 83       |

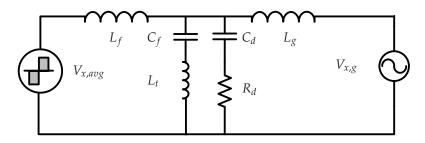

|   | 2     | Systen   | n Descrip   | tion                                             | 84       |

|   |       | 2.1      |             | ulating Current                                  | 86       |

|   |       | 2.2      |             | l Current                                        | 88       |

|   | -     | 2.3      |             | ion Scheme and the Average Pole Voltage          | 88       |

|   | 3     | 0        |             | ints                                             | 89       |

|   |       | 3.1      |             | n the Injected Harmonics                         | 89       |

|   |       | 3.2      | Peak Sw     | itch Current                                     | 89       |

|   |      | 3.3      | Active and Reactive Power Consumption of the Shunt            |     |

|---|------|----------|---------------------------------------------------------------|-----|

|   |      |          | Branch                                                        | 90  |

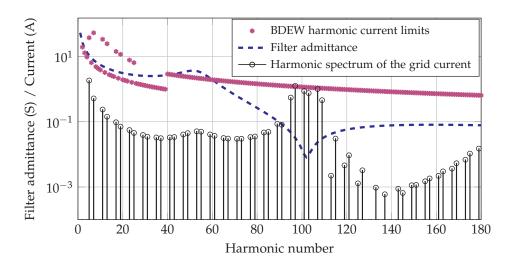

|   | 4    | Filter   | Design                                                        | 91  |

|   |      | 4.1      | Trap Filter                                                   | 92  |

|   |      | 4.2      | Design                                                        | 93  |

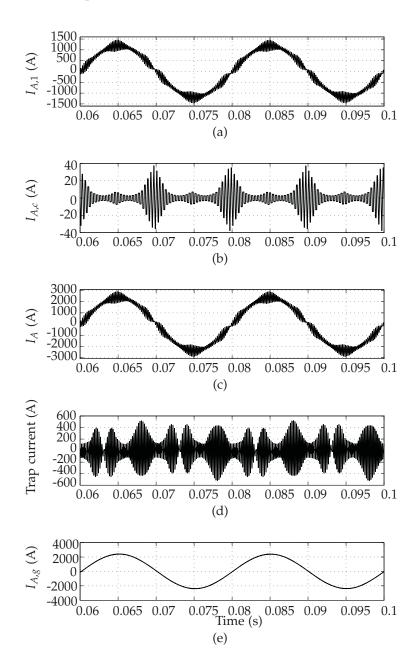

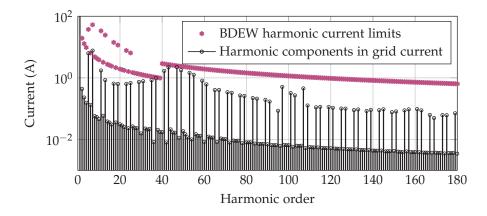

|   | 5    | Simula   | ation and Experimental Results                                | 94  |

|   | 6    |          | usion                                                         | 96  |

|   | Refe | erences  |                                                               | 97  |

| В | Line | - Filter | Design of Parallel Interleaved VSCs for High Power Wind       | 1   |

| - |      |          | nversion Systems                                              | 101 |

|   | 1    |          | •                                                             | 103 |

|   | 2    |          | el Interleaved Voltage Source Converters                      |     |

|   | -    | 2.1      | Modulation Scheme                                             |     |

|   |      | 2.2      | Voltage Harmonic Distortion                                   |     |

|   |      | 2.3      | Switch Current Ripple                                         |     |

|   |      | 2.4      | Ripple Component of the Resultant Line Current $\Delta I_x$ . |     |

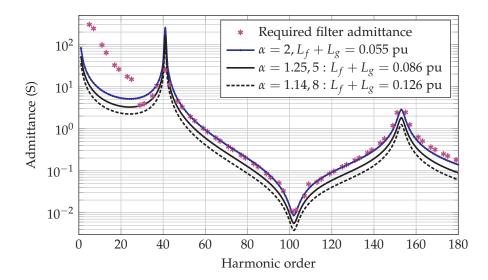

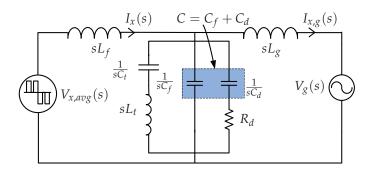

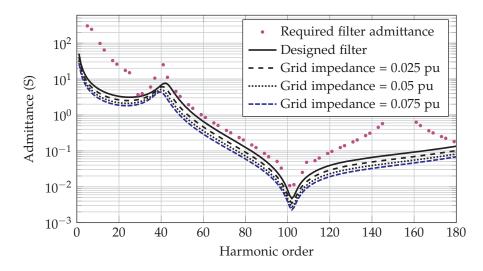

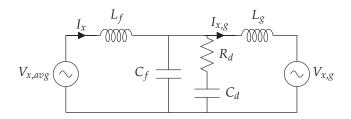

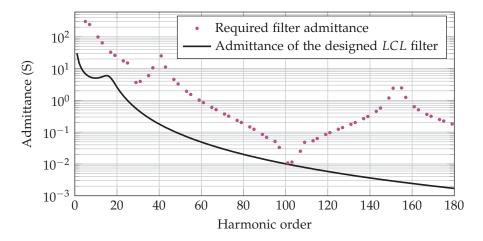

|   | 3    |          | Filter $\ldots$                                               |     |

|   | 4    |          | Design                                                        |     |

|   | _    | 4.1      | Design Constraints                                            |     |

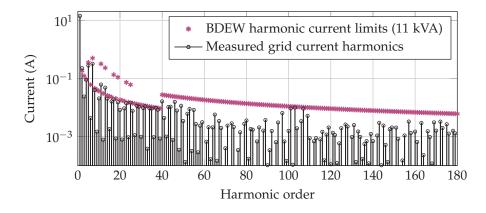

|   |      |          | 4.1.1 Harmonic Current Injection Limits                       |     |

|   |      |          | 4.1.2 Maximum Switch Current Ripple                           |     |

|   |      |          | 4.1.3 Reactive Power Consumption                              |     |

|   |      | 4.2      | Filter Design Procedure                                       |     |

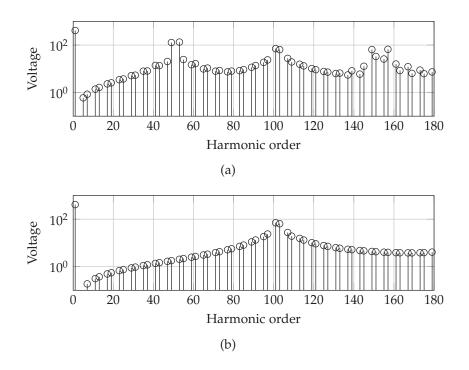

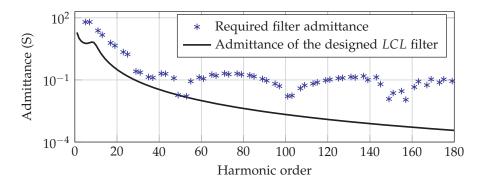

|   |      |          | 4.2.1 Virtual Voltage Harmonics                               |     |

|   |      |          | 4.2.2 Required Filter Admittance                              |     |

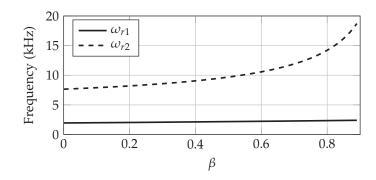

|   |      |          | 4.2.3 Selection of the <i>LC</i> Trap Branch Parameters       |     |

|   |      |          | 4.2.4 Selection of $L_f$ , $L_g$ and $C$                      |     |

|   |      |          | 4.2.5 Comparison with the <i>LCL</i> Filter                   |     |

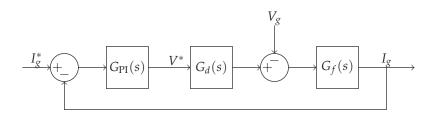

|   |      | 4.3      | Controller Design                                             |     |

|   | 5    | Simula   | ation and Experimental Results                                |     |

|   |      | 5.1      | Simulation Study                                              |     |

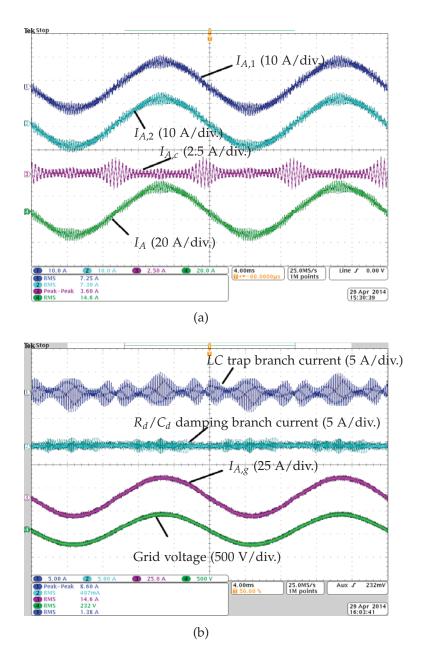

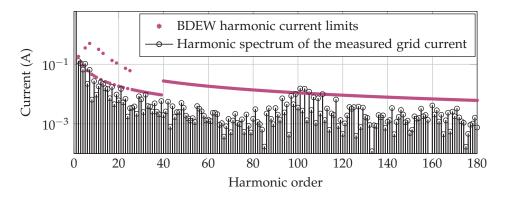

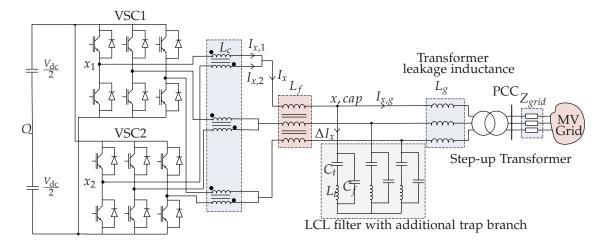

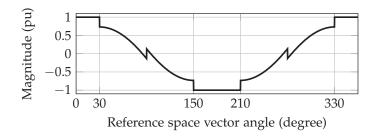

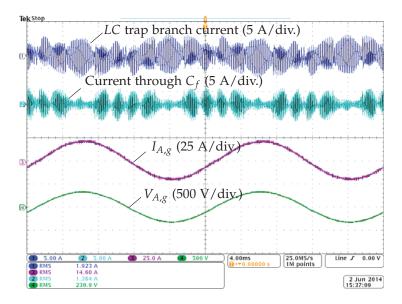

|   |      | 5.2      | Experimental Results                                          |     |

|   | 6    | Conclu   | -                                                             | 133 |

|   | А    |          | ndix                                                          | 134 |

|   | Refe |          |                                                               |     |

| С | Para | llel In  | terleaved VSCs: Influence of the PWM Scheme on the            | 2   |

|   | Des  | ign of t | the Coupled Inductor                                          | 139 |

|   | 1    | -        | luction                                                       | 141 |

|   | 2    |          | led Inductor                                                  | 143 |

|   | 3    | -        | width Modulation Schemes and their Effect on the Cou-         |     |

|   |      | pled I   | nductor Design                                                | 144 |

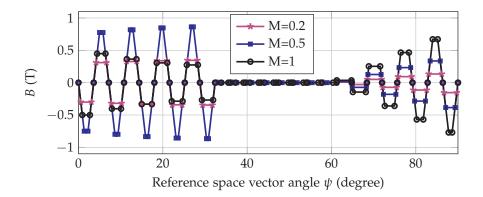

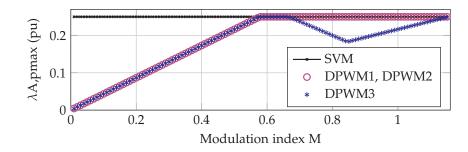

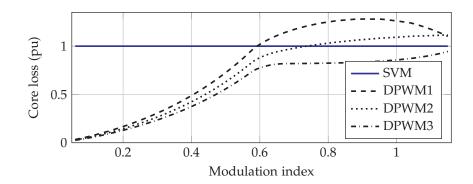

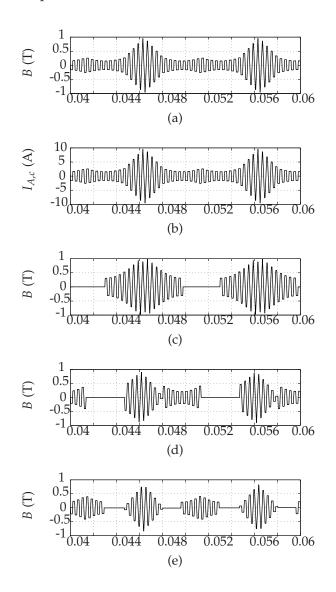

|   |      | -        |                                                               |     |

|   |              | 3.1     | The Center-aligned Space Vector Modulation              | 147 |

|---|--------------|---------|---------------------------------------------------------|-----|

|   |              | 3.2     | DPWM1: $60^{\circ}$ Clamp                               | 148 |

|   |              | 3.3     | DPWM2: 30°Lagging Clamp                                 | 149 |

|   |              | 3.4     | DPWM3: 30°Clamp                                         | 150 |

|   | 4            | Simula  | ation and Experimental Results                          | 152 |

|   | 5            | Conclu  | usion                                                   | 155 |

|   | Refe         | rences  |                                                         | 156 |

| D |              |         | Discontinuous PWM for Size Reduction of the Circulating |     |

|   |              |         | ter in Parallel Interleaved Converters                  | 159 |

|   | 1            |         | uction                                                  |     |

|   | 2            |         | el Interleaved VSCs                                     |     |

|   |              | 2.1     | Circulating Current                                     |     |

|   |              | 2.2     | Flux Linkage in Circulating Current Filter              |     |

|   |              |         | 2.2.1 Coupled Inductor                                  |     |

|   | _            |         | 2.2.2 Common-mode Inductor                              |     |

|   | 3            |         | ning Sequences and their Effect on the Flux Linkage     |     |

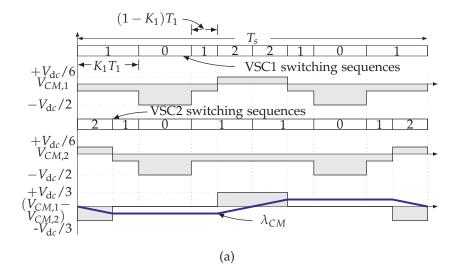

|   |              | 3.1     | Conventional Space Vector Modulation                    |     |

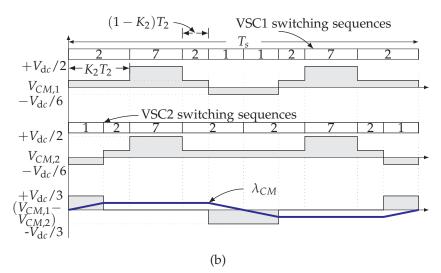

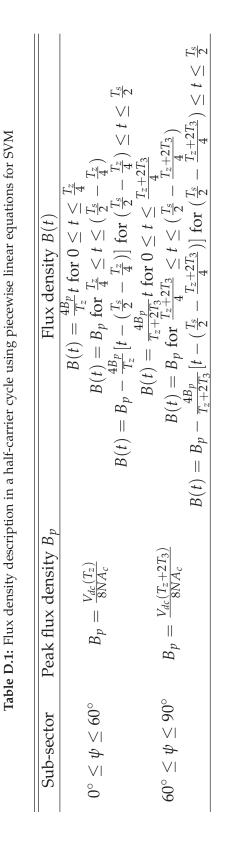

|   |              | 3.2     | 60°Clamped Discontinuous PWM (DPWM1)                    |     |

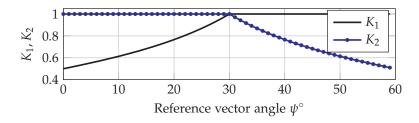

|   | 4            |         | ied DPWM for Circulating Current Reduction              | 169 |

|   |              | 4.1     | Effect of the Switching Sequences on the Circulating    |     |

|   |              |         | Current Filter Design                                   |     |

|   |              |         | 4.1.1 Coupled Inductor                                  |     |

|   |              | 4.0     | 4.1.2 Common-mode Inductor                              |     |

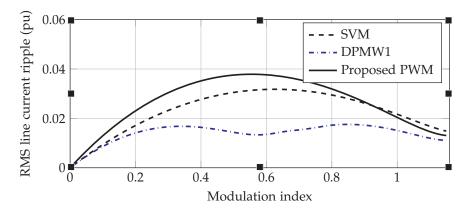

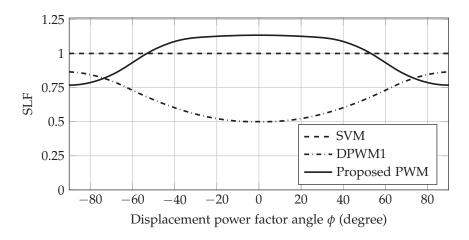

|   |              | 4.2     | Ripple Current Analysis                                 |     |

|   | -            | 4.3     | Semiconductor losses                                    |     |

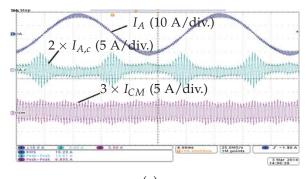

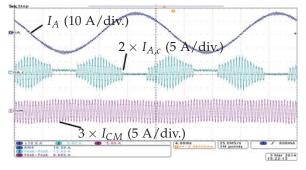

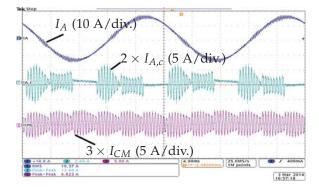

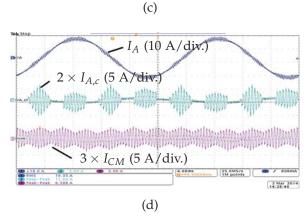

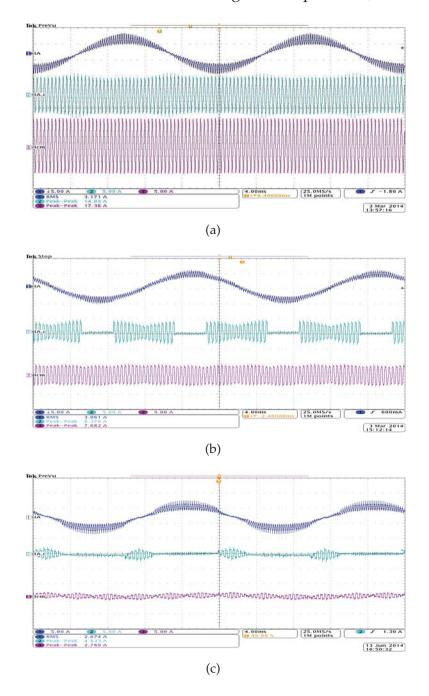

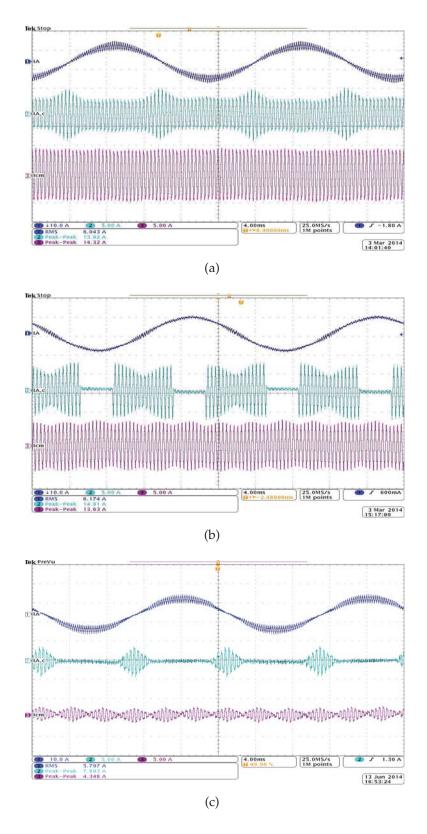

|   | 5            | -       | imental Results                                         |     |

|   | 6<br>D = ( = |         | usion                                                   |     |

|   | Kere         | erences |                                                         | 109 |

| Ε |              |         | cing Scheme for PD Modulated Three Parallel Interleaved | ł   |

|   |              |         | Coupled Inductor                                        | 195 |

|   | 1            |         | uction                                                  | 197 |

|   | 2            |         | odulation of the Parallel Interleaved VSCs and Associ-  |     |

|   |              |         | ssues                                                   |     |

|   |              | 2.1     | Operation of the Three Parallel Interleaved VSCs        |     |

|   |              | 2.2     | Coupled Inductor Saturation Under PD PWM                |     |

|   | 3            |         | lation Algorithm                                        |     |

|   |              | 3.1     | Modulation Under Steady-state Conditions                |     |

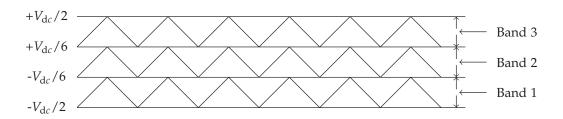

|   |              |         | 3.1.1 Modulation in Band 1                              |     |

|   |              |         | 3.1.2 Modulation in Band 2                              |     |

|   |              |         | 3.1.3 Modulation in Band 3                              |     |

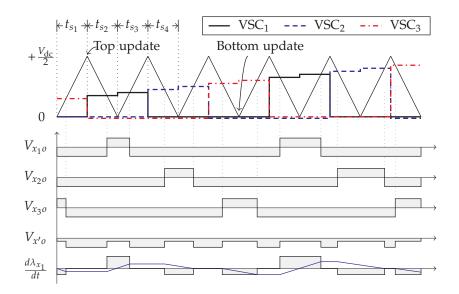

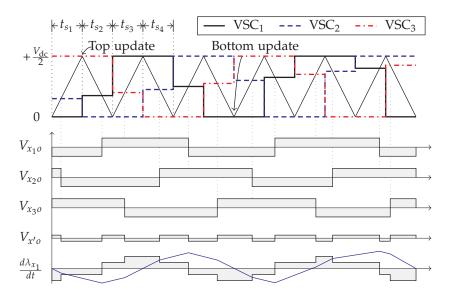

|   |              | 3.2     | Flux Balancing During Band Transition                   | 208 |

|   |      |          | 3.2.1     | Band Transition at Bottom Update               | 209  |

|---|------|----------|-----------|------------------------------------------------|------|

|   |      |          | 3.2.2     | Band Transition at Top Update                  |      |

|   |      | 3.3      | Transiti  | on in Other Cases                              |      |

|   | 4    | Imple    |           | n of the Proposed Modulation                   |      |

|   | 5    | -        |           | valuation and Results                          |      |

|   |      | 5.1      |           | ion Results                                    |      |

|   |      | 5.2      |           | are Results                                    |      |

|   | 6    | Concl    |           |                                                |      |

|   | Refe | erences  |           |                                                | 222  |

| F | An ] | Integra  | ted Indu  | ctor for Parallel Interleaved VSCs and PWM Sch | emes |

|   |      | -        | inimizat  |                                                | 225  |

|   | 1    | Introd   | luction . |                                                | 227  |

|   | 2    | Integr   | ated Ind  | uctor                                          | 229  |

|   |      | 2.1      | Simplifi  | ed Reluctance Model                            | 229  |

|   |      | 2.2      | Line Fil  | ter Inductance $L_f$                           | 231  |

|   |      | 2.3      | Circula   | ting Current Filter Inductance $L_c$           | 232  |

|   |      | 2.4      | Flux Liı  | nkage in the Common Legs                       | 233  |

|   | 3    | PWM      |           | ;                                              |      |

|   |      | 3.1      | Conven    | tional PWM Schemes                             | 234  |

|   |      | 3.2      | Reduce    | d CM Voltage PWM Schemes                       |      |

|   |      |          | 3.2.1     | Near State PWM                                 |      |

|   |      |          | 3.2.2     | AZSPWM Scheme                                  | 235  |

|   |      | 3.3      | Flux Liı  | nkage                                          |      |

|   |      |          | 3.3.1     | NSPWM                                          |      |

|   |      |          | 3.3.2     | AZSPWM                                         |      |

|   | 4    |          |           | the Line Current Quality                       |      |

|   |      | 4.1      |           | atterns                                        |      |

|   |      | 4.2      |           | nic Performance                                |      |

|   | 5    | -        | -         | grated Inductor                                |      |

|   |      | 5.1      | 0         | Procedure                                      |      |

|   |      |          | 5.1.1     | Value of the Line Filter Inductor              |      |

|   |      |          | 5.1.2     | Maximum Flux Density in Bridge Legs            |      |

|   |      |          | 5.1.3     | Maximum Flux Density in Common Legs            |      |

|   |      |          | 5.1.4     | Maximum Flux Density in Phase Legs             | 246  |

|   |      |          | 5.1.5     | Number of Turns and Cross-section Area of      |      |

|   |      |          | -         | the Cores                                      | 247  |

|   |      | 5.2      |           | rative Evaluation                              |      |

|   |      |          | 5.2.1     | Coupled Inductor                               |      |

|   |      |          | 5.2.2     | Line Filter Inductor                           |      |

|   |      | <b>.</b> | 5.2.3     | Comparison                                     |      |

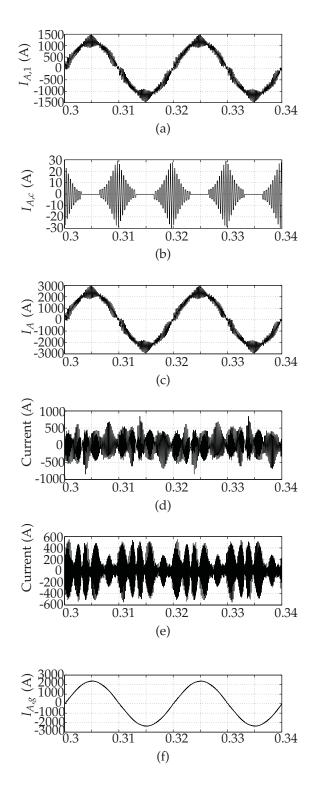

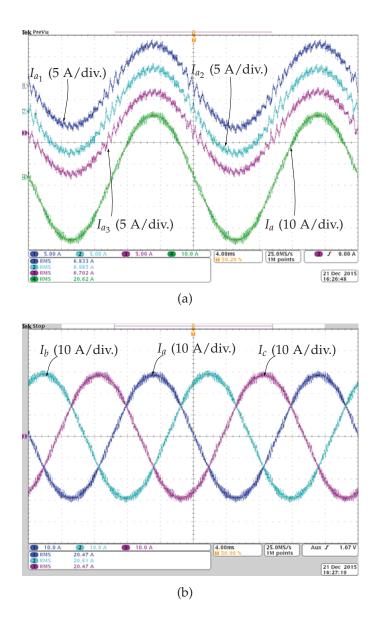

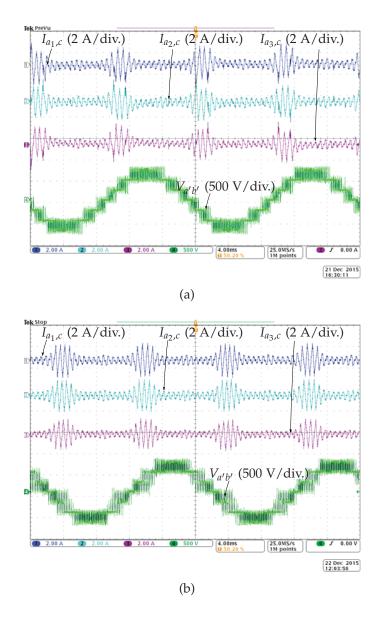

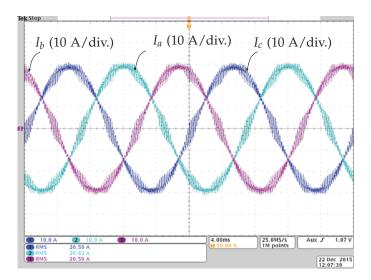

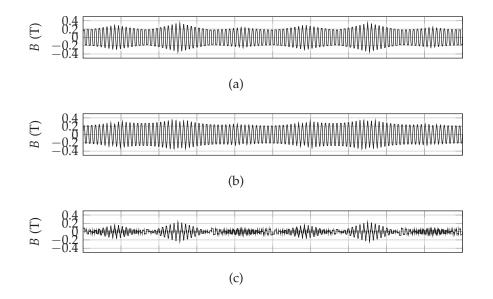

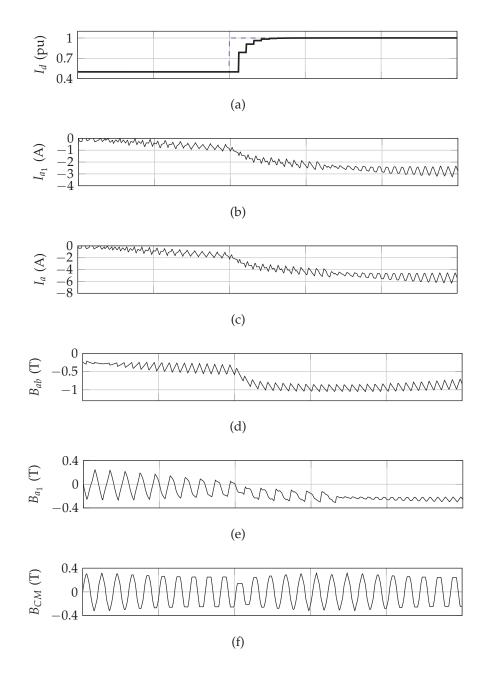

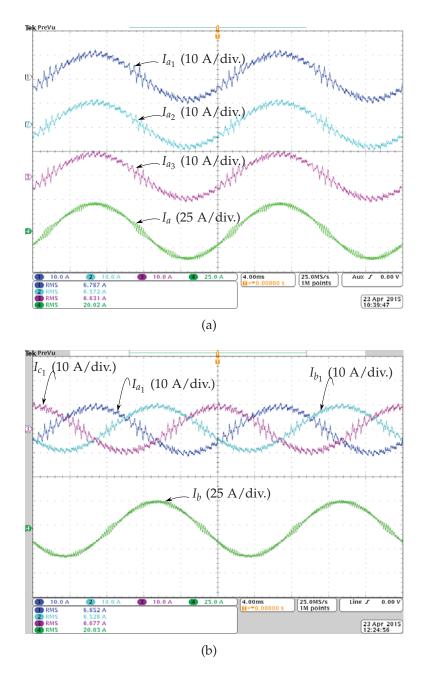

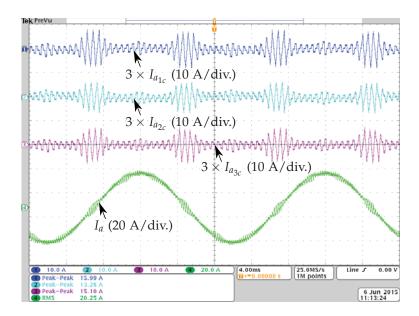

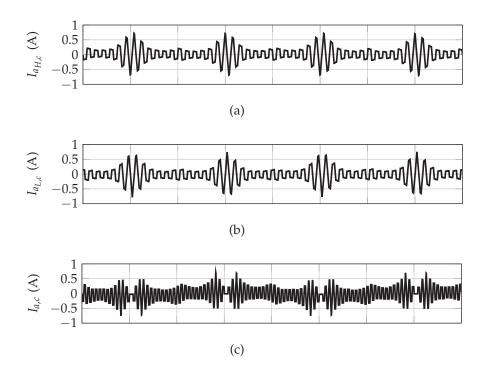

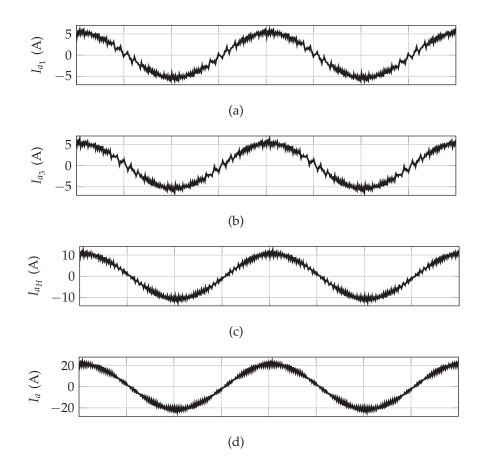

|   | 6    |          |           | l Experimental Results                         |      |

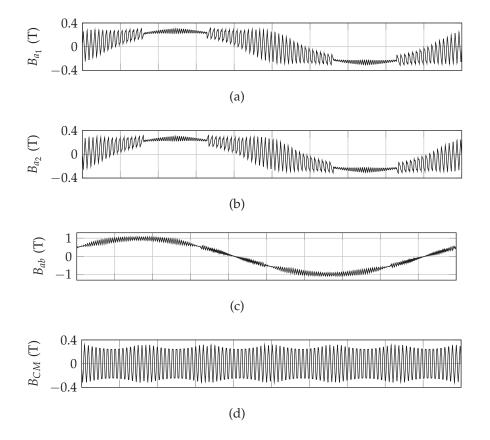

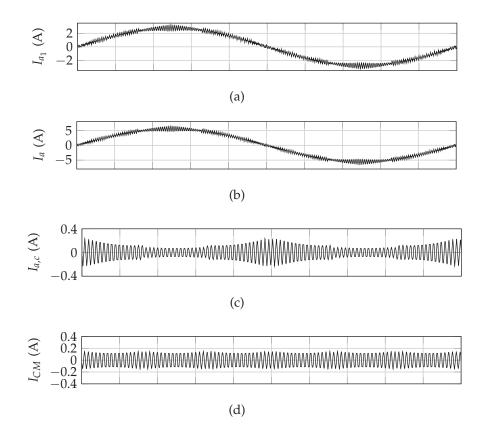

|   |      | 6.1      | Simulat   | ion Study                                      | 249  |

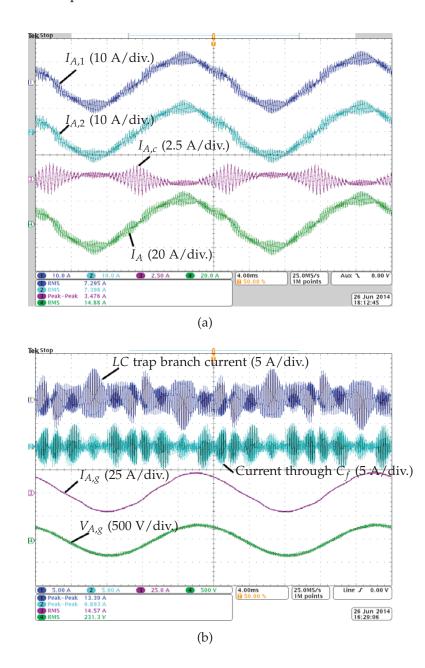

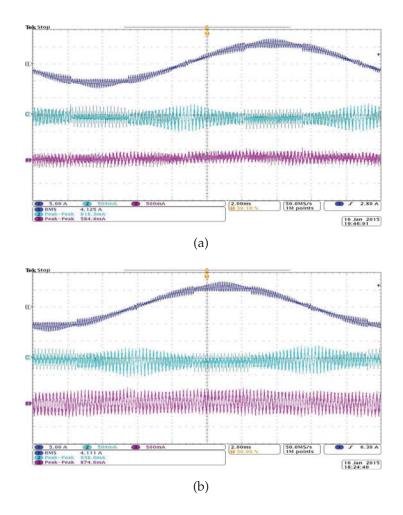

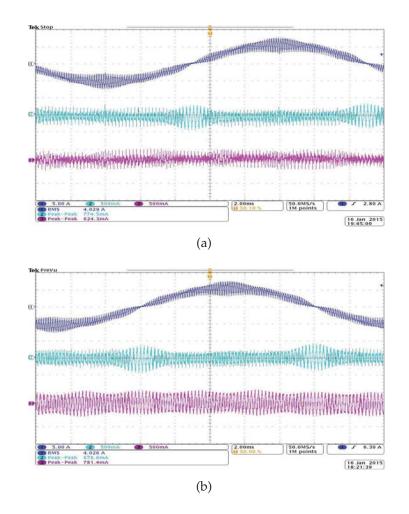

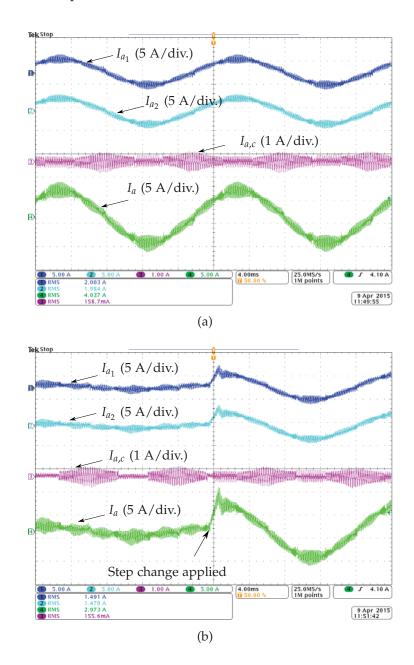

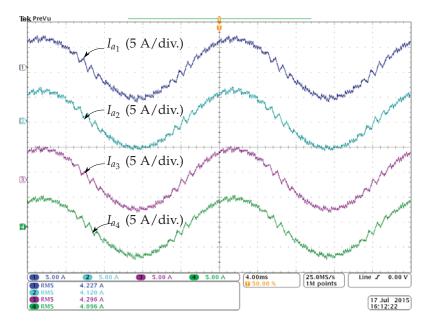

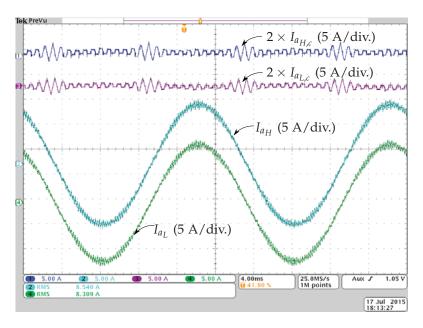

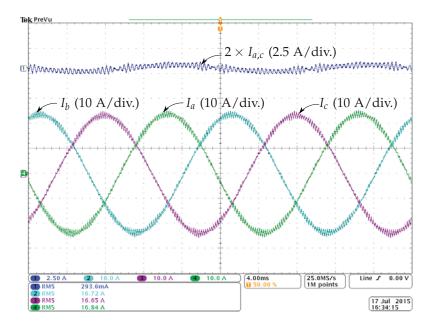

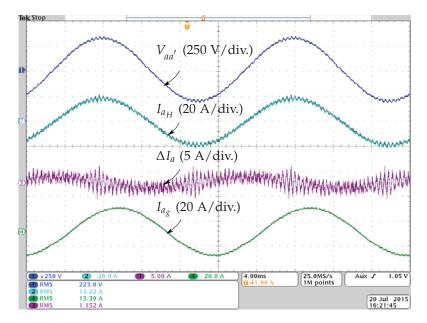

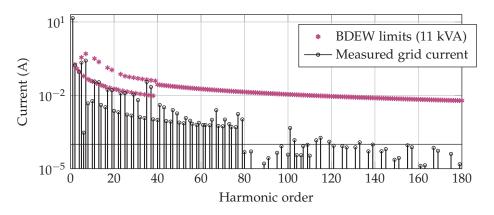

|   |                        | 6.2                                     | Hardware Results                                          | 252 |  |

|---|------------------------|-----------------------------------------|-----------------------------------------------------------|-----|--|

|   | 7                      | Conclu                                  | usion                                                     | 254 |  |

|   | Refe                   | rences                                  |                                                           | 255 |  |

|   |                        |                                         |                                                           |     |  |

| G | Inte                   | grated 1                                | Inductor for Interleaved Operation of Two Parallel Three- | -   |  |

|   | phas                   | se Volta                                | age Source Converters                                     | 259 |  |

|   | 1                      | Introd                                  | uction                                                    | 261 |  |

|   | 2                      | Paralle                                 | el Interleaved Voltage Source Converters                  | 262 |  |

|   | 3                      |                                         | ated Inductor                                             |     |  |

|   |                        | 3.1                                     | Magnetic Structure                                        |     |  |

|   |                        | 3.2                                     | Simplified Reluctance Model                               |     |  |

|   |                        | 3.3                                     | Line Filter Inductor $L_f$                                |     |  |

|   |                        | 3.4                                     | Circulating Current Inductor $L_c$                        |     |  |

|   | 4                      |                                         | n and Performance Comparison                              |     |  |

|   | -                      | 4.1                                     | Maximum Flux Density in Bridge Legs                       |     |  |

|   |                        | 4.2                                     | Maximum Flux Density in Common Leg                        |     |  |

|   |                        | 4.3                                     | Maximum Flux Density in Phase Leg                         |     |  |

|   | 5                      |                                         | ation and Experimental Results                            |     |  |

|   | 0                      | 5.1                                     | Simulation Results                                        |     |  |

|   |                        | 0.1                                     | 5.1.1 Steady-state Considerations                         |     |  |

|   |                        |                                         | 5.1.2 Transient Considerations                            |     |  |

|   |                        | 5.2                                     | Experimental Results                                      |     |  |

|   | 6                      |                                         |                                                           |     |  |

|   |                        |                                         |                                                           |     |  |

|   | itere                  | i ci i ce |                                                           | 270 |  |

| Η | An i                   | integra                                 | ted inductor for parallel interleaved three-phase voltage | •   |  |

|   | source converter 279   |                                         |                                                           |     |  |

|   | 1         Introduction |                                         |                                                           |     |  |

|   | 2                      |                                         | ated Inductor                                             |     |  |

|   |                        | 0                                       | Magnetic Structure                                        |     |  |

|   |                        | 2.2                                     | System Description                                        |     |  |

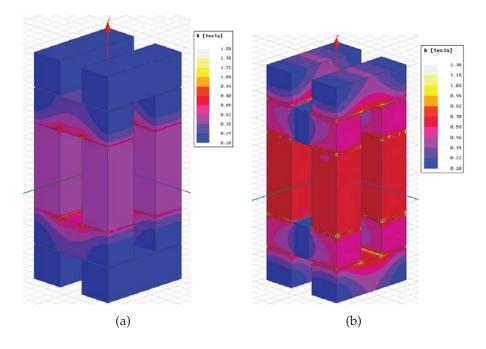

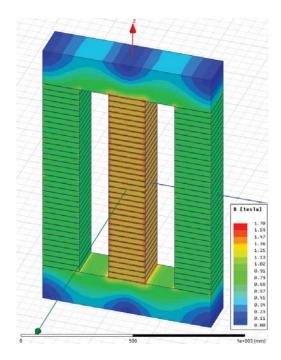

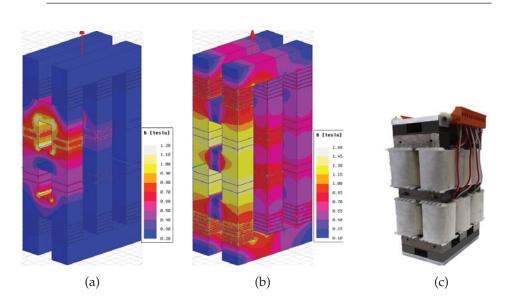

|   |                        | 2.3                                     | Finite Element Analysis                                   |     |  |

|   |                        | 2.0                                     | 2.3.1 Effect of the In-phase Harmonic Frequency Com-      |     |  |

|   |                        |                                         | ponents                                                   |     |  |

|   |                        |                                         | 2.3.2 Effect of the Phase Shifted Harmonic Frequency      | -/- |  |

|   |                        |                                         | Components                                                | 291 |  |

|   |                        | 2.4                                     | Equivalent Electrical Circuit                             |     |  |

|   |                        | 2.5                                     | Reluctance Network                                        |     |  |

|   | 3                      |                                         | n and Volumetric Comparison                               |     |  |

|   | 0                      | 3.1                                     | Pulse Width Modulation Scheme                             |     |  |

|   |                        | 3.2                                     | Maximum Flux Values                                       |     |  |

|   |                        | 0.2                                     | 3.2.1 Common Flux Component                               |     |  |

|   |                        |                                         | 3.2.1Common Plux Component3.2.2Circulating Flux Component |     |  |

|   |                        |                                         |                                                           | ムフフ |  |

|   |      |                                            | 3.2.3 Maximum Flux in Various Parts of the Inte-                                                                                                                                                                     |                                 |

|---|------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|   |      |                                            | grated Inductor                                                                                                                                                                                                      | 0                               |

|   |      | 3.3                                        | Design Methodology                                                                                                                                                                                                   | 1                               |

|   |      |                                            | 3.3.1 Calculation of the Line Filter Inductance $L_f$ 302                                                                                                                                                            | 1                               |

|   |      |                                            | 3.3.2 Area Product Requirement                                                                                                                                                                                       | 1                               |

|   |      |                                            | 3.3.3 Core Selection for the Cell and Number of turns302                                                                                                                                                             | 2                               |

|   |      |                                            | 3.3.4 Core Selection for the Bridge Legs                                                                                                                                                                             | 2                               |

|   |      |                                            | 3.3.5 Air Gap Geometry                                                                                                                                                                                               |                                 |

|   |      | 3.4                                        | Design Example                                                                                                                                                                                                       |                                 |

|   |      | 3.5                                        | Volumetric Comparison                                                                                                                                                                                                |                                 |

|   |      |                                            | 3.5.1 Three Limb Coupled Inductor                                                                                                                                                                                    |                                 |

|   |      |                                            | 3.5.2 Three Phase Line Filter Inductor $L_f$                                                                                                                                                                         |                                 |

|   | 4    | Simu                                       | lations and Experimental Results                                                                                                                                                                                     |                                 |

|   |      | 4.1                                        | Simulation Study                                                                                                                                                                                                     |                                 |

|   |      | 4.2                                        |                                                                                                                                                                                                                      |                                 |

|   | 5    | Conc                                       | lusion                                                                                                                                                                                                               |                                 |

|   | A    |                                            | endix                                                                                                                                                                                                                |                                 |

|   |      | A.1                                        |                                                                                                                                                                                                                      |                                 |

|   |      | A.2                                        | Derivation of Common Component of Flux                                                                                                                                                                               |                                 |

|   | Refe |                                            | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                |                                 |

|   |      |                                            |                                                                                                                                                                                                                      | _                               |

| Ι | Mag  | gnetic                                     | Integration for Parallel Interleaved VSCs Connected in a                                                                                                                                                             |                                 |

|   | Wh   | iffletre                                   | e Configuration 318                                                                                                                                                                                                  | 8                               |

|   | 1    | Intro                                      | duction                                                                                                                                                                                                              | 0                               |

|   | 2    | Circu                                      | lating Current in a Parallel Interleaved VSCs                                                                                                                                                                        | 3                               |

|   | 3    | Integ                                      | rated Inductor                                                                                                                                                                                                       | 4                               |

|   |      | 3.1                                        | Magnetic Circuit Analysis                                                                                                                                                                                            | 5                               |

|   |      | 3.2                                        |                                                                                                                                                                                                                      |                                 |

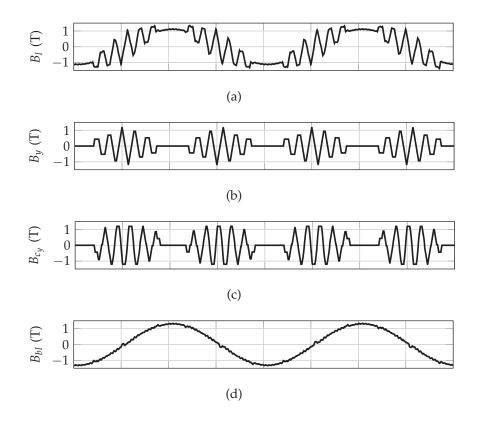

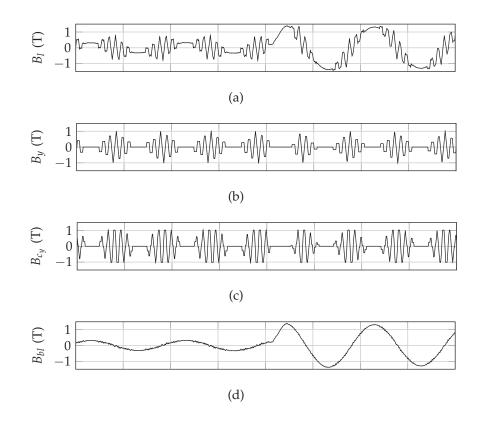

|   |      | 3.3                                        | Flux Density Analysis                                                                                                                                                                                                | 0                               |

|   |      |                                            | 3.3.1 Circulating Flux Component                                                                                                                                                                                     |                                 |

|   |      |                                            | 3.3.2 Common Flux Component                                                                                                                                                                                          |                                 |

|   |      |                                            | 3.3.3 Flux in the limbs of the cells                                                                                                                                                                                 |                                 |

|   | 4    | Circu                                      | lating Current Suppression Between the Two Converter                                                                                                                                                                 |                                 |

|   |      |                                            |                                                                                                                                                                                                                      |                                 |

|   | _    | GIUU                                       | ps                                                                                                                                                                                                                   | 3                               |

|   | 5    |                                            | ps                                                                                                                                                                                                                   |                                 |

|   | 5    |                                            | Element Analysis and Comparative Evaluation 335                                                                                                                                                                      | 5                               |

|   | 5    | Finite<br>5.1                              | Element Analysis and Comparative Evaluation                                                                                                                                                                          | 5<br>5                          |

|   | 5    | Finite                                     | Element Analysis and Comparative Evaluation                                                                                                                                                                          | 5<br>5<br>8                     |

|   | 5    | Finite<br>5.1                              | Element Analysis and Comparative Evaluation                                                                                                                                                                          | 5<br>5<br>8<br>9                |

|   |      | Finite<br>5.1<br>5.2                       | Element Analysis and Comparative Evaluation335Finite Element Analysis335Comparative Evaluation3365.2.1Volumetric Comparison3395.2.2Losses Comparison339                                                              | 5<br>5<br>9<br>9                |

|   | 5    | Finite<br>5.1<br>5.2<br>Simu               | Element Analysis and Comparative Evaluation                                                                                                                                                                          | 5<br>5<br>8<br>9<br>9           |

|   |      | Finite<br>5.1<br>5.2<br>Simu<br>6.1        | e Element Analysis and Comparative Evaluation335Finite Element Analysis335Comparative Evaluation3385.2.1Volumetric Comparison3395.2.2Losses Comparison339lation and the Experimental Results340Simulation Results341 | 5<br>5<br>8<br>9<br>9<br>0<br>1 |

|   |      | Finite<br>5.1<br>5.2<br>Simu<br>6.1<br>6.2 | Element Analysis and Comparative Evaluation                                                                                                                                                                          | 5<br>5<br>8<br>9<br>0<br>1<br>2 |

|                      | Refe | rences  | ••••        |                                                        | 346 |

|----------------------|------|---------|-------------|--------------------------------------------------------|-----|

| J                    | Opt  | imized  | harmoni     | c filter inductor for dual-converter fed open-end      | ł   |

| transformer topology |      |         |             |                                                        | 349 |

|                      | 1    | Introd  | uction .    | · · · · · · · · · · · · · · · · · · ·                  | 351 |

|                      | 2    | Dual-   | Converter   | Fed Open-End Transformer Topology                      | 353 |

|                      | 3    | Integra | ated Indu   | ictor                                                  | 354 |

|                      | 4    | Design  | n of the Ir | ntegrated Inductor                                     | 356 |

|                      |      | 4.1     | Value of    | the converter-side inductor $L_f$                      | 357 |

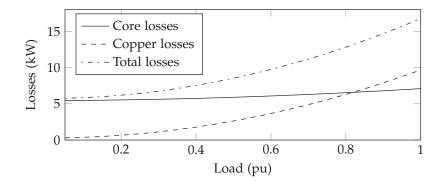

|                      |      | 4.2     |             | ss Modeling                                            |     |

|                      |      |         | 4.2.1       | Major Loop                                             | 358 |

|                      |      |         | 4.2.2       | Minor Loop                                             | 359 |

|                      |      | 4.3     | Copper      | Loss Modeling                                          | 360 |

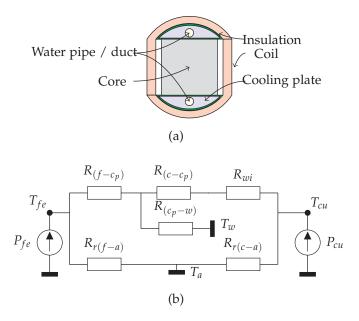

|                      |      | 4.4     | Thermal     | Modeling                                               | 361 |

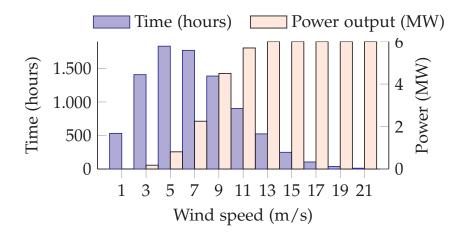

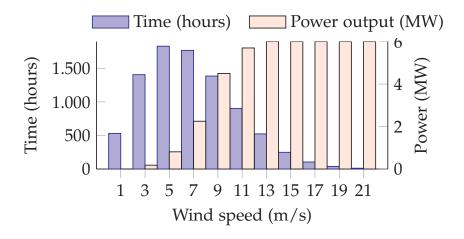

|                      |      | 4.5     | Loading     | Profile and Energy Yield                               | 362 |

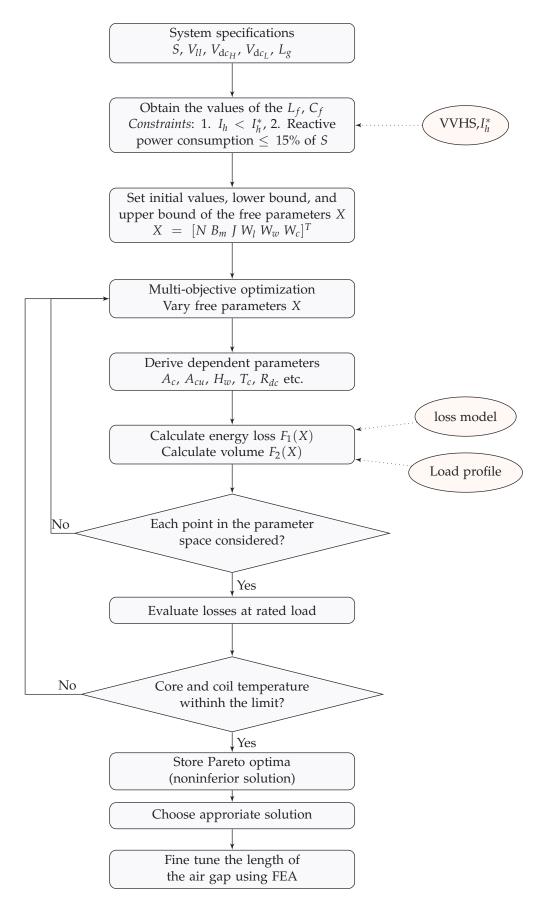

|                      |      | 4.6     | Optimiz     | ation Process                                          | 362 |

|                      |      |         | 4.6.1       | Step 1: Value of the converter-side inductor $L_f$     | 363 |

|                      |      |         | 4.6.2       | Step 2: Derive dependent design variables              | 365 |

|                      |      |         | 4.6.3       | Step 3: Objective function evaluation                  | 365 |

|                      |      |         | 4.6.4       | Step 4: Air gap length                                 | 365 |

|                      |      |         | 4.6.5       | Step 5: Temperature estimation                         | 366 |

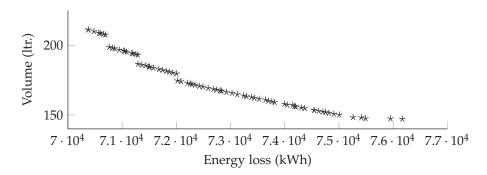

|                      |      |         | 4.6.6       | Step 6: Pareto optima solutions                        | 366 |

|                      |      |         | 4.6.7       | Step 7: FEA analysis                                   |     |

|                      | 5    | Desigr  |             | neters and Volumetric Comparison                       |     |

|                      |      | 5.1     | Volumet     | ric comparison                                         | 368 |

|                      | 6    | Simula  | ation and   | Hardware Results                                       | 369 |

|                      | 7    | Conclu  | usion       |                                                        | 371 |

|                      | Refe | rences  | ••••        |                                                        | 372 |

| K                    | Dua  | l Conv  | erter Fed   | Open-end Transformer Topology with Paralle             | 1   |

|                      |      |         |             | grated Magnetics                                       | 374 |

|                      | 1    |         |             |                                                        | 380 |

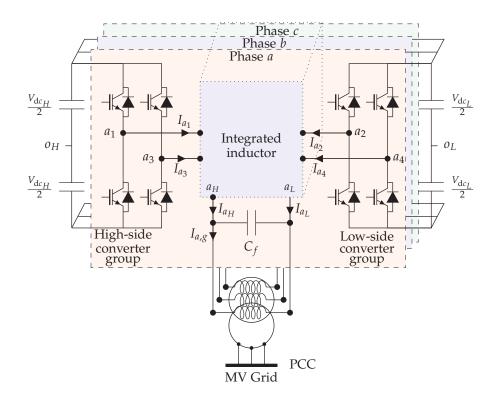

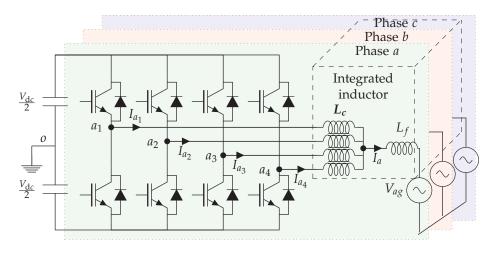

|                      | 2    | Systen  | n Descrip   | tion                                                   | 382 |

|                      |      | 2.1     | -           | tion                                                   |     |

|                      |      | 2.2     | Harmon      | ic Quality Assessment                                  | 383 |

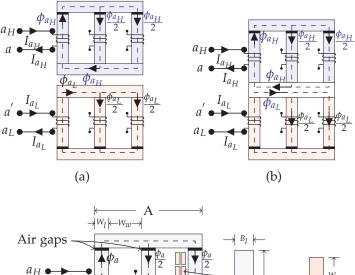

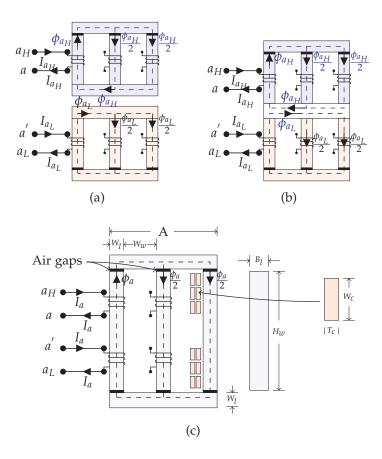

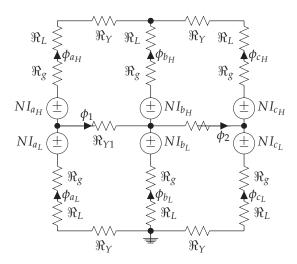

|                      | 3    | Integra | ated Indu   | ictor                                                  | 386 |

|                      |      | 3.1     | Magneti     | c Structure of Integrated Inductor                     | 386 |

|                      |      | 3.2     | Flux Lin    | king with the Coils                                    | 388 |

|                      |      | 3.3     |             | er Inductor and Circulating Current Inductor .         |     |

|                      | 4    | Desigr  |             | ology                                                  |     |

|                      |      | 4.1     |             | Equations $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ |     |

|                      |      |         | 4.1.1       | Fundamental Frequency Flux Component $\phi_{x_{k,f}}$  | 393 |

|                      |      |         | 4.1.2       | Circulating Flux Component $\phi_{x_{k,c}}$            | 393 |

|                      |      |         |             |                                                        |     |

|      |                                            | 4.1.3     | Maximum Flux Value in the Bridge Legs 394           |  |  |  |

|------|--------------------------------------------|-----------|-----------------------------------------------------|--|--|--|

|      |                                            | 4.1.4     | Maximum Flux Value in the Top and the Bot-          |  |  |  |

|      |                                            |           | tom Yokes                                           |  |  |  |

|      |                                            | 4.1.5     | Maximum Flux Value in the Common Yoke 395           |  |  |  |

|      |                                            | 4.1.6     | Maximum Flux Value in the Limb                      |  |  |  |

|      | 4.2                                        | Design    | Example                                             |  |  |  |

|      |                                            | 4.2.1     | Integrated Inductor Using Discrete Bridge Blocks396 |  |  |  |

|      |                                            | 4.2.2     | Integrated Inductor Using Split Windings 399        |  |  |  |

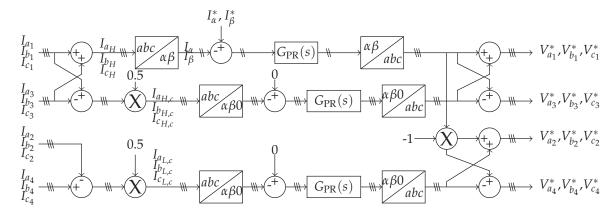

| 5    | Control Schemes and Performance Evaluation |           |                                                     |  |  |  |

|      | 5.1                                        | Control   | Scheme                                              |  |  |  |

|      |                                            | 5.1.1     | Active and Reactive Current Control 401             |  |  |  |

|      |                                            | 5.1.2     | Circulating Current Control 401                     |  |  |  |

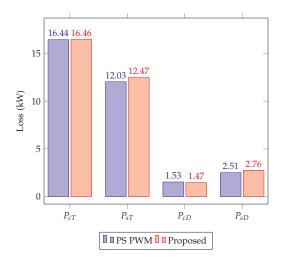

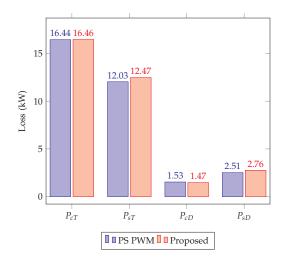

|      | 5.2                                        | Loss Ev   | aluation                                            |  |  |  |

|      |                                            | 5.2.1     | Semiconductor Losses                                |  |  |  |

|      |                                            | 5.2.2     | Inductor Losses                                     |  |  |  |

|      | 5.3                                        | Compai    | rative Evaluation                                   |  |  |  |

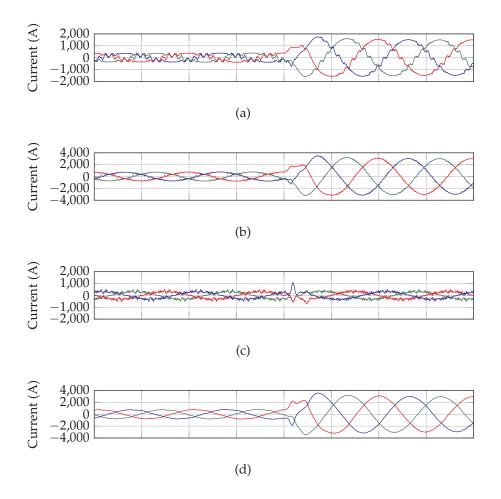

| 6    | Simul                                      | ation and | l Experimental Results 406                          |  |  |  |

| 7    | Concl                                      | usion     |                                                     |  |  |  |

| Refe | References                                 |           |                                                     |  |  |  |

## Preface

This thesis presents the work that author has carried out at the Intelligent Efficient Power Electronics (IEPE) research center at the Department of Energy Technology at Aalborg University. I would like to express my gratitude to all the members of the IEPE and all of my colleagues at the Department of Energy Technology for providing exciting working environment. A special thanks should be given to Prof. Stig Munk-Nielsen and Prof. Marco Liserre for giving me an opportunity to work in the IEPE. Acknowledgments are given to the Innovation Fund Denmark, Obel Family Foundation, Otto Mønsteds Fond, and Department of Energy Technology for their financial support.

I would like to express my sincere gratitude to my supervisor Prof. Remus Teodorescu, co-supervisor Prof. Tamas Kerekes, and former supervisor Prof. Marco Liserre for their valuable guidance and support. I want to thank Prof. Frede Blaabjerg for the constructive discussion and continuous encouragement. Many thanks to Prof. Stig Munk-Nielsen for important technical discussions. A special thank should also be given to my colleague Lorand Bede and former colleague Prof. Ramkrishan Maheshwari for the collaboration.

I articulate my sincere gratitude to Prof. Paolo Mattavelli and Prof. Maryam Saeedifard for their time and effort to evaluate this thesis. Many thanks to Prof. Francesco Iannuzzo for chairing the assessment committee.

I take this opportunity to thank Prof. Philip Carne Kjær for giving me an opportunity to work on a project with Vestas Wind Systems A/S and special thanks to Tune Pedersen and Stig Lund Pallesgaard for giving me an industry perspective on the topic. Bjørn Rannestad from KK Wind Solutions, Paul Thøgersen and Flemming Abrahamsen from PowerCon Embedded A/S also deserve my sincere gratefulness for their valuable feedback and interesting discussions.

I would also articulate my gratitude to Dr. Rafael Peña Alzola for his support during the beginning of my Ph.D. and Dr. Sanjay Chaudhary, Dr. Tushar Batra, Dr. Lajos Török, Dr. Laszlo Mathe, Dr. Huai Wang for our interesting technical discussions. Special thanks to Dr. Francisco Freijedo, Paul Dan Burlacu, and Catalin Gabriel Dancan for conducive environment in the office and our good time. I also want to thank Casper Vadstrup for helping me with the Danish translation of the abstract. I would like to acknowledge the help I received from Walter Neumayr, Jan Christiansen, Flemming Bo Larsen, Mads Lund, and Frank Rosenbeck. I also want to thank Ann Louise Henriksen, Casper Jørgensen, Corina Busk Gregersen, Tina Lisbeth Larsen, Mette Skov Jensen, and Eva Janik for their help regarding the administrative matters and making my life easy.

I wish to express my sincere gratitude to my mother Pushpa, my wife Vandana, my grandmother Gyanba and other other family members for their love and support. I want to thank my mother for loving me unconditionally and for providing formal and moral education. Sincere gratitude to my aunt Hasuba for raising me like her own son and uncle Pravinsinh for supporting my undergraduate education. I want to thank Vandana for love, understanding, and patience; this thesis would not have been possible without her support. Finally love and many thanks to my son Meghdattsinh for inspiring me to be more curious and for keeping me stress-free.

> Ghanshyamsinh Gohil Aalborg University, April 4, 2016

# Part I Summary

## Summary

The extended summary is presented in this chapter.

## 1 Introduction

The background and motivation is presented in this section. The research questions that are addressed in this thesis are described and the technical contributions are summarized. Finally the structure of the thesis is presented along with the list of the appended papers.

## 1.1 Background and Motivation

## 1.1.1 Applications

Voltage Source Converters (VSCs) are widely used in many dc/ac power electronics applications and often connected in parallel to meet the ever increasing demand for the higher power rating converter system [1, 2] in MW-level power electronics applications. Some of these applications are as follows:

- Variable speed motor drives [3–8].

- Wind energy conversion system [9–11].

- Solar photo-voltaic system [12, 13].

- Active power filters [14–17].

- Un-interrupted power supplies [18–24].

- Solid state transformers [25].

The typical Silicon Insulated Gate Bipolar Transistors (Si-IGBT) that are used in such applications suffer from excessive losses if the switching frequency is increased beyond a few kHz. Therefore, the switching frequency is often limited [26]. As a result, large harmonic filter components are required in order to meet the stringent power quality requirements imposed by the utility [27] in grid-connected applications. These harmonic filter components occupy significant amount of space in the overall system [28]. Moreover, considerable losses occur in the filter components and the overall conversion efficiency is compromised if large filter components are used [26]. They also result in increased cost of the overall converter system [29]. Therefore, the filter size should be made as small as possible to achieve efficient, compact and cost-effective system. In variable speed motor drives, it is highly desirable to reduce the harmonic content in the motor torque, specially for the drives with the lightly damped mechanical loads [7]. The size of the harmonic filter components and the harmonic content in the motor torque can be reduced by increasing the switching frequency and thereby pushing the major harmonic components in the modulated output voltage further away from the fundamental frequency component. However, this leads to more switching losses and the efficiency of the system is compromised. Therefore the efforts are being made to reduce both the size of filter components and the switching frequency. One of the ways to achieve this contradictory requirements is to employ a multi-level VSC.

A three-level neutral point diode clamped (3L-NPC) topology is commonly used [30]. However, an extra control efforts are required to balance the dc-link capacitor voltage [31]. Moreover, the semiconductor loss distribution is unequal [32] and this may lead to the de-rating of the VSC [33]. On the other hand, the two-level VSC is used extensively in many industrial applications due to its simple power circuitry and proven technology. Therefore, it is highly desirable to realize the converter system using the standard Two-Level (2L) VSC. For the parallel connected 2L-VSCs, multi-level voltage waveforms can be achieved by interleaving the carrier signals of the parallel connected VSC legs.

### 1.1.2 Overview of the Parallel Interleaved VSCs

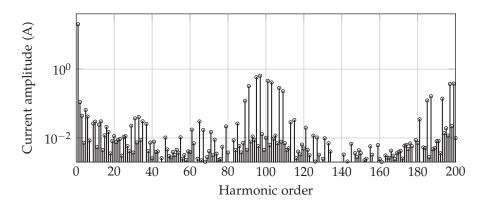

### Harmonic Performance:

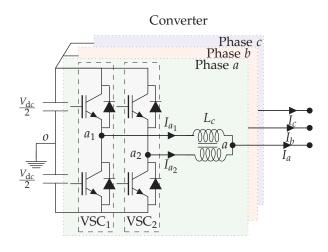

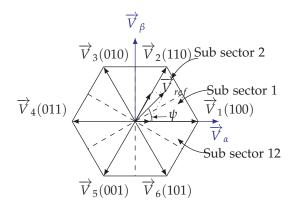

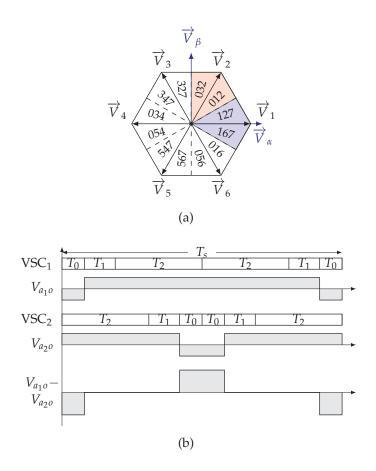

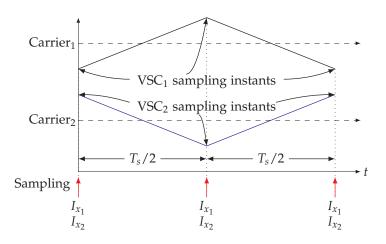

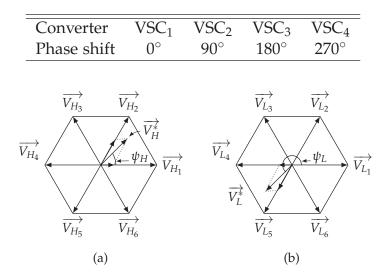

The concept of harmonic quality improvement of the parallel connected pulse width modulated VSCs by interleaving the carrier signals has been first proposed in [34, 35]. The interleaved operation of two parallel VSCs and four parallel VSCs had been proposed. The symmetrical carrier interleaving was used where the carrier signals were phase-shifted by 180° in the case of two parallel VSCs (and 90° in the case of four parallel VSCs).

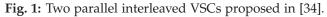

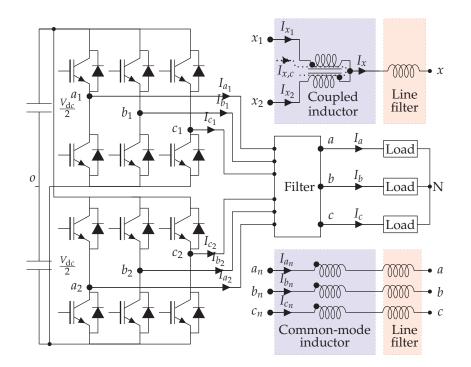

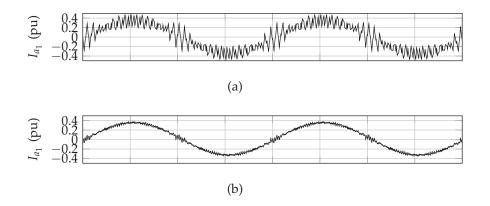

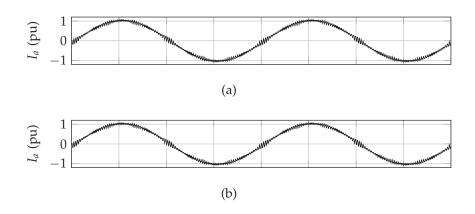

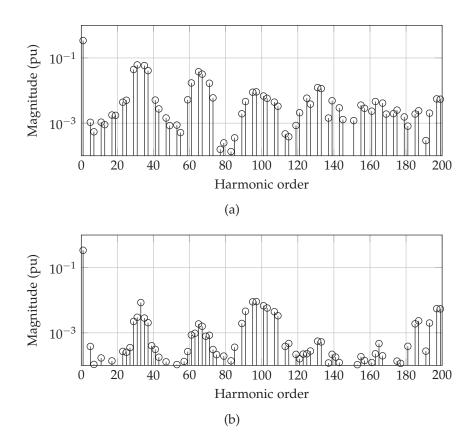

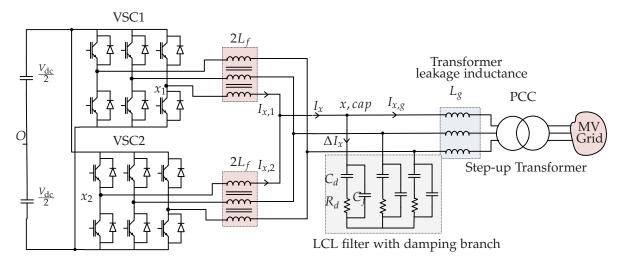

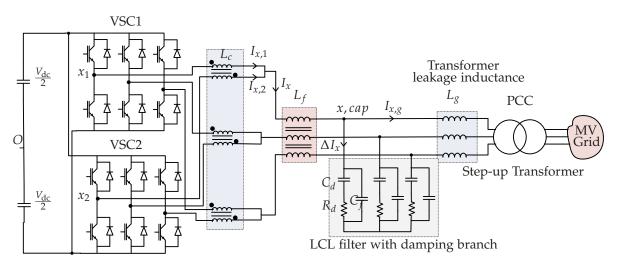

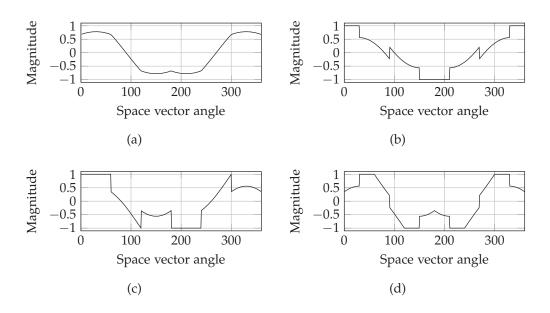

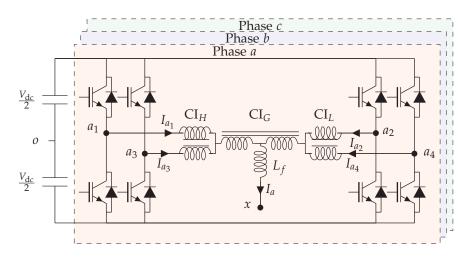

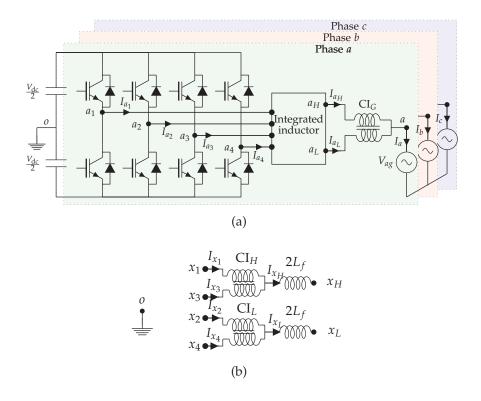

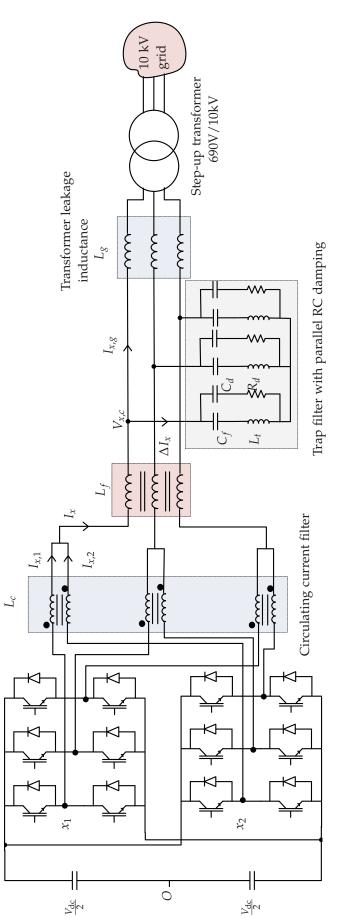

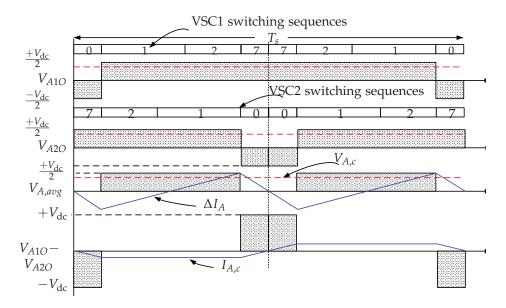

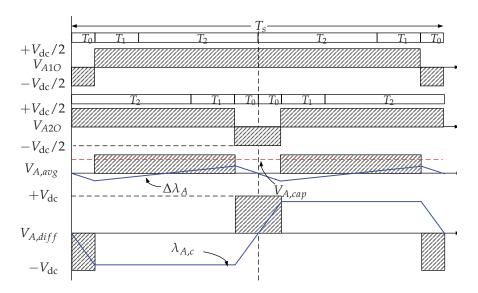

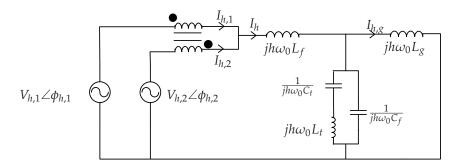

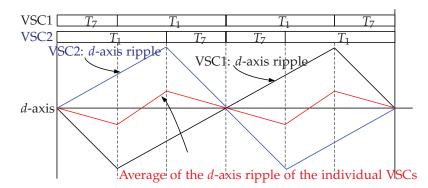

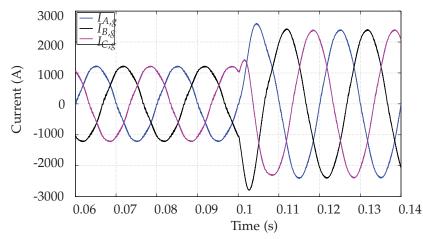

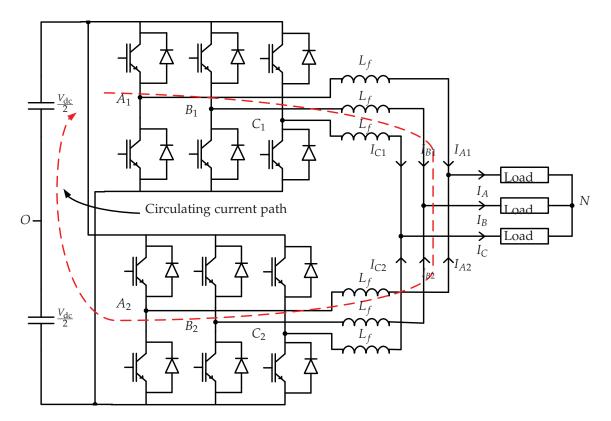

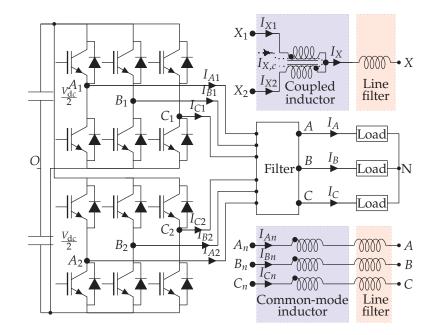

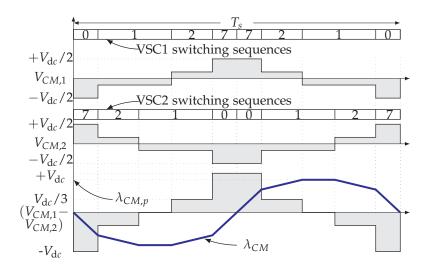

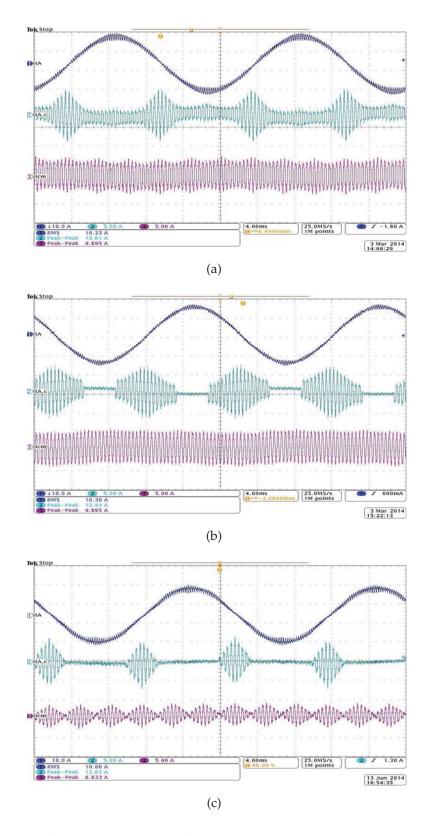

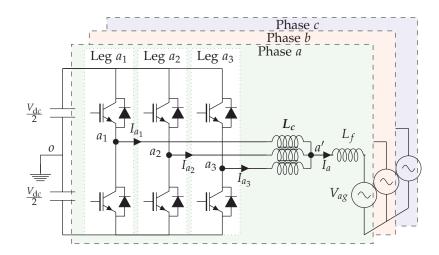

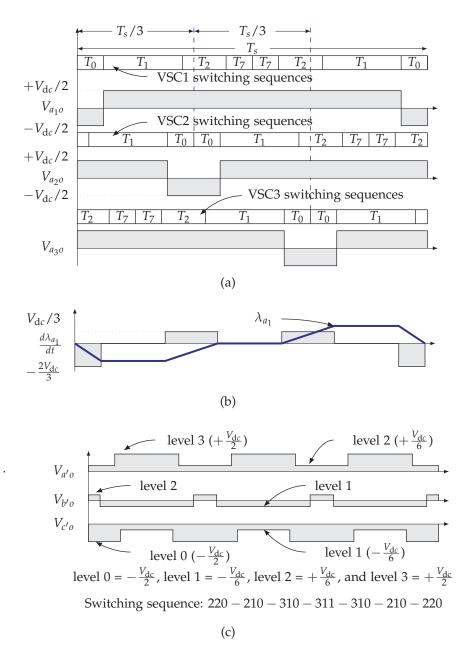

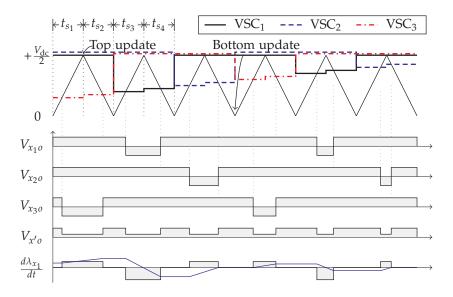

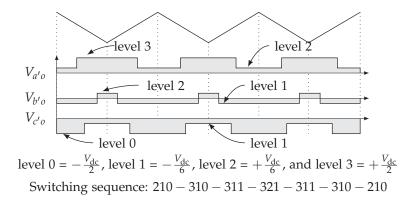

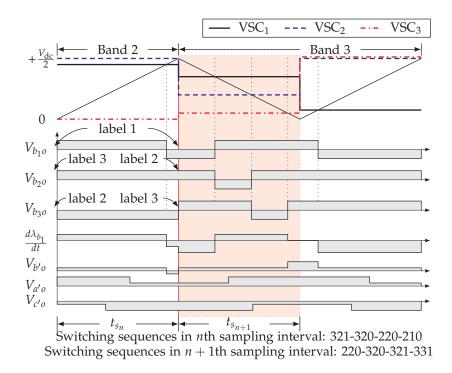

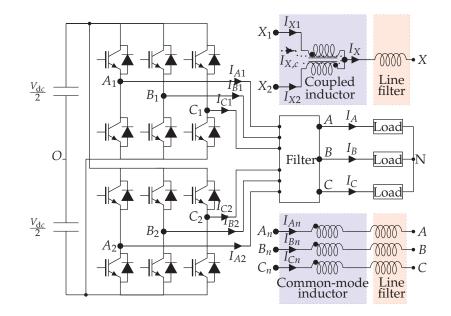

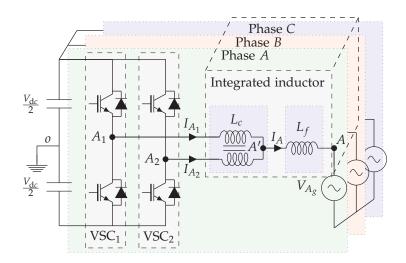

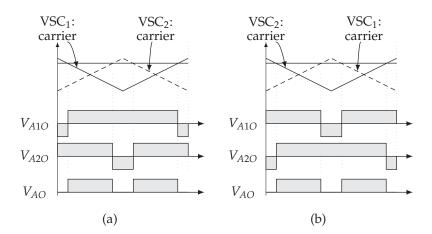

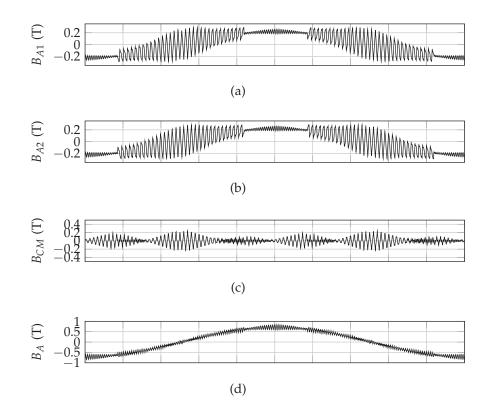

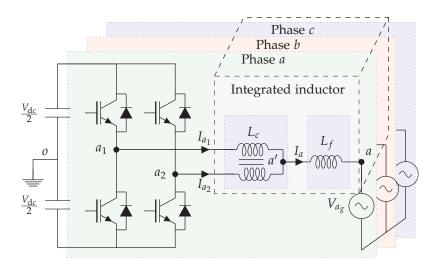

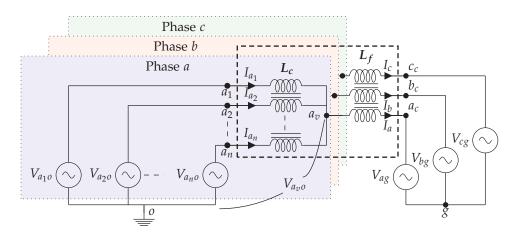

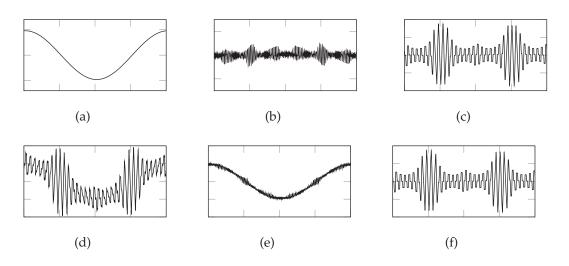

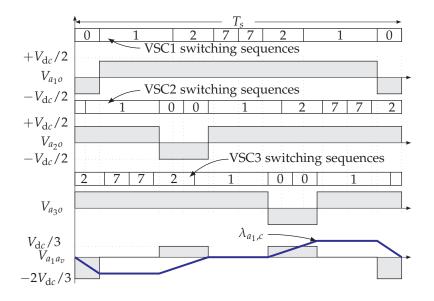

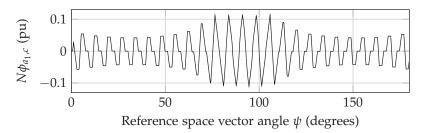

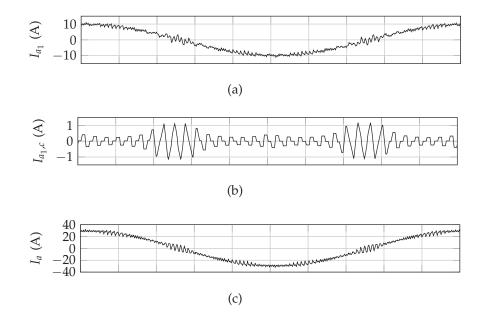

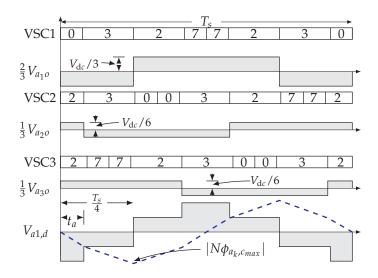

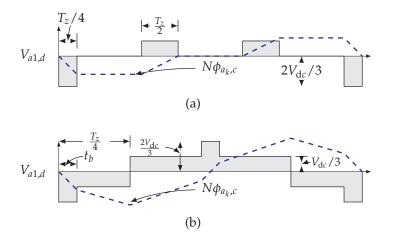

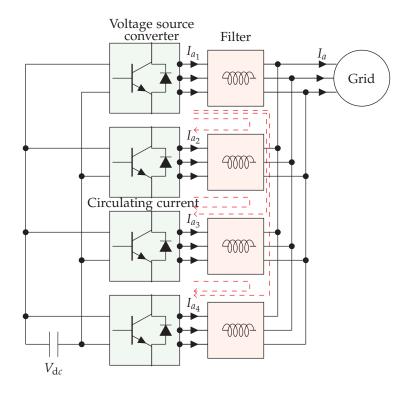

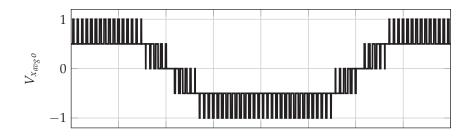

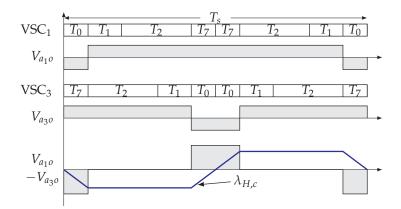

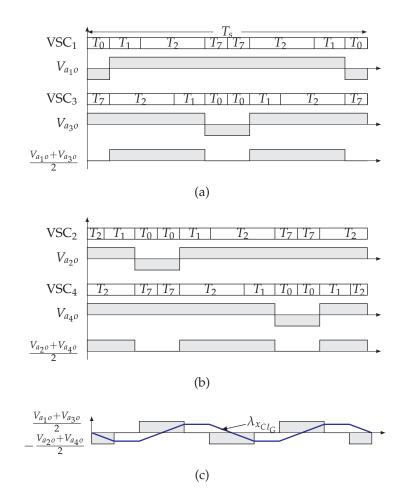

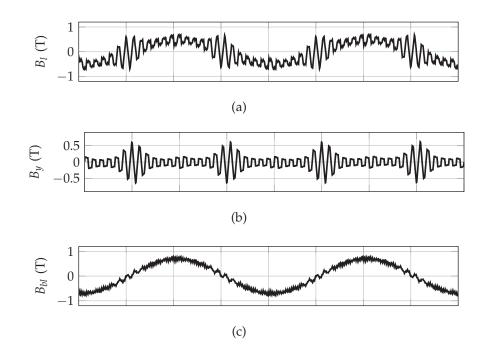

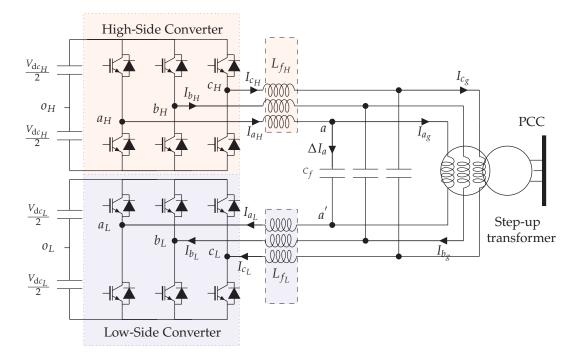

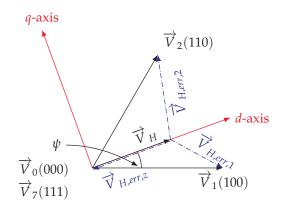

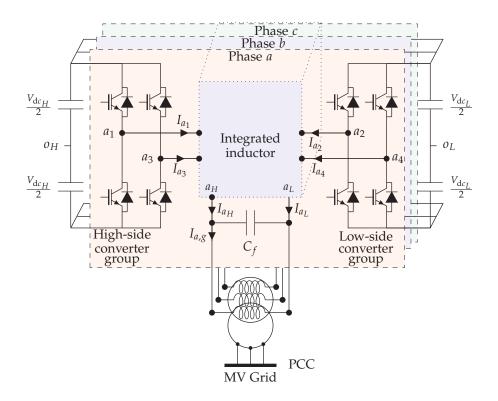

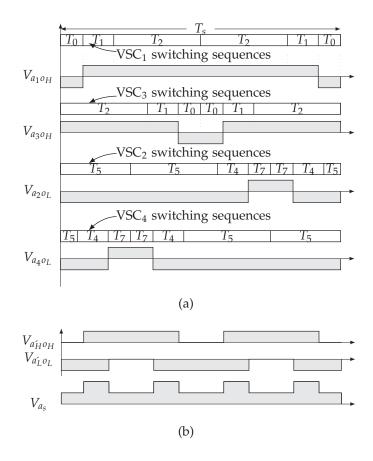

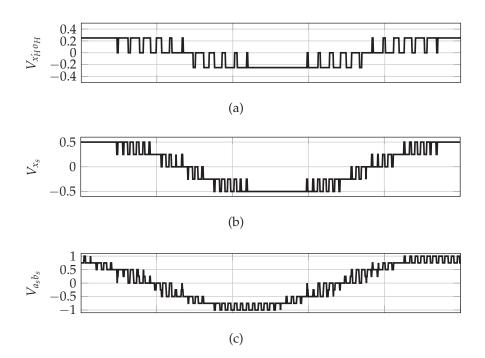

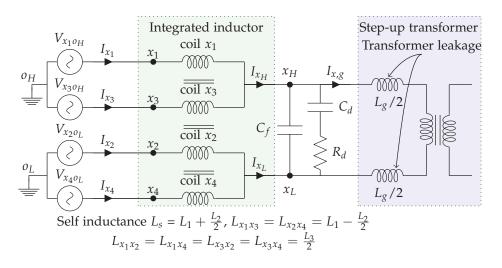

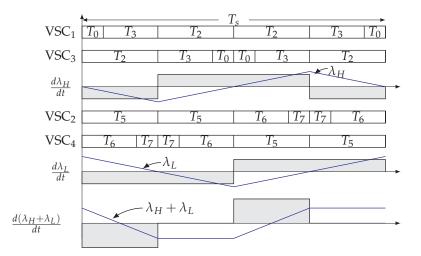

Two parallel voltage source converters are shown in Fig. 1. A carrier signals of both the VSCs are phase shifted by 180°. As a result, the switched output voltages of the parallel VSC legs (referred to as pole voltages) are also phase-shifted, as shown in Fig. 2(a) and Fig. 2(b). The resultant voltage is the average of the individual switched output voltage of the parallel legs of that phase and demonstrates three-level voltage waveforms, as shown in Fig. 2(c).

### 1. Introduction

**Fig. 2:** Simulated voltage waveforms for two parallel interleaved voltage source converters. The carrier signals of the two voltage source converters are phase-shifted by  $180^{\circ}$ . (a) Switched output voltage of leg  $a_1$ , (b) Switched output voltage of leg  $a_2$ , (c) Resultant voltage of phase a, (d) Resultant voltage of phase b, (e) Line-to-line voltage  $V_{ab}$ . The voltage waveforms are normalized with respect to  $V_{dc}/2$ .

The line-to-line voltage across the phase *a* and phase *b* is also shown in Fig. 2(d). It demonstrates five-level voltage waveforms. As a result, compared to the 2L-VSC, superior harmonic performance can be achieved.

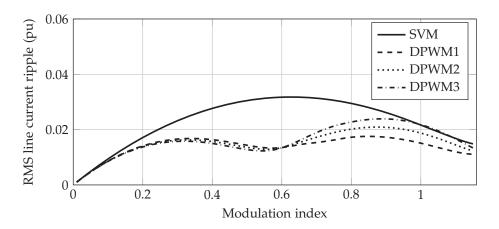

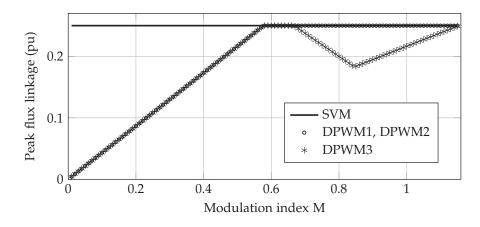

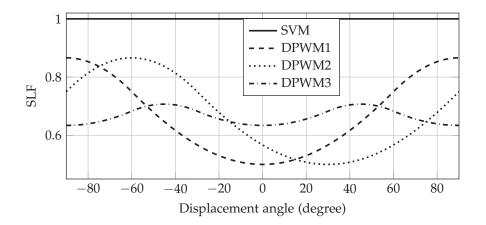

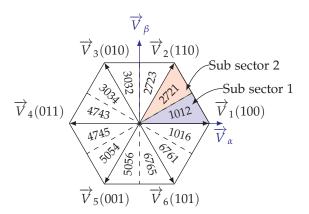

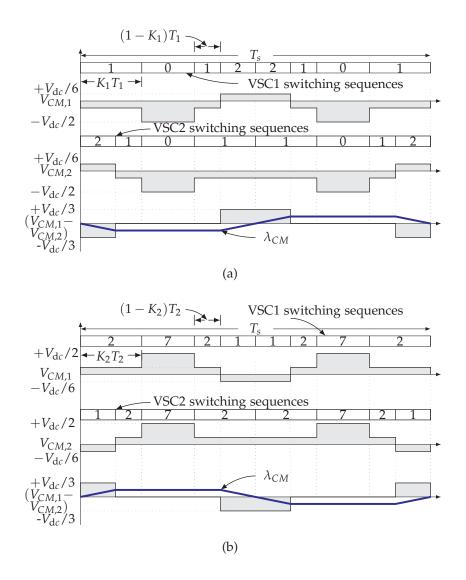

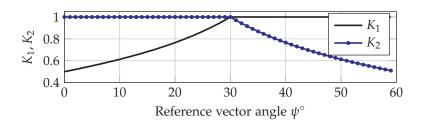

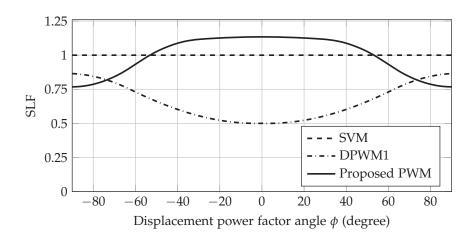

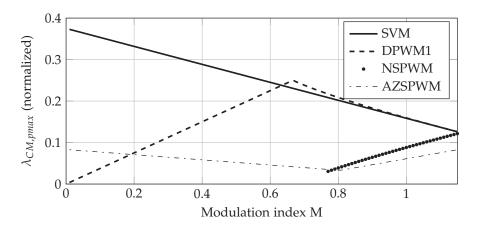

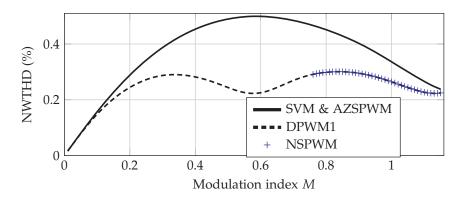

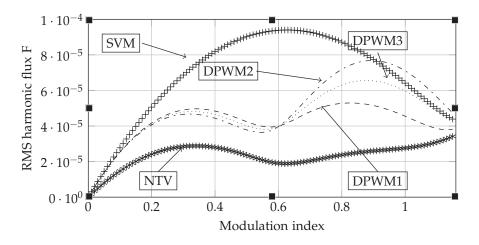

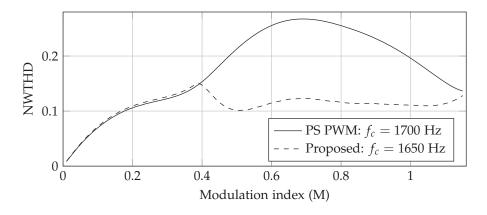

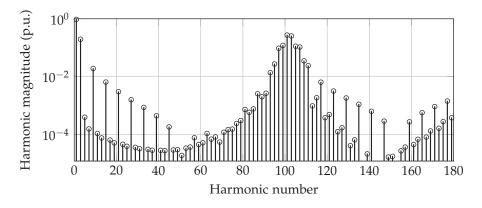

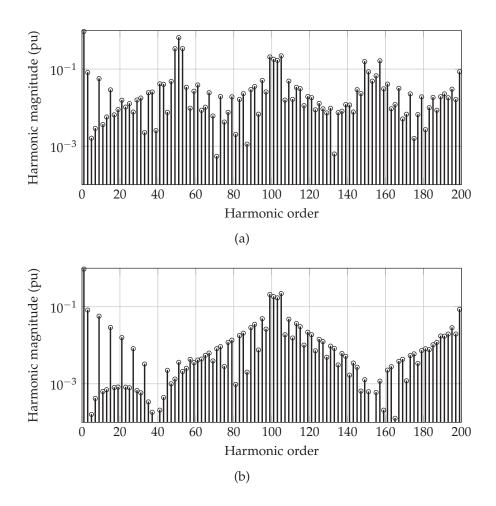

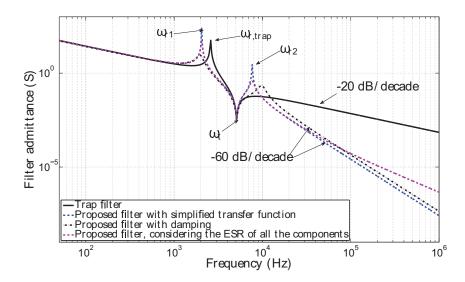

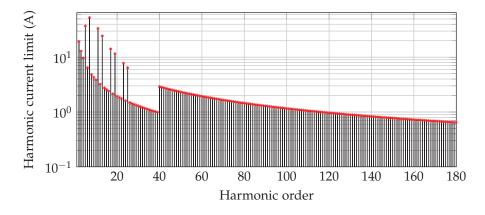

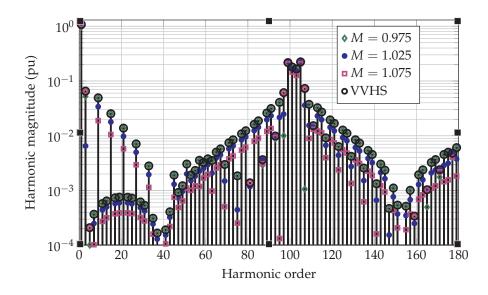

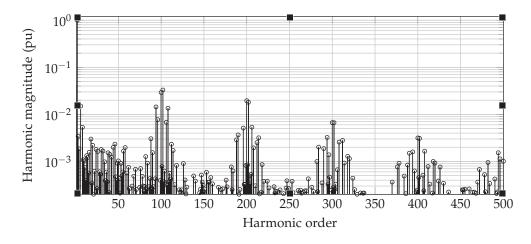

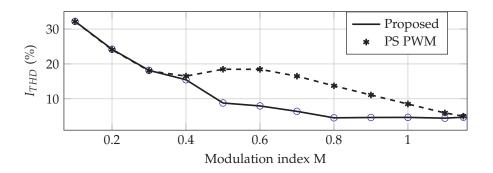

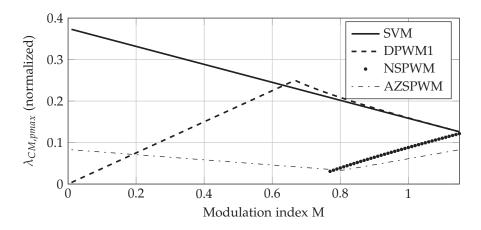

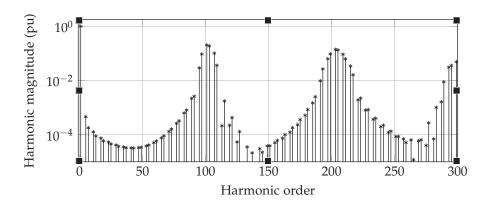

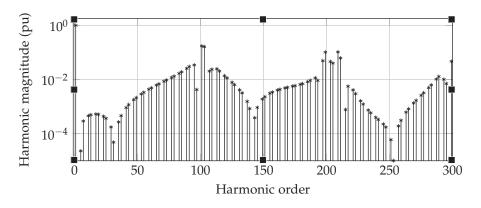

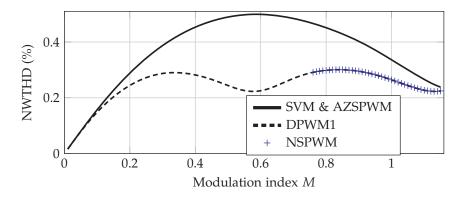

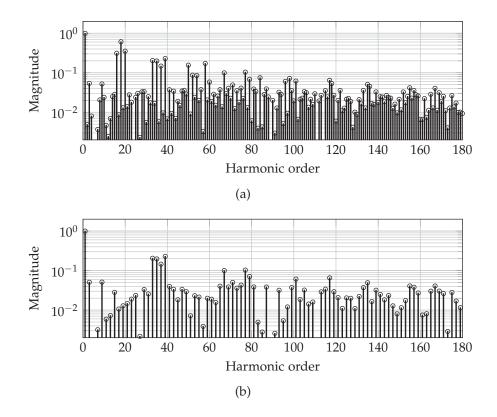

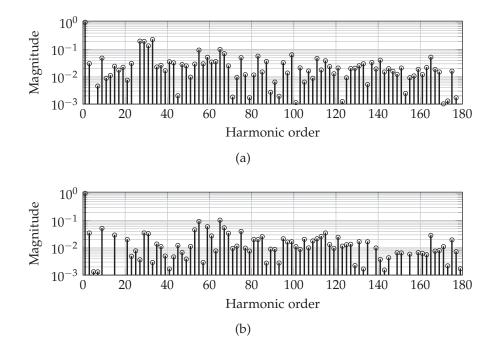

The harmonic performance for the sine triangle Pulse Width Modulation (PWM) has been investigated in [34] and it is demonstrated that for the two parallel interleaved VSCs, the carrier frequency harmonic component and its side bands can be significantly reduced in the resultant switched output voltage. Moreover, the carrier interleaving also reduces the harmonic content in the dc-link current and Common-Mode (CM) voltage [36]. So far in these studies the effects of the symmetrical interleaving were investigated. The impact of the asymmetrical interleaving angle on the harmonic performance has been investigated in [37, 38]. The concentration of the harmonic energy also depends on the modulation index and it is shown that for two parallel VSCs, modulated using the continuous Space Vector Modulation (SVM), the harmonic energy is concentrated more around the 2nd carrier frequency component for the low modulation indices. On the other hand, for the high modulation indices, the harmonic energy is concentrated around the 1st carrier frequency component [39]. Based on this findings, depending upon the modulation index, use of two different interleaving angles was proposed (interleaving angle of 90° for low modulation indices and 180° for high modulation indices). In the case of the  $60^{\circ}$  clamped discontinuous PWM (commonly referred to as DPWM1 [40]), irrespective of the modulation index, the harmonic energy is concentrated more around the 1st carrier frequency and the use of the interleaving angle of 180° was recommended. Similar conclusions were drawn in [41], where the analysis has been performed using rms grid current ripple in the synchronously rotating dq reference frame. The impact of the asymmetrical interleaving angle on the dc-link current has been also investigated in [42].

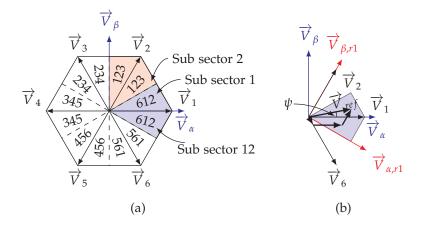

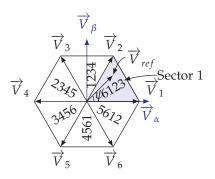

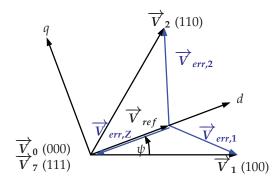

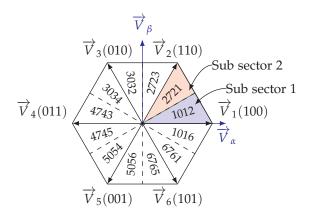

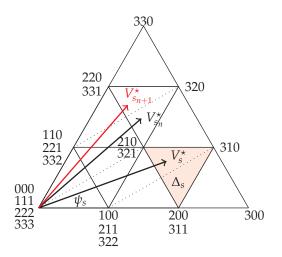

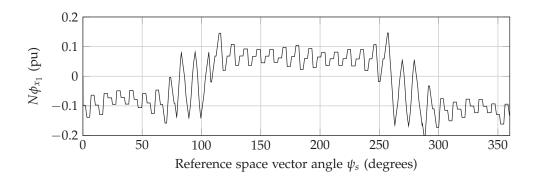

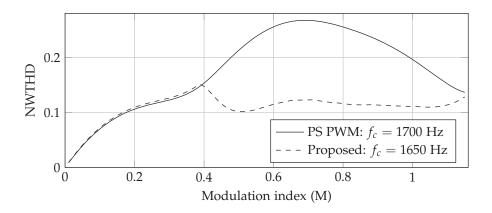

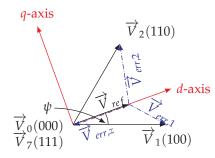

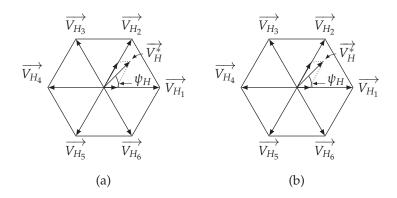

The optimal PWM scheme to improve the harmonic performance of the parallel 2L-VSCs under the Phase-Shifted (PS) PWM is presented in [43]. The effect of the combination of the several switching sequences and the different phase-shift angles between the carrier signals on the harmonic quality is investigated and optimal combination has been identified for all possible values of the reference voltage space vector having magnitude  $|V_s^*|$  and angle  $\psi_s$ . This information is then used to select the optimal combination of the switching sequences and the phase-shift during each sampling interval. Several combinations of the switching sequences and the phase-shift are used in one fundamental cycle. This would substantially increase the complexity and make it mere difficult to implement. Moreover, the Coupled Inductor (CI), that is used to suppress the circulating current, could saturate during the transition from one combination to another.

The enhanced modulator for the parallel interleaved 2L-VSCs is proposed in [44]. It uses two sets of the evenly phase-shifted carrier signals that are dy-

#### 1. Introduction

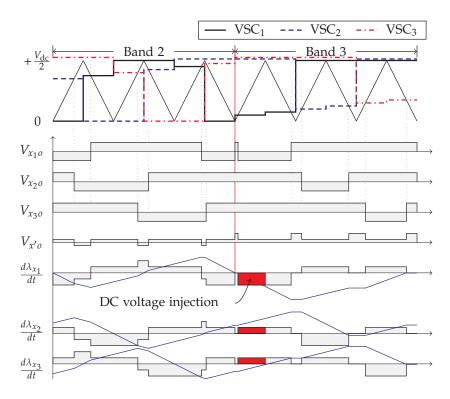

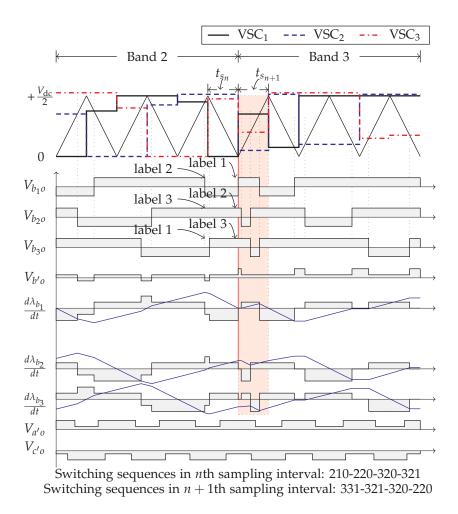

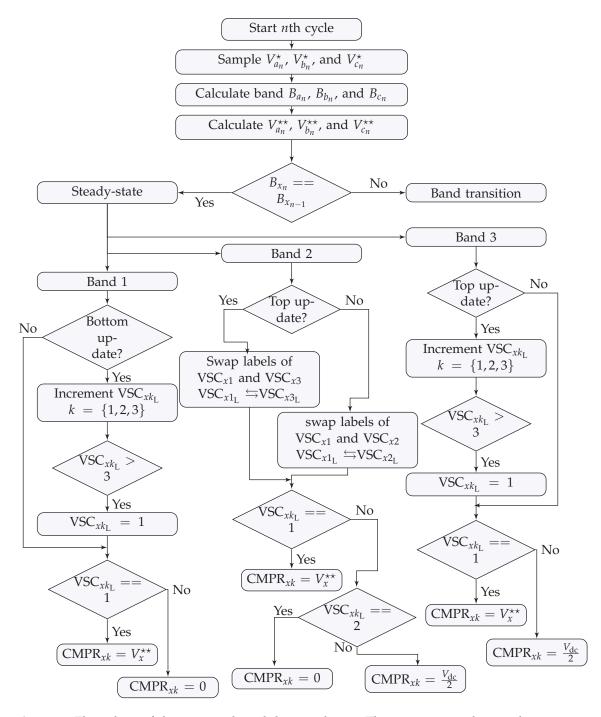

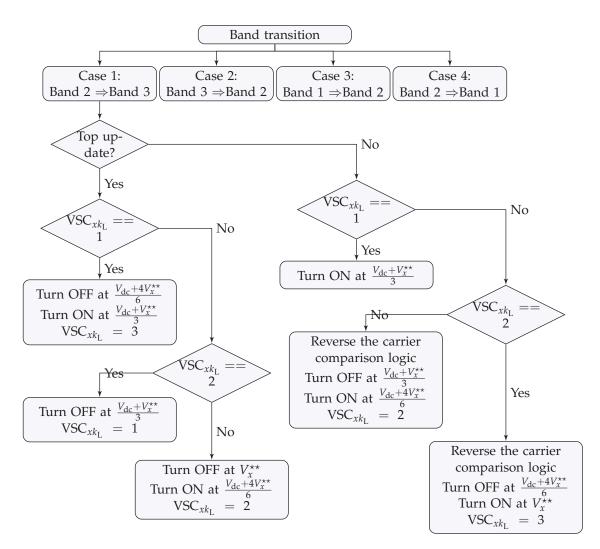

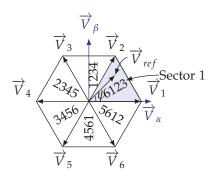

namically allocated using multiplexer, which makes it difficult to implement. Moreover, this implementation is equivalent to the Phase-Disposition (PD) PWM and CI saturation during the band transition could still happen. The PD carrier modulation scheme for the two parallel VSCs is presented in [45]. It uses a state machine to select the switching states. However, the complexity in this case increases with the increase in the number of parallel VSCs. The strategy to avoid the CI saturation during the transition from the positive value of the command reference signal to the negative value and vice-versa has been proposed for the two parallel VSCs. However, it does not ensure volt-sec balance to synthesize the reference space voltage vector during the band transition and introduces a disturbance in the line-to-line voltage of the three-phase system, which is highly undesirable. A PWM scheme overcome this problem has been presented in this thesis.

The interleaving of the carrier signals improve the harmonic performance. However, it is important to evaluate the reduction achieved in the value of the harmonic filter components to quantify the advantages of the carrier interleaving. The reduction in the value of the line filter inductor for the active power filter application has been investigated in [15] and it is shown that 70% reduction can be achieved with two parallel interleaved VSCs. Another study [39] shows 60% reduction in the weight of the magnetic component for the variable speed drives, considering the DO-160E Electro-Magnetic Interference (EMI) limits as a design constraints. The reduction in the weight of the EMI filters for the variable speed motor drive application has been also investigated in [46]. However, in most grid-connected applications, the impact of the interleaving on the harmonic filter components is so far not reported and it is investigated in this thesis.

### *Circulating Current:*

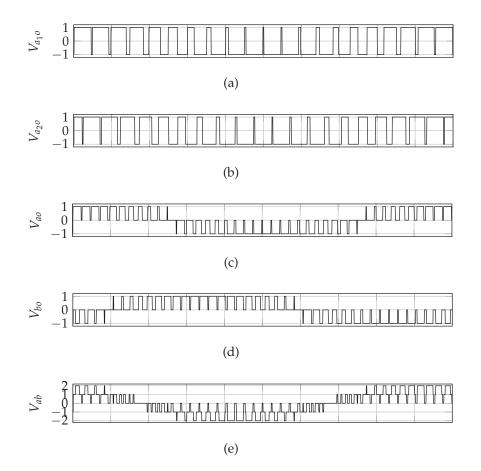

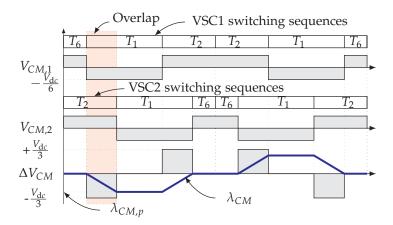

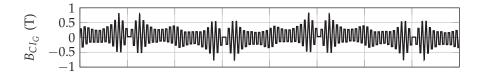

When VSCs are connected in parallel, the circulating current flows between the VSCs due to the control asymmetry and the impedance mismatch. When the carriers are interleaved, the switched output voltages of the interleaved parallel legs are phase shifted. As a result, the instantaneous potential difference exists, as shown in Fig. 3. This instantaneous potential difference further increase the circulating current, which would result in increased losses and unnecessary over-sizing of the components present in the circulating current path. Therefore, the circulating current should be suppressed to realize the full potential of the interleaved carriers in parallel connected VSCs.

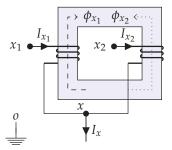

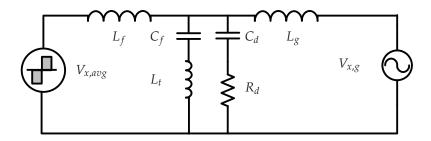

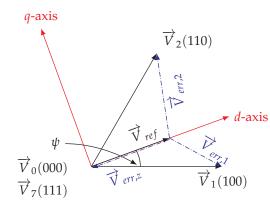

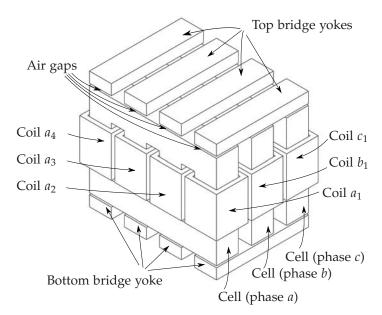

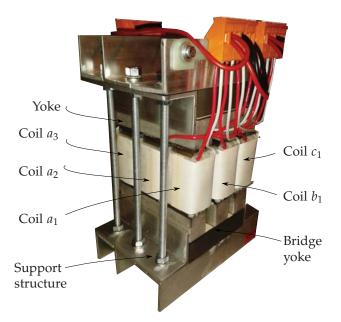

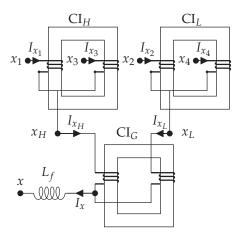

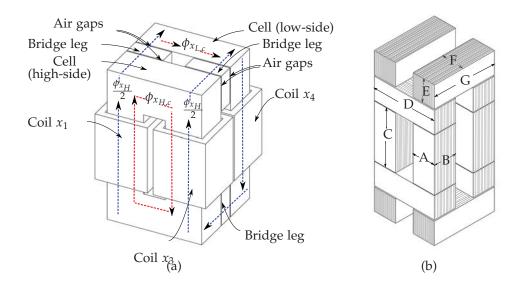

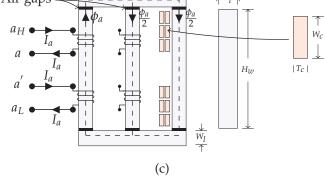

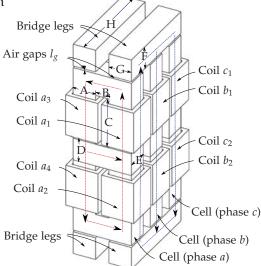

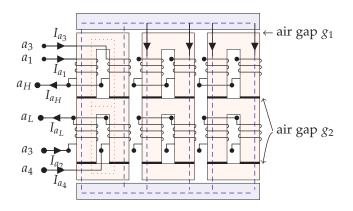

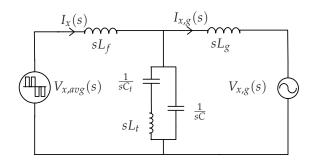

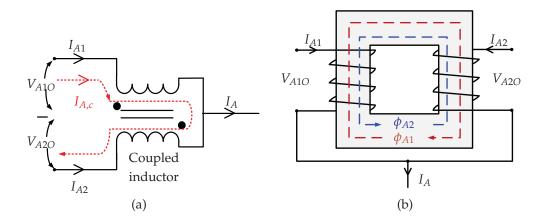

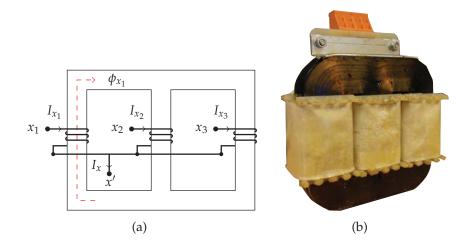

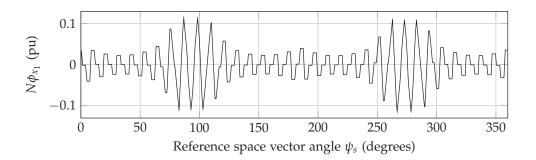

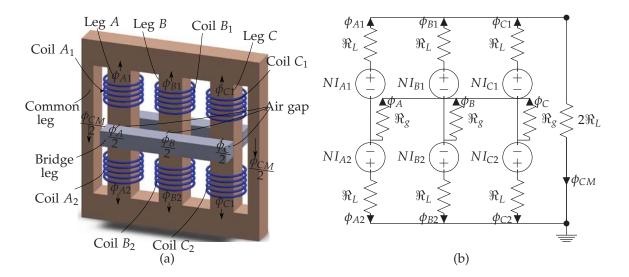

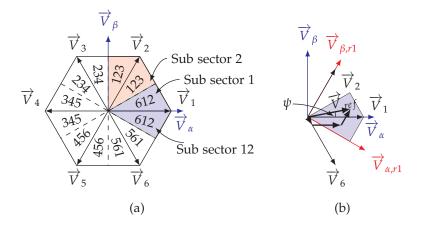

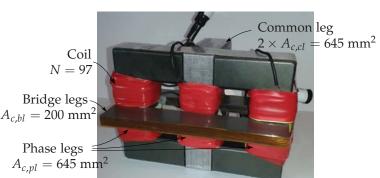

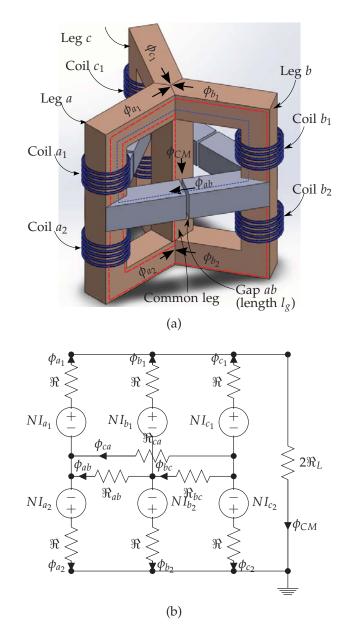

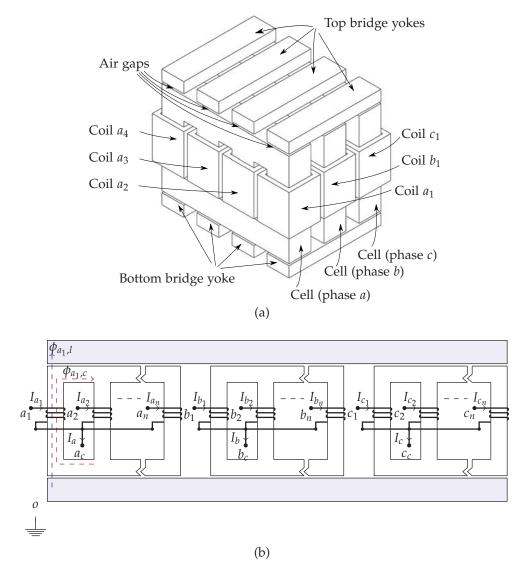

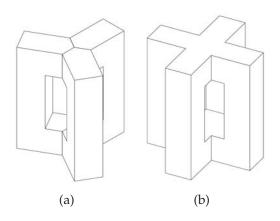

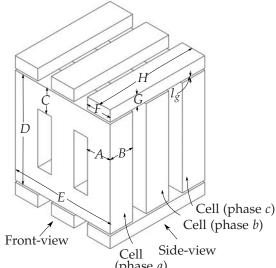

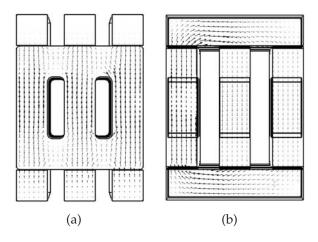

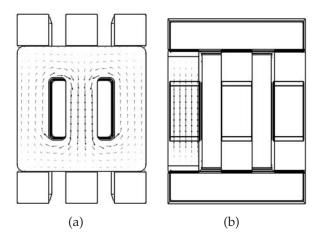

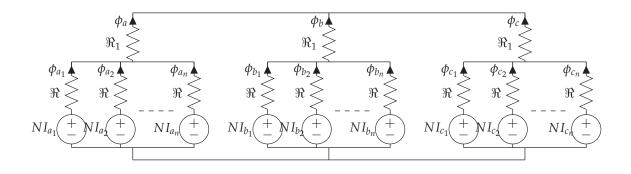

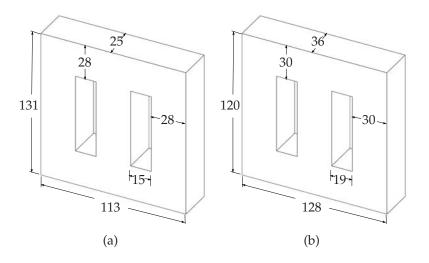

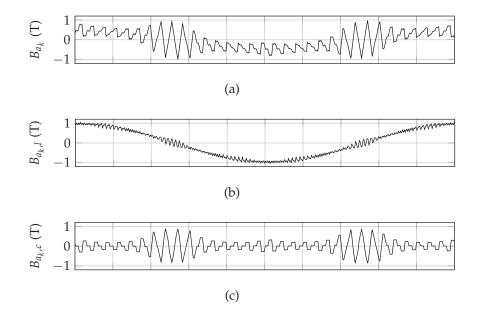

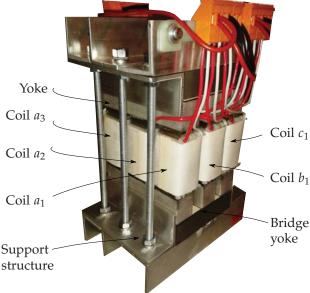

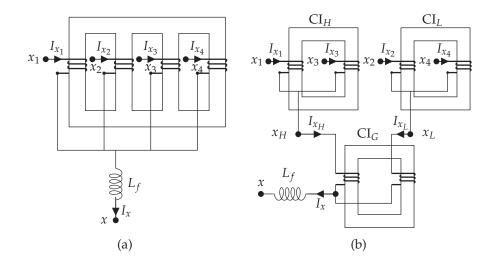

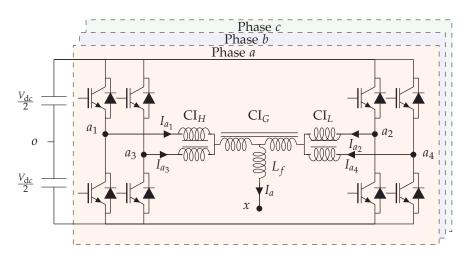

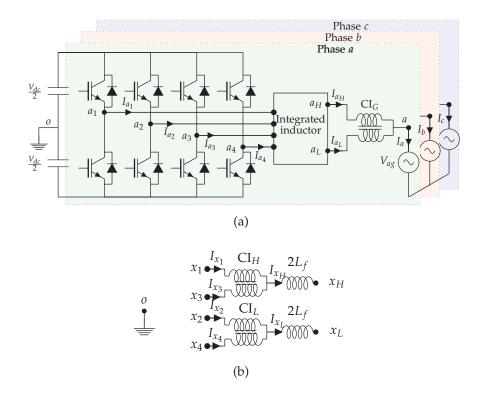

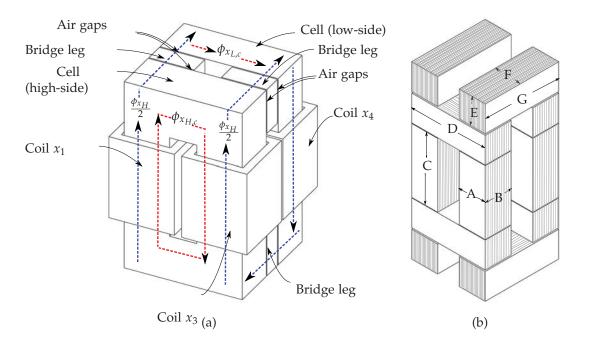

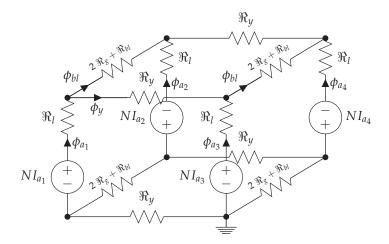

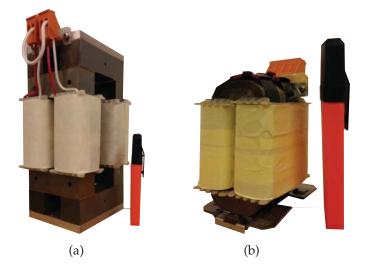

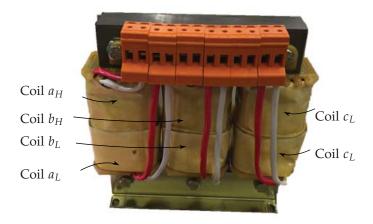

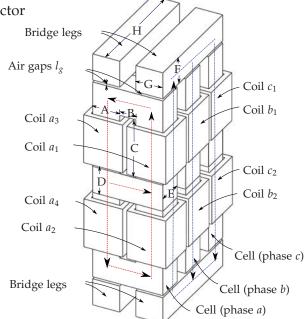

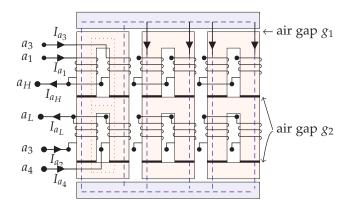

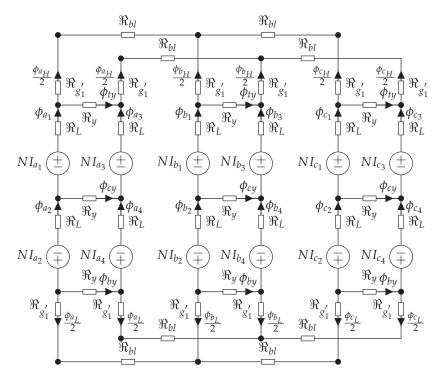

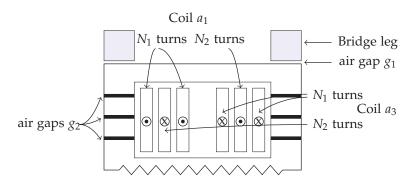

The use of the CI to suppress the circulating current is proposed in [34, 35, 47, 48] (referred to as a interphase reactor in [34]) and also shown in Fig. 1. The physical structure of the CI is shown in Fig. 4. The subscript *x* represents the phases *a*, *b*, and *c* ( $x = \{a, b, c\}$ ). The core is made up of two limbs which are magnetically coupled to each other using the top and the bottom yokes. Both the limbs carry coils with the *N* number of turns and

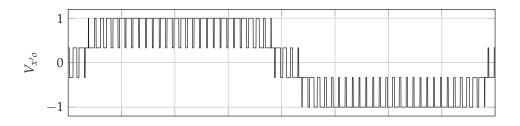

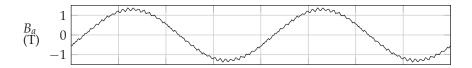

**Fig. 3:** Difference of the switched output voltages of the parallel legs. The voltage waveforms are normalized to  $V_{dc}/2$ .

**Fig. 4:** Physical arrangement of the coupled inductor. Subscript *x* represents the phases *a*, *b*, and *c*.

the coils are wound in the same direction. The starting terminals of both the coils are connected to the output of the respective VSC legs  $x_1$  and  $x_2$  and other terminals of both of the coils are connected together to form common connection point x, as shown in Fig. 4. The voltage across the coils are given as

$$V_{x_1x} = R_{CI}Ix_1 + L_s \frac{dI_{x_1}}{dt} - L_m \frac{dI_{x_2}}{dt}$$

(1a)

$$V_{x_2x} = R_{CI}Ix_2 + L_s \frac{dI_{x_2}}{dt} - L_m \frac{dI_{x_1}}{dt}$$

(1b)

where  $L_s$  is the self-inductance of the coil,  $L_m$  is the mutual inductance between the coils  $x_1$  and  $x_2$ , and  $R_{CI}$  is the resistance of the coil. The mutual inductance can be represented as  $L_m = kL_s$  ( $0 \le k \le 1$ ). Using (1), the difference of the pole voltages of the corresponding phase is given as

$$V_{x_1o} - V_{x_2o} = R_{CI}(I_{x_1} - I_{x_2}) + (L_s + L_m)\frac{d}{dt}(I_{x_1} - I_{x_2})$$

(2)

For the parallel VSCs, the leg current can be decomposed into two components

- Common current component ( $I_{\chi}/2$ , assuming equal current sharing).

- Circulating current component  $I_{x,c}$ .

therefore, the leg currents can be represented as

$$I_{x_1} = \frac{I_x}{2} + I_{x,c} \text{ and } I_{x_2} = \frac{I_x}{2} - I_{x,c}$$

(3)

#### 1. Introduction

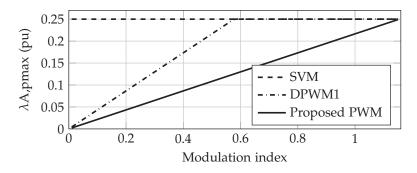

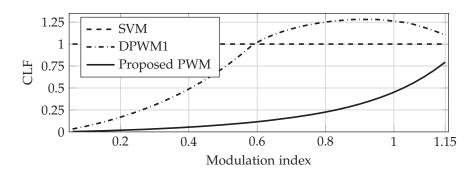

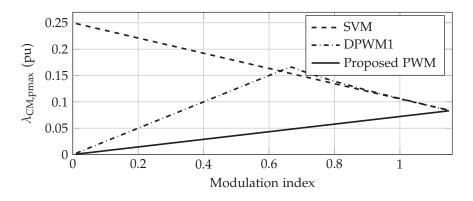

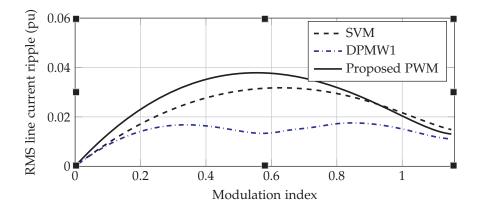

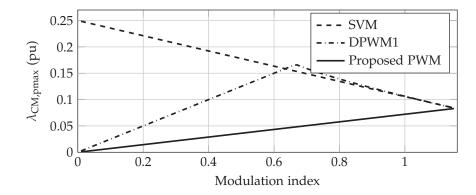

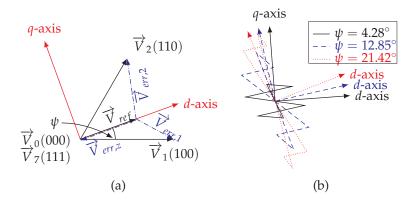

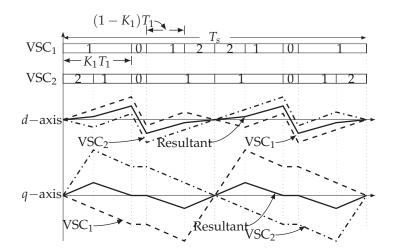

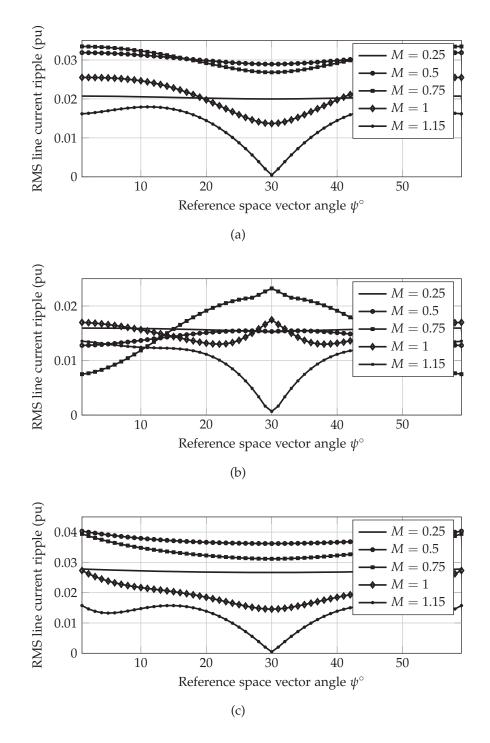

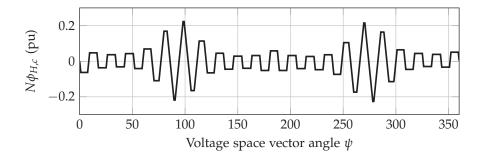

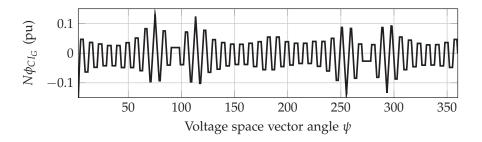

obtaining  $I_{x,c}$  from (3) and substituting in (2) yields