Aalborg Universitet

# Estimation of a 10 Gb/s 5G Receiver's Performance and Power Evolution Towards 2030

Lauridsen, Mads; Mogensen, Preben Elgaard; Sørensen, Troels Bundgaard

Published in: Vehicular Technology Conference, 2015 IEEE 82nd

DOI (link to publication from Publisher): 10.1109/VTCFall.2015.7390933

Publication date: 2015

**Document Version** Peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Lauridsen, M., Mogensen, P. E., & Sørensen, T. B. (2015). Estimation of a 10 Gb/s 5G Receiver's Performance and Power Evolution Towards 2030. In Vehicular Technology Conference, 2015 IEEE 82nd (pp. 1-5). IEEE. (IEEE VTS Vehicular Technology Conference Proceedings, Vol. 82). DOI: 10.1109/VTCFall.2015.7390933

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- ? Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

? You may not further distribute the material or use it for any profit-making activity or commercial gain

? You may freely distribute the URL identifying the publication in the public portal ?

Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# Estimation of a 10 Gb/s 5G Receiver's Performance and Power Evolution Towards 2030

Mads Lauridsen, Preben Mogensen, Troels B. Sørensen

Wireless Communication Networks Section, Department of Electronic Systems, Aalborg University, Denmark

{ml,pm,tbs}@es.aau.dk

Abstract-The 5G vision of 10 Gb/s leads to performance and power consumption challenges in the mobile terminal receiver because 10 Gb/s requires 400 MHz bandwidth, faster baseband processing, and an increased number of component carriers and MIMO streams. The contribution of this paper is to estimate the impact from these physical layer requirements to the power consumption of main receiver components, including LNA, ADC and baseband processor with Turbo decoding, in a Direct Conversion Architecture. The estimate of power consumption results from a comprehensive survey of component performance evolution, and extrapolation hereof to estimate trends, and main challenges, towards 2030. According to our results, in 2020 the receiver power consumption exceeds 3 W, and is thus a challenge to be addressed. Assuming the performance evolution continues as observed in this work, the 5G receiver will be on par with the current LTE implementations in 2027 and thus consume less than 0.8 W.

# I. INTRODUCTION

Currently industry and academia are working on concepts for a future fifth generation (5G) system, which can support the expected traffic increase in 2020 and beyond. Many of the 5G research projects target 10 Gb/s peak data rate in uplink and downlink. One example is the concept [1] we examine in this paper. However, it has not been analysed from a performance and power consumption perspective, where the latter is a 5G Key Performance Indicator [1], whether a mobile terminal in 2020 can handle a data rate 100 times higher than the commonly used LTE category 3 (supporting 100 Mb/s) [2].

In order to obtain 10 Gb/s it is necessary to increase the bandwidth, the modulation order, and the number of spatial MIMO streams, for example:

$$R_{5G} = \mathbf{BW} \cdot N_{\text{streams}} \cdot M \cdot \alpha \qquad [b/s]$$

= 400 MHz \cdot 4 \cdot 8 b \cdot 0.8 \approx 10.2 Gb/s (1)

where  $R_{5G}$  is the data rate [b/s], BW is the total bandwidth [MHz],  $N_{\text{streams}}$  is the number of spatial streams, M is the number of bits in the modulated symbol [b] (here 256QAM), and  $\alpha$  is the assumed overhead corresponding to LTE [2]. According to [1] 4x4 MIMO is the 5G baseline configuration.

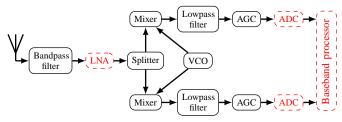

The increased requirements to bandwidth, modulation order, number of spatial streams and possible use of Carrier Aggregation (CA) will affect multiple components in a receiver. One commonly used receiver design is the Direct Conversion Architecture (DCA) [3] illustrated in Fig. 1 which due to the direct conversion to baseband consumes less power and consists of less components as compared to the superheterodyne receiver. The contribution of this paper is the comprehensive survey of the DCA main components' performance evolution and estimation of their power consumption towards 2030. This approach has not previously been applied and thus provides

Fig. 1. Block diagram of a Direct Conversion Architecture receiver.

valuable insight into what can be expected in terms of a 10 Gb/s 5G mobile terminal receiver's battery life. The examined components are the Low Noise Amplifier (LNA), the Analog-to-Digital Converter (ADC), and the baseband processor as indicated with dashed red in Fig. 1.

In the following sections the evolution of relevant performance parameters for each component is analysed after which the total power consumption of a 5G receiver is estimated. Finally a discussion with suggested future improvements is provided together with the conclusion in sec. VI and VII.

# II. ANALOG RADIO FREQUENCY EVOLUTION

The analog Radio Frequency (RF) Front End of a receiver is often based on a single chip implemented in CMOS. In this study it is therefore assumed that the performance of the LNA, mixer and other active components evolve at the same pace because they change CMOS technology node concurrently. Two existing power models also estimate that the power consumption of the LNA and mixer only differ 5-17% [4, 5]. There are a few LNA performance evolution studies available in literature and therefore it is selected as the RF Front End component in this work. In [6] the authors have examined about 30 papers published between 2004 and 2013, but only 2005 to 2011 contain more than one sample per year. Another previous work is the LNA roadmap [7] from 2001, which predicts a Figure-of-Merit (FoM) based on CMOS technology node evolution from 130 to 22 nm, but without details on power consumption. Therefore this paper includes our new literature study using 115 papers from 1991 to 2014, in total covering 145 LNA designs. Details are available in [8].

Our study shows that in 20 years the CMOS technology node and supply voltage has decreased a factor 10 and 4, respectively. This is less than what is estimated by Moore's law and [7, 9], but since most of the papers are made by academia the fabrication costs, which are inverse proportional to the CMOS technology node, may be one reason for the observed slower technological development.

The surveyed LNAs are either narrow- or wideband, but a common observation is that the maximum supported frequency

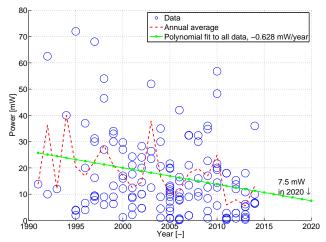

Fig. 2. LNA power consumption evolution.

has increased to 10-20 GHz, while most designs focus on cellular and WiFi bands in the region 1-5 GHz. The improvement clearly depends on application demand and thus the support for the centimeter-waves up to 30 GHz [1] is expected to emerge when mobile terminal manufacturers start to request it.

Our study in [8] shows that the Noise Figure has reduced about 1 dB the last 20 years. This corresponds well with the decreasing cellular requirements going from < 2 dB in GSM to < 3 dB in WCDMA and < 5 dB in LTE [10, 11]. The advanced receivers and higher order modulation of 5G may reverse the trend, but requirements are not yet defined.

The study also shows that the LNA gain has remained almost constant. One reason is that even though a high gain can reduce the noise, it may also result in that an interfering signal desensitizes the receiver. Furthermore, it may lead to increased linearity requirements in the subsequent components.

Finally the study shows that the intermodulation performance, specifically the third-order Intercept Point (IP3) is in the range -10 to 0 dBm. Because 5G is expected to apply Time Division Duplexing the IP3 requirements are relaxed [1].

The power consumption for the surveyed LNAs is illustrated in Fig. 2. The trend line shows how the average power consumption has been halved in 20 years. A larger reduction was expected because CMOS technology node and supply voltage have also decreased. The study however shows that the physical area has also decreased to 1/4 and thus some of the degrees of freedom have been used on minimization of area instead of power. Using the trend line for prediction the average power consumption in 2020 and 2030 is estimated to be 7.5 mW and 1.2 mW respectively.

To summarize, the LNAs power consumption and area have improved since the early nineties, while the Noise Figure, gain and IP3 have not changed significantly. We estimate that with the current evolution, LNAs can support 5G in 2020, but work is needed to support the 5-30 GHz carrier frequencies.

# III. ADC EVOLUTION

Using the Direct Conversion Architecture of Fig. 1 the next step after down-conversion to baseband is to digitize the signal. This task is performed by the ADC, which according to (1) is challenged by increased bandwidth and modulation order. Furthermore the number of ADCs will increase with the number of RF chains used for CA and MIMO.

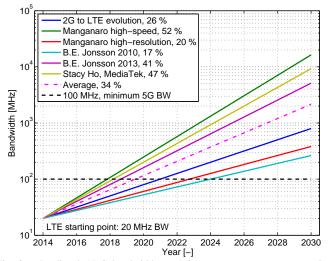

Fig. 3. Predicted ADC bandwidth assuming constant power consumption and 12 ENOB as in LTE.

ADC performance has been studied extensively, for example by Murmann, who covers 400 conference papers from 1997 to 2014 [12], and by Jonsson, who covers 1700 publications from 1974 to 2012 [13]. However, as a starting point note that in about 20 years the cellular standards, and the related mobile terminals, have evolved from using 200 kHz in GSM to 20 MHz in LTE i.e. an annual growth rate (AGR) of 26 %/year. The AGR is used as a metric in this work because in literature authors often provide an estimated improvement either in percent, absolute value, or dB over a certain period. Using AGR thus makes for a simple comparison, averaging, and scaling towards 2030. Manganaro has estimated the energy efficiency improvement [14], using the data of [12]. He estimates high speed ADCs with a bandwidth  $\geq 100$  MHz improve 52 %/year, while high resolution ADCs with a Signal-to-Noiseplus-Distortion Ratio (SNDR) ≥75 dB improve 20%/year.

In 2010 Jonsson conservatively estimated that in 2020 the sampling rate would have increased less than 5 times i.e. 17%/year [15]. However in recent work [13] he estimates the thermal FoM, defined in [13, Eq. 11.1], doubles every 2 years i.e. 41%/year. Ho from MediaTek has similarly predicted [16] that the Schreier FoM, defined as [14, Eq. 2.12]

$$FOM_{S} = SNDR + 10\log_{10} (BW/P)$$

(2)

improves 10 dB from 2014 to 2020 i.e. 47 %/year.

Assuming that the improvements are only used to increase the bandwidth and thus keeping the Effective Number of Bits (ENOB) and power consumption fixed, the bandwidth will increase as illustrated in Fig. 3 provided that the starting point of the prediction is a standard 20 MHz LTE receiver. The average improvement is 34 %/year and using this rate, 100 MHz can be supported in 2020 with the same power consumption and ENOB. If a larger bandwidth is needed the power consumption will increase and/or ENOB decrease.

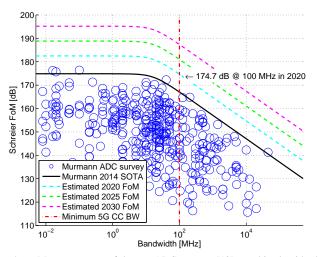

By applying the improvement of 34 %/year the future ADC performance is estimated by extending the Schreier FoM in (2) using Murmann's state of the art (SOTA) line illustrated in Fig. 4. Technical limitations induce that some combinations of power consumption, bandwidth and ENOB are not feasible, but in general the FoM<sub>S</sub> provides good insight to ADC evolution.

The current FoM<sub>S</sub> for a 100 MHz ADC with 12 ENOB is  $\approx$ 167 dB according to Fig. 4. Re-arranging (2) and noting

Fig. 4. Murmann state-of-the-art ADC survey [12] combined with the predicted Schreier FOM improvement in figure 3.

that SNDR =  $6.02 \cdot \text{ENOB} + 1.76 \text{ dB}$  the power consumption is estimated to be 50 mW. In 2020 the FOM<sub>S@100 MHz,2020</sub> is estimated to be 174.7 dB, resulting in P<sub>2020</sub> (100 MHz) =8.6 mW for an ADC with the same bandwidth and ENOB.

Murmann's SOTA line has a slope of -10 dB/decade for bandwidths above 5 MHz and therefore the power consumption as a function of bandwidth in 2020 is:

$$P_{2020} (BW) = \frac{BW}{10^{(FOM_{S@100 \text{ MHz},2020} - \text{SNDR} - 10 \log_{10}(\frac{BW}{100 \text{ MHz}}))/10}}$$

$$= P_{2020} (100 \text{ MHz}) \cdot \left(\frac{BW}{100 \text{ MHz}}\right)^2 [W] \quad (3)$$

To conclude it was observed that ADCs in 2020 can support 100 MHz of bandwidth with power consumption and ENOB similar to LTE in 2014. However, using 200 or 400 MHz ADCs will result in 4 and 16 times higher power consumption according to (3), respectively.

#### IV. BASEBAND PROCESSING EVOLUTION

The baseband processing requirements for 5G are significantly higher than for LTE because the data rate increases 33-100 times, from 100 Mb/s-300 Mb/s depending on LTE category to 10 Gb/s, and the bandwidth increases 20 times, from 20 MHz to 400 MHz [1, 2]. The latter results in more complex fast fourier transformation (FFT), channel estimation and equalization [2] while also affecting the envisioned use of interference cancellation receivers [1].

In [8] the power consumption of 6 LTE smartphones launched between May 2012 and September 2014 were examined, and it was noted how the power consumption decreases with each new generation of chipset and CMOS technology node. This can be related to Moore's observations, often referred to as Moore's law, stating chip area will be reduced by half in 2 years. Furthermore, his colleague Gene noted that Moore's law will also lead to the power consumption for the same performance to be halved every 18 months [17]. However, the International Technology Roadmap for Semiconductors has noted in their latest roadmap towards 2028 [9] that the transistor gate length will only decrease 0.7 times every fourth year instead of every second, and thus reducing the pace of Moore's and Gene's laws. Assuming this trend is valid we

TABLE I. LTE TURBO DECODERS. EFFICIENCY IS SCALED 0.79/YEAR.

| Reference                            | [18] | [19] | [20] | [21]  | [22] | [23]  | [24] | [24]  |

|--------------------------------------|------|------|------|-------|------|-------|------|-------|

| Publication year                     | 2011 | 2011 | 2011 | 2011  | 2013 | 2013  | 2014 | 2014  |

| Data rate [Mb/s]                     | 390  | 1400 | 1280 | 75    | 1013 | 292   | 301  | 2274  |

| Iterations                           | 5.5  | 8    | 6    | 6     | 5.5  | 8     | 8    | 8     |

| Decoding efficiency [nJ/b/iteration] | 0.37 | 0.12 | 0.11 | 0.658 | 0.17 | 0.078 | 0.11 | 0.079 |

| Power @ time of publication [mW]     | 794  | 1344 | 844  | 296   | 947  | 182   | 265  | 1437  |

| Power @ 10 Gb/s in 2020 [mW]         | 2543 | 1199 | 824  | 4936  | 1855 | 1238  | 2199 | 1579  |

|  | TABLE II. | 20 MHz LTE BASEBAND PROCESSORS. |

|--|-----------|---------------------------------|

|--|-----------|---------------------------------|

| References                   | [25] | [26] | [27] | Average |

|------------------------------|------|------|------|---------|

| Publication year             | 2014 | 2014 | 2013 | 2014    |

| Power @ 20 MHz in 2014 [mW]  | 480  | 576  | 517  | 524     |

| Power @ 400 MHz in 2020 [mW] | 2400 | 2880 | 2583 | 2621    |

modify Gene's law to estimate the baseband processing power consumption for the same performance is halved every 36 months. Therefore the modified Gene's law AGR is 0.79/year.

The baseband processing improvement estimate is useful because the Turbo decoding complexity, and thus power consumption, increases linearly with data rate while FFT, channel estimation and equalization complexity increases linearly with the bandwidth [2]. This observation is valid for LTE, but because the studied 5G concept [1] also applies OFDM and Turbo decoding, the same dependency is expected.

Table I provides an overview of recent LTE Turbo decoder articles. When the decoding efficiency is scaled according to the modified Gene's law of 0.79/year and the data rate is increased to 10 Gb/s the 8 references are estimated to consume  $\approx$ 2050 mW on average in 2020. Similarly Table II provides an overview of 3 recently published baseband processors. The power consumption is scaled 20 times due to the increased bandwidth that affects multiple processes in the baseband processor. The average power consumption for a 20 MHz LTE baseband processor is seen to be  $\approx$ 500 mW, while a 400 MHz LTE baseband processor consumes  $\approx$ 2600 mW in 2020 when applying Gene's law for the improvement estimation.

To summarize it was observed that increasing the data rate to 10 Gb/s will increase the power consumption of the average Turbo decoder to more than 2 W. If the bandwidth, which is expected to increase to 400 MHz, is used as the scaling parameter the average baseband processor is estimated to consume 2.6 W. Thus no matter the scaling technique the baseband will consume a significant amount of power, limiting the battery life of a 5G mobile terminal.

## V. ESTIMATION OF RECEIVER POWER CONSUMPTION

The previous sections presented selected components' performance and power consumption evolution. In this section the observations are used to estimate the power consumption evolution from 2014 and towards 2030 of a 5G receiver, capable of 10 Gb/s by use of the parameters in (1). We assume the DCA receiver is used for 5G as it has low component count and can be adapted to multiple RF bands [3].

For comparison the power consumption of an LTE category 3 receiver in 2014 is estimated first. The LTE receiver uses a single 20 MHz carrier and 2x2 MIMO to obtain 100 Mb/s. It is assumed that the DCA receiver shown in Fig. 1 is used, and therefore a single receive chain per Component Carrier (CC) for CA and per MIMO stream, composed of a common LNA, a mixer for each I and Q branch, and a Voltage Controlled Oscillator (VCO). Based on [4, 5] it is assumed that the mixers

TABLE III.ESTIMATED RECEIVER POWER CONSUMPTION FOR 2X2MIMO, 20 MHz LTE and 4x4 MIMO, 400 MHz 5G.

| RAT                                                                                                  | LTE                         | 1                           | 5G                         |                            |                           |                             |                              |                            |

|------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------|----------------------------|----------------------------|---------------------------|-----------------------------|------------------------------|----------------------------|

| Year<br>Data rate [Mb/s]<br>Bandwidth [MHz]<br>Baseband power [mW]                                   | 2014<br>10<br>20<br>524     | 0                           |                            | 202<br>100<br>40<br>262    | 00                        |                             | 2030<br>10000<br>400<br>260  |                            |

| Single CC BW [MHz]<br>Number of CCs<br>Number of chains                                              | 20<br>1<br>2                | 20<br>1<br>2                | 100<br>4<br>16             | 200<br>2<br>8              | 400<br>1<br>4             | 100<br>4<br>16              | 200<br>2<br>8                | 400<br>1<br>4              |

| ADC FoM [dB]<br>Single ADC power [mW]<br>Number of ADCs<br>Total ADC power [mW]                      | 172.9<br>2.58<br>4<br>10.3  | 180.6<br>0.44<br>4<br>1.75  | 174.7<br>8.59<br>32<br>275 | 171.7<br>34.0<br>16<br>543 | 168.7<br>135<br>8<br>1080 | 187.4<br>0.46<br>32<br>14.8 | 184.4<br>1.82<br>16<br>29.2  | 181.4<br>7.26<br>8<br>58.0 |

| Single LNA power [mW]<br>Number of LNAs<br>Number of mixers<br>Number of VCOs<br>Total RF power [mW] | 11.3<br>2<br>4<br>1<br>78.9 | 7.50<br>2<br>4<br>1<br>52.5 | 16<br>32<br>4<br>390       | 7.5<br>8<br>16<br>2<br>195 | 0<br>4<br>8<br>1<br>97.5  | 16<br>32<br>4<br>63.6       | 1.22<br>8<br>16<br>2<br>31.8 | 4<br>8<br>1<br>15.9        |

| Total power [mW]                                                                                     | 613                         | 185                         | 3290                       | 3360                       | 3800                      | 338                         | 321                          | 334                        |

and VCOs will consume roughly the same power as the LNA, while the filters and the Automatic Gain Control (AGC) are assumed to have negligible power consumption.

By combining the estimates of sec. II, III, IV on RF, ADC, and baseband processor performance, the total power consumption of an LTE receiver in 2014 is estimated to be  $\approx 600 \text{ mW}$  as shown in Table III. This estimate is close to the measurements on commercial smartphones, assumed to use DCA receivers based on [3], given in [8] where 800 mW was measured, but including the in-active transmitter and other smartphone components (in standby) such as CPU and display which could not be separated in the empirical study.

The power consumption evolution of the receiver is estimated by applying the LNA power consumption trend line in Fig. 2, the ADC FoM prediction in Fig. 4, and the modified Gene's law of 0.79/year to scale the estimated baseband processor power consumption in Table II. The LTE receiver power consumption in 2020 is estimated to be 185 mW i.e. less than 1/3 of the 2014 level and thus a significant improvement in battery life is expected.

Assuming that a 5G receiver will apply the same architecture in terms of hardware layout, use of OFDM, and Turbo decoding, the power consumption is estimated using the same procedure as above, and the results are given in Table III. Note the bandwidth is increased 20 times affecting both the baseband processor and the number of CCs. To examine how the power consumption depends on ADC and RF combinations the estimation is made for 100, 200, and 400 MHz CCs.

The main power consumer in 2020 is the baseband processor consuming more than 2.6 W. This will harm the battery life and it may cause thermal issues in the mobile terminal [9]. However, applying Gene's law the baseband processor is estimated to consume less than 300 mW in 2030. Examining the 3 different suggestions for CC bandwidth the 200 MHz is a good trade-off because it has a low ADC power consumption, while also limiting the number of RF components. However using two 200 MHz ADCs in 2020 will consume more than 500 mW, which is a significant quantity.

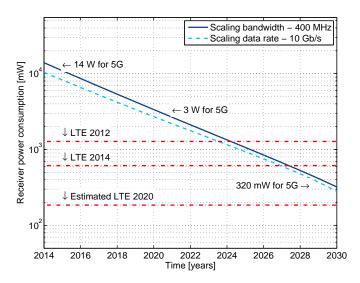

Using the aforementioned evolution parameters the 5G receiver power consumption towards 2030 is illustrated in Fig. 5. The solid blue line represents the scaling of the bandwidth to 400 MHz and also includes the ADC and RF power. For comparison the dashed, light blue line indicates the estimated

Fig. 5. Receiver power consumption evolution using 200 MHz CCs for 5G.

Turbo decoder power consumption based on Table I. The overall power consumption level is very similar and therefore we estimate that 5G receiver power consumption will first be on par with the LTE devices as of 2014 in 2027.

# VI. DISCUSSION

Based on the estimates presented in Fig. 5 it will be possible to obtain an acceptable battery life in the 5G mobile terminal, but not at the expected launch time in 2020. Unless processor and transistor technology designers generate a technology leap, it will be beneficial to consider how especially the baseband processing complexity and power consumption can be reduced. Currently, Turbo decoders are the favored choice for Forward Error Correction coding, but if another code could be developed with less energy consumed per decoded bit it would improve the situation. Therefore, it is time to consider whether other system resources like bandwidth and coverage can be traded for such improvements.

Another key research area is the reception of multiple CCs, which may cause coexistence issues in the RF Front End as LTE designers are already experiencing [3]. However, the use of multiple CCs is necessary in order to obtain sufficient amount of spectrum due to fragmentation. In addition the use of MIMO further complicates the RF Front End design, because the number of RF chains is the product of the number of MIMO branches and CCs as indicated in Table III.

The use of multiple CCs, and especially the individual carrier's bandwidth also affect ADC power consumption as discussed in sec. III. Even though a narrowband ADC is less power consuming than a wideband ADC with the same ENOB, the increased number of ADCs and RF Front Ends required to obtain an equivalent bandwidth may result in higher total power consumption. This can be seen when comparing the sum of ADC and RF power consumption for the 100 and 200 MHz CCs in Table III. Besides the impact on battery life it may also increase the physical area and component cost, but energy may be saved by combining multiple ADCs in one chip sharing voltage references, digital control, and bus connections.

Besides the increased power consumption, due to data rate and bandwidth, the cost and the power consumption of the processor's memory and buses will also increase because more

TABLE IV. POWER CONSUMPTION VARIATION DUE TO SCALING OF GENE'S LAW. ALL POWER CONSUMPTION VALUES ARE IN MW.

|         | Coefficient | Scaling Bandwidth<br>Year 2020 2025 2030 |      |      | Data rate |      |      |      |

|---------|-------------|------------------------------------------|------|------|-----------|------|------|------|

| scaling | per year    | Year                                     | 2020 | 2025 | 2030      | 2020 | 2025 | 2030 |

| -10 %   | 0.714       |                                          | 2090 | 493  | 108       | 1750 | 493  | 122  |

| 0%      | 0.794       |                                          | 3360 | 1070 | 321       | 2710 | 935  | 282  |

| 10 %    | 0.873       |                                          | 5530 | 2670 | 1300      | 4290 | 2130 | 1010 |

data must be stored in the buffers, while the buses must operate at a higher speed to transfer the data within the transceiver. However, one significant improvement is the more efficient HARQ design in 5G, which lowers the buffer space need [1].

Finally it is important to note that using scaling values 5-15 years into the future leads to large uncertainty. Table IV provides an overview of power consumption variation as a function of Gene's law. In 2025 the estimates are between 0.5 and 2.5 W depending on the coefficient, but it is worth noting that in 2020 the minimum estimate is still a very high 1.7 W.

# VII. CONCLUSION

Obtaining 10 Gb/s in 5G does not only complicate the Radio Access Technology design, but also the complexity, area, and power consumption of the mobile terminal. The reason is the decoding of the high data rate and use of 400 MHz bandwidth, 4x4 MIMO and Carrier Aggregation.

In this paper the performance and power evolution towards 2030 was studied for the Low Noise Amplifier, the Analogto-Digital Converter and the baseband processor using Turbo decoding. The estimated power consumption of a 10 Gb/s 5G receiver in 2020 is above 3 W of which more than 2 W is consumed by the baseband processor. This severely affects the battery life, which is a 5G Key Performance Indicator. The estimates further show that the 5G receiver will achieve a power consumption level similar to LTE as of 2014 in 2027. Finally the use of bandwidths above 200 MHz is challenging because the Analog-to-Digital Converter's power consumption is estimated to depend quadratically on the bandwidth.

We therefore propose that research targets to minimize Forward Error Correction coding complexity, and provide efficient support for increased bandwidth using Carrier Aggregation.

# ACKNOWLEDGEMENT

The work is partly funded by the Danish National Advanced Technology Foundation and the 4GMCT project. Thanks to Aarne Mämmelä for the useful discussions.

## References

- [1] P. Mogensen et al. "Centimeter-wave concept for 5G ultra-dense small cells". *VTC Spring, IEEE 79th.* 2014.

- [2] H. Holma and A. Toskala. *LTE for UMTS, OFDMA and SC-FDMA Based Radio Access.* Wiley & Sons, 2009.

- [3] J.M Lemenager et al. "Multimode Multiband Terminal Design Challenges". *HSPA+ Evolution to Release 12: Performance and Optimization*. Ed. by H. Holma, A. Toskala, and P. Tapia. Wiley & Sons, 2014.

- [4] Ye Li, B. Bakkaloglu, and C. Chakrabarti. "A System Level Energy Model and Energy-Quality Evaluation for Integrated Transceiver Front-Ends". VLSI Systems, IEEE Transactions on. Vol. 15. 1. 2007.

- [5] A. Didioui et al. "Power reconfigurable receiver model for energy-aware applications". *IEEE MWSCAS*. 2013.

- [6] G. Szczepkowski and R. Farrell. "Linearity vs. power consumption of CMOS LNAs in LTE systems". *ISSC* 2013, 24th IET. 2013.

- [7] R. Brederlow et al. "A mixed-signal design roadmap". Design Test of Computers, IEEE. Vol. 18. 6. 2001.

- [8] M. Lauridsen. "Studies on Mobile Terminal Energy Consumption for LTE and Future 5G". PhD thesis. Aalborg University, 2015.

- [9] International Technology Roadmap for Semiconductors. Process Integration, Devices, and Structures. 2013.

- [10] J. Rosa et al. "Adaptive CMOS analog circuits for 4G mobile terminals - Review and state-of-the-art survey". *Microelectronics Journal*. Vol. 40. 1. 2009.

- [11] G. Szczepkowski and R. Farrell. "Study of Linearity and Power Consumption Requirements of CMOS Low Noise Amplifiers in Context of LTE Systems and Beyond". *International Scholarly Research Notices -Electronics*. 2014.

- [12] B. Murmann. ADC Performance Survey 1997-2014. 2014. URL: http://www.stanford.edu/~murmann/ adcsurvey.html.

- [13] B.E. Jonsson. A/D-converter performance evolution v.1.1. 2013. URL: www.admsdesign.com.

- [14] Gabriele Manganaro. "Advanced Data Converters". *Cambridge University Press.* 2012.

- [15] B.E. Jonsson. "A survey of A/D-Converter performance evolution". 17th IEEE ICECS. 2010.

- [16] Stacy Ho. Email discussion. MediaTek USA Inc. 2014.

- [17] G. Frantz. "Digital signal processor trends". *Micro*, *IEEE*. Vol. 20. 6. 2000, pp. 52–59.

- [18] C. Studer et al. "Design and Implementation of a Parallel Turbo-Decoder ASIC for 3GPP-LTE". Solid-State Circuits, IEEE Journal of. Vol. 46. 1. 2011.

- [19] C. Wong and HC. Chang. "High-Efficiency Processing Schedule for Parallel Turbo Decoders Using QPP Interleaver". *Circuits and Systems, IEEE Transactions on*. Vol. 58. 6. 2011.

- [20] Y. Sun and J. Cavallaro. "Efficient hardware implementation of a highly-parallel 3GPP LTE/LTE-advance turbo decoder". *Integration, the VLSI Journal*. Vol. 44. 4. 2011.

- [21] V. Reis and I. Souza. "A 65Nm VLSI Implementation for the LTE Turbo Decoder". 24th SBCCI. ACM, 2011.

- [22] S. Belfanti et al. "A 1Gbps LTE-advanced turbo-decoder ASIC in 65nm CMOS". *VLSIC, Symposium on*. 2013.

- [23] C. Condo, M. Martina, and G. Masera. "VLSI Implementation of a Multi-Mode Turbo/LDPC Decoder Architecture". *Circuits and Systems, IEEE Transactions* on. Vol. 60. 6. 2013.

- [24] R. Shrestha and R.P. Paily. "High-Throughput Turbo Decoder With Parallel Architecture for LTE Wireless Communication Standards". *Circuits and Systems, IEEE Transactions on*. Vol. 61. 9. 2014.

- [25] B. Noethen et al. "10.7 A 105GOPS 36mm2 heterogeneous SDR MPSoC with energy-aware dynamic scheduling and iterative detection-decoding for 4G in 65nm CMOS". *ISSCC, IEEE*. 2014.

- [26] S. Huang et al. "A system-level design approach for SDR-based MPSoC in LTE baseband processing". *MWSCAS, IEEE 57th.* 2014.

- [27] Z. Zhu et al. "A 100 GOPS ASP based baseband processor for wireless communication". *DATE*. 2013.