## **Aalborg Universitet**

## Benchmarking of Phase Locked Loop based Synchronization Techniques for Grid-**Connected Inverter Systems**

Yang, Yongheng; Hadjidemetriou, Lenos; Blaabjerg, Frede; Kyriakides, Elias

Proceedings of the 2015 9th International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia)

DOI (link to publication from Publisher): 10.1109/ICPE.2015.7168077

Publication date: 2015

Document Version Early version, also known as pre-print

Link to publication from Aalborg University

Citation for published version (APA):

Yang, Y., Hadjidemetriou, L., Blaabjerg, F., & Kyriakides, E. (2015). Benchmarking of Phase Locked Loop based Synchronization Techniques for Grid-Connected Inverter Systems. In Proceedings of the 2015 9th International Conference on Power Electronics and ECCE Asia (ICPE-ECCE Asia) (pp. 2517-2524). [7168077] IEEE Press. DOI: 10.1109/ICPE.2015.7168077

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- ? Users may download and print one copy of any publication from the public portal for the purpose of private study or research. ? You may not further distribute the material or use it for any profit-making activity or commercial gain ? You may freely distribute the URL identifying the publication in the public portal ?

Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# Benchmarking of Phase Locked Loop based Synchronization Techniques for Grid-Connected Inverter Systems

Yongheng Yang\*<sup>1</sup>, *IEEE Member*, Lenos Hadjidemetriou<sup>†2</sup>, *IEEE Student Member*, Frede Blaabjerg\*<sup>3</sup>, *IEEE Fellow*, and Elias Kyriakides<sup>†4</sup>, *IEEE Senior Member*

\*Department of Energy Technology, Aalborg University, 9220 Aalborg, Denmark †Department of Electrical and Computer Engineering, University of Cyprus, 1678 Nicosia, Cyprus ¹yoy@et.aau.dk; ²hadjidemetriou.lenos@ucy.ac.cy; ³fbl@et.aau.dk; ⁴kyriakides@ieee.org

Abstract—Grid-connected renewables are increasingly developed in recent years, e.g. wind turbine systems and photovoltaic systems. Synchronization of the injected current with the grid is mandatory. However, grid disturbances like voltage sags, harmonics, and frequency deviations may occur during operation, becoming inevitable challenges to the synchronization of the grid-connected renewable energy systems. In order to ensure the quality of the power generation from the renewables, robust and reliable synchronization methods are in demand. Among the prior-art solutions, Phase Locked Loop (PLL) based synchronization methods have gained much popularity in grid-connected applications. However, an appropriate selection and thus a proper design of the selected PLL synchronization remain of interest in practice, especially for single-phase systems. Therefore, in this paper, a benchmarking of the main PLL synchronization methods for single-phase grid-connected inverter systems in terms of accuracy, dynamic response, harmonic immunity, etc., has been conducted. Experiments on a 1-kW single-phase gridconnected system, suffering from different grid disturbances, are performed for the benchmarking. The experimental results have verified the discussions.

Index Terms—Phase locked loop (PLL), synchronization, T/4 delay PLL, inverse park transform PLL, enhanced PLL (EPLL), second order generalized integrator PLL (SOGI-PLL), multi-harmonic decoupling cell PLL.

#### I. Introduction

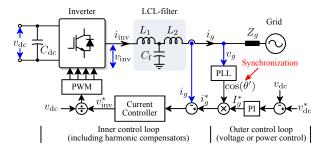

Power electronics technology has enabled an increasing integration of renewable energy into the grid [1]–[3], e.g. wind turbine and photovoltaic systems. However, due to the intermittency of renewable energy, it has also brought harmonic challenges to the grid [4]–[6], as a fluctuating power is continuously injected to the grid. Since the inner current controller of a typical two-cascaded control system [1], [4] is responsible for shaping the current (e.g., power quality issues) in such applications, efforts have to be devoted to the control of the feed-in grid current, which has to be synchronized with the grid voltage using a synchronization system. Fig. 1 demonstrates the significance of synchronization in the entire control of a single-phase system. As it can be seen in Fig. 1, the information provided by a synchronization is of ultimate

This work was under a SOLAR-ERA.NET transnational project [PV2.3 - PV2GRID] supported by the European Commission within the European Union's Seventh Framework Program (FP7/2007–2013).

Fig. 1. Overall control structure (dual-loop) of a single-phase grid-connected inverter system with an LCL-filter.

importance, and it is used at different levels of the entire control system, e.g. for a reference frame transformation (the  $\alpha\beta$ -stationary frame  $\rightarrow$  the dq-rotating frame).

In the literature, a vast of synchronization methods have been reported [4], [7]–[17], [29]. These prior-art synchronization methods can be categorized into a) mathematical analysis methods (e.g., grid synchronization based on the Discrete Fourier Transform - DFT) [16], [18]–[20] and b) Phase Locked Loop (PLL) based synchronization techniques. The first category are based on signal processing techniques, e.g. the DFT and Hilbert transform analysis, which are commonly implemented in a digital controller, and thus has a strict requirement of the sampling rate [4], [8], [21]. In contrast, a PLL synchronization method is a closed-loop system, which is widely used in the grid-connected systems [4], [12]. However, for single-phase applications, where only the grid voltage  $v_g$  is measured, it requires more dedications to the synchronization.

Advanced control strategies can thus be applied to an inverter system, while its performance significantly relies on the dynamics of the synchronization, as shown in Fig. 1. Both the mathematical analysis and the PLL based synchronization are able to provide accurate and fast information for the control in the case of a normal grid condition [8], [14], [18]. However, the grid voltage cannot always be maintained as "constant" in terms of amplitude, frequency, and phase, due to multiple eventualities like continuous connection and disconnection of loads and fault to ground [22], [23]. Together with the harmonics in the grid voltage (e.g., due to non-linear loads), a big

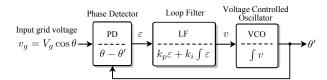

Fig. 2. Basic block diagram of a phase locked loop system for grid-connected inverter systems, where  ${\cal V}_q$  is the grid voltage amplitude.

obstacle for synchronization, especially for the Fourier based method [16], [24], has been imposed on. Thus, it calls for an advancement of these synchronization techniques in order to enhance the entire system performance, requiring a clear identification of the pros and cons of the synchronization methods. Alternatively, a benchmarking of the most commonly-employed PLL techniques could contribute to not only an enhancement of the PLLs but also a development of new PLLs. As a result, an advanced synchronization system will ensure a more reliable control of the injected current and thus a more reliable and stable operation of the entire grid-connected inverter system.

In light of the above issues, a benchmarking of several selected PLL based synchronization methods is conducted in this paper. Firstly, the basics of the single-phase PLL system are presented in  $\S$  II, including the small signal modelling and basic design considerations. Then,  $\S$  III gives a description of the selected PLL synchronization methods, including the T/4 Delay PLL, the Inverse Park Transform PLL (IPT-PLL), the Enhanced PLL (EPLL), the Second Order Generalized Integrator based PLL (SOGI-PLL), and the Multi-Harmonic Decoupling Cell based PLL (MHDC-PLL). Followingly, those synchronization techniques are benchmarked in terms of accuracy, dynamic response, harmonic immunity, and etc. by experimental tests in  $\S$  IV, where the grid suffers from various disturbances. A conclusion is then drawn.

#### II. BASICS OF SINGLE-PHASE PLL SYSTEMS

As it can be seen in Fig. 1, the PLL system plays a key role in the entire control loop of grid-connected inverter systems. Typically, a PLL system consists of a Phase Detector (PD), a Loop Filter (LF) which is performed by a Proportional Integrator (PI) controller, and a Voltage Controlled Oscillator (VCO). Fig. 2 represents the basic block diagrams of a PLL system that is widely utilized in grid-connected applications. Accordingly, the transfer function of the PLL system  $G_{\rm PLL}(s)$  can be described as,

$$G_{\text{PLL}}(s) = \frac{\theta'(s)}{\theta(s)} = \frac{k_p s + k_i}{s^2 + k_p s + k_i} \tag{1}$$

where  $\theta$  is the grid voltage phase,  $\theta'$  is the locked grid voltage phase,  $k_p$  and  $k_i$  are the proportional and integral gains of the PI controller (i.e., the LF).

It can be seen from (1) that the PLL system is a typical second order system [4]. Therefore, the damping ratio  $\xi$  and the undamped natural frequency  $\omega_n$  of (1) can be calculated by,

$$\xi = \frac{k_p}{2\omega_n}$$

, and  $\omega_n = \sqrt{k_i}$ .

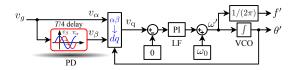

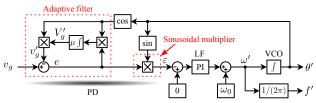

Fig. 3. Detailed structure of a phase locked loop system by introducing a quarter phase delay (T/4 Delay PLL), where  $\omega_0=2\pi f_0$  with  $f_0$  being the nominal grid frequency.

Subsequently, the settling time of the PLL system can be approximated as,

$$t_s = \frac{4.6}{\xi \omega_n} = \frac{9.2}{k_p} \tag{2}$$

which can be used to benchmark the transient performance of different PLL systems, and also can be taken as guidelines for tuning the LF parameters:

$$k_p = \frac{9.2}{t_s}$$

, and  $k_i = \left(\frac{k_p}{2\xi}\right)^2$  (3)

where  $\xi = \sqrt{2}/2$  is typically chosen for a satisfactory and optimal damping.

In the case that the control parameters of the LF (i.e.,  $k_p$  and  $k_i$ ) are set to be identical in different PLLs, the performance of the PLL synchronization methods will strongly rely on the configurations of the PD system. A sinusoidal multiplier is the most intuitive way to the implementation of a PD system, but it introduces double-frequency harmonics in the closed-loop system [13], which cannot be fully eliminated by the LF (i.e., the PI controller). Therefore, the task of advancing a PLL system is shifted to improve the detection of the phase error (i.e.,  $\varepsilon = \theta' - \theta$ ) using the input grid voltage  $v_g$  and feedback signals (e.g., the estimated phase  $\theta'$ ). The following demonstrates how the PD systems are constructed in the most commonly employed single-phase PLL techniques.

#### III. SELECTED PLL SYNCHRONIZATION METHODS

As previously discussed, a number of single-phase PLL based synchronization methods have been developed in the literature. In this section, the most popular PLL systems are presented, including their basic design guidelines.

#### A. T/4 Delay PLL

An alternative phase detection can be achieved with the aid of the Park transform  $(\alpha\beta \to dq)$ , where a virtual system  $(\beta$  variable) that is in-quadrature with the grid voltage  $v_g$   $(\alpha$  variable) is required in single-phase applications. Simply, a quarter delay of the input grid voltage is a possibility, being the T/4 Delay PLL, as it is shown in Fig. 3, where T is the known fundamental period of the input grid voltage  $v_g$ .

Specifically, on an assumption that the grid voltage is purely sinusoidal, i.e.,  $v_g(t) = V_g \cos(\theta) = V_g \cos(\omega t + \varphi_0)$  with  $\omega$  being the grid angular frequency and  $\varphi_0$  being the initial phase angle, applying the Park transform yields,

$$\mathbf{v}_{dq} = \overbrace{\begin{bmatrix} \cos(\theta') & \sin(\theta') \\ -\sin(\theta') & \cos(\theta') \end{bmatrix}}^{\mathbf{T}_{p}} \mathbf{v}_{\alpha\beta} \approx V_{g} \begin{bmatrix} 1 \\ \varepsilon \end{bmatrix}$$

(4)

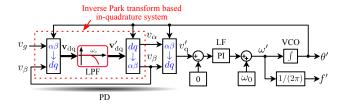

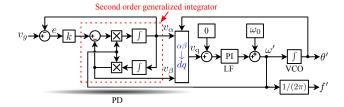

Fig. 4. Block diagram of the inverse park transform based phase locked loop (IPT-PLL).

where  $T_p$  is the Park transform matrix. Eq. (4) shows that the detected phase error  $\varepsilon$  (i.e.,  $v_q/V_g$ ) can be regulated by a PI controller so that the grid voltage phase  $\theta$  is locked as  $\theta'$  in the steady-state. In addition, the grid voltage amplitude  $V_g = v_{\rm d}$  and frequency  $f' = \omega'/(2\pi)$  can also be obtained according to (4) and Fig. 3, respectively.

In regards to the implementation of the T/4 Delay PLL, a fixed delay of a quarter period (i.e.,  $T/4=1/(4f_0)$  with  $f_0$  being the nominal grid frequency) is normally adopted for simplicity. As a result, the dependence of the grid voltage frequency  $f_0$  to create the virtual in-quadrature system makes the T/4 Delay PLL not very suitable for the single-phase applications, where the grid voltage is subjected to frequency variations [25]. Moreover, the background distortions will directly propagate to the LF when the input voltage is delayed for a quarter period. This becomes another big challenge to the T/4 Delay PLL.

#### B. Inverse Park Transform PLL (IPT-PLL)

Another possibility to detect the phase error seems to be a good one for single-phase systems, and it is based on the Inverse Park Transform (IPT,  $dq \rightarrow \alpha\beta$ ) [4]. Fig. 4 shows the block diagram of an IPT based PLL system (IPT-PLL). When compared to the T/4 Delay PLL, the IPT-PLL requires two additional Low Pass Filters (LPF), and thus certain harmonics in the grid voltage will not propagate to the LF, contributing to a good harmonic rejection. Thus, from the harmonic immunity point of view, the IPT-PLL is better than the T/4 Delay PLL.

According to Fig. 4, the PD structure of the IPT-PLL system can be described by the following:

$$\mathbf{v}_{\mathrm{dq}}(s) = \boldsymbol{T}_{p}(s) \begin{bmatrix} v_{g}(s) \\ v_{\beta}(s) \end{bmatrix}, \ \mathbf{v}'_{\mathrm{dq}}(s) = \boldsymbol{T}_{p}(s) \begin{bmatrix} v_{\alpha}(s) \\ v_{\beta}(s) \end{bmatrix}$$

(5)

and

$$\mathbf{v}'_{\mathrm{dq}}(s) = G_{\mathrm{LPF}}(s)\mathbf{v}_{\mathrm{dq}}(s) = \frac{\omega_c}{s + \omega_c}\mathbf{v}_{\mathrm{dq}}(s)$$

(6)

where  $T_p(s)$  is the *Laplace* form of  $T_p$  shown in (4), and  $G_{\text{LPF}}(s)$  is the transfer function of the first-order LPF with  $\omega_c$  being the corresponding cut-off angular frequency. Then, exploiting the Euler formula and the *Laplace* property for the frequency shifting yields [4],

$$\mathbf{v}_{\alpha\beta}(s) = \begin{bmatrix} v_{\alpha}(s) \\ v_{\beta}(s) \end{bmatrix} = \begin{bmatrix} \frac{\omega_c s}{s^2 + \omega_c s + \omega'^2} \\ \frac{\omega_c \omega'}{s^2 + \omega_c s + \omega'^2} \end{bmatrix} v_g(s) \tag{7}$$

which indicates that the performance of the IPT-PLL system is highly dependent on the LPF,  $G_{LPF}(s)$ .

Fig. 5. Enhanced phase locked loop (EPLL) system based on an adaptive filtering technique [9].

A design parameter of the IPT-PLL system can then be defined as  $k_{\rm ipt} = \omega_c/\omega'$ . In accordance to (7),  $v_q(s)$ -to $v_{\alpha}(s)$  and  $v_{q}(s)$ -to- $v_{\beta}(s)$  represent a second-order bandand low-pass filter, respectively. Consequently, the design parameter  $k_{\text{ipt}}$  should be equal to  $\sqrt{2}$  in order to ensure an optimal damping of the second-order filters in terms of good settling time and overshooting in the dynamics, and accordingly the cut-off frequency  $\omega_c$  of the LPF can be set. However, the design parameter  $k_{ipt}$ , may need to be tuned slightly in practice when considering the entire control system (e.g., computation delay effects). Nevertheless, the IPT PD system can ensure not only a proper deriving of the in-quadrature system  $(\mathbf{v}_{\alpha\beta})$  but also a filtering of the high-order harmonics of the grid voltage (i.e., since  $v_q(s)$ to- $v_{\beta}(s)$  behaves as a second-order LPF), resulting in a good harmonic immunity, which is in coincidence with the previous discussion.

#### C. Enhanced PLL (EPLL)

The basic ideas of the above two PLLs fall into the establishment of in-quadrature systems, thus enabling the Park transform to detect the phase error. Using adaptive filtering techniques is another way to the phase detection, as an adaptive filter is able to adjust the parameters automatically according to the error signal and a reference (e.g.,  $\cos(\theta')$ ) [4], [9]–[11]. The Enhanced PLL (EPLL), which was introduced in [9], is a typical representative of adaptive filtering based PLL systems. Similar principle has also been implemented in the control of the instantaneous power of a single-phase system [10].

Actually, the EPLL phase detection is achieved using an Adaptive Filter (AF) and a simple sinusoidal multiplier, as it is shown in Fig. 5, so that the EPLL can enhance the performance in contrast to a sinusoidal multiplier based PLL [8]. More specifically, the AF is used to estimate the input voltage  $v_g$  according to the detected phase error  $\varepsilon$  and the locked phase  $\theta'$  (in order to generate the filter reference  $\cos(\theta')$ ) by minimizing an objective function, e.g.,  $(v_g - v_g')^2/2$ . After a period, the frequency and phase of the EPLL will be free of oscillations [4].

As it can be observed in Fig. 5, the most important feature of an EPLL is that both the grid voltage amplitude  $V_g'$  and the phase  $\theta'$  of the input voltage  $v_g$  can be locked. According to Fig. 5, the estimated grid voltage amplitude  $V_a'$  can be expressed as,

$$\dot{V}_{q}' = \mu e \cos(\theta') \tag{8}$$

in which  $\mu$  is the control parameter and  $e=(v_g-v_g')$ . It is also implied in (8) that the dynamic response of the EPLL

Fig. 6. Second order generalized integrator based phase locked loop system (SOGI-PLL) [7].

system depends on the speed of the estimation process (i.e., the dynamics of the adaptive filtering mechanism are controlled by  $\mu$ ). Simply linearizing (8) results in,

$$\frac{V_g'(s)}{V_q(s)} = \frac{1}{\tau s + 1} \tag{9}$$

which represents a simple LPF with  $\tau=2/\mu$  being its time constant. The settling time of the AF can then be approximated as  $4\tau=8/\mu$  [8], [10]. Considering the delay induced by the LF, the EPLL will present slow dynamics, and thus it is not a good solution for the applications requiring fast responses.

#### D. Second Order Generalized Integrator PLL (SOGI-PLL)

Actually, the AF of an EPLL system is only using one adaptive weight [4], and it will take a transient period for the error signal e to come into the zero steady-state, as it has been discussed in the last paragraph. This happens only when both the frequency and the phase of the input grid voltage  $v_g$  and the estimated grid voltage  $v_g'$  are matched. That is to say, a zero steady-state tracking of the reference signal  $\cos(\theta')$  shown in Fig. 5 is achieved by the one-weight adaptive filter.

In order to further improve the performance, a second order adaptive notch filter with two adaptive weights can be a replacement of the AF in the EPLL system, and actually in that case the second order AF will act like a "generalized sinusoidal integrator". Fig. 6 shows the block diagrams of a Second Order Generalized Integrator based PLL (SOGI-PLL) system, which inherently incorporates both the sine and cosine blocks with the feedback of the detected angular frequency  $\omega'$  as the AF reference [4], [7]. Then, according to Fig. 6, the in-quadrature system of the SOGI-PLL can be described by,

$$\mathbf{v}_{\alpha\beta}(s) = \begin{bmatrix} v_{\alpha}(s) \\ v_{\beta}(s) \end{bmatrix} = \begin{bmatrix} \frac{k\omega's}{s^2 + k\omega's + \omega'^2} \\ \frac{k\omega'^2}{s^2 + k\omega's + \omega'^2} \end{bmatrix} v_g(s) \quad (10)$$

which are second-order systems with k being the control parameter of the SOGI based PD system.

For the second-order systems presented in (10), the control parameter k should be equal to  $\sqrt{2}$  so as to roughly achieve a good relationship between the settling time and the overshooting. Additionally, according to (10), the PD system of the SOGI-PLL exhibits like a band-pass filter (i.e.,  $v_g(s)$ -to- $v_\alpha(s)$ ) and a low-pass filter (i.e.,  $v_g(s)$ -to- $v_\beta(s)$ ), respectively, which is similar to that of the IPT-PLL shown in (7). Consequently, when the frequency of

the input grid voltage  $v_g$  is locked by the SOGI-PLL (i.e.,  $\omega' = \omega$ ),  $v_\alpha$  and  $v_\beta$  will be in-quadrature and also filtered, contributing to an improved phase detection associated by the Park transform. It can also be anticipated that the performance of the IPT-PLL and the SOGI-PLL will be similar if the control parameters (i.e.,  $k_{\rm ipt}$  and k) are designed appropriately. However, as it is shown in Fig. 6, the PD system of the SOGI-PLL has two feedback variables ( $\omega'$  for the in-quadrature filtering system and  $\theta'$  for the Park transform). Thus, the implementation of the SOGI-PLL is more complicated than the other three PLLs. However, it should be noted that, seen from the harmonic rejection capability, the SOGI-PLL system is a good candidate for single-phase applications in contrast with the other three.

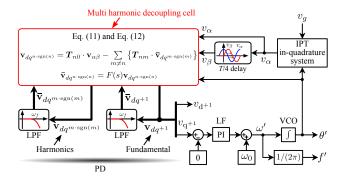

#### E. Multi-Harmonic Decoupling Cell PLL (MHDC-PLL)

Although the SOGI-PLL system can minimizes the impacts from the grid voltage background distortions to some extent, inaccuracy may still occur in the case of a very weak grid, e.g. containing both low- and high-order harmonics [14], [26]. In light of this issue, the Multi-Harmonic Decoupling Cell PLL (MHDC-PLL) was introduced in [14] for single-phase applications. The structure of the MHDC-PLL system is depicted in Fig. 7, which shows that the in-quadrature system  $\mathbf{v}_{\alpha\beta}$  is a combination of a T/4 Delay system and an IPT in-quadrature system (Figs. 3 and 4). By this mean, the MHDC-PLL system can maintain the strength of an IPT in-quadrature system to attenuate the high-order harmonics of the input grid voltage, but it also inherits the delay effect of a T/4Delay system that is sensitive to frequency variations. Nonetheless, the MHDC-PLL is focused on a mitigation of the harmonic impacts on the output locked phase  $\theta'$  and frequency f' with a relatively high performance in terms of fast dynamic responses. As a result, the grid current control can be enhanced.

It can be observed in Fig. 7 that the MHDC is designed in multiple synchronous reference frames  $(\alpha\beta\to dq^h)$  in order to cancel out the low-order harmonic effects, and i.e., the MHDC is using multiple Park transforms to dynamically extract the harmonics. Therefore, the rotational speed should be  $h\omega'$  for the Park transform (i.e.,  $\theta^h=h\omega't$ ), where h is the harmonic order. The harmonic cancellation of the MHDC can be illustrated in details as following.

If the grid voltage  $v_g$  is distorted by low-order harmonics, and thus the in-quadrature grid voltages  $\mathbf{v}_{\alpha\beta}$  will inevitably contain certain low-order harmonics that are not (or cannot be) filtered out by the IPT in-quadrature system. Without loss of generality,  $\mathbf{v}_{\alpha\beta}$  can be expressed as a summation of the fundamental component  $(\mathbf{v}_{\alpha\beta}^1)$  and each harmonic component  $(\mathbf{v}_{\alpha\beta}^h)$ . Thus, by transforming  $\mathbf{v}_{\alpha\beta}$  in any synchronous rotating frame (i.e,  $dq^{n\cdot\mathrm{sgn}(n)}$ -frame rotating with the rotational speed of  $n\cdot\mathrm{sgn}(n)\omega'$ ), an oscillation-free term will appear due to the corresponding voltage component, and several oscillation terms will appear due to the cross-coupling effect of the rest voltage components. Therefore, the MHDC system can dynamically and accurately estimate each voltage component in

Fig. 7. Multi harmonic decoupling cell based phase locked loop system (MHDC-PLL) [14].

the corresponding  $dq^{n \cdot \text{sgn}(n)}$ —frame by subtracting all the existing oscillation terms as,

$$\mathbf{v}_{\mathrm{dq}^{n\cdot\mathrm{sgn}(n)}} = \boldsymbol{T}_{n0}\cdot\mathbf{v}_{\alpha\beta} - \sum_{m\neq n} \left\{ \boldsymbol{T}_{nm}\cdot\bar{\mathbf{v}}_{\mathrm{dq}^{m\cdot\mathrm{sgn}(m)}} \right\} \ \ (11)$$

and

$$\bar{\mathbf{v}}_{\mathsf{dq}^{n}\cdot\mathsf{sgn}(n)} = F(s)\mathbf{v}_{\mathsf{dq}^{n}\cdot\mathsf{sgn}(n)} \tag{12}$$

in which F(s) is the transfer function of the LPF,  $\operatorname{sgn}(\cdot)$  is the sign function defining the rotational direction of the harmonic component, and  $T_{nm}$  is the Park transform matrix in the corresponding  $dq^{n\cdot\operatorname{sgn}(n)}$ —frame. Furthermore, the LPF F(s),  $\operatorname{sgn}(\cdot)$ , and  $T_{nm}$  can be expressed as,

$$F(s) = \frac{\omega_f}{s + \omega_f} \tag{13}$$

with  $\omega_f$  being its cut-off frequency,

$$\operatorname{sgn}(i) = \begin{cases} +1, & \text{for } i = 1, 5, 9, \cdots \\ 0, & \text{for } i = 0 \\ -1, & \text{for } i = 3, 7, 11, \cdots \end{cases}$$

(14)

and

$$\boldsymbol{T}_{nm} = \begin{bmatrix} \cos \theta_{nm} & \sin \theta_{nm} \\ -\sin \theta_{nm} & \cos \theta_{nm} \end{bmatrix}$$

(15)

where  $\theta_{nm} = \{n \cdot \operatorname{sgn}(n) - m \cdot \operatorname{sgn}(m)\} \cdot \omega' t$ .  $T_{n0}$  is the case when m = 0 for  $T_{nm}$  shown in (15).

Further noted in Fig. 7, the MHDC is using (11) and (12) once for the fundamental and once for each harmonic component in a decoupling cross-feedback network. Therefore, the MHDC enables the dynamically estimation of the fundamental voltage component (i.e.,  $\bar{\mathbf{v}}_{d\alpha^{+1}}$  that is free of any harmonic distortion). Subsequently, as it is shown in Fig. 7, the fundamental component  $v_{q+1}$  can be used for an accurate synchronization. In respect to the parameter design of the MHDC system, there is only the cut-off frequency (i.e.,  $\omega_f$ ) of the LPF F(s), but it can affect the quality factor, the oscillation damping and the dynamic response of the MHDC recursive filter. The analysis conducted in [14] reveals that a reasonable tradeoff can be achieved by setting  $\omega_f = \omega_0/3$  with  $\omega_0$  being the nominal grid angular frequency as defined previously. In that case, the recursive filtering characteristic of the MHDC enables an almost-complete mitigation of the harmonic effect while maintains a fast response similar to that in the three-phase systems [26], [27]. Additionally,

the cut-off frequency  $\omega_c$  of the IPT system in the MHDC-PLL should be tuned according to § III.B.

It is worth mentioning that, the fast synchronization response of the MHDC-PLL is particularly desired for the proper low voltage ride-through operation of the grid-connected inverter systems [22], while the good immunity against harmonic distortion is beneficial for the power quality of the injected current [23], [27], [28]. Thus, in terms of accuracy, dynamic response and harmonic immunity, the MHDC-PLL synchronization might be a good solution for single-phase systems connected to weak grids with severe harmonic distortions, but the implementation complexity of the MHDC-PLL is increased, which is one of the drawbacks. In addition, since the T/4 Delay system has been employed in the MHDC-PLL system, similar to the T/4 Delay PLL, this further weakens the frequency adaptability of the MHDC-PLL system.

## IV. BENCHMARKING OF THE SELECTED PLLS (EXPERIMENTAL RESULTS)

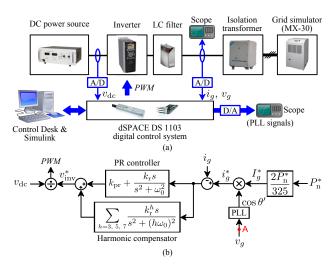

## A. Test-Rig Description

In order to benchmark the selected PLL synchronization methods, a 1-kW grid-connected single-phase inverter system has been built up referring to Fig. 1. Instead of an LCL-filter, an LC-filter is adopted and it is connected to a grid simulator (California Instruments MX-30) through an isolation transformer. Considering the transformer leakage inductance, an equivalent LCL filter is formed, where the capacitor voltage is measured for synchronization. Since a commercial DC source was used, the outer control loop is not necessary. Instead, the current reference  $I_g^*$  is set in the control system by commanding the active power reference, i.e.,  $I_g^* = 2P_{\rm n}^*/V_g$ . A Proportional Resonant (PR) controller  $G_{\rm PR}(s)$  with Harmonic Compensators (HC)  $G_{\rm HC}(s)$  is adopted as the current controller  $G_{\rm CC}(s)$  [1], and it can be expressed as,

$$G_{\text{CC}}(s) = \underbrace{k_{\text{pr}} + \frac{k_{\text{r}}s}{s^2 + \omega_0^2}}_{G_{\text{PR}}(s)} + \underbrace{\sum_{h=3, 5, 7} \frac{k_{\text{r}}^h s}{s^2 + (h\omega_0)^2}}_{G_{\text{HC}}(s)}$$

(16)

where  $k_{\rm pr}$  is the proportional control gain,  $k_{\rm r}$  is the resonant control gain, and  $k_{\rm r}^h$  is the resonant control gain of the HC with h being the harmonic order. All the PLLs and the entire current control system were implemented in a dSPACE DS 1103 system. The system parameters are listed in Table I. The current controller and the LF parameters are designed as shown in Table II. For a fair comparison, the parameters of the LF (i.e., the PI controller) are the same for all the selected PLL systems as shown in Table II, while the control parameters for the PD systems as shown in Table III are designed according to the discussions in § III for an optimal performance. Fig. 8 shows the experimental system layout and the detailed current control system.

## B. Experimental Results

The five selected PLL candidates were tested firstly under a normal grid condition (Total Harmonic Distortion,

TABLE I

PARAMETERS OF THE SINGLE-PHASE GRID-CONNECTED SYSTEM.

| Parameter                      | Symbol        | Value                         |

|--------------------------------|---------------|-------------------------------|

| Rated power                    | $P_{\rm n}^*$ | 1 kW                          |

| DC-link voltage                | $V_{ m dc}$   | 450 V                         |

| Grid voltage amplitude         | $V_{g}$       | $230\times\sqrt{2} \text{ V}$ |

| Grid nominal frequency         | $\omega_0$    | $2\pi \times 50$ rad/s        |

| DC-link capacitor              | $C_{ m dc}$   | 1100 $\mu$ F                  |

| LC filter                      | $L_1$         | 3.6 mH                        |

|                                | $C_{ m f}$    | $2.35~\mu F$                  |

| Transformer leakage inductance | $L_{g}$       | 4 mH                          |

| Sampling frequency             | $f_{ m s}$    | 10 kHz                        |

| Switching frequency            | $f_{ m sw}$   | 10 kHz                        |

TABLE II

CURRENT CONTROLLER AND LOOP FILTER PARAMETERS.

| Controller           | Symbol            | Value |

|----------------------|-------------------|-------|

| PLL loop filter (PI) | $k_p$             | 0.283 |

|                      | $k_i^r$           | 5.663 |

| PR controller        | $k_{ m pr}$       | 22    |

|                      | $k_{ m r}$        | 1300  |

| HC controller        | $k_{\rm r}^{3,5}$ | 1000  |

|                      | $k_{ m r}^7$      | 600   |

TABLE III

PARAMETERS OF THE PHASE DETECTOR SYSTEMS OF THE

SELECTED SINGLE-PHASE PLLS.

| PLL      | Symbol       | Value                                  |

|----------|--------------|----------------------------------------|

| IPT-PLL  | $k_{ m ipt}$ | 1.4                                    |

| EPLL     | au           | 8 ms                                   |

| SOGI-PLL | k            | 1.4                                    |

| MHDC-PLL | $^*\omega_c$ | $2\pi \times 50 \times \sqrt{2}$ rad/s |

|          | $\omega_f$   | $2\pi 	imes 50/3$ rad/s                |

<sup>\*</sup> LPF cut-off freq. in the IPT in-quadrature system.

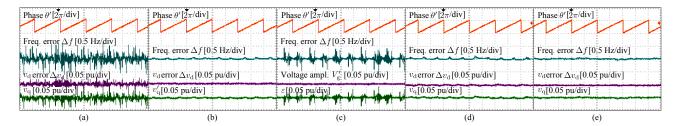

$THD_{v_q} \approx 0.71\%$ ), and the experimental results are presented in Fig. 9, where the frequency error  $\Delta f = f' - 50$ and  $v_d$  error  $\Delta v_d = v_d - 1$  (or  $v'_d - 1$ ). Since the capacitor voltage is measured as the grid voltage  $\boldsymbol{v}_g$  for synchronization which thus contains switching frequency harmonics, it is observed in Fig. 9 that the outputs of both the T/4 Delay PLL and the EPLL consist of high-order harmonics. This indicates the poor harmonic immunity of the T/4 Delay PLL and the EPLL systems. Moreover, the T/4 Delay PLL is more sensitive to the harmonics, as its in-quadrature system is based on a quarter phase delay of the input voltage, thus inevitably inheriting the harmonics. As a result, in the case of grid-connected applications using the T/4 Delay PLL or the EPLL, a LPF may be required and should be incorporated at point "A" shown in Fig. 8(b), which however can affect the dynamics of the entire system. In contrast, the IPT-PLL, the SOGI-PLL, and the MHDC-PLL are all good at eliminating these switching harmonics due to the presence of the low pass filters or the adaptive notch filter.

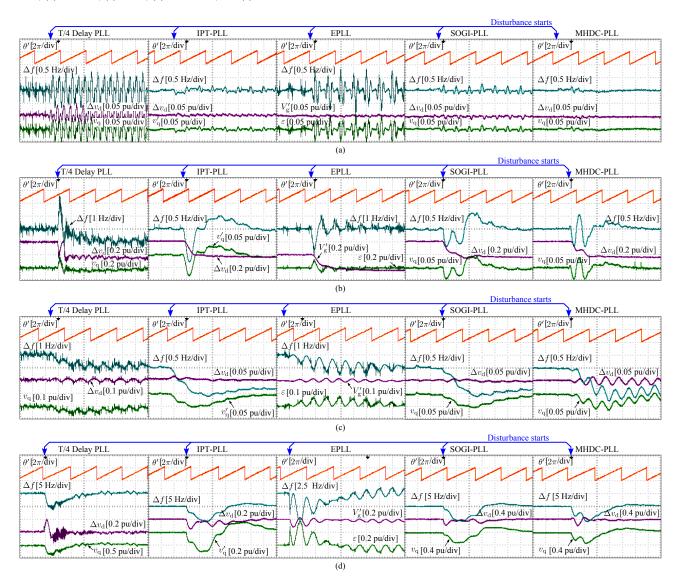

However, in the case of a very weak grid which contains not only low-order but also high-order harmonics, the PLL systems will be challenged. Fig. 10 further benchmarks the dynamic performances of the selected PLL methods

Fig. 8. Experimental setup of a 1-kW single-phase grid-connected system: (a) dSPACE platform and (b) current control system.

when the grid voltage experiences several disturbances. The harmonic sensitivity of the T/4 Delay PLL and the EPLL is clearly verified by the results shown in Fig. 10(a), where it also shows that the IPT-PLL and the SOGI-PLL are slightly affected by the low order harmonics of the grid voltage. In contrast, it can be observed in Fig. 10(a) that the estimated output frequency of the MHDC-PLL system is free of oscillations after a short period of transient. This means that the MHDC-PLL is significantly immune to the harmonics in the grid voltage.

Moreover, it can be observed in Figs. 9 and 10 that the performances of the IPT-PLL and the SOGI-PLL systems are quite alike, since the in-quadrature systems of both PLLs have similar filtering capability (i.e.,  $\mathbf{v}_{\alpha\beta}$ -to- $v_q$ ) according to (7) and (10). In addition, as it is shown in Fig. 10 (c), the T/4 Delay PLL and the MHDC-PLL systems present poor synchronization performances in the case of grid frequency variations, which may occur especially in the micro grid systems due to an injection of a large amount of fluctuating power, e.g., PV and/or wind power. This poor frequency adaptability is because of the adoption of the delay unit with a constant duration for the inquadrature systems. Nevertheless, the two PLLs present fast dynamics. For the MHDC-PLL, the dynamics are even comparable with the IPT-PLL and the SOGI-PLL in terms of a fast response and a small overshooting, as it is verified by Fig. 10(b) and (d). In all, the test results are in close agreement with the discussions in § III.

In addition to the above verification, a comparison between the SOGI-PLL and the MHDC-PLL has also been conducted with a programmed background distortion of the grid voltage (i.e.,  $THD_{v_g} = 2.91\%$ ). In this case study, the HC is disabled in order to compare how the PLL synchronization will impact the injected grid current quality. The experimental results are demonstrated in Fig. 11. It can be seen in Fig. 11 that, if the MHDC-PLL system is adopted as the synchronization, the grid current  $THD_{i_g}$  is slightly reduced in contrast to the case when the SOGI-PLL is used. Actually, when looking at the

Fig. 9. Steady-state performance of the selected PLL synchronization methods under a nominal grid condition (time [10 ms/div]): (a) T/4 Delay PLL, (b) IPT-PLL, (c) EPLL, (d) SOGI-PLL, and (e) MHDC-PLL.

Fig. 10. Dynamic responses of the selected PLL synchronization methods under various grid disturbances (time [10 ms/div]): (a) harmonics (THD $_{vg}$  changes from 0.71% to 2.91%), (b) voltage sag ( $V_g=0.75$  pu), (c) frequency jump (-0.8 Hz), and (d) phase shift ( $-30^{\circ}$ ).

individual low-order harmonics, the same conclusion can be reached. For example, the Root Mean Square (RMS) value of the 7<sup>th</sup> harmonic is 112 mA when the grid current is synchronized through the SOGI-PLL system, while the 7<sup>th</sup> harmonic of 106 mA is achieved using the MHDC-PLL system. The experimental results have demonstrated that the synchronization will affect the entire control systems as mentioned in § I. It should be emphasized that efforts can be devoted to the advancement of synchronization

methods in order to achieve a better current injection from the grid-connected inverter systems.

#### V. CONCLUSION

In this paper, a benchmarking of the most popular PLL methods (i.e., T/4 Delay PLL, EPLL, IPT-PLL, SOGI-PLL, and MHDC-PLL) for single-phase grid-connected systems has been presented. Benchmarks include the accuracy, the transient response, the harmonic immunity under

Fig. 11. Experimental results of a 1-kW single-phase grid-connected system with different PLL systems (CH1 - grid voltage  $v_g$  [250 V/div], CH2 - grid current  $i_g$  [10 A/div], CH M - FFT analysis of the grid current [1 A/div]): (a) SOGI-PLL system and (b) MHDC-PLL.

grid disturbances, and the implementation complexity. As a result, the benchmarking results provide a flexibility to choose an appropriate PLL-based synchronization technique according to a specific application. For example, the SOGI-PLL is suitable for fault ride-through operations in terms of high accuracy and a fast response speed. In contrast, the MHDC-PLL also with fast dynamic responses is good for use in a weak grid that is distorted by nonlinear loads , while its performance is poor in response to grid frequency variations due to the T/4 delay mechanism. Experimental tests on a single-phase grid-connected system have supportively verified the benchmarking.

#### REFERENCES

- [1] F. Blaabjerg, R. Teodorescu, M. Liserre, and A. V. Timbus, "Overview of control and grid synchronization for distributed power generation systems," *IEEE Trans. Ind. Electron.*, vol. 53, no. 5, pp. 1398–1409, Oct. 2006.

- [2] E. Romero-Cadaval, B. Francois, M. Malinowski, and Q. Zhong, "Grid-connected photovoltaic plants: An alternative energy source, replacing conventional sources," *IEEE Ind. Eletron. Mag.*, vol. 9, no. 1, pp. 18–32, Mar. 2015.

- [3] F. Blaabjerg, Z. Chen, and S.B. Kjaer, "Power electronics as efficient interface in dispersed power generation systems," *IEEE Trans. Power Electron.*, vol. 19, no. 5, pp. 1184–1194, Sept. 2004.

- [4] R. Teodorescu, M. Liserre, and P. Rodriguez, Grid converters for photovoltaic and wind power systems. John Wiley & Sons, 2011.

- [5] P. Gonzalez, E. Romero, V.M. Minambres, M.A. Guerrero, and E. Gonzalez, "Grid-connected PV plants: Power quality and technical requirements," in *Proc. of Electric Power Quality and Supply Reliability Conf. (PQ)*, pp. 169-176, Jun. 2014.

- [6] L. Kutt, E. Saarijarvi, M. Lehtonen, H. Molder, and T. Vinnal, "Harmonic load of residential distribution network: Case study monitoring results," in *Proc. of Electric Power Quality and Supply Reliability Conf. (PQ)*, pp. 93-98, Jun. 2014.

- [7] M. Ciobotaru, R. Teodorescu, and F. Blaabjerg, "A new singlephase PLL structure based on second order generalized integrator," in *Proc. of PESC*, pp. 1-6, 2006.

- [8] Y. Yang and F. Blaabjerg, "Synchronization in single-phase grid-connected photovoltaic systems under grid faults," in *Proc. of PEDG*, pp. 476-482, 2012.

- [9] M. Karimi-Ghartemani and M. R. Iravani, "A nonlinear adaptive filter for online signal analysis in power systems: applications," *IEEE Trans. Power Del.*, vol. 17, no. 2, pp. 617–622, Apr. 2002.

- [10] S. A. Khajehoddin, M. Karimi-Ghartemani, A. Bakhshai, and P. Jain, "A power control method with simple structure and fast dynamic response for single-phase grid-connected DG systems," *IEEE Trans. Power Electron.*, vol. 28, no. 1, pp. 221–233, Jan. 2013.

- [11] M. Karimi-Ghartemani, S. A. Khajehoddin, P. K. Jain, and A. Bakhshai, "Derivation and design of in-loop filters in phase-locked loop systems," *IEEE Trans. Instrum. Meas.*, vol. 61, no. 4, pp. 930–940, Apr. 2012.

- [12] R. M. Santos Filho, P. F. Seixas, P. C. Cortizo, L. A. B. Torres, and A. F. Souza, "Comparison of three single-phase PLL algorithms for UPS applications," *IEEE Trans. Ind. Electron.*, vol. 55, no. 8, pp. 2923–2932, Aug. 2008.

- [13] S. Golestan, M. Monfared, F. D. Freijedo, and J. M. Guerrero, "Design and tuning of a modified power-based PLL for singlephase grid-connected power conditioning systems," *IEEE Trans. Power Electron.*, vol. 27, no. 8, pp. 3639–3650, Aug. 2012.

- [14] L. Hadjidemetriou, E. Kyriakides, Y. Yang, and F. Blaabjerg, "Power quality improvement of single-phase photovoltaic systems through a robust synchronization method," in *Proc. of ECCE*, pp. 2625-2632, Sept. 2014.

- [15] P. Rodriguez, J. Pou, J. Bergas, J. I. Candela, R. P. Burgos, and D. Boroyevich, "Decoupled double synchronous reference frame PLL for power converters control," *IEEE Trans. Power Electron.*, vol. 22, no. 2, pp. 584–592, Mar. 2007.

- [16] S. Mishra, D. Das, R. Kumar, and P. Sumathi, "A power-line interference canceler based on sliding DFT phase locking scheme for ECG signals," *IEEE Trans. Instrum. Meas.*, vol. 64, no. 1, pp. 132–142, Jan. 2015.

- [17] I. Carugati, P. Donato, S. Maestri, D. Carrica, and M. Benedetti, "Frequency adaptive PLL for polluted single-phase grids," *IEEE Trans. Power Electron.*, vol. 27, no. 5, pp. 2396–2404, May 2012.

- [18] S. Shinnaka, "A robust single-phase PLL system with stable and fast tracking," *IEEE Trans. Ind. Appl.*, vol. 44, no. 2, pp. 624–633, Mar. 2008.

- [19] L. Wang, Q. Jiang, L. Hong, C. Zhang, and Y. Wei, "A novel phase-locked loop based on frequency detector and initial phase angle detector," *IEEE Trans. Power Electron.*, vol. 28, no. 10, pp. 4538–4549, Oct. 2013.

- [20] K.-J. Lee, J.-P. Lee, D. Shin, D.-W. Yoo, and H.-J. Kim, "A novel grid synchronization PLL method based on adaptive low-pass notch filter for grid-connected PCS," *IEEE Trans. Ind. Electron.*, vol. 61, no. 1, pp. 292–301, Jan. 2014.

- [21] R. G. Lyons, Understanding digital signal processing. Pearson Education, 2010.

- [22] D. Shin, K.-J. Lee, J.-P. Lee, D.-W. Yoo, and H.-J. Kim, "Implementation of fault ride-through techniques of grid-connected inverter for distributed energy resources with adaptive low-pass notch PLL," *IEEE Trans. Power Electron.*, vol. 30, no. 5, pp. 2859–2871, May 2015.

- [23] L. Feola, R. Langella, and A. Testa, "On the effects of unbalances, harmonics and interharmonics on PLL systems," *IEEE Trans. Instrum. Meas.*, vol. 62, no. 9, pp. 2399–2409, Sept. 2013.

- [24] H. Liu, Y. Sun, H. Hu, and Y. Xing, "A new single-phase PLL based on discrete Fourier transform," in *Proc. of APEC*, pp. 521-526, Mar. 2015.

- [25] Y. Yang, K. Zhou, H. Wang, F. Blaabjerg, D. Wang, and B. Zhang, "Frequency adaptive selective harmonic control for grid-connected inverters," *IEEE Trans. Power Electron.*, vol. 30, no. 7, pp. 3912– 3924, Jul. 2015.

- [26] A. Luna, J. Rocabert, I. Candela, J. Hermoso, R. Teodorescu, F. Blaabjerg, and P. Rodriquez, "Grid voltage synchronization for distributed generation systems under grid fault conditions," *IEEE Trans. Ind. Appl.*, vol. PP, no. 99, pp. 1–13, in press, DOI: 10.1109/TIA.2015.2391436, 2015.

- [27] L. Hadjidemetriou, E. Kyriakides, and F. Blaabjerg, "A robust synchronization to enhance the power quality of renewable energy systems," *IEEE Trans. Ind. Electron.*, vol. PP, no. 99, pp. 1–11, in press, DOI:10.1109/TIE.2015.2397871 2015.

- [28] R. Bojoi, L. R. Limongi, D. Roiu, and A. Tenconi, "Enhanced power quality control strategy for single-phase inverters in distributed generation systems," *IEEE Trans. Power Electron.*, vol. 26, no. 3, pp. 798–806, Mar. 2011.

- [29] J. Wang, J. Liang, F. Gao, L. Zhang, and Z. Wang, "A method to improve the dynamic performance of moving average filter based PLL," *IEEE Trans. Power Electron.*, vol. PP, no. 99, pp. 1–14, in press, DOI: 10.1109/TPEL.2014.2381673, 2015.