# Aalborg Universitet

# An Efficient Implementation of Generalized Delayed Signal Cancellation PLL

Golestan, Saeed; Freijedo Fernandez, Francisco Daniel; Vidal, Ana; Yepes, Alejandro G.; Guerrero, Josep M.; Doval-Gandoy, Jesus

Published in: I E E E Transactions on Power Electronics

DOI (link to publication from Publisher): 10.1109/TPEL.2015.2420656

Publication date: 2016

**Document Version** Early version, also known as pre-print

Link to publication from Aalborg University

Citation for published version (APA):

Golestan, S., Fernandez, F. D. F., Vidal, A., Yepes, A. G., Guerrero, J. M., & Doval-Gandoy, J. (2016). An Efficient Implementation of Generalized Delayed Signal Cancellation PLL. I E E E Transactions on Power Electronics, 31(2), 1085-1094. DOI: 10.1109/TPEL.2015.2420656

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- ? Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

? You may not further distribute the material or use it for any profit-making activity or commercial gain

? You may freely distribute the URL identifying the publication in the public portal ?

Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# An Efficient Implementation of Generalized Delayed Signal Cancellation PLL

Saeed Golestan, Senior Member, IEEE, Francisco D. Freijedo, Ana Vidal, Student Member, IEEE, Alejandro G. Yepes, Member, IEEE, Josep M. Guerrero, Fellow, IEEE, and Jesus Doval-Gandoy, Member, IEEE

Abstract-The phase, frequency, and amplitude of the fundamental-frequency positive-sequence component of the grid voltage are crucial information in control of most grid-connected power electronic based equipment. Often, a standard phaselocked loop (PLL) with a prefiltering stage is employed for the extraction of them. Inspired by the concept of delayed signal cancellation (DSC), the generalized DSC (GDSC) operator has recently been introduced as an interesting option for the PLL prefiltering stage. In its typical structure, the GDSC operator extracts the grid fundamental component and feeds it to a conventional synchronous reference frame PLL (SRF-PLL). The frequency estimated by the SRF-PLL is then fed back to the GDSC operator to make it frequency adaptive. This structure, however, suffers from two main drawbacks: 1) the system is highly nonlinear and, therefore, it is very difficult to ensure its stability under all circumstances; 2) adapting the GDSC to grid frequency variations increases the implementation complexity and computational effort, particularly when the interpolation techniques are used for this purpose. To avoid these problems while maintaining high accuracy in the extraction of grid voltage quantities, an efficient and low-cost implementation of the GDSC-PLL is suggested in this paper. The proposed structure, which is called the enhanced GDSC-PLL (EGDSC-PLL), uses a nonadaptive GDSC operator as its prefiltering stage, and compensates the phase-shift and amplitude scaling caused by this operator by using two units, called the phase-error compensator and amplitude-error compensator. The effectiveness of the EGDSC-PLL is confirmed through simulation and experimental results.

*Index Terms*—Delayed signal cancelation (DSC), phase-locked loop (PLL), synchronization.

#### I. INTRODUCTION

The phase, frequency, and amplitude of the fundamentalfrequency positive-sequence (FFPS) component of the grid voltage are crucial information in control of grid-connected power electronic based equipment such as uninterruptible power supplies [1], distributed generation systems [2], flexible AC transmission systems [3], and high voltage direct current systems [4], [5]. To extract this information, different methods have been proposed in the literature. Phase locked-loop (PLL)

Copyright © 2015 IEEE. Personal use of this material is permitted. However, permission to use this material for any other purposes must be obtained from the IEEE by sending a request to pubs-permissions@ieee.org.

S. Golestan is with the Department of Electrical Engineering, Abadan Branch, Islamic Azad University, Abadan 63178-36531, Iran (e-mail: s.golestan@ieee.org).

F. D. Freijedo and J. M. Guerrero are with the Department of Energy Technology, Aalborg University, Aalborg DK-9220, Denmark (e-mail: fran@et.aau.dk; joz@et.aau.dk).

A. Vidal, A G. Yepes, and J. Doval-Gandoy are with the Department of Electronics Technology, University of Vigo, Vigo 36310, Spain (e-mail: anavidal@uvigo.es; agyepes@uvigo.es; jdoval@uvigo.es). based algorithms are probably the most popular and widely used techniques owing to their robust performance and effectiveness.

A PLL is a closed-loop feedback control system which synchronizes its output in frequency and phase with its input [6]. The phase detector, the loop filter, and the voltage controlled oscillator are common parts of almost all PLLs [6]. A major challenge associated with PLLs is how to achieve a high disturbance rejection capability without degrading the dynamic performance [7]. Different researchers have proposed different strategies to deal with this challenge. These methods can be classified into two major categories, namely in-loop and pre-loop methods.

The in-loop approaches can be considered as any modification in the PLL control loop to improve its dynamic response/filtering capability tradeoff. Some examples of such techniques are: 1) using adaptive notch filters [8] or adaptive lead compensators [9] for selective cancellation of harmonic components in the PLL control loop; 2) dynamically adjusting the gain of the frequency estimation loop to improve the PLL dynamic performance during startups and phase angle jumps [10]; and 3) using moving average filters (MAFs) or repetitive regulators for elimination of all (or at least most) low-order harmonics in the PLL control loop [11]-[18].

The pre-loop methods, on the other hand, can be typically understood as a filtering stage which is used before the input of the PLL and is responsible for extracting the FFPS component and eliminating (or at least attenuating) some (or most) of the grid voltage harmonics. The complex coefficient filters [19], [20], the space vector Fourier transform [21], and the dual second-order generalized integrators [22] are the well-known pre-loop filtering methods.

Inspired by the concept of delayed signal cancellation (DSC) [23]-[26], the generalized DSC (GDSC) operator has recently been introduced as an effective solution to improve the performance of the PLL under adverse grid conditions [27]-[29]. Typically, the GDSC operator is employed as the PLL prefiltering stage and is responsible for extracting the grid voltage FFPS component. The PLL receives this component as its input and extracts its phase, frequency, and amplitude. The frequency estimated by the PLL is then fed back to the GDSC operator to make it frequency adaptive. The main drawback of this structure is that it is highly nonlinear, so it is very difficult to ensure the stability of the whole system under all circumstances [30]. Moreover, adapting the GDSC operator to the grid frequency variations increases the implementation complexity and computational burden, particularly when the

interpolation techniques are used for this purpose.

To avoid the aforementioned problems, an efficient and lowcost implementation of the GDSC based PLL is suggested in the paper. The proposed PLL structure employs a non-adaptive GDSC operator as its prefiltering stage, and uses two units, called the phase-error compensator (PEC) and amplitude-error compensator (AEC), to correct the phase-shift and amplitude scaling caused by this operator in the presence of frequency drifts. Designing the PEC and AEC is based on the idea of post-processing proposed in [31]. The small-signal model of the proposed PLL structure is also derived, which simplifies the tuning procedure and stability analysis. The effectiveness of the suggested PLL structure, which is called the enhanced GDSC-PLL (EGDSC-PLL), is confirmed through simulation and experimental results.

# II. OVERVIEW OF DSC-PLL AND GDSC-PLL A. DSC-PLL

Application of the DSC operator for extraction of the FFPS component in the stationary ( $\alpha\beta$ ) reference frame can be expressed as [23], [24]

$$\vec{v}_{\alpha\beta,1}^{\,+}(t) = \frac{1}{2} \left[ \vec{v}_{\alpha\beta}(t) + e^{\frac{j2\pi}{n}} \vec{v}_{\alpha\beta}(t - T/n) \right] \tag{1}$$

where  $\vec{v}_{\alpha\beta}(t) = v_{\alpha}(t) + jv_{\beta}(t)$  is the grid voltage vector in the  $\alpha\beta$  frame,  $\vec{v}^+_{\alpha\beta,1}(t) = v^+_{\alpha,1}(t) + jv^+_{\beta,1}(t)$  is the extracted FFPS voltage vector, T is the nominal value of the grid voltage fundamental period, and n is the delay factor. Taking the Laplace transform of both sides of (1) yields

$$\vec{v}_{\alpha\beta,1}^{+}(s) = \underbrace{\frac{1}{2} \left[ 1 + e^{\frac{j2\pi}{n}} e^{-\frac{T}{n}s} \right]}_{\text{DSC}_{n}(s)} \vec{v}_{\alpha\beta}(s) \tag{2}$$

where  $DSC_n(s)$  is the transfer function of the  $\alpha\beta$ -frame DSC operator.

Substituting  $s = j\omega$  into the transfer function of the DSC operator yields

$$DSC_n(j\omega) = \left| \cos\left(\frac{\omega T}{2n} - \frac{\pi}{n}\right) \right| \angle - \left(\frac{\omega T}{2n} - \frac{\pi}{n}\right).$$

(3)

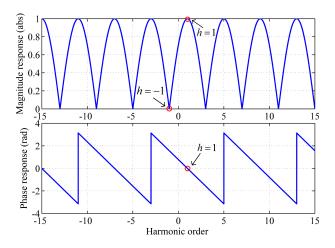

Fig. 1 illustrates the frequency response of (3) for n = 4, which is the recommended choice for blocking the fundamental-frequency negative-sequence (FFNS) component of the grid voltage [23]. As shown, the DSC<sub>4</sub> operator provides unity gain with zero phase at the fundamental frequency of positive sequence and zero gain at the fundamental frequency of negative sequence. This means that the DSC<sub>4</sub> operator passes the FFPS component and blocks the FFNS component. It can also be observed that the DSC<sub>4</sub> operator blocks all harmonics of order h = 4k - 1 ( $k = \pm 1, \pm 2, \pm 3, \ldots$ ), but leaves all harmonics of order h = 4k + 1 ( $k = \pm 1, \pm 2, \pm 3, \ldots$ ) unchanged. The 11th harmonic of negative sequence are among the most important harmonic components that the DSC<sub>4</sub> operator cannot block.

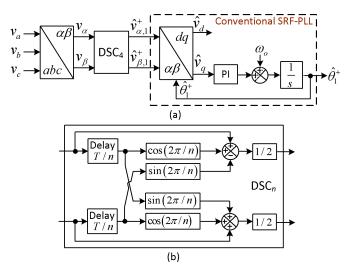

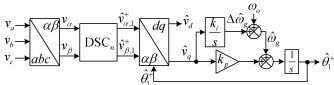

Fig. 2 shows the block diagram description of the DSC-PLL, which consists of a conventional synchronous reference frame

Fig. 1. Frequency response of the  $\mathrm{DSC}_4$  operator. h denotes the harmonic order.

Fig. 2. (a) Block diagram description of the DSC-PLL. (b) Time domain implementation of the  $DSC_n$  operator.

PLL (SRF-PLL) and  $DSC_4$  operator [25], [26]. The  $DSC_4$  operator is responsible for extracting the FFPS voltage vector, and the SRF-PLL is responsible for extracting the phase, frequency, and amplitude of this voltage vector. The DSC-PLL can provide an accurate estimation of the grid fundamental phase, frequency, and amplitude under unbalanced and/or low-distorted grid conditions; however, it fails to do so under highly distorted grid conditions, particularly when, in addition to the odd-order harmonic components, there are even-order harmonic components and dc offset in the grid voltage. To overcome this drawback, the idea of GDSC and GDSC-PLL has recently been proposed [27]-[29].

# B. GDSC-PLL

The idea behind the GDSC operator is quite simple: several DSC operators (with proper delay factors) are cascaded with the  $DSC_4$  operator to block those harmonics that it cannot. The question that may arise here is: how many DSCs are needed for this purpose? The answer to this question depends on the anticipated harmonic pattern for the grid voltage. For

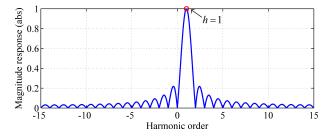

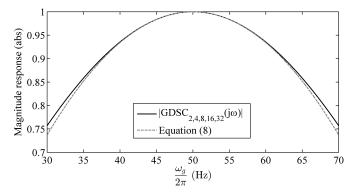

Fig. 3. Magnitude response of the  $GDSC_{2,4,8,16,32}$  operator.

example, if only odd-order harmonic components are expected in the grid voltage, then cascading three DSC operators with delay factors n = 8, 16, 32 with the DSC<sub>4</sub> operator is good enough to block them. However, the grid harmonic pattern is often unknown. Therefore, it should be assumed that all harmonic components of all sequences are present in the grid voltage. In this case, cascading four DSC operators with delay factors n = 2, 8, 16, 32 with the DSC<sub>4</sub> operator is often recommended [27]-[29]. Equation (4) describes the sdomain transfer function of the resultant GDSC operator in this condition, and Fig. 3 shows its magnitude frequency response.

$$GDSC_{2,4,8,16,32}(s) = \prod_{n=2,4,8,16,32} DSC_n(s).$$

(4)

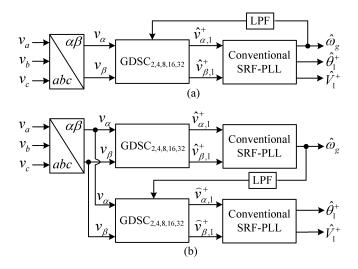

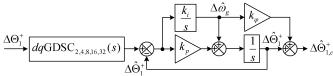

Fig 4(a) shows the GDSC-PLL proposed in [28], which consists of three distinct parts: 1) the  $GDSC_{2,4,8,16,32}$  operator, which extracts the FFPS voltage vector; 2) the SRF-PLL, which extracts the phase, frequency, and amplitude of the FFPS voltage vector; and 3) a frequency-feedback loop (FFL), which feeds back the estimated frequency to the  $GDSC_{2,4,8,16,32}$  operator to make it frequency adaptive. The main drawbacks of this structure are the following: 1) the FFL makes the system highly nonlinear, so it is very difficult to ensure the system stability under all circumstances [30]; 2) adaptation of GDSC operator to the grid frequency variations increases the required computational effort, particularly when the interpolation techniques are used for this purpose.

Fig 4(b) shows the GDSC-PLL proposed in [27]. To avoid the aforementioned stability problem, this structure uses two  $GDSC_{2,4,8,16,32}$  operators and two SRF-PLLs: one set provides an estimation of the grid frequency for the other set. However, it clearly demands more digital resources.

# **III. PROPOSED STRUCTURE**

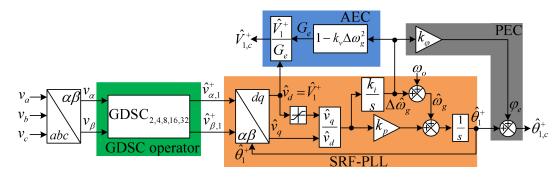

Fig. 5 shows the schematic diagram of the proposed EGDSC-PLL. As shown, to avoid the implementation complexity, the high computational burden and the nonlinearity caused by adaptive GDSC operator, a non-adaptive GDSC operator is considered as the PLL prefiltering stage. This non-adaptive operator accurately extracts the FFPS component when the grid frequency is at its nominal value. However, it fails to do so in the presence of frequency drifts: the extracted FFPS component undergoes a phase shift and amplitude scaling under off-nominal grid frequencies. To correct these

Fig. 4. Different structures of GDSC-PLL. (a) Structure proposed in [28]. (b) Structure proposed in [27].

errors, two units, called the PEC and AEC, are designed and incorporated into the SRF-PLL structure.

## A. Phase and Amplitude Error Compensation

Substituting  $s = j\omega_g$  into (4), where  $\omega_g$  is the grid fundamental frequency, gives the phase and magnitude of the GDSC operator at the fundamental frequency as

$$\angle \text{GDSC}_{2,4,8,16,32}(j\omega_g) = -\sum_{n=2,4,8,16,32} \left( \frac{\omega_g T}{2n} - \frac{\pi}{n} \right)$$

(5)

$$|\text{GDSC}_{2,4,8,16,32}(j\omega_g)| = \prod_{n=2,4,8,16,32} \left| \cos\left(\frac{\omega_g T}{2n} - \frac{\pi}{n}\right) \right|.$$

(6)

Defining  $\omega_g = \omega_o + \Delta \omega_g$ , where  $\omega_o = 2\pi/T$  is the nominal value of grid frequency and  $\Delta \omega_g$  denotes the deviation of grid frequency from its nominal value, and substituting it into (5) and (6) yields

$$\angle \text{GDSC}_{2,4,8,16,32}(j\omega_g) = -\sum_{\substack{n=2,4,8,16,32\\ \hline 2n}} \left(\frac{\Delta\omega_g T}{2n}\right)$$

$$= -\underbrace{\frac{T}{2} \left[\sum_{\substack{n=2,4,8,16,32\\ k_{\phi}}} \frac{1}{n}\right]}_{k_{\phi}} \Delta\omega_g (7)$$

$$GDSC_{2,4,8,16,32}(j\omega_g)| = \prod_{n=2,4,8,16,32} \cos\left(\frac{\Delta\omega_g T}{2n}\right)$$

$$\approx \prod_{n=2,4,8,16,32} \left[1 - \left(\frac{\Delta\omega_g T}{2n}\right)^2/2\right]$$

$$\approx 1 - \underbrace{\frac{T^2}{8} \left(\sum_{n=2,4,8,16,32} \frac{1}{n^2}\right)}_{k_v} (\Delta\omega_g)^2. \quad (8)$$

Notice that in the derivation of (7) no approximation is made; however, in the derivation of (8), it is assumed that the argument of the cosine term, which depends on the grid frequency,

Fig. 5. Block diagram description of the EGDSC-PLL.

Fig. 6. Accuracy assessment of (8) in the prediction of the magnitude frequency response of the  $GDSC_{2,4,8,16,32}$  operator around the nominal frequency.

is much lower than the unity. Therefore, the accuracy of (8) should be evaluated.

Fig. 6 compares the magnitude frequency response of the  $GDSC_{2,4,8,16,32}$  operator with that predicted by (8). It can be observed that (8) is quite accurate within the range of  $50 \pm 10$  Hz, which is much wider than the allowable range of variations of grid frequency [35].

Equations (7) and (8) show that a phase shift of  $-k_{\varphi}\Delta\omega_g$ and amplitude scaling of about  $1-k_v(\Delta\omega_g)^2$  in the extraction of the FFPS component by the PLL prefiltering stage happens. Considering that  $k_{\varphi}$  and  $k_v$  are constant gains that can be simply calculated from (7) and (8), respectively, and that the output signal of the integrator of the proportional-integral (PI) controller provides an estimation of  $\Delta\omega_g$ , these errors can be simply compensated as shown in Fig. 5.

## B. Small-Signal Modeling

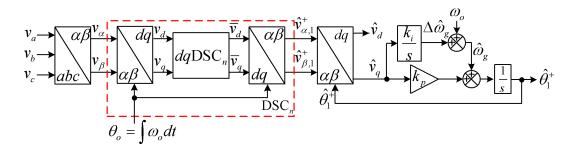

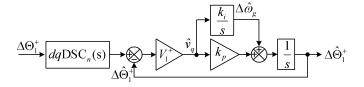

The small-signal modeling of the EGDSC-PLL is rather complicated. To simplify this task, the small-signal model of a simple DSC-PLL is first derived. This model is then extended to the proposed PLL structure. Fig. 7 shows the schematic diagram of the DSC-PLL, where DSC<sub>n</sub>, as mentioned before, denotes a  $\alpha\beta$ -frame DSC operator with delay factor n. Equation (2) expresses the transfer function of this operator.

Fig. 8 shows the alternative mathematically equivalent representation of the DSC-PLL, in which the  $\alpha\beta$ -frame DSC op-

Fig. 7. Schematic diagram of the DSC-PLL.

erator is replaced by its dq-frame equivalent, i.e., the dqDSC<sub>n</sub> operator, in a generic synchronous reference frame rotating at the nominal angular frequency. The transfer function of the dqDSC<sub>n</sub> operator, as shown in (9), can be simply obtained by replacing s by  $s + j\omega_o$  in the transfer function of the DSC<sub>n</sub> operator, because transferring from the stationary to the synchronous reference frame is mathematically equivalent to a frequency shift equal to the rotating speed of the synchronous reference frame [32].

$$dq \text{DSC}_n(s) = \text{DSC}_n(s+j\omega_o) = 0.5\left(1+e^{-\frac{T}{n}s}\right).$$

(9)

For the sake of simplicity in the modelling procedure, let the three-phase voltage in the DSC-PLL input be balanced and without harmonic distortion, i.e.,

$$v_{a}(t) = V_{1}^{+} \cos\left(\theta_{1}^{+}\right)$$

$$v_{b}(t) = V_{1}^{+} \cos\left(\theta_{1}^{+} - 2\pi/3\right)$$

$$v_{c}(t) = V_{1}^{+} \cos\left(\theta_{1}^{+} + 2\pi/3\right)$$

(10)

where  $V_1^+$  and  $\theta_1^+ = \int \omega_g dt$  are the amplitude and phase angle of the FFPS component of the grid voltage, respectively. Applying the Clarke's transformation and subsequently the Park's transformation to the three-phase voltages (10) gives the input signals of the dqDSC<sub>n</sub> operator, i.e.,  $v_d$  and  $v_q$ , as

$$v_d(t) = V_1^+ \cos\left(\Delta\theta_1^+\right)$$

$$v_q(t) = V_1^+ \sin\left(\Delta\theta_1^+\right)$$

(11)

where  $\Delta \theta_1^+ = \theta_1^+ - \theta_o = \int (\omega_g - \omega_o) dt = \int \Delta \omega_g dt$ .

Using (11) and (9) and assuming that  $\Delta \omega_g$  is a constant, the output signals of the  $dq \text{DSC}_n$  operator, i.e.,  $\bar{v}_d$  and  $\bar{v}_q$ , can be obtained as

$$\bar{v}_d(t) = 0.5V_1^+ \cos\left(\Delta\theta_1^+\right) + 0.5V_1^+ \cos\left(\Delta\theta_1^+ - \frac{\Delta\omega_g T}{n}\right)$$

$$\bar{v}_q(t) = 0.5V_1^+ \sin\left(\Delta\theta_1^+\right) + 0.5V_1^+ \sin\left(\Delta\theta_1^+ - \frac{\Delta\omega_g T}{n}\right).$$

(12)

Fig. 8. Alternative mathematically equivalent representation of the DSC-PLL.

Fig. 9. Small-signal model of the DSC-PLL.

Applying the inverse Park's transformation with a rotating angle  $\theta_o$  to (12) and then the Park's transformation with a rotating angle  $\hat{\theta}_1^+$  to the result gives the PI controller input signal, i.e.,  $\hat{v}_q$ , as

$$\hat{v}_q(t) = 0.5V_1^+ \sin\left(\Delta\theta_1^+ - \Delta\hat{\theta}_1^+\right) + 0.5V_1^+ \sin\left(\Delta\theta_1^+ - \frac{\Delta\omega_g T}{n} - \Delta\hat{\theta}_1^+\right) \quad (13)$$

where  $\Delta \hat{\theta}_1^+ = \hat{\theta}_1^+ - \theta_o$ .

By replacing the sine functions by their arguments, (13) can be approximated by

$$\hat{v}_q(t) = 0.5V_1^+ \left(\Delta\theta_1^+ - \Delta\hat{\theta}_1^+\right) + 0.5V_1^+ \left(\Delta\theta_1^+ - \frac{\Delta\omega_g T}{n} - \Delta\hat{\theta}_1^+\right) = V_1^+ \left[0.5 \left(\Delta\theta_1^+ + \Delta\theta_1^+ - \frac{\Delta\omega_g T}{n}\right) - \Delta\hat{\theta}_1^+\right].$$

(14)

Taking the Laplace transform of (14) gives

$$\hat{v}_q(s) = V_1^+ \left[ \underbrace{0.5 \left( 1 + e^{-\frac{T}{n}s} \right)}_{dq \text{DSC}_n(s)} \Delta \Theta_1^+ - \Delta \hat{\Theta}_1^+ \right]$$

(15)

where  $\Delta \Theta_1^+$  and  $\Delta \hat{\Theta}_1^+$  denote the Laplace transform of  $\Delta \theta_1^+$ and  $\Delta \hat{\theta}_1^+$ , respectively. Using (15), the DSC-PLL small-signal model can be obtained as shown in Fig. 9.

The small-signal model of the proposed EGDSC-PLL can now be derived by applying the following changes to the model shown in Fig. 9.

1) The voltage amplitude  $V_1^+$ , which appears as a gain in the forward path of the DSC-PLL model, should be removed. The reason is that the proposed PLL uses an amplitude normalization mechanism before the PI controller.

Fig. 10. Small-signal model of the EGDSC-PLL.

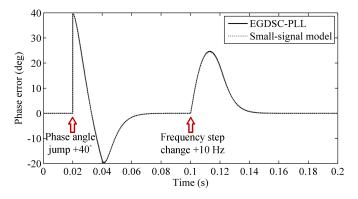

Fig. 11. Accuracy assessment of the EGDSC-PLL small-signal model. Control parameters:  $k_p = 440$ ,  $k_i = 48361$  and  $k_{\varphi} = 9.6875e - 3$ .

2) The transfer function of the dqDSC<sub>n</sub> operator in the DSC-PLL model should be replaced by

$$dq \text{GDSC}_{2,4,8,16,32}(s) = \prod_{n=2,4,8,16,32} dq \text{DSC}_n(s)$$

$$= \prod_{n=2,4,8,16,32} \frac{1}{2} \left( 1 + e^{-\frac{T}{n}s} \right) (16)$$

which is the transfer function of the dq-frame equivalent of the GDSC<sub>2,4,8,16,32</sub> operator.

The PI controller integrator output, i.e., Δŵ<sub>g</sub>, should be multiplied by k<sub>φ</sub> and added to the small-signal model output in order to model the dynamics of the PEC.

Fig. 10 shows the small-signal model of the proposed PLL, and Fig. 11 evaluates the accuracy of this model. As it can be observed, the derived small-signal model is very accurate and perfectly predicts the dynamic behavior of the EGDSC-PLL.

#### C. Stability Analysis and Parameter Design Guidelines

The derived small-signal model can be very helpful for stability analysis and for selecting the control parameters of the

TABLE I

CONTROL PARAMETERS OF THE EGDSC-PLL.

|                    | Parameter<br>Proportional gain, $k_p = 2\zeta\omega_n$<br>Integral gain, $k_i = \omega_n^2$ |                      |                           | Value    |     |     |

|--------------------|---------------------------------------------------------------------------------------------|----------------------|---------------------------|----------|-----|-----|

|                    |                                                                                             |                      |                           | 440      |     |     |

|                    |                                                                                             |                      |                           | 48361    |     |     |

|                    | PEC g                                                                                       | ain, $k_{\varphi} =$ | = 31T/64                  | 9.6875e  |     |     |

|                    | AEC gai                                                                                     | n, $k_v = 3$         | $41T^{2}/8192$            | 1.665e - | - 5 |     |

|                    |                                                                                             |                      |                           |          |     |     |

| 80                 |                                                                                             |                      |                           |          |     |     |

| <sub>50</sub> 70   |                                                                                             |                      |                           |          |     | -   |

| Phase margin (deg) |                                                                                             |                      |                           |          |     | -   |

| 100 50 -           |                                                                                             |                      |                           |          |     | -   |

| 19 40-             |                                                                                             |                      |                           |          |     | -   |

| ā 30-              |                                                                                             |                      |                           |          |     |     |

| 20                 | 50                                                                                          | 100                  | 150                       | 200      | 250 |     |

| 0                  | 50                                                                                          | 100                  |                           | 200      | 250 | 300 |

|                    |                                                                                             |                      | $\frac{\pi n}{2\pi}$ (Hz) |          |     |     |

Fig. 12. PM of the EGDSC-PLL as a function of  $\omega_n$ .

SRF-PLL. Using this model, the closed-loop transfer function of the PLL can be obtained as

$$G_{cl}(s) = \frac{\Delta \hat{\Theta}_{1,c}^+}{\Delta \Theta_1^+} = dq \text{GDSC}_{2,4,8,16,32}(s) \frac{(k_p + k_i k_{\varphi}) s + k_i}{s^2 + k_p s + k_i}$$

(17)

which shows that the proposed PLL is stable for  $k_p > 0$  and  $k_i > 0$ .

Defining  $k_p = 2\zeta \omega_n$  and  $k_i = \omega_n^2$ , where  $\zeta$  is the damping factor and  $\omega_n$  is the natural frequency,  $k_p$  and  $k_i$  can be determined by selecting appropriate values for  $\zeta$  and  $\omega_n$ . As recommended in [33],  $\zeta = 1$  is chosen for the damping factor. On the other hand, the natural frequency  $\omega_n$  should be tuned depending on the required stability margin, filtering capability and transient response. Fig. 12 shows the variation of phase margin (PM) of the EGDSC-PLL as a function of  $\omega_n$ . It can be observed that increasing  $\omega_n$ , which corresponds to raising the speed of response and reducing the filtering capability of the PLL, decreases the PM. Here,  $\omega_n = 2\pi 35$ rad/s, which corresponds to PM  $\approx 55^{\circ}$ , is adopted for the natural frequency of the EGDSC-PLL. This value ensures a fast dynamic response and good filtering capability for the PLL. Table I summarizes the selected values of the control parameters.

It should be mentioned that the gain margin (GM) of proposed PLL, which is -5.75 dB, is negative. Notice that a negative GM does not necessarily mean instability. It just means that the PLL may become unstable if the loop gain reduces too much [36]. Fortunately, the amplitude normalization mechanism included into the EGDSC-PLL structure prevents such condition and ensures its stability.

TABLE II

PARAMETERS OF DISTORTED INPUT VOLTAGE

| Voltage component                             | Amplitude (p.u.) |  |  |

|-----------------------------------------------|------------------|--|--|

| Fundamental positive-sequence                 | 1                |  |  |

| Fundamental negative-sequence                 | 0.1              |  |  |

| 5 <sup>th</sup> harmonic negative-sequence    | 0.1              |  |  |

| 7 <sup>th</sup> harmonic positive-sequence    | 0.1              |  |  |

| 11 <sup>th</sup> harmonic negative-sequence   | 0.05             |  |  |

| $13^{\mathrm{th}}$ harmonic positive-sequence | 0.05             |  |  |

## IV. SIMULATION AND EXPERIMENTAL RESULTS

In this section, the effectiveness of EGDSC-PLL is evaluated through simulation and experimental results. Simulations are carried out in Matlab/Simulink environment and experimental results are obtained using a dSPACE MABXII DS1401 platform. Throughout the simulation and experimental studies,  $f_s = 8$  kHz ( $f_s$  is the sampling frequency) and  $\omega_o = 2\pi 50$ rad/s are considered.

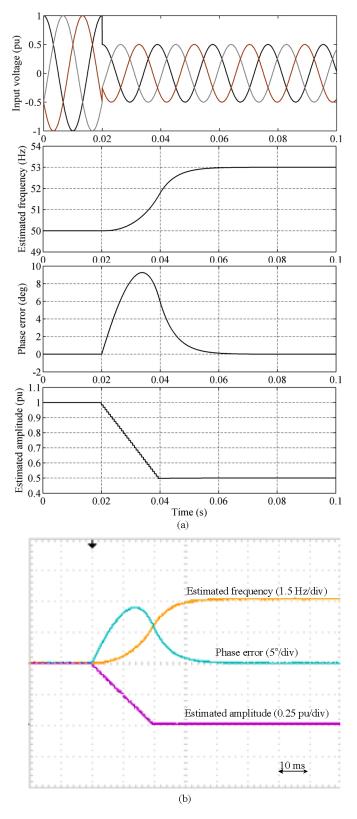

### A. Symmetrical Voltage Sag with Frequency Step Change

Fig. 13 shows the simulation and experimental results for the EGDSC-PLL under a symmetrical voltage sag of +0.5p.u. and a frequency step change of +3 Hz. It can be observed that the EGDSC-PLL provides a zero steady-state phase error and an accurate estimation of the grid voltage amplitude in the presence of frequency drifts. The PLL settling time in the estimation of amplitude and frequency are about one and two cycles of fundamental frequency, respectively. For those situations where a faster dynamic response is needed, the GDSC<sub>2,4,8,16,32</sub> operator can be used instead of the GDSC<sub>2,4,8,16,32</sub>. Notice that this solution can be employed only when the dc offset and even-order harmonic components in the PLL input voltage are negligible.

#### B. Distorted and Unbalanced Grid Condition

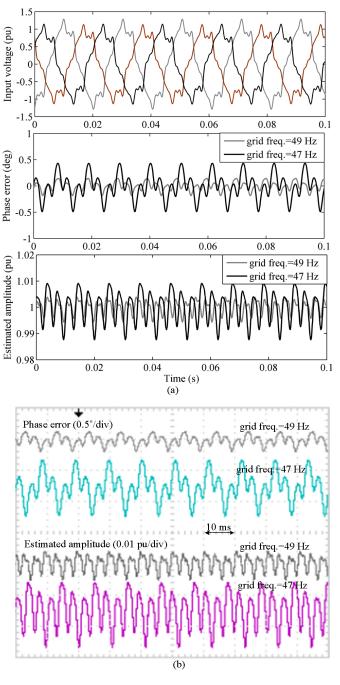

In this test, the steady-state performance of EGDSC-PLL under distorted and unbalanced grid condition is evaluated. The harmonic components of the test voltage, which are summarized in Table II, are almost twice of the maximum allowed values according to the IEC standards [37]. This test is performed under off-nominal frequencies ( $\omega_g = 2\pi 49$  and  $\omega_g = 2\pi 47$  rad/s). The obtained results are shown in Fig. 14. As it can be observed, the PLL phase and amplitude errors are limited to 0.5° and 0.01 pu, respectively, which confirm the high filtering capability of the EGDSC-PLL.

#### C. Asymmetrical Voltage Sag

This section evaluates the EGDSC-PLL performance under different levels of voltage sag at phase A of the grid voltage. During this test, the amplitudes of phase B and C are fixed at 1 pu. This test, similar to the previous one, is carried out under off-nominal grid frequencies. The obtained results are shown in Fig. 15. As it can be observed, the performance of

Fig. 13. (a) Simulation and (b) experimental results for the EGDSC-PLL when the grid voltage undergoes a symmetrical voltage sag of 0.5 p.u. with a frequency step change of +3 Hz.

the proposed PLL is quite good when the grid frequency is close to its nominal value. It, however, tends to worsen in the presence of large frequency drifts. To improve the performance

Fig. 14. (a) Steady-state simulation and (b) experimental results under distorted and unbalanced grid conditions.

of the proposed PLL in such scenarios, an extra  $DSC_4$  operator can be included in the  $GDSC_{2,4,8,16,32}$  operator.

# V. COMPARISON WITH CONVENTIONAL GDSC-PLLS

The GDSC-PLLs proposed in [27] and [28], which use frequency adaptive GDSC operator in their structure, can provide a performance as good as that of the developed EGDSC-PLL; however, their implementations require a higher computational effort, particularly when the interpolation techniques are used for adapting them to the grid frequency variations. To support this claim, Table III summarizes the key elements of the

Fig. 15. Magnitude of double frequency oscillatory error in (a) the estimated phase, (b) the estimated frequency, and (c) the estimated amplitude under single-phase voltage sags.

TABLE III

Key Elements of the Suggested GDSC-PLL Structure and Those Proposed in [27] and [28].

|                                   | EGDSC-PLL    | GDSC-PLL proposed in [28] | GDSC-PLL proposed in [27]                                             |

|-----------------------------------|--------------|---------------------------|-----------------------------------------------------------------------|

| Required number of SRF-PLLs       | one          | one                       | two                                                                   |

| Required number of GDSC operators | one          | one                       | two                                                                   |

| Type of GDSC operators            | non-adaptive | adaptive                  | first GDSC operator is non-adaptive and<br>the second one is adaptive |

TABLE IV NUMBER OF OPERATIONS REQUIRED FOR DIGITAL IMPLEMENTATION OF ADAPTIVE AND NON-ADAPTIVE GDSC<sub>2,4,8,16,32</sub> OPERATOR. **M=**MULTIPLICATION, **A=**ADDITION, AND **T=**TRIGONOMETRIC FUNCTION CALCULATION.

|                                                                      | Μ  | А  | Т  |

|----------------------------------------------------------------------|----|----|----|

| Adaptive $GDSC_{2,4,8,16,32}$ with linear interpolation <sup>*</sup> | 70 | 30 | 20 |

| Non-adaptive GDSC <sub>2,4,8,16,32</sub>                             | 12 | 16 | 0  |

\* The mathematical operations required for updating arguments of trigonometric functions and frequency dependent gains has been neglected.

suggested PLL structure and those proposed in [27] and [28], and Table IV compares the mathematical operations required for the implementation of the non-adaptive GDSC operator with those of the adaptive GDSC with linear interpolation. Based on these results, it is immediate to conclude that the EGDSC-PLL and the structure proposed in [27] demand the lowest and highest computational efforts, respectively.

#### VI. SUMMARY AND CONCLUSION

In this paper, an efficient and low-cost implementation of GDSC-PLL was proposed. The suggested PLL structure is based on employing a non-adaptive GDSC operator as the SRF-PLL prefiltering stage and two compensators, called the PEC and AEC, to correct the phase shift and amplitude scaling caused by the non-adaptive GDSC operator under off-nominal grid frequencies.

It was shown that the PEC and AEC can be simply implemented using very few mathematical operations. In the PEC design no assumption about the value of the grid frequency has been made. Therefore, the PEC can effectively compensate the phase shift caused by the non-adaptive GDSC operator regardless of the value of grid frequency. The design of the AEC, however, was made under the assumption that the grid frequency varies within a specific range. Therefore, the AEC cannot effectively correct the amplitude scaling caused by the non-adaptive GDSC operator for any value of grid frequency; however, as it was shown, it works well in the range of  $50 \pm 10$  Hz, which is wider than the allowable range of grid frequency variations defined in international standards.

The small-signal model of the proposed PLL was also presented. It was demonstrated that this model is very accurate and can be very helpful in the selection of the control parameters. The closed-loop transfer function, which was obtained using this model, also proved that the proposed PLL is stable for positive values of the control parameters.

Finally, the effectiveness of the suggested PLL structure was evaluated through simulation and experimental results. It was verified that the PEC and AEC can effectively compensate the phase shift and amplitude scaling caused by the PLL prefiltering stage, i.e., the non-adaptive GDSC operator. It was also shown that the proposed PLL provides a fast transient response and a good disturbance rejection capability. Through a comparison between the proposed PLL structure and the conventional GDSC-PLLs, it was also highlighted that the former requires a much lower computational effort in digital implementation.

#### REFERENCES

- R. Santos Filho, P. Seixas, P. Cortizo, and A. Souza, "Comparison of three single-phase PLL algorithms for UPS applications," *IEEE Trans. Ind. Electron.*, vol. 55, no. 8, pp. 2923-2932, Aug. 2008.

- [2] V. Saez, A. Martin, M. Rizo, A. Rodriguez, E. Bueno, A. Hernandez, and A. Miron, "FPGA implementation of grid synchronization algorithms based on DSC, DSOGI-QSG and PLL for distributed power generation systems," *Proc. IEEE ISIE*, 2010, pp. 2765-2770.

- [3] D. Jovcic, "Phase locked loop system for FACTS," IEEE Trans. Power Syst., vol. 18, no. 3, pp. 1116-1124, Aug. 2003.

- [4] S. Li, X. Wang, Z. Yao, T. Li, and Z. Peng, "Circulating current suppressing strategy for MMC-HVDC based on nonideal proportional resonant controllers under unbalanced grid conditions," *IEEE Trans. Power Electron.*, vol. 30, no. 1, pp. 387-397, Jan. 2015.

- [5] J. Z. Zhou, H. Ding, S. Fan, Y. Zhang, A. M. Gole, "Impact of short-circuit ratio and phase-locked-loop parameters on the small-signal behavior of a VSC-HVDC converter," *IEEE Trans. Power Del.*, vol. 29, no. 5, pp. 2287-2296, May 2014.

- [6] F. M. Gardner, Phaselock techniques. John Wiley & Sons, Inc., 2005.

- [7] S. Golestan, M. Monfared, F. D. Freijedo, and J. M. Guerrero, "Performance improvement of a prefiltered synchronous reference frame PLL by using a PID type loop filter," *IEEE Trans. Ind. Electron.*, vol. 61, no. 7, pp. 3469-3479, Jul. 2014.

- [8] F. Gonzalez-Espin, E. Figueres, and G. Garcera, "An adaptive synchronous-reference-frame phase-locked loop for power quality improvement in a polluted utility grid," *IEEE Trans. Ind. Electron.*, vol. 59, no. 6, pp. 2718-2731, Jun. 2012.

- [9] F. D. Freijedo, A. G. Yepes, O. Lopez, A. Vidal, and J. Doval-Gandoy, "Three-phase PLLs with fast postfault retracking and steady-state rejection of voltage unbalance and harmonics by means of lead compensation," *IEEE Trans. Power Electron.*, vol. 26, no. 1, pp. 85-97, Jan. 2011.

- [10] M. Karimi Ghartemani, S. A. Khajehoddin, P. K. Jain, and A. Bakhshai, "Problems of startup and phase jumps in PLL systems," *IEEE Trans. Power Electron.*, vol. 27, no. 4, pp. 1830-1838, Apr. 2012.

- [11] L. Wang, Q. Jiang, L. Hong, C. Zhang, and Y. Wei, "A novel phaselocked loop based on frequency detector and initial phase angle detector," *IEEE Trans. Power Electron.*, vol. 28, no. 10, pp. 4538-4549, Oct. 2013.

- [12] N. R. N. Ama, F. O. Martinz, L. Matakas, and F. Kassab, "Phase-locked loop based on selective harmonics elimination for utility applications, IEEE Trans. Power Electron., vol. 28, no. 1, pp. 144-153, Jan. 2013.

- [13] I. Carugati, S. Maestri, P. G. Donato, D. Carrica, and M. Benedetti, "Variable sampling period filter PLL for distorted three-phase systems," *IEEE Trans. Power Electron.*, vol. 27, no. 1, pp. 321-330, Jan. 2012.

- [14] J. Wang, J. Liang, F. Gao, L. Zhang, and Z. Wang, "A method to improve the dynamic performance of moving average filter based PLL," *IEEE Trans. Power Electron.*, vol. PP, no. 99, pp. 1-14, Dec. 2014.

- [15] S. Golestan, M. Ramezani, J. M. Guerrero, F. D. Freijedo, and M. Monfared, "Moving average filter based phase-locked loops: performance analysis and design guidelines," *IEEE Trans. Power Electron.*, vol. 29, no. 6, pp. 2750-2763, Jun. 2014.

- [16] S. Golestan, F. D. Freijedo, A. Vidal, J. M. Guerrero, and J. Doval-Gandoy, "A quasi-type-1 phase-locked loop structure," *IEEE Trans. Power Electron.*, vol. 29, no. 12, pp. 6264-6270, Dec. 2014.

- [17] S. Golestan, J. M. Guerrero, and A. M. Abusorrah "MAF-PLL With Phase-Lead Compensator," *IEEE Trans. Ind. Electron.*, vol. PP, no. 99, pp. 1-5, Dec. 2014.

- [18] M. Rashed, C. Klumpner, and G. Asher, "Repetitive and resonant control for a single-phase grid-connected hybrid cascaded multilevel converter," *IEEE Trans. Power Electron.*, vol. 28, no. 5, pp. 2224-2234, May 2013.

- [19] X. Guo, W. Wu, and Z. Chen, "Multiple-complex coefficient-filter-based phase-locked loop and synchronization technique for three-phase grid interfaced converters in distributed utility networks," *IEEE Trans. Ind. Electron.*, vol. 58, no. 4, pp. 1194-1204, Apr. 2011.

- [20] W. Li, X. Ruan, C. Bao, D. Pan, and X. Wang, "Grid synchronization systems of three-phase grid-connected power converters: a complex vector-filter perspective," *IEEE Trans. Ind. Electron.*, vol. 61, no. 4, pp. 1855-1870, Apr. 2014.

- [21] F. Neves, H. de Souza, F. Bradaschia, M. Cavalcanti, M. Rizo, and F. Rodriguez, "A space-vector discrete Fourier transform for unbalanced and distorted three-phase signals," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2858-2867, Aug. 2010.

- [22] P. Rodriguez, R. Teodorescu, I. Candela, A. V. Timbus, M. Liserre, and F. Blaabjerg, "New positive-sequence voltage detector for grid synchronization of power converters under faulty grid conditions," *Proc. IEEE PESC*, Jun. 2006, pp. 1-7.

- [23] J. Svensson and M. Bongiorno, A. Sannino, "Practical implementation of delayed signal cancellation method for phase-sequence separation," *IEEE Trans. Power Del.*, vol. 22, no. 1, pp. 18-26, Jan. 2007.

- [24] M. Bongiorno, J. Svensson, and A. Sannino, "Effect of sampling frequency and harmonics on delay-based phase-sequence estimation method," *IEEE Trans. Power Del.*, vol. 23, no. 3, pp. 1664-1672, Jul. 2008.

- [25] H. Awad, J. Svensson, and M. J. Bollen, "Tuning software phase-locked loop for series-connected converters," *IEEE Trans. Power Del.*, vol. 20, no. 1, pp. 300-308, Jan. 2005.

- [26] E. Bueno, F. J. Rodrguez, F. Espinosa, and S. Cbreces, "SPLL design to flux oriented of a VSC interface for wind power applications," *Proc. IEEE IECON*, 2005, pp. 2451-2456.

- [27] F. A. S. Neves, M. C. Cavalcanti, H. E. P. de Souza, F. Bradaschia, E. J. Bueno, and M. Rizo, "A generalized delayed signal cancellation method for detecting fundamental-frequency positive-sequence threephase signals," *IEEE Trans. Power Del.*, vol. 25, no. 3, pp. 1816-1825, Jul. 2010.

- [28] F. Wang, and Y. W. Li, "Grid synchronization PLL based on cascaded delayed signal cancellation," *IEEE Trans. Power Electron.*, vol. 26, no. 7, pp. 1987-1997, Jul. 2011.

- [29] Y. F. Wang and Y. W. Li, "Analysis and digital implementation of cascaded delayed-signal-cancellation PLL," *IEEE Trans. Power Electron.*, vol. 26, no. 4, pp. 1067-1080, Apr. 2011.

- [30] F. A. S. Neves, H. E. P. de Souza, M. C. Cavalcanti, F. Bradaschia, and E. Bueno, "Digital filters for fast harmonic sequence components separation of unbalanced and distorted three-phase signals," *IEEE Trans. Ind. Electron.*, vol. 59, no. 10, pp. 3847-3859, Oct. 2012.

- [31] J. W. Choi, Y. K. Kim, and H. G. Kim, "Digital PLL control for single phase photovoltaic system," *Proc. Inst. Elect. Eng. Elect. Power Appl.*, vol. 153, no. 1, pp. 40-46, Jan. 2006.

- [32] D. N. Zmood, D. G. Holmes, and G. H. Bode, "Frequency-domain analysis of three-phase linear current regulators," *IEEE Trans. Ind. Appl.*, vol. 37, no. 2, pp. 601-610, Mar./Apr. 2001.

- [33] F. D., Freijedo, J. Doval-Gandoy, O. Lopez, and E. Acha, "Tuning of phase-locked loops for Power converters under distorted utility conditions," *IEEE Trans. Ind. Appl.*, vol. 45, no. 6, pp 2039-2047, Nov./Dec. 2009.

- [34] Y. F. Wang, and Y. W. Li, "A grid fundamental and harmonic component detection method for single-phase systems," *IEEE Trans. Power Electron.*, vol. 28, no. 5, pp. 2204-2213, Jul. 2013.

- [35] European Standard EN-50160. Voltage Characteristics of Public Distribution Systems, CENELEC Std., Nov. 1999.

- [36] S. Golestan, M. Monfared, F. D. Freijedo, and J. M. Guerrero, "Advantages and challenges of a type-3 PLL," *IEEE Trans. Power Electron.*, vol. 28, no. 11, pp. 4985-4997, Nov. 2013.

- [37] M. McGranaghan and G. Beaulieu, "Update on IEC 61000-3-6: Harmonic emission limits for customers connected to MV, HV and EHV," in *Proc. IEEE Transmission and Distribution Conf. Exhibit.*, May 2006, pp. 1158-1161.

**Saeed Golestan** (M'11-SM'15) received the B.Sc. degree in electrical engineering from Shahid Chamran University of Ahvaz, Iran, in 2006, and the M.Sc. degree in electrical engineering from Amirkabir University of Technology, Tehran, Iran, in 2009.

In 2009, he joined the Department of Electrical Engineering, Abadan Branch, Islamic Azad University, Iran as a lecturer, where he is now head of department. His research interests include phaselocked loop and nonlinear filtering techniques for power and energy applications, power quality mea-

surement and improvement, estimation of power system parameters, and microgrid.

**Francisco D. Freijedo** received the M.Sc. degree in Physics from the University of Santiago de Compostela, Santiago de Compostela, Spain, in 2002 and the Ph.D. degree from the University of Vigo, Vigo, Spain, in 2009.

From 2005 to 2011, he was a Lecturer with the Department of Electronics Technology of the University of Vigo. From 2011 to 2014, he worked in the wind power industry as a control engineer.

Since 2014, he is a Postdoctoral Researcher at the Department of Energy Technology of Aalborg

University. His main research interests are in the areas of ac power conversion.

**Ana Vidal** (S'10) received the M.Sc. degree from the University of Vigo, Vigo, Spain, in 2010, where she is currently working toward the Ph.D. degree in the Applied Power Electronics Technology Research Group, University of Vigo.

Since 2009, she has been with the Applied Power Electronics Technology Research Group. Her research interests include control of grid-connected converters and distributed power generation systems.

**Alejandro G. Yepes** (S'10-M'12) received the M.Sc. and the Ph.D. degree from University of Vigo, Vigo, Spain in 2009 and 2011, respectively.

Since 2008 he is with the Applied Power Electronics Technology Research Group, University of Vigo. His main research interests include control of switching power converters and ac drives.

Josep M. Guerrero (S'01-M'04-SM'08-F'15) received the B.S. degree in telecommunications engineering, the M.S. degree in electronics engineering, and the Ph.D. degree in power electronics from the Technical University of Catalonia, Barcelona, in 1997, 2000 and 2003, respectively. Since 2011, he has been a Full Professor with the Department of Energy Technology, Aalborg University, Denmark, where he is responsible for the Microgrid Research Program. From 2012 he is a guest Professor at the Chinese Academy of Science and the Nanjing

University of Aeronautics and Astronautics; from 2014 he is chair Professor in Shandong University; and from 2015 he is a distinguished guest Professor in Hunan University.

His research interests is oriented to different microgrid aspects, including power electronics, distributed energy-storage systems, hierarchical and cooperative control, energy management systems, and optimization of microgrids and islanded minigrids. Prof. Guerrero is an Associate Editor for the IEEE TRANSACTIONS ON POWER ELECTRONICS, the IEEE TRANS-ACTIONS ON INDUSTRIAL ELECTRONICS, and the IEEE Industrial Electronics Magazine, and an Editor for the IEEE TRANSACTIONS on SMART GRID and IEEE TRANSACTIONS on ENERGY CONVERSION. He has been Guest Editor of the IEEE TRANSACTIONS ON POWER ELECTRONICS Special Issues: Power Electronics for Wind Energy Conversion and Power Electronics for Microgrids; the IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS Special Sections: Uninterruptible Power Supplies systems, Renewable Energy Systems, Distributed Generation and Microgrids, and Industrial Applications and Implementation Issues of the Kalman Filter; and the IEEE TRANSACTIONS on SMART GRID Special Issue on Smart DC Distribution Systems. He was the chair of the Renewable Energy Systems Technical Committee of the IEEE Industrial Electronics Society. In 2014 he was awarded by Thomson Reuters as Highly Cited Researcher, and in 2015 he was elevated as IEEE Fellow for his contributions on "distributed power systems and microgrids."

**Jesus Doval-Gandoy** (M'99) received the M.Sc. degree from Polytechnic University of Madrid, Madrid, Spain, in 1991 and the Ph.D. degree from the University of Vigo, Vigo, Spain in 1999.

From 1991 till 1994 he worked at industry. He is currently an Associate Professor at the University of Vigo. His research interests are in the areas of ac power conversion.