# **Aalborg Universitet**

# Virtual Impedance Based Stability Improvement for DC Microgrids with Constant Power Loads

Lu, Xiaonan; Sun, Kai; Huang, Lipei; Guerrero, Josep M.; Quintero, Juan Carlos Vasquez; Xing, Yan

Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE)

DOI (link to publication from Publisher): 10.1109/ECCE.2014.6953759

Publication date: 2014

Document Version Early version, also known as pre-print

Link to publication from Aalborg University

Citation for published version (APA):

Lu, X., Sun, K., Huang, L., Guerrero, J. M., Vasquez, J. C., & Xing, Y. (2014). Virtual Impedance Based Stability Improvement for DC Microgrids with Constant Power Loads. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE) (pp. 2670-2675). IEEE Press. DOI: 10.1109/ECCE.2014.6953759

### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- ? You may not further distribute the material or use it for any profit-making activity or commercial gain ? You may freely distribute the URL identifying the publication in the public portal ?

Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# Virtual Impedance Based Stability Improvement for DC Microgrids with Constant Power Loads

Xiaonan Lu

Department of Electrical

Engineering & Computer

Science

University of Tennessee

Knoxville, TN, US

Email: xlu13@utk.edu

Kai Sun, Lipei Huang Department of Electrical Engineering Tsinghua University Beijing, China Josep M. Guerrero, Juan C.

Vasquez

Department of Energy

Technology

Aalborg University

Aalborg, Denmark

Yan Xing

Jiangsu Key Lab of New

Energy and Power Conversion

Nanjing University of

Aeronautics and Astronautics

Nanjing, China

Abstract—DC microgrid provides an efficient way to integrate different kinds of renewable energy sources with DC couplings. In this paper, in order to improve the stability of DC microgrids with constant power loads (CPLs), a virtual impedance based method is proposed. The CPLs have inherent instability issues induced by negative incremental impedances. This negative impedance makes the system poorly damped and the stability is thereby degraded. To enhance the system stability, virtual impedance based stabilizer comprised of series-connected inductance and resistance is employed. In particular, two types of stabilizers are used. Type I stabilizer locates at the output capacitor branch, and Type II stabilizer locates at the output inductance branch. Meanwhile, considering that the parallel interfacing converters are commonly in parallel in a microgrid, droop control is taken into account here. To validate the stability with the above stabilizers in a DC microgrid with parallel interfacing converters and CPL, the impedance matching approach is employed. The output impedance of the source converter and input impedance of the load are calculated respectively, and the influence of droop control, negative incremental impedance of CPL, proposed stabilizers are considered in the calculation of the impedance. It is demonstrated that with the proposed stabilizers, the instable poles can be moved to the stable region in the frequency domain. Simulation model with three interfacing converters is implemented MATLAB/Simulink to verify the proposed method.

### I. INTRODUCTION

With the increasing penetration of renewable energy into modern electric grid, the concept of microgrid was proposed several years ago and has been intensively studied recently [1]. Considering the AC nature of the conventional power system, most of the research is focused on AC microgrids [2]-[5]. In order to integrate various renewable energy sources with dc couplings, the solution of dc microgrids has become an attracting approach [6]-[11]. In both AC and DC microgrid, the renewable energy sources are connected to the common bus by using the interfacing converters. Considering the distributed configuration of the system, the

power electronics interfacing converters are usually connected in parallel. In order to obtain proper load power sharing among different sources, droop control as a decentralized method is commonly employed in the control diagram of the interfacing converters [1]-[8].

Stability problems should be noticed in order to enhance the performance of a dc microgrid. Especially in the system with constant-power loads (CPLs), the stability issues are required to be further studied [12]-[14]. In a microgrid, the CPLs, also known as active loads, enable the power conditioning at the load side. Different from the passive loads, e.g. incandescent lighting and resistive heaters, the CPLs consume constant amount of power regardless what the input voltage is [14]. The impact of CPLs on the system stability is induced by its negative incremental impedance. The negative impedance makes the system poorly damped and can employ unstable poles into the control system [12]-[14]. The existing methods to deal with the above problem are mainly focused on single interfacing converter. However, in a practical microgrid, multiple interfacing converters usually coexist and are connected in parallel. Hence, it is necessary to extend the research on CPL and its damping method to the multiple converter system. Meanwhile, the commonly used droop control should be taken into account when discussing the stabilization of the microgrid with CPLs.

Virtual impedances are commonly employed in the control diagram of the interfacing converters to achieve the functionalities of matching the output impedance at the base or harmonic frequencies [15] and resonance damping [16]. In this paper, the virtual impedance based stabilization of dc microgrids with CPLs is proposed. The virtual impedance used here is comprised of series-connected resistance and inductance. Two types of stabilizers are employed. One is based on capacitor voltage feedback, and the other is based on inductance current feedback. The detailed model of the control system, including droop control for load power sharing and inherent negative incremental impedance of

CPL, are studied. The output impedance of interfacing converter ( $Z_0$ ) and the load impedance of CPL ( $Z_{load}$ ) are calculated. By using the judging principle of impedance matching [17], the stability of the control system is analyzed. Particularly, the dominant poles of  $(1+Z_0/Z_{load})^{-1}$  are obtained and tested. If and only if all of the poles are located on the left half of s plane, the system is stable. The unstable poles in the s domain can be found without the virtual impedance based stabilization. After activating the proposed virtual impedance based method, the unstable poles are forced to move into the stable region. Hence, the system stability of dc microgrid with CPL can be guaranteed.

# II. MODELING OF THE SYSTEM WITH THE PROPOSED STABILIZERS BASED ON VIRTUAL IMPEDANCE

The incremental impedance of the CPL can be calculated as follows [12]:

$$\frac{\partial v_{\text{load}}}{\partial \dot{t}_{\text{load}}}\Big|_{(V_{\text{load}}, I_{\text{load}})} = \frac{\partial}{\partial \dot{t}_{\text{load}}} \left(\frac{P_{\text{load}}}{\dot{t}_{\text{load}}}\right)\Big|_{(V_{\text{load}}, I_{\text{load}})} = -\frac{V_{\text{load}}}{I_{\text{load}}} < 0 \tag{1}$$

where  $v_{load}$ ,  $i_{load}$  and  $p_{load}$  are the load voltage, current and power, respectively.

It is seen from (1) that the CPL has negative incremental impedance, which will make the system poorly damped and influence the system stability.

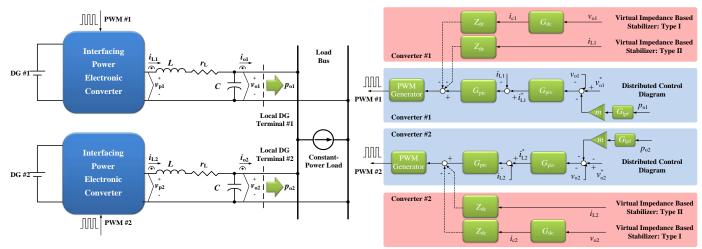

The system configuration and the control diagram for parallel interfacing converters are shown in Fig. 1. First, the system without the stabilizers is analyzed as follows. For converter # (i = 1, 2, ..., n), it is derived that

$$V_{\text{pi}} = sLI_{\text{Li}} + I_{\text{Li}}r_{\text{L}} + V_{\text{oi}}, sCV_{\text{oi}} = I_{\text{Li}} - I_{\text{oi}}$$

(2)

$$I_{\text{Li}}^* = G_{\text{piv}} \cdot (V_{\text{oi}}^* - V_{\text{oi}} - m_{\text{i}} G_{\text{lpf}} P_{\text{oi}}), V_{\text{pi}} = G_{\text{pic}} \cdot (I_{\text{Li}}^* - I_{\text{Li}})$$

(3)

where  $G_{\rm piv}$  and  $G_{\rm pic}$  are the PI controllers of the capacitor voltage and inductance current,  $V_{\rm pi}$  is the inverter output voltage,  ${V_{\rm oi}}^*$  and  ${I_{\rm Li}}^*$  are the reference values of capacitor voltage and inductance current,  $m_{\rm i}$  is the droop coefficient, and  $G_{\rm lpf}$  is the low-pass filter (LPF) used in droop control.

Perturbing (2), the small signal model is derived as follows:

$$\hat{V}_{pi} = sL\hat{I}_{Li} + \hat{I}_{Li}r_{L} + \hat{V}_{pi}, sC\hat{V}_{pi} = \hat{I}_{Li} - \hat{I}_{pi}$$

(4)

Meanwhile, for the output power of the interfacing converter, the following relationship and its small signal expression can be reached:

$$p_{\text{oi}} = v_{\text{oi}} \cdot i_{\text{oi}} \tag{5}$$

$$\hat{p}_{oi} = V_{oi} \cdot \hat{i}_{oi} + I_{oi} \cdot \hat{v}_{oi} \tag{6}$$

Converting (6) into the frequency domain and then combining the result and the perturbed results of (3), it is obtained:

$$\hat{I}_{\rm Li}^* = -G_{\rm piv} \cdot (\hat{V}_{\rm oi} + m_{\rm i}G_{\rm lpf}V_{\rm oi}\hat{I}_{\rm oi} + m_{\rm i}G_{\rm lpf}I_{\rm oi}\hat{V}_{\rm oi}), \, \hat{V}_{\rm pi} = G_{\rm pic} \cdot (\hat{I}_{\rm Li}^* - \hat{I}_{\rm Li}) \,\,\, (7)$$

Combining (4) and (7), the output impedance of converter #i can be calculated as

$$Z_{oi} = \frac{G_{pic}(1 + m_i G_{piv} G_{lpf} V_{oi}) + sL + r_L}{1 + sC(sL + r_L) + sCG_{pic} + G_{pic} G_{piv}(1 + m_i G_{lpf} I_{oi})}$$

(8)

Since parallel interfacing converters are taken into account, the output impedance of each converter can be merged. Assuming that the parameters of each converter are the same, it is derived that the equivalent output impedance of the parallel interfacing converters is

$$Z_{\text{oeq}} = \frac{Z_{\text{oi}}}{n} = \frac{G_{\text{pic}}(1 + m_{i}G_{\text{piv}}G_{\text{lpf}}V_{\text{oi}}) + sL + r_{\text{L}}}{n \cdot [1 + sC(sL + r_{\text{L}}) + sCG_{\text{pic}} + G_{\text{pic}}G_{\text{piv}}(1 + m_{i}G_{\text{lpf}}I_{\text{oi}})]}$$

(9)

The above is the derivation for the converter side. For the load side, considering the constant power nature, the incremental impedance is shown in (1), namely

$$Z_{\text{load}} = -\frac{V_{\text{load}}}{I_{\text{load}}} = -\frac{V_{\text{oi}}}{\text{n}I_{\text{oi}}}$$

(10)

In order to test the system stability, the principle of impedance matching is employed. Particularly, all of the dominant poles of  $(1+Z_{\rm oeq}/Z_{\rm load})^{-1}$  should be located in the stable region [17]. By using the Tustin bilinear transform, (9) and (10) can be discretized from s domain to z domain, and the dominant poles of  $(1+Z_{\rm oeq}/Z_{\rm load})^{-1}$  can be reached. Due to the influence of negative incremental impedance, the unstable dominant poles appear when no damping method is employed. In the certain system which is under test, the unstable poles  $p_1$  and  $p_2$  are  $0.96 \pm j0.32$  ( $|p_1| = |p_2| = 1.012 > 1$ ), which locate outside the unit circle.

## III. PROPOSED VIRTUAL IMPEDANCE BASED STABILIZER

In order to make the unstable poles move into the stable region, the virtual impedance based stabilizer is proposed. The virtual impedance used here is comprised of seriesconnected virtual resistance and inductance. Particularly, two types of stabilizers are employed, as shown in Fig. 1. Type I stabilizer is realized by capacitor voltage feedback, and Type II stabilizer is realized by inductance current feedback. The effect of the virtual impedance based stabilizer on system stability is analyzed below.

When considering the two types of virtual impedance based stabilizers in the control diagram in Fig. 1, (3) is modified as

$$I_{Li}^{*} = G_{piv} \cdot (V_{oi}^{*} - V_{oi} - m_{i}G_{lpf}P_{oi})$$

$$V_{pi} = G_{pic} \cdot (I_{Li}^{*} - I_{Li}) - k_{1} \cdot G_{dc}Z_{dc}V_{oi} - k_{2} \cdot Z_{dc}I_{Li}$$

(11)

where  $k_1$  and  $k_2$  represent the type of stabilizer, and the value of  $(k_1, k_2)$  can be only (1, 0) or (0, 1). When  $k_1$  equals 1 and  $k_2$  equals 0, Type I stabilizer is selected. When  $k_1$  equals 0 and  $k_2$  equals 1, Type II stabilizer is selected.

Meanwhile,  $G_{dc}$  and  $Z_{dc}$  are shown as:

$$G_{\rm dc} = \frac{I_{\rm Ci}}{V_{\rm ci}} = sC, Z_{\rm dc} = sL_{\rm dc} + R_{\rm dc}$$

(12)

where  $L_{dc}$  is the virtual inductance, and the  $R_{dc}$  is the virtual resistance

Fig. 1. System configuration and control diagram for parallel interfacing converters considering the virtual impedance based stabilizers.

Perturbing (11), it yields

$$\hat{I}_{Li}^{*} = -G_{piv} \cdot (\hat{V}_{oi} + m_{i}G_{lpf}V_{oi}\hat{I}_{oi} + m_{i}G_{lpf}I_{oi}\hat{V}_{oi})$$

$$\hat{V}_{pi} = G_{pic} \cdot (\hat{I}_{Li}^{*} - \hat{I}_{Li}) - k_{1} \cdot G_{dc}Z_{dc}\hat{V}_{oi} - k_{2} \cdot Z_{dc}\hat{I}_{Li}$$

(13)

Combining (4) and (13), it is derived that

$$Z_{\text{oi}}^{'} = \frac{G_{\text{pic}}(1 + m_{\text{i}}G_{\text{piv}}G_{\text{lpf}}V_{\text{oi}}) + sL + r_{\text{L}} + k_{2}Z_{\text{dc}}}{1 + sC(sL + r_{\text{L}}) + sCG_{\text{pic}} + G_{\text{pic}}G_{\text{piv}}(1 + m_{\text{i}}G_{\text{lpf}}I_{\text{oi}}) + (k_{1} + k_{2})G_{\text{dc}}Z_{\text{dc}}}$$

Similar to the analysis in Section II, if merging the output impedance of the parallel interfacing converters and noticing that  $k_1 + k_2 \equiv 1$ ,

$$Z_{\text{oeq}} = \frac{G_{\text{pic}}(1 + m_i G_{\text{piv}} G_{\text{lpf}} V_{\text{oi}}) + sL + r_L + k_2 Z_{\text{dc}}}{n \cdot [1 + sC(sL + r_L) + sCG_{\text{pic}} + G_{\text{pic}} G_{\text{piv}} (1 + m_i G_{\text{lpf}} I_{\text{oi}}) + (k_1 + k_2) G_{\text{dc}} Z_{\text{dc}}]}$$

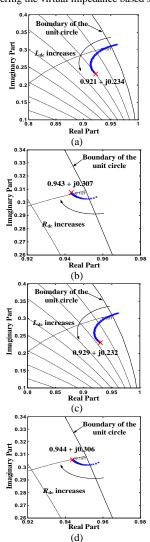

Hence, by discretizing the transfer functions, the dominant poles of  $(1+Z'_{\rm oeq}/Z_{\rm load})^{-1}$  can be obtained. The system parameters are shown in Table I. Assuming three interfacing converters are used, by using the principle of impedance matching, the stability of the control system with virtual impedance based stabilizer is verified. As shown in Fig. 2, when changing the value of the virtual inductance and resistance, the dominant poles are gradually moved to the stable region.

TABLE I System Parameters

| Item                                         | Symbol        | Value | Unit |

|----------------------------------------------|---------------|-------|------|

| Input Voltage                                | $v_{\rm in}$  | 200   | V    |

| Reference of Output Voltage                  | $v_{ m oref}$ | 600   | V    |

| Output Inductance                            | L             | 5     | mH   |

| Parasitic Resistance of Output<br>Inductance | $r_{ m L}$    | 0.06  | Ω    |

| Output capacitor                             | С             | 20    | μF   |

| Number of Converters                         | n             | 3     | -    |

| Sampling Time                                | $T_{\rm s}$   | 100   | μs   |

Fig. 2. Closed-loop dominant poles of  $(1+Z'_{oeq}/Z_{load})^{-1}$  with Type I/II virtual impedance based stabilizers.

(a)  $R_{dc}$ =2  $\Omega$ ,  $L_{dc}$ =0.5~6 mH (original result). (b)  $R_{dc}$ =2  $\Omega$ ,  $L_{dc}$ =0.5~6 mH (zoom-in result). (c)  $R_{dc}$ =0~12  $\Omega$ ,  $L_{dc}$ =6 mH (original result). (d)  $R_{dc}$ =0~12  $\Omega$ ,  $L_{dc}$ =6 mH (zoom-in result).

## IV. SIMULATION RESULTS

Simulation tests based on MATLAB/Simulink are performed to validate the proposed stabilizer. Here, the CPL is shared by the parallel interfacing converters.

#### Case I: Stabilizer activation

Take Converter #1 as an example. For Type I stabilizer, the waveform of dc output voltage is shown in Fig. 3 (a). During the period of  $20 \sim 40$  s, the stabilizer is activated. It is shown that before t=20 s, the dc voltage is unstable. When the stabilizer becomes active, the dc voltage keeps stable and maintains at its reference value 600 V. At t=40 s, since the stabilizer becomes inactive, the dc voltage turns back to the unstable status. For Type II stabilizer, the waveform of dc output voltage is shown in Fig. 3 (b). It is also seen that the system stability can be guaranteed by turning on the virtual impedance based stabilizer.

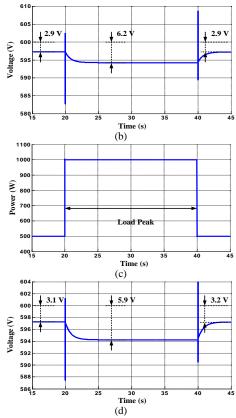

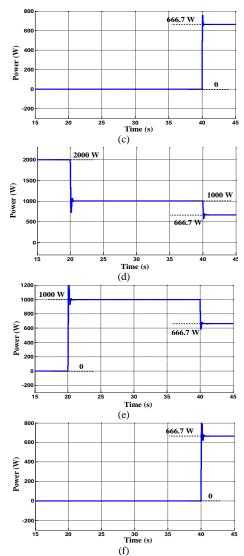

# Case II: Load peak

The performance of stabilizer is tested during load peak. Here, two interfacing converters are employed. During the period of 20 ~ 40 s, the power of the CPL is changed from 1000 W to 2000 W. Take Converter #1 as an example. By keeping Type I stabilizer active, the output power waveform is shown in Fig. 4 (a). Since droop control is used, the load power is equally shared and the output power of Converter #1 is changed from 500 W to 1000 W, which is half of the load power. Meanwhile, the dc output voltage waveforms are shown in Fig. 4 (b). It is shown that the dc voltage deviation is produced by using droop control. During the load peak, the dc voltage deviation increases from 2.9 V to 6.2 V. Similar results for Type II stabilizer can be found in Fig. 4 (c) and (d). It is seen that by using Type I/II stabilizers, the transient stability of the parallel converter system with CPLs can be ensured during load peaks.

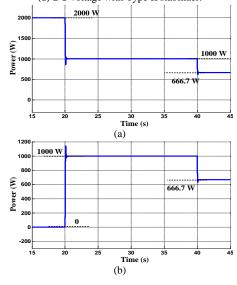

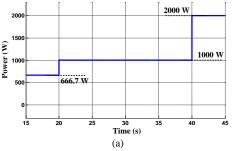

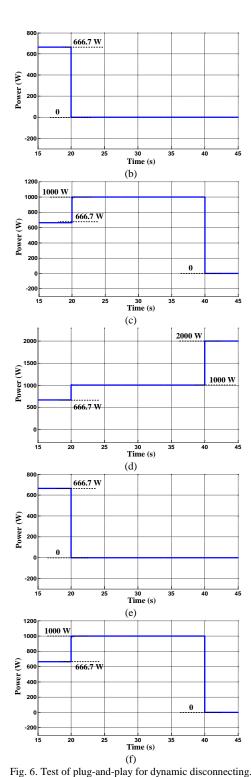

## Case III: Plug-and-play of the converter interfaces

The responses for plug-and-play are also tested to validate the performance of the proposed two types of stabilizers. Three parallel interfacing converters are used here. In Fig. 5 (a) - (c), Type I stabilizer keeps in use during the whole process. Before t = 20 s, only Converter #1 generates power for the load. At t = 20 s and 40 s, Converter #2 and #3 start sequentially. It is seen that the output power of Converter #1 decreases since the load power is shared by more converters. At the same time, the plug-and-play performance of the converter system with Type II stabilizer is also tested, as shown in Fig. 5 (d) - (f). It is demonstrated that by using Type I/II stabilizers, the system stability during the plug-and-play process can be maintained. The above results in Fig. 5 validate the effectiveness of Type I and Type II stabilizers during dynamic connecting process. Similar results are shown in Fig. 6 to test the performance of two types of stabilizers in the dynamic disconnecting process. It is also seen that with the proposed stabilizers activated, the system stability can be guaranteed.

## V. CONCLUSION

In this paper, two types of virtual impedance based stabilizers are proposed to enhance the stability of dc microgrids with CPLs. Particularly, Type I stabilizer is achieved based on capacitor voltage feedback, and Type II stabilizer is achieved based on inductance current feedback. Since the interfacing converters in dc microgrids are connected in parallel, droop control for proper output power sharing is taken into account. Meanwhile, the principle of impedance matching is employed to test the stability of the parallel inverter system with CPLs. By using the above stabilizers, the instable poles of  $(1+Z'_{oeq}/Z_{load})^{-1}$  induced by the negative incremental impedance of the CPL are forced to move into the stable region. Hence, the system stability can be enhanced.

#### ACKNOWLEDGMENT

The authors would like to thank the National Natural Science Foundation of China (51177083) to support the research of this paper.

Fig. 4. Test of load peak.

(a) Output power of converter #1 with Type I stabilizer.

(b) DC voltage with Type I stabilizer.

(c) Output power of converter #1 with Type II stabilizer. (d) DC voltage with Type II stabilizer.

Fig. 5. Test of plug-and-play for dynamic connecting. (a) Output power of converter #1 with Type I stabilizer.

(b) Output power of converter #1 with Type I stabilizer.

(c) Output power of converter #1 with Type I stabilizer.

(d) Output power of converter #1 with Type II stabilizer. (e) Output power of converter #1 with Type II stabilizer. (f) Output power of converter #1 with Type II stabilizer.

(a) Output power of converter #1 with Type I stabilizer.

(b) Output power of converter #1 with Type I stabilizer.

(c) Output power of converter #1 with Type I stabilizer.

(d) Output power of converter #1 with Type II stabilizer.

(e) Output power of converter #1 with Type II stabilizer.

(f) Output power of converter #1 with Type II stabilizer.

#### REFERENCES

- R. Lasseter, A. Akhil, C. Marnay, J. Stevens, et al, "The certs microgrid concept - white paper on integration of distributed energy resources," *Technical Report*, U.S. Department of Energy, 2002.

- [2] Y. W. Li and C. N. Kao, "An accurate power control strategy for power-electronics-interfaced distributed generation units operating in a low-voltage multibus microgrid," *IEEE Trans. Power Electron.*, vol. 24, no. 12, pp. 2977-2988, 2009.

- [3] Q. C. Zhong, "Robust droop controller for accurate proportional load sharing among inverters operated in parallel," *IEEE Trans. Ind. Electron.*, vol. 60, no. 4, pp. 1281-1290, 2013.

- [4] J. M. Guerrero, J. C. Vasquez, J. Matas, G. G. De Vicuña and M. Castilla, "Hierarchical control of droop-controlled AC and DC microgrids a general approach toward standardization," *IEEE Trans. Ind. Electron.*, vol. 58, no. 1, pp. 158-172, 2011.

- [5] N. Bottrell, M. Prodanovic and T. C. Green, "Dynamic stability of a microgrid with an active load," *IEEE Trans. Power Electron.*, vol. 28, no. 11, pp. 5107-5119, 2013.

- [6] D. Dong, I. Cvetkovic, D. Boroyevich, W. Zhang, R. Wang, et al, "Grid-interface bi-directional converter for residential DC distribution systems – part one: high-density two-stage topology," *IEEE Trans. Power Electron.*, vol. 28, no. 4, pp. 1655-1666, 2013.

- [7] X. Lu, J. M. Guerrero and K. Sun, "An improved control method for dc microgrids based on low bandwidth communication with dc bus voltage restoration and enhanced current sharing accuracy," *IEEE Trans. Power Electron.*, vol. 29, no. 4, pp. 1800-1812, 2014.

- [8] X. Lu, K. Sun, J. M. Guerrero, J. C. Vasquez and L. Huang, "State-of-charge balance using adaptive droop control for distributed energy storage systems in DC microgrid applications," *IEEE Trans. Ind. Electron.*, vol. 61, no. 6, pp. 2804-2815, 2014.

- [9] H. Kakigano, Y. Miura and T. Ise, "Low-voltage bipolar-type DC microgrid for super high quality distribution," *IEEE Trans. Power Electron.*, vol. 25, no. 12, pp. 3066-3075, 2010.

- [10] T. F. Wu, K. H. Sun, C. L. Kuo and C. H. Chang, "Predictive current controlled 5-kW single-phase bidirectional inverter with wide inductance variation for dc-microgrid applications," *IEEE Trans. Power Electron.*, vol. 25, no. 12, pp. 3076-3084, 2010.

- [11] H. Valderrama-Blavi, J. M. Bosque, F. Guinjoan, L. Marroyo and L. Martínez-Salamero, "Power adaptor device for domestic dc microgrids based on commercial MPPT inverter," *IEEE Trans. Ind. Electron.*, vol. 60, no. 3, pp. 1191-1203, 2013.

- [12] M. Cespedes, L. Xing and J. Sun, "Constant-power load system stabilization by passive damping," *IEEE Trans. Power Electron.*, vol. 26, no. 7, pp. 1832-1836, 2011.

- [13] D. Marx, P. Magne, B. Nahid-Mobarakeh, S. Pierfederici and B. Davat, "Large signal stability analysis tools in dc power systems with constant power loads and variable power loads a review," *IEEE Trans. Power Electron.*, vol. 27, no. 4, pp. 1773-1787, 2012.

- [14] N. Bottrell, M. Prodanovic and T. C. Green, "Dynamic stability of a microgrid with an active load," *IEEE Trans. Power Electron.*, vol. 28, no. 11, pp. 5107-5119, 2013.

- [15] J. M. Guerrero, L. García De Vicuña, J. Matas, M. Castilla, et al, "Output impedance design of parallel-connected UPS inverters with wireless load-sharing control," *IEEE Trans. Ind. Electron.*, vol. 52, no. 4, pp. 1126-1135, 2005.

- [16] A. A. Rockhill, M. Liserre, R. Teodorescu and P. Rodriguez "Grid-filter design for a multimegawatt medium-voltage voltage-source inverter," *IEEE Trans. Ind. Electron.*, vol. 58, no. 4, pp. 1205-, 1217.

- [17] C. M. Wildrick, F. C. Lee, B. H. Cho and B. Choi, "A method of defining the load impedance specification for a stable distributed power system," *IEEE Trans. Power Electron.*, vol. 10, no. 3, pp. 280-285, 1995.