# Southern Illinois University Carbondale OpenSIUC

#### Dissertations

Theses and Dissertations

12-1-2014

## LOW-POWER LOW-VOLTAGE ANALOG CIRCUIT TECHNIQUES FOR WIRELESS SENSORS

Chenglong Zhang Southern Illinois University Carbondale, carsonzcl@gmail.com

Follow this and additional works at: http://opensiuc.lib.siu.edu/dissertations

#### **Recommended** Citation

Zhang, Chenglong, "LOW-POWER LOW-VOLTAGE ANALOG CIRCUIT TECHNIQUES FOR WIRELESS SENSORS" (2014). *Dissertations*. Paper 982.

This Open Access Dissertation is brought to you for free and open access by the Theses and Dissertations at OpenSIUC. It has been accepted for inclusion in Dissertations by an authorized administrator of OpenSIUC. For more information, please contact opensiuc@lib.siu.edu.

### LOW-POWER LOW-VOLTAGE ANALOG CIRCUIT TECHNIQUES FOR WIRELESS SENSORS

by

Chenglong Zhang

B.S., Huazhong University of Sci. & Tech., 2005

M.S., Huazhong University of Sci. & Tech., 2007

A Dissertation

Submitted in Partial Fulfillment of the Requirements for the Doctor of Philosophy Degree

Department of Electrical and Computer Engineering in the Graduate School Southern Illinois University Carbondale December, 2014

### **DISSERTATION APPROVAL**

## LOW-POWER LOW-VOLTAGE ANALOG CIRCUIT TECHNIQUES FOR WIRELESS SENSORS

By

## Chenglong Zhang

A Dissertation Submitted in Partial

Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

in the field of Electrical and Computer Engineering

Approved by:

Dr. Wang Haibo

Dr. Ahmed Shaikh

Dr. Themistoklis Haniotakis

Dr. Qin Jun

Dr. Zhu Michelle

Graduate School

Southern Illinois University Carbondale

November 4th, 2014

#### AN ABSTRACT OF THE DISSERTATION

CHENGLONG ZHANG, for the Doctor of Philosophy degree in ELECTRICAL & COMPUTER ENGINEERING, presented on Nov. 4th, 2014, at Southern Illinois University Carbondale.

TITLE: LOW-POWER LOW-VOLTAGE ANALOG CIRCUIT TECHNIQUES FOR WIRELESS SENSORS

#### MAJOR PROFESSOR: DR. HAIBO WANG

This research investigates low-power low-voltage analog circuit techniques suitable for wireless sensor applications. Wireless sensors have been used in a wide range of applications and will become ubiquitous with the revolution of Internet of Things (IoT). Due to the demand of low cost, miniature size and long operating cycle, passive wireless sensors which have no batteries and acquire energy from external environment are strongly preferred. Such sensors harvest energy from energy sources in the environment such as radio frequency (RF) waves, vibration, thermal sources, etc. As a result, the obtained energy is very limited. This creates strong demand for low power, low voltage circuits. The RF and analog circuits in the wireless sensor usually consume most of the power. This motivates the research presented in the dissertation. Specially, the research focuses on the design of a low power high efficiency regulator, low power Resistance to Digital Converter (RDC), low power Successive Approximation Register (SAR) Analog to Digital Converter (ADC) with parasitic error reduction and a ultra-low power ultra-low voltage Low Dropout (LDO) regulator. Several of the above circuit blocks are optimized and designed for RFID (radio-frequency identifications) sensor

i

applications. However, the developed circuit techniques can be applied to various low power sensor circuits.

## DEDICATION

I dedicate this work to my mother Chunhua Xie, who is fighting with thrombosis. I further dedicate my Dissertation to my beloved father Peishan Zhang, my wife Li Lu and my baby who is coming in months.

#### ACKNOWLEDGEMENTS

I think I have finally come to the point in my life where I am happy about myself at the end of 2014. This year will definitely be an important year in my life. This year, I am going to my dissertation, completed the milestone project in company with first silicon success and more importantly, my baby is coming in months. I overcame many hurdles to complete my Dissertation. I need to express my deep gratitude to my mentor Wang Haibo whose valuable insights and guidance significantly helped my research. Also, I would like to sincerely thank Dr. Ahmed Shaikh, Dr. Themistoklis Haniotakis, Dr. Qin Jun and Dr. Zhu Michelle for their help, guidance and being on my Dissertation Committee. It is my pleasure to have you all here.

I felt sorry for my mother because I can't be there with her fighting with thrombosis in the past years. I owe her a good dish from my hand and a good hiking with my feet. I hope she will be proud of me today. I am grateful to my father and my wife for their constant support and encouragement. My parents and my wife give me a comfortable environment enabling me to complete my Dissertation in addition to the heavy work load from the company. I also like to thank all my friends and colleagues in the lab and the company for their support. I want to convey special thanks to my managers Chuanyang Wang and John Chen for their patience and understanding which helped me a lot to finish my Dissertation.

iv

| CHAPTER                                                               | PAGE |

|-----------------------------------------------------------------------|------|

| ABSTRACT                                                              | i    |

| DEDICATION                                                            | iii  |

| ACKNOWLEDGMENTS                                                       | iv   |

| LIST OF TABLES                                                        | vii  |

| LIST OF FIGURES                                                       | viii |

| CHAPTERS                                                              |      |

| CHAPTER 1 – Introduction                                              | 1    |

| 1.1 Motivation                                                        | 3    |

| 1.2 Objectives                                                        | 4    |

| 1.3 Major contribution of the research                                | 5    |

| 1.4 Organization of the thesis                                        | 7    |

| CHAPTER 2 – Related work in wireless sensor design                    | 9    |

| 2.1 Recent development of the lower-power RFID sensors                | 9    |

| 2.2 Low-power SAR ADC                                                 | 13   |

| 2.3 Ultra-low voltage digital LDO                                     | 15   |

| CHAPTER 3 – Low power analog circuit design for RFID sensing circuits | 18   |

| 3.1 System overview                                                   | 18   |

| 3.2 Rectifier design                                                  | 19   |

| 3.3 Low power regulator design                                        | 32   |

| 3.4 Resistance to digital converter                                   | 42   |

| 3.5 Experiment results                                                | 49   |

## TABLE OF CONTENTS

| 3.6 Summary                                                    | 57        |

|----------------------------------------------------------------|-----------|

| CHAPTER 4 – Reduction of parasitic capacitance impact in low p | oower SAR |

| ADC                                                            | 59        |

| 4.1 Principle of SAR ADC and effects of parasitic capacita     | nce59     |

| 4.2 Proposed circuit technique                                 | 64        |

| 4.3 Simulation results                                         | 70        |

| 4.4 Concluding remarks                                         | 79        |

| CHAPTER 5 – Digital LDO for ultra-low voltage operation        | 81        |

| 5.1 Principle of digital loop LDO regulator                    | 81        |

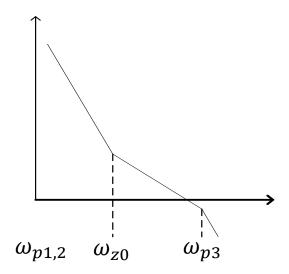

| 5.2 System stability                                           | 85        |

| 5.3 Proposed digital loop LDO regulator                        | 91        |

| 5.4 Simulation results                                         | 94        |

| 5.5 Summary                                                    |           |

| CHAPTER 6 – Conclusions and future work                        | 101       |

| REFERENCES                                                     | 104       |

| APPENDICES                                                     |           |

| Appendix A                                                     | 113       |

| Appendix B                                                     | 115       |

| Vita                                                           |           |

## LIST OF TABLES

| TABLE   | PAGE |

|---------|------|

| Table 1 | 51   |

| Table 2 | 53   |

| Table 3 | 56   |

| Table 4 | 71   |

| Table 5 | 74   |

| Table 6 | 76   |

| Table 7 | 76   |

| Table 8 | 95   |

| FIGURE    | PAGE |

|-----------|------|

| Figure 1  | 2    |

| Figure 2  | 3    |

| Figure 3  | 3    |

| Figure 4  | 12   |

| Figure 5  | 12   |

| Figure 6  | 12   |

| Figure 7  | 15   |

| Figure 8  | 16   |

| Figure 9  | 18   |

| Figure 10 | 20   |

| Figure 11 | 21   |

| Figure 12 | 24   |

| Figure 13 | 26   |

| Figure 14 |      |

| Figure 15 | 32   |

| Figure 16 | 32   |

| Figure 17 |      |

| Figure 18 | 42   |

| Figure 19 | 42   |

| Figure 20 | 45   |

| Figure 21 | 49   |

## LIST OF FIGURES

| Figure 22 | 50 |

|-----------|----|

| Figure 23 | 50 |

| Figure 24 | 51 |

| Figure 25 | 52 |

| Figure 26 | 53 |

| Figure 27 | 53 |

| Figure 28 | 54 |

| Figure 29 | 55 |

| Figure 30 | 57 |

| Figure 31 | 59 |

| Figure 32 | 61 |

| Figure 33 | 64 |

| Figure 34 | 66 |

| Figure 35 | 71 |

| Figure 36 | 71 |

| Figure 37 | 75 |

| Figure 38 | 77 |

| Figure 39 | 78 |

| Figure 40 | 81 |

| Figure 41 | 82 |

| Figure 42 | 85 |

| Figure 43 | 86 |

| Figure 44 | 86 |

| Figure 45 | 89 |

|-----------|----|

| Figure 46 | 90 |

| Figure 47 | 92 |

| Figure 48 | 93 |

| Figure 49 | 96 |

| Figure 50 | 96 |

| Figure 51 | 97 |

| Figure 52 |    |

| Figure 53 |    |

| Figure 54 | 99 |

| Figure 55 |    |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Motivation

Wireless sensor is a device which can be used to monitor the physical or environmental conditions, such as pressure, temperature, humidity, etc. It can collect data and send them back to the reader which can be a smart phone, tablet, computer, or any other electronic devices. At present, wireless sensors have been used in a wide range of applications. Some examples are discussed as follows. In medical service area, wireless sensors can be used to monitor body temperature, blood pressure, heart beating rate, and other health related data. They can also send the data to the doctors to monitor the patients' health conditions. In civil structure health monitoring applications, the sensors can be used to detect the corrosion of metals, and can help determine maintenance schedule of the buildings. In commercial area, people can use the sensors to monitor the storage environment, such as temperature, humidity, oxygen density, etc., to keep the environment suitable for commodity storage. In manufacture industry, wireless sensors can be used to monitor and control various aspects of the manufacture process to achieve near zero down time operations.

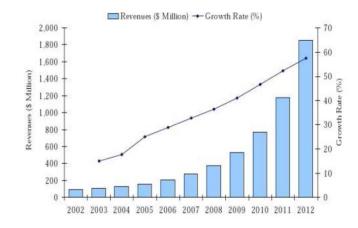

Because of these emerging applications of wireless sensors, the demand for wireless sensors increases rapidly. Figure 1 shows the revenue of wireless sensor market from 2002 to 2012 [1], which clearly indicates that the exponential growth of wireless sensors.

Figure 1. The market of the wireless sensor from 2002 to 2012 [1]

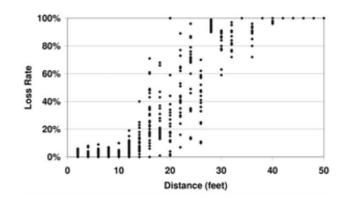

Some common characteristics of wireless sensors are low power, miniature size, and low cost. Such devices can be powered by batteries or obtain energy from external environment using energy harvesting circuits. The former is often referred as active sensors and the latter is called passive sensors. In both types of sensors, low power is extremely desirable. For active sensors, low power consumption increases sensor operating cycles and also reduces battery size. For passive sensors, low power consumption is a permanent requirement since the available energy is typically very limited. The sources for passive sensor devices to harvest energy include thermal, electromagnetic field, motion, etc. Currently a popular energy harvest approach is to acquire the energy from Radio Frequency (RF) waves, which is also the carrier of the sensor communication signals. For passive wireless sensors with RF energy harvesting function, two of the most critical factors that affect the level of harvested energy from the RF signal are operation distance and antenna size. A short distance and a large antenna help obtain more energy. Figure 2 shows experiment data from Berkeley [2], which indicates that the power loss rate increases

with the operating distance. However, longer operating distance and smaller antenna size are much more preferred in the application of wireless sensors. If we could reduce the power consumption of wireless sensors, then they can operate in relatively longer distance with a smaller antenna.

Figure 2. The loss rate of electromagnetic filed energy with distance [2]

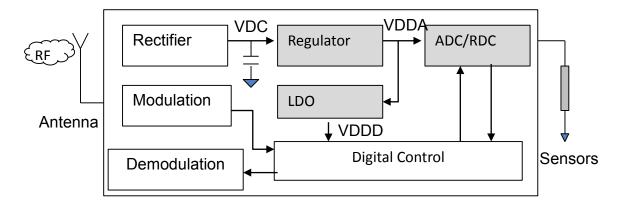

Figure 3. The typical structure of passive wireless sensor

## 1.2 Objectives

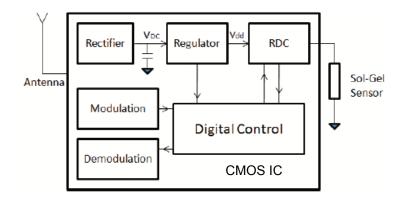

Figure 3 shows a typical structure for a passive wireless sensor with RF energy harvesting function. It consists of energy harvest circuits (antenna, rectifier, regulator), analog circuits (Low-Drop Output (LDO) regulator), analog to digital converter (ADC)/resistance to digital converter (RDC)), digital circuits (digital control and memory), modulation and demodulation circuits. The circuits that consume most of the power are the three blocks, regulator, Analog to Digital Converter (ADC)/ Resistance to Digital Converter (RDC) and Low-Drop Output (LDO) regulator, which are shaded in Figure 3. They are also the three circuits that are investigated in this research. The antenna acquires the energy from the external electromagnetic field. However, the voltage at the antenna is an AC voltage with a small amplitude, which can't be used as power supply for other circuits. The rectifier converts the low AC voltage at the antenna to a higher DC voltage and sends it to the regulator. Because the output of the rectifier is noisy and has a large variation according with the input power and the load current, it's also unsuitable to be used as power supply. Thus, a regulator is needed to generate a stable and clean power supply for other circuits from the rectifier. The ADC/RDC is used to measure the electrical signal of the sensor, such as resistance value in this example, and converts it to digital data. The digital circuits acquire the information and send the data back to the reader via a back scatter scheme [42], which is implemented by the modulation and the antenna. The LDO regulator is usually to satisfy the different power supply requirements for different circuits. Usually, the digital circuits prefer to operate with a lower power supply voltage than the analog circuits. This helps to reduce power consumption in the digital circuits. Meanwhile, the analog circuits need a clean power supply to

minimize the power supply noise impact. As discussed above, regulator, ADC and LDO are three important analog building blocks in wireless sensors. Meanwhile, they are among the most power hungry circuits in passive wireless sensors. Hence, this research intend to investigate low power low voltage design techniques for these circuits.

#### **1.3** Major contribution of the research

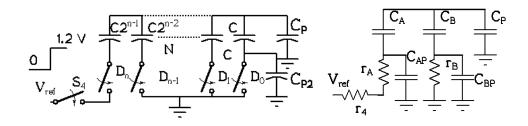

In this dissertation, we present low power circuit design techniques for voltage regulator and resistor to digital converter (RDC) circuit which could be integrated onchip in Radio-Frequency Identification (RFID) sensor applications. The proposed work is a part of integrated efforts in the development of a RFID sensor, which is used to measure the impedance of a Sol-Gel chemical sensor [58] in building corrosion detection applications. The proposed voltage regulator has simple circuit structure and near zero DC current dissipation (except the current drained by its load). The resistor to digital converter (RDC) consists of a cascaded current mirror, a reference resistor, and a CR SAR ADC circuit with 9-bit resolution. The proposed design techniques eliminate the need of dedicated voltage reference in the ADC circuit and reduce the size of the ADC capacitor array by half compared to traditional CR SAR ADCs with the same resolution. The proposed techniques also significantly reduce the circuit power consumption with enhanced measurement accuracy. The proposed low power circuits and an optimized voltage multiplier based RF energy harvesting circuit (for powering the proposed circuits) are implemented in a 0.13µm CMOS technology. The functionality and performance of the proposed circuits are

demonstrated by both of simulation and measurement results. All the circuits could also be used in other similar wireless sensing circuits.

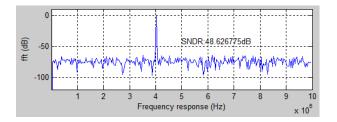

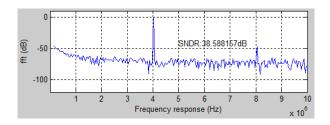

In addition, a low power CR SAR ADC which can correct the parasitic capacitance error with little hardware and energy overhead is designed [3]. SAR ADC is the most used ADC topology in low power circuits, which features low power consumption, moderate conversion speed and moderate accuracy. For CR SAR ADC, the main power consumption is due to charging the capacitor array. To minimize the power consumption, a separate small capacitor can be used to replace the capacitor array to sample the input voltage. This type of ADC is called as SAR ADC-S<sup>2</sup>C (successive approximation register analog to digital converter with separate sampling capacitor) in the low power design. However, SAR ADC-S<sup>2</sup>C will suffer from the error induced by the parasitic capacitance of the capacitor array. By avoiding the charge sharing between the capacitor array and the parasitic capacitance, the proposed ADC reduces the error associated with the parasitic capacitance. This research first compares the SAR ADC-S<sup>2</sup>C with the conventional SAR ADC and analyzes the gain error caused by parasitic capacitance in SAR ADC- $S^{2}C$  design. Although the gain error can be compensated by multiplying the ADC output by a correction coefficient, it is achieved at the cost of reduced ADC input range and requires a calibration process for determining the coefficient value. This work presents an effective technique to minimize the effect of the parasitic capacitance for the SAR ADC-S<sup>2</sup>C circuit. It requires negligible hardware overhead, does not need calibration process and additional clock phases or cycles in ADC conversion operations. In addition, the proposed technique is capable of addressing

not only the linear error caused by constant parasitic capacitance, but also the nonlinear inaccuracy in the case that parasitic capacitance varies with the voltage potential at the top plates of the CS capacitor array (similar as metal-insulatorsemiconductor (MIS) capacitor). Finally, the effectiveness of the proposed technique is demonstrated by post-layout simulation results.

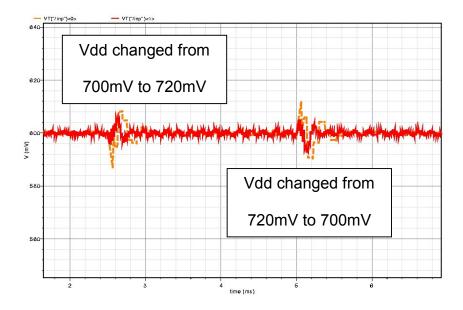

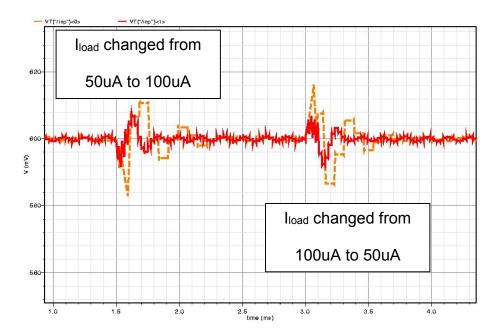

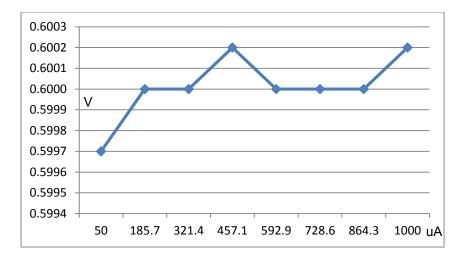

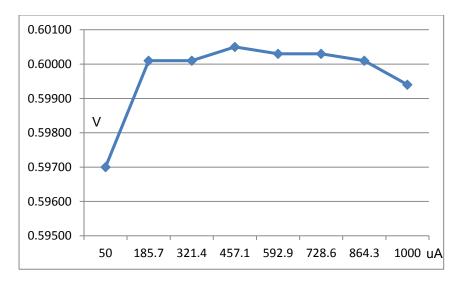

Furthermore, design techniques for low voltage LDO circuits are also investigated. To address the challenge of traditional LDO design not suitable for ultra-low voltage operation, a digital loop LDO regulator is proposed, whose power supply can be scaled to 0.7V. Its power consumption and efficiency are also superior to that of analog design. Compared to existing low-voltage digital LDO design, the proposed circuit improves the line and the load response time with minimum hardware and power overhead. The regulator response time is improved by more than three times and the ripple is significantly reduced. The start-up time is also improved. The circuit analysis are provided to explain the improvement by the proposed design. The proposed circuit is implemented using a 0.18µm CMOS technology and simulation results are presented to validate the performance improvement.

#### 1.4 Organization of the thesis

The reset of the thesis is organized as follows. Chapter 2 surveys the related work that are reported in recent literature. Chapter 3 presents the developed low power circuit design techniques for a RFID sensor circuit. The developed parasitic error reduction technique for SAR ADC circuit are described in Chapter 4. Chapter 5

presents the developed ultra-low voltage digital LDO circuits. Finally, conclusions and future work are discussed in Chapter 6.

#### **CHAPTER 2**

#### **RELATED WORK IN WIRELESS SENSOR CIRCUIT DESIGN**

#### 2.1 Recent development of low-power RFID sensors

RFID (radio-frequency identification) was initially developed as an alternative to the bar code for efficient and convenient inventory management. Later, some sensing functions are integrated into RFID circuits and this leads to a new type of low cost wireless sensors, which are commonly referred to as RFID sensors. Such sensors could be classified to passive and active sensors by the using battery or not. A passive RFID sensor does not need battery and it acquires the energy from the external electromagnetic field. It has the features of low cost, long lifetime, wireless access, battery-free and simple structure. These features make it more easily deployed and keep it remain in operation for a long time. Due to these advantages, passive RFID sensors are more preferred compared to active RFID sensor, which requires battery but are capable of operating in relatively long distance. Recently, some passive RFID sensing platforms which integrate multi-sensors, microcontroller and ports are developed such as Intel WISP (*wireless Internet service provider*) [4]. Combining with these sensors, the RFID is able to be used in environment monitor, building maintenance or structure conditions, and information collection applications. But the cost of these platforms with multi-chips is high. Single chip RFID sensors are more preferred in many applications.

Inspired by the wide applications of RFID sensors, significant research efforts have been devoted to address the design challenges of the single chip RFID sensors at both software and hardware aspects [5], [6], [7], [8], [9]. One of these stiff

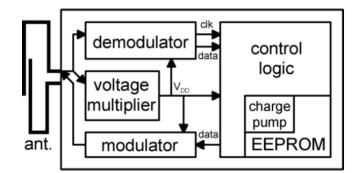

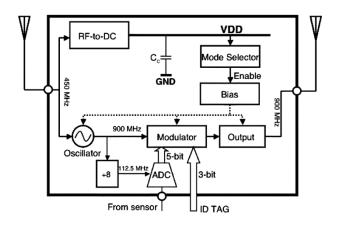

challenges in the development of RFID sensing circuits is that the energy harvested from RF signals is very limited. To address this challenge, different energy harvest circuit designs have been proposed [10], [11], [12] and design optimization techniques are investigated [13], [14], [15]. With the state of the art of circuit techniques, the efficiency of RF energy harvest circuits is still low, ranging from 10% to 20%. As a result, the physical sensing structure as well as the digital and analog sensing circuits needs to have extremely low power consumption. In [10], an ultralow power RFID with the structure shown in Figure 4 is developed, which includes voltage multiplier (rectifier), memory, control logic, modulator and demodulator. The reading distance can reach 4.5- or 9.25-m at 500-mW ERP or 4-W EIRP basestation transmit power, respectively, at the operating in the 868/915-MHz ISM (industrial, scientific and medical) band with an antenna gain less than 0.5dB. There are no external components except for the printed antenna, which reduces the cost of the tag. The tag information can be read by the integrated memory. However, because there is no any sensor or sensor connection port integrated in the tag, the application of this RFID tag is guite limited, and it can't be used for the information collection application.

Low-power analog circuits, including voltage level detection circuit with 900nA current dissipation [12] are reported with the structure in Figure 5. It uses the recovered clock from the input wireless signal as a reference in the counter to convert the analog signal to digital code. This works as a clock counter based ADC to convert the analog signal to digital code. It makes the sensor tag flexible compared to that in [10]. It's possible to be used to measure the sensor signal and

send the data to the reader. But in this circuit, the ADC can't be used to measure the resistance of sensors directly. The ADC can only be used to measure the voltage level. Thus, it needs an accuracy biasing circuit to convert the resistance of sensors to voltage level. It is not easy to achieve this in passive RFID circuit. Because of using the recovered clock as the reference, the resolution of the ADC is limited. Only 5-bits resolution is achieved in the circuit reported in [12]. The operating distance of this device is more than 18 meters under 7W base power station with a 50 $\Omega$  commercial antenna which is much larger than the printed antenna in [10].

The voltage regulators with 110nA DC current [16] and 300nA DC current [17] are proposed respectively. Although conventional circuit topologies are used in this designs, the circuits are highly optimized to address the low-power design challenges in RFID sensors. Also these circuits have complex structures and it may be difficult to make the circuits stable in the entire operation range of the passive RFID circuits. Usually they need some auxiliary circuits to help the regulator work continually. With the push to extend the operating distance of RFID sensors (hence less RF energy delivered to RFID sensors) and the use of RFID devices in more capable sensing applications, novel integrated circuits with ultra-low power design techniques are strongly needed.

Figure 4. RFID tag proposed in [10]

Figure 5. RFID tag proposed in [12]

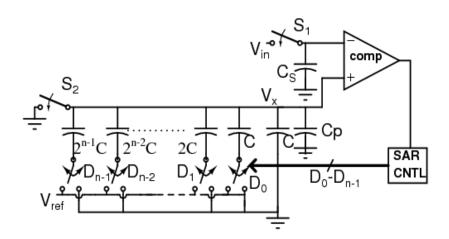

Figure 6. The single-end SAR ADC proposed in [23]

#### 2.2 Low-power SAR ADC

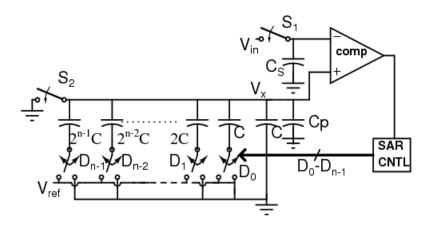

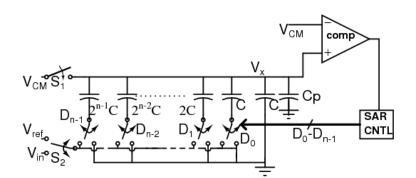

The charge scaling successive approximation register (CS SAR) ADC is an attractive design choice for low-power ADC implementations [18] [19]. They are more suitable for wireless sensor circuits. Recently, quite a few low-power CS SAR ADC circuits have been reported [20] [21] [22] [23]. Many of them are designed to operate with single-ended signals to achieve better power efficiency. The low-power advantage and the existence of a large number of sensor devices with single-ended outputs [24] make the use of single-ended ADCs appealing in many low power applications [24] [25] [26]. To reduce the power consumption of the driver circuits, SAR ADC designs using separate sampling capacitors are reported [23] [24] [25] [26] [27] as shown in Figure 6. It uses a small capacitor to sample input voltage and compares the sampled output with the voltage generated by the charge scaling (CS) capacitor array. This SAR ADC topology will be referred as SAR ADC-S<sup>2</sup>C structure (S<sup>2</sup>C stands for separate sampling capacitor). This ADC structure is more suitable for some sensor measurement, in which no differential signals are available. Despite its low-power advantage, SAR ADC-S<sup>2</sup>C design suffers from gain error and reduced input range caused by the parasitic capacitance in the CS capacitor array.

Previously, several techniques have been developed to address the effects of the parasitic capacitance in different SAR ADC designs. In [28], the bottom plate parasitic capacitance of a C-2C capacitor array is shielded by a metal layer, and the metal layer's potential is driven by a second C-2C capacitor array operating similarly as the main capacitor array. This technique works well for capacitor arrays with large unit capacitance values, but increases the total capacitor area and the energy

dissipated by the capacitor arrays. The shielding technique is also used in [29] [30] to minimize the effects of parasitic capacitance at the floating node of the CS capacitor array. In [29], the potential of the shielding layer is switched between the reference voltage and ground; while a dedicated voltage generator is used to control the potential of the shielding layer in [30]. The techniques of using configurable capacitance banks are reported to compensate the effect of parasitic capacitance in both split-capacitor array SAR ADC design [31] and fully differential ADC [32]. An SAR-ADC auto-calibration technique is presented in [33], which compensates the inaccuracy factors by injecting charge to the floating node of the capacitor array. The charge injection is achieved by using a calibration capacitor that is driven by an analog voltage determined during the calibration process.

The design in [34] includes parasitic capacitance as a part of the capacitance to be implemented in the array. To cope with variations associated with parasitic capacitance, a combination of capacitance bank based coarse-level calibration and an analog voltage controlled fine-level calibration is utilized to trim the capacitance of each branch to the desirable value. In addition to the above circuit techniques, general error models for SAR ADC circuits are developed [35] [36] and various digital compensation techniques have been proposed [37] [38] [39]. Nevertheless, the previously proposed techniques either are not suitable for the SAR ADC-S<sup>2</sup>C structure or require large hardware overhead and lengthy calibration processes.

Figure 7. Digital LDO proposed in [40]

#### 2.3 Ultra-low voltage digital LDO

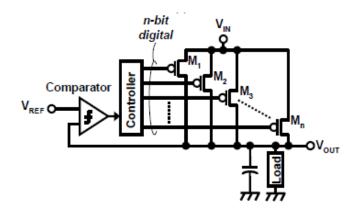

LDO regulator is widely used to provide constant power supply to other circuits. In wireless sensors, it is mostly used to provide the power supply for digital circuits and digital memory, since separate power supplies are preferred for digital and analog circuits to minimize the impact of digital switching noise on analog circuits. And lower power supply is preferred to reduce the digital power consumption. Traditional analog LDOs consume more power and their stability has to be considered carefully. Moreover, with the scaling down of power supply voltage, the design of analog LDO becomes more challenge partially due to the difficulty of high gain amplifier design with low supply voltage. To address this problem, digital LDO circuits are reported in recent literature. In [40], a digital LDO is proposed as shown in Figure 7. It uses a PMOS array to provide the load current and control the output voltage. The SAR logic is used to generate the digital control code for the PMOS array. This makes the circuit easy to be set stable, and the operation power supply can be as low 0.6V. However, the response time to the variation of the line and the load is inversely proportional to the resolution of the PMOS array in this design. If the resolution is increased to reduce the ripple at the output, and then, the response time also increases. On the other hand, the resolution is reduced to achieve shorter response time, the ripple at the output will be large and the static current will also increase. Thus the efficiency of the LDO will decrease. The start-up response is also very slow when the resolution is high. As a compromise of these considerations, 256 PMOS devices, corresponding to 8-bit resolution, are used in the array [40] to avoid long start-up and response time. Other implementations based on this structure are also reported in [45][46][47][49][52] for various applications. But they need either load detection or calibration circuits which are complex for most wireless sensor designs.

Figure 8. Digital loop LDO proposed in [41]

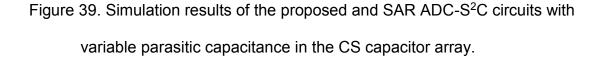

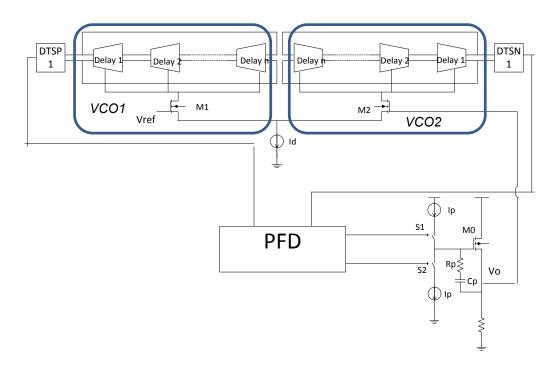

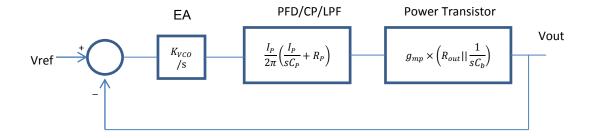

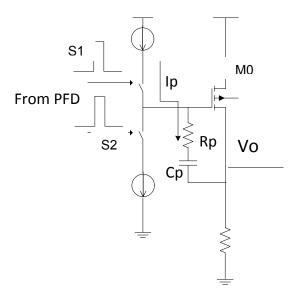

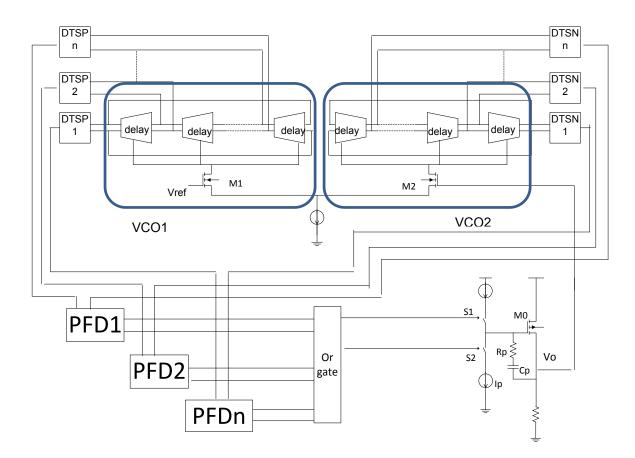

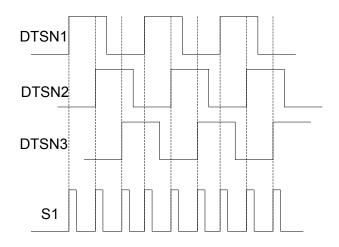

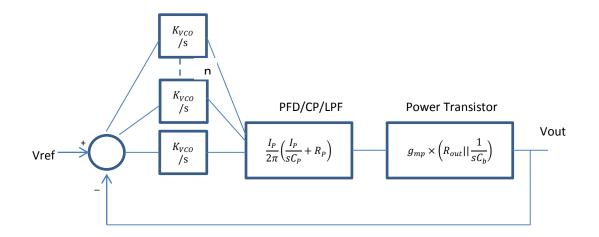

Another digital loop LDO as shown in Figure 8 is reported in [41]. It uses two voltage control oscillators (VCO) as the error amplifier (EA), and uses phase frequency detector (PFD) to generate the pulses for controlling the charge pump

(CP). After the Low-Pass Filter (LPF), a stable output voltage will be generated at the gate of the Power MOS. Then the output  $V_0$  will also be stable. The loop is designed using digital circuits which enable it to operate under 0.6V power supply. The loop is also easier to be set stable compared to its analog counterpart. But the response of the line and load variation are still slow for certain applications, especially when the power consumption is low.

#### **CHAPTER 3**

## LOW POWER ANALOG CIRCUIT DESIGN FOR RFID SENSING CIRCUITS

#### 3.1 System overview

As shown in Figure 9, the RFID Sol-Gel sensor system under investigation consists of an antenna, a CMOS IC chip, and a Sol-Gel sensing device. The Sol-Gel sensor used in the system is a type of specially synthesized ceramic oxide glass. Its electrical conductivity (or resistance) is affected by chloride ions concentration, and thus the conductivity change can reflect structure corrosion conditions when the sensors are attached to the metal in certain locations of the structure to be monitored. From the electronic design perspective, the Sol-Gel sensor can be simply treated as a conductive component, whose resistance needs to be measured.

Fig. 9. Block diagram of the RFID sol-gel sensor

The rectifier and regulator compose the energy harvesting circuit. The rectifier in the IC chip harvests the RF energy from the antenna and converts the RF voltage to a DC voltage. Because of the integration of the measurement circuits (the RDC circuit) in this chip, the current from the rectifier circuit is not large enough to support the rest circuits operating in long time term. A large on-chip capacitor is used to accumulate the harvested energy for continuous operation; and the sensing operation starts only after enough energy is accumulated. The ready state is determined by the standard that if the voltage across the capacitor exceeding 2.2V. The capacitor also functions as a low pass filter. The regulator circuit provides a constant voltage around 1.2V to power the rest RFID circuits. The RDC is the measuring circuit to sense the resistance of the Sol-Gel sensor and digitize the measured resistance into a 9-bit digital data, which will be sent back to RFID reader via back-scattering techniques [42]. The rest circuits in the IC chip, including the digital control, demodulation and antenna impedance modulation circuit, are similar to the corresponding circuits in a typical RFID tag [10].

#### 3.2 Rectifier design

Passive RFIDs harvest the energy from the electrical-magnetic (EM) field. According to the coupling techniques, it can be classified into two types, near field and far field RFID. Most near-field tags rely on the magnetic field through inductive coupling to the coil in the tag. This mechanism is based upon Faraday's principle of magnetic induction. A current flowing through the coil of a reader produces a magnetic field around it. This field causes a tag's coil in the vicinity to generate a small current. For this type of RFID, the operation range is usually less than 1m, so its application is highly limited.

Far-field passive RFID sensors usually operate in 860–960 MHz UHF (ultrahigh frequency) band or in 2.45 GHz Microwave band. Far-field coupling is commonly employed for long-range (5–20 m) RFID. In contrast to near-field, there is no restriction on the field boundary for far-field RFID. The EM field in the far-field region is radioactive in nature. Part of the energy incident on a tag's antenna is reflected back due to an impedance mismatch between the antenna and the load circuit. Changing the mismatch or loading on the antenna can vary the amount of reflected energy, which is the technique called backscattering. The attenuation of the EM field in far-field region is proportional to  $1/r^2$ , where r is the distance between the RF signal transmitter and receiver. This is smaller by orders of the magnitude than in the near-field range (which is  $1/r^6$ ). An advantage of a far-field tag operating at a high frequency is that the antenna can be small, leading to low fabrication and assembly costs. Small size is also preferred for easy deploying. Due to the advantages of the long operation distance, low cost and small size, the far field passive RFID technique is more suitable for wireless sensor applications.

Figure 10. The simplified model for passive RFID system analysis in [43]

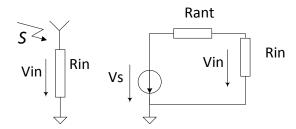

Figure 10 shows a simplified circuit model for a far-field passive RFID system [43]. It consists of the reader and the tag. The tag antenna is modeled by  $v_s$  and

$R_{ant}$ , the rest circuits of the tag are simplified to  $R_{in}$ . According to the coupling principle of far field RFID, the peak voltage on the antenna of the tag,  $v_{s,peak}$ , could be represented by [43]:

$$v_{s,peak} = 2\sqrt{2P_a R_{ANT} \cdot p} \tag{1}$$

where  $P_a$  is the power acquired by the antenna of tag and p is the polarization mismatch. It shows that  $v_{s,peak}$  is determined by the available power (related to the power sent out by the reader, the distance and the size of the antenna) and the resistance of the antenna. The resistance of the antenna is usually limited by the polarization mismatch. It is usually 50 $\Omega$  or 75 $\Omega$ . So the amplitude of  $v_{s,peak}$  is small and it's an AC voltage which can't be used as power supply for other circuits. To convert the AC voltage to a DC value and boost it to a higher voltage level which can serve as power supply for other circuits, a voltage multiplier rectifier is often needed in passive RFID tag design.

Figure 11. Dickson's voltage multiplier in [44]

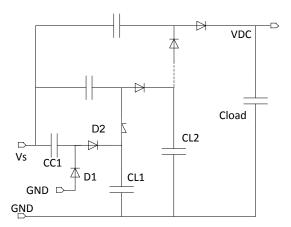

#### I Principle of rectifier

The most common voltage multiplier rectifier is the Dickson's voltage multiplier shown in Figure 11 [44].  $V_s$  is the sine wave from the antenna. When  $V_s < 0$ , and its absolute value is larger than the threshold voltage of the diode, D1,  $C_{C1}$  will be charged through D1; when  $V_s > 0$  and its absolute value is larger than the threshold voltage of the diode, D2, then  $C_{L1}$  will be charged by  $C_{C1}$ , via diode D2,  $C_{L1}$  won't be discharged. Similar,  $C_{L2}$  and other capacitors will be charged to higher voltage, and the output voltage can be derived as [44]:

$$V_O = M\left(\frac{c}{c+c_P}V_{s,peak} - \frac{I_o}{f(c+c_P)} - V_{TH}\right) - V_{TH}$$

(2)

where *M* is the number of stages,  $V_{TH}$  is the threshold voltage of the diode, *f* is the input frequency of  $V_S$ ,  $C_L = C_C = C$  and  $C_P$  is the parasitic capacitance of the diode. As the value of the expression inside the brackets is positive, the output voltage could be boost to a higher voltage which can be used by other internal circuits. In CMOS circuits, the diodes are typically implemented by MOSFET with diode configuration. Then body effect will affect  $V_{TH}$  values and such impacts is not included in Equation 2. Because of the body effect,  $V_{TH}$  increase with the output voltage. As output is high to certain level, the value of the expression inside the brackets will become 0 and hence adding additional stages will not further increase  $V_o$ . So there is a maximum value for the output voltage.

The efficiency of the rectifier is defined as:

$$Efficiency = \frac{V_o \times I_{load}}{P_{available}}$$

(3)

Where  $I_{load}$  is the load current and  $P_{available}$  is the available power for the rectifier. According to Equation 2 and 3, the efficiency is mainly determined by  $V_{s,peak}$ ,  $V_{TH}$ ,  $C_C$ and  $C_{p}$ . Large  $V_{s,peak}$  and small  $V_{TH}$  is preferred to improve the efficiency. In passive RFID tag design,  $V_{s,peak}$  is affected by the available power, distance to the reader, matching and the size of the antenna. To make the rectifier impedance match with the antenna, an inductor are often used in the rectifier design [45] [46] [47], which also helps boost the voltage to the rectifier to improve the efficiency of the rectifier. Another solution to increase the rectifier energy harvesting efficiency is to reduce  $V_{TH}$ . Several technologies have been proposed to reduce  $V_{TH}$  in the rectifier. In [48], a static threshold voltage compensation circuit has been used. In [49], the charge pump rectifier is built by low threshold diodes. However, this is difficult to be integrated in standard CMOS process. Dynamic threshold voltage,  $V_{TH}$ , cancellation circuit has been also proposed in [59]. However, this circuit is complex and its impedance is difficult to control. One of the most popular technique in latest RF energy harvesting circuits is to use zero-threshold voltage transistor or low thresholdvoltage transistor to replace the diode. This not only significantly simplifies the energy harvesting circuit design and analysis, but also improves the energy harvesting impedance matching and efficiency. More importantly, many CMOS technologies already support zero-threshold devices (intrinsic transistor). Thus, such

design can be implemented using only CMOS technologies. In the following sections, RF energy harvesting circuit are analyzed.

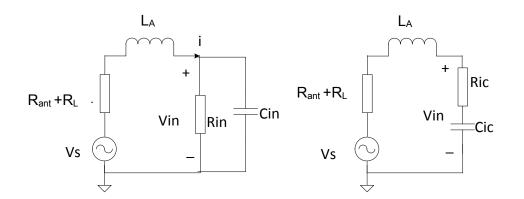

### II Impedance matching and inductor boost design

In the impedance matching analysis, the RF energy harvesting circuit can be modeled by the circuits in Figure 12 [50].  $R_{ant}$  is the resistance of the antenna;  $L_A$  is the inductor used to compensate the imaginary part of the tag;  $R_L$  represents the non-radiating antenna resistance and the loss on interconnecting from antenna to chip.  $R_{in}$  and  $C_{in}$  are the input resistance and capacitance of the chip. The impedance of the matching network, I/O Pads, wire components and PCB trace are included in  $R_{in}$  and  $C_{in}$ .

Figure 12. Circuit model used in impedance analysis in [50]

According to Figure 12, the peak value of voltage  $V_{in}$  can be derived as:

$$v_{in,peak} = v_{s,peak} \frac{R_{in}}{\sqrt{(R_{in} + R_{ANT} + R_L - \omega LQ)^2 + (\omega L + (R_{ANT} + R_L)Q)^2}},$$

(4)

where Q is the quality factor of the tag chip. Q is defined as:

$$Q_{\text{tag}} = [\omega.(\text{stored energy/dissipated energy})] = \frac{v_{in}^2 |j\omega C_{in}|}{\frac{v_{in}^2}{R_{in}}} = \omega C_{in} R_{in}$$

(5)

In the case that impedance is perfectly matched, we have:

$$R_{ANT} + R_L = \frac{R_{in}}{Q^2 + 1}$$

(6)

$$L_{ANT} = \frac{R_{in}^2 C_{in}}{Q^2 + 1} \tag{7}$$

Substituting  $V_{s,peak}$  by Equation 1, and using the impedance matching conditions given by Equation 6 and 7.  $V_{in,peak}$  can be derived as:

$$v_{in,peak} = v_{s,peak} \frac{\sqrt{Q^2 + 1}}{2} = \sqrt{\frac{R_{ANT} P_{aviable} (Q^2 + 1)}{2}}$$

(8)

Since high  $V_{in,peak}$  value helps improve the efficiency of the rectifier circuit, large  $R_{ant}$ and Q are preferred in passive RFID design. However, as described in the previous section,  $R_{ant}$  is limited by the antenna polarization mismatch and its value is usually constant (50 $\Omega$  or 75  $\Omega$ ). Moreover, Q value is also limited by the bandwidth of input RF signal. According to the established standard [51], the operation frequency for RFID are 865-868MHz in Europe and 902-928MHz in US. This limits the bandwidth of the RFID interrogation signal to be less than 20MHz. So Q is limited by the signal bandwidth for communication. And in Equation 8, Q is affected by  $R_{in}$  and  $C_{in}$ , because that  $R_{in}$  is equal  $R_{ant}$  in the matching condition. Q can only be adjusted by  $C_{in}$

The  $R_{in}$  and  $C_{in}$  in Figure 12 include the contributions from PCB trace, pins, bonding wires, matching network and rectifier. Since the impacts of the pin and bond pads are difficult to control, their values should be minimized. Thus the minimum size pad is preferred and the bond wire need to be short. To design the impedance matching circuit and rectifier separately, the impacts from the resistance and the capacitance of the rectifier,  $R_{rect}$  and  $C_{rect}$ , should be minimized, implying that large rectifier resistance and small rectifier capacitance are preferred. In this case, the impedance matching will be mainly determined by the matching network, which is independent on the rectifier design. This arrangement simplifies the circuit design.

Figure 13. A single stage MOS rectifier circuit

#### III Rectifier efficiency in steady state

Figure 13 is a rectifier implemented using MOS transistors, zero- $V_{TH}$  NMOS is used in this design. Assuming input is sine signal, when  $V_s$ <0 (the threshold of T1 is 0), T1 will turn on, and  $C_{C1}$  will be charged through T1; when  $V_s$ >0 (the threshold of T2 is 0), T1 will turn off and T2 will be on.  $C_{L1}$  will be charged through T2. For the reason of conciseness, the following discussion use T1 as an example. T1 switches between two modes during the operation. During 0-T/2 (T is the period of  $V_s$ ),  $V_s$ <0, T1 works in saturation; during T/2-T,  $V_s$ >0, it works in sub-threshold region. Because the threshold voltage is zero, it won't be completely cut-off. At time T/2, the charge stored in  $C_{C1}$  is:

$$Q_{charge} = \int_{0}^{T/2} I_{dsat} dt = \int_{0}^{T/2} K \frac{W}{L} (V_{in} - V_t)^2 dt = \int_{0}^{T/2} K \frac{W}{L} (v_{in} \sin \omega t)^2 dt$$

$$= K \frac{W}{L} \frac{v_{in}^2}{2} \frac{T}{2} = K \frac{W}{L} \frac{T v_{in}^2}{4}$$

(9)

where *W/L* is the size of the transistor T1 and  $K = \frac{1}{2} \mu_{eff} C_{ox}$ .

During T/2 – T, T1 works in sub-threshold region. The leakage current is:

$$I_{ds} = \mu_{eff} C_{ox} \frac{W}{L} \sqrt{\frac{\varepsilon_{si} q N_a}{4\psi_B}} \left(\frac{kT}{q}\right)^2 e^{q(V_g - V_i)/kT} \left(1 - e^{-qV_{ds}/kT}\right) \left(1 + \lambda V_{ds}\right)$$

(10)

Assuming

$$A = \mu_{eff} C_{ox} \sqrt{\frac{\varepsilon_{si} q N_a}{4 \psi_B}} \left(\frac{kT}{q}\right)^2$$

(11)

The *I*<sub>ds</sub> equation can be simplified as:

$$I_{ds} = A \left(\frac{kT}{q}\right)^{2} e^{q(V_{g} - V_{i})/kT} \left(1 - e^{-qV_{ds}/kT}\right) \left(1 + \lambda V_{ds}\right)$$

(12)

So the charge leakage loss due to this leakage current is:

$$Q_{leakage} = \int_{T/2}^{T} I_{leakage} dt = \int_{T/2}^{T} I_{sub} dt = \int_{T/2}^{T} A e^{-qV_t/kT} \frac{W}{L} (1 - e^{qV_{ds}/kT}) (1 + \lambda_{sub}V_{ds}) dt$$

$$= A e^{-qV_t/kT} \frac{W}{L} \int_{T/2}^{T} (1 - e^{qV_{ds}/kT}) (1 + \lambda_{sub}V_{ds}) dt$$

(13)

since  $v_{in} = v_{in,peak} \sin \omega t' > 0.1V$ ,  $1 - e^{-qV_{ds}/kT} \approx 1$ , when  $v_{in} = v_{in,peak} \sin \omega t' < 0.1V$  $(1 + \lambda_{sub}V_{ds}) \approx 1$ , Equation 13 can be approximated as:

$$Q_{leakage} = Ae^{-qV_t/kT} \frac{W}{L} \int_{T/2}^{T} (1 - e^{qV_{ds}/kT})(1 + \lambda_{sub}V_{ds})dt$$

$$\approx Ae^{-qV_t/kT} \frac{W}{L} \left[ \int_{T/2}^{t'} (1 - e^{qV_{ds}/kT})dt + \int_{t'}^{T} (1 + \lambda_{sub}V_{ds})dt \right]$$

$$= Ae^{-qV_t/kT} \frac{W}{L} \cdot \frac{T}{2}$$

$$+ Ae^{-qV_t/kT} \frac{W}{L} \left( -\lambda_{sub} \frac{V_{in,peak}}{\omega} \left( 1 - \sqrt{1 - \left(\frac{0.1}{V_{in}}\right)^2} \right) - \frac{kT}{qV_{in}\omega} e^{\left(qV_{in,peak}\pi/kT\right)} \left( e^{2f \cdot t'} - 1 \right) \right)$$

(14)

According to the charge conversation, the following relation holds in the stable state.

$$Q_{charge} - Q_{leakage} - I_{load} \cdot T = (C_P + C_C) \Delta v$$

(15)

$$\Delta v = \frac{Q_{charge} - Q_{leakage} - I_{load} \cdot T}{C_P + C_C}$$

(16)

where  $C_p$  is the parasitic capacitance of the transistor,  $I_{load}$  is the load current,  $\Delta v$  is the increase of the output voltage at a single stage.  $C_p$  is the transistor parasitic capacitance, it will be affected by the gate voltage of the transistor. It can be simplified to linearly change with the input voltage. It can be approximated as:

$$C_{average} = \frac{1}{2} \left( WLC_{ox} + \frac{WLC_{ox}}{\sqrt{1 + \left(2C_{ox}^2 V_{in} / \varepsilon_{si} q N_a\right)}} \right)$$

(17)

Based on above equations, the output voltage of the single stage can be derived. Ignoring the body effect, each stage of the rectifier in Figure 13 has the similar output voltage and the number of stages will not impact the efficiency.

#### IV Rectifier in impedance matching

As described above, to enable separate optimization for matching network and the rectifier efficiency, the resistance and capacitance of the rectifier,  $R_{rec}$  and  $C_{rec}$ , should be ignored, which means that the effect of  $C_{rec}$  and  $R_{rec}$  should be minimized. If  $C_{rec}$  is small and  $R_{rec}$  is large, the impedance of the tag is mainly determined by the matching network. To reduce  $C_{rec}$ , the size of the transistor should be small. Meanwhile, a small transistor size also helps increase  $R_{rec}$ . But according to the previous analysis in the rectifier efficiency, this may reduce the efficiency of the rectifier.

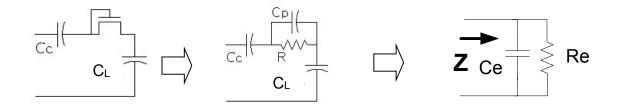

Figure 14. Equivalent circuit in rectifier impedance matching analysis [50]

To simplify the analysis, we take single stage rectifier in Figure 14 as the example [50].  $C_p$  is the parasitic capacitance of the transistor and R is the equivalent resistance of the transistor;  $C_e$  and  $R_e$  are the equivalent capacitance and resistance of the rectifier respectively. We have:

$$\begin{cases} R_{e} = \frac{1}{R_{1} \left(2\pi f \, 2C\right)^{2}} + R_{1} \left(1 + \frac{C_{p}}{2C}\right)^{2} \approx R_{1} \left(1 + \frac{C_{p}}{2C}\right)^{2} \\ C_{e} = 2C - \frac{R_{1}}{R_{e}} \left(2C + C_{p}\right) = \frac{1 + \left(4\pi f C R_{1}\right)^{2} \left(1 + \frac{C_{p}}{2C}\right) \frac{C_{p}}{2C}}{1 + \left(4\pi f C R_{1}\right)^{2} \left(1 + \frac{C_{p}}{2C}\right)^{2}} 2C \\ \approx \frac{2CC_{p}}{2C + C_{p}} \end{cases}$$

$$(18)$$

where

$$R_{1} = \frac{1}{g_{m}} = \frac{1}{\mu_{n} C_{ox} \frac{W}{L} V_{in}}$$

(19)

For multistage rectifier, the *R*<sub>e</sub> and *C*<sub>e</sub> expressions are:

$$\begin{cases} R_e \approx \frac{R_1}{N} \left( 1 + \frac{C_P}{2C} \right)^2 \\ C_e = N \cdot \frac{2CC_P}{2C + C_P} \end{cases}$$

(20)

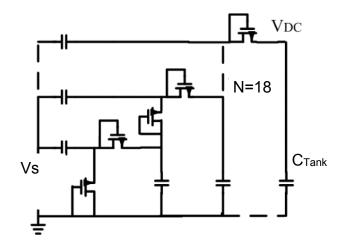

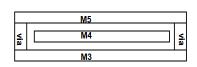

where *N* is the number of the stages in the rectifier. To achieve small  $C_e$  and large  $R_e$ , *W*/*L* could not be too large. The number of stages, *N*, also affects the values of  $C_e$  and  $R_e$ . Large *N* will reduce  $R_e$  and increase  $C_e$ . Thus in the design of high efficiency rectifier, the size of the transistors and the number of stages should be considered in the impedance matching. With these considerations, an eighteen-stage voltage multiplier is implemented as shown in Figure 15 in this design. The zero-threshold voltage transistors and 0.5pF metal-isolate-metal (MIM) capacitors are used. The rectifier could convert the 50mV AC input to the 2V DC voltage with the load around 10uA; or 200mV AC input to the 2V DC voltage with the load around 20uA. Since the load current is not large enough for some applications, a large capacitor is used at the output of the rectifier to store the energy and provide the additional power to other circuits for continuous operation.

Figure 15. Optimized 18-stages rectifier

# 3.3 Low power regulator design

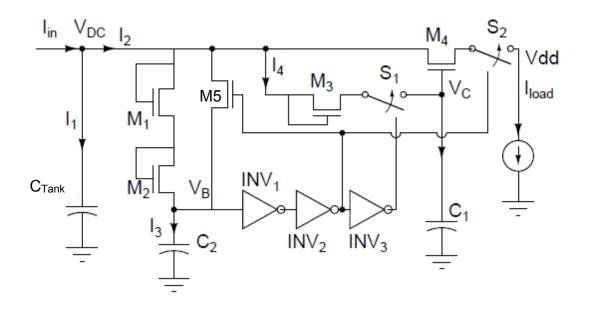

Figure 16. Proposed regulator circuits

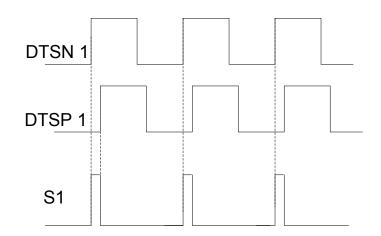

The regulator in the RFID is used to generate a stable and clean power supply for the rest of the circuits. The proposed regulator circuit is shown in Figure 16. Its input is provided by the rectifier which could be considered as the current source,  $I_{in}$ , charging the capacitance tank,  $C_{Tank}$ .  $V_{DC}$  is the voltage at the top of  $C_{Tank}$ . It works as the power supply of the regulator circuit. Initially, there is little charge stored in the capacitor tank and  $V_{DC}$  is low. Transistors M2 and M3 are off and  $V_B$ , the voltage across capacitor  $C_2$ , is low. Consequently, the output of INV3 is logic "1", which closes switch  $S_1$  to charge capacitor  $C_1$  via M3. Meanwhile, switch  $S_2$  is open to disconnect regulator load circuit from the source terminal of M4. When the rectifier circuit starts to charge the large capacitor,  $C_{Tank}$ ,  $V_{DC}$  will increase gradually. At the point that  $V_{DC}$  increases to the voltage level  $2 \cdot V_t$ , where  $V_t$  is the threshold voltage of NMOS devices, transistors M1 and M2 turn on and capacitor  $C_2$  starts to be charged. The voltage of  $C_2$  is:

$$V_B = V_{DC} - 2 \times V_t \tag{21}$$

The parasitic effects (mainly body effect) and the impacts of the charging current are ignored in this equation, since they are insignificant. With proper transistor sizing, the gate threshold of INV1 is designed to be two thirds of its power supply voltage  $V_{DC}$ . Thus, when  $V_B$  reaches  $2/3V_{DC}$ , the output of INV3 switches to ground, consequently turning off  $S_1$  and closing  $S_2$ . From the above relation and Equation 21, it is easy to see the output of INV3 switches to ground when  $V_{DC} = 6 \cdot V_t$  (which is about 2.2V for the selected CMOS technology). After  $S_1$  is open,  $V_{C1}$ , the voltage across capacitor  $C_1$ , is kept at the level of  $5 \cdot V_t$ . Hence, as long as input voltage  $V_{DC}$  is larger than  $V_{C1} - V_t$ , assuming M4 has the same threshold voltage  $V_t$ , the regulator output voltage is:

$$V_{dd} = V_{C1} - V_t - \frac{I_{load}}{g_{m4}} = 4V_t - \frac{I_{load}}{g_{m4}}$$

(22)

where  $I_{load}$  is the regulator load current and  $g_{m4}$  is the transconductance of M4. If  $g_{m4}$  is large enough (by having large size), the above  $V_{dd}$  expression can be simplified to  $V_{dd} = 4 \cdot V_t$ , which is constant. Note that transistor M5 is used to pull voltage  $V_B$  to  $V_{DC}$  level after S1 is switched off. This eliminates the static current dissipation of the inverter circuits. So the applicable energy for the load is  $V_t \cdot (C_{Tank} + C_2)$ .

In this regulator circuit, the output voltage will be mainly affected by following factors: input and output currents, leakage current and parasitic effects. To simplify the derivation, the following assumptions are applied in the analysis: (1) M1, M2 and M3 has the same threshold voltage ( $V_{t1}$ ) and size ( $W_1$ ,  $L_1$ ), (2)  $k_1 = \frac{1}{2} \mu c_{ox} \frac{W_1}{L_1}$ , (3) the

threshold voltage of M4 is  $V_{t2}$ , its size is  $\frac{W_2}{L_2}$  and  $k_2 = \frac{1}{2} \mu c_{ox} \frac{W_2}{L_2}$ , (4)  $C_1 = C_2 = C$ . In the investigation of the impacts from the input and output currents, the parasitic

capacitance and the leakage current is ignored first.  $V_{C1}$  can be approximated in

terms of overdrive voltage  $V_{C1} = 5V_{od}$ , where  $V_{od} = V_{t1} + \sqrt{\frac{I_3}{k_1}}$ ,  $I_3$  is the current

charging to C<sub>2</sub>. Also  $V_t + \frac{I_{load}}{g_{m1}}$  in Equation 22 can be substituted by

$V_{t_2} + \sqrt{\frac{I_{load}}{(1 + \lambda V_{ds}) \cdot k_2}}$ . So Equation 22 could be rewritten as:

$$V_{out} = 5V_{t1} + 5 \cdot \sqrt{\frac{I_3}{k_1}} - \left(V_{t2} + \sqrt{\frac{I_{load}}{(1 + \lambda V_{ds}) \cdot k_2}}\right)$$

(23)

Since the ratio of  $I_1$  and  $I_3$  is proportional to the capacitance values of  $C_{Tank}$  and  $C_2$ ,  $I_3$  can be derived as:

$$I_3 = I_{in} \times \left(\frac{c}{c_{Tank}} + 2\right)^{-1} \tag{24}$$

And the voltage between the drain and the source of M4,  $V_{ds}$ , is:

$$V_{ds} = V_{DC} - V_{out} \tag{25}$$

In Equation 23, threshold voltages,  $V_{t1}$  and  $V_{t2}$ , can be considered as constant which are determined by the fabrication process.  $I_{load}$  represents the current consumed by the rest circuits, which is also approximately constant.  $I_3$  is part of the input current  $(I_{in})$ , and it depends on the energy acquired by the rectifier and the antenna. Its value may varies with the change of the operating distance and the external electromagnetic power. To make the output voltage less associated with the operation environment,  $k_1$  and  $k_2$  should have large values.

Based on Equation 23, the line regulation rate ( $\frac{\Delta V_{out}}{\Delta I_{in}}$ ) and output regulation

rate ( $\frac{\Delta V_{out}}{\Delta I_{load}}$ ) can be derived as:

$$R_{1} = \frac{\partial V_{out}}{\partial I_{in}} = \frac{5}{2} \cdot \sqrt{\frac{1}{k_{1} \cdot I_{in} \cdot \left(\frac{C}{C_{Tank}} + 2\right)}}$$

(26)

$$R_2 = \frac{\partial V_{out}}{\partial I_{load}} = -\frac{1}{2} \cdot \frac{1}{\sqrt{\left(1 + \lambda \cdot V_{ds}\right) \cdot k_2 \cdot I_{load}}}$$

(27)

where  $R_1$  is the line regulation rate and  $R_2$  is the output regulation rate. Clearly, large sizes of  $M_{1-3}$  ( $M_1$ ,  $M_2$  and  $M_3$  have the same size) and  $M_4$  are preferred to reduce  $R_1$  and  $R_2$ . However, large size will induce more parasitic capacitance, which reduces the efficiency and degrades the performance of regulator as described later. So the sizes of  $M_{1-3}$  and  $M_4$  should be carefully optimized.

The leakage current impacts the regulator before and after enabling the regulator output. Before INV3 switching to "0", the voltage at node *B* will increase with  $V_{DC}$  gradually. When it's around the gate threshold voltage of INV1, both of the PMOS and NMOS in INV1 will be in saturation. So a large short circuit current will be dissipated by INVI. The maximum leakage current at the switching point is:

$$I_{leakage,max} = k_3 (4V_{t1} - V_{t3})^2$$

(28)

where  $k_3$  and  $V_{t3}$  are the parameters of the NMOS devices in INV1. Due to the effect of the leakage current, the current  $I_3$  in Equation 23 and 24 can be estimated by

$$I_3 = \left(I_{in} - I_{leakagemax}\right) \cdot \left(\frac{C}{C_{Tank}} + 2\right)^{-1}$$

(29)

According to Equation 23 and 29, the output voltage will be reduced by the leakage current. If  $I_{leakagemax} > I_{in}$ ,  $V_{DC}$  will not be able to reach 2.2V and the regulator will not be able to enter its normal operation mode. So the channel length of the PMOS and NMOS in INV1 need to be large to reduce  $I_{leakagemax}$ . In the design of the regulator, INV1 has a small leakage current and INV2 has a sharp voltage transifer curve to accelerate the model transition.

After the output voltage has been established at the output, the leakage current will draw charge from the capacitors,  $C_{Tank}$ ,  $C_1$  and  $C_2$ , which makes the output voltage and regulator efficiency reduce. Since the capacitor  $C_{Tank}$  is very large and the leakage current from  $C_{Tank}$  is usually small, which is mainly caused by the static current of the inverters, the impact of leakage current on charge tank voltage  $V_{DC}$  can be ignored.  $C_2$  can be considered as part of capacitor tank, so the leakage current impact is similar to  $C_{Tank}$  and it can also be ignored. However, the output voltage will be reduced by the leakage current on  $C_1$  will be generated by the leakage at the gate of  $M_4$ . The tunneling leakage current density has been modeled as [53] [54] [55]:

37

$$J_{DT} = A_g \left(\frac{T_{oxref}}{T_{ox}}\right)^{n_{ox}} \cdot \left(\frac{V_g V_{aux}}{T_{ox}^2}\right) \cdot \exp\left(-B_g t_{ox} \left(\alpha_g - \beta_g |V_{ox}|\right) \left(1 + \gamma_g |V_{ox}|\right)\right)$$

(30)

where  $A_g = q^2/8\pi h\phi_B$ ,  $B_g = 8\pi\sqrt{2qm_{ox}}\phi_B^{3/2}/3h$ ,  $m_{ox}$  is the effective carrier mass in oxide,  $\phi_B$  is the tunneling barrier height,  $t_{ox}$  is the oxide thickness,  $T_{oxref}$  is the reference oxide thickness, and  $V_{aus}$  is an auxiliary function which approximates the density of the tunneling carriers.  $\alpha_g$ ,  $\beta_g$ , and  $\gamma_g$  are the physical parameters determined by the CMOS fabrication process.  $V_g$  is the gate voltage of the MOSFET device,  $n_{tox}$  is a fitting parameter, and  $V_{OX}$  is the voltage across the oxide of the MOSFET device. This can be used to estimate the gate leakage of M4.

a. The coupling capacitors divider

b.The small-signal model of  $M_4$

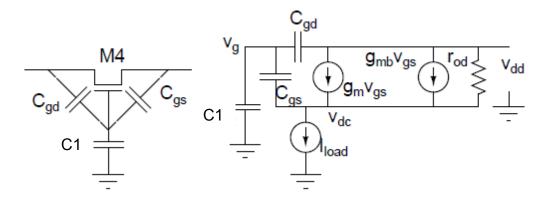

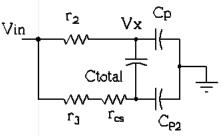

Figure 17. The model of parasitic capacitance

Another issue in this regulator is the large parasitic capacitance induced by the use of large  $M_4$ . A voltage divider will be generate by  $C_{gs}$ ,  $C_{gd}$  and  $C_1$  as shown in Figure 17(a). The small signal model of the circuit is shown in Figure 17(b). The output voltage can be derived as:

$$v_{dc} = \frac{C + A \cdot C_{gd}}{C + A \cdot C_{gd} + A \cdot C_{1}} \cdot v_{dd} - \frac{C \cdot r_{od}}{C + A \cdot C_{1} + A \cdot C_{gd}} I_{load}$$

(31)

where *A* is the instrincs gain of the regulator transistor M4,  $A = (g_m + g_{mb}) \cdot r_{od}$ , *C*<sub>total</sub> is the total capacitance at the gate of  $M_4$ ,  $C_{total} = C_1 + C_{gs} + C_{gd}$ . So the relationship between the variations of  $V_{dd}$  and  $V_{dc}$  is:

$$\frac{dv_{dd}}{dv_{dc}} = \frac{C_{total} + A \cdot C_{gd}}{C_{total} + A \cdot C_{gd} + A \cdot C_{1}}$$

(32)

If *A* is large enough and  $A \cdot C_{gd} >> C_{total}$ , the above euqation can be simplified as:

$$\frac{dv_{dd}}{dv_{DC}} = \frac{C_{gd}}{C_{gd} + C_1} \tag{33}$$

If  $C_1 >> A \cdot C_{gd}$ , we have:

$$\frac{dv_{dd}}{dv_{DC}} = \frac{1}{1+A} \tag{34}$$

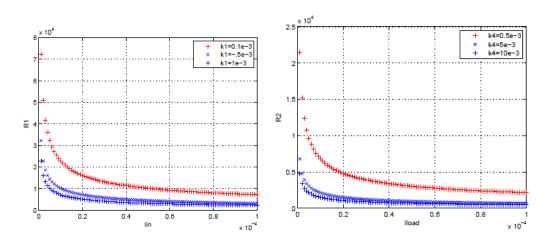

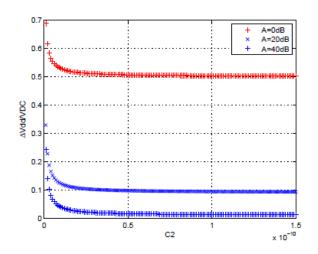

According to Equation 32 - 34, if we want to reduce the impact of the coupling capacitance on the output voltage, large A and  $C_1$  are preferred. Increasing  $C_1$  is a better choice, since the high gain usually needs large  $M_4$  which will also increases the parasitic capacitance. Figure 18 shows matlab simulations with assuming A = 10. It shows that when  $V_{DC}$  decreases by 600mV,  $V_{dd}$  will decrease by 60mV.

The proposed regulator design has a very simple circuit structure. It does not require bandgap voltage reference, operation amplifier, unit-gain buffer and loop compensation circuits that are normally used in previous traditional regulator designs [16] [17]. Also, the proposed regulator itself has zero current dissipation after the regulator output is enabled. Although the inverter circuits in the regulator design have leakage current power consumption before the regulator output is enabled, their power consumption is insignificant if the inverters are comprised of transistors with very small (W/L) ratios.

The exact voltage level of the proposed regulator output is relatively sensitive to process variations. However, the exact voltage level is not critical in this as well as many other RFID sensing applications. This is because in many sensing applications electrical parameter ratios are used to measure the interested variables and the exact voltage values are often canceled in measurement expressions.

Instead of emphasizing on the exact regulator output level, a more important design concern is to make the regulator output constant during sensing operations. Three factors potentially cause small variations at the proposed regulator output. One is the leakage current that discharges capacitor  $C_1$  analyzed in Equation 30.

40

Depending on the duration of sensing operations, the value of  $C_1$  need to be selected sufficiently large and potential leakage paths associated with  $C_1$  should be carefully examined in the layout design. The second factor is coupling capacitor in Equation 31. The voltage variation at the regulator input may affect  $V_{C1}$  through the gate-drain parasitic capacitance of M4. To minimize this,  $C_1$  need to be large. The third factor is the variation of the load current as indicated by Equation 23. The impact of this factor can be reduced by increasing the transconduction of M4,  $g_{m4}$ . Also, the variation on  $I_{load}$  can be minimized by properly scheduling circuit operations and circuit design techniques. For example, the digital circuits can be disabled during analog sensing operations to prevent digital switching activities from causing  $I_{load}$  variations. In addition, the analog sensing circuits can be designed to always drain constant current when the measurement reading is taken. Such an example is described in the following sub section.

a.  $R_1$  v.s.  $I_{in}$  with different  $k_1$

b.  $R_2$  v.s.  $I_{load}$  with different  $k_4$

c. Matlab simulation for Equation 32

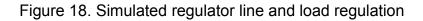

# 3.4 Resistance to digital converter

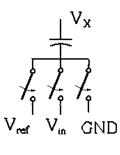

Figure 19. Resistance to digital converter circuit

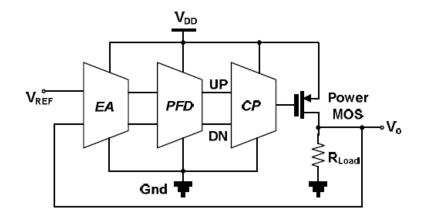

As shown in Figure 19, the RDC circuit is comprised of a cascoded current mirror (M1 - M6), a reference resistance  $R_{REF}$ , and a charge-redistribution (CR) successive approximation register (SAR) analog to digital converter (ADC). The Sol-Gel sensor, whose resistance is to be measured, is represented by resistor  $R_{SEN}$  in the figure. The resistance of the Sol-Gel sensor used in the project can vary in the range of  $200K\Omega - 700K\Omega$ . The current mirror controls the currents flowing through *R<sub>REF</sub>* and *R<sub>SEN</sub>*. To minimize power consumption, the current (*I<sub>SEN</sub>*) of *R<sub>SEN</sub>* is designed to be 1  $\mu$ A. However, the current ( $I_{REF}$ ) of  $R_{REF}$  is K times larger than ( $I_{SEN}$ ) due to the following two reasons. First,  $I_{REF}$  is used to charge the capacitor array of the CR SAR ADC and a relatively large current reduces the charging time. Second, the selection of a large I<sub>REF</sub> value allows using a small R<sub>REF</sub> value (and hence a small silicon area) to achieve a desired voltage drop across  $R_{REF}$ . For the convenience of discussion, voltages applied at  $R_{REF}$  and  $R_{SEN}$  are denoted as  $V_{REF}$  and  $V_{SEN}$ , respectively.  $V_{REF}$  works as the reference voltage in the ADC, while  $V_{SEN}$  works as the input voltage. The ADC circuit digitizes the ratio of V<sub>SEN</sub> over V<sub>REF</sub>. Assume the digital data of the ADC output is D. Then, the value of  $R_{SEN}$  can be expressed as:

$$R_{SEN} = D \times K \times R_{REF} \tag{35}$$

This equation also indicates that the power supply voltage level does not affect  $R_{SEN}$  measurement, which supports the previous discussions.

In this design,  $R_{REF}$  is implemented using poly resistor that is available in the selected CMOS technology. Due to its low temperature dependence coefficient,

temperature compensation is not needed to be considered in the current design. To cope with the uncertainties on the realized  $R_{REF}$  and K values due to process variations and devices mismatches, a simple calibration can be performed after chip fabrication. In the calibration process, instead of the Sol-Gel sensor, a high-precision resistor with known resistance value is connected to the RDC circuit. From the measured resistance, the actual value of  $K \cdot R_{REF}$  can be easily obtained from Equation 35. The error on the realized  $K \cdot R_{REF}$  value is converted into a digital word and stored in an on-chip fuse-based memory. Then, digital error compensation can be performed either by the RFID circuit or by programs in the RFID reader. In the current design, we take the latter approach to minimize the digital circuits on the RFID chip.

When digitizing the ratio of  $V_{SEN}$  over  $V_{REF}$ ,  $V_{REF}$  and  $V_{SEN}$  are fed the ADC circuit as voltage reference and ADC input, respectively. A conventional design constraint for ADC circuits is that the ADC input should be always smaller than the voltage reference level. This constraint not only unnecessarily increases circuit power consumption but also degrades resistance measurement accuracy. The former is because the ADC capacitor array is charged to a high voltage level when a high reference level is used to satisfy the above design constraint. The latter is caused by the large voltage difference between the two output branches of the current mirror. For example, if  $R_{SEN}$  value varies from 200K $\Omega$  to 700K $\Omega$  and  $I_{SEN}$  is 1  $\mu$ A, the largest  $V_{SEN}$  is 0.7 V. Then,  $V_{REF}$  needs to be 0.7 V at least. However, with this design configuration, when the Sol-Gel sensor resistance is at its low end (200K $\Omega$ ), the different between  $V_{REF}$  and  $V_{SEN}$  is about 0.5 V. Due to finite output

44

resistance of the current mirror, the ratio of  $I_{REF}$  over  $I_{SEN}$  will be impacted and, hence, the measurement accuracy is degraded.

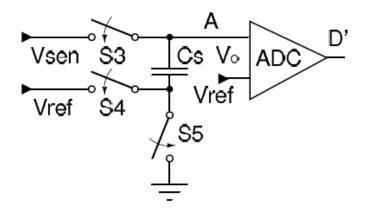

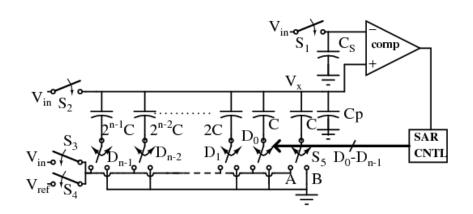

Figure 20. ADC sampling circuit with level-shifting capability

In the proposed RDC design, we eliminate the constraint,  $V_{REF} > V_{SEN}$ , by using a novel circuit technique, which is sketched in Figure 20. In this figure,  $C_S$  is the sampling capacitor of the ADC circuit. During the sampling operation, the two terminals of the capacitor are connected to  $V_{REF}$  and  $V_{SEN}$  in the design respectively. After the sampling operation, the ADC comparator first compares  $V_{REF}$  and  $V_{SEN}$ . If  $V_{REF} > V_{SEN}$ , logic "0" is assigned to the MSB of the RDC output; the status of switch S5 is not altered, and hence the voltage at node A remains  $V_{SEN}$ . Thereafter, the ADC circuit operates as a typical CR SAR ADC circuit to generate the rest bits of the RDC output. However, if  $V_{REF} > V_{SEN}$ , the MSB of the RDC output is set to logic "1". Then, the bottom plate of  $C_S$  is switched to ground by altering S4-S5 and, consequently, the voltage at node A becomes  $V_{SEN} - V_{REF}$ . After that, the ADC will follow the same charge redistribution procedure to determine the rest output bits. With the target detection range of  $200K\Omega - 700K\Omega$ , if the  $V_{REF}$  level is selected to be larger than 0.4 *V*, the new voltage level obtained by the voltage subtraction will be definitely smaller than  $V_{REF}$ . With the consideration of the low power consumption, separated sampling capacitor CS SAR ADC shown in Figure 20 is used in this design [23].

The proposed design has several advantages. First, a lowered  $V_{REF}$  level enhances the resistance measurement accuracy and reduces the energy dissipation for charging the ADC capacitor array. Second, because determining the RDC MSB does not involve the capacitor array, the proposed design uses only half of the capacitance that would be required in a conventional CR SAR ADC based implementation. In the target application, a 9-bit resolution is required and the proposed design uses a capacitor array with the size of  $256 \cdot C$  (C is the unit capacitor in the capacitor array design). As a comparison, a conventional ADC based implementation would require a capacitor array of 512 C. The reduced capacitor array size saves not only layout area but also circuit power dissipation. Third, during the sensing operation the RDC circuit always drains a constant current, which is a desirable feature to keep constant regulator output. This is achieved by using the current mirror circuit to regulate the currents going to the capacitor array or drained by the resistive loads. Since a constant current is used to charge the capacitor array, capacitors with different sizes will require different time durations to get fully charged. A variable charging cycle scheme, which is similar to the techniques in [56], is used to reduce the operation time for resistance to digital conversion.

46

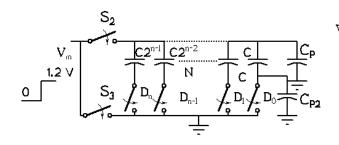

As described in previous section, because of the limit energy acquired from the rectifier circuit in long working distance or weak electromagnet field, the power supply voltage from the regulator maybe decreases during the RDC working. To save more power, the biasing circuit with high power supply rejection ratio (PSRR) is unrealistic in this application. The supply-independent biasing circuit also has a low PSRR in the condition of small current, and the large resistor and additional start-up circuit are also needed. So the simple current source in Figure 19 is applied in this circuit. The biasing current will decrease with the power supply during the operation of RDC. It will make the reference voltage of ADC  $V_{ref}$  decrease and the accuracy of RDC will also be reduced. For the current source in Figure 19, the variation of the current is given by:

$$\Delta I = k (\frac{1}{3} \Delta \nu_{dd})^2 \tag{36}$$

So the reference voltage  $V_{ref}$  will be reduced by:

$$\Delta v_{ref} = k \times (\frac{1}{3} \Delta v_{dd})^2 \times R_{ref}$$

(37)

So the reference voltage will decrease with the power supply. Assuming the n-bit digital output is  $D = D_{n-1}D_{n-2}D_{n-3} \cdots D_2D_1D_0$ , the real voltage can be derived as:

$$V_{actual} = V_{ideal} - \left(\frac{D_{n-2}}{2^2} + \frac{2D_{n-3}}{2^3} + \dots + \frac{(n-3)D_2}{2^{n-2}} + \frac{(n-2)D_1}{2^{n-1}} + \frac{(n-1)D_0}{2^n}\right) \cdot \frac{\Delta V_{ref}}{n}$$

(38)

where  $V_{ideal}$  is the voltage calculated from the digital output,

$$V_{ideal} = \left(\frac{D_{n-1}}{2} + \frac{D_{n-2}}{2^2} + \frac{D_{n-3}}{2^3} + \dots + \frac{D_2}{2^{n-2}} + \frac{D_1}{2^{n-1}} + \frac{D_0}{2^n}\right) \cdot \Delta V_{ref,0}$$

(39)

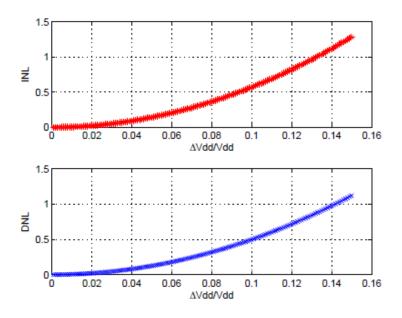

Subsequently, the *INL* and the *DNL* derived from Equation 38 and Equation 39 are expressed as:

$$INL \approx \frac{2^n \cdot a}{n} \tag{40}$$

$$DNL \approx \left(\frac{1}{8} - \frac{1}{4n}\right) \cdot 2^n \cdot a$$

(41)

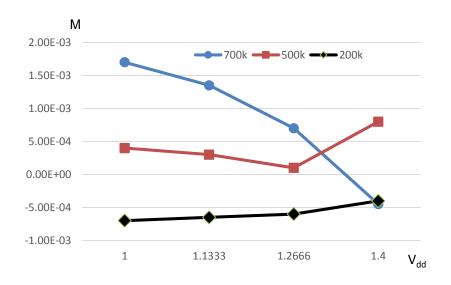

where  $a = \Delta V_{ref}/V_{ref} = (\Delta V_{dd}/V_{dd})^2$ . The detailed derivation is described in Appendix A. Figure 21 shows the Matlab simulation results of Equations 40 and 41. It shows that *INL* and *DNL* are acceptable when  $\Delta V_{dd}/V_{dd} < 0.13$ . If  $V_{dd} = 1.2V$ , the maximum decrease of  $V_{dd}$  is 156 mV. According to the previous analysis, the output of rectifier  $V_{DC}$  will decrease from 2.2V to 1.2V during RDC working. If  $\Delta V_{dd}/\Delta V_{DC} < 0.1$  which is easy to be achieved according to Figure 18,  $\Delta V_{dd}$  will be less than 158 mV, and *INL* and *DNL* will not be impacted. Because of the use of cascode structure, the mismatch of the current mirror could be considered as constant and it can be easily to be corrected.

Figure 21. INL and DNL v.s.  $\Delta V_{dd}/V_{dd}$  with n=9

## 3.5 Experiment results

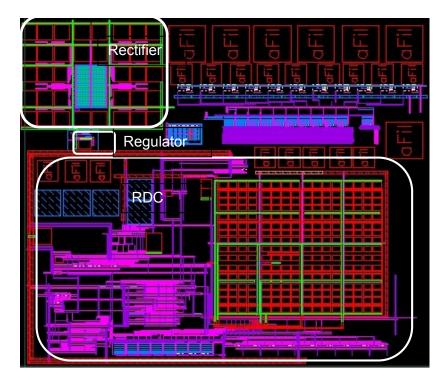

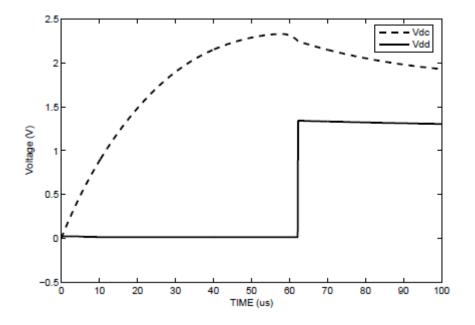

The proposed low power regulator and RDC circuits are implemented using a 0.13µm CMOS technology. The RFID energy harvesting circuit (the optimized rectifier) shown in Figure 15 is also implemented for powering the analog circuits. Figure 22 shows the layout of the design. The transistors sizes and capacitors are listed in Table 1. The transistors used in the design are zero threshold devices with minimum channel length of 420nm. Figure 23 shows the simulated rectifier and regulator outputs.

Figure 22. The layout of the proposed analog circuits for RFID sensor

Figure 23. Simulation of the rectifier and regulator

| Transistors sizes (W/L)        | 25µm/420nm |  |

|--------------------------------|------------|--|

| Capacitance of $C_C$ and $C_L$ | 500 fF     |  |

| Number of stages (N)           | 18         |  |

### Table 1. List of the devices parameters in the implemented rectifier

The rectifier consists of 18 stages and operates with 900MHz RF signals. When the input RF signal magnitude is 200mV, in the capacitor-tank charging period the efficiency of the rectifier circuit is about 10%, which is similar to a Shottky diode based implementation [49]. Note that the rectifier efficiency varies with input RF signal magnitude and load current.

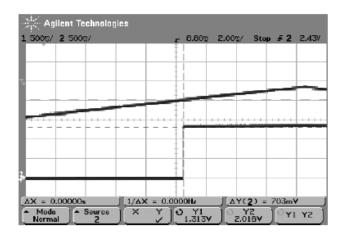

Figure 24. Transient measurement for the regulator startup

Figure 25. Measurement results for  $\Delta V_{dd}$  vs.  $\Delta V_{DC}$

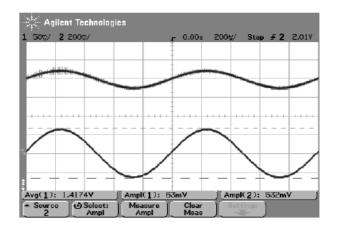

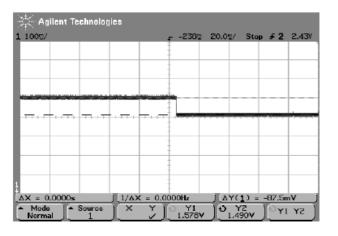

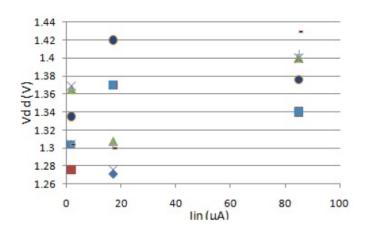

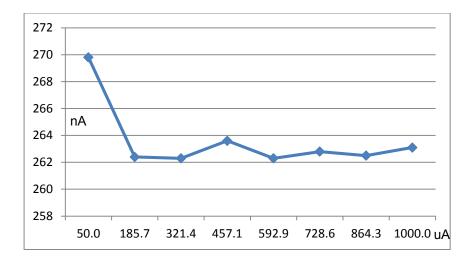

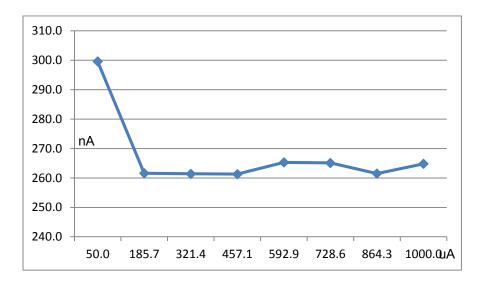

Figure 24 - 27 are the measurement results of the regulator circuit. In Figure 24, the load current is 20  $\mu$ A. It shows that when the capacitor-tank is charged to 2.02 V ( $V_{DC}$ ), the regulator starts to provide a constant voltage ( $V_{dd}$ ) of 1.31 V. The output is approximately constant as long as  $V_{DC} > V_{dd}$ . In Figure 25, when  $V_{DC}$  decreases by 532 mV,  $V_{dd}$  will drop 63 mV. According to Figure 18, it will not noticeably degrade the performance of the rest circuits. Figure 26 shows that when the load current increases from 10  $\mu$ A to 100  $\mu$ A, the drop of  $V_{dd}$  is around 87.5 mV. Figure 27 is the measurement results of  $V_{dd}$  with  $dV_{dd}/dt$  in different fabricated chips. It shows that although the start-up voltage will change with the slop of  $V_{DC}$ , which is determined by the input current, the voltage is still in the operation range from 1.2 V to 1.4 V. And the slightly changes with the variation of process can also be ignored. The performance metrics of the regulator are summarized in Table 2.

| Input regulation( $\Delta V_{dd} / \Delta V_{DC}$ )  | 11.8%    |  |  |

|------------------------------------------------------|----------|--|--|

| Load regulation( $\Delta I_{load} / \Delta V_{DC}$ ) | 972ohm   |  |  |

| Input range                                          | 1.2-2.5V |  |  |

| Current Efficiency                                   | 100%     |  |  |

| DC current                                           | 0        |  |  |

| Voltage reference                                    | No       |  |  |

| Loop compensation                                    | No       |  |  |

# Table 2. Performance metrics of the implemented regulator

Figure 26. Measurement for  $\Delta V_{dd}$  vs.  $\Delta I_{load}$

Figure 27. Measurement for  $V_{dd}$  vs.  $I_{in}$  in different chips

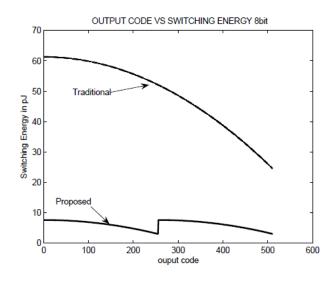

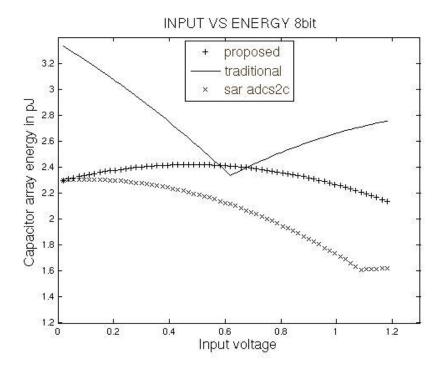

To investigate the power saving by the proposed design techniques, the energy dissipated by the RDC capacitor array is compared with the energy consumed by the capacitor array in a conventional CR SAR ADC through Matlab simulations. The method to estimate the capacitor array energy dissipation in Matlab programs is the same as that presented in [57]. The estimated energy dissipations for different RDC output values are plotted in Figure 28. The results clearly indicate that the capacitor array of the proposed RDC design consumes significantly less energy. In average, the power consumption of the capacitor array in the proposed RDC design is only 15% of that in the conventional ADC design. Since the majority of the power consumption of the RDC as well as CR SAR ADCs is due to the charging of the capacitor arrays, a significant reduction on the energy consumed by the capacitor array will lead to a large saving on the overall RDC (or CR SAR ADC) power consumption.

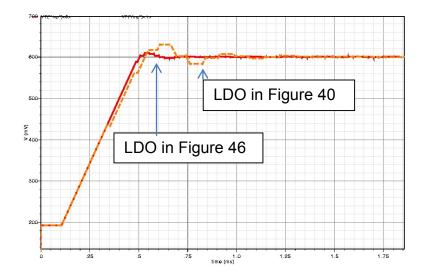

Figure 28. Comparison of capacitor array energy dissipation