## **Aalborg Universitet**

## Hard Real-Time Java

Profiles and Schedulability Analysis Bøgholm, Thomas

Publication date: 2012

Document Version Early version, also known as pre-print

Link to publication from Aalborg University

Citation for published version (APA): Bøgholm, T. (2012). Hard Real-Time Java: Profiles and Schedulability Analysis.

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- ? Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

? You may not further distribute the material or use it for any profit-making activity or commercial gain

? You may freely distribute the URL identifying the publication in the public portal ?

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# Hard Real-Time Java: Profiles and Schedulability Analysis

Thomas Bøgholm

# ABSTRACT

This thesis presents a model based approach to the program analysis of real-time Java systems and the development of Java profiles supporting such analyses. The goal of this work is to enable the development of safetycritical embedded systems in high level modern languages; languages which more elegantly capture the complexities of modern embedded systems. This work is twofold and concerns both tool development and the design of a real-time Java profile named *Predictable Java*. Throughout this project the schedulability analysis tool SARTS is developed, and then improved.

The thesis is based on six primary papers: The first paper presents the SARTS tool, a schedulability analysis tool, which among other things consists of a translator from Java bytecode to timed automata. The second paper presents design and implementations of the *Predictable Java* profile, and a constructive criticism on the upcoming Safety Critical Java(SCJ) specification. In the fourth paper, the complete reconstruction of SCJ and its predecessor the Real-Time Specification for Java(RTSJ), and the resulting four simple profiles, is presented. The third paper presents an improvement of SARTS is developed which includes the analysis of Java finalizers, made possible by the earlier work on predictable Java. In the fifth paper, a language for specifying abstract system specifications is designed, along with a techniques for checking implementation relations and schedulability for the full system; a step towards compositional schedulability analysis. The last paper describes the current state and recent work on real-time Java.

# DANSK SAMMENFATNING

Denne afhandling præsenterer en modelbaseret tilgang til programanalyse af real-tids systemer og udviklingen af Java profiler, der støtter op om sådanne analyser. Målet med dette arbejde er at gøre det muligt at udvikle sikkerhedskritiske systemer i moderne højniveausprog; sprog der mere elegant kan håndtere kompleksiteten af moderne indlejrede systemer. Dette arbejde er todelt og omhandler både udviklingen af værktøjer og et design af en real-tids Java profil kaldt *Predictable Java*. Igennem hele projektet bliver analyseværktøjet SARTS udviklet og forbedret.

Denne afhandling består af 6 primære artikler: Den første artikel præsenterer SARTS værktøjet, et skeduleringsværktøj der blandt andet består af oversætter fra Java byte-code til tidsautomater. Den næste artikel præsenterer design og implementationer af profilen *Predictable Java*, som er et modspil til den kommende Safety Critical Java(SCJ) specifikation. I en senere artikel, bliver en komplet rekonstruktion af SCJ og dens forløber Real-Time Specification for Java(RTSJ), og fire simple profiler som er resultatet af denne rekonstruktion, præsenteret. En artikel præsenterer en forbedring af SARTS, som inkluderer analyse af Java finalizers, muliggjort af det tidligere arbejde med Predictable Java. I en anden artikel bliver et sprog til abstrakte systemspecifikationer designet, sammen med teknikker til at tjekke implementeringsrelationer og skedulerbarhed af det fulde system; et skridt imod kompositionel skedulerbarhedsanalyse. En sidste artikel præsenterer nuværende og tidligere arbejde med realtids Java.

# Contents

| 1        | Introduction                 |        |                                        |    |  |  |

|----------|------------------------------|--------|----------------------------------------|----|--|--|

|          | 1.1                          | Java f | or Embedded Systems                    | 12 |  |  |

| <b>2</b> | Technical Background         |        |                                        |    |  |  |

|          | 2.1                          | Real-t | ime Systems                            | 14 |  |  |

|          | 2.2                          | Real-t | ime Systems Model                      | 15 |  |  |

|          |                              | 2.2.1  | Time Line Notation                     | 16 |  |  |

|          | 2.3                          | Real-t | ime Programming Languages              | 17 |  |  |

|          |                              | 2.3.1  | The Real-time Specification for Java   | 18 |  |  |

|          |                              | 2.3.2  | Ravenscar Java                         | 25 |  |  |

|          |                              | 2.3.3  | The Safety-Critical Java Specification | 27 |  |  |

|          | 2.4                          | Real-t | ime Scheduling                         | 34 |  |  |

|          |                              | 2.4.1  | Off-line Scheduling                    | 34 |  |  |

|          |                              | 2.4.2  | Fixed Priority Scheduling              | 35 |  |  |

|          |                              | 2.4.3  | Dynamic Scheduling                     | 35 |  |  |

|          | 2.5                          | Real-t | ime Systems Analysis                   | 36 |  |  |

|          |                              | 2.5.1  | Traditional Schedulability Analysis    | 36 |  |  |

|          |                              | 2.5.2  | Response Time Analysis                 | 38 |  |  |

|          |                              | 2.5.3  | Analysing Response Time                | 39 |  |  |

|          | 2.6                          | Model  | Checking                               | 40 |  |  |

|          |                              | 2.6.1  | Timed Automata                         | 41 |  |  |

|          |                              | 2.6.2  | Timed Automata in Practice             | 42 |  |  |

|          | 2.7                          | Platfo | rm                                     | 48 |  |  |

| 3        | Summary and Contributions 50 |        |                                        |    |  |  |

|          | 3.1                          |        | lages                                  | 51 |  |  |

|          |                              | 3.1.1  | Language Issues                        | 52 |  |  |

|          |                              | 3.1.2  | Contributions                          | 52 |  |  |

|          | 3.2                          | Sched  | ulability Analysis                     | 53 |  |  |

|          |                              | 3.2.1  | Tool Issues                            | 53 |  |  |

|          |                              | 3.2.2  | Contributions                          | 53 |  |  |

|          |                              | 3.2.3  | Perspective                            | 54 |  |  |

| 4        | Future Work                                                            | 55  |

|----------|------------------------------------------------------------------------|-----|

| <b>5</b> | Papers                                                                 | 57  |

|          | Paper A: Model-based schedulability analysis of safety critical hard   |     |

|          | real-time Java programs                                                | 59  |

|          | Paper B: A predictable Java profile: rationale and implementations     | 77  |

|          | Paper C: Schedulability analysis for Java finalizers                   | 97  |

|          | Paper E: Schedulability Analysis Abstractions for Safety Critical      |     |

|          | Java                                                                   | 111 |

|          | Paper D: Refactoring Real-Time Java profiles                           | 127 |

|          | Paper F: Towards harnessing theories through tool support for hard     |     |

|          | real-time Java programming                                             | 145 |

| 6        | Bibliography                                                           | 167 |

| 7        | Additional Papers                                                      | 183 |

|          | Paper G: Model-based Analysis of Embedded Java Programs                | 185 |

|          | Paper H: Formal Modelling and Analysis of Predictable Java $\ \ . \ .$ | 191 |

# Chapter 1

# Introduction

Embedded systems play an important role in most of the technology surrounding us today. They are for example the invisible computer systems in the traction control system of a modern car, the control system of a power plant, the control systems of the water pumps and the power metres in our houses. They also play a major role in small devices, such as hearing aids and pace makers.

Embedded computers and software differ greatly from the personal computer and office software we know and normally perceive as *computer systems*. Embedded computer systems are themselves a part of a larger system, often referred to as an *intelligent system* or *cyber physical system*. Cyber physical systems contain embedded subsystems, and thus depend largely on their correct behaviour. Correct operation is especially important since most embedded systems are mass produced, and have little or no possibility for software updates or other maintenance after being deployed [86].

This puts great emphasis on software dependability because embedded systems are often mass produced, they often carry out vital tasks inside heavy machinery, medical equipment etc., and because embedded software often cannot be updated as bugs are being detected. Therefore, even small errors can be costly or endanger human lives; there are several historical examples of how even subtle errors can cause disastrous situations:

**Therac 25, 1985-1987** The *Therac 25* radiation device, where a racecondition, a subtle error triggered by people typing too fast, resulted in the death and severe injuries of several people. A detailed investigation of the software related errors is presented in [96].

Ariane 5 Flight 501, 1996 The maiden flight of the Ariane 5 rocket, where the rocket exploded 39 seconds after lunch, delaying the project by one year, costing approximately \$400 million. This explosion was caused by an error in the system: an exception raised during the conversion from

64bit floating point to a 16bit signed integer; [92] presents an analysis of the Ariane 5 accident.

**Car recalls** Car companies are some of the major consumers of embedded systems technology; it is estimated that up to 20% of the systems produced are used by the car industry. Therefore it is not surprising that faulty systems occasionally make it to the market, affecting a great number of people, and such problems have in fact resulted in both problems and product recalls. Some examples from the media include [84]:

- Toyota recalls 75,000 Prius hybrid cars in 2005. The engine would shut down due to a software error [111],

- in 2003 There was an example of a computer crash in a BMW. Unfortunately, the finance minister of Thailand was inside the car when it happened, and a guard was forced to break a window to let him escape, since the windows, the doors, and air conditioning did not work [151],

- in 2002, BMW recalls the 745i. The fuel pump would stop working if the fuel tank was less than one third full,

- in 2001, 52,000 Jeeps were recalled due to software error.

Furthermore, a large recall of up to 6.5 million vehicles and the discontinuation of eight models by Toyota in 2010 due to *uncontrolled acceleration* problems are suspected to be related to embedded system failure, although Toyota is claiming it to be a problem with the door mat catching the pedals[3].

These are of course some of the most published cases of malfunctioning systems. They are used here to illustrate how subtle bugs can manifest themselves in a larger system. More common, however, are noncritical crashes of network switches, mobile phones, dish washers etc., errors often solved by restarting the device and most often resulting in only some inconvenience for users the involved.

However, being able to reduce the amount of errors in embedded systems will lead to higher quality products and lower recall rates, and will therefore give a company a competitive advantage and increased revenue.

**Real-time embedded systems** A subgroup of embedded systems are also subject to *real-time requirements*. Real-time systems are systems where not only functional correctness, i.e. correct computation, is important, but also the time needed for the computation. In real-time systems, the *timeliness* of the computation is just as important; if the result of a computation is not available within a set amount of time, it may result in a system failure.

In the example of a modern car, the traction control system has a realtime requirement in that when measurements of a wheel indicate a loss of road grip, an action must be performed immediately to prevent the car from sliding. It is not enough to calculate how to prevent the car from sliding, variables must be calculated and the result ready for processing, such that an action can be taken before the car actually slides.

Therefore, with the increased integration of embedded systems in our society and the demand for increased functionality, the complexity of these systems increases accordingly. This increase in complexity, and the fear for the aforementioned failures, calls for new techniques and tools for embedded systems development, as the use of traditional development techniques and tools for the now very complicated systems are becoming increasingly challenging.

This is partly caused by the programming languages in use in systems development today. The languages such as C and assembly, which are often used for todays systems, do not support the capturing and structuring of the complexities in modern systems, as well as modern programming languages.

Java is an example of a very popular modern language, taught in todays computer science classes, and used in a variety of large scale projects. Java is an object oriented language, giving an advantage over purely imperative languages like C when programs grow large, and was designed as an improvement over the existing popular languages. It is especially inspired by C/C++ syntax, but differs in in some important aspects; it was designed to result in *simpler programs*:

- A large difference is the allocation and handling of memory. In Java, programs will never run into problems caused by dangling pointers; pointers to deallocated memory. Allocation and deallocation is automatically handled, usually by a garbage collector, making dangling pointers impossible.

- Java is concurrency aware and have the notion of synchronized methods and regions. This is a large improvement over C/C++, where concurrency is achieved only through libraries, of which many implementations with varying semantics across platforms exists, hampering portability.

- Java is single inheritance, resulting in a simpler inheritance semantics; However, in Java, classes are allowed to implement multiple *interfaces*, mimicing multiple inheritance.

- Another advantage is that, because of these differences along with the Java standard library, productivity in Java is increased, fewer bugs are introduced, and it is easier to debug; [117] presents a study comparing the two languages based on bugs and productivity.

Another reason to consider Java is that this language is becoming popular in universities, and is to many students their first and primary programming language. This results in a situation with a shortage of C-programmers and an abundance of Java programmers, and with the increased interest in embedded systems development, finding qualified programmers in the languages used today may be prove difficult; in [106], the authors presents a view on this discussion.

### 1.1 Java for Embedded Systems

Java is a popular language for large scale systems, however, many of the features that make Java a language suitable for large projects are also features that make it unsuitable for embedded systems development. Embedded systems are often special purpose devices, and their interfaces are not as well defined and polished as the devices we use on personal computers. Programming such systems often require direct memory access in order to communicate with actuators and sensors. This is one of the reasons why low-level languages like C are used for such systems, as their low-level nature easily provides access to the underlying hardware.

In Java there is no direct access to the underlying hardware, as Java is built for a virtual machine, acting as an extra layer between the code and the hardware executing the program. This requires a virtual machine implementation to run on small devices, requiring additional memory, space and processing power.

The abstract layer exposed to the programmer also makes it difficult to access hardware and memory directly in standard Java, however, techniques such as *hardware objects* [133] have been suggested to allow hardware access in a structured fashion.

This abstract layer also makes reasoning about execution time very difficult, as multiple actions in multiple layers are required for each Java instruction. The difficulties in execution time reasoning are further complicated by the garbage collection based memory management of Java. Garbage collection makes reasoning about execution time very difficult, since the garbage collector can, in principle, run at any given time interrupting the program for an unspecified amount of time, i.e. the time it takes to search for dead objects and releasing the memory. To the contrary, in low-level languages, the execution time is more directly visible, as the program is translated into instructions executed directly by the hardware; another reason why low-level languages are still used extensively. In recent years, however, much research has been put into real-time enabling the high-level programming language Java, starting with Real-Time Specification for Java (RTSJ) [35, 37], and later focusing on safety-critical and embedded systems in Safety Critical Java (SCJ) and related research [137, 130, 76, 91]. There are three main areas which needs work for improvement for Java to become more suitable for safety critical embedded systems:

- Language The development of a *Java Profile*; a tweaking of the Java language in a way, such that programs written in this profile will be suitable for program analysis,

- **Tools** Analysis tools for validating programs written in the defined profile. These tools will be used to check overall properties properties such as system schedulability, but also that programs are within the boundaries set by the profile.

- **Platform** The development of a predictable execution platform with minimal footprint, making it suitable for small devices, and predictable memory allocation,

This thesis will focus on the two first points, **Language** and **Tools**, while utilizing recent work on the last point, **Platform**.

## Chapter 2

# **Technical Background**

This chapter presents the technical background for the papers presented later in this thesis. The first section gives a short introduction to real-time systems, followed by the definition of a real-time model as a way of describing real-time systems. Section 2.3 presents real-time systems development in Java, first the real-time specification for Java, followed by a summary of the upcoming safety critical Java specification. Section 2.4 gives an overview of real-time scheduling techniques, then a section on real-time systems analysis in section 2.5, followed by a section on real-time model-checking techniques and tools in section 2.6. This chapter concludes by discussing the present and future state of real-time systems analysis.

## 2.1 Real-time Systems

This chapter gives an overview of real-time systems design and defines the terminology used in the rest of this thesis. First the types of real-time systems are shortly introduced, then a task model used to reason about such systems is presented along with real-time scheduling principles.

There are three types of real-time systems, differing in the importance of timeliness and the consequences of a missed deadline.

- **Soft real-time systems** are systems where the timeliness is least important, and where a missed deadline is merely an inconvenience, such as a user waiting for a response to the action he just performed. This could be the interface on a mobile phone.

- **Firm real-time systems** is a subclass of soft real-time systems, where deadline misses are tolerated, and the result of a delayed calculation provides no value to the system, and is therefore discarded. An example of this is a media streaming system. If a frame is delayed a few seconds, it will be dropped and not displayed.

Hard real-time systems are the strictest of the three, where a deadline miss is considered an error. In a hard real-time system such an error may be disastrous, e.g. a missile defence system, missing an incoming attack.

Often, systems are compositions of subsystems in some of these categories. It is important the hard real-time system components do not suffer from interference from none or soft real-time components [45]. Depending on whether the class of system developed, different techniques apply, especially in choosing scheduling algorithm and analysis techniques. In this thesis, we are only concerned with **hard real-time systems**.

### 2.2 Real-time Systems Model

This section defines a model used to describe real-time systems. This model is used in the design phase of the development and is the input for some verification techniques. In this model, a real-time system is expressed as a group of tasks, with task properties, such as deadline, and execution time. Tasks are released, i.e. their execution is started, according to a release pattern, which is either periodic or aperiodic. This release pattern continue until system shutdown or possibly forever. A special case of the aperiodic release pattern is introduced, as an aperiodic pattern with a minimum inter-arrival time constraint, known as the sporadic release pattern. This constraint makes reasoning about aperiodic tasks in a hard real-time environment possible, as the release rate is bounded by the added constraint. It would otherwise be hard to include a guarantee that all tasks would meet their deadline, since a short time burst of aperiodic task releases may delay all the tasks of a lower priority.

The basic parameters of tasks in this model are:

- D, the deadline relative to the task release,

- T, period, in case of a periodic task, or the minimum inter-arrival time in case of sporadic tasks,

- C, the execution cost of the task, or Worst Case Execution Time (WCET) of the task, and

- *B*, the worst case blocking time experienced by a task.

The two first parameters, D and T are part of the specification of the tasks, and come from the problem domain. For example, in a missile defense system, there is a hard deadline on the task calculating how to shoot down an incoming missile, which may be calculated based on assumptions on the

distance a missile can be detected, and the time before impact. Such assumptions will also be the base of the choices of periods or minimal inter-arrival time.

The execution time C is the result of a worst case execution time analysis, a conservative estimate of the maximum time needed to execute the task, in isolation without any interruption from other tasks; a good overview of techniques and tools for WCET analysis is provided in [167].

B, the worst case blocking time is a conservative estimate of the maximum blocking a task may experience, in there case of shared resources between tasks. This is an upper bound, and it is not certain this blocking will be experienced at all. A task is blocked if it, according to the scheduling strategy, is the task with the highest priority, however, its execution is prevented by a lower priority task holding a resource.

Before presenting scheduling principles and related algorithms, a notation for presenting the execution of real-time systems in this model is presented in the next section.

#### 2.2.1 Time Line Notation

To be able to reason about tasks and their execution patterns, we define a graphical notation of task executions. This graphical representation of task release and execution patterns will be used throughout this thesis.

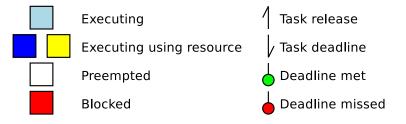

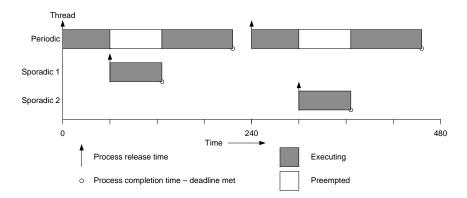

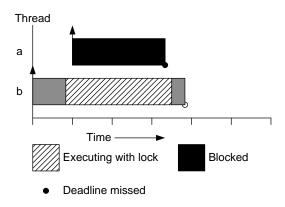

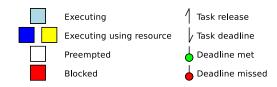

This time line notation, inspired by [45], is depicted in Figure 2.1.

Figure 2.1: Time line notation

In this terminology, when a task is:

- Executing: the task is exclusively using the processor.

- Executing using resource: the task is exclusively using the processor holding the resource represented by the colour.

- Preempted: the task is interrupted by higher priority task.

- Blocked: the task is unable to run because a lower task holds a resource and has elevated priority.

The time points can be of the following types:

- Task release: the task is started, meaning that it is either executing, executing using resource, preempted, or blocked.

- Task deadline: the task must have finished execution by this time.

- Deadline met: the task finishes its executing before the deadline.

- Deadline missed: the task failed to finish its execution before the deadline.

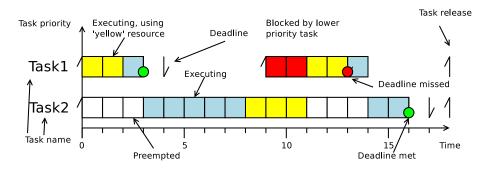

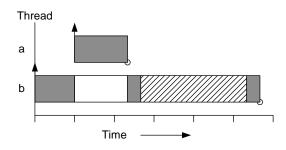

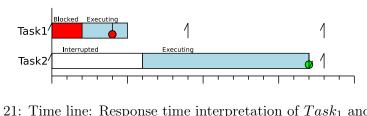

Consider the example in Figure 2.2. In this example there are two periodic tasks, Task 1 and Task 2, with deadlines 4 and 17, and periods 9 and 18 respectively. Task 1 has the highest priority, starts by executing for two time units with exclusive rights to the resource marked as the yellow resource, and then executes for one time unit, finishing before reaching its deadline. Task 2, the lower priority task, starts out preempted for three time units, while Task 1 is executing; then executes for five time units, before entering a critical section using the yellow resource for three time units, blocking Task 1 for two time units since Task 1 is trying to enter a critical section using the resource. At 11, Task 2 is preempted by Task 1, which executes as in last release, but misses its deadline at 13.

Figure 2.2: Time line example

## 2.3 Real-time Programming Languages

Embedded systems are today mainly programmed in the C programming language, or in a variant designed especially for embedded systems. This is because C, while being more abstract than assembly languages, allows lowlevel access to the underlying hardware and it allows the production of fast programs with low memory overhead. Its semantics are, however, influenced by the hardware on which it is executed and there is no language support for concurrency [124]; these are just two of the many reasons why C is not the best language choice for critical systems. Java is a modern language suitable for complex systems development, however, it is not very suitable for real-time embedded systems, especially due to lack of predictability in execution time. In recent years, however, Java has received much attention from the real-time community, and is being suggested as a new alternative to the traditionally used languages.

The Real-Time Specification for Java (RTSJ) was the first standardisation project working with standardising a real-time version of Java. RTSJ was proposed in 1998 as JSR-1<sup>1</sup>, and the initial specification was accepted by Java Community Process (JCP) in 2000. Since then, a number of bugs and inconsistencies were discovered, and six years after the initial version, version 1.02 was released June 2006. The requirement for compatibility with the first version by the JCP, resulted in a new proposal for RTSJ 1.1 was suggested in 2006, as a new specification under the name JSR-282 [53], allowed to break compatibility with the original specification. The newest version of this was released in 2009 [54].

The RTSJ received a great deal of attention in the real-time community, and it became apparent that the RTSJ was far too dynamic and expressive for high integrity systems [129, 122, 137, 91].

This lead to the work on smaller real-time profiles based on RTSJ, restricted with a smaller set of available, such that programs written are easier to analyse using static analysis techniques and thereby more likely to be certified. The work on such profiles relate to what has been previously done for Ada to enable the development of certifiable safety-critical systems. This work has resulted in Ada profiles such as SPARK [48, 18] and the Ada Ravenscar profile [56].

#### 2.3.1 The Real-time Specification for Java

The real-time specification for Java was proposed to allow real-time programming in Java, as standard Java lacks the properties needed for a real-time language. Predictability in particular was an issue, however, it is an attractive language for real-time and embedded systems programming. Java is an attractive language because it by design offers safety, object orientation, language level concurrency, and of course the write once, run everywhere philosophy of Java; features that all are attractive for such systems.

Standard Java, however, is not designed with real-time or critical systems in mind. In fact, some particularities, for example thread behaviour, are intentionally specified weakly [36], when designed by James Gosling in 1995. This was done in order to achieve high portability, which is one of the main design criteria for Java.

RTSJ strengthens the Java specification through refined semantics and a number of classes. The design philosophy behind RTSJ is based on cri-

<sup>&</sup>lt;sup>1</sup>http://goo.gl/vkRLm (http://jcp.org/aboutJava/communityprocess/mrel/ jsr001/index2.html)

teria such as backwards compatibility, predictability, standard Java syntax, etc. However, in some cases these criteria are conflicting; an example is backwards compatibility which suffers in order to provide predictability, e.g. standard Java threads have been changed to allow the design of a predictable extension. The RTSJ extensions are residing in the javax.realtime package, and provides improvements in six important areas [36, 163]:

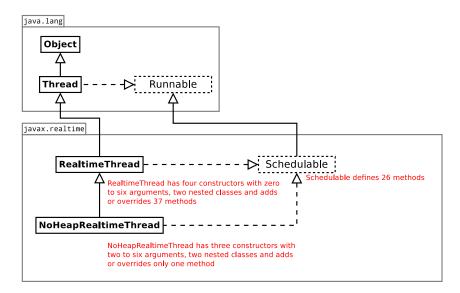

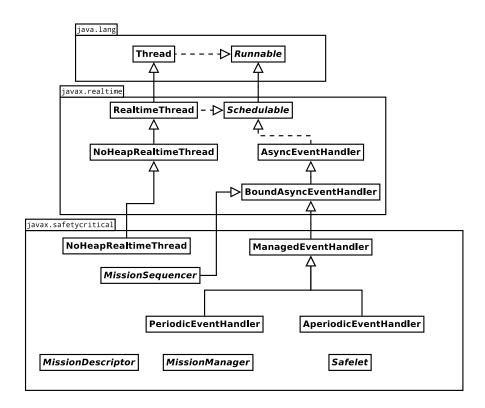

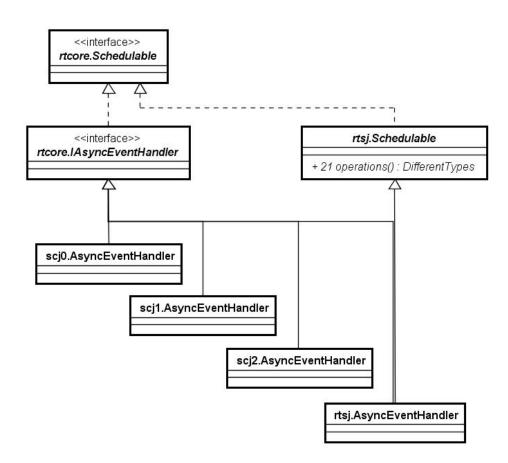

1. Real-time threads Real-time threads are introduced in the RTSJ due to the semantics of standard Java threads [36] being weakly specified, intentionally, to ease potability to other systems. Two new thread classes are introduced: RealtimeThread and NoHeapRealtimeThread. These, and their relationship to standard Java is shown in Figure 2.3. The latter of the two, NoHeapRealtimeThread, is not allowed to access heap memory, and can thus be allowed to safely preempt the garbage collector, as the heap state will always be consistent.

Figure 2.3: RealtimeThread classes in RTSJ

The RealtimeThread extends java.lang.Thread further by adding ReleaseParameters and MemoryParameters to allow implementation of periodic threads and other common thread types. The real-time threads implements the newly introduced javax.realtime.Schedulable interface, and defines 37 new methods and 4 constructors implementing RTSJ thread related capability, such as a refined thread group concept in the case of scoped memory, overrun handlers, and asynchronous interruption.

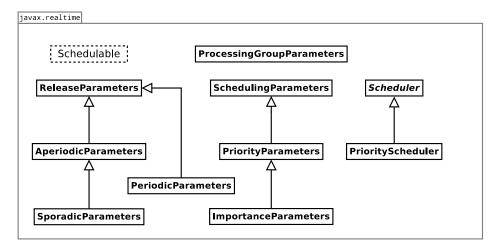

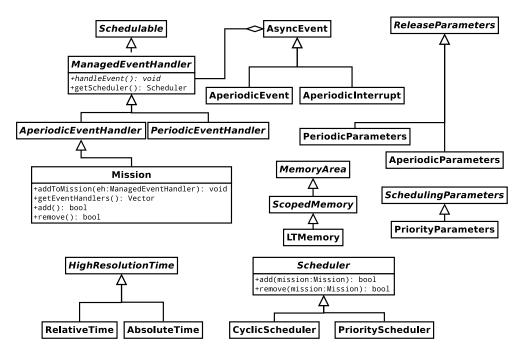

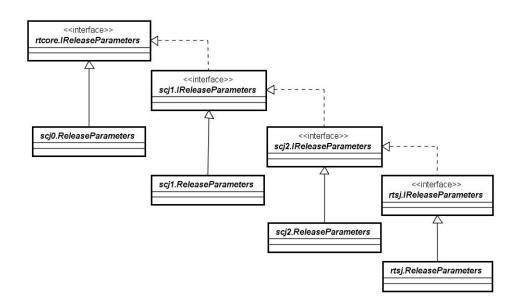

2. Scheduling RTSJ adds a number of classes in the area of scheduling in order to provide real-time facilities to Java. An overview of the classes defined related to scheduling can be seen in Figure 2.4. The Schedulable interface, extending the java.lang.Runnable interface, is introduced to generalize the concept of schedulable objects making RTSJ independent of the thread concept, and making it possible to support any type of concept other than threads, e.g. tasks. It is worth noting that this interface is quite elaborate, defining 23 methods to be implemented.

Figure 2.4: Scheduling related classes in RTSJ

Apart from implementing the Schedulable interface, a schedulable entity must have information on release criteria and other scheduling requirements. This information is contained in the various parameters class hierarchies of Figure 2.4:

- ReleaseParameters which describes the release-pattern of a schedulable object, with the default implementations: AperiodicParameters, SporadicParameters, and PeriodicParameters, parameters for each type of real-time thread or task; parameters such as sporadic parameters hold information about minimal inter-arrival time, and an exception will be thrown in case of violation of this property;

- SchedulingParameters, which contains information used by the scheduler; default implementations are PriorityParameters, determining the priority of a schedulable object and used when execution order is determined by a single integer, and the subclass ImportanceParameters, which adds an importance parameter, an extra priority parameter used in the case when two tasks share the same priority level.

Scheduling in the RTSJ is intended to be as flexible as possible. Therefore it should be possible to add new scheduling algorithms; The specification [36] even mentions dynamic loading of scheduling policy modules, in future versions of the specification. It is the intention to allow new scheduler implementations through extension of the abstract Scheduler class, however, RTSJ does not make this possible as an RTSJ user, but this should be part of a specific RTSJ implementation.

A minimum RTSJ implementation must provide at least one scheduler implementation, the PriorityScheduler. This is a fixed priority preemptive scheduler with 28 unique priority levels. Of the current RTSJ implementations from Sun (Java RTS), Aicas (JamaicaVM), Timesys, and IBM (WebSphere Real-time), the PriorityScheduler is the only scheduler implementation available.

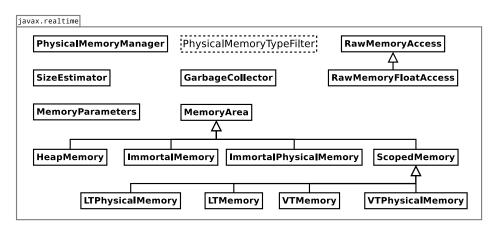

3. Memory management There are several memory related classes in RTSJ, and they are purposed to allow different types of memory allocations in different parts of a program, with the main types being immortal memory, heap memory, and scoped memory; an overview of the memory management classes is shown in Figure 2.5. The classes

Figure 2.5: Memory related classes

of the MemoryArea hierarchy provides the functionality to allocate objects, each with different semantics. The MemoryArea provides methods for allocating objects inside the area, querying consumed memory in the particular area, getting the total size of the area, and different methods used to execute logic using the memory as allocation context. That is, objects allocated using new in the logic executed in the area, including libraries used, are allocated inside the memory area and are deallocated when the area is closed.

**ImmortalMemory** Objects allocated in this area will never be deallocated or garbage collected, and hence objects in immortal memory may be referenced from every thread and schedulable object in the program.

- **ImmortalPhysicalMemory** This is a separate class with the same properties as ImmortalMemory, however, it uses a specified physical address space.

- HeapMemory The HeapMemory class allows logic non-heap allocation contexts execute and allocate in heap memory, using the method executeInArea(Runnable logic).

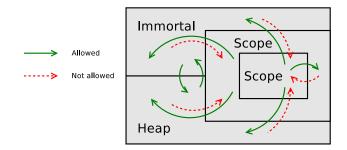

- **ScopedMemory** This is a type of memory area differing most from ordinary heap memory known from standard Java. This hierarchy provides an areas with limited life time, freed when no schedulable object has access to objects inside. The scoped memory areas are advantageous from a performance and predictability point of view in the sense that no garbage collection is needed, and no deallocation of objects is performed. The scope is simply torn down as the data within a stack frame. However, it is a very challenging, error prone, and unusual programming model for ordinary Java programmers [119, 78, 118, 38]; techniques and patterns have been suggested in [118, 38], to ease the use of scoped memory areas. The main issue with scoped memory areas is that they introduce the possibility of dangling references; this is not allowed in Java, and therefore run-time checks are needed to ensure that no dangling references exist. These runtime checks are performed at every memory operation and exceptions are thrown at illegal access. An overview of memory areas and references between areas is shown in Figure 2.6; only references to objects of an area with longer lifetime are allowed.

There are four types of scoped memory areas specified by RTSJ, these are:

- Linear time scoped memory: LTMemory and its physical memory variant, LTPhysicalMemory which specify the use of a given physical address space range. These areas guarantee allocation in linear time in the size of the allocated object.

- Variable time scoped memory: VTMemory and its physical variant VTPhysicalMemory; these areas do not specify bounds on allocation time.

Additional memory classes for raw memory access are provided, giving direct access to a fixed sequence of bytes in physical memory. Access set/get methods are provided for most primitive types, including float types in the specialized RawMemoryFloatAccess class. Objects cannot be allocated this way, as this would be unsafe [36] because the memory it is not managed.

Some classes not directly associated with allocation are provided:

Figure 2.6: Rules for references in the RTSJ memory hierarchy

- SizeEstimator: provides size estimates of objects.

- GarbageCollecter: provides information about garbage collector overhead and temporal behaviour, and allows limited capabilities to alter the garbage collection algorithm.

- PhysicalMemoryManager: responsible for physical memory access, and should not be implemented by the RTSJ user, but rather equipment manufacturers or the like. An additional interface related to this is PhysicalMemoryTypeFilter, describing memory characteristics of devices, and is to be used only by the physical memory manager.

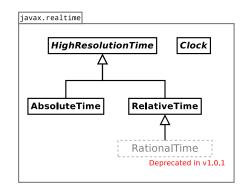

- 4. **Time** There are five time related classes in RTSJ, depicted in Figure 2.7. One Clock class used to access time values, and three time representations generalized in the HighResolutionTime class:

- High resolution time The class HighResolutionTime represents time with nanosecond granularity. This class is used as frequent as possible throughout the API and its subclasses will be used appropriately according to the time they represent. The direct subclasses are RelativeTime and AbsoluteTime. These time-representations has an associated clock-object which determines how the time is interpreted e.g. in timers.

- Rational time The class RationalTime, is represents intervals divided into subintervals, and is supposed to represent period in periodic events, but allow for some jitter. The use of this type of time representation has been subject to much confusion and as of RTSJ 1.0.1 this class is marked as deprecated.

- 5. Asynchrony and timers RTSJ provides the ability to bind logic to internal and external events, and the ability to perform asynchronous transfer of control. The class AsyncEventHandler contains logic executed when events occurs, and have much the same parameters as

Figure 2.7: Time related classes

RealtimeThread classes, such as associated memory area, release parameters etc., and it also implements the Schedulable interface. When events occur the handler is dynamically bound to a real-time thread, though a specialized version, BoundAsyncEventHandler has this execution context preallocated.

Asynchronous event handlers are fired by asynchronous events, represented by the AsyncEvent. The AsyncEvent class can be used directly to fire an event handler, or the Timer subclasses, which are the PeriodicTimer or the OneShotTimer.

RTSJ introduces the concept of asynchronous transfer of control, which will immediately take control from a running schedulable object. This is achieved using special exceptions thrown inside a thread, by running thread.interrupt(), terminating the currently executing method, and not continue execution, even after handling the event. As this could cause an inconsistent state, threads will only be interrupted, i.e. accept the transfer of control, if it is currently executing method declaring that it throws the AsynchronouslyInterruptedException. There are some special semantics used in these types of exceptions. After catching the exception, the program must manually stop the propagation of the exception using AsynchronouslyInterruptedException.clear().

6. Standard Java Backwards compatibility to standard Java programs is one of the guiding principles behind the design of RTSJ, however, some modifications to standard Java classes are required in order to do a proper implementation. The need for modifications is due to the introduction of Real-time threads in RTSJ which inherit from the Java thread class, java.lang.Thread, and override the set/getPriority methods. The most important difference affecting standard Java is the requirement that priorities set by Thread.setPriority must not violate the synchronization protocol in use: priority ceiling or priority inheritance, controlled by the classes PriorityCeilingEmulation and PriorityInheritance. It is interesting to note that in the family of RealtimeThread descendants, setPriority will throw IllegalArgumentException in case the set priority is out of the currently allowed range<sup>2</sup>. Additionally, setPriotiy may throw ClassCastException if the thread is a real-time thread and its SchedulingParameters object is not an instance of PriorityParameters. An overview of these changes can be found in the Standard Java Classes section of the RTSJ 1.0.2 specification[37].

Java thread groups, ThreadGroup, are changed to adhere to the memory management of RTSJ. Changes are needed because a root Thread-Group object resides in heap- or immortal memory, and from that ThreadGroup objects are created in a tree like manner. From this follows:

- A thread group cannot be created in scoped memory, since references to scoped memory are not allowed from outside the scope.

- No thread created in a scope can be part of a thread-group, and thus holds a null thread group reference.

- NoHeapRealtimeThread can not be a member of a thread group.

This has some interesting consequences for threads and thread groups; the interested reader is referred to the Standard Java Classes section of the RTSJ 1.0.2 specification. It seems such changes may seriously affect the backwards compatibility principle, however, this effect is to be expected and the changes somewhat justified. One could argue, however, that such changes are dangerous, as there will be programmers who are firm in Java, but new to RTSJ – and after all, an argument often used in the discussion about Java for real-time systems, is the large number of Java developers.

Apart from these changes, classes for handling monitor control i.e. either priority inheritance or priority ceiling, other general system settings, and tools such as wait-free queues etc. are also part of the RTSJ. Also, there are 18 new exceptions which have been added to RTSJ.

#### 2.3.2 Ravenscar Java

The real-time specification for Java has been criticised for being too large and dynamic for high integrity systems, and work in the direction of defining analysable and safer subsets of the RTSJ have since been done. Inspired by the Ravenscar profile for Ada [56], which has become the *de facto* standard in the high integrity system domain [91], the Ravenscar Java profile [91] is

$<sup>^2\</sup>mathrm{A}$  set of threads in RTSJ may have different schedulers, so the allowed priority-range may vary for each thread in the system.

a Java profile designed for high-integrity systems. It alleviates some of the problems of the RTSJ, and is an attempt to design a Java profile resulting in more reliable systems, following a set of software guidelines used by the U.S. Nuclear Regulatory Commission [1], and provides predictability in the areas of memory utilization, timing, and control/data flow.

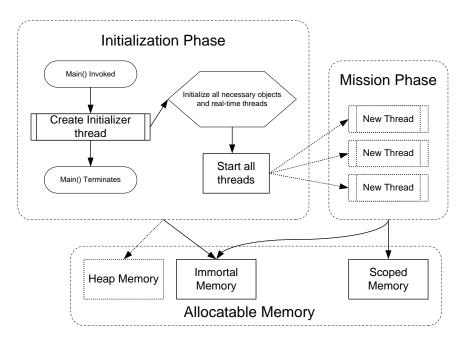

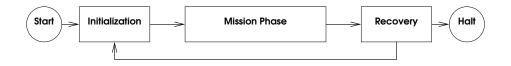

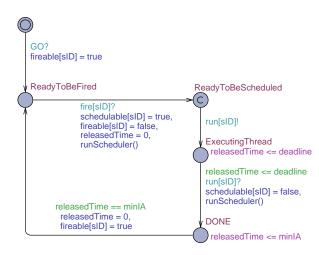

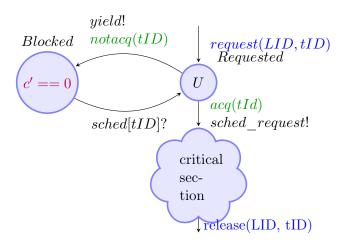

Figure 2.8: Execution phases in Ravenscar-Java [91]

The computation model offered by the Ravenscar profile is divided into two phases: the initialization phase and the mission phase, which are depicted in Figure 2.8. The initialization does not have real-time requirements, and is responsible for performing initialization of data and threads, where the mission phase, is the critical phase of the program subject to real-time requirements, where the system will be spending most of the time. In a mission, there are sporadic or periodic threads subject to fixed priority preemptive scheduling.

To simplify the memory model, the use of garbage collector in Ravenscar is forbidden, and only the linear time memory and immortal memory is offered, as defined by RTSJ. Furthermore, memory areas cannot be shared between tasks and cannot be nested.

To simplify the program structure and flow, the profile:

- Requires that all classes defined in the program must have constructors performing initialization of all class-fields.

- Forbids the use of asynchronous transfer of control.

- Puts restrictions to the use of continue and break.

- Disallows the use of the wait and notify methods.

- Requires that all for-loop constraints are statically defined.

**Issues** The Ravenscar Java profile builds on the body of knowledge gained in the high-integrity Ada community, and certainly defines a more analysable subset of RTSJ, suitable for high-integrity systems. The approach, however, builds on the RTSJ and through class inheritance inherits some of the complexities instead of hiding these through composition. Moreover, some of the enhancements may result in more complex programs, as a mixture of requirements, such as deadlines and periods and parameters for execution time cost. These are pointed out in [137]. Additionally [144] points out inconsistencies and weaknesses in the semantics, and questions the notion of deadline missed handlers, and furthermore suggests the *RAVENSCARlet*, which is a concept analogous to the MIDlet of Java Micro Edition (Java ME).

#### 2.3.3 The Safety-Critical Java Specification

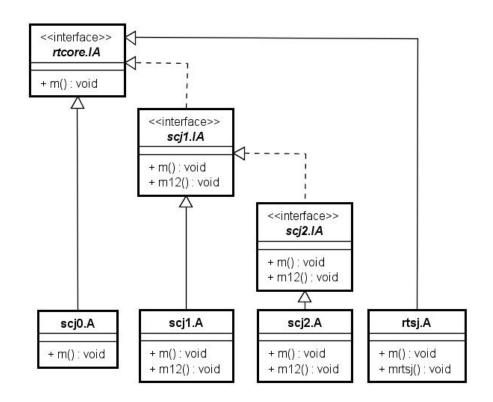

This section provides an overview of the Safety Critical Java Specification, based an early draft from August 2008<sup>3</sup>, as some of the work in this thesis is based on this version. Later, some differences between this and the latest draft, version 0.79, May 16 2011, are highlighted.

The Safety Critical Java specification is a Java profile proposal, aimed at development of safety critical embedded applications certifiable under the DO-178B/ED-12B[125, 126] specification<sup>4</sup>, level A.

#### **DO-178B** Specification

The DO-178B specification is a specification used in the certification process in the aviation industry. It contains five levels rating from A to E, where the levels A, B, C are critical levels, and the levels D, E, are noncritical levels. The levels are informally described in [103] as:

- **Level A** Errors at this level are *catastrophic* and will prevent continued safe flight and landing.

- **Level B** Errors at level B are *hazardous* potentially causing fatal injuries to a small number of the aircrafts occupants.

- **Level C** At this level, errors are a *major failure* condition, resulting in discomfort and possibly injuries to aircraft occupants.

<sup>&</sup>lt;sup>3</sup>Safety Critical Specification for Java, version 0.5, August 2008

$<sup>^4\</sup>mathrm{ED}\text{-}12\mathrm{B}$  is the European version of DO-178B.

**Level D** A non-critical level where errors are *minor* and do not reduce aircraft safety or functionality.

Level E At this level, errors have *no* effect on aircraft operational capability.

The three critical levels, A, B, C, are focused upon in SCJ.

#### **SCJ** Introduction

SCJ, while being based on RTSJ, puts additional constraints on the Java language. SCJ inherits functionality from RTSJ, but constrains some of the RTSJ complexities through the use of annotations, such as the SCJAllowed annotation, which, for example, specifies the level e.g. a method is allowed. In SCJ the following areas are changed:

- Concurrency and memory Many new restrictions are put on allocation, heap usage and concurrency to simplify program analysis. These restrictions are common in the safety critical community [103, p. 6]. These restrictions are based on RTSJ (version 1.0.2) and Java version 5. A safety-critical application will be able to execute correctly on an RTSJ compliant platform with Safety Critical Java libraries.

- **Classes** The new classes provided by SCJ will be implementable using RTSJ, however, they will be hiding much of the complexities from RTSJ.

- **Annotations** SCJ comes with annotations, used to restrict memory management and concurrency to aid analysis. They are used to document programs with programmer made assumptions.

The levels A,B,C in the DO-178B specification corresponds to three levels defined by SCJ, but denoted level 0,1,2 respectively.

#### SCJ Overview

To facilitate certification, SCJ describes a more restrictive programming model than RTSJ, especially with regards to concurrency and memory usage. At its top level, SCJ introduces missions and safelets, both concepts are new and not part of RTSJ.

**Safelets** The logic of an SCJ program is implemented in terms of missions, as a single mission or as a sequence of missions. As the entry point to an application, SCJ uses safelets, a concept very similar to that of midlets in J2ME. This is different from RTSJ, which uses an entry method, main, as do standard Java applications.

The Safelet interface defines two methods, the getLevel method, which returns the current level of the application, and the getSequencer method, which returns an implementation of the abstract MissionSequencer class.

The mission sequencer will start, shutdown and switch between missions, and is itself a BoundAsyncEventHandler. This, among other things, means the initial allocation context can be non-heap memory; heap-memory would be used when executing the main method.

**Missions** The mission concept is introduced as a balance between flexibility and restrictions in order to provide limited startup, shutdown, and mission restart. In SCJ, a mission is simply a container for handlers.

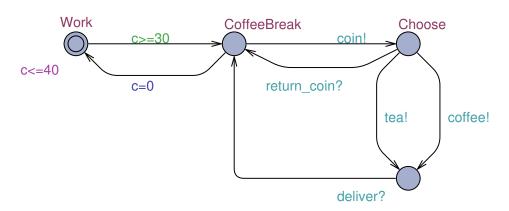

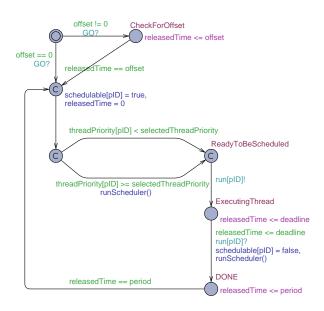

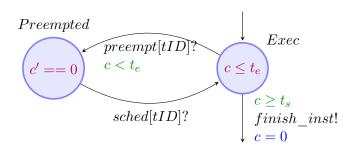

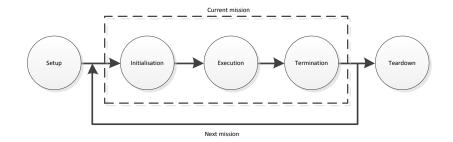

During during the life of a mission it enters different modes, as depicted in Figure 2.9.

Figure 2.9: SCJ mission modes [104, p. 30]

Missions start out in an initialisation mode, where object allocation is allowed in the immortal memory and the mission memory. Objects created in mission memory will be deallocated when the mission ends, upon exiting the mission. After initialization mode, missions move to mission mode, this is the actual system operation mode where they will spend most their time. In this mode no allocation in immortal memory or mission memory is allowed. From this mode, mission can be shut down. At this point, it is uncertain if there is a shutdown mode to do cleanup, however, it is possible to restart the mission and reinitialise the mission [104, p. 9][103, p. 10].

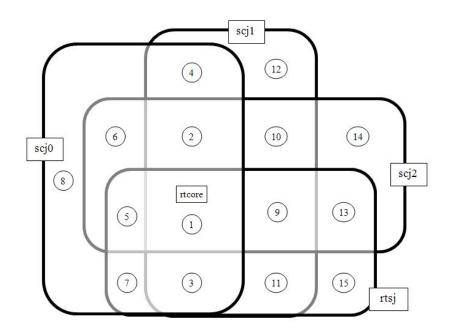

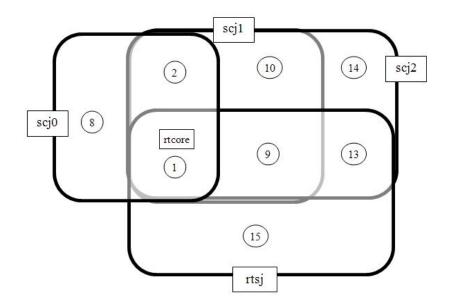

These complexity levels are nested with concurrent missions allowed SCJ level 2, the highest most liberal level, and a single thread of execution at level 0, being the lowest most restrictive level.

Execution during a mission is performed by schedulable objects as defined in the RTSJ, see Section 2.3.1. Schedulable objects have associated private memories that are not shared with other schedulable objects. The number of schedulable objects running concurrently and of which type (aperiodic, periodic, no heap real-time threads) are allowed, is decided by the SCJ compliance level. These levels are described as:

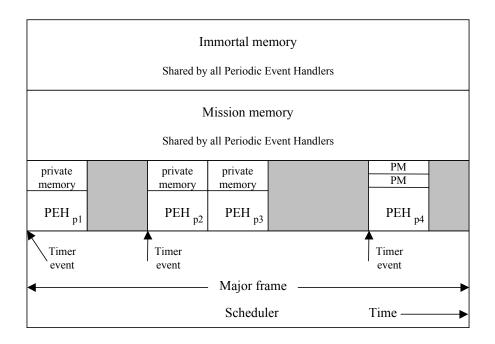

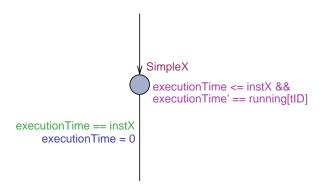

SCJ level 0 The most conservative level is SCJ level 0, and it consists of only one single thread of execution. This results in a cyclic scheduling model as described in Section 2.4.1; this model is shown in Figure 2.10. At this level, a mission consists of only periodic event handlers, and as there is only one thread of execution, no synchronization will be necessary. However, developers are encouraged to use such synchronization mechanisms, as this will ensure correctness if a is executed on a platform complying to level level 1 or higher. The operations wait and notify are not allowed, and only periodic events are allowed, i.e. no threads nor aperiodic events; schedulable objects have private memories used for allocation which are cleared at the end of a run.

Figure 2.10: SCJ level 0 [104, p. 11]

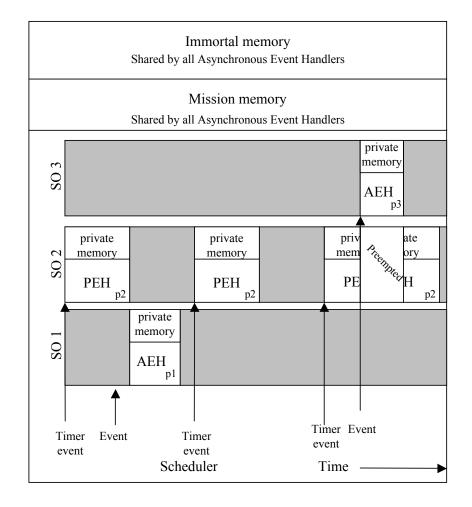

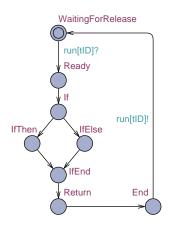

- SCJ level 1 At level 1 schedulable objects are executed concurrently using a fixed priority preemptive scheduling mechanism, as described in Section 2.4.2; this is shown in Figure 2.11. This level allows both aperiodic and periodic tasks, however, threads at this level are disallowed. Schedulable objects have private memories, cleared at the end of their execution, and which cannot be shared; wait and notify are not allowed.

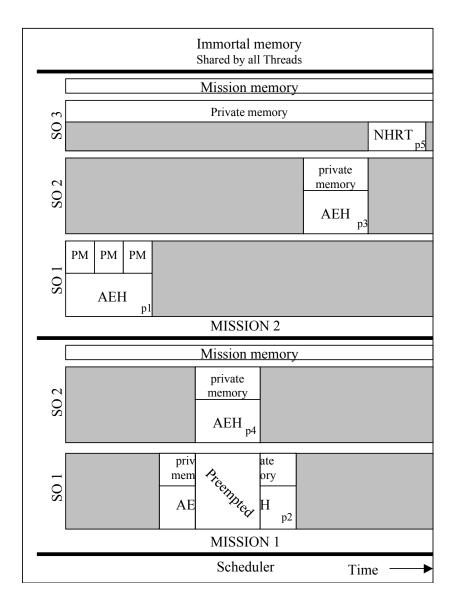

- SCJ level 2 Level 2 is the level allowing the most complexity. It allows most schedulable objects, aperiodic, periodic, and no-heap real-time threads, and multiple nested missions. Each mission has its own mission memory. At this level, the methods wait and notify are available. The execution model provided at level 2 is shown in Figure 2.12.

Figure 2.11: SCJ level 1 [104, p. 13]

SCJ does not contain sporadic event handlers, as this would require additional checks on the arrival of such events and error handling in case they arrive too often. This is deemed too complex to handle for critical applications, even at level 2. SCJ also do only provide immortal, mission and scoped memory; the use of heap is therefore disallowed, and thus there is only the concept of NoHeapRealtimeThread in the specification. Schedulable objects such as RealtimeThread, from RTSJ, and java.lang.Thread are therefore not allowed in SCJ applications. It is important to notice that many of the details of RTSJ are disallowed, such as RealtimeThread and Thread. This is done by using annotations, and by annotating all allowed classes and methods with details on at which level they are allowed.

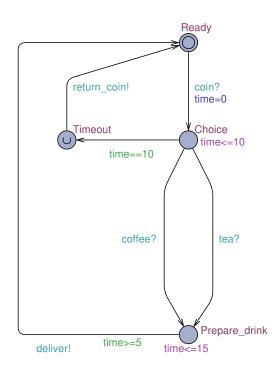

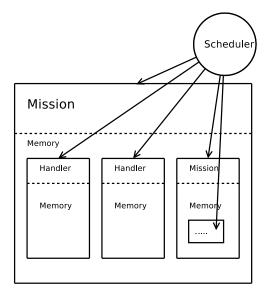

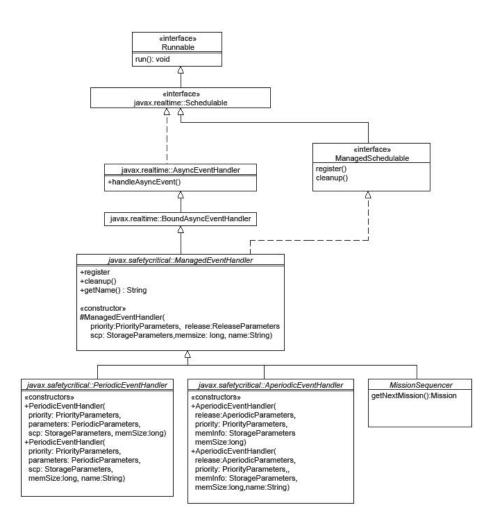

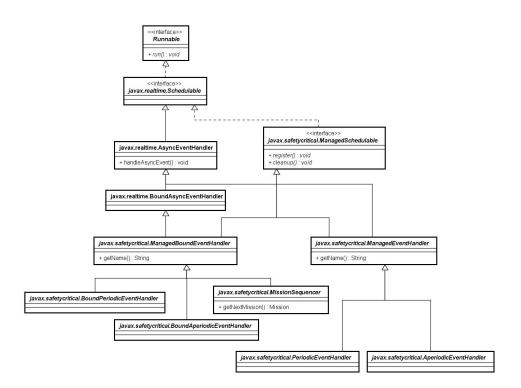

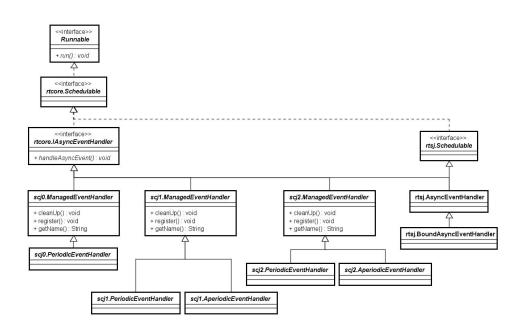

The hierarchy of mission related classes and the schedulable objects allowed in SCJ and their relation to RTSJ is shown in Figure 2.13. The mission

Figure 2.12: SCJ level 2 [104, p. 15]

concept in SCJ is handled by multiple classes:

MissionDescriptor A mission is simply a grouping of schedulable objects and a mission memory, contained by the MissionDescriptor class<sup>5</sup>. This class defines methods such as initialize and cleanup. The ini-

$<sup>^{5}</sup>$ The SCJ draft specification additionally mentions a Mission class, either to be extended by MissionDescriptor, or as a separate class - seems, however, that MissionDescriptor and Mission are at this point the same class

tialize method will prepare handlers and memory in the mission.

- MissionManager The mission manager is responsible for starting and stopping missions, and it defines methods such as start, requestTermination, and the cleanup method performShutdown.

- MissionSequencer The mission sequencer is describing how missions are executed, and in which order. This class is actually an implementation of an asynchronous event handler which will perform the actual mission initializations. The specific implementation of MissionSequencer is defined in an implementation of the Safelet.getSequencer method.

Figure 2.13: The class hierarchy related missions and schedulable objects

#### SCJ Memory Management

Two new memory classes are introduced in SCJ, however, the memory related classes and their rules result in a simpler hierarchy and model. These are PrivateMemory, for use in event handlers and MissionMemory used by missions. These memory classes are based on RTSJLTMemory. Each handler is executed using its own PrivateMemory, which is an instance of ScopedMemory, which cannot be shared with other handlers. Handlers are allowed to create new

nested scopes, however, these scopes cannot be shared with other handlers. The MissionMemory is shared between handlers, however, no allocation in this memory is allowed during the mission phase; all objects are allocated during mission initialisation.

## 2.4 Real-time Scheduling

The concept of a real-time scheduling is to execute the tasks of a real-time system in an order, such that no task misses its deadline. There are different aspects to consider when choosing a scheduling mechanism. Perhaps most important, it must be possible to perform a feasibility analysis of the system to ensure correct behaviour of the system under a given scheduling approach. This is an important field, discussed in Section 2.5. It is also important to consider the type of system to be scheduled, as scheduling approaches differ substantially in terms of overhead and the number of preemptions and scheduling complexity. However, the behaviour of the system is greatly affected by the choice of scheduling algorithm. Some algorithms perform predictably under stress, and some do not, and also the computational overhead must be taken into account.

There are three main categories of real-time scheduling:

- Off-line scheduling

- Fixed-priority scheduling

- Dynamic scheduling

#### 2.4.1 Off-line Scheduling

Off-line scheduling is an approach to scheduling where a static schedule, i.e. the interleaving of task invocations, of the system is designed such that no deadline is missed [17, 45], and a single program, called the cyclic executive, is constructed.

The full static schedule is actually repeating a finite schedule of the tasks to be executed, since the full schedule is likely to be infinite. The schedule is divided into a major cycle which is repeated an infinite number of times. The major cycle determines the actions to be performed during a fixed period of time. The length of this major cycle is the least common multiple of the periods of all tasks in the system, as this is the time from where the past execution will be repeated forever.

This major cycle is further divided into smaller minor schedules of the code to perform the actions of the tasks, called the minor cycle. The size of a minor cycle should be a common divisor for all the periods in order to accommodate all task releases.

Advantages of the cyclic executive approach include:

- The proof of schedulability is done by constructing the cyclic executive and thus no other schedulability tests are needed.

- A low overhead, as there is no need for preemption and no need for ensuring integrity using for example mutexes, as only one thread is running the whole program.

Disadvantages include:

- This approach is not very suited for systems containing tasks of aperiodic nature, as room in multiple minor cycles must be allocated to handle these, which may lead to a substantial amount of idle CPU time in the system.

- The construction of a cyclic executive with larger tasks can be somewhat complicated, as any sizable tasks will have to be split up to fit into the minor cycles.

#### 2.4.2 Fixed Priority Scheduling

Fixed priority preemptive scheduling is a more flexible approach when compared to that of cyclic executives. In this approach, tasks are assigned an offline calculated fixed priority, which it keeps throughout the lifetime of the program.

This approach has an advantage when applied to more dynamic systems where tasks have very different execution times, as there is no need to split up tasks to fit into different minor cycles, as in the cyclic executive. The application will itself also be more flexible, and minor changes in requirements will not affect the implementation as much as in the statically defined cycle; for the interested reader, an in depth comparison of the cyclic executive and priority scheduling is presented in [102].

Priorities are usually assigned according to task deadlines, where shorter deadlines equal higher priorities; this is called Deadline Monotonic Scheduling(DMS) [95], which is a successor to the earlier more restrictive approach of basing priorities on task periods, known as Rate Monotonic Scheduling(RMS) [100].

DMS is optimal among static scheduling approaches given the simple model presented in Section 2.2. The priority based scheduling approach will in many cases also prove helpful in debugging errors caused by missed deadlines, as the task execution patterns are predictable. Deadlines will be missed by tasks with a lower priority, and thus a higher deadline.

#### 2.4.3 Dynamic Scheduling

In the dynamic scheduling approach, priorities are assigned dynamically to the running tasks during the execution of the system according to some importance measure. An example of a dynamic scheduling algorithm is the Earliest Deadline First (EDF) algorithm [100], where the importance is based on the time left before a task meets its deadline. This algorithm has the advantages of being able to achieve higher processor utilization than the fixed priority approach, and being able to handle more dynamic systems than the cyclic executive. This approach is also optimal among all the scheduling approaches on single processor systems, meaning that if a set of tasks characterised by executiontime, deadline and arrival pattern is schedulable by any algorithm, it will be schedulable by EDF.

EDF holds advantageous properties, however, it is a complex algorithm to implement, especially in limited systems. It has a high overhead, and in the case of an overloaded system, it will not behave predictably, as is the case when priorities are assigned statically.

### 2.5 Real-time Systems Analysis

The correctness of a real-time system is heavily dependent on the timely reaction to external events, i.e. it will execute an event handler while the result of the computation is still useful. This means that the system, at any given point, must have enough available resources, computing power or simply time, to handle all occurring events before their respective deadlines. This property is known as schedulability; a system is schedulable if all events are handled before their respective deadlines.

Because real-time systems are often critical systems, and are often embedded systems produced in large quantities, the schedulability property must be proven as a part of the development, before the product is shipped. This proof is achieved through schedulability analysis, which is discussed in the rest of this chapter.

### 2.5.1 Traditional Schedulability Analysis

The established approach to schedulability analysis, known as traditional schedulability analysis, is based on the work by Liu and Layland in 1973 [100]. In the original work, Liu and Layland present a task model based on cost, period, and deadline, in which tasks are scheduled by either the static scheduling algorithm Rate Monotonic Scheduling (RMS), where periods are mapped to priorities, or the dynamic scheduling algorithm EDF, where the currently running tasks with earliest deadline will have highest priority. Additionally, four restrictions are placed on the system limiting expressiveness:

- 1. A system consists of only periodic tasks.

- 2. All tasks in the system has a deadline equal to their period.

- 3. All tasks are independent.

4. All tasks have a constant computation time.

Additionally, some implicit assumptions are made in the original work, and clarified in [15]:

- No process may voluntarily suspend itself.

- All processes are released as soon as they arrive.

- All overheads are ignored; they are assumed to be 0.

For this model the authors present a schedulability analysis based on processor utilisation, the utilisation test. This amounts to calculating the processor utilisation (eq. 2.1), of a given system, and then this is compared to an upper bound on processor utilisation (eq. 2.2). If the processor utilisation is lower than the upper bound, the system in question is guaranteed schedulable, a sufficient, but not necessary test [45], meaning systems passing this test are guaranteed schedulable, and a system failing the test may still be schedulable.

Utilisation for a set of m tasks is given by the following equation:

$$U = \sum_{i=1}^{m} \frac{C_i}{T_i} \tag{2.1}$$

where  $C_i$  is the cost and  $T_i$  is the period of  $task_i$ .

The upper bound for utilisation is dependent only on the number of tasks, and it is given by the following equation:

$$m(2^{\frac{1}{m}}-1)$$

(2.2)

where m is the number of tasks.

| _ |    |             |  |

|---|----|-------------|--|

|   | m  | utilisation |  |

| Γ | 1  | 100%        |  |

|   | 2  | 82.8%       |  |

|   | 3  | 77.9%       |  |

|   | 4  | 75.6%       |  |

|   | 5  | 74.3%       |  |

|   | 10 | 71.7%       |  |

Table 2.1: Processor utilisation bounds

Examples of processor utilisation bounds are given in Table 2.1, and as the number of tasks in the system goes to infinity, the utilisation bound settles at 69.3%:

$$\lim_{m \to \infty} m(2^{\frac{1}{m}} - 1) = 0.693$$

This means the amount of wasted processing time in most systems will be around 30%, which is a relatively high number for limited devices.

#### 2.5.2 Response Time Analysis

A substantial amount of research has been invested in real-time systems analysis since the utilisation based tests were developed. The major disadvantage to using utilisation as a schedulability test is the coarseness of the analysis and the assumptions and restrictions put on the system expressiveness. The response time analysis [14] is a further development of the technique and allows analysis of more expressive systems. More specifically, the basic response time analysis relaxes some important constraints and allows:

- Sporadic tasks, with minimum inter-arrival times.

- Dependencies between tasks through the notion of blocking time for each task, i.e. the time a task can be blocked by a lower priority task through exclusive access to resources.

- Release jitter, the time between release and actual execution of a task.

In the response time analysis, the response time is calculated for each task, and the system is schedulable if the response time for a task is less than its deadline. Sporadic tasks are essentially included as periodic tasks with their period set to the minimum inter-arrival time. The blocking time is calculated based on priority inversion avoidance protocols, priority inheritance or priority ceiling.

We use the following notation:

- T denotes period or minimum inter-arrival time.

- *D* is the deadline relative to the task release.

- *B* is the time a task is blocked by lower priority tasks.

- C is WCET.

- hp(i) is the set of tasks of higher priority than task *i*.

#### Synchronisation Protocols

In a system with interdependent tasks, tasks can experience blocking caused by lower priority tasks holding a shared resource, which is also required by a higher priority task. This blocking time is affecting the response time of the task, and must therefore be bounded.

These analyses assume the use of synchronisation protocols to avoid unbounded priority inversion. The two protocols considered here are the priority inheritance protocol and the priority ceiling protocol [140]. The latter of the two has two slightly different versions, Immediate Priority Ceiling Protocol (IPCP) and Original Priority Ceiling Protocol (OPCP). The priority inheritance protocol only avoids unbounded priority inversion, where the priority ceiling protocol also avoids deadlocks and the worst case blocking for the two ceiling protocols is at the most one critical section.

**Priority Inheritance** In priority inheritance, if a lower priority task is blocking a higher priority task, it will inherit the priority of the blocked task.

After the priority boosted task finishes executing the critical section causing the block, it will be reassigned its original priority. This protocol will prevent unbounded priority inversion, however, it will not prevent deadlock situations.

**Priority Ceiling** The Priority Ceiling Protocol (PCP) ensures freedom from deadlocks, predictably bounds blocking times, and it will result in less context switches than Priority Inheritance Protocol (PIP). To each resource in the system, a priority equal to the maximum priority of all the threads accessing the resource is assigned, and each task has a static priority.

- OPCP then works as follows:

- The priority of a task after locking a resource:

- \* remains, if no higher priority tasks are blocked because of acquired resource,

- \* is raised to the maximum of inherited priority and the static priority, if it is blocking a higher priority task.

- A resource can only be acquired by a task if it has a priority higher than any locked resource not locked by the task itself.

- In IPCP, a task priority is immediately raised to the maximum of the locked resources.

In IPCP, even tasks without critical sections may be blocked, whereas in OPCP, these tasks will only be indirectly blocked by blocked higher priority tasks. Additionally, the difference lies in the number of context switches and hence the number of locking operations, where IPCP will perform less locking operations and cause less switches than OPCP.

### 2.5.3 Analysing Response Time

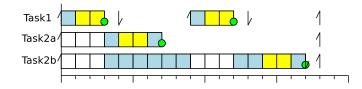

For a set of tasks, indexed i = 1..n, with static priority,  $P_i$ , the response time analysis of  $task_i$ ,  $R_i$  is given by the equation:

$$R_i = C_i + B_i + I_i \tag{2.3}$$

where:

- $C_i$  is the execution time of  $task_i$ .

- $B_i$  is the maximum blocking time of  $task_i$ . This is dependent on the protocol used for priority inversion avoidance.

- The maximum blocking for  $task_i$  using PIP is given by the equation:

$$B_i = \sum_{r \in R} usage(i, r)C_r \tag{2.4}$$

- The maximum blocking time for  $task_i$  using PCP is given by:

$$B_i = \max_{r \in R} usage(i, r)WCET_r \tag{2.5}$$

where R is a set of resources,  $C_r$  is the WCET of the critical sections involving resource r, and usage(i, r) evaluates to 1 if resource r is used by a task with lower priority than  $task_i$  and used by a task with priority higher than or equal to the priority of  $task_i$ ; or 0 otherwise.

•  $I_i$  is the maximum interruption time of  $task_i$  by tasks of higher priority, given by the equation:

$$I_i = \sum_{j \in hp(i)} \left\lceil \frac{R_i}{T_j} \right\rceil C_j \tag{2.6}$$

where hp(i) is the set of tasks of higher priority than task *i*.

This gives the following recursion:

$$R_i^{n+1} = C_i + B_i + \sum_{j \in hp(i)} \left\lceil \frac{R_i^n}{T_j} \right\rceil C_j$$

(2.7)

for which a fix-point solution,  $R_i^{n+1} = R_i^n$  with  $R_i^0 = C_i$ , is guaranteed if the utilisation is less than 1 [14].

### 2.6 Model Checking

Model checking is another interesting approach to program analysis. Models can be built as a part of the real-time system specification, and some tools, such as TIMES [11], provide code synthesis from models, in order to gain some correspondence between the model and the code. Other tools use binary code as input and perform analysis on a model generated directly from this [50], again to ensure tight correspondence between the analysis and the actual program. Similarly, functional correctness is checked in tools such as Bandera [49] by generating models from the code. Java pathfinder [40] is a similar tool which works by symbolically executing the byte-code. Model checking is also an interesting method for solving the schedulability problem [90, 59, 60], which is more flexible than traditional approaches, and it is able to take into account more of the problem specific details, such as the environment and task interaction. The general approach taken is to build an abstract specification of the system on which the schedulability property is verified, it is then implemented after a positive verdict, or, by building an abstract model of an existing implementation to verify that it is actually correct with regards to schedulability.

### 2.6.1 Timed Automata

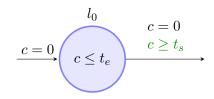

In this section an overview of Timed Automata is presented, based on [16, 9]. A Timed Automaton is a finite directed graph, a set of clocks, and a set of constraints on these clocks. The nodes of the graph we call locations and the edges are called switches.

For a set of clocks C, a clock valuation v, is a mapping  $C \to \mathbb{R}_+$ , assigning a nonnegative real value to each clock in C; v[X := 0] denotes the valuation v where zero is assigned to the clocks in  $X \subseteq C$ . For  $d \in \mathbb{R}_+$ , v + d denotes the valuation where each clock  $c \in C$  maps to v(c) + d.

Locations and switches each have an associated set of clock constraint, called invariant for locations and guard for switches.

**Definition 1** (Clock constraint). Let x be an integer and  $c \in C$  be a clock, then a clock constraint is defined by the grammar:

$$\phi := c \le x | c < x | c = x | c > x | c \ge x | \phi \land \phi$$

Time elapses in locations, and only while the invariant holds, while switches are instantaneous. Any switch can reset a set of clocks.

**Definition 2** (Timed Automata). [9] A timed automaton is a tuple  $\langle L, l_0, F, \Sigma, C, E, I \rangle$  where:

- *L* is a finite set of locations.

- $l_0 \in L$  is the initial location.

- $F \subseteq L$  is a set of accept locations.

- $\Sigma$  is a finite set of actions.

- C is a finite set of clocks.

- $E \subseteq L \times \Phi(C) \times \Sigma \times 2^C \times L$  is the set of switches, where  $\langle l, g, a, r, l' \rangle \in E$  is the switch between locations, from l to l', guarded by the constraint g, a is an action, and r is the set of clocks to be reset.

- $I: L \to \Phi(C)$  assigns a set of invariants to each location.

We use  $l \xrightarrow{g,a,r} l'$  to denote  $\langle l, g, a, r, l' \rangle \in E$ .

**Definition 3** (Semantics of Timed Automata). A state in a timed automata is a pair  $(l, v) \in L \times \mathbb{R}^C$  where  $\Phi(l)$  holds for the clock valuation v of C. The initial state is  $(l_0, v)$  where  $\forall c \in C : v(c) = 0$ , and a transition is either a delay transition or a location transition:

- Delay transition: for a state (l, v) and a delay d,  $(l, v) \xrightarrow{d} (l, v + d)$ , if  $\forall d' : 0 \leq d' \leq d, v + d' \in I(l)$ .

- Location transition:  $(l, v) \xrightarrow{a} (l', v)$ , if there exists  $l \xrightarrow{g,a,r} l' s.t.v \in g, v' = [r := 0], v' \vdash I(l')$

### 2.6.2 Timed Automata in Practice

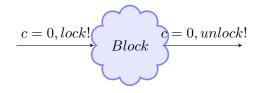

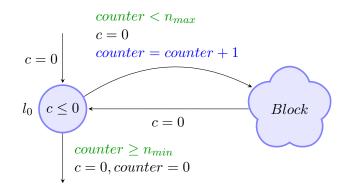

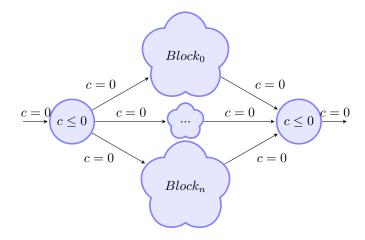

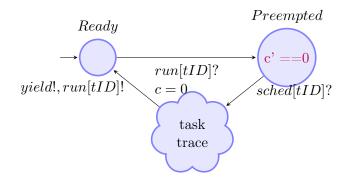

UPPAAL is a tool for modeling and verification of real-time systems using a variation of timed automata as the underlying formal foundation. A system is expressed as a network of timed automata along with variable, function, and other declarations, and requirements are expressed as Timed Computational Tree Logic (TCTL) formulae [16]. This section gives a short introduction to the modeling language of UPPAAL, based on [24].

UPPAAL works on an extended definition of timed automata. This extended definition includes bounded variables along with an imperative C inspired language for manipulating these variables. Elements are also added to make the modelling of commonly used concepts easier, such as urgent locations. Additionally elements from the imperative language can be used in guards, for example, thus increasing flexibility. Clocks are defined as usual, however, the action concept varies slightly, as this is used for synchronization.

An automaton in UPPAAL is then defined as in Definition 4 inspired by [158, 24].

**Definition 4** (Uppaal Timed Automata). A timed automaton in UPPAAL is a tuple  $\langle L, l_0, \Sigma, V, F, C, E, I \rangle$  where

- *L* is a finite set of locations.

- $l_0 \in L$  is the initial location.

- $\Sigma$  is a finite set of actions, co-actions, and the internal action  $\tau$ .

- V is a finite set of variables.

- F is a finite set of function declarations.

- C is a finite set of clocks.

- $E \subseteq L \times \Phi(C) \times \Psi(V, F) \times \Sigma \times 2^C \times 2^V \times L$  is the set of switches, where:

$-\langle l, g, a, r, u, l' \rangle$  is the switch from location l to location l' where:

- \* g is a guard:  $g = (g^c, g^v) \in \Phi(C) \times \Psi(V, F)$ , a conjunction of clock-constraints,  $g^c$ , and variable-constraints,  $g^v$ .

- \* a is an action.

- \* r is the set of clocks to be reset.

- \* u is the set of variable updates.

- $I: L \to \Phi(C) \times \Psi(V, F)$  assigns a set of invariants to each location.

Where the set of clock constraints  $\Phi(C)$  is defined as in Definition 1 (except x is now an expression evaluating to an integer), and  $\Psi(V)$  is defined by:

$$\psi := i \oplus k \mid \psi \land \psi \mid \psi \lor \psi$$

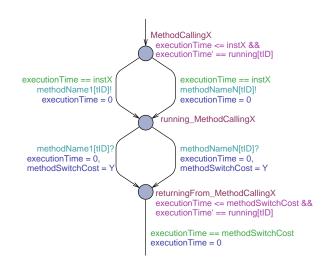

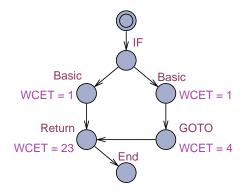

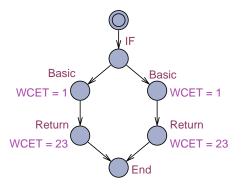

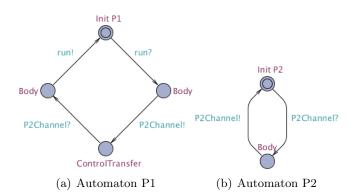

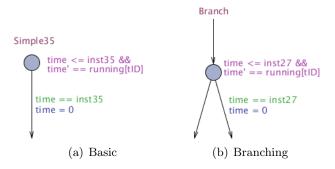

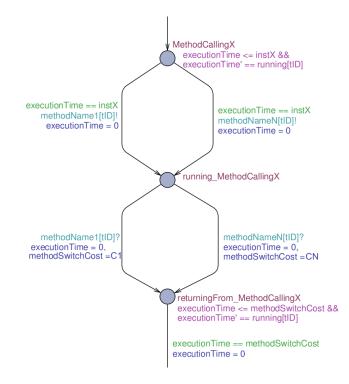

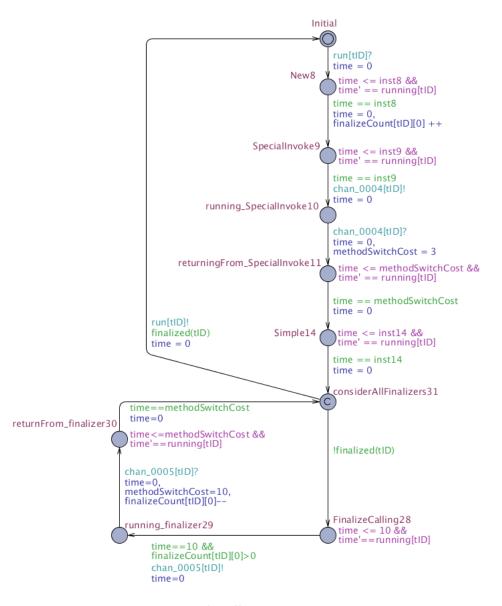

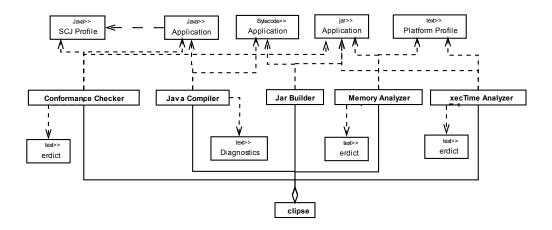

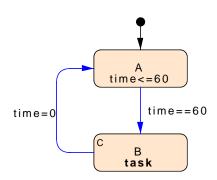

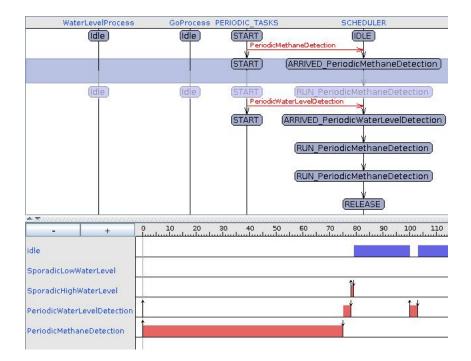

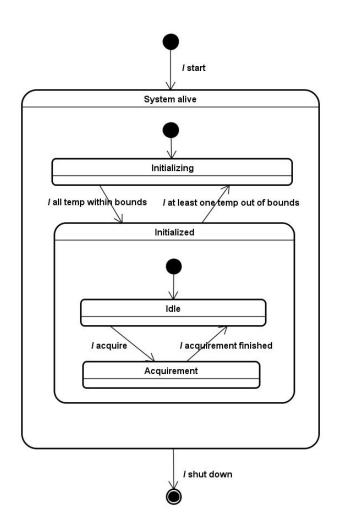

where  $\oplus \in \{<, \leq, =, \geq, >\}$  and i, k both evaluate to integers.