**Aalborg Universitet**

### A Novel Single Pass Authenticated Encryption Stream Cipher for Software Defined Radios

Khajuria, Samant

Publication date: 2012

Document Version Early version, also known as pre-print

Link to publication from Aalborg University

Citation for published version (APA): Khajuria, S. (2012). A Novel Single Pass Authenticated Encryption Stream Cipher for Software Defined Radios.

### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

? Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

? You may not further distribute the material or use it for any profit-making activity or commercial gain

? You may freely distribute the URL identifying the publication in the public portal ?

Take down policy If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

## A Novel Single Pass Authenticated Encryption Stream Cipher for Software Defined Radios

A DISSERTATION SUBBMITTED TO THE DEPARTMENT OF ELECRONIC SYSTEMS OF AALBORG UNIVERSITY IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

> Samant Khajuria Center for Wireless Systems and Applications Center for TeleInFrastruktur – Copenhagen Dept. of Electronic Systems AAU

### Supervisor:

Professor Ramjee Prasad, CTIF, Aalborg University, Denmark Professor Birger Andersen, CWSA-CTIF, Copenhagen University College of Engineering, Denmark

The examination committee:

Moderator:

Date of defense:

ISSN: \*\*\*\_\*\*\* ISBN: \*\*\_\*\*\*\*\_\*\*\*\_\*

### Copyright © 2012 by Samant Khajuria

All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without written permission from the author.

## Abstract

With the rapid growth of new wireless communication standards, a solution that is able to provide a seamless shift between existing wireless protocols and high flexibility as well as capacity is crucial. Software Defined Radio (SDR) technology offers this flexibility. It gives the possibility of adapting the radio to users' preferences and the operating environment and supporting multiple standards without requiring separate hardware for each standard. In order to avail this enabling technology that is applicable across a wide range of areas within the wireless infrastructure, these radios have to propose cryptographic services such as confidentiality, integrity and authentication. Therefore, integration of security services into SDR devices is essential.

Authenticated Encryption schemes donate the class of cryptographic algorithms that are designed for protecting both message confidentiality and its authenticity. Traditionally, authenticated encryption was achieved by using two independent algorithms for encryption and authentication. For past few years, new modes of operation of block cipher have been developed that allow us to use one algorithm for encryption as well as authentication. This makes authenticated encryption very attractive for low-cost low-power hardware implementations, as it allows for the substantial decrease in the circuit area and power consumed compared to the traditional schemes.

In this thesis, an authenticated encryption scheme is proposed with the focus of achieving high throughput and low overhead for SDRs. The thesis is divided into two research topics. One topic is the design of a 1-pass authenticated encryption scheme that can accomplish both message secrecy and authenticity in a single cryptographic primitive. The other topic is the implementation of this design on re-configurable hardware in SDRs by closely observing the trade-off between area/throughput performance parameters.

For test and performance evaluation the design has been implemented in Xilinx Spartan -3 sxc3s700an FPGA. The resulting implementation consumes moderate number of slices on FPGA and achieves throughput in the range of 0.8 Gbps which can be suitably used for SDR applications. Comparing with traditional two pass approaches, the presented design demonstrates high throughput and small area to performance ratio.

## Dansk Resume

Med den hurtige vækst i nye trådløse kommunikationsstandarder, er en løsning, der er i stand til at levere et problemfrit skifte mellem eksisterende trådløse protokoller og høj fleksibilitet samt kapacitet afgørende. Software Defined Radio (SDR) teknologi tilbyder denne fleksibilitet. Det giver mulighed for at tilpasse radioen til brugernes præferencer og driftsmiljøet og understøtte flere standarder uden at kræve separat hardware for hver standard. For at kunne benytte denne teknologi, der kan anvendes på tværs af en lang række områder indenfor trådløse infrastruktur, er disse radioer nødt til at tilbyde kryptografiske tjenester såsom fortrolighed, integritet og autentificering. Derfor er integration af sikkerhedstjenester i SDR-enheder af afgørende betydning.

Autentificeret krypteringsmetoder tilhører klassen af kryptografiske algoritmer, der er designet til at beskytte både besked fortrolighed og dens ægthed (autensitet). Traditionelt blev autentificeret kryptering opnået ved hjælp af to uafhængige algoritmer til kryptering og autentificering. De sidste få år er nye former for blokalgoritmer blevet udviklet, som giver os mulighed for at bruge samme algoritme til kryptering samt autentificering. Dette gør autentificeret kryptering meget attraktivt for billige energibesparende hardware implementeringer, da det giver mulighed for betydelig reduktion af kredsløbets omfang og strømforbruget sammenlignet med traditionelle metoder.

I denne afhandling er foreslået en autentificeret krypteringsmetode med fokus på at opnå høj kapacitet og lavt overhead for SDR. Afhandlingen er opdelt i to forskningsområder. Det ene er udformningen af en 1-passage autentificeret krypteringsmetode, der kan benyttes til både hemmeligholdelse og autenticitet vha. et enkelt kryptografisk primitiv. Det andet område er implementering af dette design på rekonfigurérbar hardware i SDR ved nøje at observere trade-off mellem kredsløbets omfang og kapacitets præstationsparametre.

For test og evaluering er designet blevet implementeret i Xilinx Spartan - 3 sxc3s700an FPGA. Den resulterende implementering forbruger moderat antal slices på FPGA og opnår kapacitet i området ca. 0,8 Gbps, som kan være passende for SDR applikationer. I sammenligning med traditionelle to passage metoder demonstrerer det præsenterede design høj kapacitet og lille kredsløbsomfang. som ydelsesforhold.

## Acknowledgements

I would like to take the opportunity to thank the people who supported and accompanied me during my PhD studies.

First and foremost I would like to thank my supervisors Prof. Ramjee Prasad and Prof. Birger Andersen for all the support and feedback, without which I would not have been able to complete my research work and write my thesis. I would also like to thank Prof. Rajarathnam Chandramouli and Goce Jakimoski for giving me the opportunity to work under their guidance in which they gave me their expertise and timely advices during my research at Stevens Institute of Technology.

I would like to thank Center for Wireless Systems and Applications (CWSA) for sponsoring first year of my research. Next, I would like to thank my colleagues, the current once and the ones that have already gone from CWSA. I have always appreciated their precious feedback and long discussions with them about my research. I would also like to thank John Kryger Sørensen for his support and guidance.

I would also like to thank Susanne Nørrevang and Inga Hauge for their help during my travels.

Last, I would like to thank my friends and family for all their unconditionally support during my PhD

Thank you all

## Table of Contents

| List of Figures  | xii |

|------------------|-----|

| List of Tables   | xiv |

| List of Acronyms | XV  |

| 1 | Introduction        |                                                 | 1  |

|---|---------------------|-------------------------------------------------|----|

|   | 1.1 Software        | Defined Radio                                   | 1  |

|   | 1.1.1               | Cognitive Radio                                 | 3  |

|   | 1.1.2               | Field Programmable Gate Arrays / System on Chip | 5  |

|   | <b>1.2</b> Need for | Security                                        | 5  |

|   | 1.2.1               | FPGAs for Cryptographic Application             | 6  |

|   | 1.2.2               | Attacks on FPGA                                 | 8  |

|   | 1.3 Confiden        | tiality and Authenticity                        | 10 |

|   | 1.4 Motivatio       | n                                               | 11 |

|   | 1.5 Problem I       | Definition                                      | 12 |

|   | 1.6 Limitation      | ns                                              |    |

|   | 1.7 Contribut       | ion                                             | 13 |

|   | 1.8 Organizat       | ion                                             |    |

|   | References          |                                                 |    |

## Part I – Algorithm Analysis & Development

| 2 | Cryptography  |                                  | 21 |

|---|---------------|----------------------------------|----|

|   | 2.1 Symmetri  | c Encryption                     |    |

|   | -             | bhers                            |    |

|   | 2.2.1         | Advanced Encryption Standard     |    |

|   | 2.3 Stream Ci | phers                            |    |

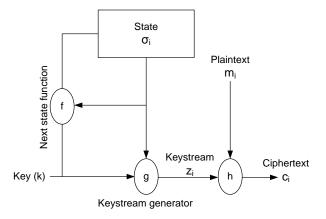

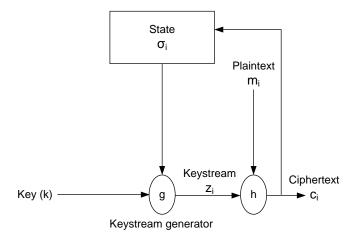

|   | 2.3.1         | Synchronous Stream Cipher        |    |

|   | 2.3.2         | Self-Synchronizing Stream Cipher |    |

| 2.4 Authentication     |                                               | 34 |  |

|------------------------|-----------------------------------------------|----|--|

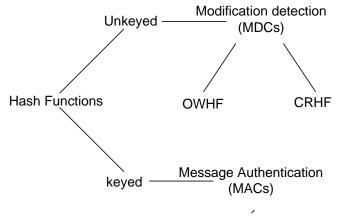

| 2.4.1                  | Cryptographic Hash Functions                  | 35 |  |

| 2.4.2                  | Message Authentication Codes (MAC)            |    |  |

| 2.4.3                  | Dedicated Hash functions                      |    |  |

| 2.4.4                  | Secure Hash Algorithm                         | 40 |  |

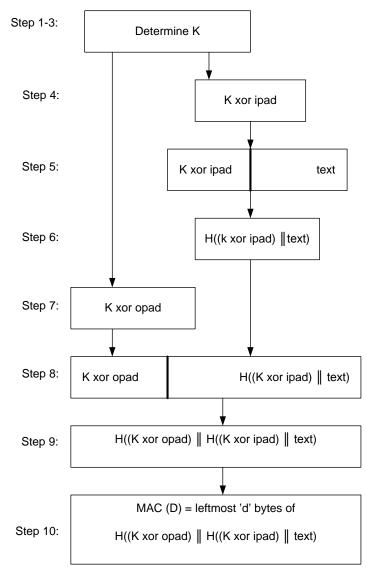

| 2.4.5                  | Keyed-Hash Message Authentication Code (HMAC) | 42 |  |

| 2.4.6                  | CBC-MAC                                       | 44 |  |

| <b>2.5</b> Conclusions |                                               | 46 |  |

| References             | References                                    |    |  |

| 3 | Authenticated E                      | ncryption51                                |

|---|--------------------------------------|--------------------------------------------|

|   | 31 Conoria (                         | Composition 52                             |

|   | <b>3.1</b> Generic C                 | Composition                                |

|   | 3.1.1                                | MAC – then – Encrypt                       |

|   | 3.1.2                                | Encrypt – then – MAC                       |

|   |                                      | Combined mode                              |

|   | <b>3.2</b> 1 w0 Pass<br><b>3.2.1</b> |                                            |

|   | 3.2.2                                | EAX Mode                                   |

|   | 01212                                | ss Combined Mode                           |

|   | U                                    |                                            |

|   | 3.3.2                                | IAPM                                       |

|   | 3.3.3                                |                                            |

|   |                                      | OCB                                        |

|   | 3.4 AE Stream 3.4.1                  | m Ciphers                                  |

|   |                                      | Helix                                      |

|   | 3.4.2                                | Sober-128                                  |

|   |                                      | An Authenticated encryption Stream Cipher  |

|   |                                      | LEX Stream Cipher                          |

|   |                                      | ASC-1 Specification                        |

|   | -                                    | Considerations                             |

|   | 3.6.1                                | 5                                          |

|   |                                      | ries                                       |

|   | 3.7.1                                |                                            |

|   | •                                    | n ASC-1                                    |

|   | 3.8.1                                | The Information-Theoretic Case             |

|   | 3.8.2                                | Computational Security Analysis of ASC-185 |

|   | 3.9 Conclusio                        | ns                                         |

|   | References                           |                                            |

## Part II – Implementation & Results

| 4 | Field programn        | nable Gate Arrays (FPGAs)                         | 95  |

|---|-----------------------|---------------------------------------------------|-----|

|   | 4.1 FPGA Ar           | chitecture                                        | 96  |

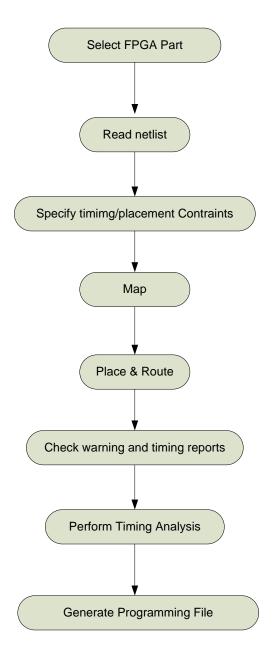

|   | 4.1.1                 | FPGA Implementation Flow                          | 97  |

|   | 4.1.2                 | Xilinx Spartan 3AN                                |     |

|   | <b>4.2</b> Role of Fl | PGAs in SDR                                       |     |

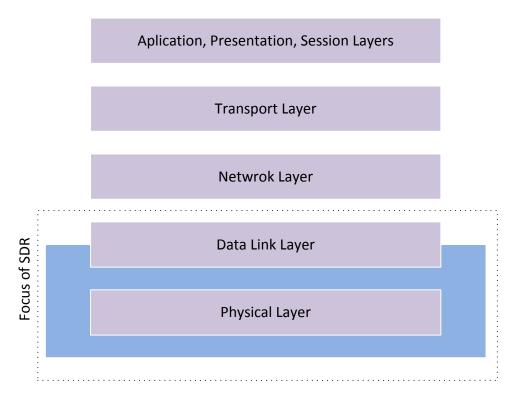

|   | 4.2.1                 | Cross Layer Architecture of SDR                   | 101 |

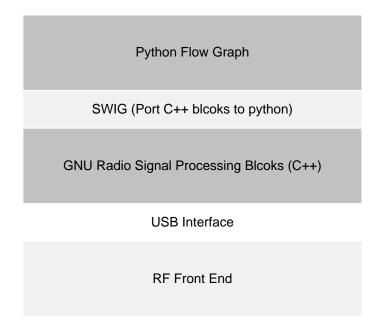

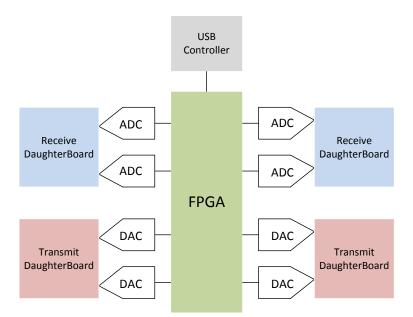

|   | 4.2.2                 | GNU Radio and USRP                                |     |

|   | 4.3 Generic S         | DR Structure                                      | 106 |

|   | 4.3.1                 | SOC in SDR                                        |     |

|   | 4.3.2                 | Secure Communication                              | 109 |

|   | 4.4 Implemen          | tation of ASC-1                                   | 110 |

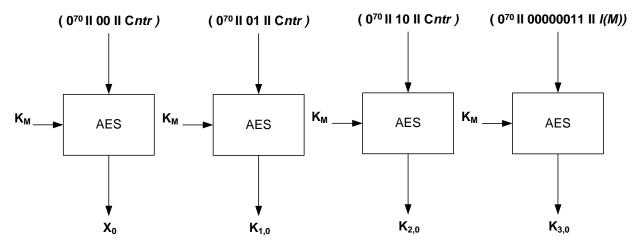

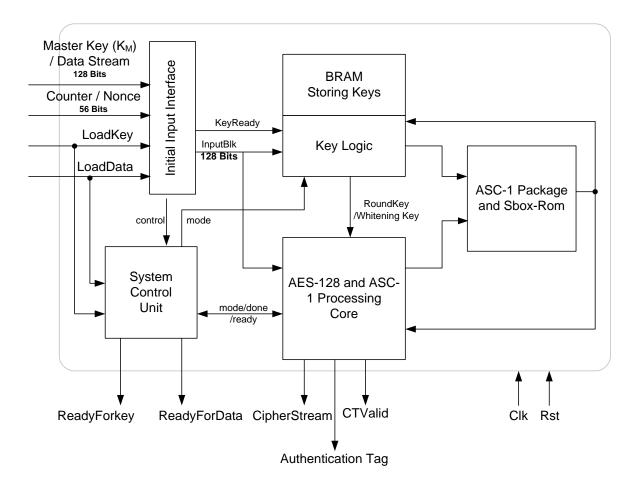

|   | 4.4.1                 | Initial phase Generation                          | 111 |

|   | 4.4.2                 | Encryption Process                                | 111 |

|   | 4.4.3                 | Proposed ASC-1 Architecture                       | 113 |

|   | 4.5 Conclusio         | ons                                               |     |

|   | References            |                                                   | 119 |

|   | 5.1 Paramete          | ers of Hardware Implementation                    | 122 |

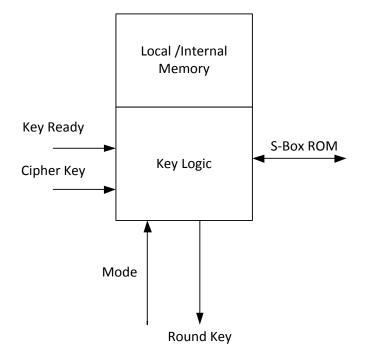

|   |                       | bher Modes of Operation                           |     |

|   | -                     | Hardware Architecture for Feedback cipher modes   |     |

|   | 5.2.2                 | Hardware Architecture in Non-feedback cipher mode |     |

|   | <b>5.3</b> Performan  | nce of ASC-1 Crypto core                          |     |

|   |                       | lay                                               |     |

|   |                       | Length on Effective Throughput                    |     |

|   | <b>5.6</b> LTE and `  | WiMAX                                             |     |

|   | 5.6.1                 | OFDM in LTE and WiMAX                             | 138 |

|   | 5.6.2                 | Confidentiality and Integrity in LTE and WiMAX    |     |

|   | 5.7 Conclusion        | ons                                               | 142 |

|   | References            |                                                   | 143 |

| 6 | Summary & Fut         | ture Scope                                        | 147 |

|   |                       |                                                   |     |

|   | 6.1 Contribut         | ion of This Thesis                                | 147 |

| References | 150 |

|------------|-----|

|------------|-----|

| Appendix I - Test Vectors                      |     |

|------------------------------------------------|-----|

| A.1 ASC-1 Preprocessing/ Initial Phase         | 153 |

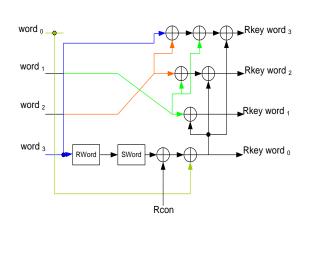

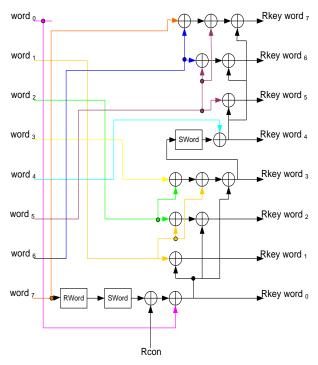

| A.2 Key Expansion                              | 154 |

| A.3 ASC-1 Encryption                           |     |

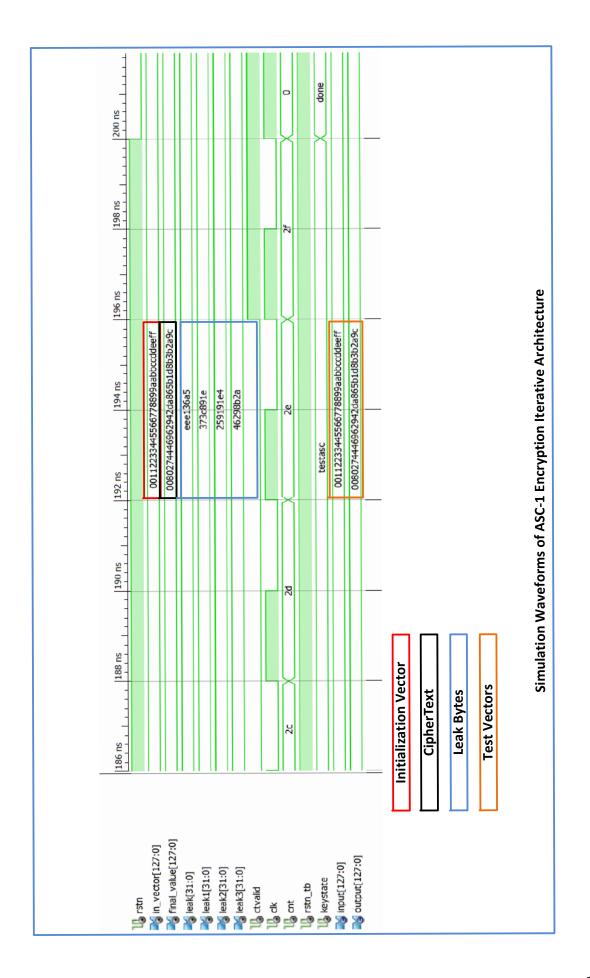

| Appendix II - Xilinx Sample Code and Waveforms | 163 |

| B.1 Advanced Encryption Standard (AES) – 128   |     |

| B.2 Key Expansion                              | 169 |

| B.3 ASC-1 Encryption                           |     |

## List of Figures

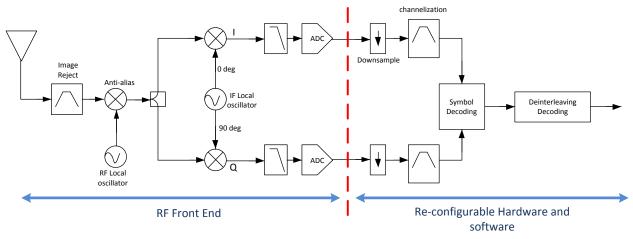

| 1.1 Generic SDR transceiver                                                              | 2  |

|------------------------------------------------------------------------------------------|----|

| 1.2 Thesis Outline                                                                       | 15 |

| 2.1 Electronic Codebook                                                                  | 25 |

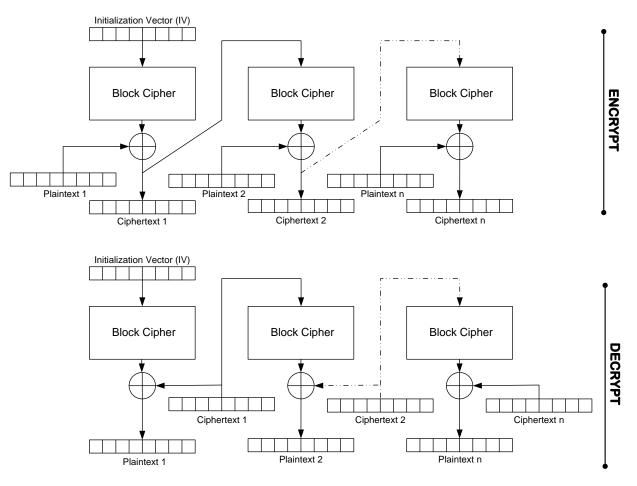

| 2.2 Cipher Block Channing                                                                |    |

| 2.3 Cipher Feedback                                                                      |    |

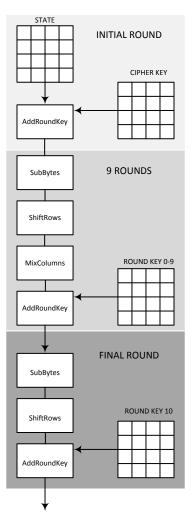

| 2.4 Output Feedback                                                                      |    |

| -                                                                                        |    |

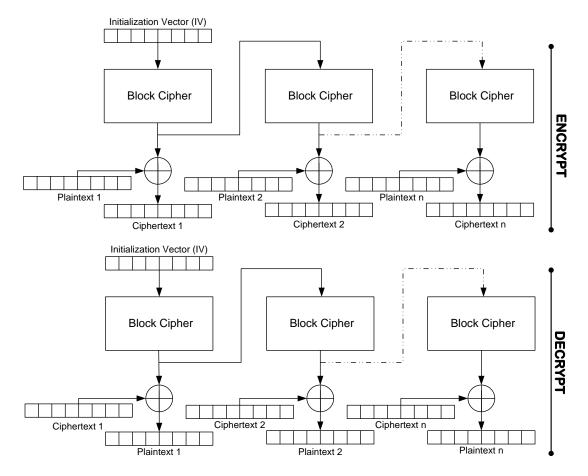

| 2.5128 bits Advanced Encryption Standard                                                 |    |

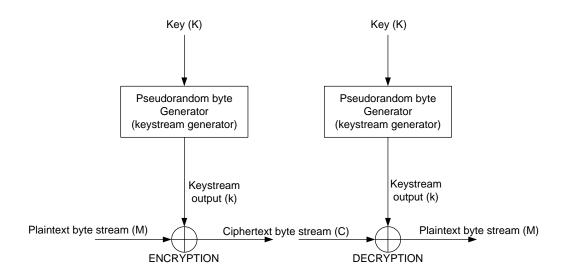

| 2.6 Stream Cipher                                                                        |    |

| 2.7 Synchronous Stream Cipher                                                            |    |

| 2.8 Self-Synchronizing Stream Cipher                                                     |    |

| 2.9 Classification of cryptographic hash functions                                       |    |

| 2.10 HMAC Construction                                                                   |    |

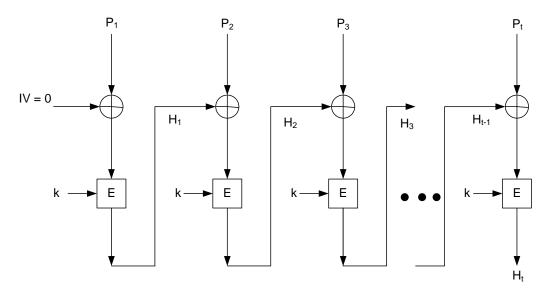

| 2.11 CBC-based MAC algorithm                                                             | 44 |

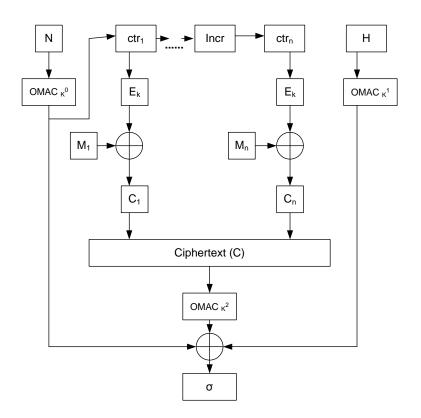

| 3.1 EAX mode                                                                             | 50 |

| 3.2 Integrity Aware Parallelizable Mode scheme                                           |    |

| •••                                                                                      |    |

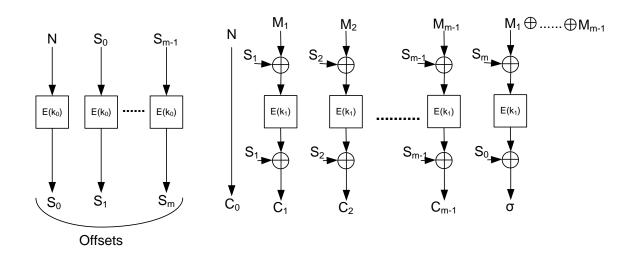

| 3.3 Extended Cipher Mode Chaining Encryption mode scheme                                 |    |

| 3.4 Offset CodeBook mode scheme                                                          |    |

| 3.5 LEX Stream Cipher                                                                    |    |

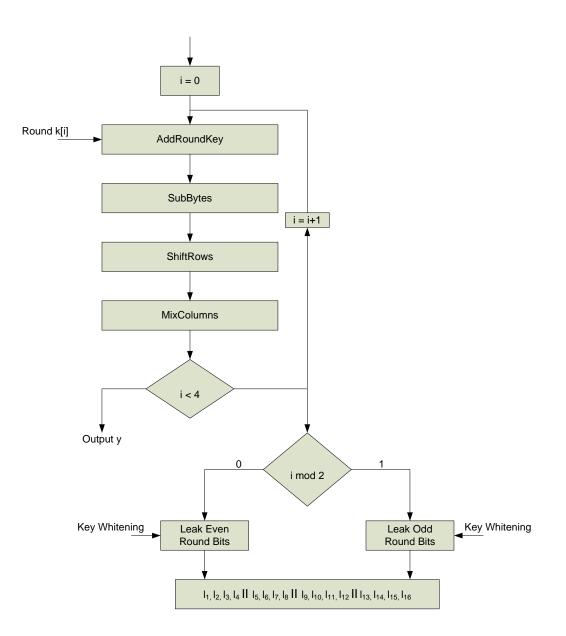

| 3.6 Leak Positions in odd and even rounds                                                |    |

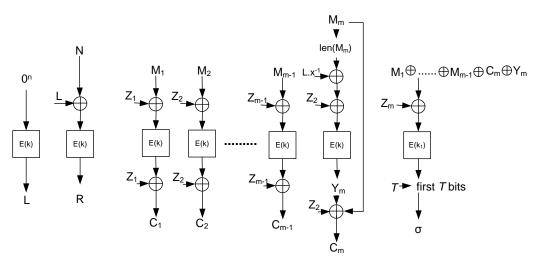

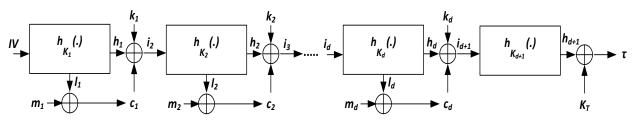

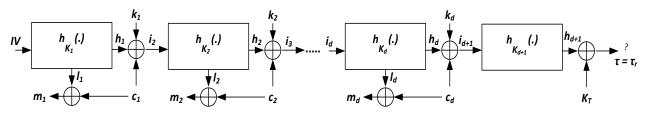

| 3.7 The Encryption and decryption algorithms of ASC-1                                    |    |

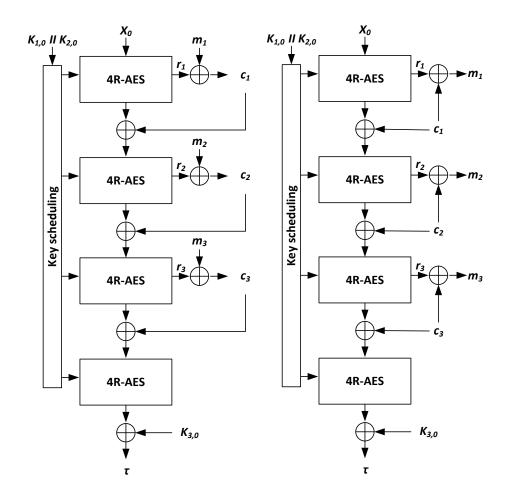

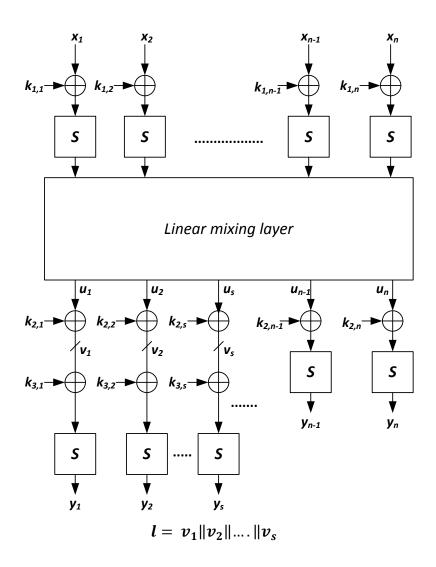

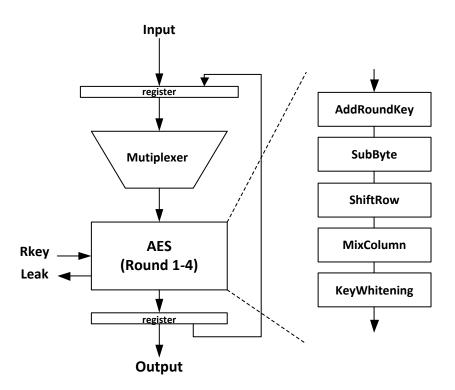

| 3.8 The 4R-AES transformation                                                            |    |

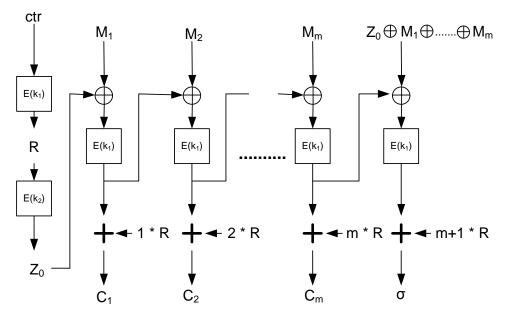

| 3.9 An authenticated encryption scheme construction based on a LAXU hash function family |    |

| CFB-like mode                                                                            |    |

| 3.10 A two round SPN structure with a leak                                               |    |

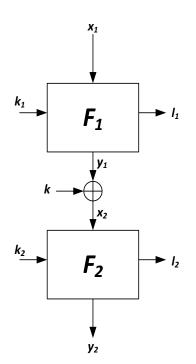

| 3.11 A composition of a transformation                                                   | 82 |

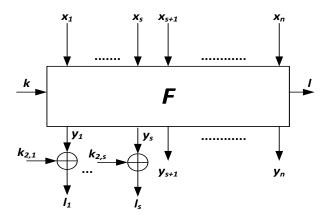

| 3.12 The first s output of a non-linear function <i>F</i>                                | 83 |

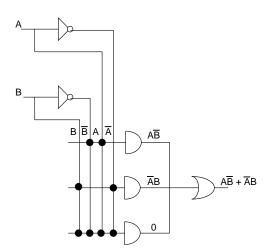

| 4.1 Programmable-Logic-Arrays | 9 | <b>)</b> : | 5 |

|-------------------------------|---|------------|---|

|-------------------------------|---|------------|---|

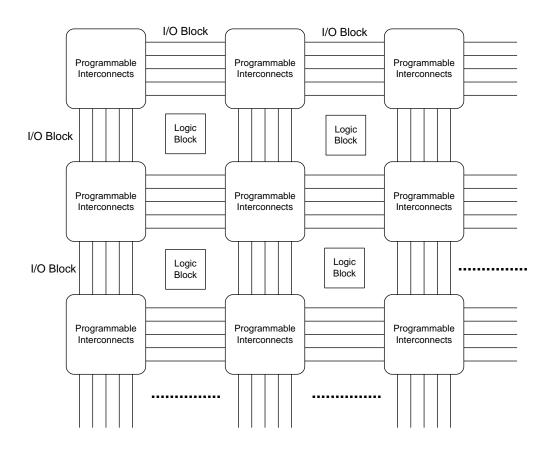

| 4.2 Field Programmable Gate Array                   | 96  |

|-----------------------------------------------------|-----|

| 4.3Xilinx implementation Flow                       |     |

| 4.4 Xilinx Spartan 3AN                              |     |

| 4.5 Software Defined Radio                          | 100 |

| 4.6 SDR Layers in OSI                               |     |

| 4.7 Block diagram of GNU Radio Components           | 104 |

| 4.8 Block Diagram of the USRP                       | 105 |

| 4.9 Practical SDR receiver                          |     |

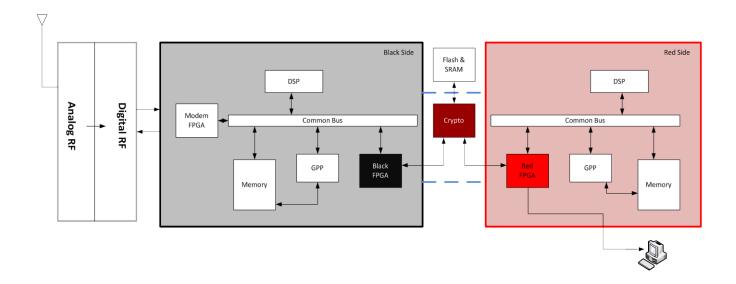

| 4.10 SCA Structure, showing the Red and Black FPGAs | 109 |

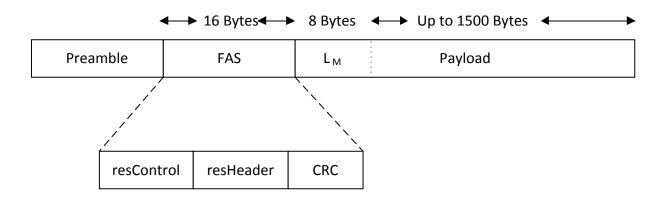

| 4.11 Frame Structure                                | 110 |

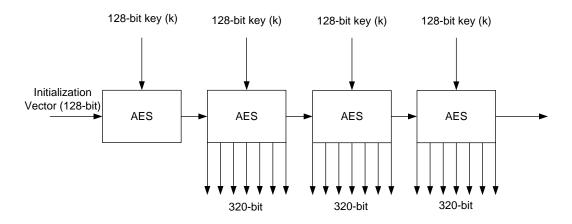

| 4.12 Initialization vector and Key Generation       |     |

| 4.13 ASC-1 Flowchart                                |     |

| 4.14 Block diagram of ASC-1                         |     |

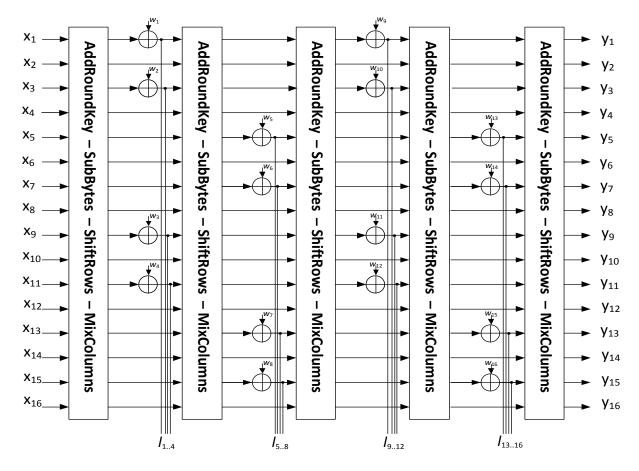

| 4.15 Fully parallel pipelined structure             |     |

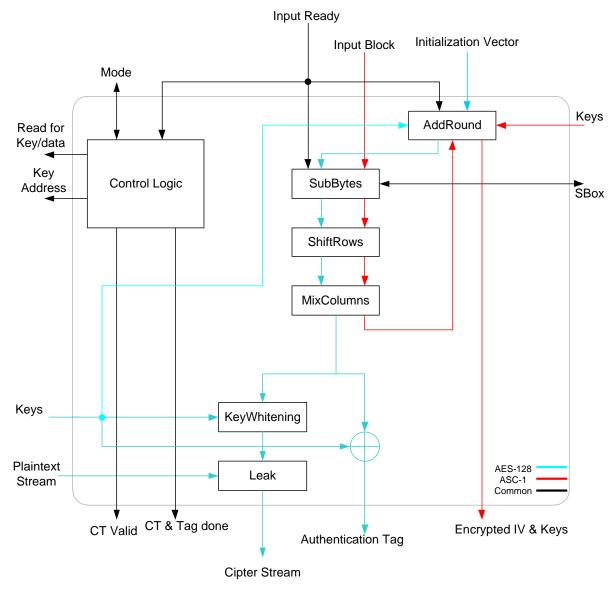

| 4.16 AES-128 & ASC-1 encryption core block          | 117 |

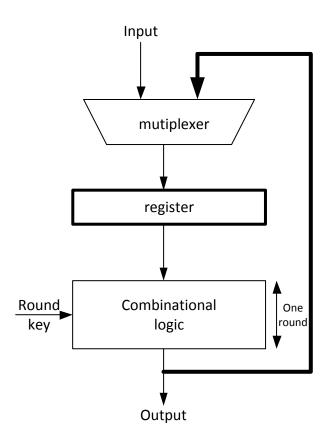

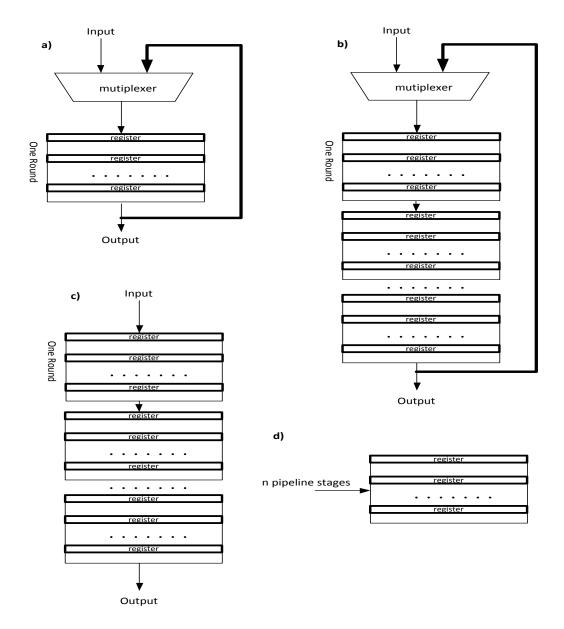

| 5.1 Iterative Architecture of Block cipher                                       | 123 |

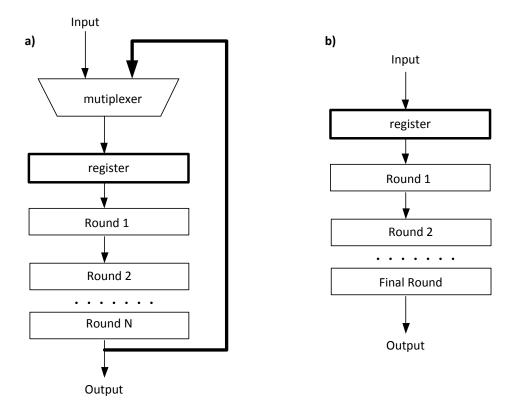

|----------------------------------------------------------------------------------|-----|

| 5.2 Hardware Architecture                                                        | 124 |

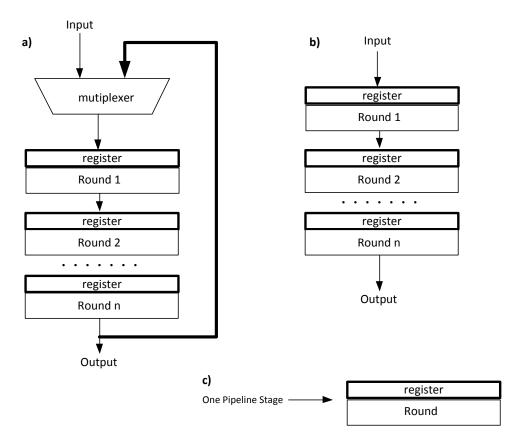

| 5.3 Hardware architecture for non-feedback cipher modes                          | 125 |

| 5.4 Optimal Hardware Architecture for non-feedback cipher modes                  | 126 |

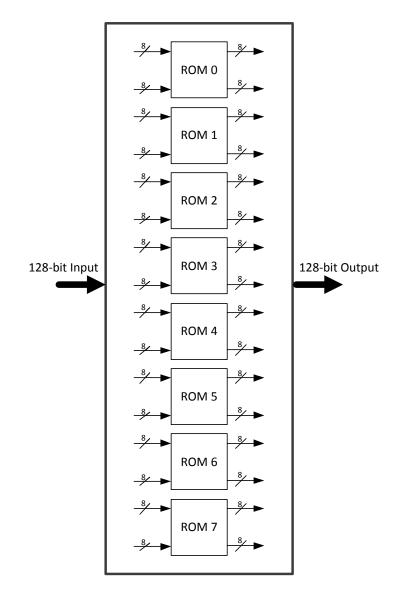

| 5.5 S-Box organized as 8 banks of 256 x 8 dual port ROMs                         | 128 |

| 5.6 Key Logic Unit                                                               | 129 |

| 5.7 Proposed AES-128 Hardware Architectures                                      | 131 |

| 5.8 Proposed ASC-1 Iterative Hardware Architectures                              | 133 |

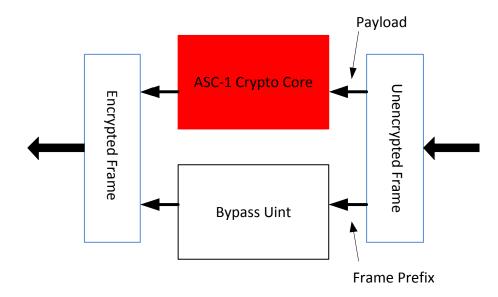

| 5.9 Crypto Architecture                                                          | 134 |

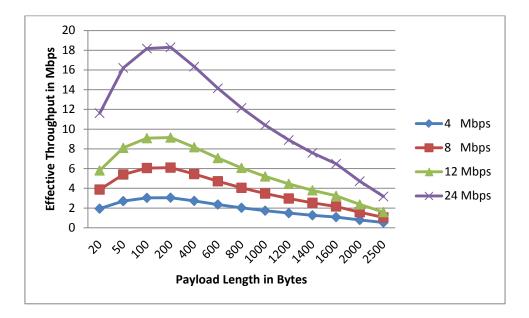

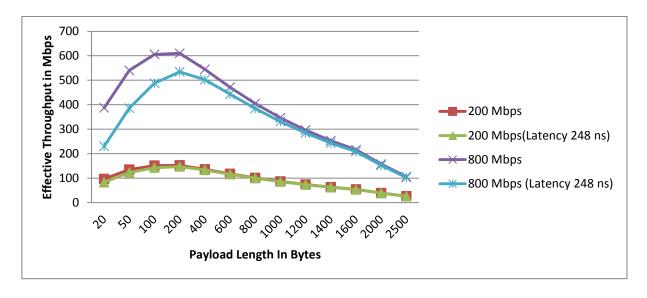

| 5.10 Throughput vs. Payload length at a bit error rate of $10^{-4}$ in a channel | 135 |

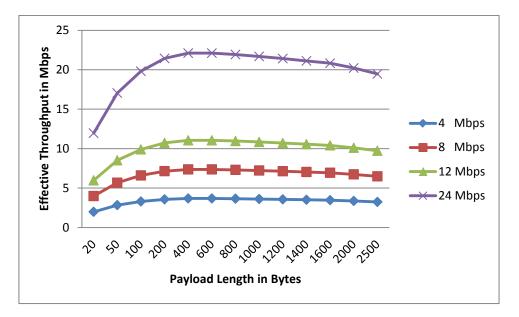

| 5.11 Throughput vs. Payload length at a bit error rate of $10^{-5}$ in a channel | 136 |

| 5.12 Throughput vs. Payload length at a bit error rate of $10^{-4}$ in a channel |     |

| with no latency and with latency of 248ns                                        | 137 |

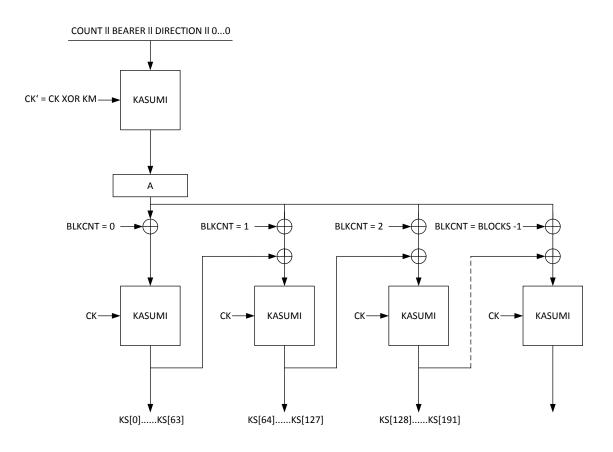

| 5.13 Confidentiality Algorithm f8                                                | 140 |

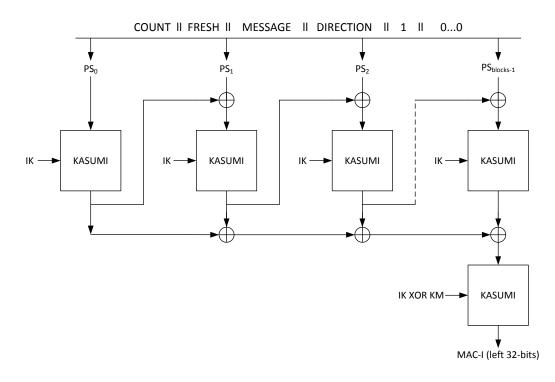

| 5.14 Integrity Algorithm f9                                                      | 141 |

## List of Tables

| 2.1 Hash Functions and MAC Algorithms                                        | 45  |

|------------------------------------------------------------------------------|-----|

| 3.1 Security Results in different composite authenticated encryption schemes | 56  |

| 5.1 Performance of Basic Operations in AES block cipher                      | 128 |

| 5.2 Performance of AES-128 & AES-256 Key Expansion in Parallel               |     |

| and Iterative Architecture                                                   | 130 |

| 5.3 Performance of AES-128 Encryption in Parallel and Iterative Architecture | 130 |

| 5.4 Performance of ASC-1 Encryption core Iterative Architecture              | 132 |

| 5.5 Physical Layer Parameter for LTE and WiMAX                               | 139 |

|                                                                              |     |

## List of Acronyms

| A2D   | Analog-to-Digital                             |

|-------|-----------------------------------------------|

| ASIC  | Application Specific Integrated Circuits      |

| AES   | Advanced Encryption Standard                  |

| ASC-1 | Authentication Stream Cipher One              |

| AEAD  | Authenticated encryption with associated-data |

| AE    | Authenticated encryption                      |

| AH    | Authentication header                         |

| AU    | Almost Universal hash function                |

| AXU   | Almost XOR Universal hash function            |

| BER   | Bit Error Rate                                |

| CR    | Cognitive radio                               |

| CFB   | Cipher feedback mode                          |

| CA    | Certificate Authority                         |

| CBC   | Cipher Block Chaining                         |

| CFB   | Cipher Feedback                               |

| CRHF  | <b>Collision Resistant Hash Functions</b>     |

| CPLD  | Complex Programmable Logic Device             |

| DSP   | Digital Signal Processor                      |

| DSA   | Dynamic Spectrum Access                       |

| DES   | Data Encryption Standard                      |

| DoS   | Denial of Service                             |

| DPA   | Differential Power Analysis                   |

| DDC   | Digital Down-convertors                       |

| DoD   | Department of Defense                         |

| D2A   | Digital-to-Analog                             |

| ECB   | Electronic Code Book                          |

| ESP   | Encapsulating security payload                |

| FAS   | Frame Alignment Signal                        |

| FPGA  | Field Programmable Gate Array                 |

| HDL   | Hardware Description Language                 |

| IF    | Intermediate Frequency                        |

| INT-PTXT | Integrity of the plaintexts                           |

|----------|-------------------------------------------------------|

| INT-CTXT | Integrity of the ciphertexts                          |

| IND-CPA  | Indistinguishability under a chosen plaintext attack  |

| IND-CCA  | Indistinguishability under a chosen ciphertext attack |

| IACBC    | Integrity Aware CBC                                   |

| IAPM     | Integrity Aware Parallelizable Mode                   |

| JTRS     | Joint Tactical Radio Software Program                 |

| LAXU     | Leak-safe XOR Universal hash function                 |

| MAC      | Message Authentication Codes                          |

| MDC      | Modification Detection Codes                          |

| NIST     | National Institute of Standards and Technology        |

| NM-CPA   | Non-malleability under a chosen plaintext attack      |

| NM-CCA   | Non-malleability under chosen ciphertext attack       |

| OFB      | Output Feedback                                       |

| OWHF     | One-Way Hash Functions                                |

| OCB      | Offset CodeBook mode                                  |

| PKC      | Public-Key Cryptography                               |

| PROM     | Programmable Read-Only Memory                         |

| PLA      | Programmable logic array                              |

| QoS      | Quality of Service                                    |

| RF       | Radio Frequency                                       |

| RTL      | Register transfer level                               |

| SDR      | Software Defined Radio                                |

| SHS      | Secure Standard                                       |

| SHA      | Secure Hash Algorithm                                 |

| SCA      | Software Communication Architecture                   |

| SS       | Spectrum Sensing                                      |

| SD       | Spectrum Decision                                     |

| SM       | Spectrum Mobility                                     |

| SSH      | Spectrum Sharing                                      |

| SoC      | System-on-Chip                                        |

| SPA      | Simple Power Analysis                                 |

| SSL      | Secure Socket Layer                                   |

| XCBC     | Extended Cipher Block Chaining Encryption             |

# **1** Introduction

Software-defined radio (SDR) has been recognized as one of the most important technologies for wireless communications. It offers a flexible mechanism to change transmitter and receiver characteristics such as modulation type, radiated power, and air interfaces by making software changes. This gives rise to the possibility of adapting the radio to users' preferences and the operating environment and of supporting multiple standards without requiring separate hardware for each standard. However lots of security concerns are raised in terms of reconfiguring the radio through software (downloading new radio functionality), platform integrity, key management, spectrum management, and integrity and confidentiality of data.

The concept of SDR appeared in 1970's in USA and Europe and the term was coined by Joseph Mitola III in 1991[JMI1]. The idea was to signal the shift from digital radio to multiband multimode software-defined radios where 80% of the functionality is provided in software. Mitola presented these radios as an intelligent agent able to track radio resources and related computer-to-computer communications and able to detect user communications needs as a function of use context, and to provide radio resources and the wireless services most appropriate to those needs. In 1992 United States Department of Defense (DoD) began the development of SDR technology through the SPEAKeasy research project, where the idea was to bring all the discrete military radios under one umbrella using software radio technology [RJD]. In 1997, the United State government launched the Joint Tactical Radio Software Program (JTRS) with the mission to develop standardized software architecture in order to improve software component portability, know as *Software Communication Architecture (SCA)* [JTR].

Initially SCA was mainly developed for military purposes. In 1999 SDR Forum adopted the SCA standard and promoted SDR technologies with applications for commercial cellular, Personal Communication Systems (PCS), and third generation (3G) and emerging fourth generation (4G) cellular services.

### **1.1 Software Defined Radio**

The typical hardware radio system consists of a variety of analogue elements like filters, converters, modulators and demodulators. These hardware devices are expensive and offer low compatibility with other components. This prompted the idea of SDR, where the user could use

SDR technology to realize many applications without a lot of efforts in integration of different components by moving from analogue to digital technology. Different software modules can be implemented to support different modulators and demodulators in the SDR platform. Also with the exponential increase in digital technology in terms of performance and productivity will continue to move closer to the antenna and replace much of the analogue front end.

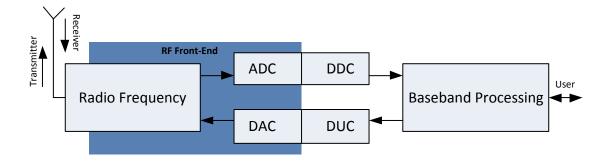

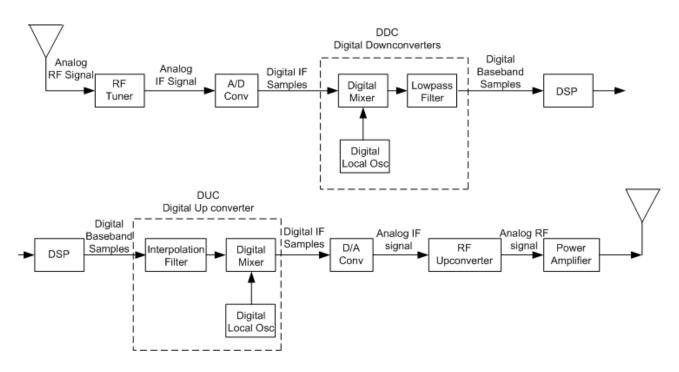

Figure 1.1 shows a generic SDR transceiver, where the main components are the radio front-end and baseband processor. The front-end part consists of analog hardware modules. As the receiver side, the RF front-end part is responsible for RF amplification, down conversion from radio frequency (RF) to intermediate frequency (IF) signal and finally convert the signal from Analog-to-Digital (A2D). On the transmit path, the signal is converted from Digital-to-Analog (D2A) then analog up conversion and RF power amplification. The baseband processing unit performs the baseband operations, these operations are quite different based on the type of communication technologies. However based on their role, it can be categorized into five function blocks: Channel coding/decoding, block interleaving/ de-interleaving, modulation/ demodulation, channel estimation, and pulse shaping [TUL].

Figure 1.1: Generic SDR transceiver

The main feature of SDR is its ability to dynamically adapt according to the radio environment through the re-configurability of its components. More precisely, the re-configurability is the ability of adjusting operational parameters for the transmission on-the-fly without any modifications on the hardware components. This feature gives SDR systems the ability to support a variety of mobile radio standards. Unlike implementing radio functional blocks on inflexible Application Specific Integrated Circuits (ASIC) in the past, the technologies such as Field programmable Gate Array (FPGA), Digital Signal Processor (DSP) and General-Purpose Processor (GPP) are used to build software radio blocks. These components have reconfigurable capability and deliver flexibility of programmable architectures with power efficiency and performance. In

[TUL] one identifies four different opportunities for reconfiguration in software-defined radio:

- *Pre-deployment* Late changes are made in the design process based on the target architecture just before the device is deployed.

- *In-field upgrade* Device software / firmware is updated to support a new standard or feature that was not included at deployment.

- *Reconfiguration per call or session* Device is reconfigured at the start of the session i.e., a voice or data transmission. This could be to select the most efficient or cheapest service available at the point of time.

- *Reconfiguration during a call or session* Device is reconfigured during voice or data transmission e.g. to hand over from one service to another.

### 1.1.1 Cognitive Radio

The idea of cognitive radio (CR) was first described by Mitola [JMI2], as the natural evolution of the SDR. The CR by Mitola was presented as an intelligent fully reconfigurable wireless transceiver that is able to detect user communication needs and automatically adapts its communication parameters most appropriate to those needs. Later the focus of the research was shifted towards the intelligent and opportunistic use of the radio resources, a technique known as Dynamic Spectrum Access (DSA).

Based on this, the concept of CR was more emphasized towards DSA, which led to a new CR definition[SHY]: an intelligent wireless communication system, aware of its surrounding environment that uses the methodology of understanding-by-building to learn from the environment and to adapt its internal states to statistical variations in the incoming RF stimuli by making corresponding changes in certain operating parameters (e.g., transmit-power, carrier-frequency, and modulation strategy) in real-time, with two primary objectives in mind: highly reliable communications whenever and wherever needed and efficient use of the radio spectrum.

One of the main capabilities of the CR is its ability to reconfigure, which is enabled by the SDR platform, upon which the CR is built. The key enabling technologies of CR are the functions that provide the capabilities to share the spectrum in an opportunistic manner. Most of the spectrum is already assigned but not used all the time. Here the challenge is the optimal sharing of the

spectrum with other existing networks without interfering with their transmission. In order to do so the CRs makes uses of temporarily unused spectrum known as Spectrum Holes or white spaces. By definition in [SHY] a spectrum hole is a band of frequencies assigned to a primary user, but at a particular time and specific geographic location, the band is not being used by that user. However if CR is using a particular spectrum hole and another user also starts using this space then the CR either move to another spectrum hole or continue using it by altering its transmission power level or modulation scheme to minimize interference. Therefore CR is a perfect example for using the available spectrum in an efficient and opportunistic manner and through it, it is possible to:

- Sense the available spectrum;

- Decide the best available channel;

- Coordinate with other users;

- Vacate the channel either due to primary user or when the channel conditions worsen.

**Cognitive Radio Functions** - The main goal of CR is to enable networks to use the available spectrum band according to network users Quality of Service (QoS) requirements. However CR networks impose unique challenges due to the presence of primary network. Thus new spectrum management functions for CR networks are taken into consideration in order to avoid critical design challenges like – Interface avoidance, QoS awareness and Seamless communication. These functions are as follows:

- *Spectrum sensing (SS):* The purpose of SS is to allocate only the unused portions of the spectrum. The radio monitors the available spectrum bands and look for spectrum holes.

- Spectrum decision (SD): Based on the available spectrum bands and associated potential channel estimated channel capacity, the CR user can allocate the channel. The decision is not only based on the availability of the channel but also QoS requirements such as data rate, error rate, mode of transmission, bandwidth etc.

- *Spectrum mobility (SM):* SM is an important function which allows a network to use the spectrum in a dynamic manner. If the specific portion of the spectrum in use is required by the primary user, the communication must be continued in another vacant portion of the spectrum.

- Spectrum Sharing (SSH): Due to the shared nature of the wireless channel there may be multiple CR users trying to access the spectrum, access to the network should be coordinated in order to prevent multiple users colliding in overlapping portions of the spectrum.

### 1.1.2 Field Programmable Gate Arrays/ System on Chip

For past few years FPGAs have become an increasingly important resource for SDR. A successful SDR design is build by designing powerful processing blocks and connecting these blocks to form a flowgraph. These blocks are either implemented in software or in soft hardware with an FPGA. However with the development in the field of programmable logic, FPGA has ushered in an era of rapid prototyping for digital systems. The FPGAs are cost efficient and supplies abundant resources too for the system designers. FPGAs are programmed using Hardware Description Language (HDL) commonly known as VHDL. Same VHDL code could run on any FPGA that has enough logic cells, this characteristic give further flexibility and dynamic upgradeability to SDR device. FPGAs reprogrammable nature makes it ideal for SDRs, so any upgrades or changes in the operational parameters can be easily uploaded to the device without any hardware reconfigurations.

**Partial Reconfiguration** – A shared resources model is referred as more efficient architecture for SDRs. As compared to dedicated resource model, shared resources are capable of supporting ex., multiple waveforms across a single set of processing resources; this allows for much more efficient usage of the resources. The technology that facilitates this model is partial reconfiguration of the FGPA. Partial reconfiguration allows the replacement of one or multiple functional blocks with a different implementation while other portions are either being used by other applications or going unused. Without partial reconfiguration, it would be necessary to reconfigure entire FPGA. However, using partially reconfigurable platform FPGAs as an SDR system-on-chip (SoC) will substantially decrease the component count of the SDR device and reduce power consumption while still providing the necessary functionality [PKG].

### **1.2 Need for Security**

Communication between two or more devices over insecure channel, flexibility of implementing radio functions such as modulation/demodulation, signal generation etc, on software and reconfiguration of radios to upgrade or adapt to user preferences, and regional regulations may lead to serious radio security concerns. While reconfiguring the radios have many benefits, the ability to reconfigure radio functionalities with software may lead to many security problems such as unauthorized use of application and network services, unauthorized modification of software and manipulation of radio sets. For example, malicious software can be uploaded into the device that changes its radio frequency so that the device will no longer function within the regulated

constraints. This could lead to the Denial of Service (DoS) attacks. Additionally, transmission of unencrypted data over insecure channel could compromise the confidentiality and integrity of the data.

The concept of transmission security is broadly divided at three different levels of security [TAJ], as follows:

- *Detection* If an unauthorized user is able to distinguish between transmission signal and noise, a signal is said to be detected.

- Interception After transmission signal being detected if an unauthorized user is able to identify the specific class of a signal and distinguish from signals belonging to other classes, a signal is said to be intercepted.

- *Exploitation* If an unauthorized user is able to recover any useful information such as the message contents or the origin of the message, then a signal is said to be exploited.

Security has always being a hot topic in SDRs weather it is for military or commercial applications. However the subject of security for SDR systems is quite broad and covers many issues. In the past SDR security has followed few general directions ex., the first direction mentioned in [SS1][SS2][HRM] covers the list of security requirements for the underlying hardware, integrity of the platform, downloading upgrades, key management issues, and content protection and possible threats on SDR. The second issue explores the essential issue of secure downloading of new radios parameters. A framework for establishing secure download using a tamper-proof hardware module is proposed [RFL][LMI][ABR]. The third direction focuses on spectrum management and policy enforcement of SDR [PFL][KSA][ATO].

### 1.2.1 FPGAs for Cryptographic Application

FPGAs are generic semiconductor devices contain programmable logic components called "logic blocks" that can be programmed and reprogrammed, as per user-defined logic functions. In recent years, FPGAs are designed using the latest technologies to be as competitive as possible with ASICs in terms of performance, power and space. FPGAs compete by being reconfigurable and combine the advantages of software and hardware implementation. Additionally, FPGA reconfigurable hardware gives advantage in cryptographic applications [ACR][TWC]. Following shows the benefits of implementing Crypto solutions on FPGAs:

Algorithm Flexibility - The term flexibility in algorithms refers to the switching of cryptographic

algorithms during operation of the targeted application. Based on the degree / level of the security various encryption algorithms could be programmed or reprogrammed on the fly. Majority of security protocols such as IPSec are algorithm independent and allow for multiple encryption algorithms. These algorithms are negotiated on a per-session basis and wide variety may be required.

Algorithm Upload - It is to be recognized that the devices need to be upgraded at some point with newer or securer cryptosystem. The reason could be compatibility concerns with new applications. Algorithm upload is necessary because a current algorithm for ex., AES (Advanced Encryption Standard) uses only 128-bit encryption keys and to increase the level of security it needs to be replaced by AES 256-bit. This could be achieved under the assumption that there is some kind of connection to a network, where FPGA-equipped encryption devices can upload the new configuration code. As compared to FPGA-implemented this upgrade is practically infeasible to ASIC-implemented algorithms.

Architecture Modification - Most of the encryption algorithms used today are standardized. But in certain cases hardware architecture can be much more efficient if it is designed for specific set of performance parameters like implementation area, throughput and latency. Based on the type of cryptosystem and resources, and area available these algorithms could be implemented on sequential or parallel hardware architectures. For example as shown in chapter 5 section 5.3, hardware implementation of AES in fully parallel hardware architecture can achieve maximum throughput of 32 Gbits/s on Xilinx Vertix -5VLX50T and 51% of area is consumed. Whereas sequential architecture uses 20% of area and can achieve maximum throughput of 0.876 Gbits/s.

*Resource Efficiency* - Today most of the security protocols used for communication between two or more devices are hybrid protocols. This means, that a public-key algorithm is used for secure key exchange and private key algorithm for encryption of data over channel. Once the keys are exchanged and devices are authenticated, the public-key algorithm is not used for the session. Since the algorithms are not used simultaneously, the same FPGA device can be utilized for both through run-time reconfiguration. This is an important factor in many implementations where resources are limited.

*Throughput* - Comparing FPGAs to general purpose CPU and ASICs, FPGA implementations have the potential of running substantially faster than software implementations but slower than ASIC implementation. General purpose CPUs are not optimized for fast execution especially in the case of public-key algorithms. That happens mainly because they lack those instructions for modular arithmetic operations on long operands. AES block cipher for example reaches the data rate of 112.3 Mbit/s and 718.4 Mbit/s on a DSP TI TMS320C6201 and Pentium III, respectively [ACR]. As compared to FPGA implementation of AES on Virtex XCV-1000BG560-6 achieved 12 Gbit/s using 12,600 slices and ASIC, the Amphion CS5240TK can reach 25.6 Gbit/s at 200 Mhz [TWC].

### 1.2.2 Attacks on FPGA

For past few years, the industrial market is more inclined towards FPGAs due to their benefits of re-programmability. With FPGAs being used in a variety of military and commercial applications that require security features and as these designs have become more valuable, attackers look for possible vulnerabilities and developers for defenses.

In case of an implementation of cryptographic algorithm, the main objective of an attacker is to recover a secret key that could be a symmetric key or the private key of an asymmetric encryption algorithm. Most of the cryptographic algorithms used in commercial applications are publicly known and recovering the key facilitates the attacker to decrypt all the future and past communication.

Rest of the section summarizes security issues produced by attacks against given FPGA implementation.

*Cloning* – Due to the generic nature of FPGAs, the image generated for one FPGA device could also be used in any other device for same family and size. In such case, attackers can clone image and use them in cheaper devices that can compete with the originals. This security vulnerability is usually common in volatile FPGA, where the configuration data is stored externally in a nonvolatile memory and is transmitted to the FPGA at power-up. An adversary could easily eavesdrop on the transmission and get the configuration file. There are many different concerns with regards to cloning. For original system developers, the clone system can hurt the bottom line after significant development investments and it could affect the reputation of the original product if the clone or poor quality products are marketed as originals. Another threat is cloning /copying of a cryptographic algorithm together with its key. In few cases it is possible to run the cloned application in decryption mode to decrypt communication. An attacker can also lunch man-in-the-middle attack and masquerade as the attacked communication party.

*Black Box Attack* – Black box attack is a classical method to reverse engineer a chip. The attacker launches a variant of known-plaintext attack, where an attacker inputs all possible combinations, while saving the corresponding outputs. This attack can be used to reveal secret information such as secret keys and code books. However this attack is only successful if a small FPGA with specific inputs and outputs are attacked and a lot of processing power is available. With today's design complexity and the size of state-of-the-art FPGAs this attack is not really a threat nowadays.

*Readback Attack* – It is a feature in FPGAs, where the snapshot of the FPGAs current state could be retrieved while it is still in operation. It is used for read a configuration out of the FPGA for easy debugging. The image (snapshot) is different from original bit stream by missing the herder, footer and initialization commands etc. But an attacker can easily readback the design, add the missing

static header and footer and use it in other device. The feature can be prevented by adding few security bit provided by the manufactures. Xilinx provides security bit for disabling readback, but it can be easily found. When these security bit are used, multiple, majority-voted, disabling registers are activated with the FPGA to prevent readback [SAD] [JMA]. Despite of countermeasures, an adversary is still able to attack FPGAs with fault injection. This kind of attack was first introduced in [DBR], where it was shown to break public-key algorithms by exploiting hardware faults. There has been many publications presenting different techniques to insert faults e.g., electromagnetic radiation [JJQ], infrared laser [CAJ], and flash light [SSR].

*Reverse engineering the image/bitstream* - Once the attacker is in possession of the image, assuming the case where image is unencrypted. The attacker will be able to transform bitstream into a functionality equivalent description of the original design. Image could be reversed fully or partially. Partial image can be used for the extraction of data for the image such as secret keys or Block Ram/LUT content without gaining the full functionality of the design. In full reverse image one can gain the full functionality of the design and reproduce another bitstream completely different from the original one such that it would be hard to prove in fingerprint.

Side Channel Attacks – An attack based on the information gained due to the unwanted leak in the physical implementation of a cryptosystem instead of theoretical weakness in the algorithm are known as side-channel attacks. Example of side channels include in particular- power consumption, timing behavior and electromagnetic radiation. Today while implementing an encryption system on FPGA, additional input / output are used which are not the plaintext or ciphertext. The devices produce timing information, radiations, power consumption statistics and lot more. Additionally these devices also have additional "unintentional" inputs such as voltage that can be tampered with to cause predictable outcomes. Side channel attacks make use of all this information with other know techniques to retrieve keys. In terms of power analysis side channel side channel attacks are further classified as Simple Power Analysis (SPA) and Differential Power Analysis (DPA), where the attacker studies the power consumption of an encryption device. SPA is based on the visual representation of the power consumption of a device will encryption is in process. The attacker simply observes system power consumption, as the amount of power consumed varies depending on the instruction performed. DPA consists not only of visual but also statistical analysis and error-correction statistical methods, to obtain information about keys.

### **1.3 Confidentiality and Authentication**

Communication between two parties over an insecure channel often concerns with two main security objectives: confidentiality and authenticity of the data. The objective of confidentiality is to keep the contents of the information secure and no one but the sender and authorized receivers are able to read the data. Authentication of message data verifies the origin and improper or unauthorized modification of data.

In the past, confidentiality of the data was the main and probably the only issue that was considered. This was mainly because no other security objectives such as authentication or integrity prevented to have access to the information. Only message encryption can protect data from eavesdroppers. However encryption of messages provides some sort of authentication but as compared to present authentication techniques it is weak and cannot be relied upon. In addition to confidentiality, authentication services have been implemented but as add on feature to provide extra information security. Encryption algorithms are used to ensure confidentiality while Message Authentication Codes (MAC) can be used to provide authentication. In past few years, techniques have been invented which can combine encryption and authentication into a single algorithm. By combining these two security features and performing single pass operation might possibly provide following advantage for hardware implementation:

- The rapid growth of portable electronic devices with limited area has opened a vast scope for compact circuit design opportunities. Implementation of single algorithm instead of two separate algorithms with definitely has less area requirements. Reduction in area requirements on chip is directly proportional to the reduction in cost.

- Small and compact designs tend to consume less power as compared to bulky designs. This is an attractive feature for low-power devices like Cellular phone, PDAs and smartcards.

- Even though separate keys are used for encryption and authentication for better security of the system. But both the keys are usually derived from the same master key. This will have a slight advantage with regards to the key storage issues over separate algorithms.

- Most of the new designs target performance goals like throughput and throughput-area trade-off. In many cases, combined schemes are based on block ciphers, and designers have tried to be efficient with the number of block cipher calls required for getting both confidentiality and authentication from the algorithm. Based on the mode of the operations some of these combined schemes can run in parallel and achieve much higher speed than older techniques.

From above, the cryptographic schemes that provide both confidentiality and authentication are called authenticated encryption schemes. The scheme is designed in such a way that the sender produces the ciphertext as well as an authentication tag which is verified by the receiver.

### **1.4 Motivation**

The main focus of the thesis is to propose a single pass authenticated encryption scheme to achieve faster encryption and message authentication for reconfigurable chips such as FPGAs in Software Defined radios. The motivation to focus only on this issue comes from the fact that the information security is one of the key relevant aspects of SDR, whether it is for data transmission or downloading of radio parameters or upgrades. Additionally, proposing a crypto solution for reconfigurable chips instead of ASICs gives us the possibility to improve and correct hardware components. This will reduce the vulnerabilities in the device and improves radio interoperability and upgradeability.

The future of communication systems is expected to be based on SDR principals. SDR provides an efficient and comparatively inexpensive solution to the problem of building multi-mode, multiband, multi-functional wireless devices that can be enhanced using software upgrades. As such SDR can be considered an enabling technology that is applicable across a wide range of areas within the wireless infrastructure, both military and commercial. The main issue in these communication systems is security, whereby an adversary can take control of a radio system to their advantage. Additionally, if a third party modifies a stream at lower layers then higher layers can be caused damage upon i.e. application level of a mobile phone. As a result, documents and traditional applications of a device can be changed. Thus, various security functions such as authenticity, integrity and confidentiality need to be supported in SDR transceivers.

The goal of this research is to find an encryption scheme that can accomplish both message secrecy and authenticity in a single cryptographic primitive with the focus to achieve high throughput and minimal overhead for these radios. As, it is expected that the speed of the network will increase beyond Giga-bit so the need for fast cryptographic solution will be increased in the nearest future to take advantage of the future fast speed network.

So the above gives the motivation for the design and careful implementation of an Authenticated Encryption Stream Cipher for optimal results in terms of security and speed. Different hardware architectures are also taken into consideration to explore trade-off between area utilization and throughput in the implementation.

### **1.5 Problem Definition**

The problem tackled in this thesis is on how to develop a cryptosystem that could cover security features like confidentiality and authentication in single pass as opposed to traditional two pass approach. Additionally, keeping the security of the design at par with traditional systems, another problem was how to downsize the system and increase the efficiency so the design is ideal for implementation of low-cost, low-power SDR device. With this in mind this research gives answers to the following questions:

- What important parameters need to be kept under consideration while designing a single pass authenticated encryption scheme?

- Parameters like two separate keys for encryption and authentication, Initialization vector, underlying block cipher. For hash functions, security parameters like – preimage resistance, second pre-image resistance and collision resistance.

- What is the right trade-off between the security and the performance of the cipher?

- Design of block ciphers are mostly built from a round function in an iterative way. Using signal round function for encryption and its repeated use leaves patterns. This could be used to break the cipher. To add additional security extra rounds can be added but it also increases the complexity of the cipher. Thus, there should be right trade-off between the number of rounds and performance of the cipher.

- What are the optimum choices of hardware architecture for cryptosystem?

- In this thesis we explore different hardware architectures for implementation. Hardware architectures for cryptosystem are based on feedback and non-feedback modes of operation. Such as basic iterative architecture, partial /full loop unrolling architecture and pipelined architecture.

- What is the trade-off between minimum area, minimum power consumption, maximum throughput, maximum throughput to area ratio, etc?

- Hardware architectures mentioned above have their own pros and cons, ex: in a basic iterative architecture only single block cipher is implemented as a combinational logic where as in partial loop N rounds are implemented as a combinational logic.

In this thesis each one of these questions have been analyzed and solved.

### **1.6 Limitations**

Many issues need to be covered in order to make SDR systems secure. The security of SDRs has followed many general directions such as:

- Security Threats on the devices;

- Secure download of new radio parameters;

- Security concerned with spectrum management and policies;

In this thesis we have limited our research on the authenticity and privacy of the data transmission. This could also be applied for the secure upgrade and download of new radio parameters.

Another limitation is based on our proposed Authenticated Encryption (AE) cipher. ASC-1 operates in a cipher feedback mode (CFB) in order to compute an authentication tag, which means the encryption core of the scheme is limited to run in feedback modes hardware architectures, i.e., basic iterative or partial loop unrolling. This will certainly limit the throughput of the design as compared to the designs in non-feedback mode hardware architectures. However in such kind of encryption modes, the encryption and decryption operations are similar so there is no need for inverse block ciphers. From implementation point of view this is considered as an advantage.

As mentioned this research is mainly focused on two fundamental information security goals: confidentiality and message authentication. Issues like key exchange between communicating parties are not considered. We assume that the recipient has knowledge of the secret key that is used to derive the Initialization vector and keys for encryption and authentication. Additionally we also assume that the secret / master key is securely placed in a crypto module inside the FPGA.

### **1.7 Contribution**

The contributions given throughout this thesis are the following:

- An Authenticated encryption scheme ASC-1 (Authentication Stream Cipher One) that is designed using a stream cipher approach instead of a block cipher mode approach;

- Proving the security of ASC-1, by showing that it is secure if one cannot distinguish the case when the round keys are uniformly random from the case when the round keys are derived by the key scheduling algorithm of ASC-1;

- Design and implementation of ASC-1 and Introducing a new crypto unit for reconfigurable chips;

- Analysis of performance parameters such as Area utilization, throughput and latency by releasing different hardware architectures.

The Publications performed during the Ph.D work:

- Samant Khajuria and Henrik Tange, Implementation of Diffie-Hellman Key Exchange on Wireless Sensor Using Elliptic Curve Cryptography : Wireless Communication Society, Vehicular Technology, Information Theory and Aerospace and Electronic Systems Technology, Wireless VITAE 2011

- Goce Jakimoski and Samant Khajuria, *ASC-1 : An Authenticated Encryption Stream Cipher :* Selected Areas of Cryptography (SAC), LNCS 7118, Springer, pp. 356-372, 2012.

- Samant Khajuria and Birger Andersen, *Authenticated Encryption for Low-Power Reconfigurable Wireless Devices:* Accepted for Journal of Cyber Security and Mobility, 2012.

- Samant Khajuria, Comparative Analysis of the Hardware Implementation of ASC-1 : In *Pipeline.*

### 1.8 Organization

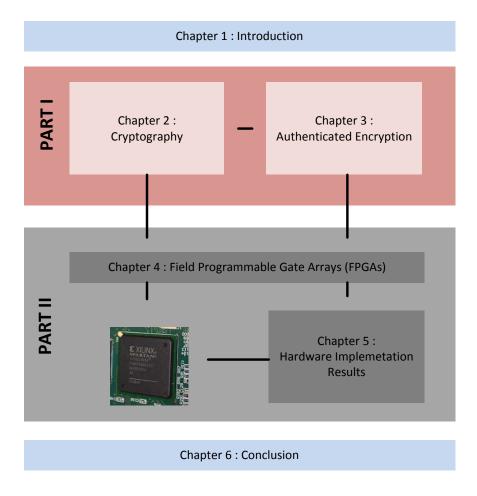

Figure 1.2 shows the outline of this thesis, as shown below the thesis is divided into two parts. Part I covers the cryptography part of the thesis and Part II is based on the design and implementation for the cryptographic schemes.

**Chapter 1** provides the overview on Software Defined Radios and the benefits of re-configurable architecture, together with the need of security for these architectures and the motivation for the

work developed and described in the thesis.

**Chapter 2** gives the general introduction of two prime security requirements – Confidentiality and Authentication of data. We introduce the cryptographic concept such as symmetric-key encryption and cryptographic primitives known as block and stream ciphers with some examples. Under Authentication we also give some background information on cryptographic hash functions, where both un-keyed and keyed hash functions are covered.

Figure 1.2: Thesis Outline

**Chapter 3** is based on Authenticated Encryption (AE) schemes, where we initially discuss the solution to the problem of privacy and authentication in a traditional manner known as "generic composition". Then we look into the advantages and disadvantages of 2-pass and 1-pass combined approach with few well known AE schemes. Based on this finally we present "ASC-1 : An Authentication Encryption Stream Cipher " and proof of security of ASC-1 by discussing The

information-theoretic case and computational security analysis.

**Chapter 4** presents the design and implementation of ASC-1 for FPGAs. At the start of the chapter we discuss the architecture and Implementation flow of the FPGAs followed by the role of FPGA in SDR with an example of Gnu radio framework and USRP hardware. This chapter also discusses the generic SDR structure and System-on-chip (SOC). Finally we present an implementation of ASC-1 for Xilinx Spartan-3 xc3s700an FPGA. For better performance and efficient resource allocation the design is divided into two parts – Initial phase generation and encryption process.

**Chapter 5** summarizes the results for hardware implementation of ASC-1. Performance parameters like area utilization, throughput and latency are also discussed and analyzed for different hardware architectures for feedback and non-feedback cipher modes. The results also show the optimal payload lengths of maximum throughput corresponding to the Bit Error Rate (BER) for different data rates. In the end we discuss OFDM modulation in LTE and WiMAX.

**Chapter 6** gives the final conclusion and outlook for the future work.

# References

[JMI1] J.Mitola. Software Radios: Survey, Critical Evaluation and Future Directions, *In Proceedings of the National Telesystems Conference*, NY: IEEE Press, May 1992.

[JMI2] J.Mitola and G.Q Maguire Jr. Cognitive radio: making software radios more personal. *IEEE Personal Communications*, 13-18, Aug.1999.

[RJD] R. J. Lackey and D. W. Upmal. Speakeasy: The military software radio, *IEEE Commun. Mag.*, vol. 33, pp. 56–61, May 1995.

[JTR] Software Communications Architecture Specification, JTRS Std. 2.2.2, Rev. FINAL, May 2006.

[TUL] T. Ulversøy. Software defined radio: Challenges and opportunities, *Communications Surveys Tutorials*, IEEE, vol. 12, no. 4, pp. 531–550, 2010.

[SHY] S. Haykin. Cognitive radio: brain-empowered wireless communications. *IEEE Journal on Selected Areas in Communications*, 23(2):201-220February 2005.

[PKG] P.K Gopalakrishnan. Hardware Platforms for Software Defined Radio, KPIT Cummins Infosystems Ltd, V1.2 Sept-2011.

[TAJ] Taj A. Strunman. Enabling Choatic Waveform Diversity, *Waveform Diversity and Design Conference*, IEEE Conference publications, pp. 160-167, 2009.

[HRM] R.Hill Myagmar and S. Campbell. Threat Analysis of GNU Software Radio, *In Proceedings of the WWC'05*. Palo Alto, CA, 2005

[SS1] SDR system security, SDRF-02-A-0006, Tech. Rep., 2002.

[SS2] A structure for software defined radio security, SDRF-03-I-0010, Tech. Rep., 2003.

[SS3] SDR wireless security, SDRF-04-I-0023, Tech. Rep., 2004.

[RFL] R. Falk, J. F. Esfahani, and M. Dillinger. Reconfigurable radio terminals - threats and security objectives *SDRF-02-I-0056*, Tech. Rep., 2002.

[LMI] L. Michael, M. Mihaljevic, S. Haruyama, and R. Kohno. A framework for secure download for software-defined radio, *IEEE Communications Magazine*, vol. 40, no. 7, pp. 88–96, July 2002.

[ABR] A. Brawerman, D. Blough, and B. Bing. Securing the download of radio configuration files for software defined radio devices. *In Proceedings of the International Workshop on Mobility Management & Wireless Access Protocols*, pp. 98–105,Sept. 2004.

[PFL] P. Flanigan, V. Welch, and M. Pant. Dynamic policy enforcement for software defined radio. In *Proceedings of Software Defined Radio Technical Conference and Product Exposition*, Nov. 2005.

[KSA] K. Sakaguchi, C. Fung Lam, T. Doan, M. Togooch, J. Takada, and K. Araki. ACU and RSM based radio spectrum management for realization of flexible software defined radio world, *IEICE Trans. Communications E Series B*, vol. 86, no. 12, pp. 3417–3424, Dec. 2003.

[ATO] A. Tonmukayakul and M. Weiss. Secondary use of radio spectrum: A feasibility analysis, In *Proceeding* of the Telecommunications Policy Research Conference, Oct. 2004.

[ACR] Alexandru Coman and Radu Fratila. Cryptographic Applications using FPGA Technology, Journal of Mobile, Embedded and Distributed Systems, vol. III, no.1, 2011

[SAD] S. Drimer. Volatile FPGA design security – a survey, Computer Laboratory, University of Cambridge, IEEE Computer Society Annual Volume, 2008.

[TWC] T. Wollinger and C. Paar. How secure are FPGAs in cryptographic applications?, In *Proceedings. of the 13th International Conference on Field-Programmable Logic and its Applications(FPL)*, pages 91–100, 2003.

[JMA] J. M. Aplan, D. D. Eaton, and A. K. Chan. Security Antifuse that Prevents Readout of some but not other Information from a Programmed Field Programmable Gate Array. United States Patent, No. 5898776, April 27 1999.

[DBR] D. Boneh, R. A. DeMillo, and R. J. Lipton. On the Importance of Checking Cryptographic Protocols for Faults. In *Advances in Cryptology — EUROCRYPT '97*, pages 37–51. Springer-Verlag, 1997. LNCS 1233.

[JJQ] J.-J. Quisquater and D. Samyde. Electro Magnetic Analysis (EMA): Measures and Countermeasures for Smart Cards. In *International Conference on Research in Smart Cards, E-smart 2001*, pages 200 – 210, Cannes, France, September 2001

[CAJ]C. Ajluni. Two New Imaging Techniques to Improve IC Defect Indentification. *Electronic Design*, 43(14):37–38, July 1995.

[SSR]S. Skorobogatov and R.J. Anderson. Optical Fault Induction Attacks. In *Workshop on Cryptographic Hardware and Embedded Systems — CHES 2002*, pages 2–12. Springer-Verlag, LNCS 2523. 2002

# <u>PART I – Algorithm Analysis &</u> <u>Development</u>

# 2

# Cryptography

The name Cryptography comes from the Greek words "kryptos" which means "hidden secret" and "graph" which means "writing" and is the art of hiding information. This definition may be historically accurate where the focus was only on the problem of secret communication and until 20<sup>th</sup> century, cryptography was an art. By late 20 century, a rich theory emerged enabling the rigorous study of cryptography as a science and today Cryptography is much more than secret information and art. For example, in addition to confidentiality it deals with the problems of data integrity, entity authentication, data origin authentication and much more.

As classical Cryptography is basically the process of encrypting and decrypting message, encryption is the process of converting normal message or communication (plaintext) into unintelligible text (ciphertext). Decryption is the reverse, moving from unintelligible ciphertext to plaintext. A cipher is a pair of algorithms which perform this encryption and decryption. This operation of a cipher is controlled both by the algorithms and the keys. In communication, cryptography is necessary when communicating over any unsecure medium, which includes particularly wireless communication. Within the context of any application-to-application communication, there are some specific security requirements including [MOV]:

*Confidentiality* - Ensuring that no one except the intended receiver should be able to read the message when transmitting a message over insure channel. An unauthorized eavesdropper should not get any information about the contents of the message. Also stored data should be protected against unauthorized access.

Authentication - The process of proving one's identity. This function applies to both entities and information itself. Two users trying to communicate should identify each other and/or information delivered over a communication channel should be authenticated. For the above mentioned reasons, this aspect of cryptography is usually subdivided into two major cases: *entity authentication* and *data origin authentication*. Entity authentication assures the identity of the entity involved and data origin authentication ensures the integrity of the data, if the is message is modified and the source had changed.

*Data integrity* - Assuring the receiver that the received message (neither accidently nor on purpose) has not been altered in any way from the original. To assure this, one must be able to

detect manipulation by unauthorized parties.

*Non-Repudiation* – A mechanism to prove that the sender really sent the message. This prevents an entity from denying previous actions.

A fundamental goal of cryptography is to adequately address these four areas in both theory and practice. For secure communication there are two types of cryptographic schemes typically used, Symmetric Encryption (Secret-key cryptography) and Asymmetric Encryption (Public-key cryptography). In this thesis we focus on symmetric encryption schemes and Hash functions which are supposed to provide confidentiality and message authentication.

# 2.1 Symmetric Encryption

Two parties want to communicate over an insecure channel without allowing an eavesdropper to obtain or modify any information about their conversation. Another problem is the key management issue, where we assume that both the parties have somehow exchanged a secret key over a secure channel. The main purpose of these encryption algorithms is to protect the secrecy of the message transmitted over an insecure channel.

Generally an encryption scheme consists of two mathematical transformations: an encryption function E and a decryption function  $D = E^{-1}$ . An encryption function takes the plaintext (P) as input and transforms into the corresponding ciphertext C = E(P), and a decryption function inverts the encryption function D(C) = P. In order for this encryption scheme to work, E should be designed in such a way that an eavesdropper cannot extract any information about the plaintext after intercepting ciphertext and the decryption function should be kept secret. By looking into the practical issues, keeping the whole algorithm secret is never a good idea because it means that several algorithms are needed for different partners [CAB]. The idea to overcome this problem is to construct a parameterized encryption algorithm. In this scheme both encryption and decryption function uses an additional parameter also called as secret key (k),  $D_{k'}(E_k(P))$ for  $k' \neq k$  does not reveal any information about the plaintext P. This secret key is usually a bit string and depending on encryption scheme the length of this key could vary from few bits to couple of hundred bits. A single key is used from both encryption and decryption functions. The sender uses the key k to encrypt the plaintext p and sends the ciphertext  $C = E_k(P)$  to the receiver. The receiver applies the same key k to decrypt the message and recover the plaintext  $P = D_k(C)$ .

Definition 2.1 [STN]: A symmetric cryptosystem, also called a symmetric encryption scheme, is a

five-tuple (P, C, K, E, D) where P is the finite field set of plaintexts, C is the finite set of ciphertexts and K is the key space. For each key  $k \in K$  there is an encryption function  $E_k \in E$  with respect to k,

$E_k: P \rightarrow C$ and a corresponding decryption function  $D_k \in D$ ,

$D_k: C \rightarrow P$

Such that  $D_k$  ( $E_k$  (p)) = p for all plaintexts  $p \in P$ .

From the above, it is clear that the key must be known to both the sender and the receiver. The biggest difficulty with this approach is the distribution of the key; exchange of secret key over a secure channel beforehand. In 1970s, Diffie and Hellman proposed trapdoor one-way functions where the secrecy of the encryption function was not necessary. These are functions which are easy to evaluate, but cannot be efficiently inverted, unless some extra information (the trapdoor) is given. This insight gave birth to Public-Key Cryptography (PKC). Two keys are used in public-key cryptosystem; a public and a private key, where the public defines the encryption function and the private key is the trapdoor information needed to invert the encryption function. When user Awants to send a message to user B, user A then encrypts the message using B's public key. Public is usually obtained by a direct exchange over insecure channel or from a trusted source, often referred to as Certificate Authority (CA). Afterwards, user B is able to decrypt the message using it own private key. Public-key cryptography has huge advantage as both the parties do not have to exchange any information over secure channel before they start exchanging messages. However, symmetric cryptography still plays a vital role in practical systems because symmetric encryption is an order of magnitude more efficient than public key encryption. In the remainder of this thesis we only consider symmetric encryption schemes.

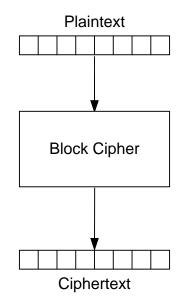

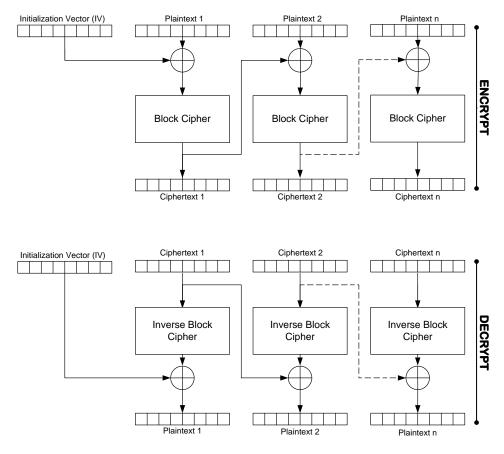

Symmetric encryption algorithm are traditionally divided into two categories: *stream ciphers* and *block ciphers*; A stream cipher operate on a single bit, byte, and word at a time and implement some form of feedback mechanism so that the key is constantly changing. As the name say in a block cipher, the scheme encrypts one block of data at a time using the same key on each block. In general, the same plaintext block will always encrypt to the same ciphertext when using the same key in a block cipher whereas the same plaintext will encrypt to different ciphertext in a stream cipher.

# 2.2 Block Cipher

Block ciphers can be either symmetric-key or asymmetric-key. In this thesis our main focus is symmetric-key block ciphers. Symmetric-key block ciphers play an important role in many cryptographic systems. Their flexibility allows construction of pseudorandom number generators, stream ciphers, Messages Authentication codes and hash function.