#### **Aalborg Universitet**

| The Use of Active Elements to Reduce the Size and Weight of Passive Components in Adjustable Speed Drives |

|-----------------------------------------------------------------------------------------------------------|

| Maheshwari, Ram Krishan                                                                                   |

|                                                                                                           |

|                                                                                                           |

Publication date: 2012

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Maheshwari, R. K. (2012). The Use of Active Elements to Reduce the Size and Weight of Passive Components in Adjustable Speed Drives. Department of Energy Technology, Aalborg University.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- ? Users may download and print one copy of any publication from the public portal for the purpose of private study or research. ? You may not further distribute the material or use it for any profit-making activity or commercial gain ? You may freely distribute the URL identifying the publication in the public portal ?

Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

## The Use of Active Elements to Reduce the Size and Weight of Passive Components in Adjustable Speed Drives

By RamKrishan Maheshwari

Aalborg University, Denmark Department of Energy Technology

#### **Acknowledgement**

It had been an honor for me to work as a PhD student in the Department of Energy Technology, Aalborg University, Denmark. I would like to thank the department to give me the opportunity to work on this project.

I am grateful to my supervisor Dr. Stig Munk-Nielsen from Aalborg University for his support and patience during the project. It was always a great pleasure to discuss different technical issues with him and gain knowledge from his experience. I am truly indebted and thankful to my supervisor Dr. Henrik Kragh from Grundfos A/S for his assistance and advice.

I owe sincere and earnest thankfulness to Dr. Sergio Busquets-Monge of Technical University of Catalonia, Spain for his help during development of the controller for the three-level inverter. His positive attitude and energy towards solving a problem are always source of inspiration for me.

I want to thank Dr. Kaiyuan Lu from Aalborg University for his constructive criticism, which improved my work on the active damping technique.

This dissertation would not have been possible without the support of the Electronics Hardware Team, Grundfos A/S, Bjerringbro, Denmark. I would like to thank Mr. Thorkild Kvisgaard, Hardware Technology Manager, Grundfos A/S for his endless support, technical as well as non-technical, during the project. Special thanks to Mr. Palle M. Obel, Mr. Bjarne Henriksen, and Mr. Niels H. Petersen for their help, feedback, and discussions concerning the development of hardware. I would like to acknowledge Mr. Klaus Bak for his fine PCB design, which helped me develop the three-level inverter without any difficulty.

It was of great joy to work with my friends Sanjay Kumar Chaudhary, Lajos Torok, Szymon Beczkowski, Ionut Trintis, Laszlo Mathe, Benoit Bidoggia, Pukar Mahat, and Jayakrishnan Pillai. It was exciting to have discussions with them, both academic as well as non-academic.

I also thank Mr. Walter Neumayr for helping in the purchase of the components. I would like to thank Mr. Jan Christiansen and Mr. Flemming Bo Larsen for their help in the lab on various occasions.

I would like to express my deepest gratitude to my parents and sisters for their unconditional love and support. This dissertation would have simply been impossible without them.

#### **Abstract**

Adjustable speed drives are considered as workhorse of industry due to various applications in different kind of industries. According to a market survey, low voltage drives are most profitable in the drive industries. The drive consists of a machine and a converter, which processes grid power and converts into usable power for the machine. The converter consists of active and passive components. The size, weight, and volume of the drive are decided by the passive components since they typically contribute to 75% of the weight and volume of the drive. Most popular topology for the low voltage drive is a six-pulse diode bridge rectifier followed by a two-level inverter. For these drives, the DC-link capacitor is the major contributor among the passive components.

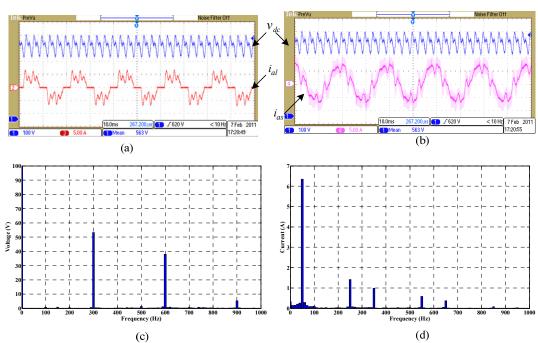

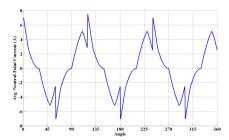

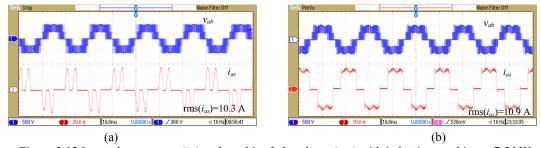

The DC-link capacitance value can be reduced in the drive systems known as small DC-link capacitor based drives. However, small DC-link capacitor based drive system shows instability while it is operated with high input line inductance at the operating points with high power. This thesis presents a simple, new active damping technique that can stabilize effectively the drive system at the unstable operating points offering greatly reduced input line current THD. The active damping terms introduced are linked directly to the DC-link voltage ripple, and damping voltage components are added to the input voltage of the drive machine. The stabilizing effect of the active damping terms is demonstrated for an induction machine drive system. To facilitate the design and analysis of the active damping terms, the effects of the active damping terms on the machine current and the DC-link voltage of the drive system are discussed. A design recommendation for the proposed active damping terms is given. Simulation and experimental results verifying the effectiveness of the new active damping method are presented.

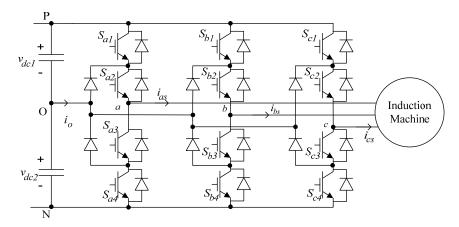

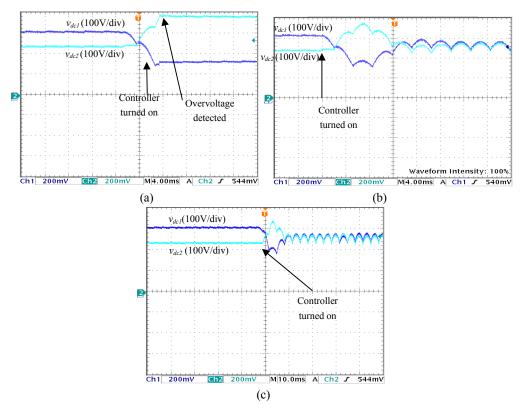

A Neutral-Point-Clamped (NPC) three-level inverter with small DC-link capacitors is selected as viable option for a two-level inverter in this thesis for low voltage applications. This inverter requires zero average neutral-point current for stable neutral-point potential. The small DC-link capacitors may not maintain the capacitor voltage balance even with zero neutral-point current due to nonlinearities present in the circuit. This requires a fast control of the neutral-point voltage. A simple carrier-based modulation strategy is proposed which allows modeling the neutral-point voltage dynamics as a continuous function of the power drawn from the converter. This model shows that the neutral-point current is proportional to the power drawn from the converter, and it enables the use of well established classical control theory for the neutral-point voltage controller design. A simple PI controller is designed for the neutral-point voltage balance based on this model. The design method for optimum performance is discussed. The implementation of the proposed modulation strategy and controller is very simple. The controller is implemented in a 7.5 kW induction machine based drive with only 14 µF DC-link capacitors. A fast and stable performance of the neutral-point voltage controller is achieved and verified by experiments.

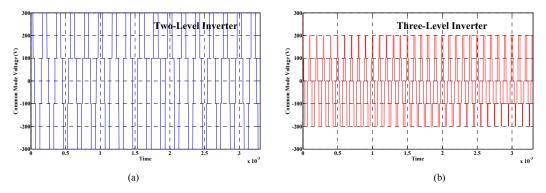

The performances of the two-level and three-level inverter based drive systems with small DC-link capacitors are compared. The shaft voltage, the common mode

voltage, the conducted emissions, and the efficiency of the two systems are compared since they are major factors which affect the size of the passive components in the drives. Although the three-level inverter requires higher number of active components as compared to the two-level inverter, it has been found that the three-level inverter is better solution than the two-level inverter even with small DC-link capacitors if the passive components size is concerned.

| Acknowledgement                                                                           | i   |

|-------------------------------------------------------------------------------------------|-----|

| Abstract                                                                                  | iii |

| Chapter 1 Introduction                                                                    | 1   |

| 1.1 Background and Motivation                                                             | 1   |

| 1.2 Objectives and Scope of the Project                                                   | 2   |

| 1.2.1 Objectives                                                                          | 2   |

| 1.2.2 Project Scope                                                                       |     |

| 1.2.3 Tools used                                                                          |     |

| 1.3 Major Contributions                                                                   | 3   |

| 1.4 Outline of the Thesis                                                                 | 4   |

| 1.5 List of Publications                                                                  | 5   |

| Chapter 2 Small DC-Link Capacitor Based Two-Level Converter                               | 7   |

| 2.1 Stability of Small DC-Link Capacitor Based Drive                                      | 8   |

| 2.1.1 The DC-link Current ( <i>i</i> <sub>dc</sub> )                                      |     |

| 2.1.2 Stability Analysis                                                                  |     |

| 2.1.2.1 Case 1: $(v_{dcs} = v_{dc})$                                                      |     |

| 2.2 Overview of Stabilization Techniques for the Small DC-Link Capacitor Based Drive      |     |

| 2.3 Detailed Drive Model                                                                  |     |

| 2.3.1 Linearized Induction Machine Equation                                               |     |

| 2.3.2 Detailed Drive Model                                                                |     |

| 2.4 Active Damping Terms                                                                  | 20  |

| 2.5 Effect of Damping Terms on the DC-Link Voltage and the Machine                        |     |

| Currents in Steady State                                                                  |     |

| 2.5.1 The Machine Current                                                                 |     |

| 2.5.2 The DC-link Current                                                                 |     |

| 2.6 Experimental and Simulation Results                                                   |     |

| •                                                                                         |     |

| 2.7 Summary and Conclusion                                                                |     |

| Chapter 3 Active Damping Technique in Vector-Controlled Drive                             |     |

| 3.1 Induction Machine Model in Stator Flux Oriented Reference Frame                       |     |

| 3.2 Controller and Estimator for Induction Machine in Stator Flux Oriente Reference Frame |     |

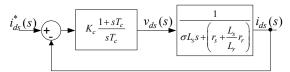

| 3.2.1 Current Controller Design                                                           |     |

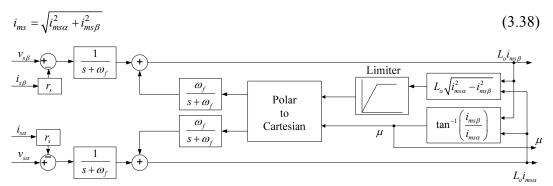

| 3.2.2 Speed and Flux Estimation                                                           |     |

| 3.3 Active Damping Technique in Closed Loop Controlled Drive                              | 45  |

| 3.4 Summary and Conclusion                                                                | 47  |

| Chapter 4 Three-Level Neutral-Point Clamped Inverter                                      | 49  |

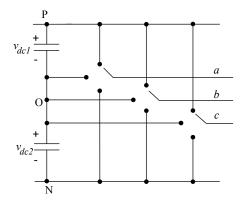

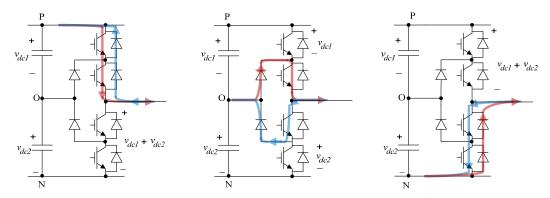

| 4.1 Principles of the NPC Three-Level Inverter                                            |     |

| 4.2             | Modulation Strategies for NPC Three-Level Inverter                                 |                 |

|-----------------|------------------------------------------------------------------------------------|-----------------|

| 4.2.            |                                                                                    |                 |

| 4.2.            |                                                                                    |                 |

| 4.2.            | 1                                                                                  |                 |

| 4.2.            | 4 Discontinuous PWM Techniques                                                     |                 |

|                 | .2.4.1 The 120 DPWM                                                                |                 |

| -               | 2.4.3 The 30° DPWM                                                                 |                 |

| 4.3             | Control of the Neutral-Point Voltage                                               | 62              |

| 4.3.            | S C                                                                                |                 |

| 4.3.            | 2 Neutral-Point Voltage Control by PWM Techniques                                  |                 |

| · -             | .3.2.1 Carrier-Based PWM Approach for Neutral-Point Current Analysis               |                 |

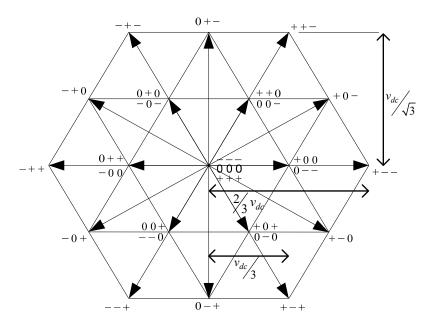

|                 | Space Vector PWM Based Approach for Neutral-Point Current Analysis                 |                 |

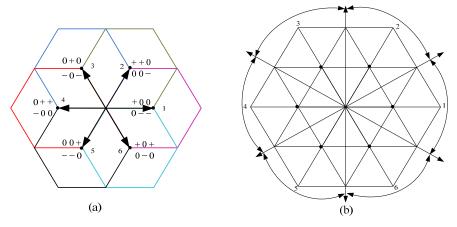

| 4.4             | PWM Techniques and Controllers with Zero Neutral-Point Current                     | 71              |

| 4.4.            | 1 PWM Techniques with Zero Neutral-Point Current                                   |                 |

| 4.4.<br>Tec     | 2 Neutral-Point Voltage Controller based on Zero Neutral-Point Current PWM hniques | 73              |

| 4.5             | Summary and Conclusion                                                             |                 |

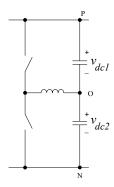

| Chapter         | Three-level Inverter with Small DC-link Capacitor                                  | 75              |

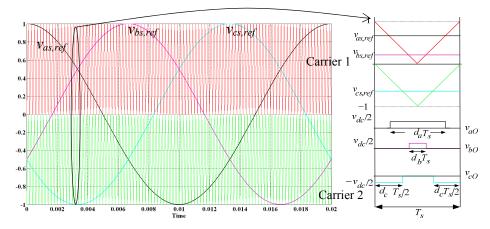

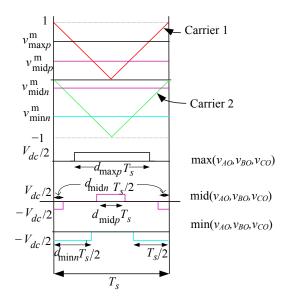

| 5.1             | Carrier-Based PWM for Zero Neutral-Point Current                                   | 76              |

| 5.2             | Model of Neutral-Point Voltage Dynamics                                            | 79              |

| 5.3             | Controller for Neutral-Point Voltage Balance                                       | 82              |

| 5.4             | Small DC-Link Capacitors Based Converter                                           |                 |

| 5.5             | Experimental Results                                                               | 86              |

| <b>5.6</b>      | Summary and Conclusion                                                             | 90              |

| Chapter         | · 6 Performance Comparison of Two-Level and Three-Level Inverte                    | r               |

| with Sm         | all DC-Link Capacitors                                                             | 91              |

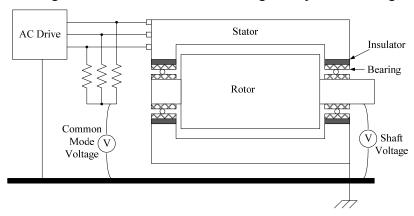

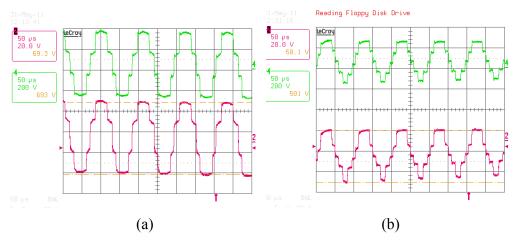

| <b>6.1</b> 6.1. | Common Mode Voltage and Shaft Voltage                                              | <b>92</b><br>94 |

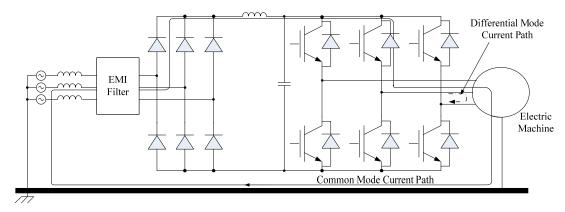

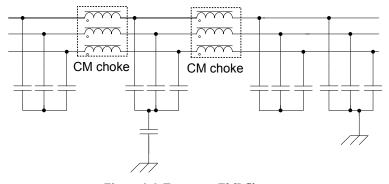

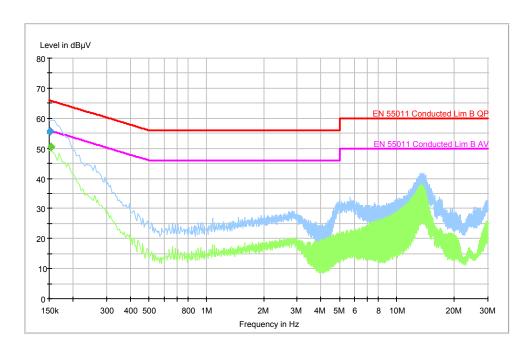

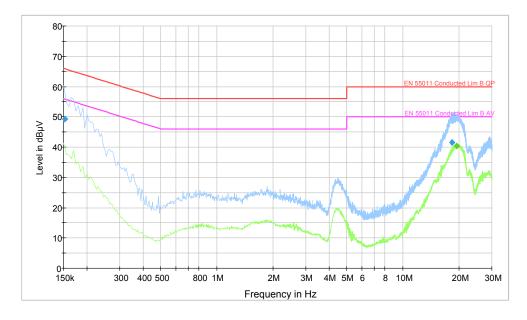

| 6.2             | Electromagnetic Interference (EMI) Measurements                                    | 96              |

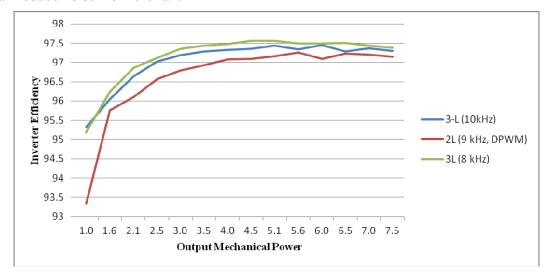

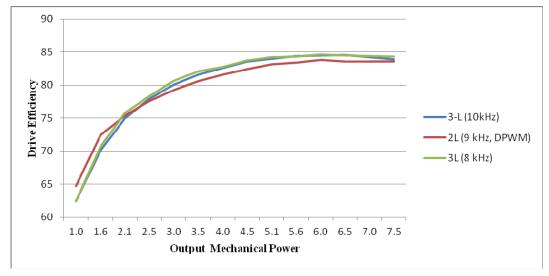

| 6.3             | Efficiency Measurements                                                            | 98              |

| 6.4             | Summary and Conclusion                                                             | .100            |

| Chapter         | 7 Conclusion and Future Work                                                       | 103             |

| Referen         | ces                                                                                | 105             |

| Append          | ix A                                                                               | 109             |

| Annend          | iv R                                                                               | 111             |

## Chapter 1

## Introduction

## 1.1 Background and Motivation

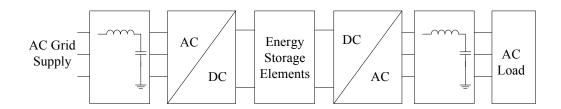

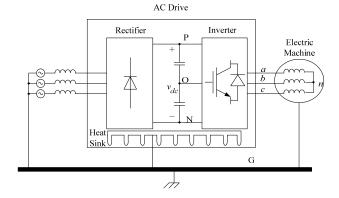

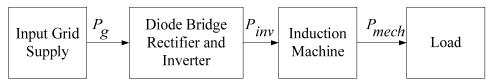

Adjustable Speed Drives (ASD) are extensively used in various industries like traction; process industry; and heating, ventilation, and air-conditioning (HVAC) etc. They require controlled frequency and voltage magnitude of AC supply for easy control. However, the available power is the grid power, which has AC supply of constant amplitude and frequency. Grid power is converted to controlled AC power using AC to AC converter for electric drive applications. An typical AC to AC converter can have following parts as shown in Figure 1-1.

- 1. Input Filters

- 2. Power Processing Section (AC-AC conversion)

- a. AC to DC Rectification Stage

- b. Energy Storage Elements after Rectification Stage

- c. DC to AC Inversion Stage

- 3. Output Filter

Each part can consist of active or passive components. Input filter, energy storage elements after rectification stage, and output filter consist of only passive components such as inductors, capacitors etc. The DC to AC inversion stage is made of active components such as insulated gate bipolar transistors (IGBT), microcontrollers, etc. The AC to DC rectification stage may consist of active or passive components and it depends on the topology. If AC to DC rectifier is based on diode bridge rectification, it consists of diodes and transformers (for medium and high power applications). On the other hand, if the rectifier is realized by a power electronics converter, it consists of active components.

According to a market research on AC drives, low power drives (5 to 40 kW) segment was the most profitable segment in 2010 [87]. The most common topology for this power level is a six-pulse diode bridge rectifier stage followed by a two-level inverter. This topology has passive components, which typically contribute to 75% of the size and weight of a power inverter [99]. The passive components;

Figure 1-1 Different Parts of an ASD.

capacitors, magnetics, and thermal management components; are the major parts of the drive system [99].

The evolution of power semiconductor devices, which are used as active components, is rapid. Thyristors are the first generation of power semiconductor devices and they were introduced in market in 1958 for high power applications [41]. They are dominating high power low frequency applications even nowadays. Some 35 years ago, Power MOSFETs were introduced by International Rectifiers. They made linear power supplies, which used bipolar junction transistors, obsolete and replaced them with switched mode power supplies [91]. Few years later, IGBT was introduced, which had revolutionized the power electronics industry. It has been estimated that a cumulative cost saving of \$15.8 trillion for over the last 20 years has been achieved by this technology [92]. During past years, from the 1<sup>st</sup> generation to the 5<sup>th</sup> generation of IGBT, overall losses are reduced to one third [18]. Recent developments show that the wide band gap material such as GaN and SiC can help increase in efficiency of the converters [86], [97]. However, the passive components evolution is slow. It can be seen from Fig. 13 in [99] that the highest contribution to the weight and volume of the drive is from capacitors. In voltage fed inverters such as two-level and three-level inverters, which are most common converter for drive applications, research has been focused on reducing the size of capacitors [9], [14], [26], [67], [75], [82]. However, small DC-link capacitor based drive system exhibits unstable operating point while it is operated with high input line inductance at operating points with high power. The instability of the operating point can be explained if the load connected to the drive system is considered as constant power load. Constant power load acts as negative impedance and can cause unstable operating point at high power [75].

### 1.2 Objectives and Scope of the Project

#### 1.2.1 Objectives

The main objectives of this project were:

1. To provide active damping for Small DC-link capacitor based ASD

The small DC link capacitor based drive may show unstable operating point at high power level. This unstable operating point may cause poor THD at the input line current and high voltage oscillation at the DC-link. A stabilization technique is required.

2. To reduced passive components size and volume in a three-level inverter based drive

The three-level inverter generates less electromagnetic interference. This reduces the requirement of EMI filter in the three-level inverter. However, the requirement for DC-link capacitor size is higher as compared to the two-level inverter. This depends on the modulation strategies. A modulation strategy is required to minimize the size of DC-link capacitor in the three-level inverter.

#### 1.2.2 Project Scope

This project focuses on the reduction of passive components in an adjustable speed drive. The induction machine based drive is considered for experiments. However, the developed methods or techniques in the project should be in such a way that it can also be used for a permanent magnet synchronous machine.

The low voltage drives are considered in this project and the power range is 5 kW -40 kW.

#### 1.2.3 Tools used

Following softwares are used during this project

- 1. MATLAB® ver. 7.10.0.499 (R2010a): MATLAB is used for various numerical calculations in this project.

- 2. Simulink ver. 7.5 (R2010a): This is a dynamic system simulation tool for MATLAB<sup>®</sup>. In this project, Simulink is used for simulation of various controllers and dynamics systems.

- 3. Plecs ver. 3.1.1: This simulation tool is used for simulation of the electrical components.

- 4. Code composer studio ver. 3.3.59.4: This is a tool for programming the Texas Instrument's processors. In this project TMS320F28335 digital signal controller is used for implementing various control algorithms for the inverters. Code composer studio is used as a development platform for this digital signal controller.

- 5. Altium Designer 6: This software is used to design different printed circuit boards (PCB) during this project.

### 1.3 Major Contributions

The main contributions of this project are listed below:

1. A detailed model of the drive system is presented. This detailed model is linearized about an operating point for stability analysis of the operating point since the system is nonlinear.

- 2. It has been shown that the small DC-link capacitor based drive exhibits stable limit cycle at unstable operating point. This limit cycle causes high DC-link voltage oscillation and poor input line current THD.

- 3. A simple active damping technique is proposed in this thesis to stabilize the unstable operating point. This helps improving the input line current THD. The active damping terms add harmonic component of the DC-link voltage to the stator voltage of machine.

- 4. The effect of active damping terms on the machine current is analyzed and a design recommendation is derived based on the analysis.

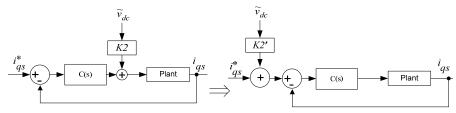

- 5. In a drive with vector control, the damping term can be added to a current reference command of the machine. Using simple block diagram reduction techniques, a relationship between damping terms added to the machine voltage and damping terms added to the machine current reference is established.

- 6. A three-phase neutral-point clamped three-level inverter requires high DC-link capacitance value due to nonzero neutral-point current. A new modulation strategy, which adds a scaled common mode offset to the three-phase voltage reference command, is developed.

- 7. A simple, first-order continuous model, which defines the dynamics of the neutral-point voltage, is derived for the proposed modulation strategy. Using this model, linear control theories can be applied to design a fast and robust neutral-point voltage controller.

#### 1.4 Outline of the Thesis

The organization of the thesis is given as follows:

Chapter 2 deals with small DC-link capacitor based two-level inverter. It presents a detailed model of the drive system. Since small DC-link capacitor based system may have unstable operating point, an active damping technique is proposed in this chapter to stabilize the operating point. The active damping terms add harmonic components of the DC-link voltage to the machine stator voltage. This affects the harmonic components of the machine current. Analysis of the harmonic components of the machine current is also presented in the chapter and this analysis leads to design recommendations for selecting active damping terms. Simulation and experimental results are also presented for open loop *V/f* controlled drive to support the analysis.

Chapter 3 presents with the closed loop control of the small DC-link capacitor based two-level inverter. The active damped technique can be implemented in a closed loop system. A stator flux oriented closed loop control drive is considered. It has been discussed that the active damping term can be added to either the stator voltage command or the stator current reference. A relationship between these two methods is presented in this chapter.

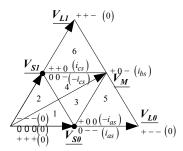

A neutral-point clamped (NPC) three-level inverter can be a viable option for the DC-AC inverter. This topology helps in reducing size of the passive components in the drive. Chapter 4 presents an overview of the NPC three-level inverter. In this chapter, different modulation strategies and neutral-point voltage controllers, which are proposed in the literature, are discussed in brief. It has been found that the design of the neutral-point voltage controller for small DC-link capacitor based NPC three-level inverter is complicated due to discontinuous model of the system.

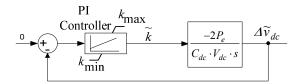

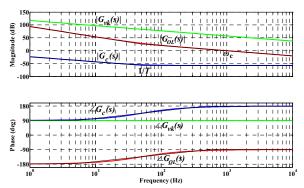

Chapter 5 discusses a new modulation strategy for the NPC three-level inverter. This modulation strategy is based on the scaled common mode offset approach. With this modulation strategy, a simple first-order continuous equation is derived for neutral-point voltage dynamics. This continuous equation enables the use of classical control theory for the neutral-point voltage controller. In this chapter, a proportional-integral (PI) controller design is presented and it is verified by the experimental results.

Chapter 6 shows performance comparison for the two-level and the three-level inverter based on small DC-link capacitors. The common mode voltage, shaft voltage, conducted emission, and efficiency are compared since they are main factors for passive components in an inverter. It has been shown that the three-level inverter with small DC-link capacitors can reduce the size of passive components by increasing the efficiency and reducing the conducted emission.

Chapter 7 concludes the thesis with mention of future work related to the work presented in the thesis.

#### 1.5 List of Publications

#### **Conference Publications**

- 1. Maheshwari, R.; Munk-Nielsen, S.; Henriksen, B.; Obel, P.M.; Kragh, H.; , "Active damping technique for small DC-link capacitor based drive system," *Industrial Electronics (ISIE), 2010 IEEE International Symposium on*, vol., no., pp.1205-1209, 4-7 July 2010.

- Maheshwari, R.; Munk-Nielsen, S.; , "Closed loop control of active damped small DC-link capacitor based drive," *Energy Conversion Congress and Exposition (ECCE)*, 2010 IEEE , vol., no., pp.4187-4191, 12-16 Sept. 2010.

- 3. Maheshwari, R.; Munk-Nielsen, S.; , "Performance analysis of active damped small DC-link capacitor based drive for unbalanced input voltage supply," *Power Electronics and Applications (EPE 2011), Proceedings of the 2011-14th European Conference on*, vol., no., pp.1-10, Aug. 30 2011-Sept. 1 2011.

- 4. Maheshwari, RamKrishan; Munk-Nielsen, Stig; Busquets-Monge, Sergio; , "Neutral-point current modeling and control for Neutral-Point Clamped three-level converter drive with small DC-link capacitors," *Energy*

- Conversion Congress and Exposition (ECCE), 2011 IEEE, vol., no., pp.2087-2094, 17-22 Sept. 2011.

- Maheshwari, R.; Munk-Nielsen, S.; Busquets-Monge, S.; "EMI performance comparison of two-level and three-level inverters in small dc-link capacitors based motor drives," Industrial Electronics (ISIE), 2012 IEEE International Symposium on , vol., no., pp.652-657, 28-31 May 2012.

#### **Transaction Publications**

6. Maheshwari, R.; Munk-Nielsen, S.; Busquets-Monge, S.; , "Design of Neutral-Point Voltage Controller of a Three-level NPC Inverter with Small DC-Link Capacitors," Industrial Electronics, IEEE Transactions on , vol.PP, no.99, pp.1, 0. doi: 10.1109/TIE.2012.2202352

#### Transaction Publications (under review)

- 7. Maheshwari, R.; Munk-Nielsen, S.; Kaiyuan Lu; , "An Active Damping Technique for Small DC-Link Capacitor Based Drive System," under review in *Transaction of Industrial Informatics*.

- 8. Maheshwari, R.; Munk-Nielsen, S.; , "Performance Analysis of Active Damped Small DC-link Capacitor Based Drive for Unbalanced Input Voltage Supply," under review in *EPE journal*.

## Chapter 2

Converter

## Small DC-Link Capacitor Based Two-Level

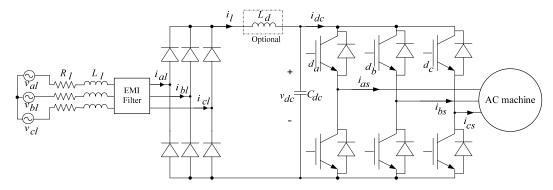

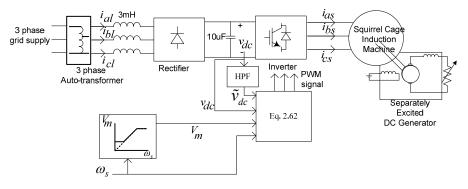

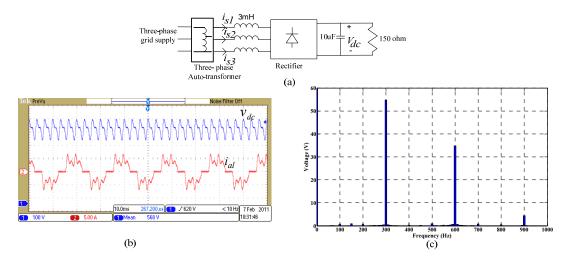

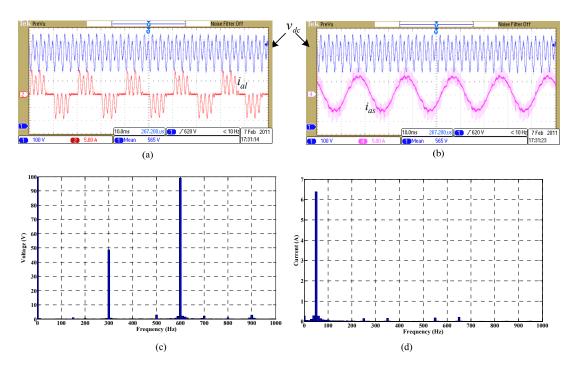

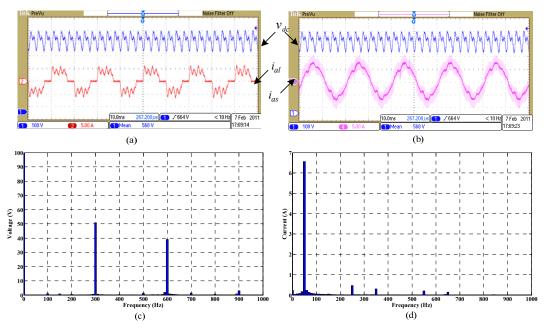

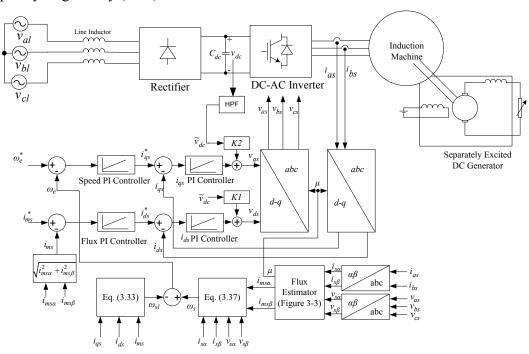

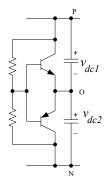

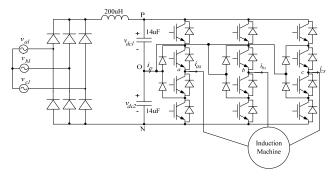

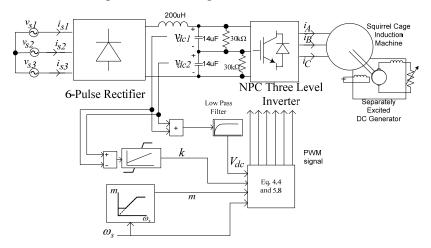

A typical adjustable speed drive consists of a six-pulse diode bridge rectifier followed by a two-level inverter with a DC-link filter as an in-between stage as shown in Figure 2-1. The DC-link filter consists of a DC-link capacitor and an optional DC-link inductor. The DC-link capacitor (generally an electrolytic capacitor) and the DC-link inductor contribute to passive components in a drive besides high frequency EMI filters. The poor reliability and cost of the electrolytic capacitor has been a major driving force to reduce the value of capacitance and use film capacitors [9]. These kinds of drives are referred as slim DC-link or small DC-link drives.

The six-pulse diode bridge rectifier output voltage consists of harmonic components of sixth multiple of line frequency. These frequency components are filtered by DC-link filter if a high value of DC-link capacitor is used and the DC-link voltage has constant value. Since small DC-link capacitor based drive has small value of DC-link capacitor, the DC-link voltage has harmonic components of sixth multiple of line frequency. In other words, the DC-link voltage in the small DC-link capacitor based drive has oscillations. These oscillations may cause unstable operating point of the drive for constant power load. If the load is assumed as constant power load, the current drawn by the DC-AC inverter decreases with increase in the DC-link voltage and vice versa. The load then can be considered as a load with negative impedance and can be the cause of unstable operating point.

Section 2.1 describes the instability of the operating point using a small-signal model. An overview of the methods to stabilize the operating point available in the literature is given in Section 2.2. An improved stabilization technique, which is based on the detailed model of the drive system, is presented in this chapter. The detailed model is presented in Section 2.3 followed by the proposed stabilization technique which is described in Section 2.4. The stabilization technique affects the input and output currents of the drive which is explained in Section 2.5. The stabilization technique is verified by simulation and experiments for an induction machine based drive with open loop V/f control, and the results are presented in Section 2.6.

Figure 2-1 Adjustable speed drive topology.

## 2.1 Stability of Small DC-Link Capacitor Based Drive

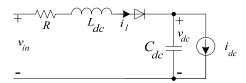

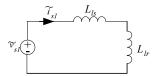

A typical adjustable speed drive (ASD) consists of an AC to DC converter followed by a DC-link capacitor and a DC to AC inverter which drives an AC machine. The AC to DC converter is realized by the six-pulse diode bridge rectifier, and a two-level inverter is used as the DC to AC inverter as shown in Figure 2-1. To analyze the stability of the system, a simple model is used where the two-level inverter and the AC machine is modeled as a current source as shown in Figure 2-2. The equivalent resistance (R) and the equivalent DC-link inductance ( $L_{dc}$ ), as shown in Figure 2-2, are related to the DC-link inductance ( $L_{dl}$ ), the source resistance ( $R_{ll}$ ), and the source inductance ( $L_{ll}$ ), which include the resistance and inductance offered by the grid supply together with the impedance offered by any series choke between grid and rectifier (Figure 2-1), as given by

$$R = 2R_l + \frac{3\omega_g L_l}{\pi}$$

,  $L_{dc} = L_d + 2L_l$  (2.1)

where  $\frac{3\omega_g L_l}{\pi}$  corresponds to the nonohmic voltage drop due to commutation in the diodes.  $\omega_g$  is the frequency of the supply voltage.

Figure 2-2 Equivalent model of the drive.

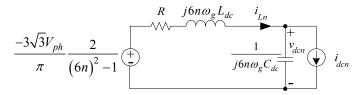

The input voltage  $v_{in}$  in Figure 2-2 can be approximated by

$$v_{in} = \frac{3\sqrt{3}V_{ph}}{\pi} \left( 1 - \sum_{n=1}^{\infty} \frac{2}{(6n)^2 - 1} \cos(6n\omega_g t) \right)$$

(2.2)

where  $V_{ph}$  represents the amplitude of the three phase input voltages  $v_{al}$ ,  $v_{bl}$ , and  $v_{cl}$  to the rectifier as shown in Figure 2-1.

The equivalent circuit shown in Figure 2-2 has two state variables (the inductor current  $(i_l)$  and the DC-link voltage  $(v_{dc})$ ) and two inputs (the input voltage  $(v_{in})$  and equivalent DC-link current  $(i_{dc})$ ). The equations defining the dynamics of the state variables  $i_l$  and  $v_{dc}$  are given as

$$L_{dc} \frac{di_l}{dt} + Ri_l = v_{in} - v_{dc}$$

$$C_{dc} \frac{dv_{dc}}{dt} = i_l - i_{dc}$$

$$i_l \ge 0$$

(2.3)

It can be seen from (2.3) that the system dynamics depends on the DC-link current  $(i_{dc})$ , which in turn depends on the duty cycle of the IGBTs in the inverter and machine current. An equation for  $i_{dc}$ , as a function of the machine currents, is derived in the next subsection.

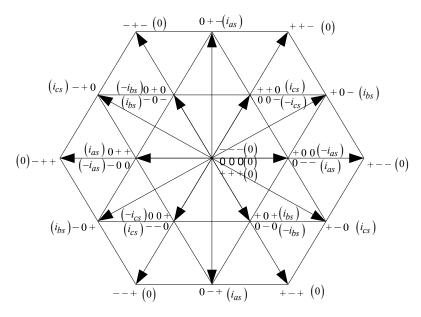

#### 2.1.1 The DC-link Current ( $i_{dc}$ )

It can be seen from Figure 2-1 that the DC-link current is equal to the sum of the machine phase currents if those particular phases are connected to the top DC-link terminal. The time for which a particular phase is connected to the top DC-link terminal is decided by the duty cycles of the top IGBTs of the two-level converter. An expression of the DC-link current averaged over a switching period is given as

$$i_{dc} = d_a i_{as} + d_b i_{bs} + d_c i_{cs} (2.4)$$

where  $d_a$ ,  $d_b$ , and  $d_c$  are the duty cycles of the top IGBTs, and  $i_{as}$ ,  $i_{bs}$ , and  $i_{cs}$  are the machine phase currents as shown in Figure 2-1.

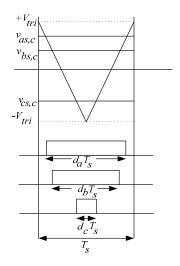

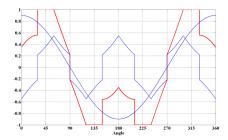

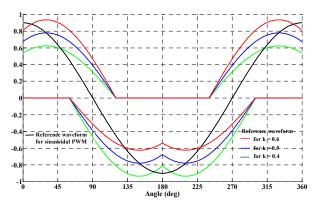

Typically, carrier-based modulation is used for generating the duty cycles for the IGBT in the ASDs. The duty cycle is generated by comparing the triangular carrier wave by the control signals as shown in Figure 2-3 [5]. Inputs to the modulator are the control voltages ( $v_{as,c}$ ,  $v_{bs,c}$ , and  $v_{cs,c}$ ) of different phases. Using symmetry of triangles in Figure 2-3, the duty cycles for the corresponding phases can be expressed as

$$d_{a} = \frac{V_{tri} + v_{as,c}}{2V_{tri}}; d_{b} = \frac{V_{tri} + v_{bs,c}}{2V_{tri}}; d_{c} = \frac{V_{tri} + v_{cs,c}}{2V_{tri}}$$

(2.5)

where  $V_{tri}$  is the peak value of the carrier wave signal of the modulator.

Figure 2-3 PWM duty cycle generation.

Replacing (2.5) in (2.4) and assuming  $i_{as}+i_{bs}+i_{cs}=0$ , the DC-link current can be expressed as

$$i_{dc} = \frac{1}{2V_{tri}} \left( v_{as,c} i_{as} + v_{bs,c} i_{bs} + v_{cs,c} i_{cs} \right)$$

(2.6)

The control voltages supplied to the modulator are proportional to the ratio of the required inverter pole voltages of their respective phases and the DC-link voltage as given by

$$v_{ks,c} = v_{ks} \frac{2V_{tri}}{v_{dcs}}$$

;  $k = 1, 2, 3$  (2.7)

where  $v_{ks}$  is the fundamental component of the inverter pole voltage to be applied and  $v_{dcs}$  is the sensed DC-link voltage.

By using (2.6) and (2.7),  $i_{dc}$  can be expressed as

$$i_{dc} = \frac{1}{v_{dcs}} \left( v_{as} i_{as} + v_{bs} i_{bs} + v_{cs} i_{cs} \right)$$

(2.8)

The machine variables  $v_{as}$ ,  $v_{bs}$ ,  $v_{cs}$ ,  $i_{as}$ ,  $i_{bs}$ , and  $i_{cs}$  can be transformed from the stationary reference frame to an arbitrary rotating reference frame using the transformation as described in Appendix A. The equation for  $i_{dc}$  in terms of the variables referred to an arbitrary rotating dq-reference frame can be given by

$$\begin{split} i_{dc} &= \frac{1}{v_{dcs}} \begin{bmatrix} v_{as} & v_{bs} & v_{cs} \end{bmatrix} \begin{bmatrix} i_{as} \\ i_{bs} \\ i_{cs} \end{bmatrix} \\ i_{dc} &= \frac{1}{v_{dcs}} \begin{bmatrix} v_{ds} & v_{qs} \end{bmatrix} \begin{bmatrix} 1 & -0.5 & -0.5 \\ 0 & 0.866 & -0.866 \end{bmatrix} \begin{bmatrix} 1 & 0 \\ -0.5 & 0.866 \\ -0.5 & -0.866 \end{bmatrix} \begin{bmatrix} i_{ds} \\ i_{qs} \end{bmatrix} \\ i_{dc} &= \frac{1}{v_{dcs}} \begin{bmatrix} v_{ds} & v_{qs} \end{bmatrix} \begin{bmatrix} 1.5 & 0 \\ 0 & 1.5 \end{bmatrix} \begin{bmatrix} i_{ds} \\ i_{qs} \end{bmatrix} \end{split}$$

$$i_{dc} = \frac{1}{v_{dcs}} \frac{3}{2} \left( v_{ds} i_{ds} + v_{qs} i_{qs} \right) = \frac{p_e}{v_{dcs}}$$

(2.9)

where  $v_{ds}$  and  $v_{qs}$  are the stator d- and q-axis voltages, and  $i_{ds}$  and  $i_{qs}$  are the stator d- and q-axis currents. It can be noted from (2.9) that the term  $\frac{3}{2}(v_{ds}i_{ds}+v_{qs}i_{qs})$  is the electrical power drawn by the machine expressed in terms of the dq-axes machine voltages and currents and is denoted as  $p_e$ .

#### 2.1.2 Stability Analysis

The DC-link current is an input to the equivalent system shown in Figure 2-2. By substituting the DC-link current (2.9) into (2.3), the system dynamics can be expressed as

$$L_{dc} \frac{di_l}{dt} + Ri_l = v_{in} - v_{dc}$$

$$C_{dc} \frac{dv_{dc}}{dt} = i_l - \frac{p_e}{v_{dcs}}$$

$$i_l \ge 0$$

(2.10)

The dynamic equations given in (2.10) require the sensed DC-link voltage ( $v_{dcs}$ ) which can be equal to the instantaneous DC-link voltage ( $v_{dc}$ ) or the average DC-link voltage ( $V_{dc}$ ). If the instantaneous DC-link voltage is used, the load to the rectifier acts as a negative impedance, on the other hand, if the average DC-link voltage is used, it does not cause negative impedance for the rectifier, and the system is always stable. For both cases, the system stability analyses are shown in the following.

#### 2.1.2.1 Case 1: $(v_{dcs}=v_{dc})$

The system dynamic equations for  $v_{dcs} = v_{dc}$  are given as

$$L_{dc} \frac{di_l}{dt} + Ri_l = v_{in} - v_{dc}$$

$$C_{dc} \frac{dv_{dc}}{dt} = i_l - \frac{p_e}{v_{dc}}$$

$$i_l \ge 0$$

(2.11)

The system dynamic equations are nonlinear. To analyze the stability of the system, the linearized equations are required about an operating point. Considering only the first-order terms of the Taylor series expansion of (2.11), the linearized equations for the system are given by

$$L_{dc} \frac{d\tilde{i}_{l}}{dt} + R\tilde{i}_{l} = \tilde{v}_{in} - \tilde{v}_{dc}$$

$$C_{dc} \frac{d\tilde{v}_{dc}}{dt} = \tilde{i}_{l} - \frac{\tilde{p}_{e}}{V_{dc}} + \frac{P_{e}}{V_{dc}^{2}} \tilde{v}_{dc}$$

(2.12)

where " $\sim$ " indicates the small-signal value, and capital letter denotes the quiescent value of that particular variable or input. Using (2.12), the transfer function from the inductor current ( $\tilde{i}_l$ ) to the input voltage ( $\tilde{v}_{in}$ ) may be given as

$$\frac{\tilde{i}_{l}(s)}{\tilde{v}_{in}(s)} = \frac{C_{dc}s - \frac{P_{e}}{V_{dc}^{2}}}{L_{dc}C_{dc}s^{2} + \left(RC_{dc} - \frac{L_{dc}P_{e}}{V_{dc}^{2}}\right)s + 1 - \frac{RP_{e}}{V_{dc}^{2}}}$$

(2.13)

and the characteristic equation for the system becomes

$$L_{dc}C_{dc}s^{2} + \left(RC_{dc} - \frac{L_{dc}P_{e}}{V_{dc}^{2}}\right)s + \left(1 - \frac{RP_{e}}{V_{dc}^{2}}\right) = 0$$

(2.14)

The poles related to the system may be found by solving (2.14). Equation (2.14) is a quadratic equation, and the coefficient of 's' in the equation should be positive for stable poles with negative real part for the stable operating point of the system which gives a criterion

$$RC_{dc} - \frac{L_{dc}P_e}{V_{dc}^2} > 0$$

$$\frac{R}{L_{dc}} > \frac{P_e}{C_{dc}V_{dc}^2}$$

(2.15)

If the criterion (2.15) is not satisfied, the system operating point about which the equations are linearized will be unstable. At high power with small DC-link capacitance, the term  $\frac{P_e}{C_{dc}V_{dc}^2}$  may become more than  $\frac{R}{L_{dc}}$  and results in an unstable

operating point. Generally an unstable operating points exhibit limit cycles. This can be analyzed using the phase plane analysis. In the following, the phase plane analysis [3] is presented for the unstable operating point of the system.

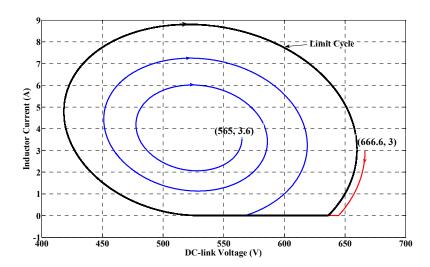

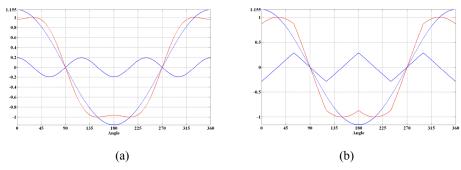

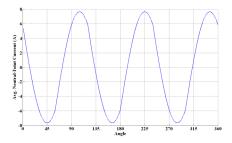

Let us consider a system with parameters given in Table 2-1. The operating point of the system is given in Table 2-2. Using (2.14), the poles for the linearized system about this operating point can be calculated as  $230 \pm j4063.2$ , which correspond to an unstable operating point. The phase portraits of the system for two different initial conditions ((565 V, 3.6 A) & (666.6 V, 3 A)) are plotted as shown in Figure 2-4. It can be seen form Figure 2-4 that the trajectory of the states is approaching towards the limit cycle in steady state. Figure 2-4 shows that the operating points, which are used as the initial conditions for the system, are not stable since the trajectory of the states are moving away from those initial conditions. The trajectory will tend to infinity if negative inductor current ( $i_l$ ) is allowed. The diodes are preventing negative inductor current, and it results in a stable limit cycle.

Table 2-1 System Parameters

| $L_{dc}$ | 6 mH  |

|----------|-------|

| $C_{dc}$ | 10 μF |

| R        | 1 Ω   |

Table 2-2 System Operating Point

| $P_e$    | 2 kW  |

|----------|-------|

| $V_{dc}$ | 565 V |

Figure 2-4 Phase portrait of the sytem.

#### 2.1.2.2 Case 2: $(v_{dcs}=V_{dc})$

Using (2.10), the system dynamic equations for  $v_{dcs}=V_{dc}$  are given as

$$L_{dc} \frac{di_l}{dt} + Ri_l = v_{in} - v_{dc}$$

$$C_{dc} \frac{dv_{dc}}{dt} = i_l - \frac{p_e}{V_{dc}}$$

(2.16)

By comparing (2.16) to (2.11), it can be seen that (2.16) is a linear equation since  $V_{dc}$ , which is not varying, is the average value of the DC-link voltage. Using (2.16), the transfer function from the inductor current  $(i_l)$  to the input voltage  $(v_{in})$  may be given as

$$\frac{i_l(s)}{v_{in}(s)} = \frac{C_{dc}s}{L_{dc}C_{dc}s^2 + RC_{dc}s + 1}$$

(2.17)

and the characteristic equation for the system is given by

$$L_{dc}C_{dc}s^2 + RC_{dc}s + 1 = 0 (2.18)$$

which is a characteristic equation for a second-order RLC filter. The system is

always stable in this case since all the coefficients of the characteristic equation are positive, and the poles will never be in the right half s-plane.

## 2.2 Overview of Stabilization Techniques for the Small DC-Link Capacitor Based Drive

The system stability is analyzed in the previous section. It is shown that the system operating point may become unstable if the instantaneous value of the DC-link voltage is used for calculating the duty cycles. Different stabilization techniques are presented in the literature. The main idea behind the stabilizing techniques discussed in literature is to vary the power drawn from the rectifier in proportional to the DC-link voltage variation [14], [26], [67], [75]. However, they differ in implementation of this idea.

The stabilization technique presented in [75] suggests to vary the torque produced by the machine in proportional to the DC-link voltage variation, which in turn will vary the power drawn by the machine in proportional to the DC-link voltage variation. In other words, the power drawn from the rectifier will be proportional to the DC-link voltage variation. The torque is controlled by controlling the machine current in this method. This implementation demands a fast control of the machine current since the torque reference command vary in proportional to the DC-link voltage variation having frequency equal to six times the grid frequency. The performance of this method depends on the current controller bandwidth.

A similar approach of stabilizing the operating point is presented in [67]. The torque producing current component of the machine is added to a current command, which is proportional to the DC-link voltage variation. It is shown that the characteristic equation of (2.18) for the system can be achieved by this method, where the poles of the linearized system are decided by the system parameters only, independent of the system operating point. However, same performance can be achieved by simply using the average DC-link voltage for duty cycle calculations as proposed in the previous section. In this case, the damping of the system is decided by the resistance present in the system. It is also shown in [67] that the damping of the system can be increased further, but it requires the knowledge of parameters (R,  $L_{dc}$ , and  $C_{dc}$ ) of the system. However, the performance of this method also depends on the current controller bandwidth.

The stabilizing techniques presented in [67] and [75] require the current controller, which can response to the 300 Hz variation present in DC-link voltage. If a current controller with a low bandwidth is used in the drive system, a stabilizing technique where the torque producing voltage reference command is modified, can be used as proposed in [14] and [26]. In this technique, the voltage reference is added to a voltage component proportional to the DC-link voltage variation. Since this component is added to the output of the current controller, current controller bandwidth should be low enough not to respond to components of 300 Hz. The generation of the stabilizing voltage component added to the torque producing voltage reference command requires a high-pass filter. The bandwidth of the high-

pass filter depends on the operating point and the parameters of the system. Thus it requires online tuning for the optimal performance if the system parameters are changed. This situation can occur very often if the drive system is used for different kinds of grids.

A new technique for the stabilizing the operating point is proposed in this chapter. This technique adds voltage components, which is proportional to the high frequency variation in the DC-link voltage, to the machine terminal voltages. The voltage components are referred to as active damping terms, since they stabilize the unstable operating point while actively damping the system. The implementation of the damping terms is independent of the system parameter change. These terms are derived using a detailed linearized model of the machine and (2.10). The detailed linearized model of the drive system is presented in the next section followed by the discussion of the active damping terms in Section 2.4.

#### 2.3 Detailed Drive Model

It can be seen from (2.9) that the DC-link current depends on the machine voltages and the machine currents, which are governed by the induction machine model. The detailed model of an induction machine [8], which is used as the AC machine in the drive, is presented in the following.

#### 2.3.1 Linearized Induction Machine Equation

The three-phase induction machine has constant magnitude field flux, but it is revolving in the space in steady state. So the dynamic model of induction machine is somewhat complicated. A model presented in [8] is used in this section. The assumptions made for the induction machine model are

- The distribution of magneto motive force in air gap is sinusoidal.

- The effect of iron losses and saturation are neglected.

- The zero sequence components do not exist.

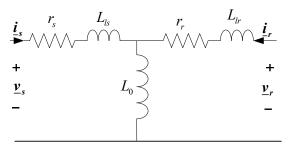

Based on the equivalent circuit shown in Figure 2-5, the stator voltage equation in the stationary stator reference frame is given as

$$r_{s}\underline{\boldsymbol{i}}_{s} + L_{s}\frac{d}{dt}\underline{\boldsymbol{i}}_{s} + L_{o}\frac{d}{dt}(\underline{\boldsymbol{i}}_{r}e^{j\varepsilon}) = \underline{\boldsymbol{v}}_{s}(t)$$

(2.19)

and rotor voltage equation in rotor reference frame is given as

$$r_{r}\underline{\mathbf{i}}_{r} + L_{r}\frac{d}{dt}\underline{\mathbf{i}}_{r} + L_{o}\frac{d}{dt}(\underline{\mathbf{i}}_{s}e^{-j\varepsilon}) = \underline{\mathbf{v}}_{r}(t)$$

(2.20)

where  $L_s$  is the stator inductance and equals to the sum of the stator leakage inductance  $(L_{ls})$  and the mutual inductance  $(L_o)$   $(L_s = L_{ls} + L_o)$ , and  $L_r$  is the rotor inductance and equals to the sum of the rotor leakage inductance  $(L_{lr})$  and the mutual inductance  $(L_o)$   $(L_s = L_{lr} + L_o)$  [8]. The space phasor quantities are set by bar under

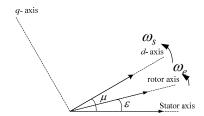

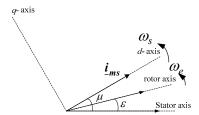

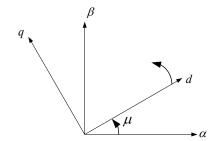

letter ('\_'), e.g.,  $\underline{v}_s$ ,  $\underline{i}_s$ ,  $\underline{v}_r$  etc. s and r subscripts are used for the stator and rotor variables, respectively.  $\varepsilon$  is the angle between the stator and rotor axis.  $r_s$  and  $r_r$  are the stator and rotor resistances.  $\mu$  is the angle between the stator axis and the d- axis as shown in Figure 2-6.

Figure 2-5 Induction machine equivalent circuit

The dynamic equations of the three-phase AC machine are expressed in a synchronously rotating dq reference frame because of easy control. The details will be discussed in the next chapter.

Figure 2-6 Synchronously rotating reference frame

The stator voltage and current phasors in the synchronously rotating reference frame can be expressed in terms of the stator voltage and current phasors in the stator reference frame and the angle between them as

$$v_{ds} + jv_{qs} = \underline{v}_s e^{-j\mu} \tag{2.21}$$

$$i_{ds} + ji_{qs} = \underline{i}_s e^{-j\mu} \tag{2.22}$$

Similarly, the rotor voltage and current phasors in the synchronously rotating reference frame can be expressed in terms of the rotor voltage and current phasors in the rotor reference frame and the angle between them as

$$v_{dr} + j v_{qr} = \underline{v}_r e^{-j(\mu - \varepsilon)}$$

(2.23)

$$i_{dr} + ji_{qr} = \underline{i}_r e^{-j(\mu - \varepsilon)}$$

(2.24)

Substituting  $\underline{v}_s$ ,  $\underline{i}_s$ ,  $\underline{v}_r$ , and  $\underline{i}_r$  from (2.21), (2.22), (2.23), and (2.24) into (2.19) and (2.20), the voltage equations of the induction machine (2.19) and (2.20) may be transformed to equations in an arbitrary dq- reference frame rotating with the synchronous speed ( $\omega_s$ ) [8] and expressed as

$$r_{s}\left(i_{ds}+ji_{qs}\right)e^{j\mu}+L_{s}\frac{d}{dt}\left(\left(i_{ds}+ji_{qs}\right)e^{j\mu}\right)+L_{o}\frac{d}{dt}\left(\left(i_{dr}+ji_{qr}\right)e^{j\mu}\right)=\left(\left(v_{ds}+jv_{qs}\right)e^{j\mu}\right)(2.25)$$

$$r_{r}\left(i_{dr}+ji_{qr}\right)e^{j(\mu-\varepsilon)}+L_{r}\frac{d}{dt}\left(\left(i_{dr}+ji_{qr}\right)e^{j(\mu-\varepsilon)}\right)+L_{o}\frac{d}{dt}\left(\left(i_{dr}+ji_{qr}\right)e^{j(\mu-\varepsilon)}\right)=\left(v_{dr}+jv_{qr}\right)e^{j(\mu-\varepsilon)}$$

(2.26)

By comparing the real and imaginary parts of both sides of (2.25) and (2.26), the dynamic model of the induction machine in the arbitrary dq- reference frame rotating with the synchronous speed can be obtained as

$$v_{ds} = r_{s}i_{ds} + L_{s}\frac{di_{ds}}{dt} - \omega_{s}L_{s}i_{qs} + L_{o}\frac{di_{dr}}{dt} - \omega_{s}L_{o}i_{qr}$$

$$v_{qs} = r_{s}i_{qs} + L_{s}\frac{di_{qs}}{dt} + \omega_{s}L_{s}i_{ds} + L_{o}\frac{di_{qr}}{dt} + \omega_{s}L_{o}i_{dr}$$

$$v_{dr} = r_{r}i_{dr} + L_{r}\frac{di_{dr}}{dt} - (\omega_{s} - \omega_{e})L_{r}i_{qr} + L_{o}\frac{di_{ds}}{dt} - (\omega_{s} - \omega_{e})L_{o}i_{qs}$$

$$v_{qr} = r_{r}i_{qr} + L_{r}\frac{di_{qr}}{dt} + (\omega_{s} - \omega_{e})L_{r}i_{dr} + L_{o}\frac{di_{qs}}{dt} + (\omega_{s} - \omega_{e})L_{o}i_{ds}$$

$$(2.27)$$

where

$$\omega_s = \frac{d\mu}{dt}$$

(2.28)

and

$$\omega_e = \frac{d\varepsilon}{dt}$$

(2.29)

and d and q subscript describe the d- and q- axes variables, and  $\omega_e$  is the speed of the machine in electrical rad/s. The equation defining the dynamics of the machine speed is given by

$$J\frac{d\left(\frac{2}{P}\omega_{e}\right)}{dt} = \frac{3}{2}\frac{P}{2}L_{o}\left(i_{dr}i_{qs} - i_{ds}i_{qr}\right) - m_{L}$$

$$(2.30)$$

where J is the moment of inertia of the machine, P is the number of poles in the machine and  $m_L$  is the load torque applied to the machine.

Since the system under consideration is nonlinear, the linearized induction machine equations about an operating point can be given as [6]

$$\tilde{v}_{ds} = r_s \tilde{i}_{ds} + L_s \frac{d\tilde{i}_{ds}}{dt} - \omega_s L_s \tilde{i}_{qs} + L_o \frac{d\tilde{i}_{dr}}{dt} - \omega_s L_o \tilde{i}_{qr}

\tilde{v}_{qs} = r_s \tilde{i}_{qs} + L_s \frac{d\tilde{i}_{qs}}{dt} + \omega_s L_s \tilde{i}_{ds} + L_o \frac{d\tilde{i}_{qr}}{dt} + \omega_s L_o \tilde{i}_{dr}

\tilde{v}_{dr} = r_r \tilde{i}_{dr} + L_r \frac{d\tilde{i}_{dr}}{dt} - (\omega_s - \omega_e) L_r \tilde{i}_{qr} + L_o \frac{d\tilde{i}_{ds}}{dt} - (\omega_s - \omega_e) L_o \tilde{i}_{qs} + (L_r I_{qr} + L_o I_{qs}) \tilde{\omega}_e$$

$$\tilde{v}_{qr} = r_r \tilde{i}_{qr} + L_r \frac{d\tilde{i}_{qr}}{dt} + (\omega_s - \omega_e) L_r \tilde{i}_{dr} + L_o \frac{d\tilde{i}_{qs}}{dt} + (\omega_s - \omega_e) L_o \tilde{i}_{ds} - (L_r I_{dr} + L_o I_{ds}) \tilde{\omega}_e$$

$$J \frac{d(\frac{2}{P} \tilde{\omega}_e)}{dt} = \frac{3}{2} \frac{P}{2} L_o (\tilde{i}_{dr} I_{qs} - \tilde{i}_{ds} I_{qr} + I_{dr} \tilde{i}_{qs} - I_{ds} \tilde{i}_{qr}) - \tilde{m}_L$$

where "~" indicates the small-signal value, and the capital letter denotes the DC value of that particular variable or input. Equation (2.31)can be written in state-space form as

$$\frac{d}{dt} \begin{bmatrix} \tilde{i}_{ds} \\ \tilde{i}_{qs} \\ \tilde{i}_{dr} \\ \tilde{i}_{qr} \\ \tilde{\omega}_{e} \end{bmatrix} = A \begin{bmatrix} \tilde{i}_{ds} \\ \tilde{i}_{ds} \\ \tilde{i}_{dr} \\ \tilde{i}_{qr} \\ \tilde{\omega}_{e} \end{bmatrix} + B \begin{bmatrix} \tilde{v}_{ds} \\ \tilde{v}_{qs} \\ \tilde{v}_{dr} \\ \tilde{v}_{qr} \\ \tilde{m}_{L} \end{bmatrix}$$

(2.32)

where

$$\boldsymbol{A} = \begin{bmatrix} \frac{-r_s}{\sigma L_s} & \omega_s + \frac{\omega_e L_o^2}{\sigma L_s L_r} & \frac{r_r L_o}{\sigma L_s L_r} & \frac{\omega_e L_o}{\sigma L_s} & \frac{L_o \left(L_r I_{qr} + L_o I_{qs}\right)}{\sigma L_s L_r} \\ -\left(\omega_s + \frac{\omega_e L_o^2}{\sigma L_s L_r}\right) & \frac{-r_s}{\sigma L_s} & -\frac{\omega_e L_o}{\sigma L_s} & \frac{r_r L_o}{\sigma L_s L_r} & -\frac{L_o \left(L_r I_{dr} + L_o I_{ds}\right)}{\sigma L_s L_r} \\ \frac{r_s L_o}{\sigma L_s L_r} & -\frac{\omega_e L_o}{\sigma L_r} & -\frac{r_r}{\sigma L_r} & \omega_s - \frac{\omega_e}{\sigma} & -\frac{\left(L_r I_{qr} + L_o I_{qs}\right)}{\sigma L_r} \\ \frac{\omega_e L_o}{\sigma L_r} & \frac{r_s L_o}{\sigma L_s L_r} & -\left(\omega_s - \frac{\omega_e}{\sigma}\right) & -\frac{r_r}{\sigma L_r} & \frac{\left(L_r I_{dr} + L_o I_{ds}\right)}{\sigma L_r} \\ -\left(\frac{P}{2}\right)^2 \frac{3}{2} \frac{L_o I_{qr}}{J} & \left(\frac{P}{2}\right)^2 \frac{3}{2} \frac{L_o I_{dr}}{J} & \left(\frac{P}{2}\right)^2 \frac{3}{2} \frac{L_o I_{qs}}{J} & -\left(\frac{P}{2}\right)^2 \frac{3}{2} \frac{L_o I_{ds}}{J} & 0 \end{bmatrix}$$

and

$$\mathbf{B} = \begin{bmatrix} \frac{1}{\sigma L_s} & 0 & \frac{-L_0}{\sigma L_s L_r} & 0 & 0\\ 0 & \frac{1}{\sigma L_s} & 0 & \frac{-L_0}{\sigma L_s L_r} & 0\\ \frac{-L_0}{\sigma L_s L_r} & 0 & \frac{1}{\sigma L_r} & 0 & 0\\ 0 & \frac{-L_0}{\sigma L_s L_r} & 0 & \frac{1}{\sigma L_r} & 0\\ 0 & 0 & 0 & 0 & -\frac{P}{2J} \end{bmatrix}$$

where  $\sigma$  is the total leakage factor defined as

$$\sigma = 1 - \frac{L_o^2}{L_s L_r} \tag{2.33}$$

#### 2.3.2 Detailed Drive Model

Using (2.11), the linearized equations of the system, which describe the dynamic behavior of  $i_l$  and  $v_{dc}$ , in terms of the machine voltages and currents, can be given as

$$L_{dc} \frac{d\tilde{i}_{l}}{dt} + R\tilde{i}_{l} = \tilde{v}_{in} - \tilde{v}_{dc}$$

$$C_{dc} \frac{d\tilde{v}_{dc}}{dt} = \tilde{i}_{l} - \frac{1}{V_{dc}} \frac{3}{2} \left( \tilde{v}_{ds} I_{ds} + \tilde{v}_{qs} I_{qs} + V_{ds} \tilde{i}_{ds} + V_{qs} \tilde{i}_{qs} \right) + \frac{1}{V_{dc}^{2}} \frac{3}{2} \left( V_{ds} I_{ds} + V_{qs} I_{qs} \right) \tilde{v}_{dc}$$

(2.34)

By combining (2.34) and (2.32) for a squirrel cage induction machine ( $\tilde{v}_{dr}=0$ ,  $\tilde{v}_{qr}=0$ ), the linearized state-space equation of the complete drive system is given by

$$\frac{d}{dt} \begin{bmatrix} \tilde{i}_{ds} \\ \tilde{i}_{qs} \\ \tilde{i}_{dr} \\ \tilde{i}_{qr} \\ \tilde{\omega}_{e} \\ \tilde{i}_{l} \end{bmatrix} = \mathbf{A} \begin{bmatrix} \tilde{i}_{ds} \\ \tilde{i}_{qs} \\ \tilde{i}_{qr} \\ \tilde{\omega}_{e} \\ \tilde{v}_{dc} \\ \tilde{i}_{l} \end{bmatrix} + \begin{bmatrix} \mathbf{B}_{5X3} & \mathbf{0} \\ \mathbf{B}_{5X3} & \mathbf{0} \\ -\frac{3}{2} \frac{I_{ds}}{V_{dc} C_{dc}} & -\frac{3}{2} \frac{I_{qs}}{V_{dc} C_{dc}} & \mathbf{0} \\ 0 & 0 & 0 \end{bmatrix} \begin{bmatrix} \tilde{v}_{ds} \\ \tilde{v}_{qs} \\ \tilde{m}_{L} \\ \tilde{v}_{in} \end{bmatrix}$$

where

$$A' = \begin{bmatrix} A_{5X5} & 0 & 0 \\ -\frac{3}{2} \frac{V_{ds}}{V_{dc} C_{dc}} & -\frac{3}{2} \frac{V_{qs}}{V_{dc} C_{dc}} & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 \end{bmatrix} \frac{3}{2} \frac{\left(V_{ds} I_{ds} + V_{qs} I_{qs}\right)}{C_{dc} V_{dc}^2} & \frac{1}{C_{dc}} \\ -\frac{1}{L_{dc}} & -\frac{R}{L_{dc}} \end{bmatrix}$$

(2.35)

It can be seen from (2.35) that the matrix A' has a null block matrix. Using block matrices in A', it can be written as

$$A' = \begin{bmatrix} A_{5x5} & \theta_{5x2} \\ C'_{2x5} & B'_{2x2} \end{bmatrix}$$

(2.36)

where

$$C' = \begin{bmatrix} -\frac{3}{2} \frac{V_{ds}}{V_{dc} C_{dc}} & -\frac{3}{2} \frac{V_{qs}}{V_{dc} C_{dc}} & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 \end{bmatrix}$$

and  $B' = \begin{bmatrix} \frac{3}{2} \frac{\left(V_{ds} I_{ds} + V_{qs} I_{qs}\right)}{2} & \frac{1}{C_{dc}} \\ -\frac{1}{L_{dc}} & -\frac{R}{L_{dc}} \end{bmatrix}$

The poles of the detailed system described by (2.35) are given by the eigenvalues of A', and the eigenvalues of A' are equal to the eigenvalues of A and B'. It can be proven as follows

$$|A'-sI| = \begin{bmatrix} A-sI & 0 \\ C' & B'-sI \end{bmatrix}$$

$$|A'-sI| = \begin{bmatrix} A-sI & 0 \\ 0 & I \end{bmatrix} \begin{bmatrix} I & 0 \\ 0 & B'-sI \end{bmatrix} \begin{bmatrix} I & 0 \\ (B'-sI)^{-1}C' & I \end{bmatrix}$$

or,

$$|(A'-sI)| = |(A-sI)||(B'-sI)|$$

(2.37)

Typically, the eigenvalues of A are in the left half s-plane if the machine is operating in the negative slope region of the torque-speed characteristics [6]. The eigenvalues of B' can be given by

$$L_{dc}C_{dc}s^{2} + \left(RC_{dc} - \frac{3}{2}\frac{V_{ds}I_{ds} + V_{qs}I_{qs}}{C_{dc}V_{dc}^{2}}\right)s + \left(1 - \frac{3}{2}\frac{\left(V_{ds}I_{ds} + V_{qs}I_{qs}\right)R}{V_{dc}^{2}}\right) = 0$$

(2.38)

which is same as (2.14) since  $P_e = \frac{3}{2} \left( V_{ds} I_{ds} + V_{qs} I_{qs} \right)$  and supports criterion (2.15),

described in the subsection 2.1.2.1. It gives an important indication that for a small DC-link capacitor value  $(C_{dc})$  and/or the high power load on the machine, term  $3(V_{ds}I_{ds}+V_{qs}I_{qs})/(2\cdot C_{dc}V_{dc}^2)$  may eventually be greater than  $R/L_{dc}$ . As a consequence, the coefficient of 's' of the quadratic equation (2.38) will become negative. This results in positive real part of the roots of (2.38), which are related to the input  $L_{dc}-C_{dc}$  filter and the operating point becomes unstable. These roots can be forced to move into the left half s-plane by introducing the active damping terms.

### 2.4 Active Damping Terms

As discussed in the previous section, small DC-link capacitor based drive has the unstable operating point at high power load. To stabilize the operating point, active damping terms are defined as

$$\tilde{v}_{ds} = K1 \cdot \tilde{v}_{dc}

\tilde{v}_{as} = K2 \cdot \tilde{v}_{dc}$$

(2.39)

where K1 and K2 are constants. The idea here is to add the DC-link voltage dependant voltage components to the dq-axes stator voltages of the machine. By introducing these active damping terms, the unstable poles in the original state-space matrix of the drive system may be effectively modified, and the stability of the drive system is greatly improved. The modified state-space matrix involving the active damping terms (2.39) is given by

$$A'' = \begin{bmatrix} \frac{K1}{\sigma L_s} & 0 \\ \frac{K2}{\sigma L_s} & 0 \\ -\frac{K1 \cdot L_o}{\sigma L_s L_r} & 0 \\ -\frac{K2 \cdot L_o}{\sigma L_s L_r} & 0 \\ -\frac{3}{2} \frac{V_{ds}}{V_{dc} C_{dc}} & -\frac{3}{2} \frac{V_{qs}}{V_{dc} C_{dc}} & 0 & 0 & 0 \end{bmatrix} \begin{bmatrix} \frac{3}{2} \left( \frac{V_{ds} I_{ds} + V_{qs} I_{qs}}{V_{dc}^2 C_{dc}} - \frac{K1 \cdot I_{ds} + K2 \cdot I_{qs}}{V_{dc} C_{dc}} \right) & \frac{1}{C_{dc}} \\ 0 & 0 & 0 & 0 & 0 \end{bmatrix}$$

$$(2.40)$$

This is derived by substituting (2.39) in (2.35) and rearranging the state-space matrix. It can be seen from (2.35) and (2.40) that the term  $\frac{3(V_{ds}I_{ds}+V_{qs}I_{qs})}{2V_{dc}^2C_{dc}}$  is now

changed to  $\frac{3}{2} \left( \frac{V_{ds}I_{ds} + V_{qs}I_{qs}}{V_{dc}^2C_{dc}} - \frac{K1 \cdot I_{ds} + K2 \cdot I_{qs}}{V_{dc}C_{dc}} \right)$  in the state-space matrix. The effect of

these active damping terms may be easily observed. For example, by choosing proper values of

$$K1 = \frac{V_{ds}I_{ds} + V_{qs}I_{qs}}{V_{dc}I_{ds}} \quad K2 = 0$$

(2.41)

or

$$K1 = 0 K2 = \frac{V_{ds}I_{ds} + V_{qs}I_{qs}}{V_{dc}I_{qs}} (2.42),$$

the term  $\frac{3}{2} \left( \frac{V_{ds}I_{ds} + V_{qs}I_{qs}}{V_{dc}^2 C_{dc}} - \frac{K1 \cdot I_{ds} + K2 \cdot I_{qs}}{V_{dc}C_{dc}} \right)$  can be forced to be zero and the stability of

the drive system becomes independent of the working power range and the DC-link capacitor value. It can be seen form (2.41) and (2.42) that the values of K1 and K2 are independent of the system parameters.

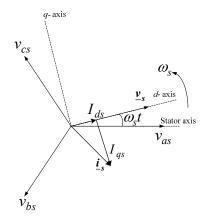

The signs of K1 and K2 depend on the signs of  $I_{ds}$  and  $I_{qs}$ , which in turn depend on the choice of the synchronously rotating reference frame. In this chapter, the d-

axis of the synchronously rotating reference frame is aligned with the stator voltage space vector as shown in Figure 2-7.  $v_{as}$ ,  $v_{bs}$ , and  $v_{cs}$  are the machine phase voltages. For this reference frame choice,  $I_{ds}$  is positive and  $I_{qs}$  is negative as shown in Figure 2-7. From (2.41) and (2.42), it can be seen that a positive value of K1 and/or a negative value of K2 are required for achieving active damping effects.

Figure 2-7 Synchronously rotating reference frame.

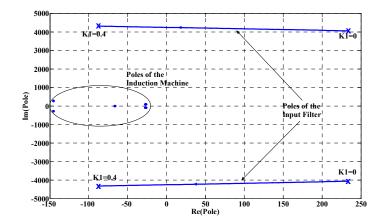

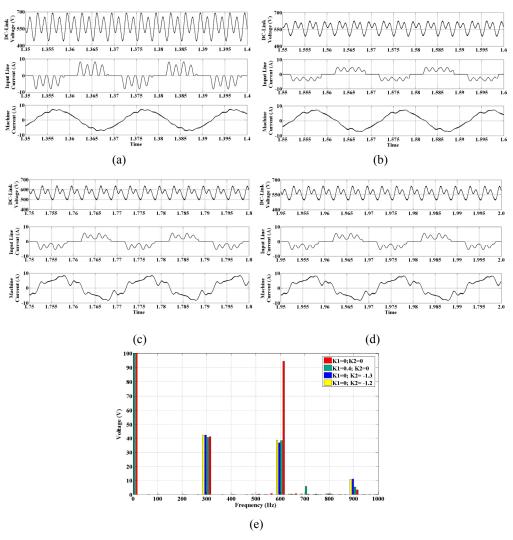

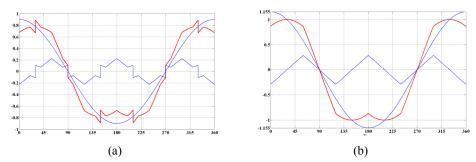

The values of parameters K1 and K2 depend on the drive system operating point. The effect of the damping technique will be demonstrated by using an induction machine drive system. The parameters of the drive system to be studied are summarized in Appendix B. The model of the drive system is linearized about a selected working point given in Table 2-3, which exhibits an unstable operating point. The poles of the system are calculated using A' given in (2.35). It can be seen from Table 2-4 that the poles relating to the input  $L_{dc}$  – $C_{dc}$  filter have positive real parts for this particular operating point. This shows that the selected operating point of the drive system is unstable. The operating point can be stabilized using the active damping terms given by (2.39). By substituting this operating point values in (2.41), K1 is calculated as 0.4. The root locus plot of the system is shown in Figure 2-8, which shows the change in the poles of the drive system as K1 is varied. It is important to note that by changing K1, the poles related to the induction machine also change. When K1 is increased from 0 to 0.4, the induction machine poles still remain in the left half s-plane and will not cause any stability problems.

| Table 2-3 Ope | rating Point | of the I | Jrive |

|---------------|--------------|----------|-------|

|---------------|--------------|----------|-------|

| $V_{ds}$ =225 V          | $I_{ds}$ =5.95 A          | $I_{dr} = -6.1 \text{ A}$ |

|--------------------------|---------------------------|---------------------------|

| $V_{qs}$ =0 V            | $I_{qs} = -3.8 \text{ A}$ | $I_{qr} = 0.5 \text{ A}$  |

| $V_{dc} = 565 \text{ V}$ | $\omega_e$ =305 rad/s     | $\omega_s$ =314.2 rad/s   |

Table 2-4 Poles of the System

| $232 \pm 4063j$ – | $145 \pm 286$ j $-27.5 \pm 8$ | 37.40j – 66 |

|-------------------|-------------------------------|-------------|

|-------------------|-------------------------------|-------------|

Figure 2-8 Root locus plot of the system as K1 varies 0 to 0.4 with K2=0.

The effect of the active damping terms on the poles of the induction machine at a particular operating point needs to be evaluated to secure the stability of the operating point. Application of the active damping terms may move the poles of the induction machine towards the right half s-plane. The change in a particular pole  $(\delta\lambda)$  due to the change in the state-space matrix introduced by adding the active damping terms can be calculated using first-order perturbation theory [2], which gives

$$\delta\lambda = \frac{\boldsymbol{w}^T \cdot \boldsymbol{\delta} \boldsymbol{A} \cdot \boldsymbol{v}}{\boldsymbol{w}^T \cdot \boldsymbol{v}} \tag{2.43}$$

where v and w are the right and left eigenvector of matrix A', and

$$\delta A = A'' - A' = \begin{bmatrix} \frac{K1}{\sigma L_s} & 0 \\ \frac{K2}{\sigma L_s} & 0 \\ -\frac{K1L_o}{\sigma L_s L_r} & 0 \\ -\frac{K2L_o}{\sigma L_s L_r} & 0 \\ 0 & 0 \\ -\frac{3}{2} \left( \frac{K1I_{ds} + K2I_{qs}}{V_{dc} C_{dc}} \right) & 0 \\ 0 & 0 \end{bmatrix}$$

(2.44)

By solving (2.43), the expression for  $\delta\lambda$  can be given as

$$\delta\lambda = \frac{v_6}{\boldsymbol{w}^T \cdot \boldsymbol{v}} \boldsymbol{w}^T \begin{bmatrix} \frac{K1}{\sigma L_s} & \frac{K2}{\sigma L_s} & -\frac{K1L_o}{\sigma L_s L_r} & -\frac{K2L_o}{\sigma L_s L_r} & 0 & -\frac{3}{2} \frac{K1I_{ds} + K2I_{qs}}{C_{dc} V_{dc}} & 0 \end{bmatrix}^T$$

(2.45)

where  $v_6$  is the sixth element of the right eigenvector  $\mathbf{v}$  of matrix  $\mathbf{A}$ '. Equation (2.45) may be used to calculate the change in the poles of the linearized system for different values of K1 and K2.

The change in the poles of the system for K1=0.4 are shown in Table 2-5. These values are calculated using (2.45) and are in agreement with the root locus plot shown in Figure 2-8. It can be seen from the Table 2-5 that the poles of the induction machine are moving towards the right half s-plane, while the poles affected by the input  $L_{dc}$ - $C_{dc}$  filter are moving towards the left half s-plane. But the effect of K1=0.4 on the induction machine poles is not significant, and all the poles remain in the left half s-plane, giving a stable drive operating point.

| K1=0, K2=0            | K1=0.4, K2=0        |

|-----------------------|---------------------|

| $232 \pm j \ 4063$    | $-87.1 \pm j  4338$ |

| $-145 \pm j \ 286$    | -145± j 265         |

| $-27.5 \pm j \ 87.40$ | -26± j 88           |

| -66                   | -67                 |

Table 2-5 Poles of the Linearized Drive System

# 2.5 Effect of Damping Terms on the DC-Link Voltage and the Machine Currents in Steady State

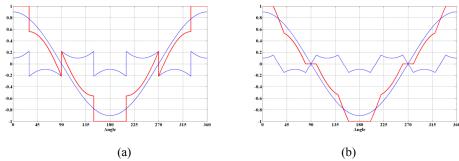

It is shown in the previous section that the unstable operating point of the drive system can be stabilized by using active damping terms. These terms add a voltage proportional to the small-signal variation of the DC-link voltage ( $\tilde{v}_{dc}$ ) in the d- or q-axes voltages of the induction machine. The small-signal variation of the DC-link voltage consists of high frequency signal of the DC-link voltage. Since the equivalent circuit of the rectifier and the grid (Figure 2-2) is excited by the input voltage  $v_{in}$  having spectral components only at sixth multiples of the line frequency given by (2.2), the high frequency signal of the DC-link voltage have the same frequency components. From (2.39), the small-signal variation in the d- and q- axis machine voltage in steady state may be approximated as

$$\tilde{v}_{ds} = K1 \cdot \tilde{v}_{dc} = K1 \sum_{n=1}^{\infty} v_{dcn} = K1 \sum_{n=1}^{\infty} V_{dcn} \cos\left(6n\omega_g t + \phi_n\right)$$

$$\tilde{v}_{qs} = K2 \cdot \tilde{v}_{dc} = K2 \sum_{n=1}^{\infty} v_{dcn} = K2 \sum_{n=1}^{\infty} V_{dcn} \cos\left(6n\omega_g t + \phi_n\right)$$

(2.46)

where  $v_{dcn}$  is the 6nth harmonics of the DC-link voltage having amplitude  $V_{dcn}$  and phase  $\Phi_n$ . The effect of PWM on the machine harmonics voltages is neglected for simplicity. These high frequency components of the machine voltage will induce the high frequency components in the machine currents, which in turn introduce the

high frequency components in the DC-link current which are governed by (2.9). An expression for the high frequency component of the machine current and the DC-link current will be derived in this section. This DC-link current is also an input of the equivalent circuit of the rectifier and the grid as shown in Figure 2-2 and affects the DC-link voltage. A simplified closed form solution for the DC-link voltage harmonics components is derived in this section using only first-order terms. Using this solution, it is shown that the same amplitude of DC-link voltage harmonics can be achieved by applying the active damping terms to either the *d*-axis or the *q*- axis.

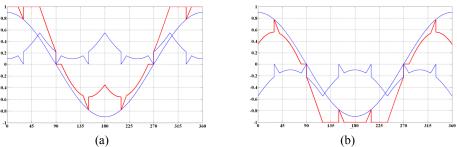

#### 2.5.1 The Machine Current

The active damping terms introduce the harmonic components of sixth multiples of line frequency in the machine d- and q- axes voltages. They produce harmonic components in the machine currents, which are governed by the leakage inductances of the induction machine only. This is because the impedance offered by induction machine at that frequency may be approximated as the impedance due to the sum of the stator leakage inductance ( $L_{ls}$ ) and the rotor leakage inductance ( $L_{lr}$ ) in the stationary reference frame as shown in Figure 2-9 [70].

Figure 2-9 Equivalent circuit of the induction machine for a harmonic component.

Using (2.46), the machine phase voltage in the stationary reference frame, because of the 6*n*th harmonic component of the DC-link voltage, can be given by

$$v_{a,n} = K1 V_{dcn} \cos\left(6n\omega_g t + \phi_n\right) \cos\left(\omega_s t\right) - K2 V_{dcn} \cos\left(6n\omega_g t + \phi_n\right) \sin\left(\omega_s t\right)$$

$$v_{a,n} = \frac{K V_{dcn}}{2} \left(\cos\left(\left(6n\omega_g - \omega_s\right)t + \phi_n - \phi_k\right) + \cos\left(\left(6n\omega_g + \omega_s\right)t + \phi_n + \phi_k\right)\right)$$

(2.47)

where

$$K = \sqrt{K1^2 + K2^2}$$

,  $\phi_k = \tan^{-1}\left(\frac{K2}{K1}\right)$ , and  $v_{a,n}$  denotes the voltage of phase  $a$  of the

machine caused by the 6nth harmonic component of the DC-link voltage added as the active damping terms. Since the machine acts as an inductance for high frequencies, the machine current for phase  $a(i_{a,n})$  due to  $v_{a,n}$  may be given as

$$i_{a,n} = \frac{K V_{dcn}}{2(6n\omega_g - \omega_s)(L_{ls} + L_{lr})} \cos\left((6n\omega_g - \omega_s)t + \phi_n - \phi_k - \frac{\pi}{2}\right) + \frac{K V_{dcn}}{2(6n\omega_g + \omega_s)(L_{ls} + L_{lr})} \cos\left((6n\omega_g + \omega_s)t + \phi_n + \phi_k - \frac{\pi}{2}\right)$$

$$(2.48)$$

Using phase symmetry of the three-phase machine and park's transformation, the *d*-and *q*- axis machine currents, due to the 6*n*th harmonic component of the DC-link

voltage added as the active damping terms, denoted as  $i_{dsn}$  and  $i_{qsn}$ , are expressed as given by

$$i_{dsn} = \frac{K V_{dcn}}{2 \left( L_{ls} + L_{lr} \right)} \left( \frac{\cos \left( 6n\omega_g \ t + \phi_n - \phi_k - \frac{\pi}{2} \right)}{\left( 6n\omega_g - \omega_s \right)} + \frac{\cos \left( 6n\omega_g \ t + \phi_n + \phi_k - \frac{\pi}{2} \right)}{\left( 6n\omega_g + \omega_s \right)} \right)$$

$$i_{qsn} = \frac{K V_{dcn}}{2 \left( L_{ls} + L_{lr} \right)} \left( \frac{\sin \left( 6n\omega_g \ t + \phi_n - \phi_k - \frac{\pi}{2} \right)}{\left( 6n\omega_g - \omega_s \right)} + \frac{\sin \left( 6n\omega_g \ t + \phi_n + \phi_k - \frac{\pi}{2} \right)}{\left( 6n\omega_g + \omega_s \right)} \right)$$

$$(2.49)$$

Using  $K = \sqrt{K1^2 + K2^2}$ ,  $\sin \phi_k = \frac{K2}{K}$ , and  $\cos \phi_k = \frac{K1}{K}$ ; this can be simplified as

$$i_{dsn} = \frac{V_{dcn}}{2\left(L_{ls} + L_{lr}\right)} \left(\frac{K1 \cdot \sin\left(6n\omega_{g} \ t + \phi_{n}\right)12n\omega_{g}}{\left(6n\omega_{g} - \omega_{s}\right)\left(6n\omega_{g} + \omega_{s}\right)} - \frac{K2 \cdot \cos\left(6n\omega_{g} \ t + \phi_{n}\right)2\omega_{s}}{\left(6n\omega_{g} - \omega_{s}\right)\left(6n\omega_{g} + \omega_{s}\right)}\right)$$

$$i_{qsn} = \frac{V_{dcn}}{2\left(L_{ls} + L_{lr}\right)} \left(\frac{K1 \cdot \cos\left(6n\omega_{g} \ t + \phi_{n}\right)2\omega_{s}}{\left(6n\omega_{g} - \omega_{s}\right)\left(6n\omega_{g} + \phi_{n}\right)12n\omega_{g}} + \frac{K2 \cdot \sin\left(6n\omega_{g} \ t + \phi_{n}\right)12n\omega_{g}}{\left(6n\omega_{g} - \omega_{s}\right)\left(6n\omega_{g} + \omega_{s}\right)}\right)$$

$$(2.50)$$

The d- axis machine current contains two components. The first component, which is proportional to K1 and 12n times the grid frequency, is the current induced by the d-axis voltage. The second component, which is proportional K2 and twice the synchronous frequency, is the current induced due to the q-axis voltage. Similar components are present in the q-axis machine harmonic current. If  $\omega_s = \omega_g$ , in the d-axis current, the harmonics current induced by the d-axis active damping term will be 6n times the harmonics current induced by the q-axis active damping term with same gain (K1=K2).

#### 2.5.2 The DC-link Current

It can be seen from (2.50) that the d- and q- axes currents have frequency equal to  $6n\omega_g$  due to the applied machine voltage of same frequency. The machine currents and voltages decide the DC-link current ( $i_{dc}$ ) as given by (2.9). Using only first-order terms of Taylor series expansion of (2.9), for  $v_{dcs}=v_{dc}$ , the small-signal variation of the DC-link current may be given by

$$\tilde{i}_{dc} = \frac{3}{2} \frac{1}{V_{dc}} \left( \tilde{v}_{ds} I_{ds} + \tilde{v}_{qs} I_{qs} + V_{ds} \tilde{i}_{ds} + V_{qs} \tilde{i}_{qs} \right) - \frac{3}{2} \frac{1}{V_{dc}^2} \left( V_{ds} I_{ds} + V_{qs} I_{qs} \right) \tilde{v}_{dc}$$

(2.51)

If the small-signal variation is approximated as the high frequency component, the 6nth harmonic component of the DC-link current ( $i_{dcn}$ ) may be given by

$$i_{dcn} = \frac{3}{2} \frac{1}{V_{dc}} \left( K1 \cdot v_{dcn} I_{ds} + K2 \cdot v_{dcn} I_{qs} + V_{ds} i_{dsn} + V_{qs} i_{qsn} \right) - \frac{3}{2} \frac{1}{V_{dc}^2} \left( V_{ds} I_{ds} + V_{qs} I_{qs} \right) v_{dcn}$$

Since  $V_{qs} = 0$ ;

$$i_{dcn} = \frac{3}{2} \frac{1}{V_{dc}} \left( K1 \cdot v_{dcn} I_{ds} + K2 \cdot v_{dcn} I_{qs} + V_{ds} i_{dsn} \right) - \frac{3}{2} \frac{1}{V_{dc}^2} \left( V_{ds} I_{ds} \right) v_{dcn}$$

(2.52)

In steady state, the machine is operated with the synchronous speed of 50 Hz, which is equal to grid supply frequency ( $\omega_s = \omega_g$ ). In this case, the *d*-axis and the *q*-axis active damping terms have different effect on the harmonics components of the DC-link current which are governed by (2.52). If the *d*-axis active damping term is only applied (K2=0), using (2.46), (2.50), and (2.52), the 6*n*th harmonic component of the DC-link current ( $i_{dcn}$ ) is given by

$$\begin{split} i_{dcn}\big|_{K2=0} &= \frac{3}{2} \frac{1}{V_{dc}} \left( K1 \cdot V_{dcn} \cos(6n\omega_g t + \phi_n) I_{ds} + V_{ds} \frac{K1 \cdot V_{dcn}}{2(L_{ls} + L_{lr})} \left( \sin\left(6n\omega_g t + \phi_n\right) \frac{12n}{\left(6n - 1\right)\left(6n + 1\right)\omega_g} \right) \right) \\ &- \frac{3}{2} \frac{1}{V_{dc}^2} \left( V_{ds} I_{ds} \right) V_{dcn} \cos(6n\omega_g t + \phi_n) \end{split}$$

or,

$$i_{dcn}\big|_{K2=0} = \frac{3}{2} \frac{1}{V_{dc}} \left( \left( K1 - \frac{V_{ds}}{V_{dc}} \right) \cdot V_{dcn} \cos(6n\omega_g t + \phi_n) I_{ds} + V_{ds} \frac{K1 \cdot V_{dcn}}{2(L_{ls} + L_{lr})} \left( \sin\left(6n\omega_g t + \phi_n\right) \frac{12n}{(6n-1)(6n+1)\omega_g} \right) \right)$$

(2.53)

Similarly, from (2.52), the 6*n*th harmonic component of the DC-link current ( $i_{dcn}$ ), for K1=0, is given by

$$i_{dcn}|_{K_{1=0}} = \frac{3}{2} \frac{1}{V_{dc}} \left( K_2 \cdot v_{dcn} I_{qs} + V_{ds} i_{dsn} \right) - \frac{3}{2} \frac{1}{V_{dc}^2} \left( V_{ds} I_{ds} \right) v_{dcn}$$

(2.54)

Using (2.46) and (2.50),  $v_{dcn}$  and  $i_{dsn}$  is replaced in (2.54) for  $\omega_s = \omega_g$ .

$$\begin{split} i_{dcn}\big|_{K1=0} &= \frac{3}{2} \frac{1}{V_{dc}} \left( K2 \cdot V_{dcn} \cos(6n\omega_g t + \phi_n) I_{qs} + V_{ds} \frac{K2 \cdot V_{dcn}}{2(L_{ls} + L_{lr})} \left( \cos\left(6n\omega_g t + \phi_n\right) \frac{-2}{\left(6n - 1\right)\left(6n + 1\right)\omega_g} \right) \right) \\ &- \frac{3}{2} \frac{1}{V_{dc}^2} V_{ds} I_{ds} V_{dcn} \cos(6n\omega_g t + \phi_n) \end{split}$$

or,

$$i_{dcn}\big|_{K_{1}=0} = \frac{3}{2} \frac{V_{dcn}}{V_{dc}} \left( K_{2} \cdot I_{qs} - \frac{K_{2} \cdot V_{ds}}{2(L_{ls} + L_{lr})} \frac{2}{(6n-1)(6n+1)\omega_{g}} - \frac{V_{ds}I_{ds}}{V_{dc}} \right) \cos(6n\omega_{g}t + \phi_{n})$$

(2.55)