#### **Aalborg Universitet**

| CMOS Power Amplifiers for Wireless Communication Systems           |

|--------------------------------------------------------------------|

| Sira, Daniel                                                       |

|                                                                    |

|                                                                    |

|                                                                    |

| Publication date: 2011                                             |

| Document Version Accepted author manuscript, peer reviewed version |

| Link to publication from Aalborg University                        |

|                                                                    |

| Citation for published version (APA):                              |

Sira, D. (2011). CMOS Power Amplifiers for Wireless Communication Systems. Department of Electronic Systems, Aalborg University.

**General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- ? Users may download and print one copy of any publication from the public portal for the purpose of private study or research. ? You may not further distribute the material or use it for any profit-making activity or commercial gain ? You may freely distribute the URL identifying the publication in the public portal ?

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# CMOS Power Amplifiers for Wireless Communication Systems

### **Daniel Sira**

A dissertation submitted in partial fulfillment of the requirements for the degree of

**Doctor of Philosophy**

in Wireless Communications

**Aalborg University**

**Department of Electronic Systems**

December 2010

CMOS Power Amplifiers for Wireless Communication Systems Copyright © Daniel Sira

#### Published by:

Aalborg University

Faculty of Engineering and Science

Department of Electronic Systems

Technology Platforms

Niels Jernes Vej 12, DK-9220 Aalborg, Denmark

Phone +45 9940 9839, Fax +45 9815 1583

tps@es.aau.dk

www.es.aau.dk

ISBN: 978-87-92328-49-6

#### **Abstract**

This thesis summarizes results obtained during three year research in the field of CMOS RF power amplifiers (PA) at Technology Platforms Section of Aalborg University. In order to increase the data throughput of a wireless link modern communication systems employ both the amplitude and phase modulation of the RF carrier. This requires the use of linear RF power amplifiers. The linear PAs suffer by inherently low efficiency that leads to decreased talk time. To satisfy the demand for high linearity and high efficiency PAs there is need for new approach. A linearized and highly efficient switch-mode PA is one of the feasible alternatives.

Switch-mode PAs offer high efficiency but they are highly non-linear. Using suitable linearization technique they can be utilized in modern wireless transmitters. Nowadays the polar transmitter topology, where the amplitude and phase modulated signals are processed in two separate paths, is one of the major techniques that enables to employ a switch-mode PA in the RF transmitters with varying amplitude signals.

Because the amplitude modulated signal can not be directly applied to the RF input port as in a linear PA, a switch-mode PA has to use different method to combine the amplitude and phase modulated signals. In this thesis a new approach for amplification of modulated varying envelope signals is presented. The concept is called cascode modulated class-E PA.

The main advantages of the cascode modulated class-E PA are high output power dynamic range and no need for an external supply modulator as it is in the conventional power supply modulation method. The major drawback of cascode modulation is higher AM-AM distortion compared to the supply modulation.

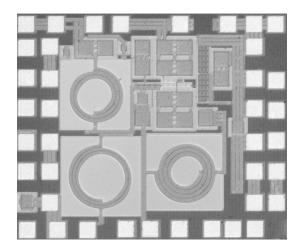

Feasibility of the cascode modulated class-E PA concept was verified via its implementation in CMOS technology. The PA was tested with EDGE and WCDMA signals. In order to meet the linearity requirements imposed by GSM/EDGE and 3GPP standards a digital predistortion is used to linearize the PA.

**Keywords:** Class-E amplifier, CMOS, Envelope modulator, Polar transmitter, Power control, RF power amplifier

# CMOS effektforstærkere til trådløse kommunikationssystemer

#### Resumé

Denne afhandling sammenfatter de resultater, der er opnået gennem tre års forskning i CMOS RF effektforstærkere (PA) ved Technology Platforms sektionen ved Aalborg Universitet. For at efterkomme transmissionskapaciteten bruger moderne kommunikationssystemer både amplitude og fasemodulation af RF bærebølgen. Det kræver brug af lineære RF effektforstærkere. Men en lineær PA har grundlæggende en lav effektivitet, hvilket medfører nedsat taletid. For at opfylde kravet om effektforstærkere med høj effektivitet og høj linearitet er der brug for en ny fremgangsmåde. En højeffektiv og lineariseret switch-mode PA er et af de egnede alternativer.

Switch-mode PA'er har høj effektivitet, men er meget ulineære. Ved brug af en passende lineariseringsteknik kan de anvendes i moderne trådløse sendere. For tiden er den polære sendertopologi , hvor amplitude og faseinformation behandles i to separate grene, en af de vigtigste teknikker som gør det muligt at anvende en switch-mode PA i RF sendere med signaler med varierende amplitude.

Da det amplitudemodulerede signal ikke kan tilføres direkte til RF indgangen som i en lineær effektforstærker, måen switch-mode PA bruge en anden metode til at kombinere amplitude og faseinformation. I denne afhandling er en ny metode til forstærkning af et moduleret signal med varierende amplitude præsenteret. Metoden kaldes kaskodemoduleret klasse E PA.

De vigtigste fordele ved den kaskodemodulerede klasse E PA er et stort dynamikområde for udgangseffekten og intet behov for en ekstern modulation af forsyningsspændingen, i modsætning til den traditionelle metode med ekstern modulation af forsyningsspændingen. Den største ulempe ved kaskodemodulation er højere AM-AM forvrængning i sammenlignet med modulation af forsyningsspændingen.

At princippet i en kaskodemoduleret klasse E PA er egnet, er vist via en implementation i en CMOS teknologi. PA'en er afprøvet med EDGE og WCDMA signaler. For at opfylde de linearitetskrav, der stilles i standarderne fra GSM/EDGE og 3GPP er der brugt digital modforvrængning til at linearisere PA'en.

# **CMOS Power Amplifiers for Wireless Communication Systems**

#### **Assessment committee**

Professor **Henrik Sjöland**, Ph.D. *Lund University* Sweden

Professor **Timo Erkki Rahkonen**, Ph.D. *University of Oulu* Finland

Professor **Søren Holdt Jensen**, Ph.D. *Aalborg University* Denmark

## **Supervisor**

Professor **Torben Larsen**, Dr. Techn. *Aalborg University* Denmark

# **Co-supervisors**

**Jens Christian Lindof** and **Pia Thomsen** *Texas Instruments* Denmark

Date Approved: December 14, 2010

This work was supported by

**Texas Instruments Denmark**

# **Contents**

| 1 |            | oductio  |                                  | 1          |

|---|------------|----------|----------------------------------|------------|

|   | 1.1<br>1.2 |          | n wireless communication systems | 1          |

|   |            |          |                                  |            |

| 2 |            |          | tals of RF PAs                   | 5          |

|   | 2.1        | Transc   | conductance PAs                  | 6          |

|   |            | 2.1.1    | Class-A                          | 6          |

|   |            | 2.1.2    | Classes AB, B and C              | 8          |

|   |            | 2.1.3    | Class-F                          | 10         |

|   | 2.2        | Switch   | n-mode PAs                       | 11         |

|   |            | 2.2.1    | Class-D                          | 11         |

|   |            | 2.2.2    | Class-E                          | 13         |

|   | 2.3        | Figure   | s of merit                       | 15         |

|   |            | 2.3.1    |                                  | 15         |

|   |            | 2.3.2    |                                  | 16         |

|   |            | 2.3.3    |                                  | 17         |

|   |            | 2.3.4    | , ,                              | 20         |

| 3 | Line       | ar tran  | smitters using switch-mode PAs   | 29         |

| • | 3.1        |          |                                  | <b>-</b> 9 |

|   | 3.2        |          |                                  | 23<br>31   |

|   | 3.3        |          | · · · ·                          | 33         |

|   | 5.5        | 3.3.1    |                                  | 55<br>41   |

|   |            | 3.3.2    |                                  | 42         |

|   |            |          | •                                | 42<br>44   |

|   |            | 3.3.3    | Digitally modulated polar PA     | 44         |

| 4 | Clas       | s-E PA   | 1                                | 47         |

|   | 4.1        | Class-I  | E PA design                      | 47         |

|   | 4.2        | Praction | cal design aspects               | 54         |

|   |            | 4.2.1    | ON resistance of the switch      | 54         |

|   |            | 4.2.2    | Non-ideal LC tank                | 55         |

|   |            | 4.2.3    | Finite RFC technique             | 56         |

|   | 4.3        | Imped    | ance transformation              | 58         |

| 5 | Cas        | code m   | odulated Class-E PA              | 61         |

|   | 5.1        | Ideal C  | Class-E PA                       | 62         |

|   | 5.2        |          |                                  | 64         |

|   | 5.3        |          |                                  | 69         |

|   |            |          |                                  | 70         |

|   |            |          |                                  | 70         |

x Contents

|     |        | 5.3.3   | Cascode circuit                           |  |  | <br>83  |

|-----|--------|---------|-------------------------------------------|--|--|---------|

|     |        | 5.3.4   | Modulation BW                             |  |  | 94      |

|     |        | 5.3.5   | Process and temperature variation         |  |  |         |

|     | 5.4    |         | de modulation and adaptive supply voltage |  |  |         |

|     | 5.5    | Reliabi | ility                                     |  |  | 100     |

| 6   | The    | model   | of the cascode modulated class-E PA       |  |  | 105     |

|     | 6.1    | Drain o | current analysis                          |  |  | <br>105 |

|     | 6.2    | Equiva  | lent DC model                             |  |  | 110     |

|     | 6.3    | Empiri  | cal model                                 |  |  | <br>113 |

|     | 6.4    | -       | ical model                                |  |  | 115     |

|     |        | 6.4.1   | Saturation region                         |  |  |         |

|     |        | 6.4.2   | Linear region                             |  |  |         |

|     |        | 6.4.3   | Analytical model verification             |  |  | 118     |

| 7   | Ехре   | eriment | tal Results                               |  |  | 121     |

|     | 7.1    | Cascoo  | de power control                          |  |  | <br>121 |

|     |        | 7.1.1   | Supply voltage power control technique    |  |  | 121     |

|     |        | 7.1.2   | Cascode power control technique           |  |  | 122     |

|     |        | 7.1.3   | Measurements                              |  |  | <br>123 |

|     | 7.2    | ,       | g envelope modulation                     |  |  |         |

|     |        | 7.2.1   | Linearization                             |  |  | 131     |

|     |        | 7.2.2   | EDGE signal experimental results          |  |  |         |

|     |        | 7.2.3   | WCDMA signal experimental results         |  |  | <br>138 |

| 8   | Sum    | mary    |                                           |  |  | 143     |

|     | 8.1    | Summa   | ary                                       |  |  | <br>143 |

|     | 8.2    | Furthe  | r research                                |  |  | <br>144 |

| Bil | bliogr | aphy    |                                           |  |  | 145     |

| ۸   | nond   | icos    |                                           |  |  |         |

| Αþ  | pend   | ices    |                                           |  |  |         |

| Α   | Bon    | d-wire  | inductor model                            |  |  | 151     |

| В   | Rep    | int of  | publications                              |  |  | 153     |

# List of Abbreviations

3G Third generation wireless technology defined by International Mobile

Telecommunications-2000

3GPP 3rd generation partnership project

ACLR Adjacent channel leakage ratio

AM Amplitude modulated signal

BB Base-band signal

BPF Bandpass filter

BW Bandwidth

CPCT Cascode power control technique

CW Continuous wave signal

DE Drain efficiency

EDGE Enhanced Data rates for GSM Evolution

EVM Error vector magnitude

GMSK Gaussian minimum shift keying

GSM Global System for Mobile communications

IMD Intermodulation distortion

LINC Linear amplification with non-linear components

LUT Look-up table

P<sub>in</sub> The available average input power

$P_{\rm out}$  The average output power delivered into the 50  $\Omega$  load at the fundamental

frequency

PA Power amplifier

PAE Power added efficiency

PAPR Peak to average power ratio

PM Phase modulated signal

PWM Pulse width modulation

QAM Quadrature amplitude modulation

QPSK Quadrature phase shift keying

$R_{

m L}$  Load resistor

RFC RF choke inductor

SRC Series resonant circuit

SVPCT Supply voltage power control technique

UMTS Universal Mobile Telecommunications System

$V_{\mathrm{DD}}$  The supply voltage

VNA Vector network analyzer

WCDMA Wideband Code Division Multiple Access

ZVS Zero voltage switching

# Introduction

#### Contents

| 1.1 | Modern wireless communication systems | 1 |

|-----|---------------------------------------|---|

| 1.2 | Organization of the thesis            | 3 |

Contemporary wireless communication technologies use complex digital modulation schemes what require the use of linear RF power amplifiers. The linear PAs suffer by inherently low efficiency what leads to a decreased talk time. Therefore, a new approach is needed to satisfy the demand for high linearity and high efficiency PAs. The linearized and high efficient switch-mode PA is one of the feasible alternatives.

Nowadays, most of the commercially available PAs use GaAs or InGaP devices that exhibit better high-frequency performance and higher quality of the passive on-chip components. On the other hand, high performance digital circuits are usually fabricated in the CMOS technology. There has been a significant effort to develop a fully integrated RF transmitter in the standard CMOS process technology. This will reduce the size and the costs of the RF transceivers.

The research in the wireless transceivers has been focused on the new system topologies that can reduce the power consumption and increase the system integration. Indeed, the number of additional discrete components has been significantly decreased but the ultimate goal of having the digital baseband circuits integrated with the high efficient RF circuits on the same die has not been achieved.

### 1.1 Modern wireless communication systems

Nowadays, it is very common to share the personal high-resolution photos and videos with friends, connect to life audio and video streams, download emails or just browse the internet. Beside that users expect soon to have available an internet access with very high data rates (at least 100 Mbps) and also the possibility of the on-line gaming (that requires the latency below 10 ms in the wireless network).

Modern communication systems employ both the amplitude and phase modulation of the RF carrier in order to increase the data throughput of a wireless link. The amount of data transferred through the mobile terminals in the wireless network has significantly increased. To satisfy these needs the mobile standards have to evolve rapidly. The frequency spectrum is scarce and therefore spectrally efficient modulations are used. This leads to the use of varying amplitude and phase modulation techniques.

The first widely used standard which employed the phase and amplitude modulation was the Enhanced Data rates for GSM Evolution (EDGE). It offers much higher data rates and has much higher spectral efficiency (bps/Hz) than the Global System for Mobile Communications (GSM). It is using 8PSK modulation which results in 3.4 dB peak to average power ratio (PAR). The maximum data rate is 473.6 kbit/s for both the up-link and down-link.

The most widely used mobile data systems are employing the third generation wireless technology (3G). In Europe it is implemented by the UMTS (Universal Mobile Telecommunications System). This system is using the CDMA (Code Division Multiple Access) technology. The up-link modulation scheme utilizes the QPSK (Quadrature Phase Shift Keying) or in case of HSPA+ (Evolved High Speed Packet Access) 16-QAM (Quadrature Amplitude Modulation). Both modulations require a linear amplification to prevent the power leakage into the neighboring channels.

The emerging standard is called LTE (Long Term Evolution) or sometimes it is referred to as 3.9G. It supports both the FDD (Frequency Division Duplex) and TDD (Time Division Duplex). The down-link utilizes OFDMA (Orthogonal Frequency Division Multiple Access) and the up-link SC-FDMA (Single Carrier FDMA) scheme. The LTE is employing QPSK, 16-QAM or 64-QAM modulation which requires a linear amplification. It allows up to 326 Mbpsk downlink and 86 Mbpsk uplink speeds.

The selected mobile standards are compared in the Table. 1.1. Note that only the highest theoretical performance indicators are specified (max down-link and up-link speeds).

|                                            | GSM             | EDGE               | WCDMA | HSPA                  | HSPA+          | LTE                      |

|--------------------------------------------|-----------------|--------------------|-------|-----------------------|----------------|--------------------------|

| Max down-link speed [bps]                  | 85.6 k          | 473.6 k            | 384 k | 14 M                  | 56 M<br>(MIMO) | 326 M<br>(4x4 MIMO)      |

| Max up-link speed [bps]                    | 42.8 k          | 473.6 k            | 384 k | 5.7 M                 | 22 M           | 86 M<br>(64-QAM)         |

| Latency<br>(round trip) [ms]               | 600             | 600 300 150 100 50 |       | 10                    |                |                          |

| Channel<br>bandwidth [Hz]                  | 200 k           | 200 k              | 5 M   | 5 M 5 M 5 M 1.5 M - 2 |                | 1.5 M - 20 M             |

| Duplex schemes                             | FDD FDD FDD FDD |                    | FDD   | FDD, TDD              |                |                          |

| Access schemes (up-link)                   | TDMA<br>FDMA    | TDMA<br>FDMA       | CDMA  | CDMA                  | CDMA           | SC-FDMA                  |

| Modulation types<br>supported<br>(up-link) | GMSK            | 8-PSK              | QPSK  | BPSK<br>QPSK          | 16-QAM         | QPSK<br>16-QAM<br>64-QAM |

Table 1.1: Comparison of selected mobile systems.

The linear PA has to operate with a sufficient power back-off in order to amplify signals with a high PAR otherwise the output signal will be distorted. This degrades the

PA efficiency. On the other hand, the phase modulated PA always operates at its peak efficiency. The peak PA efficiency is not an important performance indicator because the output signal only seldom reaches the maximum. More important is the average efficiency that is calculated based on the probability distribution function of the power in the given system (EDGE, WCDMA etc.). The average efficiency is directly related to the mobile device efficiency in the wireless network.

The consequence of the varying amplitude modulation is that the PA has to be linear. Any non-linear effects which disturb the amplitude signal will cause errors in data and a distortion in the adjacent channels. Switch-mode PAs offer a high efficiency but they are highly non-linear. By using a linearization technique they can be utilized in modern wireless transmitters. Because the amplitude modulated signal can not be directly applied to the RF input port as in a linear PA, a switch-mode PA has to use a different method to combine the amplitude and phase modulated signals. Usually it is done using the polar transmitter topology.

In this thesis a new approach for amplifying modulated varying envelope signals is presented. The whole work is focused on switch-mode RF PAs that are attractive due to their high efficiency. The proposed concept of "cascode modulated class-E PA" was practically implemented in CMOS technology and tested with EDGE and WCDMA signals. Digital predistortion is used to linearize the PA in order to meet the linearity requirements imposed by the EDGE and WCDMA standards.

#### 1.2 Organization of the thesis

The thesis is organized as follows. Chapter 2 explains the fundamental aspects of RF power amplifiers. The basic classes of operation are briefly introduced. Then the most important figures of merit of the PAs are discussed. Particular attention is given to the PA efficiency analysis. Linearity aspects of the RF PAs are explained.

In Chapter 3 linear transmitters using switch-mode PAs are discussed. The chapter starts with the description of three different topologies which can be used to accommodate switch-mode PAs to amplify varying amplitude signals. First two methods, which are based on the pulse width modulation (PWM) technique and linear amplification using non-linear components (LINC) technique, are introduced in brief. The third method, polar transmitters, is explained in detail because it was used in the experimental work. State-of-the-art approaches of polar modulate PAs are shown.

Chapter 4 handles the class-E PA analysis and design. The principles of operation of the class-E amplifier are explained and the architectural design issues are discussed. The chapter starts with an analytical section where the operation of the class-E amplifier is mathematically described. Later non-idealities that significantly influence the behavior of the class-E amplifier are introduced. The chapter is concluded with a small section on the impedance transformation.

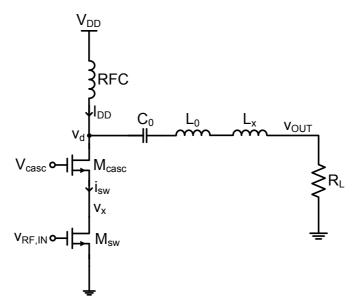

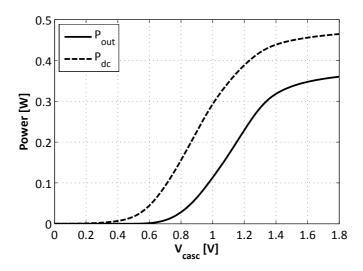

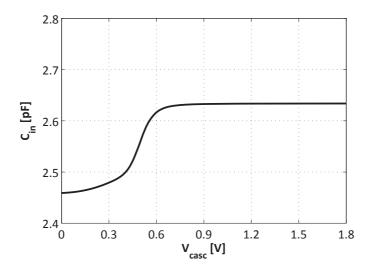

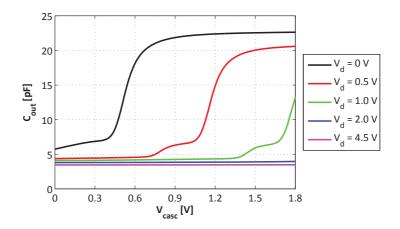

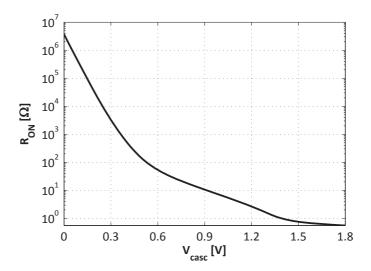

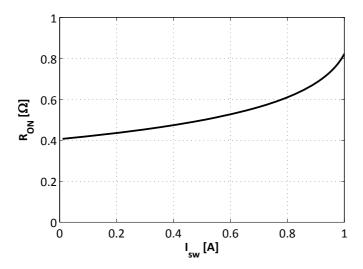

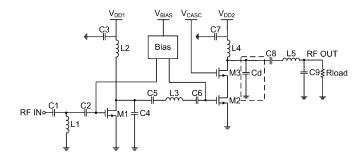

Chapter 5 discuss various aspects of the cascode modulated class-E PA. The simulated performance of the simplified cascode class-E PA is shown. The main part of the chapter is the analysis of design aspects and trade-offs in the cascode class-E PA.

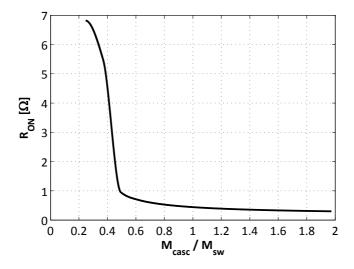

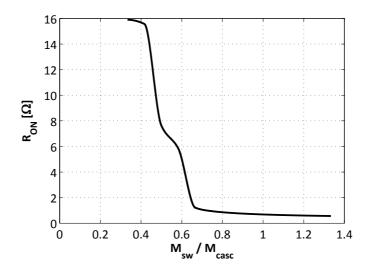

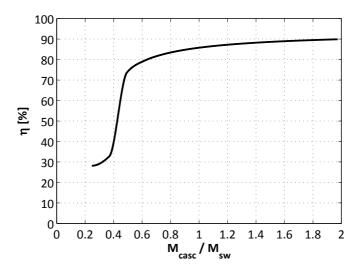

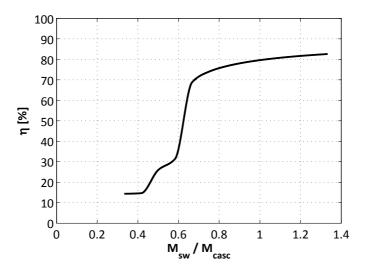

The focus is on the study of how the sizing of the cascode transistors influences the input and output capacitance, ON resistance, drain efficiency and the PA driving requirements. The reliability issues of CMOS class-E PAs are described with particular focus on the reliability of the proposed cascode modulated class-E PA.

In Chapter 6 various models of the cascode modulated PA are discussed. Firstly, the current RF analysis of the cascode class-E PA is performed. Then two DC models are proposed. The last step in the cascode class-E PA modeling is the analytical model. The goal of the modeling is to analytically describe the transfer function of the PA and to understand the distortion mechanisms in the cascode modulated PA.

Chapter 7 presents the experimental results of the implemented cascode modulated class-E PA in CMOS technology. The suitability of the cascode class-E PA concept for PA power control is firstly demonstrated. In the second part of the chapter the measured results of the cascode modulated class-E PA using EDGE and WCDMA test signals are shown. The simulated and measured results are compared. In addition, the digital predistortion linearization technique is described. The digital predistortion technique is used to linearize the PA. The performance with and without the digital predistortion is compared.

Chapter 8 summarizes the thesis and also provides ideas for possible future research in the area of CMOS polar PAs.

# Fundamentals of RF PAs

| Contents | S     |                                                            |           |

|----------|-------|------------------------------------------------------------|-----------|

| 2.1      | Trar  | nsconductance PAs                                          | 6         |

|          | 2.1.1 | Class-A                                                    | 6         |

|          | 2.1.2 | Classes AB, B and C                                        | 8         |

|          | 2.1.3 | Class-F                                                    | 10        |

| 2.2      | Swit  | tch-mode PAs                                               | 11        |

|          | 2.2.1 | Class-D                                                    | 11        |

|          | 2.2.2 | Class-E                                                    | 13        |

| 2.3      | Figu  | res of merit                                               | <b>15</b> |

|          | 2.3.1 | Output power                                               | 15        |

|          | 2.3.2 | Efficiency                                                 | 16        |

|          | 2.3.3 | Output power and efficiency of amplitude modulated signals | 17        |

|          | 2.3.4 | Linearity                                                  | 20        |

|          |       | 2.3.4.1 Amplitude and phase distortion                     | 21        |

|          |       | 2.3.4.2 IMD                                                | 23        |

|          |       | 2.3.4.3 ACLR                                               | 27        |

|          |       | 2.3.4.4 EVM                                                | 27        |

The PAs can be divided into several groups according to linearity, efficiency, frequency, technology and output power. Traditionally, the PAs are divided into two groups: linear and switch-mode PAs. The common characteristic of all the PAs is that the most linear classes are the least efficient.

In the linear class the power transistor operates as a transconductor. One can expect that in the linear PA the output power is a linear function of the input power. This is literally true only for the class-A PAs and as it is shown further, not all linear PAs exhibit a high linearity. Therefore, a better name for this group of PAs would be the transconductance PAs.

In the switch-mode class the power transistor operates as a switch. Sometime these PAs are referred to as saturated or non-linear. The switching PAs are very efficient but they require harmonic filtering at the output in order to obtain the desired output signal.

The first part of this chapter will describe the basic types of RF PAs. The second part will introduce the common figures of merit of the PAs.

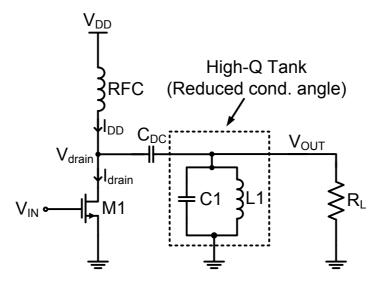

**Figure 2.1:** Simplified circuit of class-A amplifier (dashed LC tank is used for reduced conduction angle operation).

#### 2.1 Transconductance PAs

In these PAs the active device operates as a transconductor or simply as a voltage controlled current source. The transconductance PAs are divided into classes A, AB, B and C. Class-F is usually assigned as a switch-mode PA, but the active device of class-F PA operates as a transconductor (unless it is driven very hard) and therefore it should belong to the transconductance PAs.

#### 2.1.1 Class-A

The class-A PA is biased in such a way that the active device is always ON and it always conducts a quiescent current. The conduction angle, which represents the time of the RF cycle when the PA is ON, is  $360^{\circ}$ . The idealized class-A amplifier is shown in Fig. 2.1.

If the active device exhibits a linear transconductance characteristic, the output waveform has no distortion. Therefore, the output power can be expressed as

$$P_{out} = \frac{V_{out}^2}{2R_L} \tag{2.1}$$

where  $V_{out}$  is the amplitude of the output RF voltage and  $R_L$  is the load. Note that the harmonic filter at the PA output is not needed (in ideal operation) because the output signal contains only the fundamental component (see Fig. 2.2). In order to calculate the drain efficiency the DC power drawn from the supply has to be known. This can be written as

$$P_{DC} = V_{DD}I_{DD} = \frac{V_{DD}^2}{2R_L} \tag{2.2}$$

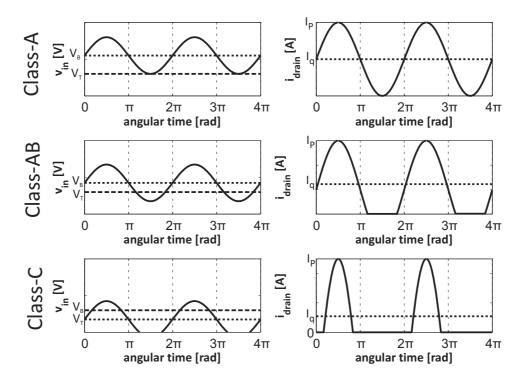

**Figure 2.2:** Illustration of input and output waveforms of class-A, AB and C amplifiers.  $V_T$  is the threshold voltage of the active device and  $V_B$  is the bias voltage of the amplifier.  $I_p$  is the peak current and  $I_q$  is the quiescent drain current through the output device.

where  $V_{DD}$  and  $I_{DD}$  are the supply voltage and the supply current respectively. It is assumed that the quiescent current is chosen to maximize the output voltage swing and equals to  $V_{DD}/R_L$ . Finally the maximum drain efficiency is equal to

$$\eta_{max} = \frac{P_{out,max}}{P_{DC}} = \frac{1}{2} \frac{V_{out,max}^2}{V_{DD}^2} = \frac{1}{2} \left(\frac{V_{DD}}{V_{DD}}\right)^2 = 50\%$$

(2.3)

where it is assumed that the maximum amplitude of the output voltage equals to  $V_{DD}$ . Practically the drain efficiency will be even lower because the maximum output voltage swing is decreased by the necessary drain-source voltage needed to keep the MOS transistor in the saturated region. The drawback of the high quiescent current is therefore low peak drain efficiency. The DC power (it is constant and independent of the output power) which is not converted into the RF power has to dissipate in the PA (in the form of heat). The heat dissipation is highest when the output power is low.

If the active device exhibits a non-linear transconductance, for example the square law characteristics as in the CMOS transistor, then the drain current through the power

transistor will be distorted. This can be seen from

$$i_{d} = K v_{in}^{2} = K (V_{B} + V_{in} \sin(\omega t))^{2}$$

$$= K V_{B}^{2} + \frac{1}{2} K V_{in}^{2} + 2 K V_{B} V_{in} \sin(\omega t) + \frac{1}{2} K V_{in}^{2} \cos(2\omega t)$$

(2.4)

where  $V_B$  is the bias voltage and K is a constant. It can be seen that the drain current has beside the DC and fundamental components also the second harmonic component. Therefore, the harmonic filter at the output of such a class-A PA is needed to select the fundamental component. The linearity of the PA using the square law transconductance active device is deteriorated compared to the linear transconductance active device but the peak drain efficiency increased to 66.7% [Cripps 2002].

#### 2.1.2 Classes AB, B and C

One possibility to increase the efficiency of the class-A amplifier is to limit the conduction angle. If the transistor doesn't have to conduct during the whole RF period it will be more efficient. The class-AB PA has a conduction angle between  $180^{\circ}$  and  $360^{\circ}$ .

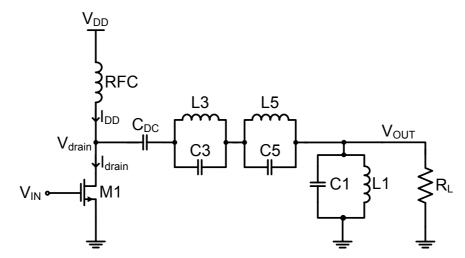

The topology of the class-AB amplifier is the same as for class-A amplifier with the exception that the class-AB amplifier requires an output harmonic filter (Fig. 2.1). If the output resonant tank has a high quality factor, the output voltage will be a sine wave.

The conduction angle is adjusted by the bias voltage (Fig. 2.2). As the input voltage drops below the threshold voltage the drain current goes to zero. The conduction angle is directly related to the quiescent current (Fig. 2.2) of the PA. The lower conduction angle is a result of the lower input bias voltage and this will lead to the lower quiescent device current

By decreasing the conduction angle even further the efficiency is improved but the linearity decreases. Class-B amplifier is defined as an amplifier with conduction angle of  $180^{\circ}$ .

In the class-B amplifier half of the output signal is clipped every RF cycle compared to the class-A amplifier. This will produce even components in the output signal but no odd harmonics. The main advantage of class-B amplifier is that the output power level of the fundamental tone is the same as in class-A amplifier but the peak drain efficiency is increased to 78.5 % due to the reduced DC current [Albulet 2001].

The DC input power and the drain efficiency of the class-B amplifier can be expressed as [Albulet 2001]

$$P_{DC} = V_{DD}I_{DD} = \frac{2}{\pi} \left(\frac{V_{DD}}{R_L}\right) V_{drain} \tag{2.5}$$

$$\eta_{max} = \frac{P_{out,max}}{P_{DC}} = \frac{\pi}{4} \left( \frac{V_{drain,max}}{V_{DD}} \right) = \frac{\pi}{4} = 78.5\%$$

(2.6)

where  $V_{drain}$  is the amplitude of the RF voltage across the active device.

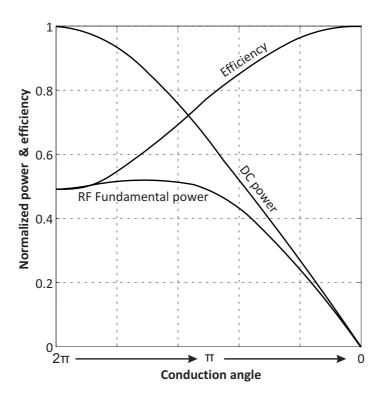

**Figure 2.3:** The comparison of RF Fundamental output power, drain efficiency and DC power as a function of conduction angle.

It is important to note, that the class-B amplifier exhibits only one half of the gain of a class-A amplifier and therefore it requires a 6 dB higher input drive level in order to deliver the same output power and to keep the same peak transistor current [Cripps 2006].

Further reduction of the bias voltage results in a conduction angle below 180° and this is the area of operation of the class-C amplifier. This amplifier can theoretically achieve 100% drain efficiency but it will deliver no RF output power (Fig. 2.3). This can be explained by that the reduction of the bias voltage leads to a very high drain current peak (if the output power has to be maintained). The maximum current is limited by the safety operation area of the device. Therefore, for a given maximum drain current the output power and the quiescent current are decreasing with decrease of the conduction angle. The 100% drain efficiency is achieved but the output power and the DC power goes to zero [Reynaert & Steyaert 2006]. The application of class-C amplifiers in low voltage CMOS technologies is limited due to the low output power. The comparison of RF output power, efficiency and DC power is shown in Fig. 2.3.

The class-AB PA is often used in wireless communication transmitters because it is more efficient than the class-A amplifier and it still maintains a high linearity (compared to the class-B or class-C amplifiers) [Cripps 2002]. The class-C amplifier can be used in such applications that don't require the linear amplification (for example amplifying

Figure 2.4: Simplified circuit of the class-F amplifier.

CW or FM signals).

#### 2.1.3 Class-F

The main idea used in class-F amplifiers is that by the proper harmonic terminations, the drain voltage and current waveforms have no overlap what will result in minimized power losses in the active device. The schematic of a class-F PA is shown in Fig. 2.4.

If the drain voltage is square wave like then the instantaneous overlap between the drain voltage and current is minimized and there is no power loss in the power transistor. The square waveform contains ideally no even harmonics but an infinite number of the odd harmonics. Therefore, by choosing the output network which filters out all even harmonics and is open for odd harmonics, the square waveforms can be achieved.

Practical implementations are usually using third and fifth harmonics what is sufficient to produce significant improvement in the drain efficiency [Reynaert & Steyaert 2006]. The active device of such amplifier can not be substituted by a switch (switch will produce infinite number of harmonics) and therefore the class-F PA with limited harmonics peaking is as biased as the class-B PA.

The main drawbacks of the class-F PA implementation in the CMOS technology are as follows. In order to shape the harmonics at the output of the active device the harmonics must be present in the active device output current. The problem is that the large output capacitance will provide a low-impedance path for the higher harmonics and the squaring process will be less pronounced. If the third and fifth harmonic peaking is used the theoretical drain efficiency is 88 % and 92 % respectively [Reynaert & Steyaert 2006]. Another drawback is that the implementation of the output network in CMOS is difficult and might not be even feasible (several high quality resonant tanks or a  $\lambda/4$  transmission line are needed).

Figure 2.5: Simplified circuit of the class-D amplifier.

#### 2.2 Switch-mode PAs

The switch-mode PAs are divided into two main classes D and E. The common characteristic of the switch-mode amplifiers is that the active device operates as a switch. In the ideal switch there is no overlap of current and voltage waveforms and this leads to the theoretical  $100\,\%$  drain efficiency. The main drawback of the switching PAs is that the linearity is completely lost. This is a consequence of operating the active device as an ideal switch which has only two (ON/OFF) states. These amplifiers are not-suitable for the amplitude modulated signals. In order to use them to amplify varying envelope signals a linearization technique has to be used.

#### 2.2.1 Class-D

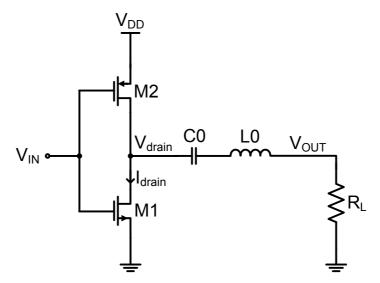

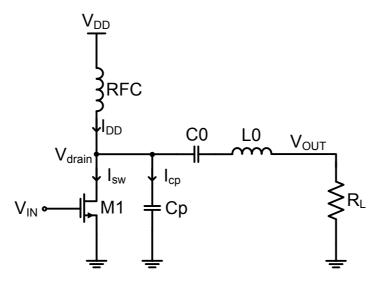

The schematic diagram of a class-D amplifier is shown in Fig. 2.5. The series resonant output network is connected to the push-pull circuit. The active devices are working in anti-phase (one device is ON and the second device is OFF). The output network is alternately connected to the DC supply voltage or to the ground. The waveforms of the class-D amplifier are shown in Fig. 2.6.

It can be seen that the voltage at the drain of the transistors is a square wave. The output current is sinusoidal due to the series resonant output circuit which is tuned to the fundamental frequency. The positive half of the sine wave is conducted by the top switch M2 and the negative by the bottom switch M1.

The output current is sinusoidal at can be written as [Albulet 2001]

$$i_{out}(\phi) = \frac{2}{\pi} \left( \frac{V_{DD}}{R_L} \right) \sin(\phi)$$

(2.7)

Figure 2.6: Drain voltage and current waveforms of the class-D amplifier.

where  $\phi$  is angular time given as  $(\omega t + \varphi)$ . The output power is given by

$$P_{out} = I_{DD}(I_{DD}R_L) = \frac{2}{\pi^2} \frac{V_{DD}^2}{R_L}$$

(2.8)

The DC power can be calculating according to

$$P_{DC} = V_{DD}I_{DD} = V_{DD} \left( \frac{1}{2\pi} \int_{n=0}^{2\pi} i_1(\phi)d\phi \right) = V_{DD} \left( \frac{2}{\pi^2} \frac{V_{DD}}{R_L} \right) = \frac{2}{\pi^2} \frac{V_{DD}^2}{R_L}$$

(2.9)

and the maximum drain efficiency can be expressed as

$$\eta_{max} = \frac{P_{out}}{P_{DC}} = 100\%$$

(2.10)

Several circuit modifications of the class-D amplifier are known [Albulet 2001]. These modifications include the transformer coupled voltage or current output circuit.

The main difficulty of implementing class-D RF PA in CMOS technology is decreased efficiency. It is assumed that the active devices in Fig. 2.5 operate as ideal switches. Such large transistors have large parasitic output capacitances that have to be charged and discharged every RF cycle. This energy will be dissipated in the switch. Large output capacitance will also limit the usable operation frequency. Furthermore, the finite turn-on and turn-off time will increase the power losses because the voltage and current waveforms will overlap. Class-D requires a high driving power because of the large input capacitance (two transistors has to be driven).

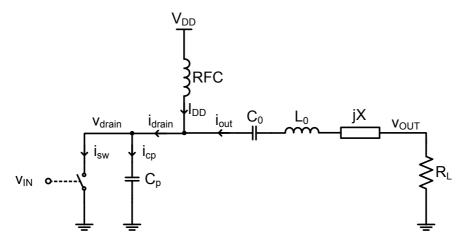

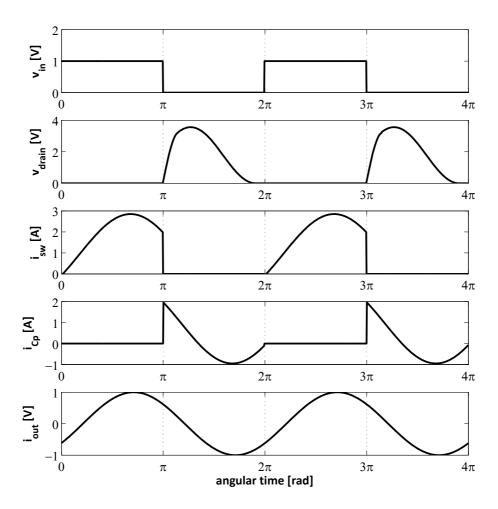

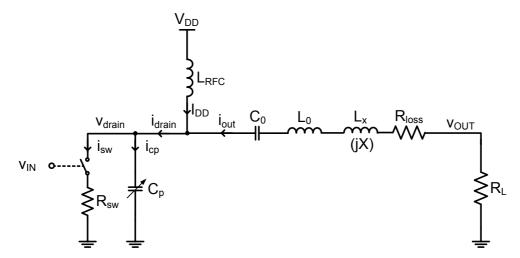

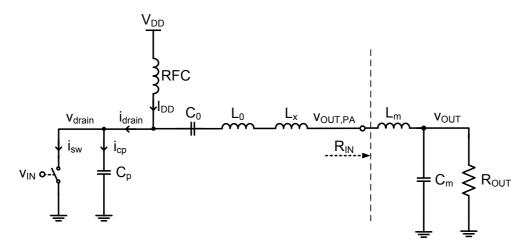

Figure 2.7: Simplified circuit of the class-E amplifier.

#### 2.2.2 Class-E

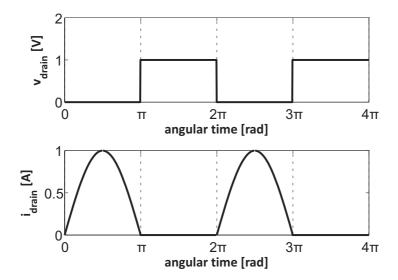

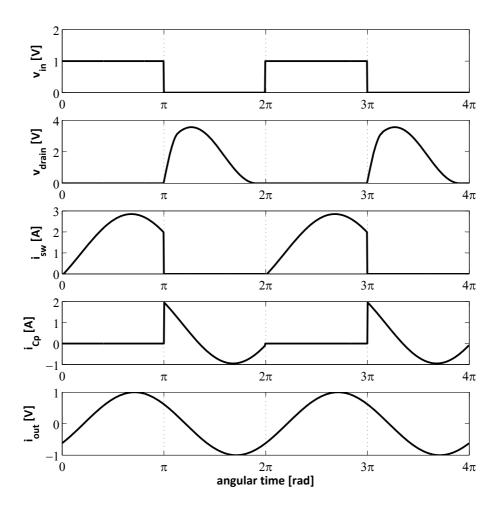

Another type of the switch-mode amplifier is the class-E amplifier. It can achieve theoretically  $100\,\%$  drain efficiency as the class-D amplifier, but its concept is based on a completely different approach. The basic topology of the class-E PA is shown in Fig. 2.7.

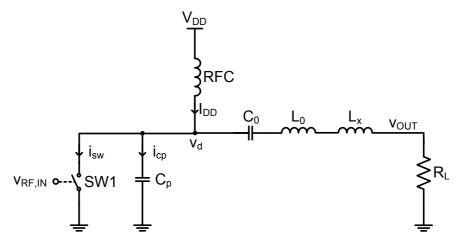

The basic class-E amplifier utilizes a single transistor which acts as a switch (M1). The output network consists of series resonant circuit (C0 and L0) and shunt capacitor (Cp). The main advantage of the class-E is that the parasitic output capacitance of the active device becomes an element in the output network design. In the previously described classes the parasitic output capacitance of the active device is unwanted and it degrades the performance of the PA. The class-E amplifier requires a small number of passive components (especially compared to the class-F amplifier) what makes it a promising candidate for the CMOS integration.

The role of the output network in class-E amplifier is to shape the drain voltage and device current in such way that there is no instantaneous overlap between them. The basic equations of class-E amplifier are derived in Section 4.1. One of the first detailed mathematical analysis can be found in [Raab 1977]. Very comprehensive analysis of class-E PA can be also found in this book [Albulet 2001]. The class-E PA can be analyzed from various perspectives (duty cycle ratio, finite turn-on and turn-off times, parasitic resistance and inductance of the active device, quality of the output resonant tank, finite RF choke inductance and etc.). Even though the analysis is based on very simplified circuit and assumptions the mathematical derivations are still very complex.

There are three conditions which have to be fulfilled in order to achieve a high efficiency. The first is called the zero voltage switching (ZVS) condition and the second is zero voltage derivative switching (ZVDS) condition. The ZVS condition dictates that the voltage across the switch has to be zero in the instance the switch goes ON. The

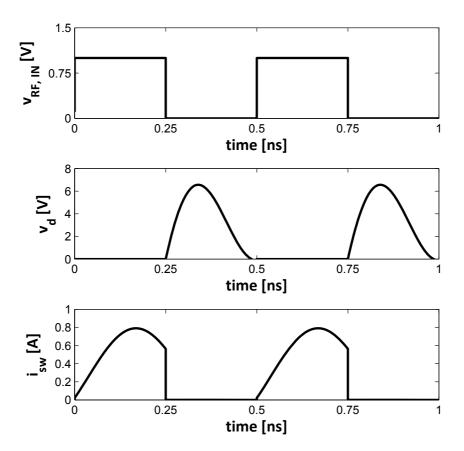

Figure 2.8: The waveforms of the class-E amplifier.

ZVDS condition says that also the derivative of the voltage across the switch has to be zero. These two condition guarantee that the power loss during the switch turn-on is minimized. The third condition is that the rise of the voltage across the switch has to be delayed until the switch is turned OFF to reduce the turn-off transition loss. A more broaden definition of the conditions, provided by the founders of class-E PA, can be found in [Sokal & Sokal 1975]. If the amplifier meets the three conditions it is called an optimum class-E amplifier.

Fig. 2.8 shows the ideal waveforms of the class-E amplifier. It is assumed that the input signal is a square wave with 50% duty cycle.

It can be seen that there is no instantaneous overlap of  $V_{drain}$  and  $I_{sw}$  and therefore the switch operates losslessly. When the switch is ON the current flowing through the active device is equal to the DC current  $(I_{DD})$  minus the output current  $(i_{out})$ . When the switch is turned OFF the DC current minus the output current will charge the

shunt capacitor  $C_d$ . The shape of the drain voltage of the active device in the OFF state, which equals to the voltage across the capacitor  $C_d$ , is controlled by the output network. The output network is designed to turn the voltage across  $C_d$  back to zero (fully discharge the  $C_d$ ) before the switch is again turned ON. The output current  $i_{out}$  is filtered by the ideal series resonant circuit and therefore it is assumed to be sinusoidal. It can be seen from Fig. 2.7 that the sinusoidal output current is a sum of partial sinusoid currents through the switch (during ON state) and through the shunt capacitor  $C_d$  (during OFF state).

It is important to note that the class-E is designed in the time domain because the behavior of the class-E (shapes of device voltage and current waveforms) is described in the time domain (by ZVS and ZVDS conditions).

The main drawback of the class-E amplifier is that the drain voltage peak (during the OFF state) is very high, theoretically  $3.6\,V_{DD}$  [Sokal & Sokal 1975]. This represents a serious reliability problem. A transistor with a high break-down voltage is needed or another special technique (like transistors stacking) can be used to relieve the voltage stress of the active device. More on reliability is in Section 5.5.

#### 2.3 Figures of merit

In this section some basic figures of merit of PAs are introduced. Firstly typical parameters of PAs like the output power, power added efficiency (PAE) and peak-to-average power ratio (PAR) are explained. Selected topics on the PA linearity are discussed including AM-AM, AM-PM, harmonic distortion, intermodulation distortion (IMD), adjacent channel leakage ratio (ACLR) and error vector magnitude (EVM).

#### 2.3.1 Output power

The instantaneous output power can be calculated as

$$p_{out}(t) = v_{out}(t)i_{out}(t) \tag{2.11}$$

where  $v_{out}(t)$  and  $i_{out}(t)$  are instantaneous output voltage and current respectively. The average output power can be written as

$$P_{out} = \overline{p_{out}(t)} = \lim_{T \to \infty} \frac{1}{T} \int_{-T/2}^{T/2} p_{out}(t) dt$$

(2.12)

where  $\overline{p_{out}(t)}$  represents the average of the instantaneous output power. If it is not stated otherwise, in this work under the output power we understand the average output power. If the output signal is periodical with the period given by

$$T_0 = \frac{2\pi}{\omega} \tag{2.13}$$

where the angular frequency  $\omega$  is defined as  $\omega = 2\pi f_c$ . The average power of a periodic signal can then be calculated using

$$P_{out} = \frac{1}{T_0} \int_{-T_0/2}^{T_0/2} p_{out}(t) dt$$

(2.14)

The average power delivered to a purely resistive load can also be calculated from the current and the voltage signal according to

$$P_{out} = \frac{V_{out,RMS}^2}{R_L} = I_{out,RMS}^2 R_L$$

(2.15)

where  $V_{out,RMS}$  and  $I_{out,RMS}$  are the RMS values of the output voltage and the current respectively.

#### 2.3.2 Efficiency

In general, the term efficiency signifies how efficiently the PA is converting the DC power from the supply to the RF output power. The DC power drawn from the supply can be simply expressed as

$$P_{DC} = \frac{1}{T} \int_{0}^{T} V_{DD} i_{dd} dt = \frac{V_{DD}}{T} \int_{0}^{T} i_{dd} dt = V_{DD} I_{DD}$$

(2.16)

The more specific DC power calculation can be obtained for each PA class. The drain efficiency is defined as

$$\eta = \frac{P_{out}}{P_{DC}} \tag{2.17}$$

where  $P_{out}$  is the average output power at the fundamental frequency. Usually every PA consists of the output stage and at least one driver stage. The driver stage consumes also the DC power from the supply and therefore taking this into consideration, the total drain efficiency can be calculated according to

$$\eta_{tot} = \frac{P_{out}}{P_{DC,PA} + \sum_{i=0}^{n} P_{DC,DRV_i}}$$

(2.18)

where n is the number of driver stages.

The drawback of drain efficiency is that it doesn't depend on the gain of the PA. If two PAs have the same output power and draw the same DC power they still might have different gain and input power. Hence, a different concept is often used to characterize

the efficiency of the PA. It is called PAE (Power Added Efficiency) and it is defined as

$$PAE = \frac{P_{out} - P_{in}}{P_{DC,PA} + \sum_{i=0}^{n} P_{DC,DRV_i}}$$

(2.19)

where  $P_{in}$  is the available input power. If the power gain is defined as

$$G_P = \frac{P_{out}}{P_{in}} \tag{2.20}$$

then the equation 2.19 can be rewritten as

$$PAE = \eta_{tot} \left( 1 - \frac{P_{in}}{P_{out}} \right) = \eta_{tot} \left( 1 - \frac{1}{G_P} \right)$$

(2.21)

It can be seen that if the two PAs have the same output power and DC power, the PA which has a higher gain will have a higher PAE.

In the previous section the peak drain efficiencies of a different PA classes were given. In some classes this efficiency was  $100\,\%$ . But the total drain efficiency and PAE of the PA are always below  $100\,\%$ . The PAs are usually characterized by both PAE and drain efficiency.

#### 2.3.3 Output power and efficiency of amplitude modulated signals

The previous analysis is valid for the constant envelope signals. If an amplitude modulated signal is applied to the PA both the output power and the efficiency are also functions of the varying envelope signal.

The output is varying according to the amplitude modulated signal. This variation can be described by parameters like Crest Factor (CF) in case of voltage signals and by Peak to Average Power Ratio (PAPR) when the power signals are handled. The PAPR is defined as

$$PAPR = \frac{PEP}{P_{out}} \tag{2.22}$$

where PEP stands for Peak Envelope Power and  $P_{out}$  is the average output power of the amplitude modulated signal. The peak envelope power is defined as the average power supplied to the antenna transmission line by a transmitter during one RF cycle at the crest of the modulation envelope, under normal operating conditions [ITS 1996]. The PEP of the PA can be expressed as

$$PEP = max\{P_{out}\} = \frac{max\{v_{out}^2(t)\}}{R_L} = \frac{V_{out}^2}{R_L}$$

(2.23)

where  $V_{out}$  is the amplitude of the output voltage signal  $v_{out}$ . The average output

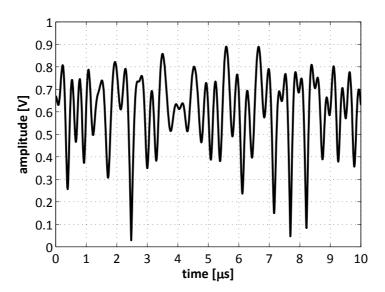

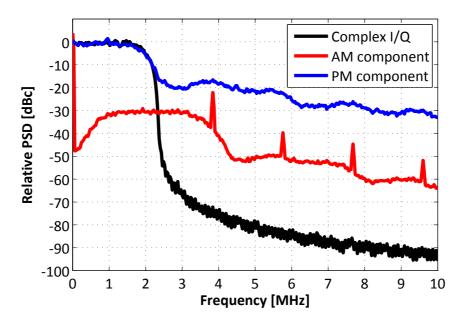

Figure 2.9: The AM component of the WCDMA signal.

power of the PA can be calculated as

$$P_{out} = \frac{V_{out,RMS}^2}{R_L} = \frac{1}{2} \frac{V_{out}^2}{R_L}$$

(2.24)

where a sinusoidal output signal is assumed. The Crest Factor (CF) is defined as the peak amplitude divided by the RMS value of the waveform

$$CF = \frac{max\{v_{out}\}}{V_{out,RMS}} = \frac{V_{out}}{V_{out,RMS}}$$

(2.25)

Fig. 2.9 shows the example of the time varying amplitude modulated component of the WCDMA signal. The PAPR equals to  $PAPR=CF^2$  according to

$$PAPR = \frac{\frac{V_{out}^2}{R_L}}{\frac{V_{out,RMS}^2}{R_L}} = \frac{V_{out}^2}{V_{out,RMS}^2} = (CF)^2$$

(2.26)

If both PAPR and CF are in dBs then PAPR = CF according to

$$PAPR[dB] = 10 \log \frac{V_{out}^2}{V_{out,RMS}^2} = 20 \log \frac{V_{out,max}}{V_{out,RMS}} = CF[dB]$$

(2.27)

The CF of some selected signals can be find below in the Table. 2.1.

Generally, the efficiency of the PA which has to transmit a signal with a high PAPR will be much lower than the peak efficiency of the PA when it is saturated. The linear PA which has to amplify a modulated signal with high PAPR has to be capable to

|                   | DC | Sine wave | Two-tone | QPSK    | 16-QAM | 64-QAM | OFDM |

|-------------------|----|-----------|----------|---------|--------|--------|------|

| Crest Factor [dB] | 0  | 3.01      | 3 - 6    | 3.5 - 4 | 6.7    | 7.7    | 12   |

Table 2.1: Crest factor comparison of various waveforms.

transmit the PEP but the average output power will be much lower. The input power of the linear PA has to be decreased according to the PAPR of the modulated signal so that the signal can be transmitted without pushing the PA into saturation. This mode of operation is called power back-off. The power back-off linearization technique significantly decreases the overall efficiency of the PA and it is one of the major reasons why the linear PAs have such a low efficiency when they transmit complex modulated wireless signals with a high PAPR.

The efficiency of a PA is a function of the varying envelope signal (A(t)). Generally, the efficiency is always a function of the output power. Because the amplitude modulation modulates the output power it will also change the efficiency. To characterize this effect one can define the average drain efficiency as [Reynaert & Steyaert 2006]

$$\eta = \langle \eta(A(t)) \rangle = \lim_{T \to \infty} \frac{1}{T} \int_{-T/2}^{T/2} \eta(A(t)) dt$$

(2.28)

Notice that the equation obove gives an arithmetic average of drain efficiency and it is different from average efficiency calculated based on Eq. (2.17).

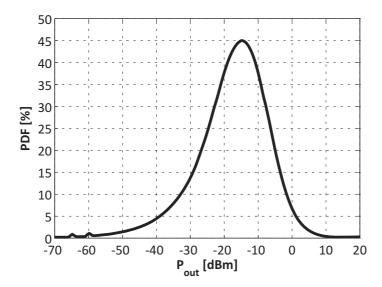

Another effect which directly influences the overall efficiency is the probability distribution function (PDF) of the output power. The average output power level is usually set by the base station which is constantly evaluating the quality and power of the received signal. The active power control can be used to increase the battery life time of a mobile device but it can also be used by the wireless network to maximize its capacity (WCDMA). The period of the power level adjustment is different for each mobile standard. The PDF of the output power is obtained by long term measurements and it is usually specified for the different network environments (urban or rural). An example of the output power PDF in EDGE/WCDMA is shown in Fig. 2.10.

The drain efficiency can be expressed as a function of the PDF according to

$$\eta = \frac{\int\limits_{P_{out,min}}^{P_{out,max}} P_{out} PDF(P_{out}) dP_{out}}{\int\limits_{P_{out,min}}^{P_{out,min}} \frac{P_{out}}{\eta(P_{out})} PDF(P_{out}) dP_{out}}$$

(2.29)

**Figure 2.10:** PDF versus output power of the WCDMA mobile station transmitter [Hamalainen *et al.* 1999].

#### 2.3.4 Linearity

Linearity is one of the most important figures of merit of PAs. There are several ways to characterize the linearity, such as AM-AM and AM-PM distortion, intermodulation distortion (IMD), adjacent channel leakage ratio (ACLR), error vector magnitude (EVM), total harmonic distortion (THD) and third order intercept point (IP3). The non-linearity of a PA has to be properly classified and evaluated as a figure of merit.

One of the most basic PA metrics is 1 dB compression point (P1dB). It is defined as the output power level  $P_{out,-1dB}$  corresponding to 1 dB deviation from the ideal linear behavior. It can be also referred to the input power level  $P_{in,-1dB}$ . The  $P_{out,-1dB}$  usually specifies the maximum linear output power of the PA and  $P_{in,-1dB}$  specifies what is the maximum input drive of the PA to operate still in linear region. The disadvantage of this metric is that it is not a very accurate indicator for complex modulated signals because it is based on a single-tone measurement and it can not provide information about the spectral regrowth near the carrier frequency.

Another linearity figure of merit used often in the low frequency amplifiers is the total harmonic distortion (THD). It is defined as the sum of the power of harmonic components to the power in the fundamental. Mathematically it can be written as

$$THD = \frac{\sum_{n \ge 2}^{\infty} P_{out,n}}{P_{out,1}} \tag{2.30}$$

where the n represents the number of harmonics considered in the simulation or measurements and  $P_{out,1}$  is the power at the fundamental frequency. The THD is usually expressed in dBc units.

#### 2.3.4.1 Amplitude and phase distortion

The amplitude and phase distortion are the consequence of the PA transfer characteristic nonlinearity. Assume that the transfer function of the PA is approximated by a third-order polynomial

$$y(t) = a_1 x(t) + a_2 x^2(t) + a_3 x^3(t)$$

(2.31)

where x(t) and y(t) are the input and output signals of the PA respectively and  $a_1 - a_3$  are constants. Suppose that the input signal is a sinusoid of this form

$$x(t) = A\cos(\omega_c t) = \frac{1}{2}(e^{j\omega_c t} + e^{-j\omega_c t})$$

(2.32)

The resulting output signal is thus

$$y(t) = a_1 A \cos(\omega_c t) + a_2 A^2 \cos^2(\omega_c t) + a_3 A^3 \cos^3(\omega_c t)$$

(2.33)

this can be further expanded as

$$y(t) = a_1 A \cos(\omega_c t) + a_2 A^2 \left(\frac{1 + \cos(2\omega_c t)}{2}\right) + a_3 A^3 \left(\frac{3\cos(\omega_c t) + \cos(3\omega_c t)}{4}\right)$$

$$(2.34)$$

finally the output can be written as

$$y(t) = \frac{1}{2}a_2A^2 + (a_1A + \frac{3}{4}a_3A^3)\cos(\omega_c t) + \frac{1}{2}a_2A^2\cos(2\omega_c t) + \frac{1}{4}a_3A^3\cos(3\omega_c t)$$

(2.35)

where the first term represents the DC offset (as a result of the second-order term in the transfer characteristic), the second term represents the linear amplification at the fundamental frequency, the third and fourth terms represent the second and third harmonic distortion respectively.

The output power at the fundamental frequency can be written as

$$P_{out,1} = \frac{1}{2R_L} V_{out,1}^2 = \frac{1}{2R_L} \left( a_1 A + \frac{3}{4} a_3 A^3 \right)^2$$

$$= \frac{1}{R_L} \frac{A^2}{2} \left( a_1 + \frac{3}{2} a_3 \left( \frac{A^2}{2} \right) \right)^2 = \frac{1}{R_L} P_{in} a_1^2 \left( 1 + \frac{3}{2} \frac{a_3}{a_1} (P_{in}) \right)^2$$

(2.36)

and the power gain at the fundamental frequency is

$$G = \frac{1}{R_L} a_1^2 \left( 1 + \frac{3}{2} \frac{a_3}{a_1} (P_{in}) \right)^2 \tag{2.37}$$

where  $P_{in}=A^2/2$  is the normalized input power per Ohm. The term  $a_1^2$  is the linear gain coefficient. The term  $3a_3/2a_1$  represents a gain compression factor (usually is  $a_3/a_1<0$  otherwise the PA would have gain expansion) and it is a cause of that the large signal gain G decreases with the input power. It can be seen that the output power and the power gain at the fundamental frequency are no longer linear functions of the input power.

The AM-AM and AM-PM characteristics show the relation of the output signal amplitude and phase on the input signal amplitude. An ideal linear PA has the output signal linearly dependent on the input signal and the output phase is independent of the input signal amplitude. Practically, a PA exhibits always some non-linearity. Therefore, with increasing the input signal level the PA goes into gain compression and the AM-AM will be nonlinear. Similarly the AM-PM response will be changed by increasing the input signal power. This can be mathematically described as

$$y(t) = F(A(t))\cos(\omega_c t + \phi(t) + \Phi(A(t)))$$

(2.38)

where A(t) is the amplitude of input signal. The F(A(t)) is a nonlinear function of A(t) and  $\Phi(A(t))$  is not constant with the input signal level. There is a non-linear relationship between the input and output amplitude (AM-AM) and between the output phase and input amplitude (AM-PM).

There are several ways to measure AM-AM and AM-PM characteristics. The AM-AM and AM-PM response of the PA can be measured using the CW input signal with a swept power level. This is referred to as large signal S-parameters where the input source is a large signal (high power) source.

Another approach is to calculate the AM-AM and the AM-PM characteristics using a real modulated signal. The distorted output signal of the PA can be recorded and demodulated by a vector signal analyzer (VSA). The original baseband (BB) signal is then compared with the measured signal and the AM-AM and the AM-PM functions are obtained.

The AM-PM response is not measured as an absolute value of the phase between the input and output signal but it is the change of the phase as a function of the input signal power.

It is possible to plot the AM-AM and AM-PM characteristics as a function of the DC bias or ambient temperature. When the modeling of the PA is the main objective then the AM-AM and AM-PM response can be measured in a pulse mode in order to minimize the temperature increase caused by the previous input signal power level.

The AM-AM and AM-PM characteristics are not sufficient to fully characterize the non-linearity of the PA. This is especially true if input signals with different bandwidths (BW) are applied to the PA. Modern mobile standards do not specify the requirements on the AM-AM or AM-PM functions (neither on the IMD products) and other indicators like the ACLR or EVM have to be used.

The AM-AM and AM-PM can be expressed from the transfer function only if the coefficients  $a_k$  (in Eq. 2.31) are complex values (otherwise there is no AM-PM). The main problem of using AM-AM and AM-PM curves as a non-linearity figure of merit is

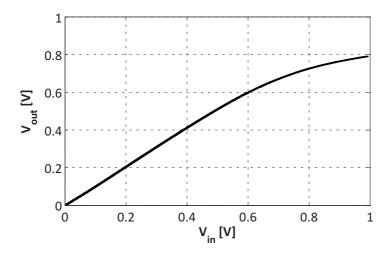

Figure 2.11: Example of AM-AM characteristic.

that they quantify the nonlinearity effect on the fundamental signal. The fundamental signal has a strong linear component and it might be difficult to precisely characterize the non-linear terms of the transfer function. The AM-AM and AM-PM curves are often used to linearize the PA.

### 2.3.4.2 IMD

In this subsection the intermodulation distortion (IMD) as a basic non-linearity figure of merit will be introduced. Single-tone tests are not sufficient to characterize the non-linearity of PAs because they don't provide any information about the PA behavior over the whole modulation band. Therefore, a two-tone test was introduced in order to investigate the PA non-linearity in the narrowband around the RF carrier. It can be used to investigate the amplitude and phase distortion of the PA.

By performing a two-tone test one can describe the intermodulation distortion (IMD) products and the spectral regrowth. The two test signals are individual single-tone signals. If the PA would have no distortion the output spectrum will contain only those two tones. The two-tone signal has a varying envelope in the time domain.

The PAPR parameter as a basic tool of characterizing varying envelope signals was described in Section 2.3.3. If the two-tone signal is defined as

$$s(t) = A\cos[(\omega_c - \omega_m)t] + B\cos[(\omega_c + \omega_m)t]$$

(2.39)

then the PAPR of the two tone signal can be calculated according to [Rouphael 2009]

$$PAPR[dB] = 10 \log \left(\frac{PEP}{P_{out}}\right) = 10 \log \left(\frac{(A+B)^2}{\frac{1}{2}(A^2+B^2)}\right)$$

(2.40)

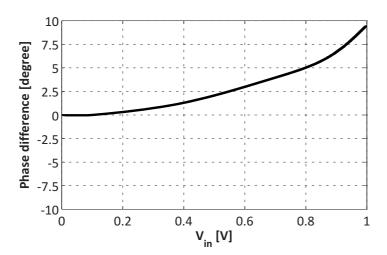

Figure 2.12: Example of AM-PM characteristic.

and if the two tones have equal power (A = B) then

$$PAPR[dB] = 10\log(4) \approx 6 dB \tag{2.41}$$

The result is that the two tone signal can represented the signals with PAPR lower than 6 dB (PAPR can be decreased by using a two tones unequal of unequal powers).

When the two-tone input signal is applied to the PA with second-order non-linearity the result is

$$x(t) = A\cos(\omega_1 t) + B\cos(\omega_2 t) \tag{2.42}$$

$$y(t) = K_1 x(t) + K_2 x^2(t)$$

(2.43)

$$y(t) = K_1[A\cos(\omega_1 t) + B\cos(\omega_2 t)] + K_2[A\cos(\omega_1 t) + B\cos(\omega_2 t)]^2$$

(2.44)

the second (quadratic) term can be expanded to

$$y(t) = K_2 \left[ A^2 \cos^2(\omega_1 t) + 2AB \cos(\omega_1 t) \cos(\omega_2 t) + B^2 \cos^2(\omega_2 t) \right]$$

$$= K_2 \left[ A^2 \left( \frac{1}{2} + \frac{\cos(2\omega_1 t)}{2} \right) + B^2 \left( \frac{1}{2} + \frac{\cos(2\omega_2 t)}{2} \right) + AB \cos(\omega_1 t \pm \omega_2 t) \right]$$

(2.45)

It can be seen that the output contains the two original tones, second harmonics and two additional tones at frequencies  $f_1 \pm f_2$ . These two additional tones are called second-order intermodulation products. These two tones are quite far away from the band of interest and therefore can be easily filtered.

The PA with third-order non-linearity will produce at the output these six additional

tones compared to the previous case

$$f_{IM3a} = 3f_1$$

$$f_{IM3b} = 3f_2$$

$$f_{IM3c} = 2f_1 + f_2$$

$$f_{IM3d} = f_1 + 2f_2$$

$$f_{IM3e} = 2f_1 - f_2$$

$$f_{IM3f} = f_1 - 2f_2$$

(2.46)

where the tones at frequencies  $2f_1 \pm f_2$  and  $f_1 \pm 2f_2$  will fall usually very close to the signal band of the PA and it is difficult to filter them out. They are called third-order intermodulation products (IMD3).

In general, the n-th order intermodulation components can be calculated according to

$$f_{IM} = \sum_{a=0}^{n} a f_1 \pm (n-a) f_2 \tag{2.47}$$

The outcome of the two-tone excitation is that additional tones are generated in addition to the DC and harmonics generated by an single-tone excitation. The odd-order intermodulation distortion products (especially third-order and fifth-order) fall very close to the signal band (adjacent and alternate bands) and can not be easy filtered out and they cause a distortion which leads to noncompliance with the non-linearity requirements imposed by a specific telecommunication standard.

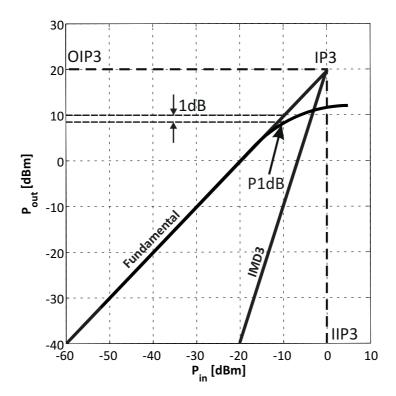

The second-order and third-order distortion products are produced by the second-order and third-order terms in the PA transfer characteristic. Notice that the power of these terms is quadratically and cubically increasing with the input power (the fundamental term increases linearly). With increasing the input power, there would be a point where the power in the fundamental component is equal to the power in the harmonic distortion product. This point is called the intercept point. As mentioned above, the third-order distortion is usually the most significant distortion in the PA and the third-order intercept point (IP3) is an important non-linearity indicator of the PA. The IP3 refers either to the input power (IIP3) or the output power (OIP3).

The concept of the IP3 is shown in Fig. 2.13. The power of the IMD3 components increases by 3 dB per each 1 dB increase in the input power. The point where the fundamental and IMD3 power plots meet is called IP3 (this point is based on extrapolation of both IMD3 and fundamental power curves and can not be practically reached and measured).

It can be shown that [Sechi & Bujatti 2009]

$$P_{IIP3} [dBm] = P_{out-1dB} + 9.6 (2.48)$$

$$P_{OIP3}[dBm] = P_{out,-1dB} + 10.6$$

(2.49)

where  $P_{out,-1dB}$  is the single-tone output power at 1dB compression point.

Figure 2.13: Third-order intercept point and 1 dB compression point definition.

The IP3 can be calculated as [Rogers & Plett 2003]

$$OIP3 [dBm] = P_{in} + \frac{1}{2} (P_{out,fund} - P_{out,IM3})$$

(2.50)

$$IIP3 [dBm] = OIP3 - G \tag{2.51}$$

It can be seen from Fig. 2.13 that for each  $1\,dB$  power drop the IM3 drops by  $2\,dB$ . Note that the IM3 at the compression point is -20 dBc.

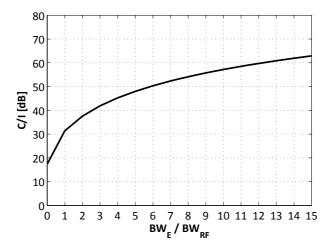

The carrier to intermodulation ratio (C/I) is defined as the ratio between the useful power and IMD products. This can be written mathematically as

$$C/I [dBc] = 10 \log \frac{P_{f_{n(m)}}}{P_{2f_{n(m)} - f_{m(n)}}} \qquad n, m = 1, 2$$

(2.52)

$$C/I[dBc] = 2(OIP3 - P_{out}) = 2(IIP3 - P_{in})$$

(2.53)

where  $P_{out}$  and  $P_{in}$  are the output and input power of each single tone in a two-tone signal.

The drawback of the IP3 as a non-linearity indicator is that it will not predict the non-linearity of amplitude modulated signals which are using a complex modulation. The two-tone measurement is very convenient but such a simple signal does not model

the actual operation of the PA using typical modulated signals (QPSK, OFDM etc.) accurately because it has different signal statistics.

Note that the IP3 concept can not be used in switch mode PAs. As it is shown in the next chapter (Section 3.3) the power of the switch-mode PAs is adjusted by the supply voltage and not by the input power as it is in transconductance PAs. The switch-mode PA should be always driven with a high enough input power so that the power transistor operates as a switch. Therefore, the IP3 characterization which is based on the sweeping of the input power of the two-tone signal is not valid for switching PAs.

### 2.3.4.3 ACLR

The adjacent channel power leakage ratio (ACLR) is defined as a ratio of the power that is contained in the adjacent channel to the power in the channel band. The signal band, the adjacent band and allowed ACLR limit has to be specified by the standard. Some standards (GSM/EDGE) do not specify ACLR but uses the spectrum mask where the transmitted output power spectrum has to be confined below certain limit.

The single-tone or two-tone measurement techniques can be used to investigate the PA non-linearity in a narrowband system. They can be used to emulate selected properties of the multicarrier input signals (PAPR) but the commonly used modulated signals in mobile networks might highly deviate from them. Therefore, ACLR was introduced for band-limited input signals. The main advantage of the ACLR method is that it uses real modulated signals and hence it provides the useful information about the signal distortion and the spectral regrowth. The ACLR can be calculated as

$$ACLR [dBc] = 10 \log \frac{\int_{B \text{ or } HB} P_{out}(f) df}{\int_{band} P_{out}(f) df}$$

(2.54)

where LB and HB are lower adjacent band and higher adjacent band respectively. The ACLR can be calculated separately for the upper or lower adjacent bands but it can be also expresses as total ACLR where the power in both adjacent bands is considered. The alternate channel power leakage ration (ACLR2), is defined for the alternate channels.

The ACLR can be combined with previous non-linearity characterization methods. For example the ACLR is directly related to the third-order IMD products.

### 2.3.4.4 EVM

The error vector magnitude (EVM) characterizes the deviation of the received (demodulated) signal due to the non-linearity of the PA. It is defined as the magnitude of the error vector between the ideal constellation points and the received symbols constellation points. The EVM characterizes the in-band distortion (modulation fidelity) of the PA.

# Linear transmitters using switch-mode PAs

## Contents

| 3.1 | LING                                      | G                            | 29 |

|-----|-------------------------------------------|------------------------------|----|

| 3.2 | Pulse width and pulse position modulation |                              | 31 |

| 3.3 | Pola                                      | r transmitters               | 33 |

| 3   | .3.1                                      | Polar PAs                    | 41 |

| 3   | .3.2                                      | Two point modulation         | 42 |

| 3   | .3.3                                      | Digitally modulated polar PA | 44 |

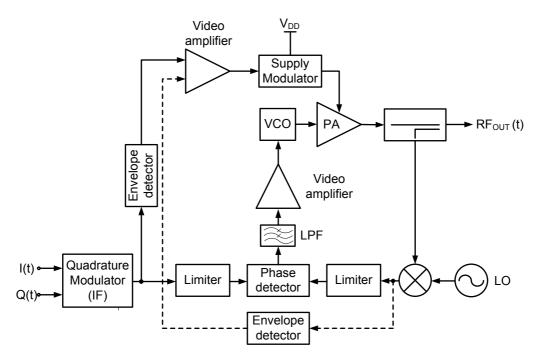

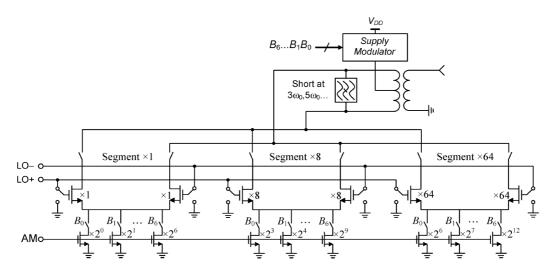

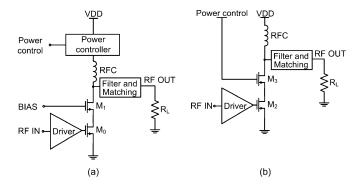

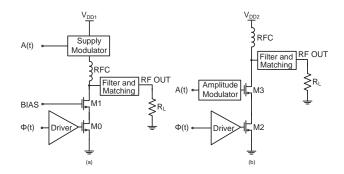

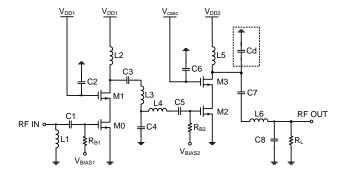

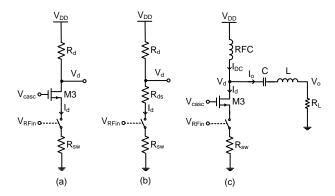

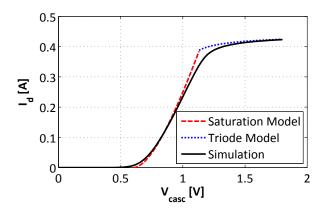

In this chapter transmitter topologies capable of transmitting varying envelope signal using switch-mode PAs are discussed. The focus on the switch-mode PAs is mainly due to their potential for high efficiency and integration in the CMOS technology. These PAs are naturally suitable to amplify constant envelope signals, as explained in the previous chapter. To employ switch-mode PAs in the RF transmitters using varying amplitude signals requires a linearization. There are three main approaches to accomplish that: Linear amplification with Non-linear Components (LINC), Pulse Width and Pulse Position Modulation (PWPPM), and polar transmitters. The first two techniques are introduced in this work only briefly as a background for the polar transmitter.

The polar transmitters are described and analyzed in more detail. The requirements on the PA are discussed. The chapter is concluded with two state-of-the-art examples of polar PAs.

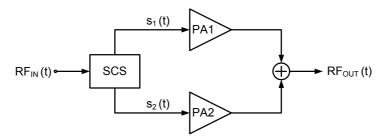

# 3.1 **LINC**

LINC technique was originally introduced by Chireix in the 30's [Chireix 1935] and therefore it is sometimes referred to as Chireix amplifier. The concept of LINC amplifier is illustrated in Fig. 3.1

The basic idea of this concept is that a generic RF band pass signal, which can be defined as

$$RF_{in} = A(t)\cos(\omega_c t + \varphi(t)) = A\cos(\phi(t))\cos(\omega_c t + \varphi(t))$$

(3.1)

Figure 3.1: Block diagram of the LINC transmitter.

is applied to the input of the signal component separator (SCS) block. A is the maximum amplitude of the amplitude modulated signal A(t). The SCS block performs the amplitude to phase modulation. The varying amplitude and phase RF input signal is converted into the two constant envelope and phase modulated signals. This process can be described as

$$RF_{in} = s_1(t) + s_2(t)$$

$$= \frac{1}{2}A\cos(\omega_c t + \varphi(t) + \phi(t)) + \frac{1}{2}A\cos(\omega_c t + \varphi(t) - \phi(t))$$

(3.2)

where

$$\phi(t) = \cos^{-1}\left(\frac{A(t)}{A}\right) \tag{3.3}$$

The two signals  $s_1(t)$  and  $s_2(t)$  can be then amplified by a highly efficient but nonlinear switch-mode PAs (PA1 and PA2 in Fig. 3.1). The output signal can be simply written as

$$RF_{out} = G(s_1(t) + s_2(t)) = 2GA(t)\cos(\omega_c t + \varphi(t))$$

(3.4)

where G is the power gain of each power amplifier.

This concept is indeed very appealing and the LINC transmitter would exhibit both a high efficiency and a high linearity. Unfortunately, there are several important difficulties (practical challenges) which prevent the implementation of such transmitters without a severe deterioration of the performance (especially efficiency).

The first issue arises with  $s_1(t)$  and  $s_2(t)$  signals generation. The SCS block performs the signal separation according to the equation (3.2). This operation is quite complex because the phase of the original signal  $RF_{in}$  has to be modulated by  $\phi(t)$  which is a non-linear function of the amplitude modulated signal A(t) (3.3). The first SCS circuits were implemented on the circuit level but the circuits are very complex and not suitable for RF integrated transmitters [Cox & Leck 1975].

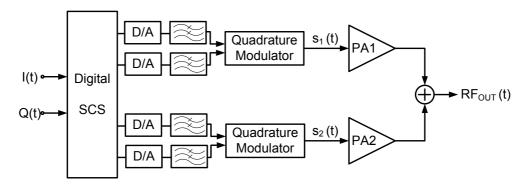

Another approach is to use the power of today's DSP chips. The schematic of a modern LINC transmitter is shown in Fig. 3.2.

The SCS function is performed in the baseband by the DSP and then each IQ signals

**Figure 3.2:** Block diagram of the LINC transmitter with SCS function implemented in baseband by the DSP.

are up converted to the RF and applied to the switch-mode PAs [Hakala et al. 2005]. The DSP and D/A converters have to operate at a high sampling rate and that will significantly increase the power consumption. The main problem of this approach is that the signal separation is a non-linear operation (3.3) which will create a bandwidth regrowth. The bandwidth of the two BB signals is much larger that the bandwidth of the original amplitude and phase modulated BB signal. Depending on the BB BW of the original signal the required BW might be at the edge of the capabilities of the best today DSPs. This approach (without a BW reduction technique) will not be feasible to implement in the mobile station transmitters.

Another difficulty is to maintain the mismatch between the two signal paths low. The amplifiers and quadrature modulators in the two channels need to have a precisely matched gain and phase response. Several complex methods have been proposed to correct either the gain or the phase errors or both. A summary of the linearization techniques can be found in [Vankka 2005]. A fully digital predistortion technique can be also used to compensate the gain and phase impairments [Garcia et al. 2005].

And the last but very significant issue of the LINC transmitter is the efficient power combining [Cripps 2006]. The requirements on the power combiner are that it should have low loss and high isolation between the two PAs. A conventional hybrid combiner can be used to combine the two signals. It provides a high isolation but the major disadvantage is a high loss if the two signals are not equal (uncorrelated signals have loss of 3 dB). A more efficient combining technique suitable for the LINC transmitters is required.

All of the above mentioned issues will lead to significant efficiency degradation. This is the main reason why the LINC transmitters are so popular among researchers. LINC offers an interesting research challenges, but it has not been implemented in the commercial mobile RF transmitters.

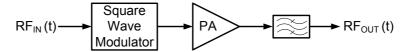

# 3.2 Pulse width and pulse position modulation

Pulse width modulation (PWM) is a recently re-discovered approach which encodes the envelope modulated signal into the pulse width so that it can be processed by a switch-

mode PA. The RF PWM was firstly demonstrated by Raab [Raab 1973]. A modern RF transmitter using the PWM concept is shown in Fig. 3.3.

Figure 3.3: Simplified block diagram of the RF transmitter using PWM.

In the pulse width and pulse position modulation (PWPPM) one pulse is transmitted during each RF period. The RF input signal can be described by equation (3.1) where A(t) and  $\Phi(t)$  are the amplitude and phase varying signals respectively. The pulse width of the PWPM signal is related to the A(t) signal and pulse position depends the  $\Phi(t)$  signal. In this way the amplitude and phase modulated signal is transformed into constant envelope PWPPM signal.

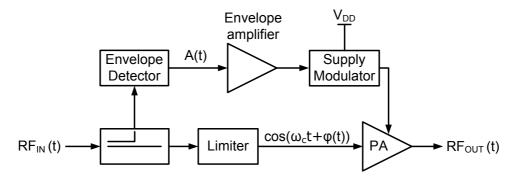

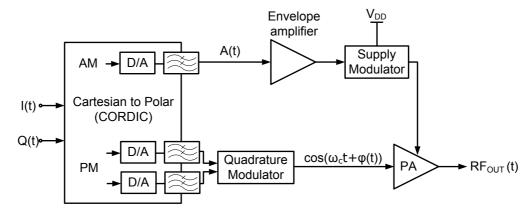

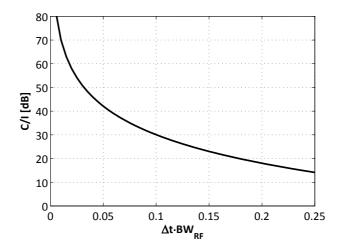

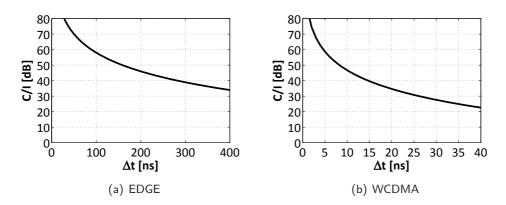

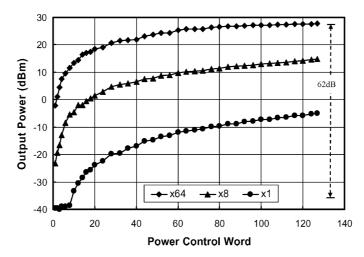

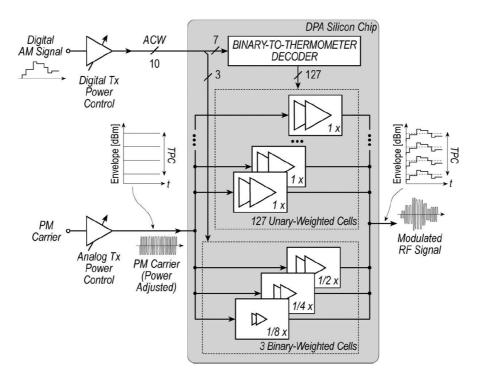

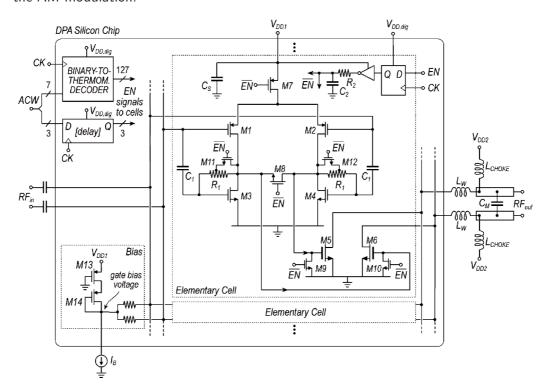

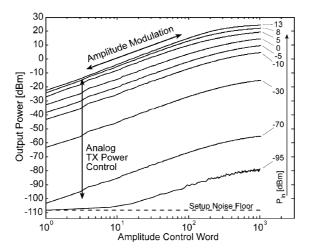

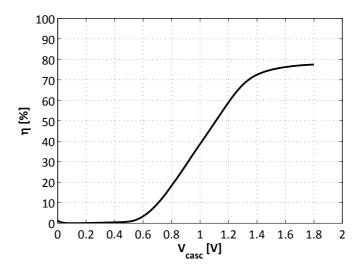

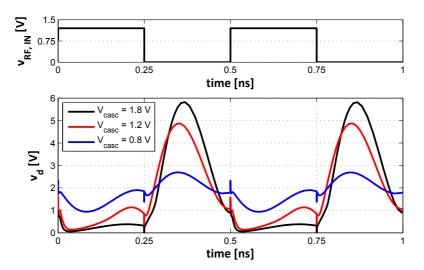

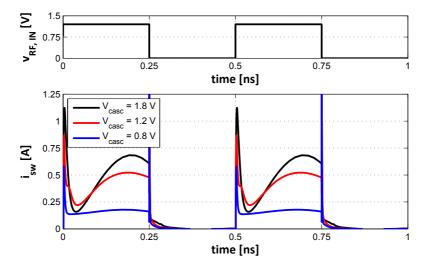

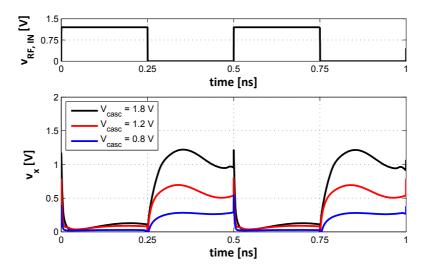

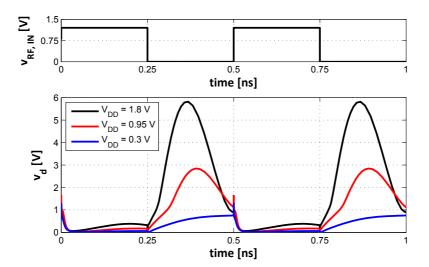

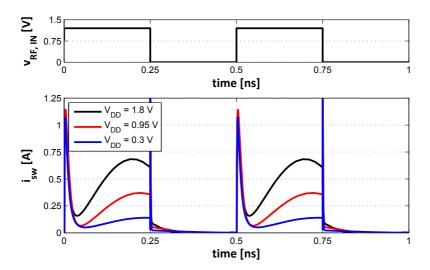

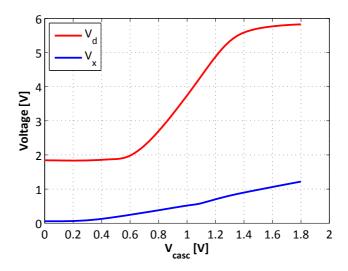

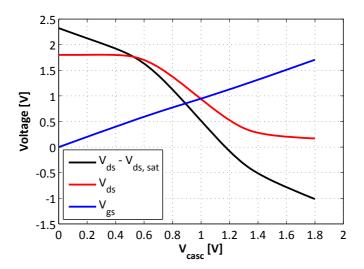

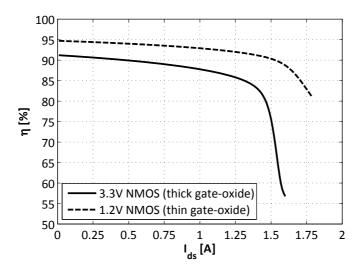

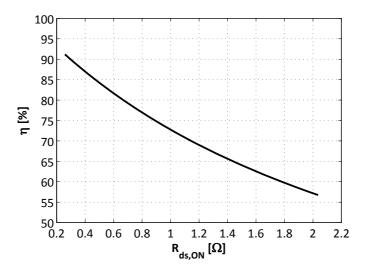

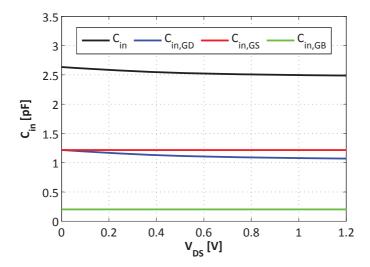

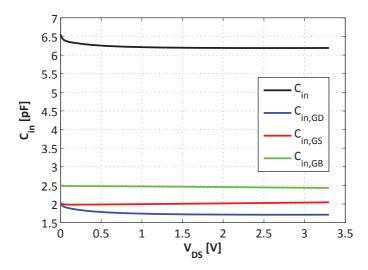

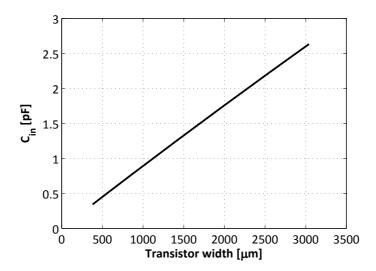

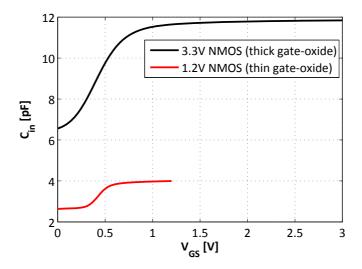

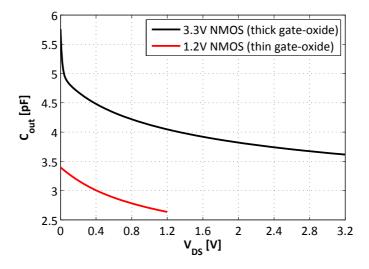

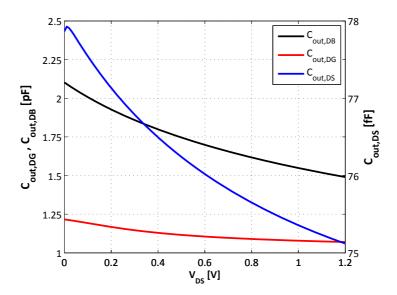

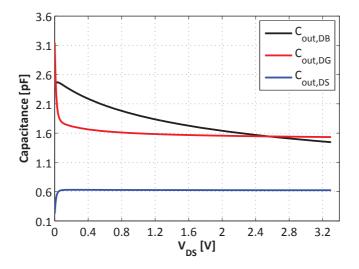

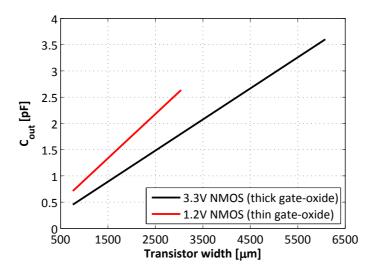

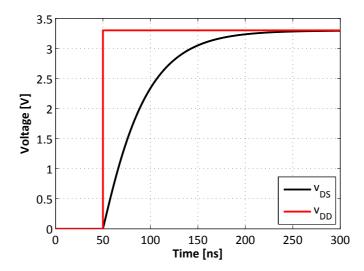

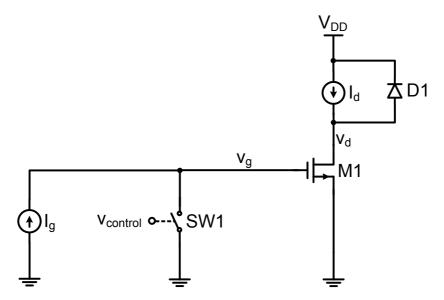

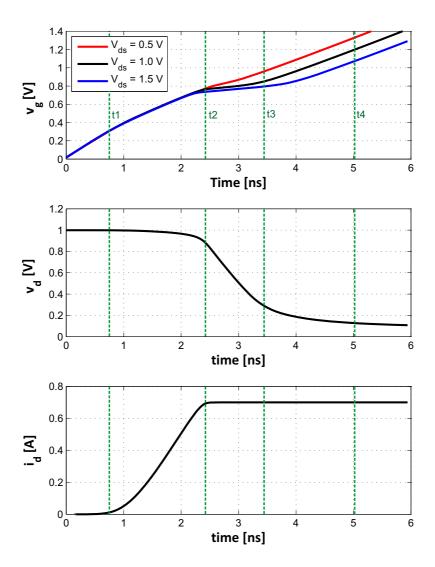

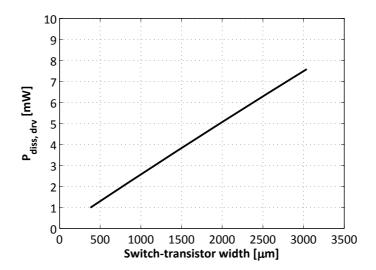

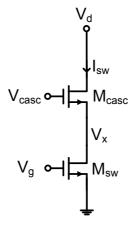

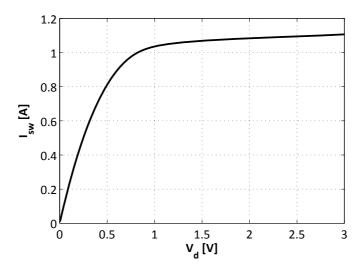

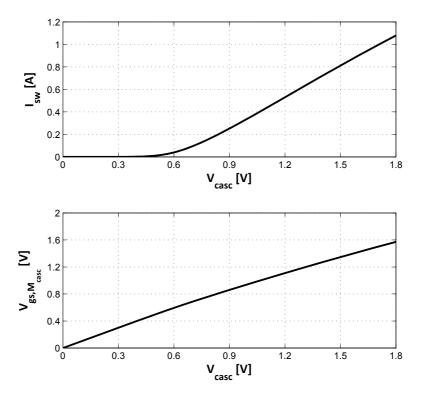

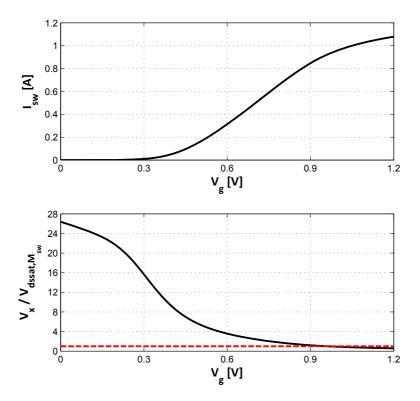

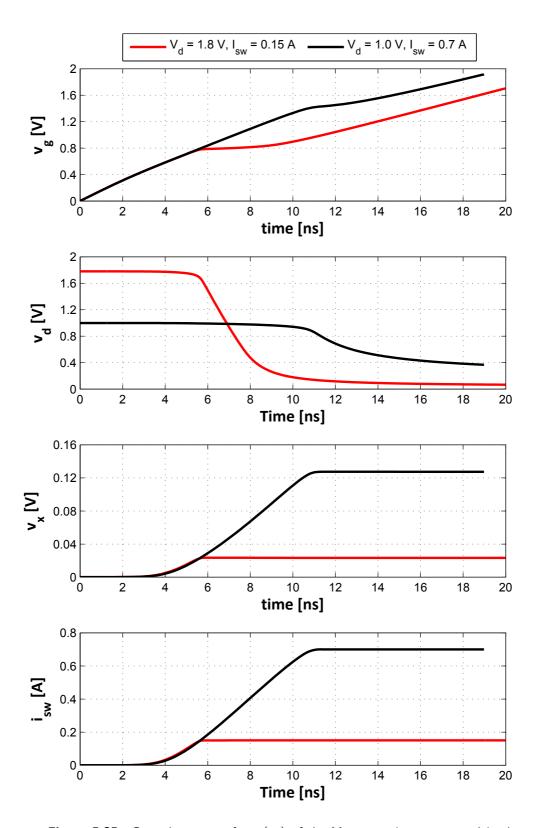

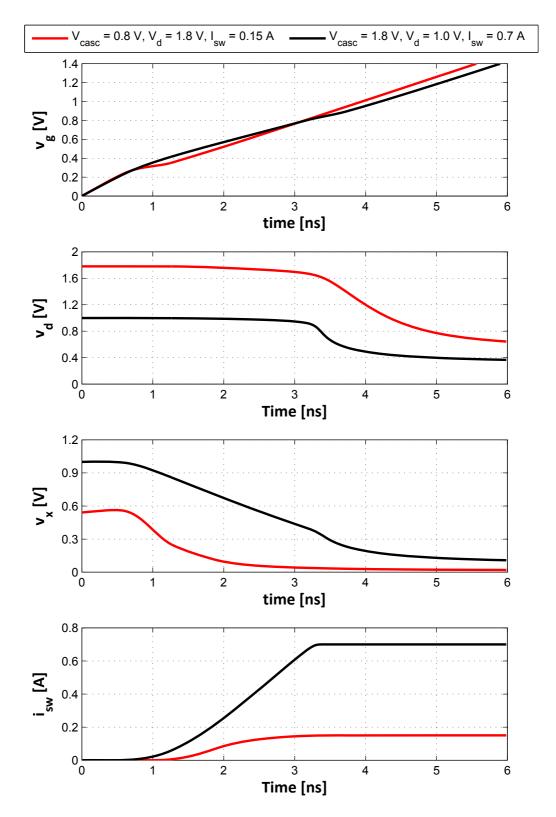

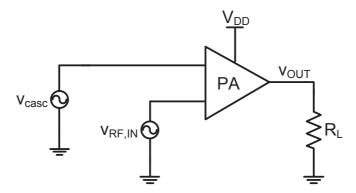

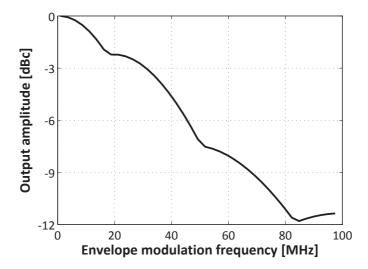

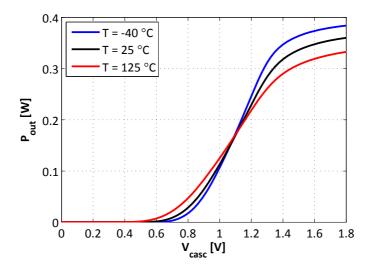

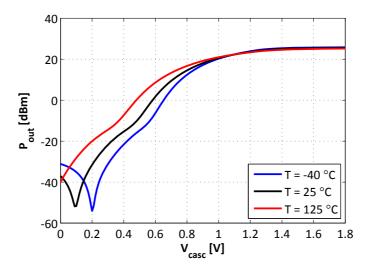

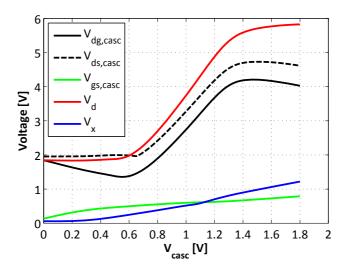

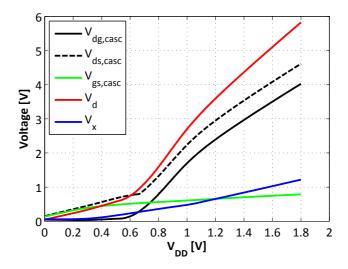

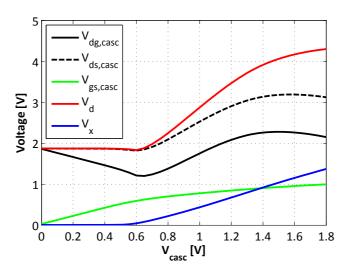

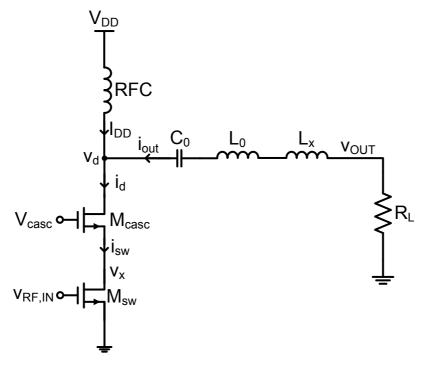

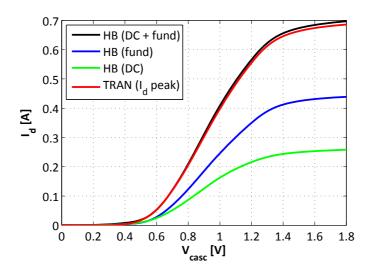

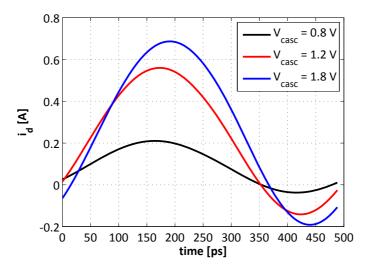

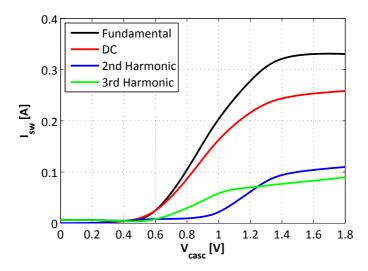

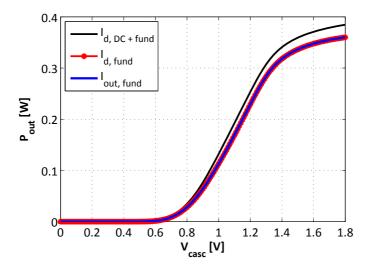

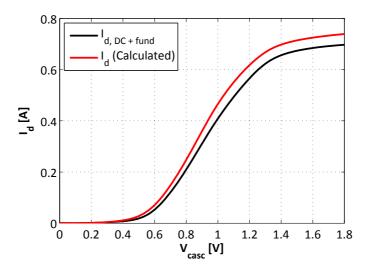

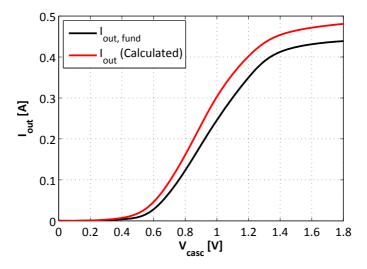

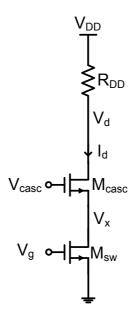

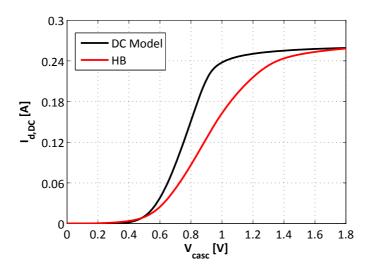

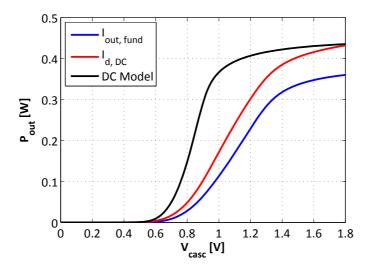

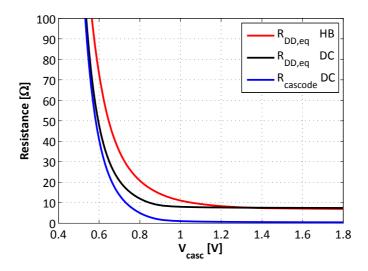

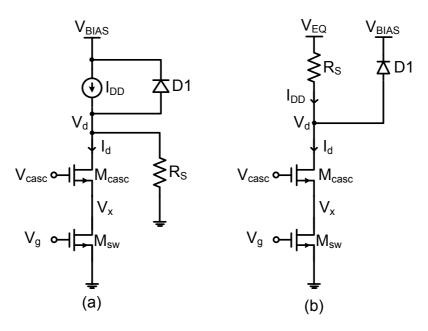

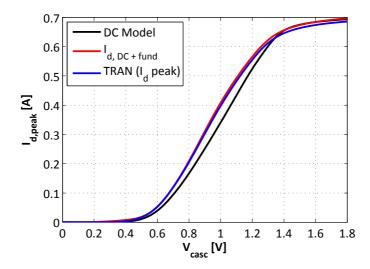

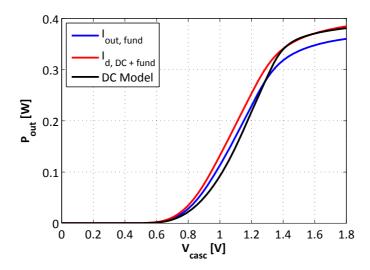

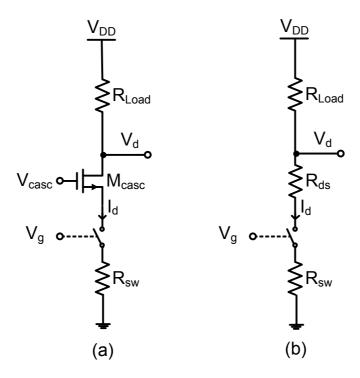

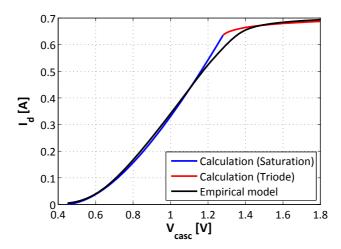

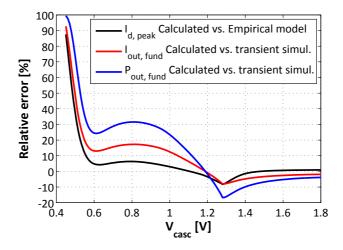

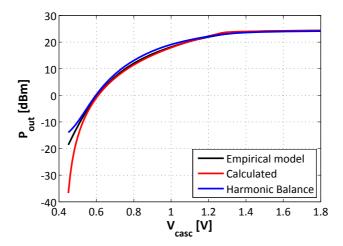

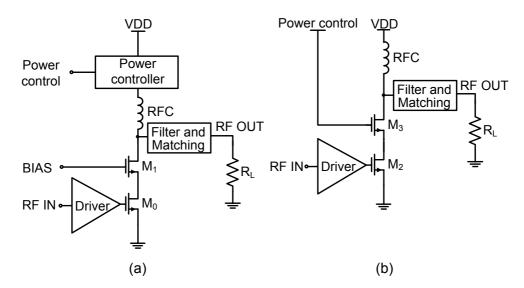

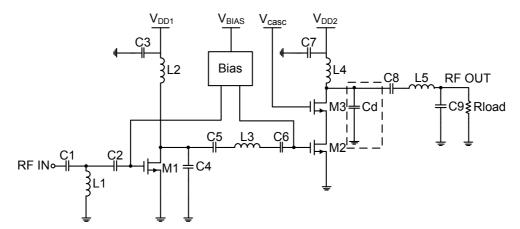

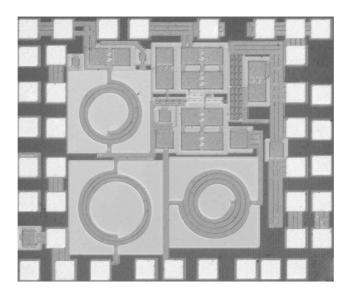

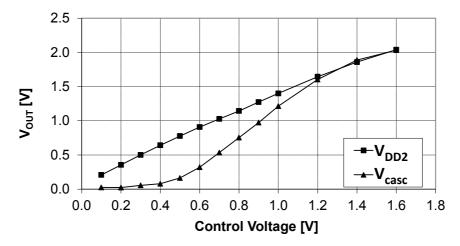

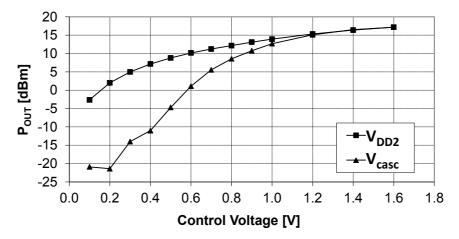

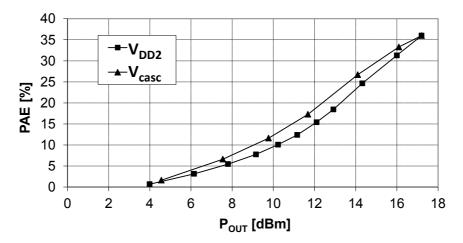

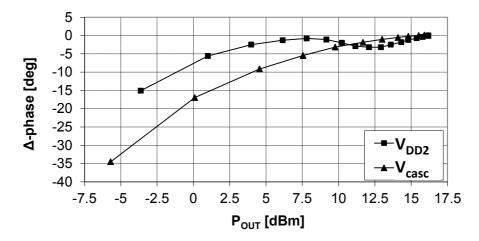

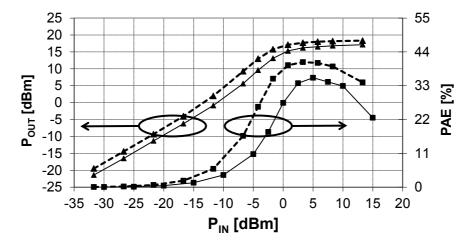

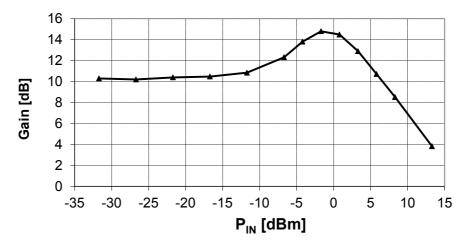

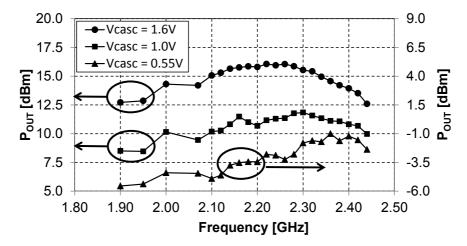

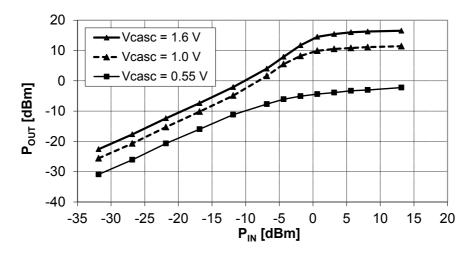

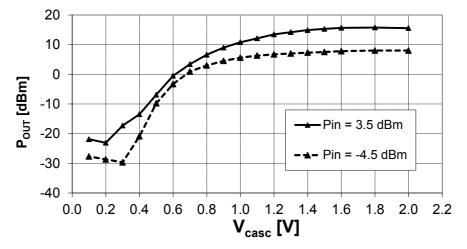

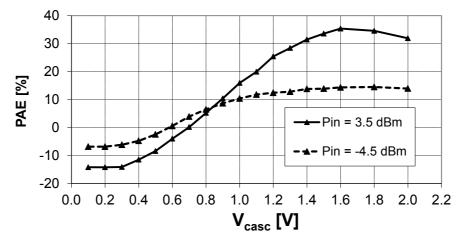

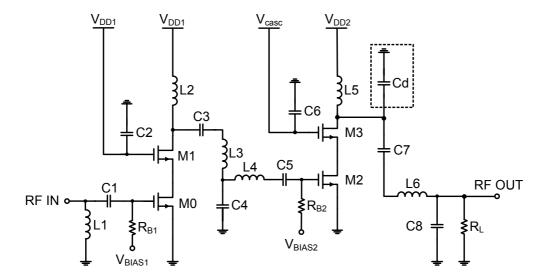

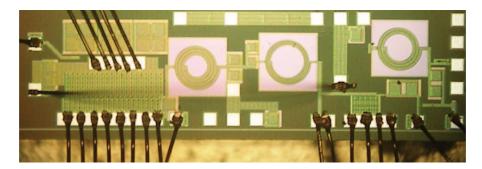

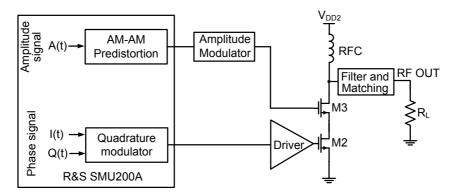

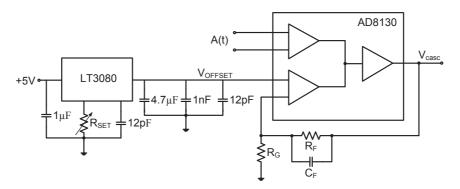

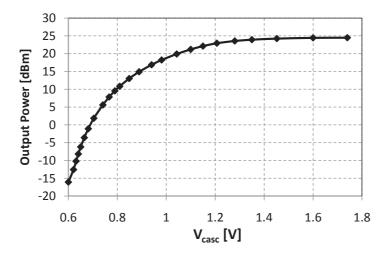

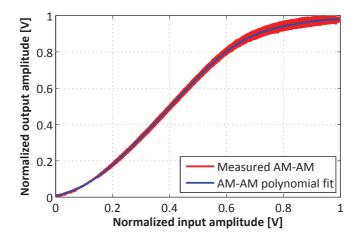

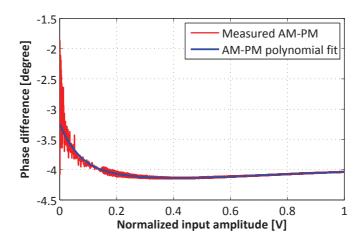

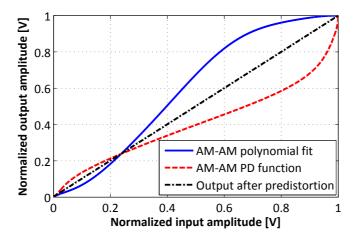

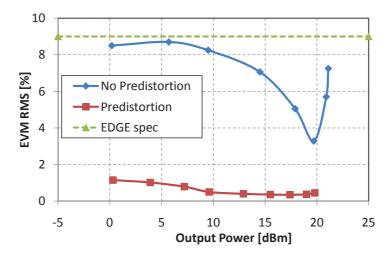

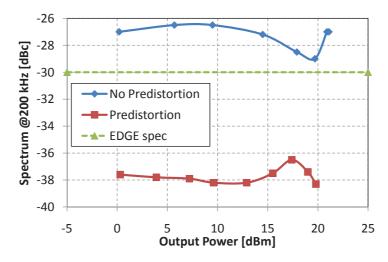

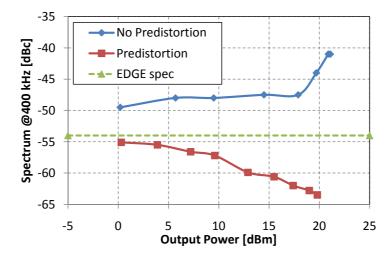

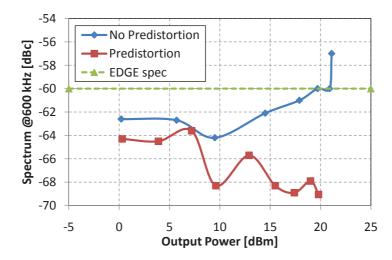

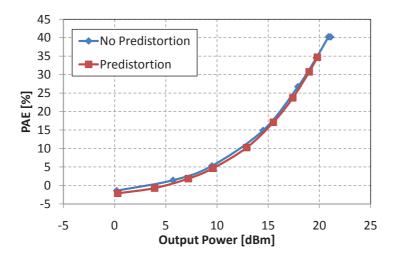

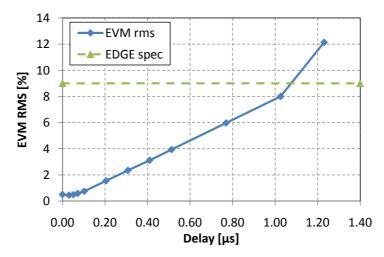

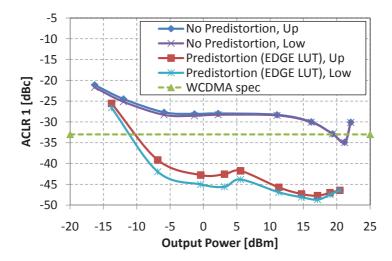

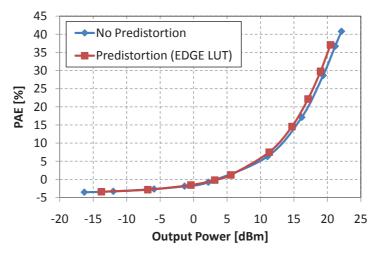

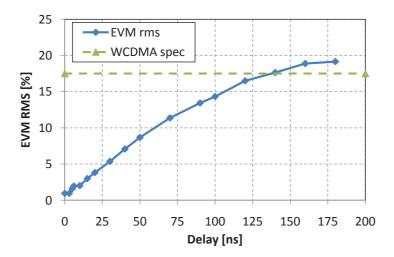

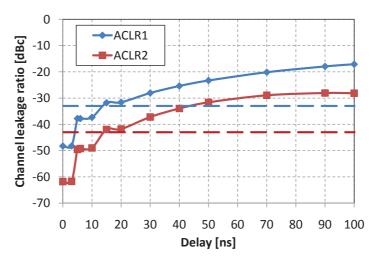

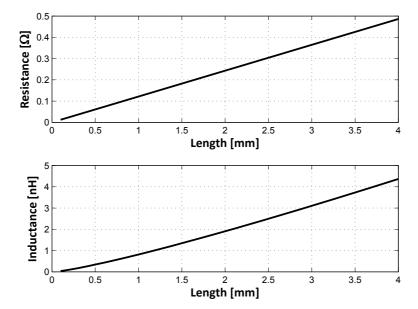

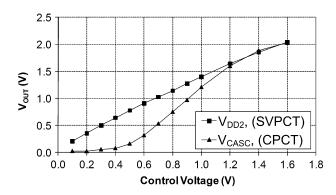

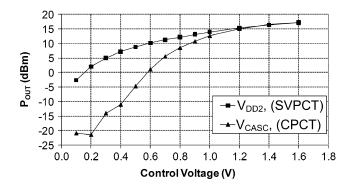

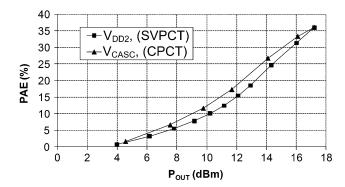

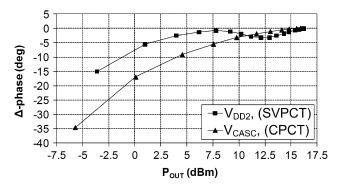

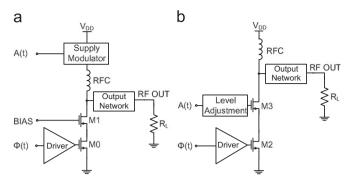

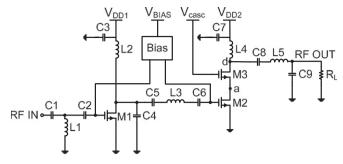

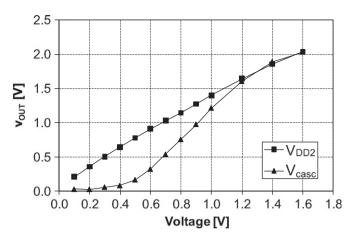

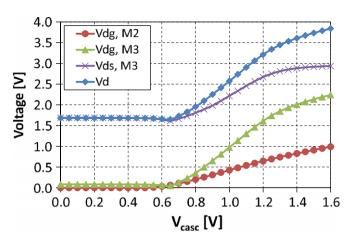

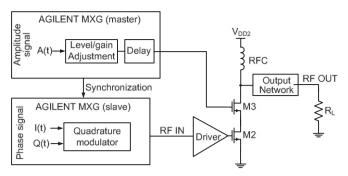

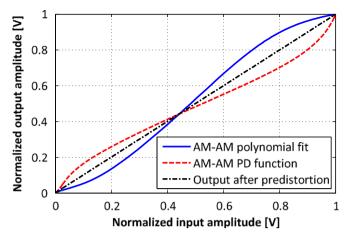

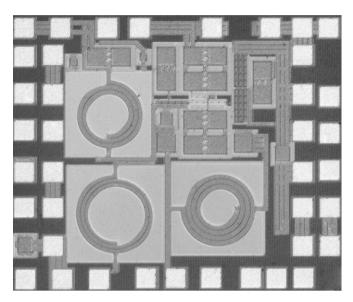

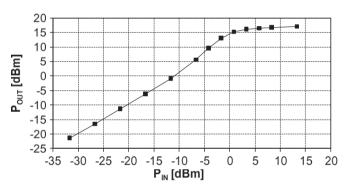

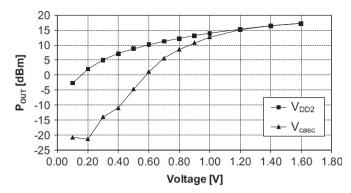

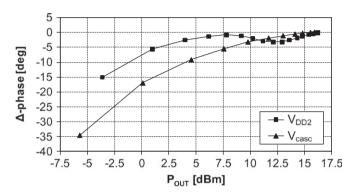

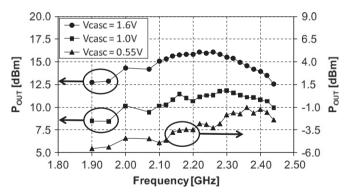

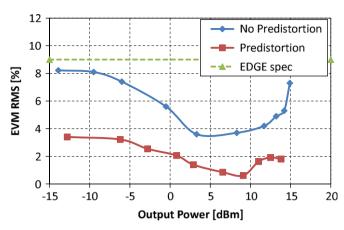

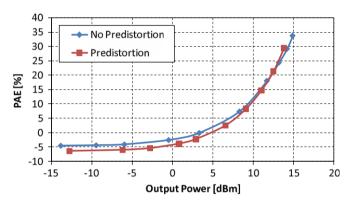

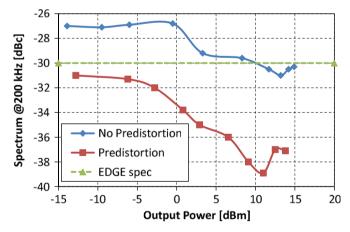

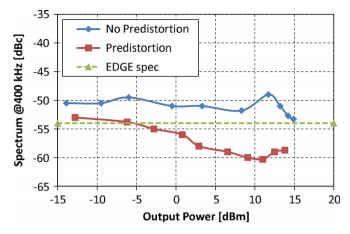

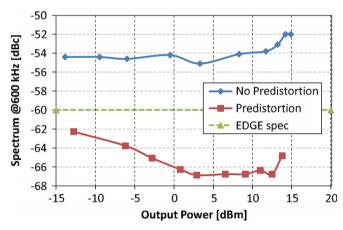

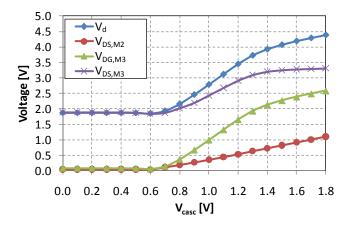

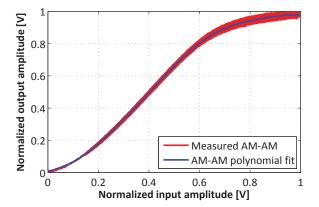

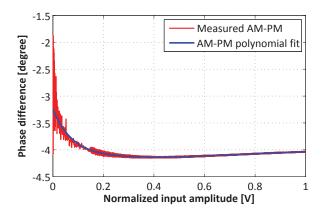

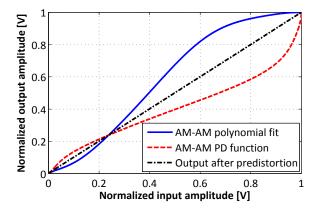

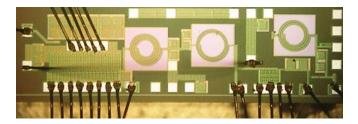

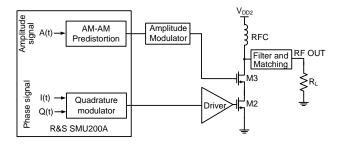

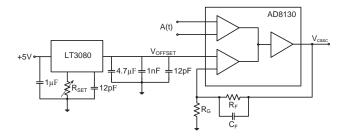

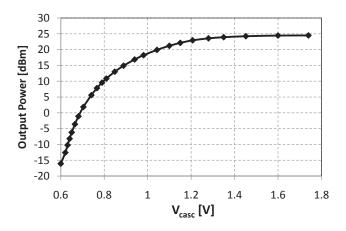

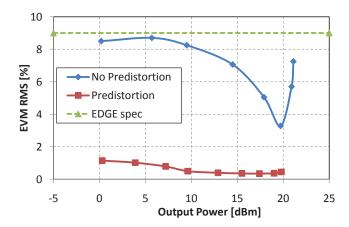

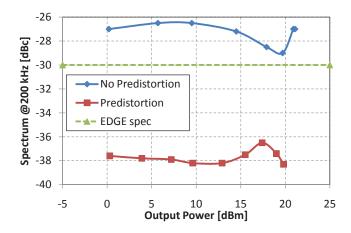

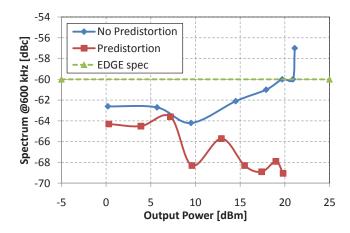

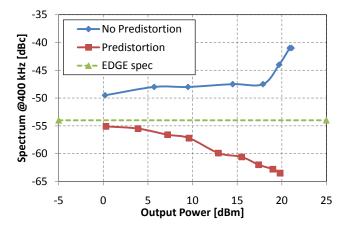

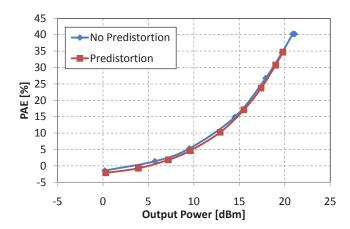

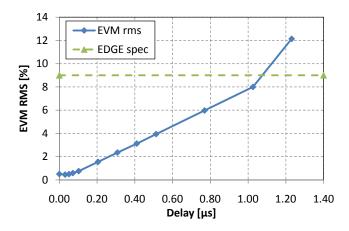

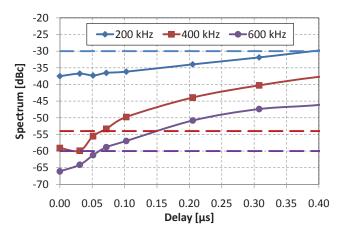

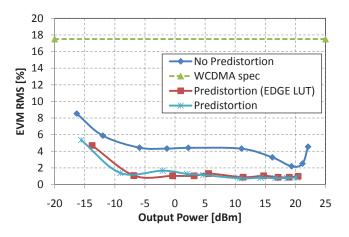

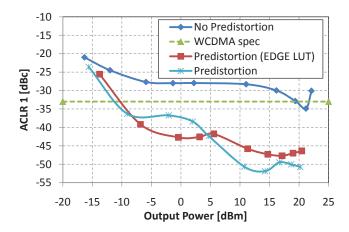

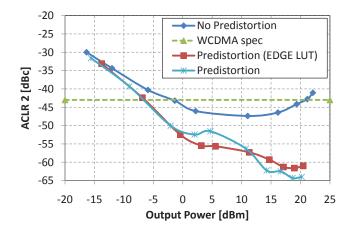

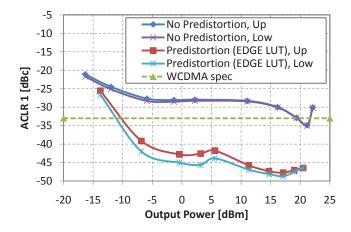

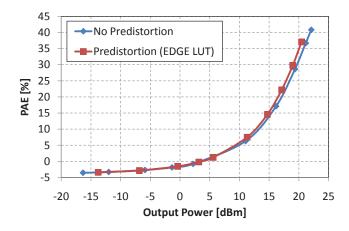

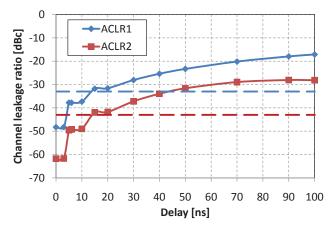

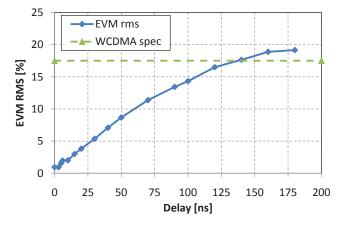

The pulse modulated signals allow to use high efficient switch-mode amplifiers to amplify varying envelope signals. There are several techniques to create the pulse modulated signals. The first approach is using the sigma delta  $(\Sigma\Delta)$  modulation [Hung et al. 2007]. Hung et al. proposed a technique where the bandpass  $\Sigma\Delta$  is fully implemented in the DSP. The transmitter is using a CMOS class-D PA operating at 800 MHz. This approach increases the flexibility of the system, avoids the problems associated with many analog circuits and can be easily implemented in a mobile handset RF transceiver. The modulated IQ BB signals are up-converted (in DSP) and processed by the bandpass sigma delta modulator. The main problem of this approach is the quantization noise which is a common issue for all the pulse modulation concepts which are using  $\Sigma\Delta$  modulator. Even though the quantization noise is spectrally shaped into out of the band frequencies it is still difficult to meet the spectral emission mask. The bandpass filter at the output of the PA is required but the feasibility of its implementation was not investigated in [Hung et al. 2007].