Aalborg Universitet

### High Efficiency Boost Converter with Three State Switching Cell

Klimczak, Pawel; Munk-Nielsen, Stig

Published in:

Proceedings of the International Exhibition & amp; Conference for Power Electronics Intelligent Motion Power Quality, PČIM 2009

Publication date: 2009

**Document Version** Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Klimczak, P., & Munk-Nielsen, S. (2009). High Efficiency Boost Converter with Three State Switching Cell. In Proceedings of the International Exhibition & Conference for Power Electronics Intelligent Motion Power Quality, PCIM 2009 Curran Associates.

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- ? Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- ? You may not further distribute the material or use it for any profit-making activity or commercial gain ? You may freely distribute the URL identifying the publication in the public portal ?

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

### High Efficiency Boost Converter with Three State Switching Cell

Pawel Klimczak, Aalborg University, Denmark Stig Munk-Nielsen, Aalborg University, Denmark

### Abstract

The boost converter with the three-state switching cell seems to be a good candidate for a dc-dc stage for non-isolated generators based on alternative energy sources. It provides a high voltage gain, a reduced voltage stress on transistors and limited input current ripples. In this paper the focus is on performance improvement of this type of the converter. Use of foil windings helps to reduce conduction losses in magnetic components and to reduce size of these components. Also it has been demonstrated that the regulation range of this type of converter can be increased by operation with duty cycle lower than 50%.

### 1. Introduction

Increasing interest in alternative and renewable energy creates a demand for novel power conversion systems, which interfaces different energy sources to a load or to an utility grid. Very often it's necessary to boost a low voltage from a source (commercial fuel cells, most of photovoltaic panels) to a high dc voltage suitable for an inverter. In many cases safety isolation is not requires, thus it's possible to use a non-isolated topology. The required voltage gain may exceed value of 20 in some cases. Such gain is attainable for a basic boost converter with SiC diodes and novel MOSFET transistors (SuperFET, CoolMOS etc.), but by a cost of poor semiconductors utilization and the efficiency limited by MOSFET conduction losses [1]. Further efficiency improvement requires low voltage switches which ensure lower conduction losses and improved switching performance. In the literature [2-6] one may find several topologies based on a coupled inductor principle, which offer a high voltage gain and reduced voltage stress on the active switch. The main drawback among these topologies is large input current ripples. On one hand significant input current ripples may lead to faster degradation of a fuel cell stack or disturb maximum power point tracking in case of PV application. An additional input filter can solve these problems, but it increases size, complexity and cost of the converter. Also large ripples result in a large peak current, which leads to increased conduction losses and requires oversized components. The topology introduced in [7] and presented on Fig. 1 offers a high voltage gain and reduced voltage stress on transistors. Reference [8] reports a very

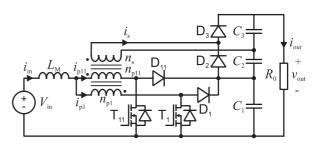

Fig. 1. Diagram of the three state switching cell boost converter

good performance of this topology in high voltage gain application ( $V_{in}$ =35 V,  $V_{out}$ =400V). The main focus of this paper is to improve a power density and an efficiency of this type of converter.

### 2. Description of the converter

The selected topology is presented on Fig. 1. It incorporates so called three-state switching cell

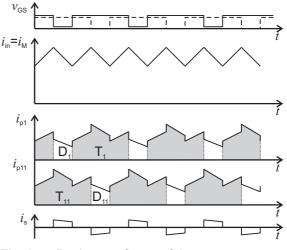

Fig. 2. Basic waveforms of the converter

(switches  $T_1$ ,  $T_{11}$ ,  $D_1$ ,  $D_{11}$  and the transformer) [7, 9]. The secondary side of the transformer with diodes  $D_2$ ,  $D_3$  and capacitors  $C_2$ ,  $C_3$  compose the voltage doubler rectifier. Basically the converter operates in so called overlapping mode, i.e. with the duty cycle larger than 50% and in continuous conduction mode (CCM).

# 2.1. Operation with duty cycle larger than 50%

Key waveforms for are presented on Fig. 2. There are four basic operating modes. Mode 1 and 3 are identical while both transistors are turned-on and share the input current equally  $(n_{p1}=n_{p11})$ . During this period the input inductor  $L_{M}$  is being charged. Both primary windings are effectively connected anti-parallel. In this case no voltage induces in the secondary winging and there is no current flow in the secondary winding too. Next, in mode 2 the transistor T<sub>1</sub> is being turned-off and energy stored in  $L_{M}$  is being released thru the primary winding  $(n_{p1})$  and the diode D<sub>1</sub> to the capacitor  $C_1$ , and thru the secondary winding and the diode  $D_3$  to the capacitor  $C_3$ . In this operating mode primary windings are effectively connected in series and the voltage  $V_{C1}$  is applied to them. The voltage equal to  $V_{C1}$  *n* induces in the secondary winding. Term *n* means the transformer primary-tosecondary turns ratio. The last mode 4 is similar to mode 2 - while transistor T1 remains turned-on and  $T_{11}$  is turned-off. In this mode diodes  $D_{11}$  and  $D_2$  conduct. It's important that the capacitor  $C_1$  is charged twice over one cycle, while capacitors  $C_2$ and  $C_3$  are charged only once. The converter voltage gain in CCM is given by (1). The maximum voltage across switches is given by (2) and (3).

$$V_{\rm out} = \frac{1+n}{1-D} \cdot V_{\rm in} \tag{1}$$

$$V_{\text{T1max}} = V_{\text{D1max}} = V_{\text{C1}} = \frac{1}{1+n} \cdot V_{\text{out}}$$

(2)

$$V_{\text{D2max}} = V_{\text{D3max}} = \frac{n}{1+n} \cdot V_{\text{out}}$$

(3)

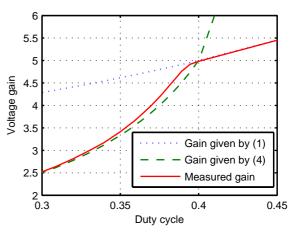

# 2.2. Operation with duty cycle lower than 50%

Unlike a conventional current-fed push-pull converter [10] the topology presented on Fig. 1 is able to operate with the duty cycle lower than 50%. However the voltage gain function becomes strongly non-linear in this case. For duty cycles just below 50% converter operates normally and it's voltage gain follows (1). Also the voltage stress on components fits to (2) and (3). On the other

end, at the very low duty cycles the converter behaves like a two-phase interleaved boost with coupled inductor [11]. In this case voltage gain is given by (4).

$$V_{\text{out}} = \frac{1}{1 - 2 \cdot D} \cdot V_{\text{in}} \tag{4}$$

Under such conditions diodes  $D_2$  and  $D_3$  are forward biased all the time so there is no voltage across capacitors  $C_2$  and  $C_3$ . The whole the output voltage appears across the capacitor  $C_1$ . It may create an additional voltage stress on transistors and diodes  $D_1$  and  $D_{11}$ .

The boundary between one and the other mode is defined by the crossing of voltage gain functions (1) and (4). By combining these two equations one may find the critical duty cycle  $D_{cr}$  at the crossing point (5).

$$D_{\rm cr} = \frac{n}{2 \cdot n + 1} \tag{5}$$

### 3. Magnetic components

Magnetic components are essential for any dc-dc converter design. Their performance reflects directly on converter's performance. Typically design and optimization process focuses on loss reduction inside magnetics as well as on reduction of parasitics, so external circuit is not affected. Volume of magnetics is an important issue too.

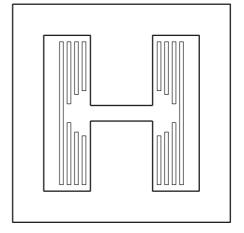

### 3.1. Dc inductor

In the considered topology the dc indutor  $L_{\rm M}$  conducts essentially the dc current with limited ac component (ripples). It means that the flux ac component is fairly low too, thus core losses are small and the design is so called saturation limited design [12]. To improve performance of such design it is important to reduce dc and ac

Fig. 3. Foil winding arrangement on a gapped core

conduction losses, but low dc resistance is crucial. Basically one may choose between a solid round wire, a Litz wire and a foil winding. Use of a single round wire provides a good window fill factor, a low dc resistance and a low manufacturing cost. To improve window utilization one may use few thinner wires or a rectangular wire if available. Another choice is a Litz wire which provides a good ac/dc resistance ratio, but it requires a larger window area because of a poor copper fill factor. Finally a winding made of a copper foil may provide a very good copper fill factor (depends on copper and insulation thickness) and a very low dc However two main drawbacks are resistance. recognized. First, it's a multilayer design since one turn means one layer. In this case proximity losses may become large quickly. The solution is to use as few turns as possible and the copper thickness smaller than the penetration depth for given frequency. Second drawback relates to use of a ferrite core with a discrete air gap. Because of a fringing field around the air gap huge eddy currents induce in inner layers of the winding. It creates large losses and risk of hot spot in proximity of the gap. This issue is solved by use of a core with distributed air gap, e.g. a powder core. If a core with a discrete air gap is an only option then the special winding arrangement is necessary. It is simply done by notching of inner layers of the winding, so the fringing field doesn't penetrate thru the winding [13, 14]. An example of such winding is presented on Fig. 3.

### 3.2. Three winding transformer

Fig. 4. Transformer primary currents and their components

Fig. 5. Primary currents flow in transformer windings

Fig. 4 presents transformer primary currents and its components: the input dc current  $i_{in(dc)}$ , the input current ripple  $i_{in(ac)}$  and the reflected secondary current  $i_s$ '. Fig. 5 shows how these components flow in particular windings of the transformer. The input current flows into the beginning of the winding  $n_{p11}$  and into the end of the winding  $n_{p1}$  like presented on Fig. 1 and Fig. 5. For this current component primary windings are effectively connected anti-parallel. In an ideal case half of the input current flows into one primary winding while the other half goes into the other. In this way fluxes generated by these currents cancel each other, so there is no effect on the secondary side of the transformer. Secondary current is flows in the secondary winding and the reflected secondary current  $i_s$ ' flows in primaries as presented on Fig. 5. For this current component primary windings are connected effectively in series.

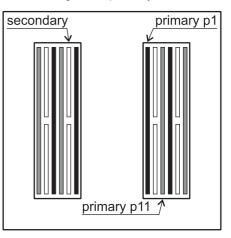

Such mixture of ac and dc components creates a challenge for the design of transformer windings, especially primaries. Reduction of dc and ac resistances of primary windings is crucial. Use of a Litz wire helps to reduce skin and proximity effects and provides a good ac/dc resistance ratio. Unfortunately in the same time a Litz wire has a poor copper fill factor, and thus requires a core with a large window. Also the leakage inductance of such winding is high. A round wire has a better copper fill factor and a dc resistance is reduced in compare to the Litz wire. But due to the skin effect the ac loss is fairly high. By taking several thinner round wires one may reduce layer thickness and the ac resistance, but it requires fairly complicated winding arrangement. A foil winding seems to be a good solution once again. It has a very good copper fill factor and the dc resistance is low. Small thickness of the foil reduces the skin effect, while interleaving of primary and secondary

Fig. 6. A three winding transformer foil windings arrangement

windings attenuates the proximity effect [15]. The proposed winding arrangement of the three winding transformer is presented on Fig. 6. Primary and secondary windings are interleaved. Primary windings  $n_{p1}$  and  $n_{p11}$  are made of a thin foil occupying whole available window width. Each of primary windings has just a single turn per layer and the secondary winding is sandwiched between primaries. The secondary winding has few turns arranged in a single layer like presented on Fig. 6. Such winding arrangement provides low dc and ac resistances for all mentioned above current components and a good coupling between primary and secondary windings. This solution has two main drawbacks. First, because of intensive interleaving there is a large surface area of primary and secondary winding facing each other. Depends on the insulation material and the insulation thickness it may result in a significant interwinding capacitance which decreases performance. The second drawback is reduced flexibility in terms of turns ratio. It's fairly easy to achieve integer turns ratio, like 1:2 or 1:3. But it may be difficult to achieve non-integer turns ratio, like 1:2.5.

### 4. Experimental results

In order to verify theoretical analysis and simulations the 500 W breadboard has been built and tested. The converter input voltage is 30-50 V and the output voltage is regulated at 400 V. The switching frequency is  $f_s$ =50 kHz. The assembled converter is presented on Fig. 7. The inductor  $L_M$  bases on E42/21 ferrite core with 1 mm air gap. The winding is made of 24x0.3 mm copper foil and there are 12 turns, which gives the inductance  $L_M$ =47 µH. It limits input current ripples to 3.5 A peak to peak, which is about 20% of the maximum input dc current. Measured dc resistance of the inductor winding is  $R_{Mac}$ =2.7 mΩ while respective ac resistance is  $R_{Mac}$ =120 mΩ for 100 kHz (double

Fig. 7. Assembled 500 W converter

of the switching frequency). The transformer bases on E42/21 core too. Because of core losses its peak induction is limited to 0.15 T at high input voltage and it requires at least 6 turns in each of primary windings. Primary windings are made of 24x0.15 mm copper foil. The transformer turns ratio is  $n_{p1}:n_{p11}:n_s=1:1:2$ , thus the secondary winding has 12 turns and it's made of 10x0.15 mm Measured dc resistance is copper foil.  $R_{p1dc}=R_{p11dc}=3$  m $\Omega$  for the primary winding and  $R_{\rm sdc}$ =12 m $\Omega$  for the secondary. The ac resistance of the transformer is measured in respect to particular current components flowing in its windings and described in section 3.2. The ac resistance seen from the secondary winding while primaries are connected in series and shorted is  $R_{\rm sac} + R_{\rm p1ac} + R_{\rm p1ac} = 21 \text{ m}\Omega$ . This resistance is related to the secondary current and the reflected secondary current. Next the resistance for input current dc and ac components is evaluated with windings connected primary anti-parallel.

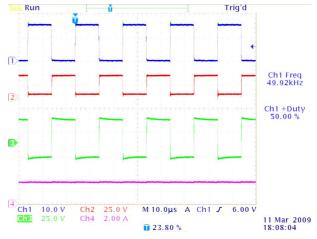

Fig. 8. Waveforms of the converter operating with  $V_{in}$ =10V and 50% duty cycle

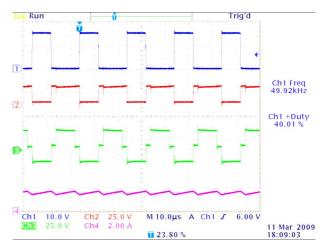

Fig. 9. Waveforms of the converter operating with  $V_{in}$  =10 V and 40% duty cycle

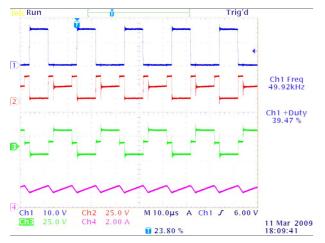

Fig. 10. Waveforms of the converter operating with  $V_{in}$  =10V and 39.5% duty cycle

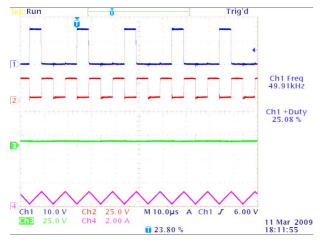

Fig. 11. Waveforms of the converter operating with  $V_{in}$  =10 V and 25% duty cycle

Measured dc resistance is about  $R_{p1dc}||R_{p11dc}=1.5$  m $\Omega$  and the ac resistance is about  $R_{p1ac}||R_{p11ac}=1.8$  m $\Omega$ . The transformer turns ratio is 1:1:2 and it enables to use of 150 V MOSFETs (IRF4321PbF). Diodes D<sub>1</sub> and D<sub>11</sub> are 150 V Schottky's (30CPQ150PbF) while D<sub>2</sub> and D<sub>3</sub> are 600 V SiC diodes (IDT10S60C).

Next, the test at low duty cycles and reduced input voltage is being performed. The input voltage is set to 10 V and the duty cycle is changed from 50% down to 25%. From (5) it's found that the critical duty cycle  $D_{cr}$ =40%. Fig. 8, Fig. 9, Fig. 10 and Fig. 11 present observed waveforms at 50%, 40%, 39.5% and 25% duty cycle respectively. On these figures Ch1 presents the gating signal for the transistor, Ch2 presents the drain-source voltage of the respective transistor, Ch3 presents the transformer secondary voltage and Ch4 presents the input current. The voltage  $V_{C1}$  is determined by the transistor drain-source peak voltage (Ch2),

Fig. 12. Voltage gain of the converter operating at low duty cycle

Fig. 13. Measured efficiency of the converter for 30 V and 50 V input voltage

while voltages  $V_{C2}$  and  $V_{C3}$  are given by the transformer secondary voltage (Ch3). For duty cycles 50% and 40% output capacitors share the output voltage equally and the voltage gain follows (1). When the duty cycle decreases just below  $D_{cr}$  (Fig. 10) the voltage  $V_{C1}$  quickly increases (the peak of Ch2) and voltages  $V_{C2}$  and  $V_{C3}$  decrease (the amplitude of Ch3). When the duty cycle decreases farther then the transformer secondary voltage collapses down to zero. In this case only the capacitor  $C_1$  contributes to the output voltage. Fig. 12 compares theoretical voltage gains (given by (1) and (4)) against measured voltage gain.

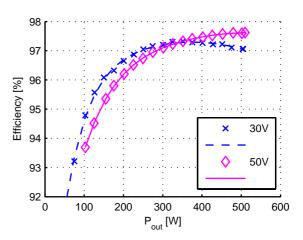

Finally the efficiency of the converter has been measured using four precision digital multimeters Fluke 8845A. Since the input current exceeds the multimeter current range an external precise shunt resistor has been used. Measured efficiency curves are presented on Fig. 13.

## 5. Conclusion

This paper describes the boost converter with the three-state switching cell. To improve the design and reduce size of the converter foil windings are used instead of round wires or Litz wires. The dc inductor with foil winding is characterized by a very low dc resistance. For the three winding transformer (the push-pull transformer) proper arrangement of foil windings ensures a very low resistance for all current components present in its windings. Measured peak efficiency exceeds 97% for low and high input voltage. Also it has been demonstrated that the regulation range of this type of converter can be increased by operation with duty cycle between 50% and  $D_{\rm cr}$ .

# Acknowledge

This project is supported by Dansk Energi net under PSO project no. 562/06-14-26808.

## References

- [1] P. Klimczak and S. Munk-Nielsen, "Comparative study on paralleled vs. scaled dc-dc converters in high voltage gain applications," in *Power Electronics and Motion Control Conference, 2008. EPE-PEMC 2008. 13th*, 2008, pp. 108-113.

- [2] B. Ju-Won, R. Myung-Hyo, K. Tae-Jin, Y. Dong-Wook, and K. Jong-Soo, "High boost converter using voltage multiplier," in *Industrial Electronics Society, 2005. IECON* 2005. 31st Annual Conference of IEEE, 2005, p. 6 pp.

- [3] Z. Qun and F. C. Lee, "High-efficiency, high step-up DC-DC converters," *Power Electronics, IEEE Transactions on,* vol. 18, pp. 65-73, 2003.

- [4] W. Rong-Jong and D. Rou-Yong, "High stepup converter with coupled-inductor," *Power Electronics, IEEE Transactions on,* vol. 20, pp. 1025-1035, 2005.

- [5] K. C. Tseng and T. J. Liang, "Novel highefficiency step-up converter," *Electric Power Applications, IEE Proceedings -,* vol. 151, pp. 182-190, 2004.

- [6] R. J. Wai and R. Y. Duan, "High-efficiency DC/DC converter with high voltage gain," *Electric Power Applications, IEE Proceedings* -, vol. 152, pp. 793-802, 2005.

- [7] G. V. Torrico-Bascope, R. P. Torrico-Bascope, D. S. Oliviera, F. L. M. Antunes, S. V. Araujo, and C. G. C. Branco, "A Generalized High

Voltage Gain Boost Converter Based on Three-State Switching Cell," in *The 32nd Annual Conference of the IEEE Industrial Electronics Society IECON'06*, Paris, France, 2006, pp. 1927-1932.

- [8] P. Zacharias, B. Sahan, S. V. Araújo, F. L. M. Antunes, and R. T. Bascopé, "Analysis and Proposition of a PV Module Integrated Converter with High Voltage Gain Capability in a non-isolated Topology," in *The 7th International Conference on Power Electronics* Daegu, Korea: IEEE, 2007.

- [9] G. V. T. Bascope and I. Barbi, "Generation of a family of non-isolated DC-DC PWM converters using new three-state switching cells," in *Power Electronics Specialists Conference, 2000. PESC 00. 2000 IEEE 31st Annual*, 2000, pp. 858-863 vol.2.

- [10] E. H. Kim and B. H. Kwon, "High step-up resonant push-pull converter with high efficiency," *Power Electronics, IET,* vol. 2, pp. 79-89, 2009.

- [11] L. Po-Wa, L. Yim-Shu, D. K. W. Cheng, and L. Xiu-Cheng, "Steady-state analysis of an interleaved boost converter with coupled inductors," *Industrial Electronics, IEEE Transactions on,* vol. 47, pp. 787-795, 2000.

- [12] C. W. T. McLyman, *Transformer and inductor design handbook*: Marcel Dekker, 2004.

- [13] J. D. Pollock and C. R. Sullivan, "Gappedinductor foil windings with low AC and DC resistance," in *Industry Applications Conference, 2004. 39th IAS Annual Meeting. Conference Record of the 2004 IEEE*, 2004, p. 557.

- [14] J. D. Pollock and C. R. Sullivan, "Modelling Foil Winding Configurations with Low AC and DC Resistance," in *Power Electronics Specialists Conference, 2005. PESC '05. IEEE 36th*, 2005, pp. 1507-1512.

- [15] M. Nymand and M. A. E. Andersen, "A new approach to high efficiency in isolated boost converters for high-power low-voltage fuel cell applications," in *Power Electronics and Motion Control Conference, 2008. EPE-PEMC 2008.* 13th, 2008, pp. 127-131.