Universidad Politécnica de Cartagena E.T.S. de Ingeniería de Telecomunicación

Espacio-Tele⊏o n<sup>0</sup>1 (2010) Revista de la ETSIT-UPCT

## Estimulador Coclear: Prototipo de evaluación y emulación

ERNESTO ARTURO MARTÍNEZ RAMS $^1$ , SERGIO DANIEL CANO ORTIZ $^1$  Y VICENTE GARCERÁN HERNÁNDEZ $^2$

- 1. Universidad de Oriente, Santiago de Cuba.

- 2. Departamento de Electrónica, Tecnología de Computadoras y Proyectos. Universidad Politécnica de Cartagena.

eamr@fie.uo.edu.cu; scano@fie.uo.edu.cu; vicente.garceran@upct.es

#### Resumen

En el presente trabajo se expone el diagrama en bloque de un diseño electrónico que permite emular el funcionamiento de un estimulador coclear o comúnmente conocido como implante coclear con fines investigativos. Dado a la versatilidad de su diseño permite emular y probar en tiempo real múltiples estrategias de estimulación coclear, tanto las actualmente conocidas (CIS, etc.) como cualquier variante nueva.

Proyecto/Grupo de investigación: Diseño electrónico y técnicas de tratamiento de señales.

Líneas de investigación: Implantes Cocleares; Estimulador Coclear.

#### 1. Introducción

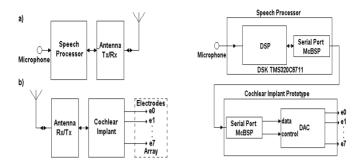

Los implantes cocleares [1-6] son dispositivos electrónicos introducidos en el oído interno, por medio de los cuales algunas personas totalmente sordas pueden lograr la audición, Figura 1, izquierda [2-4]. Procesan la señal en el rango audible del ser humano y, de acuerdo a la teoría tonotópica [1], [6-10], estimulan la cóclea para producir la audición. Este trabajo tiene como objetivo el desarrollo de un prototipo de implante coclear con características versátiles que permita emular nuevas variantes de estimulación coclear, así como las ya conocidas, permitiendo probar la factibilidad de la implementación de nuevas

Figura 1: Izquierda: Esquema simplificado en bloques de un implante coclear, a) Dispositivo externo compuesto por procesador del habla y el circuito de antena, b) Dispositivo implantable constituido por la antena, el implante propiamente dicho, y la matriz de electrodos. Derecha: Esquema general del diseño propuesto.

estrategias que demanden un mayor número de cálculos a un DSP (Procesador Digital de Señales) en tiempo real y que a su vez estas mejoren la calidad de la audición del implantado. La Figura 2 muestra el diagrama general en bloques del diseño desarrollado. El procesador del habla constituido por una tarjeta con un DSP, y acoplado con la maqueta prototipo de implante a través de un puerto serie.

El procesador del habla de la Figura 2 lo constituye una tarjeta de evaluación DSK (Digital Starter Kit) la cual posee un DSP de la serie TMS320C6711 de Texas Instruments perteneciente a la familia del C6000, y acoplado con la maqueta prototipo de implante a través del puerto de bus serie multicanal (McBSP) [11-16].

El DSP TMS320C6711 de aritmética flotante, es capaz de ejecutar 1,200 millones de operaciones en punto flotante por segundo, por lo que por su alta potencialidad y velocidad permite el desarrollo de las funciones del procesador del habla para implantes cocleares, admitiendo las actuales estrategias y cualquier otra nueva que demande más velocidad que las actuales.

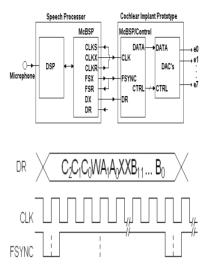

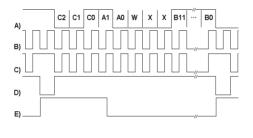

La Figura 2 (superior) muestra el diagrama en bloques de las señales de comunicación entre el procesador y el prototipo de implante. La Figura 4 muestra una descripción de las señales empleadas en la comunicación serie. DR es la señal o trama de datos a transmitir y porta información correspondiente al nivel de estimulación por electrodo del implante, CLK es la señal de reloj generada por el procesador del habla y enviada al implante para que los procesos trabajen de forma sincrónica en conjunto con la señal FSYNC que completa el proceso de sincronía, indicándole al implante el inicio y fin de cada trama de datos.

Figura 2: Superior: Diagrama en bloques de las señales de comunicación a través del puerto serie sincrónico. Inferior: Señales de la comunicación serie. La estructura de la trama de datos de DR es:  $C_2C_1C_0$  los bits para la selección del conversor digital analógico (DAC); W es un bit reservado (0h);  $A_1A_0$  es la dirección del registro interno del DAC empleado; XX son dos bits opcionales (cualquier valor);  $B_{11...}B_0$  constituye el código de conversión.

# 2. Prototipo de implante coclear

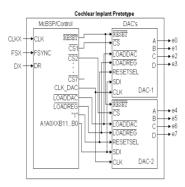

La tarjeta que emula el implante coclear fue diseñada con circuitos integrados de tecnología CMOS de alta velocidad y de montaje superficial, permitiendo manejar señales digitales de alta razón de bits. La tarjeta prototipo de implante coclear posee 8 salidas analógicas con entrada por puerto serie. Cada salida tiene una resolución de 12 bits, permitiendo actualizar las respectivas salidas de forma secuencial. Los datos provenientes del procesador del habla son dirigidos a sus respectivas salidas analógicas, para obtener la estimulación coclear deseada. El diseño permite obtener 8 canales de salidas analógicas y actualizadas de forma secuencial, logrando 1 canal de 64kHz, o 2 canales de 32kHz, ó 4 canales de 16kHz, ó 8 canales de 4kHz. Indistintamente se pueden emplear valores de frecuencia de salida siempre y cuando la  $\sum_{n=1}^8 f_{canal}\left(n\right) = 64kHz$  siendo 64kHz el máximo valor que se puede obtener a la salida. La tarjeta emuladora del implante se divide en dos partes: bloque McBSP/Control, y el bloque de conversión. La Figura 5 muestra las señales de entrada y salida de cada uno de estos bloques.

Al bloque McBSP/Control le llega la señal de reloj CLKX proveniente del procesador de habla, junto con la señal de sincronismo FSX y la trama de datos DX.

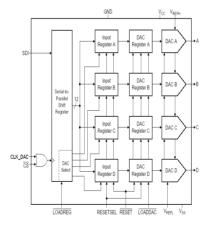

Figura 3: Diagrama en bloques del implante coclear.

El mismo decodifica la trama de datos recibida y actúa sobre las señales de control  $\overline{RESET}$ ,  $\overline{CS_n}$ ,  $\overline{LOADDAC}$ ,  $\overline{LOADDEG}$ , además de los bits  $A_1A_0$  y los datos  $B_{11} \dots B_0$ , que se entregan al bloque conversor seleccionado que contiene los conversores digitales analógicos.

Los datos provenientes de la trama de recepción (Figura 4) se descomponen en dos partes: bits de control o direcciones ( $C_2C_1C_0WA_1A_0XX$ ) y los bits ( $B_{11}...B_0$ ) correspondientes al voltaje de la correspondiente salida analógica de estimulación coclear, indicada por los bits de direccionamiento.

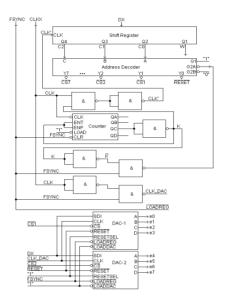

La Figura 4 muestra la lógica de control del bloque McBSP/Control. Este deja pasar directamente la señal DX recibida a la entrada de los bloques conversores, pero en este último solo serán procesados los últimos 16 bits de la trama ( $A_1A_0XXB_{11}...B_0$ ). La señal del reloj (CLKX) se lleva a un contador que junto con la señal de sincronismo FSYNC deja pasar solo 4 pulsos del reloj al registro de desplazamiento así como los bits de control ( $C_2C_1C_0W$ ) que luego se presentarán de forma paralelo al decodificador de direcciones, generando este último las señales de "chip select" (CS) o  $\overline{RESET}$ , ver tabla 1. La señal de  $\overline{RESET}$ , automáticamente reinicia todos los DAC del implante. La señal  $CS_1$  y  $CS_2$  selecciona al primer o al segundo bloque conversor respectivamente. Los bits  $A_1A_0$  seleccionan la correspondiente salida analógica (A-D) dentro del bloque seleccionado (figuras 3, 4, 5 y tabla 2).

La trama de datos de 16 bits de conversión (dirección de registro interno  $A_1A_0$ , más los bits XX no usados, y el código de conversión  $B_{11}...$   $B_0$ ) llegan en forma serie al mismo tiempo a los dos bloques conversores, pero el dato solo será procesado por el bloque conversor seleccionado por la señal CSn. El bloque conversor se representa en la Figura 5.

Figura 4: Lógica de control del bloque McBSP/Control.

Figura 5: Diagrama del bloque conversor DAC, formado por: un registro de desplazamiento serie/paralelo común para los cuatros canales del bloque conversor, más 2 registros por canal, registro de entrada y registro DAC respectivamente. La señal  $\overline{LOADREG}$  controla al registro de entrada, y la señal  $\overline{LOADDAC}$ maneja al registro DAC.

Otro dato de interés es que el diseño permite obtener tanto señales de salida bipolares como unipolares. La tabla 1 refleja el tipo de salida analógica que se puede obtener (unipolar o bipolar) de acuerdo al código recibido ( $B_{11...}B_0$ ) para la conversión digital/analógica y el voltaje de referencia empleado ( $V_{REFL}$  y  $V_{REFH}$ ).

| Bits de |       | Chip Select (CS) |                                 |        |        |       |

|---------|-------|------------------|---------------------------------|--------|--------|-------|

| control |       |                  | "0": activado; "1": no activado |        |        |       |

| $C_2$   | $C_1$ | $C_0$            | $CS_7CS_3$                      | $CS_2$ | $CS_1$ | RESET |

| 0       | 0     | 0                | 1                               | 1      | 1      | 0     |

| 0       | 0     | 1                | 1                               | 1      | 0      | 1     |

| 0       | 1     | 0                | 1                               | 0      | 1      | 1     |

| 0       | 1     | 1                | reservados                      | 1      | 1      | 1     |

| 1       | X     | X                | reservados                      | 1      | 1      | 1     |

Cuadro 1: Selección del bloque conversor

| Bits    | de    | Salida Analógica                      |   |   |   |  |

|---------|-------|---------------------------------------|---|---|---|--|

| control |       | "1": actualizada; "0": no actualizada |   |   |   |  |

| $A_1$   | $A_0$ | D                                     | С | В | A |  |

| 0       | 0     | 0                                     | 0 | 0 | 1 |  |

| 0       | 1     | 0                                     | 0 | 1 | 0 |  |

| 1       | 0     | 0                                     | 1 | 0 | 0 |  |

| 1       | 1     | 1                                     | 0 | 0 | 0 |  |

Cuadro 2: Bits de control de la tarjeta prototipo de implante coclear.

Debido al negativo efecto de la interacción entre canales adyacentes de estimulación [1], [6], [10], se escogió para la implementación la variante de estimulación secuencial, la cual en el presente diseño se logra manteniendo la señal  $\overline{LOADDAC}$  en el nivel lógico alto para que los datos pasen directamente desde el registro serie/paralelo al registro DAC, e instantáneamente tener a la salida el voltaje analógico equivalente al dato presente en el registro DAC.

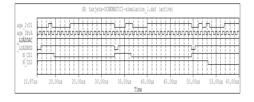

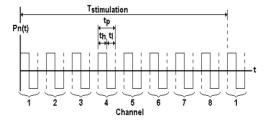

La Figura 6 (superior) muestra el cronograma de las señales de control del estimulador coclear. La Figura 6 (inferior) muestra la simulación de las señales de control con el simulador ORCAD/PSPICE a la velocidad de trabajo del implante. La Figura 7 muestra el cronograma de las señales de salida de estimulación coclear en un único eje de tiempo. Cada pulso corresponde a la estimulación de un determinado punto de la cóclea. Como se aprecia se logra la estimulación secuencial de cada electrodo de la cóclea, y es la forma de estimulación que mejores resultados ha dado con respecto a la estimulación instantánea de todos los electrodos [1], [10], por las interferencias entre canales que genera esta última.

| Tipo     | Registro | $\mathbf{V}_{REFL}$ | $\mathbf{V}_{REFH}$ | Voltaje             |

|----------|----------|---------------------|---------------------|---------------------|

| de       | de en-   |                     |                     | analógico           |

| salida   | trada    |                     |                     |                     |

|          | 0x000h   |                     |                     | - V <sub>REFL</sub> |

| Bipolar  | 0x800h   | _                   | +                   | 0V                  |

|          | 0xFFFh   |                     |                     | $+ V_{REFH}$        |

|          | 0x000h   |                     |                     | 0V                  |

| Unipolar | 0x800h   | 0V                  | +/-                 | +/-                 |

|          |          |                     |                     | $V_{REFH}/2$        |

|          |          |                     |                     |                     |

|          | 0xFFFh   |                     |                     | +/-                 |

|          |          |                     |                     | $V_{REFH}$          |

Cuadro 3: Niveles de salida del prototipo de implante coclear.

Figura 6: Superior: Cronograma de las señales de control del estimulador coclear. (A) DX; (B) CLKX; (C)  $CLK\_DAC$ ; (D) FSYNC o  $\overline{LOADREG}$ ; (E)  $\overline{CS_1}$  Inferior: Simulación de las señales de control.

Figura 7: Cronograma de las señales de salida de estimulación coclear

Del cronograma presentado en la Figura 7 se obtiene:

$$t_p = t_H + t_L, \quad T_{stim} = \frac{1}{F_{stim}} = N \cdot 3 \cdot t_H,$$

$$t_H = \frac{T_{stim}}{N \cdot 3}, \quad t_{CLK} = \frac{1}{F_{CLK}} = \frac{t_H}{N_{bits}}.$$

$t_H$  y  $t_L$  son los tiempos en el nivel alto y bajo del pulso de estimulación respectivamente. En el diseño realizado se tomó como criterio a  $t_H$  igual  $at_L$ ;  $t_P$  es el tiempo de duración del pulso bifásico;  $T_{stim}$  es el período de la señal de estimulación por electrodo;  $F_{stim}$  es la frecuencia de estimulación por electrodo;  $t_{CLK}$  y  $F_{CLK}$  son el período y frecuencia del reloj de transmisión serie (señal CLK); N es el número de canales activos a estimular;  $N_{bits}$  es el número de bits de la trama a transmitir.

#### 3. Resultados

El presente diseño fue probado con muy buenos resultados, para una frecuencia de estimulación por canal de 4kHz  $(F_{stim})$ , para un período de 0.25ms por canal  $(T_{stim})$ , y 8 canales activos (N), tramas de transmisión de 20bits  $(N_{bits})$ ; duración de los pulsos en nivel alto  $(t_H)$  o bajo  $(t_L)$  de 10.417 $\mu$ s, dando como resultado finalmente el empleo de un reloj de transmisión de 1.92MHz  $(F_{CLK})$ , para un período de 0.521 $\mu$ s  $(t_{CLK})$ .

Una de sus características más importantes es que permite acoplarse a cualquier DSP desarrollado por la firma de la Texas Instruments por su conectividad a través del puerto McBSP. El implante prototipo posee 8 salidas analógicas para lo cual emplea conversores digitales analógicos de alta velocidad y con una resolución de 12 bits cada uno, para una relación señal a ruido máxima de 72dB. Cada salida analógica equivale a una zona de generación de estímulos eléctricos a enviar al cerebro. La versatilidad del diseño consiste en que a pesar del reducido número de salidas, permite emular: estimulación secuencial (8 salidas multiplexadas en tiempo); razón de estimulación igual o diferente por canal; estimulación bifásica y monofásica.

La Figura 8 (izquierda) muestra una fotografía del Estimulador Coclear Prototipo de Evaluación formado por el procesador del habla y la tarjeta que emula la función mecánico-eléctrica de la cóclea, acopladas a través de puerto serie sincrónico McBSP. La Figura 8 (derecha) muestra el osciloscopio analógico digital HM407-2 de HAMEG-Instruments utilizado para efectuar las mediciones de las señales de salida, así como los parámetros de tiempos y frecuencias de las señales, (en su pantalla muestran 2 canales de salida de la tarjeta).

Para la comprobación del diseño del hardware y la realización del PCB de la tarjeta se empleó el software CADENCE PSD 14.2. Para la programación del

Figura 8: Izquierda: Tarjeta emuladora de estimulación coclear acoplada al DSK TMS320C6711. Derecha: Visualización de dos canales de salida de la tarjeta.

Procesador del habla se empleó el Code Composer Studio (CCS) versión 2.0 del TMS320C6711.

### 4. Conclusiones

Con el presente trabajo se logró implementar un estimulador coclear prototipo para fines investigativos. En este el procesador del habla realiza las funciones del oído interno implementando las funciones de la membrana basilar de la cóclea, más los mecanismos de compresión de la señal como lo hace un oído normal.

Como se expone en el trabajo, la versatilidad del diseño consiste en que permite emular y probar diferentes estrategias de estimulación coclear tanto las actualmente conocidas como cualquier otra variante que se pretenda emular en tiempo real. Permitiendo el diseño emular en tiempo real estimulación secuencial (8 salidas multiplexadas en tiempo), más permite estimulación bifásica y monofásica como los implantes de las firmas MEDEL, Cochlear Corporation y Nucleus, pero el diseño permite además como una característica novedosa estimulación con igual o desigual razón de estimulación por canal, permitiendo implementar estimulación con multiresolución.

El presente diseño fue probado con muy buenos resultados en tiempo real estimulando 8 electrodos de forma secuencial a una frecuencia de estimulación de 4kHz (0.25ms de período) por canal, lo cual permite una buena representación espectral de la señal de voz filtrada por la membrana coclear. Puede lograr pulsos bifásicos por canal de duración como mínimo de  $20.833\mu s$ ,  $10.417\mu s$  de duración del pulso en nivel alto y bajo.

## 5. Agradecimientos

Agradecemos la colaboración brindada por el Departamento de Electrónica, Tecnología de Computadoras y Proyectos de la Universidad Politécnica de Cartagena de España, y a la Agencia Española de Cooperación Internacional (AECI).

#### Referencias

- [1] Advanced Bionics Corporation, CLARION TM. Multi Strategy Cochlear Implant. Version 2.0. 12740 San Fernando Road Sylmar, California 91342-3728: 1996.

- [2] Advanced Bionics Corporation. http://www.cochlear.com/Spanish/.

- [3] MED-EL. http://www.medel.com/LANG/SPA/.

- [4] Nucleus. http://www.cochlear.com/spanish/.

- [5] Philip Loizou, "Introduction to cochlear implants", IEEE Engineering in Medicine and Biology Magazine, vol. 18, no. 1, pp. 1-36, 1999.

- [6] Philip Loizou, "Signal Processing for Cochlear Prosthesis: A Tutorial Review", Proceedings of the 40th Midwest Symposium on Circuits and Systems (IEEE MWSCAS'97), vol. 2, no. 1, pp. 200-204, 1997.

- [7] Michael S.Landy. Course of Perception.

- [8] Hearing and Balance. WEB. 22-3-1996.

- [9] Fundamentals of Hearing & Speech Science.

- [10] Loizou, P. C., "Signal processing for cochlear prosthesis: a tutorial review", Proceedings of the 40th Midwest Symposium on Circuits and Systems (IEEE MWSCAS'97), vol. 2, no. 1, pp. 881-885, 1998.

- [11] Texas Instruments. Using the TMS320C6x McBSP as a High Speed Communication Port. SPRA455, 1998.

- [12] Texas Instruments. TMS320C6000 McBSP: AC'97 Codec Interface (TLC320AD90). SPRA528. 1999.

- [13] Texas Instruments. TMS320C6000 Peripherals Reference Guide. SPRU190D. 2001.

- [14] Texas Instruments. TMS320C6000 DSP. Multichannel Buffered Serial Port (MCBSP). Reference Guide. SPRU580A. 2003.

- [15] Texas Instruments. TMS320C6000 DSP. Multichannel Buffered Serial Port (MCBSP). Reference Guide. SPRU580B. 2003.

- [16] Texas Instruments. TMS320VC5501/5502/5509/5510 DSP. Multichannel Buffered Serial Port (MCBSP). Reference Guide. SPRU592A. 2002.