# Efficient Estimation and Correction of Mismatch Errors in Time-Interleaved ADCs

Christian A. Schmidt, Juan E. Cousseau, *Senior Member, IEEE*, José L. Figueroa, *Senior Member, IEEE*, Benjamin T. Reyes, and Mario R. Hueda

Abstract—We present a novel method for the estimation and correction of mismatch errors in time-interleaved analog-todigital converters. The estimation of the mismatch errors requires a training signal, but it is efficient, accurate, and effective while keeping low the complexity of the associated algorithm, when compared with other works in the literature. The compensation strategy uses the estimated parameters for offset and gain mismatch error correction, and implements a low-complexity (similar to that of a finite-impulse response filter) Lagrange interpolation filter to correct errors due to timing mismatch, which depends on the dynamics of the input signal. The proposed compensation strategy achieves almost ideal behavior over a wide bandwidth, i.e., only 12% of oversampling is required for an almost complete cancelation of distortion. The method has been tested under severe mismatch conditions (up to 10% timing mismatch and 5% gain and offset mismatch), showing an improvement of over 6 bits in the effective number of bits and 50 dB in the spurious-free dynamic range. In addition, when compared with the available techniques, no limitation on the number of channel converters is introduced since the compensator effectively cancels the distortion even in the presence of large mismatches.

*Index Terms*—Analog-to-digital converter (ADC), correction, estimation, mismatch error, time interleaved (TI).

### I. INTRODUCTION

S THE bandwidth, dynamic range, and operation frequency of modern telecommunication systems increase, efficient high-resolution analog-to-digital converters (ADCs) operating at higher sampling rates are required. While some ADC architectures can obtain high resolution at a relatively high conversion speed, for some applications, the conversion speed of a single ADC might not be enough [1].

Among the alternative architectures to solve the tradeoff, a possible solution is to use time-interleaved (TI) ADCs. The TI architecture has several ADCs interleaved in time such that the overall conversion rate of the system is propor-

Manuscript received March 5, 2015; revised September 2, 2015; accepted September 8, 2015. The Associate Editor coordinating the review process was Dr. Niclas Bjorsell.

C. A. Schmidt, J. E. Cousseau, and J. L. Figueroa are with the Instituto de Investigaciones en Ingeniería Eléctrica-Consejo Nacional de Investigaciones Científicas y Técnicas (CONICET), Universidad Nacional del Sur, Bahía Blanca 8000, Argentina (e-mail: cschmidt@uns.edu.ar; jcousseau@uns.edu.ar; figueroa@uns.edu.ar).

B. T. Reyes and M. R. Hueda are with the Laboratorio de Comunicaciones Digitales, Universidad Nacional de Cordoba-CONICET, Córdoba X5016GCA, Argentina (e-mail: breyes@efn.uncor.edu; mhueda@efn.uncor.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TIM.2015.2490378

tionally increased to the number of ADCs used [1]. Unfortunately, any mismatch in gain, offset, or sampling time among these converters will result in nonlinear distortion of the sampled signal, thus deteriorating the performance of the whole system. Just to give an application example, in [2], it is shown that even a slight mismatch in the TI ADC structure can severely affect the bit error rate (BER) behavior of an Orthogonal Frequency Division Multiplexing link. Therefore, the mismatches among ADCs in a TI structure should be estimated and their effects should be compensated for.

1

The estimation and correction of mismatch errors in TI ADCs and the tools available have been widely studied in the last few years [3]-[20]. Brief descriptions of the main approaches found in the literature are presented in [12] and [14]. The main strategies can be divided into two different groups: 1) adaptive (blind) equalization [6], [9], [11], [15] and 2) offline estimation plus online correction [3], [4], [7], [8], [13], [21]. In general, the first type of compensation has the advantage that neither prior information about the mismatches nor the input signal is required. Another characteristic is that it adapts to changes in the parameters involved. However, it exhibits a large convergence period of time before the compensation actually works [6], [9], [11], [15], and the final result has in general lower accuracy than the offline estimation plus online correction-based methods [22].

Furthermore, the solutions obtained are usually tailored for a particular channel ADC architecture [9], [11], [15] or valid for a limited number of TI ADCs. Also, in some cases, the required computation complexity becomes quite high [6].

Foreground calibration, using the previous estimation of the mismatch between the different ADCs, leads to more accurate results. However, the use of a training sequence is required for the estimation of the parameters involved [3], [4], [7], [13]. For example, this approach is particularly suitable for wireless communication standards, where data transmission is performed in frames with training data for channel equalization and synchronization. The methods available so far providing high compensation performance in the presence of large mismatches over a wide bandwidth require a high computational cost. While some methods are also capable of coping with intrachannel nonlinear effects, they are either architecture dependent [9], [11] or the computational cost is orders of magnitude higher [4]. As an alternative, these effects can be corrected before mismatch compensation is needed [11].

In this paper, we propose a simple strategy for the estimation of mismatch errors in TI ADCs and a low-complexity compensator that effectively removes the associated distortion in the whole Nyquist bandwidth. In particular, we propose an efficient estimation method for the mismatch parameters through least squares (LS) by choosing adequate error functions. After compensating for offset and gain errors, a (low-complexity) Lagrange interpolation polynomial is used to deal with timing errors.

Timing mismatch correction, which is a particular case of recovering uniformly sampled data from nonuniform samples [23], is usually the main concern in TI ADCs, due to its dynamic and frequency-dependent nature. As illustrated by the simulation results, the compensation performance in terms of Signal-to-Noise and Distortion Ratio/spurious-free dynamic range (SFDR) improvement, accuracy in the estimation of mismatch parameters, and robustness to mismatch variations is very good even under severe mismatch conditions. Indeed, only 12% of oversampling is required for an almost complete cancelation of distortion, showing an improvement of over 6 bits in the effective number of bits (ENOB) and 50 dB in the SFDR for up to 10% timing mismatch and 5% gain and offset mismatch. Furthermore, a low complexity for both estimation and correction of all three main mismatch errors is maintained.

As previously mentioned, while some methods are also capable of coping with large timing mismatches (about 10%) [6]–[8], the associated computational complexity for both estimation and correction of the output digital signal is by far higher than that of the method proposed here. On the other hand, other methods with lower computational cost [9], [11], [15] either correct only gain and offset mismatches [15] or exhibit other limitations such as a large convergence time inherent to most adaptive methods and are targeted for a specific ADC channel architecture [9], [11].

In general, no other method so far simultaneously offers the following features of our proposal:

- accurate, yet low-complexity, mismatch error estimation and correction for all three main sources of error (gain, offset, and timing);

- 2) robustness to the presence of large mismatches for the three sources of error mentioned above;

- 3) no additional reference ADCs required;

- 4) accurate compensation over a wide bandwidth (close to the whole Nyquist band).

This paper is organized as follows. In Section II, a brief description of TI ADCs is provided, and the effect of mismatch errors is analyzed and modeled. In Section III, a new simple and efficient approach for the estimation of mismatch errors is presented and compared with other methods found in [3], [7], [11], and [14] in terms of accuracy and computational complexity. Compensation of mismatch errors is discussed in Section IV, where the issue of timing mismatch compensation is analyzed and different interpolation methods are considered. A novel simplified form of Lagrange interpolation polynomials is presented, which is shown to outperform the other interpolation techniques. The method is compared with other state-of-the-art proposals, both in

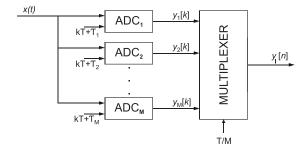

Fig. 1. Interleaved ADCs.

terms of complexity and performance [3], [13]. The evaluation and simulation results are provided in Section V, and the conclusion is presented in Section VI.

### II. TIME-INTERLEAVED ADCs

Fig. 1 shows the block diagram of a TI ADC array with M ADCs working in parallel. Each ADC samples the input signal with a sampling period T and a relative phase shift (m-1)T/M. We first consider the conversion of x(t) into  $y_{Im}(t)$  at the mth converter by modulation of x(t) with the Dirac comb function

$$q_{Im}(t) = \sum_{k=-\infty}^{\infty} \delta(t - kT - \tau_{Im})$$

(1)

where

$$\tau_{Im} = \frac{m-1}{M}T\tag{2}$$

such that

$$y_{Im}(t) = x(t)q_{Im}(t) = x(t)\sum_{k=-\infty}^{\infty} \delta(t - kT - \tau_{Im}).$$

(3)

Due to the time-shifting property of the Dirac function, we get

$$y_{Im}(t) = \sum_{k=-\infty}^{\infty} x(kT + \tau_{Im})\delta(t - kT - \tau_{Im}).$$

(4)

Hence, at the output of the mth ADC, we get the discretetime sequence of samples

$$y_{Im}[k] = x(kT + \tau_{Im}). \tag{5}$$

Then, considering the sampling procedure for the M ADCs, we can write

$$y_{I}(t) = \sum_{m=1}^{M} y_{Im}(t)$$

$$= \sum_{m=1}^{M} \sum_{k=-\infty}^{\infty} x(kT + \tau_{Im})\delta(t - kT - \tau_{Im})$$

$$= \sum_{n=-\infty}^{\infty} x\left(n\frac{T}{M}\right)\delta\left(t - n\frac{T}{M}\right)$$

(6)

where n = Mk + m - 1 so that the multiplexed output of the M ADCs in the TI structure can be represented by the discrete-time sequence

$$y_I[n] = x \left( n \frac{T}{M} \right) \tag{7}$$

thus obtaining an equivalent sampling frequency M times higher. From now on, index n refers to the sample number at the output of the TI ADC array.

### A. Gain and Offset Mismatch Errors in TI ADCs

Unfortunately, due to fabrication process inaccuracies, any TI ADC architecture presents mismatch errors between the different ADC channels, which lead to a nonideal behavior. In this paper, we analyze the estimation and correction of offset, gain, and timing mismatch-induced errors. Offset mismatch is caused by different dc levels at each ADC output, whereas gain mismatch results when the gain from the analog input to the digital output is different for each ADC in the interleaved array. Timing mismatch is more critical and will be discussed in the next section.

Let us now consider the output of the *m*th ADC with only offset and gain mismatch

$$y_m[k] = G_m y_{Im}[k] + O_m = G_m x(kT + \tau_{Im}) + O_m$$

(8)

where  $G_m$  and  $O_m$  are the gain and offset of the mth ADC, respectively.

It is clear that  $G_m$  and  $O_m$  terms affect the multiplexed output y[n] every Mth sample. Hence, by defining the discrete sequences

$$P_G[n] = \sum_{k=-\infty}^{\infty} G[n - kM]$$

(9)

and

$$P_O[n] = \sum_{k=-\infty}^{\infty} O[n - kM]$$

(10)

where  $G[n] = [G_0, G_1, \ldots, G_{M-1}]$  and  $O[n] = [O_0, O_1, \ldots, O_{M-1}]$ , respectively (both defined for 0 < n < M - 1). Thus, we can model the nonideal output y[n] (affected by offset and gain mismatches) as a function of mismatch errors on the ideally sampled signal  $y_I[n]$  as follows:

$$y[n] = y_I[n]P_G[n] + P_O[n]. \tag{11}$$

Several remarks can be made about (11). First of all, since a time-domain product means convolution in the frequency domain, gain mismatch errors introduce different gains to the sampled band-limited replicas of x(t). However, if x(t) = 0 or  $G_m = \alpha$ ,  $\forall m = 1, ..., M$ , where  $\alpha$  is an arbitrary constant, there is no distortion. This is because if  $\alpha$  is the same for every ADC in the array, there is no gain mismatch. Second, since addition in time means addition in frequency, offset mismatch errors will introduce constant spurious tones independently of the input signal. In fact, distortion due to offset mismatch errors will appear in the output spectrum even if x(t) = 0. A similar expression to (11) is obtained in [12] following a slightly different analysis.

# B. Timing Mismatch Errors in TI ADCs

Timing mismatch is due to a phase shift  $\Delta t_m$  in the clock of ADC m, which results in deviation of the sampling instant

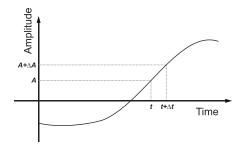

Fig. 2. Phase error while sampling.

(and hence an amplitude error in the sample taken), as illustrated in Fig. 2.

Now let us consider the *m*th ADC channel with all kinds of mismatch errors. According to the notation used so far, the output of such an ADC should be rewritten as

$$y_m[k] = G_m x(kT + \tau_m) + O_m \tag{12}$$

where now a timing mismatch is allowed between each ADC, and therefore

$$\tau_m = \tau_{Im} + \Delta t_m = \frac{m-1}{M}T + \Delta t_m. \tag{13}$$

As shown in Fig. 2, a  $\Delta t$  shift in the sampling instant will result in an amplitude error  $\Delta A$ . Therefore, we can model the effect of timing mismatch as an additive distortion to the ideal sample  $y_{Im}[k]$

$$y_m[k] = G_m(y_{Im}[k] + \Delta y_m[k]) + O_m.$$

(14)

It is clear from Fig. 2 and (12)–(14) that the error due to timing mismatch depends on the dynamics of the input signal. The output signal from the TI ADC with all mismatch errors is then

$$y[n] = (y_I[n] + \Delta y[n])P_G[n] + P_O[n]. \tag{15}$$

This manner to model the timing mismatch distortion as an (unknown) additive error renders the sequential estimation and correction of all mismatch errors possible and efficient, as will be shown in the following sections.

# III. ESTIMATION OF MISMATCH ERRORS IN TI ADCs

Estimation of mismatch errors is required as a first step in order to compensate for them. In addition, the quality of the estimates should be as high as possible while keeping low complexity for the compensation to be effective and feasible. In this section, we propose an estimation method that is simple and capable of accurately estimating the parameters even for large mismatch errors. We assume a sinusoidal training sequence to illustrate the method [i.e.,  $x(t) = \sin(2\pi f t + \phi)$ , f < 2M/T, such that at least two samples per period are taken in each channel in order to avoid aliasing in the training phase]. The estimation of mismatch errors is performed offline, and thus the exact training signal can be estimated as well without much effort. For example, in [24], the training sequence was estimated offline from a set of measurements of the ADC output by minimizing the rms error between the acquired data and an ideal ADC. Alternative methods to recover the training signal, such as sine-wave fitting, are described in [3], [7], and [25].

For the estimation of the mismatch parameters, we compare the output of each channel with an ideal sample (not the output of the complete TI ADC array).

Consider the output of the mth ADC in the interleaved array with gain, offset, and timing mismatch errors given by (14). If we compare it with the ideal sample  $y_{Im}[k]$ , we get

$$E_{O_m}[k] = y_m[k] - y_{Im}[k]$$

=  $(G_m - 1)y_{Im}[k] + G_m \Delta y_m[k] + O_m.$  (16)

Then, after taking L data samples, we can define a set of equations in vector form

$$\mathbf{E_{O_m}} = \mathbf{y_m} - \mathbf{y_{Im}} = \mathbf{1_L} O_m + \mathbf{v_O}$$

(17)

where

$$\mathbf{E_{O_m}} = [E_{O_m}[1], \dots, E_{O_m}[L]]^T$$

(18)

$$\mathbf{1}_{\mathbf{L}} = [1, \dots, 1]_{L}^{T} \tag{19}$$

and

$$\mathbf{v_O} = [v_O[1], \dots, v_O[L]]_L^T \tag{20}$$

where  $v_O[k] = (G_m - 1)y_{Im}[k] + G_m \Delta y_m[k]$ . Hence, the LS estimates of the offset yield

$$\hat{O}_m = \left(\mathbf{1_L}^T \mathbf{1_L}\right)^{-1} \mathbf{1_L}^T \mathbf{E_{O_m}} = \frac{1}{L} \sum_{k=1}^L E_{O_m}[k]. \tag{21}$$

Therefore, the estimate of the offset for the *m*th ADC is given by

$$\hat{O}_{m} = \frac{1}{L} \sum_{k=1}^{L} E_{O_{m}}[k]$$

$$= \frac{1}{L} \sum_{k=1}^{L} [(G_{m} - 1)y_{Im}[k] + G_{m} \Delta y_{m}[k] + O_{m}]. \quad (22)$$

We recall from (5) and (12)–(14) that  $\Delta y_m[k] = x(kT + \tau_{Im} + \Delta t_m) - x(kT + \tau_{Im})$ , and thus if  $y_{Im}[k]$  has zero mean, so does  $\Delta y_m[k]$ . The estimator is unbiased, and therefore, we have from (22) that if L is large enough and  $y_{Im}[k]$  has zero mean, then  $\hat{O}_m \cong O_m$ . Note that the offset estimator becomes unbiased for high values of L, and it therefore is asymptotically unbiased.

Now consider the gain error function defined as

$$E_{G_m}[k] = \frac{y_m[k] - \hat{O}_m}{y_{Im}[k]} = G_m + \frac{G_m \Delta y_m[k] + O_m - \hat{O}_m}{y_{Im}[k]}.$$

(23)

Similarly, we can take L data samples and formulate a set of equations in vector form as

$$\mathbf{E}_{\mathbf{G_m}} = \frac{\mathbf{y_m} - \hat{O}_m}{\mathbf{y_{Im}}} = \mathbf{1}_{\mathbf{L}} G_m + \mathbf{v_G}$$

(24)

where

$$\mathbf{E}_{\mathbf{G_m}} = [E_{G_m}[1], \dots, E_{G_m}[L]]^T$$

(25)

$$\mathbf{1}_{\mathbf{L}} = [1, \dots, 1]_{L}^{T} \tag{26}$$

and

$$\mathbf{v_G} = [v_G[1], \dots, v_G[L]]_L^T \tag{27}$$

where  $v_G[k] = (G_m \Delta y_m[k] + O_m - \hat{O}_m)/y_{Im}[k]$ . Hence, the LS estimates of the gain yield

$$\hat{G}_{m} = (\mathbf{1}_{L}^{T} \mathbf{1}_{L})^{-1} \mathbf{1}_{L}^{T} \mathbf{E}_{\mathbf{G}_{m}}$$

$$= G_{m} + \frac{1}{L} \sum_{k=1}^{L} \frac{G_{m} \Delta y_{m}[k] + O_{m} - \hat{O}_{m}}{y_{Im}[k]}.$$

(28)

We can therefore estimate the gain mismatch error  $G_m$  as

$$\hat{G}_m = \frac{1}{L} \sum_{k=1}^{L} E_{G_m}[k] = G_m + \frac{1}{L} \sum_{k=1}^{L} \frac{G_m \Delta y_m[k] + O_m - \hat{O}_m}{y_{Im}[k]}.$$

(29)

Having unbiased estimates of  $O_m$ , we see from (29) that if L is large enough, provided  $y_{Im}[k] \neq 0$ , then  $\hat{G}_m \cong G_m$ . If  $y_{Im}[k] = 0$ , then that sample is simply discarded for the estimation of  $G_m$ .

Let us now define the remaining error due to timing mismatch after correcting for offset and gain mismatches

$$E_{\Delta t_m}[k] = \frac{1}{\hat{G}_m} [y_m[k] - \hat{O}_m] - y_{Im}[k] \cong \Delta y_m[k].$$

(30)

Assuming a sinusoidal input signal, i.e.,  $x(t) = \sin(2\pi f t + \phi)$ , we can consider a simple and efficient manner to estimate the timing mismatch as follows.

According to [1], the maximum amplitude error  $\Delta A$  due to a shift  $\Delta t$  in the sampling instant occurs for the higher frequency component of the input signal. As we are using a sinusoidal training signal, we should chose a frequency close to half the channel sampling frequency, and the maximum error will occur near the zero crossings, where the slope of a sinusoidal signal is maximum. It can therefore be computed from a vector of L data samples as

$$\hat{\Delta}t_m = \frac{\max\left[E_{\Delta t_m}\right]}{2\pi f_0} \tag{31}$$

where  $f_0$  is the frequency of the input signal. The derivation of (31) can be found in [1].

Similar approaches for offset mismatch error estimation have been derived in [11] and [15]. There, the offset estimate is obtained either by simply averaging the output samples of each ADC [11] regardless of the input sequence or by comparing the output samples with a (slower but more accurate) reference ADC and averaging the result [15]. However, our offset estimator leads to more accurate results with faster convergence (in the sense that less samples are required to obtain a good estimate), even in the presence of large gain and timing mismatches. This feature is due to the lower variance of the proposed estimator. Consider, for example, the estimator proposed in [11], where the offset estimate is the average of each ADC output

$$\hat{O}_m = \frac{1}{L} \sum_{k=1}^{L} [G_m(y_{Im}[k] + \Delta y_m[k]) + O_m].$$

(32)

Then, the variance is given by

$$\operatorname{var}(\hat{O}_m) = \frac{1}{L} \sum_{k=1}^{L} [G_m(y_{Im}[k] + \Delta y_m[k]) + O_m - \mu]^2.$$

(33)

From (32), if  $y_{Im}[k]$  has zero mean, then  $\Delta y_m[k]$  also has zero mean and  $\mu = O_m$ . Thus, the variance of the estimator is given by

$$\operatorname{var}(\hat{O}_m) = \frac{1}{L} \sum_{k=1}^{L} [G_m(y_{Im}[k] + \Delta y_m[k])]^2.$$

(34)

Similarly, it can be easily shown that the variance of the estimator proposed in this paper is given by

$$\operatorname{var}(\hat{O}_m) = \frac{1}{L} \sum_{k=1}^{L} ([G_m - 1] y_{Im}[k] + G_m \Delta y_m[k])^2$$

(35)

which is clearly much smaller.

On the other hand, the simple, accurate, and efficient manner for the estimation of gain and timing mismatches presented here is only possible thanks to the model described by (15). For example, the algorithm for the estimation of gain (and offset) mismatch errors derived in [7] requires matrix inversion in the frequency domain after a fast Fourier transform calculation, which implies a computational complexity that is orders of magnitude higher. Also, the three methods mentioned in [11] and [14] as widely used in the literature for gain mismatch estimation require statistical information of the TI ADC output, modulation with a pseudorandom signal, or correlations, which obviously imply a higher computational complexity than the method proposed here.

As for the timing mismatch estimation, the widely used sine-fitting method, described, for example, in [3], involves the following procedure:

- applying a sine wave with a specified frequency to the TI ADC:

- 2) recording L output samples of each channel ADC;

- fitting a sine-wave function to each channel ADC output using an LS criterion to minimize the sum of the squared errors between this function and the recorded data;

- 4) choosing one of the *M* ADCs as a reference and computing the relative parameter difference between all ADCs to obtain the individual timing mismatches.

This procedure obviously implies a higher computational complexity than the estimator proposed in this paper.

Finally, the sequential estimation of mismatch errors proposed in this paper, which uses the previous estimates of the other error sources, enhances the estimation and gives robustness to large mismatches in the other parameters. The offset mismatch errors are computed first, then the gain mismatch errors are computed (subtracting the offset estimates), and finally, the timing mismatch (subtracting the offset estimates and dividing by the gain estimates) is calculated.

The estimation of mismatch errors is performed offline, and thus the exact training signal can be estimated as well without much effort. For example, in [24], the training sequence was estimated offline from a set of measurements of the ADC output by minimizing the rms error between the acquired data

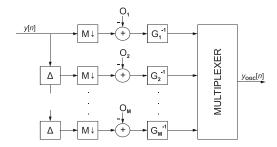

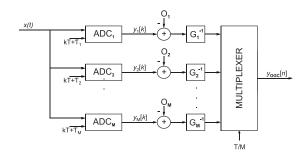

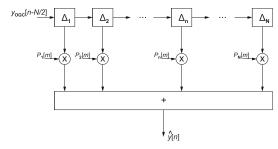

Fig. 3. Possible gain and offset compensation scheme. Here, y[n] is the multiplexed output of the TI ADC array.

Fig. 4. Improved gain and offset compensation scheme, prior to multiplexing the outputs of the ADCs.

and an ideal ADC. In practice, the ideal input signal used as reference is in fact estimated by the method proposed in [24].

The gain estimation requires the computation of the perfect discrete-time version of the input sine wave. Due to this point, bias on the gain estimation could be present. Nonetheless, this effect was considered in the simulations, where it is shown that even when the gain estimates are not exactly the real values (see Table II), this hardly affects the compensation performance (see Fig. 10).

We can assume that the issue of nonlinear distortion in each ADC channel has been previously corrected either by postprocessing or calibration, such that the effect of mismatch errors in the interleaved structure is dominant. There are many articles that treat that problem, for example, [24]. The focus of this article is set on the effect of mismatch in interleaved ADCs at a system level.

# IV. COMPENSATION OF MISMATCH ERRORS IN TI ADCs

### A. Compensation of Gain and Offset Mismatch Errors

Compensation of gain and offset mismatch errors in TI ADCs can be easily accomplished by first subtracting the estimated offset from the output samples of each ADC and then multiplying by the inverse of the estimated gain error. This procedure can be performed, for example, as shown in Fig. 3 (after multiplexing the ADCs' outputs), where y[n] is the output of the TI ADC without any compensation and  $y_{OGC}[n]$  is the output of the TI ADC after compensating for offset and gain errors, respectively.

Note that the gain and offset mismatch errors can also be corrected before multiplexing the ADCs' outputs, as shown in Fig. 4, with lower computational complexity.

### B. Compensation of Timing Mismatch Errors in TI ADCs

After compensating for gain and offset errors, which can be easily compensated for in a static manner as illustrated in Figs. 3 and 4, the remaining error due to timing mismatch between the different ADCs is usually quite big, especially for high timing mismatches and higher frequencies of the input signal [see (30) and (31)].

Errors due to timing mismatch arise when the input analog signal is sampled at periodic but nonuniform time instants. As the timing shifts have previously been estimated and the overall ideal sampling frequency is known, we have the following data available:

- 1) the actual instants where samples are being taken in each ADC ( $t_m[k] = kT + \Delta t_m$ );

- 2) the value of the samples taken at the actual time instants after correcting for offset and gain errors  $y_m[k]$ ;

- 3) the ideal sampling instants with no timing mismatches t[n] = nT/M.

Therefore, we can estimate the ideal samples that would have been taken at the ideal time instants through interpolation between the available samples using the available timing information. For that purpose, we analyze three types of interpolations with different complexities, which are representative of the problem formulation, i.e., linear interpolation, cubic spline interpolation, and Lagrange polynomial interpolation. For the problem at hand, we propose the use of Lagrange interpolation, a particular form of polynomial interpolation, since it provides the best solution among the three alternatives.

1) Linear Interpolation: Consider two consecutive samples at the output of the TI ADC array (already corrected for offset and gain mismatches)  $y_{\text{OGC}}[n]$  and  $y_{\text{OGC}}[n+1]$  taken at the sampling instants  $t[n] = nT/M + \Delta t_m$  and  $t[n+1] = (n+1)T/M + \Delta t_{m+1}$ , respectively. Then, we can trace a straight line between both samples and estimate the sample  $\hat{y}[n+1]$  belonging to the same line at the ideal sampling instant  $t_I[n+1] = (n+1)T/M$ . By definition, the slope will be the same for any points included in the line, in particular

$$\frac{y_{\text{OGC}}[n+1] - y_{\text{OGC}}[n]}{T/M + \Delta t_{m+1} - \Delta t_m} = \frac{y_{\text{OGC}}[n+1] - \hat{y}[n+1]}{\Delta t_{m+1}}$$

(36)

where we can obtain the estimated sample from (36) as

$$\hat{y}[n+1] = y_{\text{OGC}}[n+1] - \Delta t_{m+1} \frac{y_{\text{OGC}}[n+1] - y_{\text{OGC}}[n]}{T/M + \Delta t_{m+1} - \Delta t_m}.$$

(37)

Note from (37) that only few operations per sample are required to compute the corrected sample, and thus the complexity is as low as we can get.

2) Cubic Spline Interpolation: Splines are piecewise polynomials smoothly connected, where the joining points are called knots. For a spline of degree N, each segment is a polynomial of degree N and the additional smoothness constraint imposes the continuity of the spline and its N-1 derivatives at the knots. In general, cubic splines are preferred since higher order splines do not result in better results [26].

Therefore, given N+1 knots  $(t_i, y_{\text{OGC}i}), i = 0, 1, ..., N$ , we can interpolate between all pairs of knots  $(t_{i-1}, y_{\text{OGC}i-1})$

and  $(t_i, y_{OGCi})$  with polynomials  $q_i(t), i = 1, ..., N$  such that  $q'_i(t_i) = q'_{i+1}(t_i)$  and  $q''_i(t_i) = q''_{i+1}(t_i)$ , where ' denotes the derivative operator.

An algorithm for determining the polynomial  $q_i(t)$  for each segment is described in [27]. Following that approach, we can define:

$$q_i(t) = c_{0,i} + c_{1,i}(t - t_i) + c_{2,i}(t - t_i)^2 + c_{3,i}(t - t_i)^3$$

(38)

where the condition on the second derivative implies

$$q_i''(t) = k_i \frac{t_{i+1} - t}{t_{i+1} - t_i} + k_{i+1} \frac{t - t_i}{t_{i+1} - t_i}.$$

(39)

Integrating (39), we get

$$q_i'(t) = -\frac{k_i}{2} \frac{(t_{i+1} - t)^2}{t_{i+1} - t_i} + \frac{k_{i+1}}{2} \frac{(t - t_i)^2}{t_{i+1} - t_i} + \alpha_i$$

(40)

and integrating (40) gives

$$q_i(t) = -\frac{k_i}{6} \frac{(t_{i+1} - t)^3}{t_{i+1} - t_i} + \frac{k_{i+1}}{6} \frac{(t - t_i)^3}{t_{i+1} - t_i} + \alpha_i t + \beta_i.$$

(41)

Thus, after applying the continuity and smoothness conditions on  $q_i(t)$  and its derivatives at the knots, each segment polynomial can be determined, and the interpolation function is obtained.

# C. Lagrange Interpolation for Timing Mismatch Error Correction

Lagrange interpolation is composed of a set of N orthonormal polynomials of Nth order. Then, given a function f(t) and a data set  $f(t_1), \ldots, f(t_N)$ , the nth polynomial described by

$$P_n(t) = \prod_{\substack{j \neq n \\ j=1}}^{N} \left[ \frac{t - t_j}{t_n - t_j} \right]$$

(42)

satisfies  $P_n(t) = 1$  if  $t = t_n$  and  $P_n(t) = 0$  for  $t = t_j$ ,  $j \neq n$ . Hence, the polynomial defined as

$$P(t) = \sum_{n=1}^{N} [P_n(t) f(t_n)]$$

(43)

is an approximation for f(t) in the given interval, defined by the available data set.

It is clear from (42) and (43) that  $P(t_n) = f(t_n)$ , n = 1, ..., N. The approximation of f(t) by P(t) will be better at the center of the interval of data samples used for fitting the polynomial (around  $t_{N/2}$ ) and the approximation will be more accurate for higher N. However, if N is high, convergence problems will arise in the borders, i.e., around  $t_1$  and  $t_N$ .

In TI ADCs,  $f(t_n)$  is the output sample of the TI ADC array after correcting for gain and offset mismatches, and  $t_n = nT + \Delta t_m$  is the sampling instant at the periodic but nonuniform time interval defined by the sampling frequency of each ADC and the (previously estimated) sampling shift  $\Delta t_m$  in the mth ADC. Hence, we want to estimate f(t) at the correct sampling instant t.

From (42) and (43), that procedure requires  $N^2$  multiplications, N(N-1) divisions, and N sums for each sample.

Thus, the complexity of such an approach can be quite high for large N. Since we know a priori the values of subsequent  $t_n$ , thanks to the estimation of  $\Delta t_m$  for each ADC, a simpler implementation can be obtained after some considerations inherent to TI sampling.

# D. Simplified Lagrange Interpolation Due to the Periodic Nature of Order M of the Polynomials for TI ADCs

For the particular application of interpolation in TI ADCs for the compensation of timing mismatches,  $t_n$  and  $t_j$  in (42) are the time instants of the samples taken, whereas t is the ideal time instant without mismatch for which the value of the ideal sample will be estimated.

Given the periodic nature of the sampling time instant deviations in TI ADCs, the following (more detailed) notation can be used instead:

$$t_n = nT_s + \Delta t_n$$

$$t_j = jT_s + \Delta t_j.$$

(44)

Note that for M TI ADCs, the time deviation will be the same for every M sample, and therefore we can write

$$t_{n+M} = (n+M)T_s + \Delta t_n$$

$$t_{j+M} = (j+M)T_s + \Delta t_j.$$

(45)

Therefore, if we estimate the sample at the ideal time instant t at the center of the time window

$$t = (N/2)T_s t + MT_s = (N/2 + M)T_s.$$

(46)

Then

$$P_{n}(t + MT_{s}) = \prod_{\substack{j \neq n \\ j=1}}^{N} \left[ \frac{t + MT_{s} - t_{j+M}}{t_{n+M} - t_{j+M}} \right]$$

$$= \prod_{\substack{j \neq n \\ j=1}}^{N} \left[ \frac{t + MT_{s} - (j + M)T_{s} - \Delta t_{j}}{(n + M)T_{s} + \Delta t_{n} - (j + M)T_{s} - \Delta t_{j}} \right]$$

$$= \prod_{\substack{j \neq n \\ j=1}}^{N} \left[ \frac{t - jT_{s} - \Delta t_{j}}{(n - j)T_{s} + \Delta t_{n} - \Delta t_{j}} \right] = P_{n}(t). \quad (47)$$

That allows to conclude that the orthogonal polynomials  $P_n(t)$  in the available time window are exactly equal for an M time shift. This means that after M time instants, the Nth-order orthogonal polynomial coefficients need not be computed all over again as they coincide with previous calculations. Thus, considerable simplifications in complexity can be obtained. In addition, we know a priori the estimated values  $\Delta t_n$ ,  $\forall n$ , and we can therefore compute the MN different polynomial coefficients and store them in memory. Hence, we can think of  $P_n(t) = P_n(m)$  for  $m = 1, \ldots, M$ . This leads to the time-varying filter implementation shown in Fig. 5. The coefficients of the resulting time-variant filter are known, so the computational complexity is not really a big issue. However, it could also be implemented in parallel form, to further improve the performance.

Fig. 5. Time-variant filter for the implementation of Lagrange interpolation polynomials.

TABLE I

INTERPOLATION COMPUTATIONAL COMPLEXITY

| Interpolation method | Additions | Products/divisions | Total   |  |

|----------------------|-----------|--------------------|---------|--|

| Linear               | 4         | 2                  | 6       |  |

| Cubic splines        | 28        | 23                 | 51      |  |

| FIR filter [3]       | N         | N                  | 2N      |  |

| Simplified Lagrange  | N         | N                  | 2N      |  |

| Lagrange             | N         | $2N^2 - N$         | $2N^2$  |  |

| Method in [13]       | MN        | M(N+1)             | M(2N+1) |  |

Note that this is the exact solution for the Lagrange orthonormal interpolation polynomials and not an finiteimpulse response (FIR) approximation as proposed in [3]. An FIR approximation would imply that  $P_n(t)$  takes the same value for all t, which is clearly not the case. Such an approximation can lead to poor performance under certain conditions such as high-frequency input signals or large timing mismatches [3]. As will be shown by simulations, the method proposed here overcomes these limitations. Table I shows the computational complexity associated with the different interpolation methods previously analyzed, measured in terms of number of operations per output sample. The computational complexity of the algorithm presented in [13] is also included. Because the quality of the mismatch parameter estimates is the key for the compensation performance, for a fair comparison, we used our method to estimate the gain, offset, and timing mismatch parameters in all cases. Therefore, all methods compared use exactly the same estimates, and only the way in which they are used to perform the compensation differs.

### V. SIMULATION RESULTS

A set of simulations have been performed in order to evaluate the proposed method for the estimation and correction of mismatch errors in TI ADCs. The method was analyzed in its two main stages: 1) estimation of the mismatch quantities and 2) correction of gain, offset, and timing mismatch errors using the estimations obtained. The focus of the correction stage is on timing mismatch compensation performance, as this is the challenging part of the compensation procedure.

Following the model introduced in [13], a TI ADC array model composed of eight ADCs of 12-bit resolution was considered, each operating at 260 MHz for an aggregate sampling rate of 2.08 GS/s. This particular configuration was chosen so as to maximize the benefits of interleaving. For that purpose, the following condition should be

|                              | $ADC_1$ | $ADC_2$ | $ADC_3$ | $ADC_4$ | $ADC_5$ | $ADC_6$ | $ADC_7$ | $ADC_8$ |

|------------------------------|---------|---------|---------|---------|---------|---------|---------|---------|

| 0                            | 0.0213  | 0.0112  | 0.0429  | 0.0294  | 0.0125  | 0.0260  | 0.0331  | 0.0317  |

| Ô                            | 0.0213  | 0.0112  | 0.0429  | 0.0294  | 0.0125  | 0.0260  | 0.0332  | 0.0317  |

| G                            | 1.0444  | 1.0445  | 1.0398  | 1.0214  | 1.0046  | 1.0297  | 1.0457  | 1.0250  |

| $\hat{G}$                    | 1.0444  | 1.0445  | 1.0399  | 1.0214  | 1.0046  | 1.0296  | 1.0457  | 1.0250  |

| $\Delta t[ps]$               | 4.15    | 1.96    | 36.13   | 15.57   | 3.20    | 44.39   | 2.61    | 3.27    |

| $\hat{\Delta t}[	exttt{ps}]$ | 4.23    | 2.05    | 36.19   | 15.63   | 3.29    | 44.38   | 2.71    | 3.35    |

TABLE II

REAL AND ESTIMATED MISMATCH ERRORS

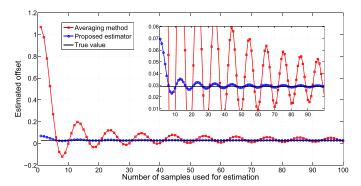

Fig. 6. Offset mismatch convergence as a function of the number of samples used.

satisfied [16]:  $M < (B+1)\ln(2)$ , where M is the number of interleaved ADCs and B is the bit resolution of each ADC. In this case,  $(B+1)\ln(2) = 9.01$ , so eight ADCs are used.

The input signal used as training sequence for the estimation of mismatch errors is a sinusoid  $x_t(t) = \sin(2\pi f t)$ ,  $f \le 130$  MHz, such that each channel ADC fulfills the Nyquist sampling criterion. For the compensation stage, the input signal considered is a sinusoid  $x_c(t) = \sin(2\pi f t)$ ,  $1 \le f \le 1000$  MHz.

Following this setup, several simulations were performed. The results are analyzed in the following sections.

### A. Performance of the Estimators for Mismatch Errors

First, a TI ADC array with 5% gain and offset errors and a timing mismatch of 10% was simulated in MATLAB for a sinusoidal input signal of 730 MHz and a total sampling frequency of 2.08 GHz. Table II shows the offset, gain, and timing shifts for each ADC (randomly generated with normal distribution), along with the corresponding estimations using the method described in Section III. As can be observed in Table II, the estimated parameters are very close to the real values.

As an example, we show in Fig. 6 the convergence of the estimated offset mismatch as a function of the number of samples using both our estimator and the commonly used averaging method.

# B. Analysis of Performance in Timing Mismatch Compensation for Several Interpolation Methods

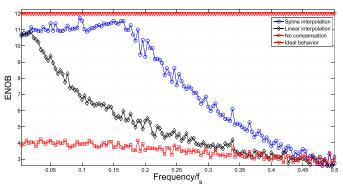

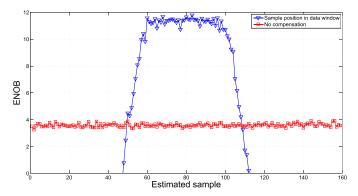

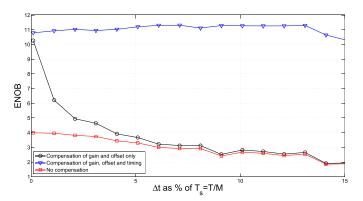

Fig. 7 shows the ENOB at the output of a TI ADC array when compensating for the timing mismatch error with either

Fig. 7. Timing mismatch compensation by linear interpolation and interpolation by cubic splines. Red lines: ideal behavior and uncompensated TI ADC with mismatch errors.

linear interpolation (black line) or cubic spline interpolation (blue line). In this case, a 12-bit resolution ADC is assumed with a 5% mismatch in gain, offset, and sampling time. The ENOB of the TI ADC prior to any compensation is also shown (red line). As illustrated in Fig. 7, a 5% dispersion in the parameters causes the effective resolution to fall from 12 to about 4 bits, and therefore there is no doubt that their effect must be compensated for.

It can also be observed that linear interpolation is able to correct only timing mismatch errors when the frequency of the input signal is very low. This condition means that an important oversampling is required. On the other hand, using spline interpolation improves the performance of the compensation in the sense that a wider bandwidth is correctly compensated for, but an oversampling of about three is still needed. Therefore, that approximation is still insufficient.

In this paper, we propose the use of Lagrange polynomials for interpolation in order to overcome the problems of the two previously mentioned interpolators. We show that it is possible to obtain good compensation results while keeping the complexity low, thanks to the simplified implementation proposed in Section IV-D.

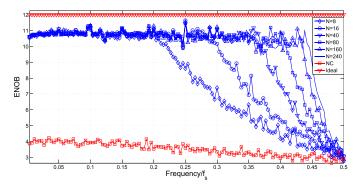

# C. Compensation Results Using the Proposed Simplified Lagrange Interpolator

Fig. 8 shows the ENOB before and after compensation with Lagrange interpolation filters of orders 8, 16, 40, 80, 160, and 240. It can be observed that the compensation strategy effectively reduces the distortion due to mismatch errors, achieving close to ideal behavior. Also, a higher compensation

Fig. 8. Timing mismatch compensation by Lagrange interpolation for different polynomial orders (8, 16, 40, 80, 160, and 240). Red lines: ideal behavior (top) and uncompensated TI ADC with mismatch errors (bottom).

Fig. 9. Timing mismatch compensation by Lagrange interpolation for different sample positions during estimation N=80. Red line: uncompensated TI ADC with mismatch errors.

bandwidth is obtained when using higher order Lagrange interpolation filters. For example, when using a filter of order 160, about only 12% of oversampling is needed to obtain an ENOB higher than 10 in the signal frequency band.

Recalling the previous discussion about the best approximation zone for the Lagrange polynomial given N data samples in Section IV-C, we simulated the ENOB obtained at the output of the compensator for a filter of order 160 as a function of the sample position within the data window during estimation. The results are shown in Fig. 9. As discussed, the best result is obtained around  $t_{N/2}$ , in this case 80.

# D. Spectral Purity After Compensation: Comparison With Other Methods

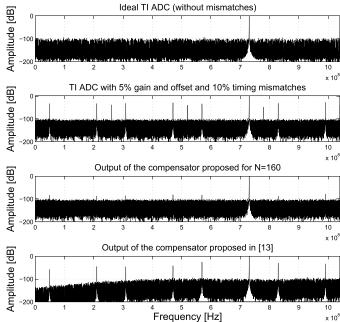

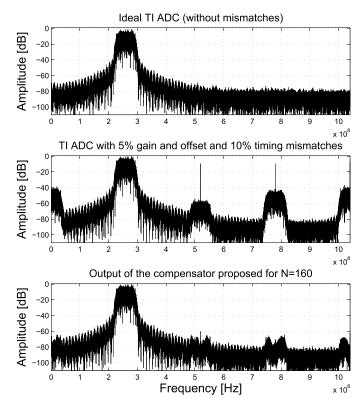

Fig. 10 shows the spectrum of an ideal TI ADC (top), the simulated TI ADC with 5% gain and offset mismatch errors and 10% timing mismatch, the output of the compensator proposed for N=160, and the output of the compensator proposed in [13]. It can be observed that the distortion is successfully canceled through compensation by our proposal, thus not only enhancing the ENOB but also improving the SFDR for about 50 dB. On the other hand, it can also be observed that the method proposed in this paper outperforms by far that of the method described in [13].

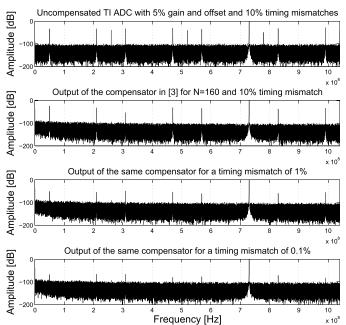

The performance of the Lagrange interpolator proposed in [3], which is an FIR approximation of what we propose

Fig. 10. Output spectrum of an ideal ADC and an uncompensated TI ADC with 5% gain and offset and 10% timing mismatches, the output of the compensator proposed for N=160, and the output of the compensator proposed in [13].

Fig. 11. Output spectrum of an uncompensated TI ADC with 5% gain and offset and 10% timing mismatches and the output of the compensator proposed in [3] for N = 160 and 10%, 1%, and 0.1% timing mismatches.

here, was evaluated as a function of the amount of timing mismatch. The results are shown in Fig. 11. The top plot of Fig. 11 is the output of an uncompensated TI ADC with 5% gain and offset mismatches with 10% timing mismatch. The three remaining plots are the spectra at the output of the compensator for 10%, 1%, and 0.1% of timing mismatch, respectively. As discussed earlier, it can be observed that this

Fig. 12. Output spectrum of an ideal TI ADC and an uncompensated TI ADC with 5% gain and offset and 10% timing mismatches and the output of the compensator proposed for N=160 with 5% gain and offset and 10% timing mismatches.

Fig. 13. ENOB as a function of  $\Delta t$  variation before compensation, after compensating only for gain and offset mismatches, and compensating for gain, offset, and timing. Here, N=160 in the Lagrange interpolation filter.

approximation is able to cancel the distortion as long as the timing mismatch is low enough.

Fig. 12 shows the compensation performance of the proposed method under the same mismatch conditions when using a more realistic input signal for validation. The signal used is a randomly generated binary sequence passed through a raised cosine filter and is Quadrature Amplitude Modulation modulated. It is shown that the spectral purity of the compensated signal is also maintained in this case.

### E. Robustness Tests

An additional simulation is presented in order to show the robustness of the method to changes in the size of timing mismatch. The results are shown in Fig. 13, where a random

Fig. 14. ENOB as a function of the ADC resolution before (dashed line) and after compensation (solid line) for 5% gain and offset mismatches and 10% timing mismatch.

gain and offset mismatch with a maximum value of 5% was added to each channel, while the amount of timing mismatch varies from 0.1% to 15% of the total sampling period  $T_s$ . As shown in Fig. 13, the ENOB enhancement is almost constant independently of the amount of timing mismatch even for a high-frequency input signal.

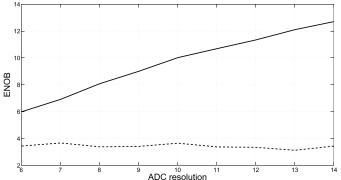

Finally, we show in Fig. 14 the compensation performance as a function of the ADC resolution for a TI ADC with 5% gain and offset mismatches and timing mismatch within 10%, using an interpolator of order 160. It can be observed that the compensated ADC achieves an ENOB close to the ideal ADC resolution in all cases, although the resolution enhancement is a little lower when the ADC resolution is higher than 10 bits. However, an important improvement is observed even in such conditions.

Some possibilities to improve the performance of the proposed method are to increase the number of analyzed samples, to use a more accurate estimated training signal than that achieved by the method proposed in [24], or to use a more accurate interpolation method, possibly at the cost of an increased computational complexity.

### F. Validation With Experimental Data

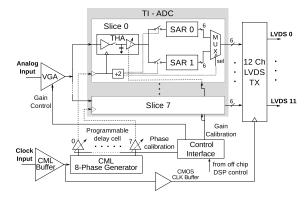

The experimental results presented in this section are based on the sampled data of a 6-bit 2-GS/s TI *successive approximation register* (SAR) ADC. This converter test chip is detailed in [28], and it has been designed to be used as a test platform to evaluate mixed-signal calibration algorithms like [29]. However, it can also be used to test digital calibration techniques as in this case.

The core of the chip is a hierarchical TI ADC (see Fig. 15). It includes eight parallel channels (slices) where each channel consists of one Track and Hold Amplifier (THA) and two subinterleaved SAR ADCs. Each THA is managed by a clock signal at frequency  $F_{\rm slice} = F_s/8 = 2 \text{ GHz/8} = 250 \text{ MHz}$ . The THA and SARs are synchronized by a clock divider that generates two clock signals from THA clock with 25% duty cycle at  $F_{\rm SAR} = F_{\rm slice}/2 = 125 \text{ MHz}$ . After quantization, the two SAR outputs are multiplexed to provide a single 6-bit output bus at  $F_{\rm slice}$  rate. The eight THA clock phases are provided by a multiple-phase clock generator. Finally, the digital TI ADC outputs (8 channels × 6 bits) are sent to a high-speed

Fig. 15. TI ADC chip architecture.

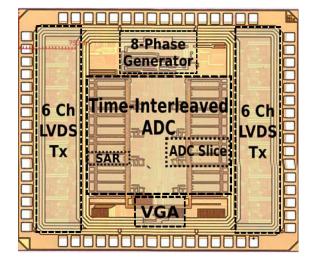

Fig. 16. Chip die photo. Die size:  $3 \text{ mm} \times 3.5 \text{ mm}$ .

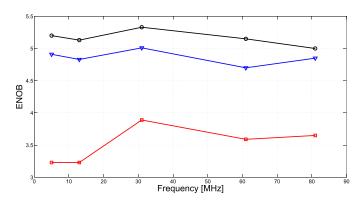

Fig. 17. ENOB as a function of frequency before (squares) and after (triangles) compensation for the TI ADC. The line with circles shows the maximum ENOB of a single-channel ADC.

transmitter interface. Note that in this design, the full data rate (12 Gbits/s) without decimation is sent off-chip.

The ADC fabricated in a  $0.13-\mu m$  CMOS process achieves 33.9 dB of signal-to-noise-and-distortion ratio and 192 mW of power consumption at 1.2 V. Fig. 16 shows the chip die micrograph.

Fig. 17 shows the ENOB of the TI ADC output before and after compensation and the maximum ENOB of a singlechannel ADC for a set of measured frequencies, where the effectiveness of the method can be observed. In this case, an increment of about 2 bits in the ENOB is achieved, showing good agreement with the simulation results.

#### VI. CONCLUSION

A novel method for efficient estimation and correction of mismatch errors in TI ADCs has been presented. The estimation of mismatch errors is efficient, accurate, and effective while keeping the complexity of the algorithm low. The compensation strategy uses the estimated parameters for a simple offset and gain mismatch error correction and implements a low-complexity Lagrange interpolation filter to correct errors due to timing mismatch. The simulation results show that the proposed compensation strategy achieves an almost ideal behavior over a wide bandwidth. In addition, the compensator effectively cancels the distortion even in the presence of large mismatches.

#### REFERENCES

- R. J. van de Plassche, CMOS Integrated Analog-to-Digital and Digital-to-Analog Converters. Dordrecht, The Netherlands: Kluwer, 2003

- [2] S. Ponnuru, M. Seo, U. Madhow, and M. Rodwell, "Joint mismatch and channel compensation for high-speed OFDM receivers with time-interleaved ADCs," *IEEE Trans. Commun.*, vol. 58, no. 8, pp. 2391–2401, Aug. 2010.

- [3] Y. X. Zou, S. L. Zhang, Y. C. Lim, and X. Chen, "Timing mismatch compensation in time-interleaved ADCs based on multichannel Lagrange polynomial interpolation," *IEEE Trans. Instrum. Meas.*, vol. 60, no. 4, pp. 1123–1131, Apr. 2011.

- [4] J. Goodman, B. Miller, M. Herman, G. Raz, and J. Jackson, "Polyphase nonlinear equalization of time-interleaved analog-to-digital converters," *IEEE J. Sel. Topics Signal Process.*, vol. 3, no. 3, pp. 362–373, Jun. 2009.

- [5] D. Marelli, K. Mahata, and M. Fu, "Linear LMS compensation for timing mismatch in time-interleaved ADCs," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 56, no. 11, pp. 2476–2486, Nov. 2009.

- [6] J. Elbornsson, F. Gustafsson, and J.-E. Eklund, "Blind equalization of time errors in a time-interleaved ADC system," *IEEE Trans. Signal Process.*, vol. 53, no. 4, pp. 1413–1424, Apr. 2005.

- [7] J. M. D. Pereira, P. M. B. S. Girão, and A. M. C. Serra, "An FFT-based method to evaluate and compensate gain and offset errors of interleaved ADC systems," *IEEE Trans. Instrum. Meas.*, vol. 53, no. 2, pp. 423–430, Apr. 2004.

- [8] Y. X. Zou and X. J. Xu, "Blind timing skew estimation using source spectrum sparsity in time-interleaved ADCs," *IEEE Trans. Instrum. Meas.*, vol. 61, no. 9, pp. 2401–2412, Sep. 2012.

- [9] F. Centurelli, P. Monsurrò, and A. Trifiletti, "Efficient digital background calibration of time-interleaved pipeline analog-to-digital converters," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 59, no. 7, pp. 1373–1383, Jul. 2012.

- [10] S. Maymon and A. V. Oppenheim, "Quantization and compensation in sampled interleaved multichannel systems," *IEEE Trans. Signal Process.*, vol. 60, no. 1, pp. 129–138, Jan. 2012.

- [11] W. Liu and Y. Chiu, "Time-interleaved analog-to-digital conversion with online adaptive equalization," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 59, no. 7, pp. 1384–1395, Jul. 2012.

- [12] C. Vogel and H. Johansson, "Time-interleaved analog-to-digital converters: Status and future directions," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2006, pp. 3385–3389.

- [13] M. Seo, M. J. W. Rodwell, and U. Madhow, "Comprehensive digital correction of mismatch errors for a 400-Msamples/s 80-dB SFDR timeinterleaved analog-to-digital converter," *IEEE Trans. Microw. Theory Techn.*, vol. 53, no. 3, pp. 1072–1082, Mar. 2005.

- [14] C. Vogel, M. Hotz, S. Saleem, K. Hausmair, and M. Soudan, "A review on low-complexity structures and algorithms for the correction of mismatch errors in time-interleaved ADCs," in *Proc. IEEE 10th Int. New Circuits Syst. Conf. (NEWCAS)*, Jun. 2012, pp. 349–352.

- [15] V. Ferragina, A. Fornasari, U. Gatti, P. Malcovati, and F. Maloberti, "Gain and offset mismatch calibration in time-interleaved multipath A/D sigma-delta modulators," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 51, no. 12, pp. 2365–2373, Dec. 2004.

- [16] B. Razavi, "Design considerations for interleaved ADCs," IEEE J. Solid-State Circuits, vol. 48, no. 8, pp. 1806–1817, Aug. 2013.

- [17] H. Kopmann, "Comprehensive model-based error analysis of multiple concurrent, time-interleaved, and hybrid ultra-wideband analogue-todigital conversion," Signal Process., vol. 84, pp. 1837–1859, Oct. 2004.

- [18] S. Lou and G. Bi, "Aliased polyphase sampling," Signal Process., vol. 90, pp. 1323–1326, Apr. 2010.

- [19] K. M. Tsui and S. C. Chan, "New iterative framework for frequency response mismatch correction in time-interleaved ADCs: Design and performance analysis," *IEEE Trans. Instrum. Meas.*, vol. 60, no. 12, pp. 3792–3805, Dec. 2011.

- [20] T. I. Laakso, V. Valimaki, M. Karjalainen, and U. K. Laine, "Splitting the unit delay [FIR/all pass filters design]," *IEEE Signal Process. Mag.*, vol. 13, no. 1, pp. 30–60, Jan. 1996.

- [21] S. K. Sindhi and K. M. M. Prabhu, "Reconstruction of N-th order nonuniformly sampled bandlimited signals using digital filter banks," *Digit. Signal Process.*, vol. 23, no. 6, pp. 1877–1886, Dec. 2013.

- [22] S. O. Haykin, Adaptive Filter Theory. Englewood Cliffs, NJ, USA: Prentice-Hall, 1996.

- [23] V. Harish, P. Sommen, and K. M. M. Prabhu, "Perfect reconstruction of uniform samples from *K*-th order nonuniform samples," *Signal Process.*, vol. 91, pp. 2677–2684, Nov. 2011.

- [24] C. A. Schmidt, O. Lifschitz, J. E. Cousseau, J. L. Figueroa, and P. Julián, "Methodology and measurement setup for analog-to-digital converter postcompensation," *IEEE Trans. Instrum. Meas.*, vol. 63, no. 3, pp. 658–666, Mar. 2014.

- [25] IEEE Standard for Terminology and Test Methods for Analog-to-Digital Converters, IEEE Standard 1241-2010, Jan. 2011, pp. 1–139.

- [26] M. Unser, "Splines: A perfect fit for signal and image processing," *IEEE Signal Process. Mag.*, vol. 16, no. 6, pp. 22–38, Nov. 1999.

- [27] S. A. Dyer and J. S. Dyer, "Cubic-spline interpolation: Part 1," *IEEE Instrum. Meas. Mag.*, vol. 4, no. 1, pp. 44–46, Mar. 2001.

- [28] B. T. Reyes et al., "A 6-bit 2GS/s CMOS time-interleaved ADC for analysis of mixed-signal calibration techniques," in Proc. IEEE 5th Latin Amer. Symp. Circuits Syst. (LASCAS), Feb. 2014, pp. 1–4.

- [29] B. T. Reyes, V. Gopinathan, P. S. Mandolesi, and M. R. Hueda, "Joint sampling-time error and channel skew calibration of time-interleaved ADC in multichannel fiber optic receivers," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 2012, pp. 2981–2984.

**Christian A. Schmidt** received the B.Sc. degree in electronics engineering and the Ph.D. degree in engineering from the Universidad Nacional del Sur, Bahía Blanca, Argentina, in 2005 and 2012, respectively.

His current research interests include nonlinear dynamic systems modeling and post-processing techniques for distortion reduction in analog-to-digital-converters.

**Juan E. Cousseau** (M'94–SM'00) received the B.Sc. degree from the Universidad Nacional del Sur (UNS), Bahía Blanca, Argentina, in 1983, and the M.Sc. and Ph.D. degrees from the COPPE/Universidade Federal do Rio de Janeiro, Rio de Janeiro, Brazil, in 1989 and 1993, respectively, all in electrical engineering.

He was a Visiting Professor with the University of California at Irvine, Irvine, CA, USA, in 1999, and the Signal Processing Laboratory, Helsinki University of Technology, Espoo, Finland,

in 2004 and 2006. He has been with the Undergraduate Program, Department of Electrical and Computer Engineering, UNS, since 1984, where he has also been with the Graduate Program since 1994. He has been involved in scientific and industry projects with research groups from Argentina, Brazil, Spain, and USA. He is currently a Senior Researcher of the National Scientific and Technical Research Council of Argentina. He is a Coordinator of the Signal Processing and Communication Laboratory with UNS.

Dr. Cousseau was the IEEE Circuits and Systems Chair of the Argentine Chapter from 1997 to 2000, and a member of the Executive Committee of the IEEE Circuits and Systems Society in 2000/2001 (Vice President for Region 9). He participated in the IEEE Signal Processing Society Distinguished Lecturer Program 2007.

**José L. Figueroa** (M'98–SM'01) received the B.Sc. degree in electrical engineering and the Ph.D. degree in systems control from the Universidad Nacional del Sur, Bahía Blanca, Argentina, in 1987 and 1991, respectively.

He has been with the Universidad Nacional del Sur and the National Scientific and Technical Research Council of Argentina since 1995. His current research interests include control systems and signal processing.

Benjamin T. Reyes received the Degree in electronics engineering from Universidad Tecnologica Nacional at Córdoba, Córdoba, Argentina, in 2008. In 2015, he received the Ph.d. degree in engineering at Universidad Nacional del Sur, Bahía Blanca, Argentina.

He was with ClariPhy Argentina S.A., Córdoba, in 2009, where he was involved in the design of mixed-signal circuits and analog high-speed circuits. He is currently a member of the Research Staff with the Digital Communications Laboratory,

Universidad Nacional de Cordoba, Córdoba. His current research interests include high-speed mixed signal circuits, analog-front-end design for digital communications, and digital-assisted analog design.

Mario R. Hueda was born in Jujuy, Argentina, in 1967. He received the Electrical and Electronic Engineering and Ph.D. degrees from the Universidad Nacional de Cordoba, Córdoba, Argentina, in 1994 and 2002, respectively.

He was a Visiting Scholar with Lucent Technologies–Bell Labs, Murray Hill, NJ, USA, in 1996, where he was involved in CDMA receivers. Since 1997, he has been with the Digital Communications Research Laboratory, Department of Electronic Engineering, Universidad Nacional

de Cordoba. He is currently with the National Scientific and Technological Research Council. He holds six patents issued or pending, and has authored over 50 technical papers in journals and conferences. His current research interests include digital communications and performance analysis of communication systems.

Dr. Hueda received a fellowship from the Scientific and Technological Research Council of Cordoba to carry out research and development in the area of voiceband data transmission from 1994 to 1996.