#### **Aalborg Universitet**

#### Specification and Test of Real-Time Systems

Nielsen, Brian

Publication date: 2000

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Nielsen, B. (2000). Specification and Test of Real-Time Systems. Allborg Universitetsforlag. Publication: Department of Computer Science, The Faculty of Engineering and Science, Aalborg University No. 12

#### General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- ? Users may download and print one copy of any publication from the public portal for the purpose of private study or research. ? You may not further distribute the material or use it for any profit-making activity or commercial gain ? You may freely distribute the URL identifying the publication in the public portal ?

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# AALBORG UNIVERSITY DEPARTMENT OF COMPUTER SCIENCE

Fredrik Bajers Vej 7E, 9220 Aalborg Øst, Denmark

### Specification and Test of Real-Time Systems

PhD thesis

by

Brian Nielsen

Supervisor: Arne Skou

April 2000

COPYING PARTS OF THIS REPORT IS NOT PERMITTED WITHOUT WRITTEN PERMISSION FROM THE AUTHOR

#### **Abstract**

Distributed real-time computer based systems are very complex and intrinsically difficult to specify and implement correctly; in part this is caused by the overwhelming number of possible interactions between system components, but especially by a lack of adequate methods and tools to deal with this complexity. This thesis proposes new specification and testing techniques.

We propose a real-time specification language which facilitates modular specification and programming of reusable components. A specification consists of a set of concurrent untimed components which describes the functional behavior of the system, and a set of constraint patterns which describes and enforces the timing and synchronization constraints among components.

We propose new techniques for automated black box conformance testing of real-time systems against densely timed specifications. A test generator tool examines a specification of the desired system behavior and generates the necessary test cases. A main problem is to construct a reasonably small test suite that can be executed within allotted resources, while having a high likelihood of detecting unknown errors. Our goal has been to treat the time dimension of this problem thoroughly.

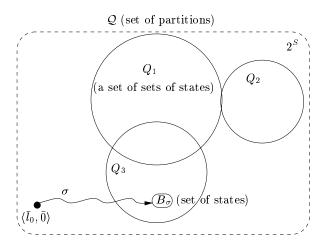

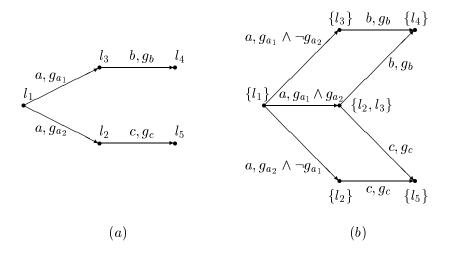

Based on a determinizable class of timed automata, Event Recording Automata, we show how to systematically and automatically generate tests in accordance with Hennessy's classical testing theory lifted to include timed traces. We select test cases from a coarse grained state space partitioning of the specification, and cover each partition with at least one test case, possibly selecting extreme clock values. In a partition, the system behavior remains the same independently of the actual clock values.

We employ the efficient symbolic constraint solving techniques originally developed for model checking of real-time systems to compute the reachable parts of these equivalence classes, to synthesize the timed tests, and to guarantee a coverage of the equivalence class partitioning. We have implemented our techniques in the RTCAT test case generation tool.

Through a series of examples we demonstrate how Event Recording Automata can specify untrivial and practically relevant timing behavior. Despite being theoretically less expressive than timed automata, it has proven sufficiently expressive for our examples, but sometimes causing minor inconveniences. Applying RTCAT to generate tests from these specifications, including the Philips Audio Protocol, resulted in encouragingly small test suites.

We conclude that our approach is feasible and deserves further work, but also that it should be generalized and allow timing uncertainty and modeling of the environment. Some implementation improvements are also necessary.

#### Dansk Resumé

Distribuerede tidstro computer baserede systemer er notorisk komplekse og svære at udvikle korrekt. En væsentlig årsag hertil er den enorme og uoverskuelige mænge af mulige interaktioner imellem samtidige komponenter. Der mangler metoder og værktøjer til håndtering af denne kompleksitet. Denne afhandling foreslår nye teknikker til specifikation og test af tidstro systemer.

Det første bidrag er et specifikationssprog, der forbedrer mulighederne for at konstruere genbrugelige specifikationer og programkomponenter. En sådan specifikation består af et antal samtidige komponenter, som beskriver systemets logiske adfærd, og en mængde restriktorer, der gennemtvinger de tidsog synkroniseringskrav, der skal holde imellem komponenterne.

Afhandlingens hovedbidrag er nye teknikker til automatiseret konformitetstest med fokus på test af tidskrav. Et test genereringsværktøj analyserer en given tidsautomat specifikation af den ønskede systemadfærd og genererer automatisk de nødvendige tests. Et væsentligt problem er at generere en passende mængde af tests, der kan udføres inden for de ressourcer, der er afsat til aftestning, men som har stor sandsynlighed for at detektere ukendte fejl.

Afhandlingen viser, hvorledes det er muligt automatisk og systematisk at generere tests fra en determinisérbar klasse af tidsautomater kaldet Event Recording Automata. Testene er udledt fra Hennessy's klassiske testteori, som er udvidet til at omfatte tid. Udvælgelse af tests sker på baggrund af en grovkornet inddeling af specifikationens tilstandsrum. Specifikationens adfærd i hver del er identisk uanset specifikke urværdier. Hver del af tilstandsrummet dækkes med mindst en test, og potentielt ved valg af ekstreme urværdier.

Til beregning af specifikationens opnåelige tilstande og til udledning af tests anvendes nye effektive teknikker til symbolsk løsning og repræssentation af de lineære uligheder over urene, som forekommer i specifikationen. Disse teknikker er oprindligt udviklet til formel bevisførelse af tidstro systemer vha. modelchecking. Teknikkerne er implementeret i testgenereringsværktøjet RTCAT.

Ved specifikation af en række eksempler har det vist sig, at Event Recording Automata er egnede til specifikation af utrivielle og praktisk relevante tidskrav. Selv om udtrykskraften af denne automat model teoretisk set er mindre end generelle tidsautomater, har den været tilstrækkelig, dog sommetider med visse komplikationer. Mængden af tests generereret af RTCAT værktøjet for disse specifikationer, inklusive en Philips Audio Protokol, er kun moderat stor, hvilket er lovende for anvendeligheden af teknikkerne på større systemer.

Det konkluderes, at de foreslåede teknikker er potentielt anvendelige og bør videreudvikles. De bør genereraliseres og muliggøre specifikation af tidsusikkerhed og omgivelsesantagelser. Visse implementationsaspekter bør forbedres.

#### Acknowledgments

"One does not discover new lands without consenting to lose sight of the shore for a very long time." (André Gide)

Doing a PhD is not only searching for new technical discoveries, but also a personal, and sometimes an alone, endeavor. But without the support of a number of people, I would most likely still be paddling in open seas with no shore lines in sight. First and foremost, I owe a lot of gratitude to my supervisor, Arne Skou, for making this project possible, and for continuously supporting and guiding me through the years (all of them).

I'm also grateful to all my colleagues in the Distributed Systems and Semantics research unit at Aalborg University for making this an agreeable place to work. Special thanks to Mikkel Christiansen, Peter K. Jensen, Kåre Kristoffersen, Paul Pettersson, Anders P. Ravn, and my office mate on more than one occasion, Yogi, for their comments and time for discussions.

My year long stay at the Open Systems Laboratory at University of Illinois in 1995 is still a recurring theme in my dreams. It has been more than a stay abroad, but an experience for life. I'm grateful to Gul Agha for hosting me, and for supervising me during this time. Special thanks to Mark Astley, Shangping Ren, Masahiko Saito, and Dan Sturman, for their friendships on and off work.

Also thanks to Jan Peleska and the members of the Distributed Systems and Operating Systems group at the University of Bremen for hosting me from November 1999 to January 2000. This gave me valuable insight into their approach to testing, and moreover, the quiescence I needed to finish the writing of this thesis.

Financial support was provided by the Danish Technical Research Foundation (STVF) and the Danish Research Academy.

Last, but not least, thanks to my family and friends for accepting my long periods of mental and physical absence.

# Contents

| Ĺ | Intr | oducti | ion                                | 1  |

|---|------|--------|------------------------------------|----|

|   | 1.1  | Distri | buted Real-Time Systems            | 2  |

|   | 1.2  | Testin | g                                  | 4  |

|   |      | 1.2.1  | Testing in Context                 | 4  |

|   |      | 1.2.2  | Automated Testing                  | 5  |

|   |      | 1.2.3  | Test Selection                     | 7  |

|   |      | 1.2.4  | Testing and Verification           | 8  |

|   | 1.3  | The T  | hesis                              | 10 |

|   |      | 1.3.1  | Specification of Real-Time Systems | 10 |

|   |      | 1.3.2  | Testing of Real-Time Systems       | 11 |

|   |      | 1.3.3  | Contributions                      | 13 |

|   |      | 1.3.4  | Structure of the Thesis            | 13 |

x CONTENTS

| 2 | Unt | imed ' | Testing                                        | 15 |

|---|-----|--------|------------------------------------------------|----|

|   | 2.1 | Specif | fication of Concurrent Systems                 | 16 |

|   |     | 2.1.1  | Communicating State Machines                   | 16 |

|   |     | 2.1.2  | Labeled Transition Systems                     | 18 |

|   |     | 2.1.3  | Semantics of Communicating State Machines      | 20 |

|   | 2.2 | Testin | g Theory for Non-deterministic Systems         | 22 |

|   |     | 2.2.1  | Goals and Assumptions                          | 22 |

|   |     | 2.2.2  | Tests and Test Execution                       | 24 |

|   |     | 2.2.3  | Implementation Relations                       | 25 |

|   |     | 2.2.4  | Interpretation of Implementation Relations     | 28 |

|   |     | 2.2.5  | Test Languages                                 | 31 |

|   | 2.3 | Test ( | Generation                                     | 34 |

|   |     | 2.3.1  | Relevant Hennessy Testers                      | 34 |

|   |     | 2.3.2  | A Direct Test Generation Algorithm             | 34 |

|   |     | 2.3.3  | Success Graphs                                 | 38 |

|   |     | 2.3.4  | Test Selection and Coverage                    | 41 |

|   | 2.4 | A Tes  | t Generation Tool: TestGen                     | 42 |

|   |     | 2.4.1  | Tool Features                                  | 42 |

|   |     | 2.4.2  | Construction of the Success Graph              | 43 |

|   |     | 2.4.3  | Divergency Check                               | 46 |

|   |     | 2.4.4  | Construction of Must Sets                      | 46 |

|   |     | 2.4.5  | Example: Peterson's Mutual Exclusion Algorithm | 47 |

|   |     | 2.4.6  | Example: The Alternating Bit Protocol          | 48 |

|   |     | 2.4.7  | Size Matters                                   | 51 |

|   | 2.5 | Summ   | nary                                           | 54 |

CONTENTS xi

| 3 | Tin | ied Tes | sting                                  | 57 |

|---|-----|---------|----------------------------------------|----|

|   | 3.1 | Timed   | Automata                               | 58 |

|   |     | 3.1.1   | Informal Description of Timed Automata | 58 |

|   |     | 3.1.2   | Dense Time Semantics of Timed Automata | 60 |

|   |     | 3.1.3   | Discrete versus Dense Time             | 64 |

|   | 3.2 | Timed   | Must Tests                             | 65 |

|   |     | 3.2.1   | Assumptions                            | 65 |

|   |     | 3.2.2   | The Implementation Relation            | 66 |

|   |     | 3.2.3   | Test Automata                          | 67 |

|   |     | 3.2.4   | Interpretation                         | 68 |

|   | 3.3 | Timed   | Test Generation                        | 70 |

|   | 3.4 | State I | Based Selection                        | 72 |

|   |     | 3.4.1   | State Space Partitioning               | 72 |

|   |     | 3.4.2   | Instantiations                         | 74 |

|   |     | 3.4.3   | Choice of Coverage Criterion           | 78 |

|   | 3.5 | Summ    | arv                                    | 79 |

xii CONTENTS

| 4 | Syn | nbolic                | Test Generation                                     | 81  |

|---|-----|-----------------------|-----------------------------------------------------|-----|

|   | 4.1 | Event                 | Recording Automata                                  | 82  |

|   |     | 4.1.1                 | Definition of Event Recording Automata              | 83  |

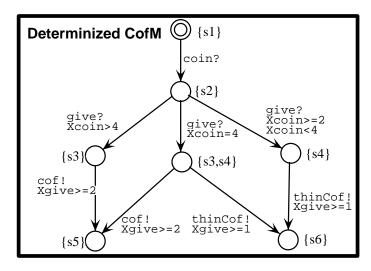

|   |     | 4.1.2                 | Determinization of Event Recording Automata         | 85  |

|   | 4.2 | Test (                | Generation from Event Recording Automata            | 86  |

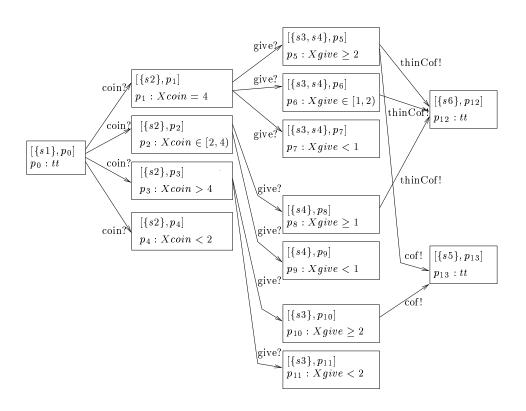

|   |     | 4.2.1                 | Overall Algorithm                                   | 86  |

|   |     | 4.2.2                 | State Partitioning                                  | 89  |

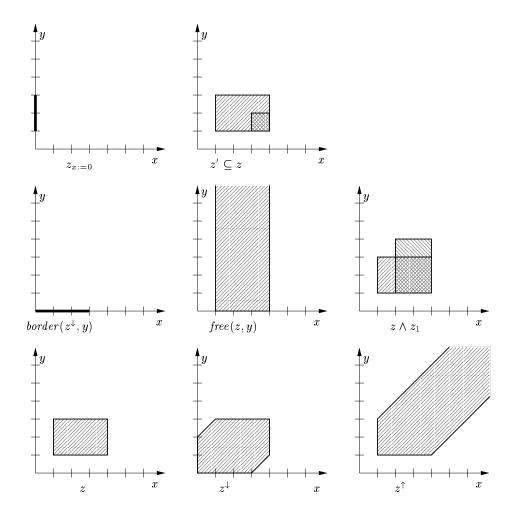

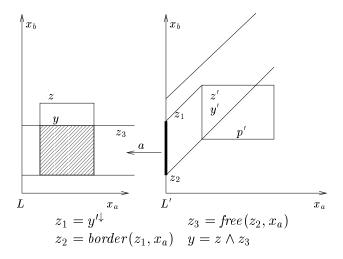

|   | 4.3 | $\operatorname{Symb}$ | olic Techniques                                     | 93  |

|   |     | 4.3.1                 | Zones                                               | 93  |

|   |     | 4.3.2                 | Difference Bound Matrixes                           | 95  |

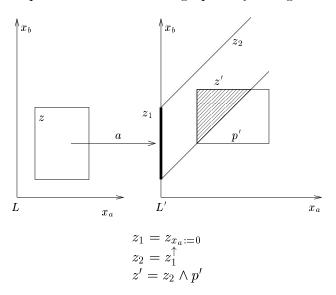

|   |     | 4.3.3                 | Forward Reachability                                | 96  |

|   |     | 4.3.4                 | Back Propagation of Constraints                     | 99  |

|   |     | 4.3.5                 | Timed Trace Computation                             | 100 |

|   |     | 4.3.6                 | Extreme Value Selection                             | 101 |

|   |     | 4.3.7                 | Symbolic Execution of Unrestricted Timed Automata . | 102 |

|   | 4.4 | Termi                 | nation                                              | 104 |

|   |     | 4.4.1                 | Termination of Forward Reachability                 | 104 |

|   |     | 4.4.2                 | Pragmatic Termination Criteria                      | 106 |

|   | 4.5 | Comp                  | osing Tests                                         | 107 |

|   |     | 4.5.1                 | Composition Algorithm                               | 107 |

|   |     | 4.5.2                 | Back Propagation in the Test Tree                   | 109 |

|   |     | 4.5.3                 | Mutation of Test Trees                              | 110 |

|   | 4.6 | Imple                 | mentation                                           | 111 |

|   |     | 4.6.1                 | Facilities                                          | 111 |

|   |     | 4.6.2                 | Tool Options                                        | 112 |

|   |     | 4.6.3                 | Implementation Remarks                              | 112 |

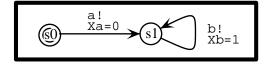

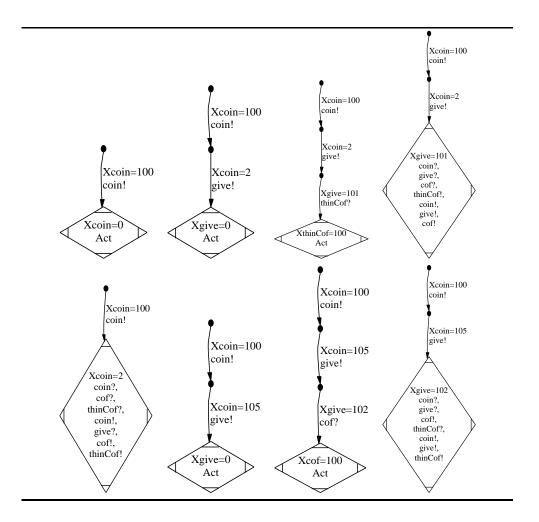

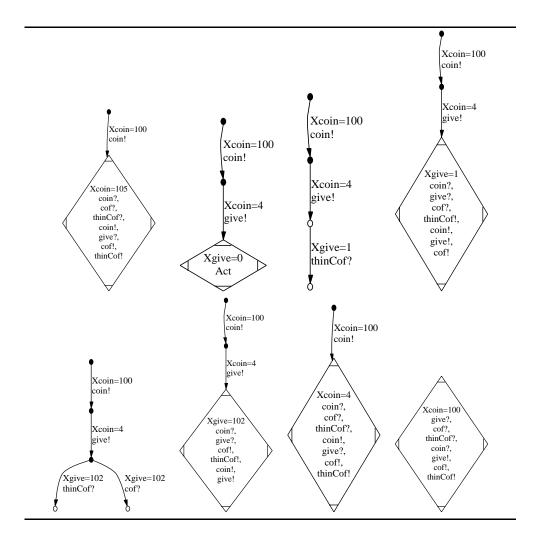

|   |     | 4.6.4                 | Example of Generated Test Cases                     | 115 |

|   | 4.7 | Summ                  | nary                                                | 117 |

CONTENTS xiii

| 5 | $\mathbf{E}\mathbf{v}\mathbf{a}$ | luatior | ı                                            | 119 |

|---|----------------------------------|---------|----------------------------------------------|-----|

|   | 5.1                              | Event   | Recording Automata Specifications            | 119 |

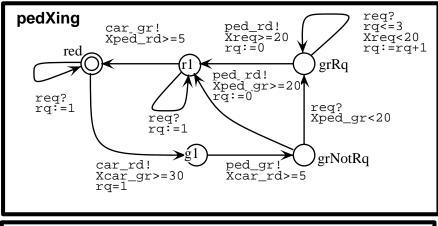

|   |                                  | 5.1.1   | Pedestrian Crossing                          | 120 |

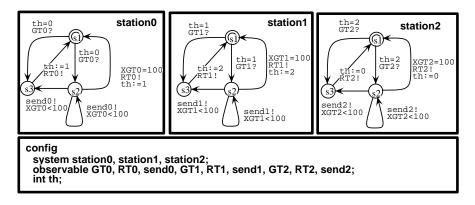

|   |                                  | 5.1.2   | Token Passing Protocol                       | 121 |

|   |                                  | 5.1.3   | Philips Audio Protocol                       | 122 |

|   | 5.2                              | Numb    | er of Generated Tests                        | 128 |

|   |                                  | 5.2.1   | Composition and Construction Order           | 128 |

|   |                                  | 5.2.2   | Scalability                                  | 130 |

|   | 5.3                              | Testin  | g Setup                                      | 133 |

|   |                                  | 5.3.1   | Event Recording Automata                     | 133 |

|   |                                  | 5.3.2   | Test Language                                | 137 |

|   |                                  | 5.3.3   | Environment modeling                         | 138 |

|   |                                  | 5.3.4   | Test Selection                               | 139 |

|   | 5.4                              | Imple   | mentation                                    | 141 |

|   |                                  | 5.4.1   | Symbolic Reachability Techniques for Testing | 141 |

|   |                                  | 5.4.2   | Prototype Tool Implementation                | 142 |

|   |                                  | 5.4.3   | Verification Techniques and Testing          | 142 |

|   | 5.5                              | Summ    | ary                                          | 143 |

xiv CONTENTS

| 6 | $\mathbf{Rel}$ | ated W | Vork                                       |   | 145 |

|---|----------------|--------|--------------------------------------------|---|-----|

|   | 6.1            | Untim  | ned Testing                                | ٠ | 145 |

|   |                | 6.1.1  | Test Observations                          | ٠ | 145 |

|   |                | 6.1.2  | Approaches to Test Generation              | ٠ | 147 |

|   |                | 6.1.3  | Checking Experiments                       |   | 149 |

|   |                | 6.1.4  | Domain Based Selection                     |   | 152 |

|   | 6.2            | Timed  | l Testing                                  |   | 153 |

|   |                | 6.2.1  | Observations and Timed Preorders           |   | 153 |

|   |                | 6.2.2  | Checking Experiments for Real-time Systems | ٠ | 155 |

|   |                | 6.2.3  | Real-Time Testing                          |   | 157 |

|   |                | 6.2.4  | Algorithms                                 |   | 159 |

|   | 6.3            | Novelt | ties of Our Approach                       |   | 160 |

|   | 6.4            | Summ   | nary                                       |   | 161 |

| 7            | Con              | clusions and Future Work 1                  | L <b>63</b>  |  |  |

|--------------|------------------|---------------------------------------------|--------------|--|--|

| $\mathbf{A}$ | Tow              | ards Reusable Real-Time Objects             | l <b>7</b> 1 |  |  |

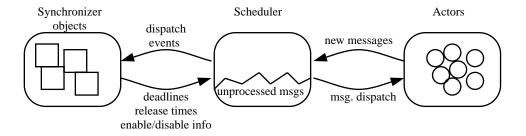

|              | A.1              | Motivation                                  | 172          |  |  |

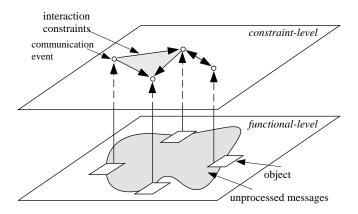

|              | A.2              | Separation and Reuse                        | 173          |  |  |

|              | A.3              | Specification of Interaction Constraints    | 175          |  |  |

|              |                  | A.3.1 Example 1: Steam Boiler Constraints   | 178          |  |  |

|              |                  | A.3.2 Example 2: New Boiler                 | 179          |  |  |

|              |                  | A.3.3 Example 3: Time Bounded Buffer        | 181          |  |  |

|              |                  | A.3.4 Example 4: Rate Control               | 182          |  |  |

|              | A.4              | Formal Definition                           | 183          |  |  |

|              |                  | A.4.1 Semantics of Actors                   | 183          |  |  |

|              |                  | A.4.2 RT-Synchronizers Semantics            | 186          |  |  |

|              |                  | A.4.3 Combining Actors and RT-Synchronizers | 188          |  |  |

|              | A.5              | Middleware Scheduling of RT-Synchronizers   | 190          |  |  |

|              | A.6              | Related Work                                | 196          |  |  |

|              | A.7              | Discussion                                  | 198          |  |  |

| Bi           | Bibliography 201 |                                             |              |  |  |

xvi CONTENTS

### Chapter 1

### Introduction

"The biggest problem at the moment is the timing between the electronics in the star camera that determines the satellite's orientation in space, and the satellite's main computer. This implies that the orientation of the satellite is not accurately known when it measures the magnetic field.

According to Lars Tøffner-Clausen from the Danish Meteorologic Institute, the time stamp on the data from the star camera occasionally leaps 1 second. Therefore, the recorded time of a measured datum may be up to 50 seconds wrong. So far, the technicians have been unable to locate the cause of the error in the satellite, and the hope is therefore that the error can be corrected by post processing the data on earth."

The above excerpt is translated from the Danish technical weekly "Ingeniøren" [86]. The news story concerns the Danish Ørsted satellite whose purpose is to make accurate and detailed measurements of the earth's magnetic field. Although the error is not fatal, it degrades the value of the satellite if not corrected.

Unfortunately, similar reports of malfunctioning computer based systems are rather commonly reported in the technical news.

Another, widely cited case, is the Therac-25 therapeutic radiation machine in which software malfunctions caused patients to be exposed to massive radiation overdoses resulting in deaths and injuries of several patients in the period of 1985–87 [69]. One kind of errors, among Therac-25's horribly many, is described by the Tylor incidents where unanticipated operator behavior led to wrong radiation type. Through a computer console the operator keyed in

the treatment parameters such as length, strength, and type of therapy (electron vs. x-ray radiation). The machine would then prepare for the treatment by changing its physical setup, including positioning of bending magnets that would take 8 seconds. The normal treatment was x-ray radiation, so when occasionally electron radiation was required, the operator sometimes routinely set it to x-rays. The Therac-25 user interface permitted editing of the treatment parameters while the machine was changing its setup. When the operator recognized his mistake and was fast enough to change the treatment parameters before this setup was completed, the machine would fail to recognize the change from x-ray radiation to the more benign electron radiation. When the operator later prompted the machine to start the treatment, it would emit a large x-ray dose despite the user interface indicating electrons. Lack of systematic testing and other poor software engineering practices is stated to be a major contribution to the faulty behavior of Therac-25 [69].

The problem with faulty computer systems is even bigger because newspapers only report on such spectacular cases.

### 1.1 Distributed Real-Time Systems

The Ørsted satellite is an example of a large class of computer based systems that are distributed and that must operate according to real-time constraints. Other examples are numerous: control and monitoring of factory plants, automatic train control systems, anti break/spin systems for cars, etc. A distributed system consists of multiple concurrent communicating components. It is well known that the communication protocols, which describe the exact rules for how the components can and should communicate, are very complex and intrinsically difficult to specify and implement correctly. One reason for this, as the Ørsted, Therac-25, and other cases illustrate, is that the possible interactions between system components internally, and between the system and its environment, is incomprehensible even for few and small systems. Also, the lack of global state and accurate global time caused by distribution of the components to several independent processors plays an important role. In addition, processors may fail independently, which adds a wealth of fault tolerance problems and opportunities.

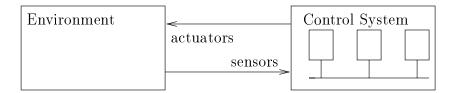

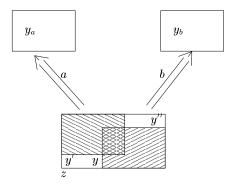

The components not only communicate internally, but also interact with external environment or human operators. The external environment consists of the physical equipment that is monitored and controlled by the computer system. The system can query the state of the environment through analogue sensors and analog-to-digital converters, and affect the equipment via actuators and digital-to-analogue converters. This model is depicted in Figure 1.1.

Figure 1.1. Model of a distributed real-time system.

The physical laws governing the environment induces a set real-time constraints which the control system must obey in order to achieve satisfactory or safe operation. Thus, a real-time system must not only produce the correct result or make the correct reaction to a stimuli, but must also produce the result or reaction at the correct time instant; neither too early nor too late. In other words, a timely reaction is just as important as the kind of reaction. These real-time requirements add a further layer of complexity to the already complex distributed systems. Their real-time properties must the specified, implemented, and validated.

Distributed real-time systems remain among the most challenging class of systems to develop correctly. The challenge arises in part from the inherent complexity in these systems, but in particular from the lack of adequate methods and tools to deal with this complexity. This applies to most development activities, including specification, design and implementation.

This thesis is concerned with the development of correct distributed real-time systems, in particular with their specification and test. We believe that the following items should be ingredients in a sound and effective systems development method:

- Methods should be rooted in formal methods. Formal methods not only support more stringent development, but, more importantly, permit development of sophisticated tools that can assist the developers in managing complex systems.

- Testing should be fully automatic. We propose fully automated testing from a formal specification as a way of improving correctness.

- Components should be reusable. New systems should to the widest possible extend be constructed by composing existing and previously tested components. This avoids unnecessary re-development and retesting.

Section 1.2 introduces testing, and Section 1.3 introduces our thesis.

#### 1.2 Testing

In the following we introduce testing, and discuss how it is presently being used, and why it needs to be improved. We also relate it to other validation strategies such as formal verification.

#### 1.2.1 Testing in Context

In essence, testing consists of executing a program or system with the intention of finding undiscovered errors in the system. As much as about a third of the total development time is spent on testing, and therefore constitutes a significant portion of the cost of the product. As discussed in the following, testing is performed throughout the product development cycle, and for various purposes.

Programmers usually test their own modules to check their correctness during development. Programmers also participate in the various integration tests also performed during the product development. Customers participate in the final acceptance test, where the goal is to determine whether the product satisfies the requirements listed in the original development contract negotiated between the customers and the software house.

Many companies employ dedicated test engineerers that exclusively focus on writing test cases and/or executing these. Some even use dedicated test departments that tests the products developed by another development department. The test departments may further be isolated (in clean rooms) from the developers in order to minimize 'contamination' of the test team by prejudices, presuppositions, and internal knowledge, that could biase tests.

Frequently, the products from different, and sometimes competing, companies must interoperate. To ensure this, standardization committees develop common standard specifications which must be adhered to by all vendors. A compliant product must pass a standard test suite also developed by the standardization committee. Typical examples of this are found in the found in the telecommunications world where standardization committees like ITU (International Telecommunication Union) and ISO (International Organization for Standardization) develop and manage communication protocol standards and corresponding standard test suites. For example, before a new mobile phone is mass produced, a sample must be sent to an accredited testing site that tests the product for protocol conformance and interoperability with the equipment used by mobile network providers.

Finally, safety critical systems must undergo extremely thorough testing, and the test results must convince public safety boards that the systems are sufficiently safe, e.g., the United States Federal Aviation Administration, FAA.

1.2. TESTING 5

Despite of the many man-hours and resources that are spent on testing, and despite the many errors found and corrected, significant errors remain. Because testing is the most dominating validation activity used by industry today, there is an urgent need for improving its effectiveness, both with respect to the use of time and resources, and the number of uncovered errors. A potential solution that is being examined by researchers is to formalize testing, and to provide tools that automates test case generation and execution. This approach has experienced some level of success: Formal specification and automatic test generation are being applied in practice [19, 72, 80, 98], and commercial test generations tools are emerging [59, 82]. However, little research deals systematically with the special needs of real-time systems.

#### 1.2.2 Automated Testing

The type of testing examined in this thesis is conformance testing. The goal is to check by means of testing whether the behavior of the implementation under test conforms to a specification. The implementation under test is viewed as a black box whose internal structure and behavior is unknown to the tester. In general, only its interface to the external world is known. Exactly when a implementation conforms to a specification is defined by a formal implementation relation. There are several possible definitions, and we shall return to these throughout the thesis.

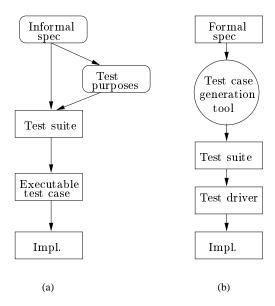

In conventional manual conformance testing the programmer or test engineer is responsible for constructing and executing test cases, see Figure 1.2.

He typically scrutinizes the specification given as informal prose, and identifies a set of test purposes. A test purpose is a specific goal or action deemed necessary to test. For example, in a communications protocol, a typical test purpose is to check that a connection can be established. In a steam boiler controller, a test purpose could be to check that the steam valve opens when the pressure in a water tank reaches a given threshold. For each test purpose, the test engineerer constructs at least one test that checks for that purpose. A collection of tests that concerns the same specification is called a test suite. The final step is to construct a program that implements the test, and to execute it.

In its simplest form, a test case is a sequence of input events, expected outputs, and a pass/fail verdict for each step of the sequence. The system passes a test if its execution reaches a state with a pass verdict. A test consists of three sub-sequences: A preamble brings the implementation to a state where the test purpose can be examined. Then follows the central sequence for the test purpose. A postamble brings the system to a known (or safe idle) state.

Figure 1.2. Manual testing (a), and fully automatic testing (b).

It is important to realize that the test engineerer is responsible for two critical steps: identifying what should be tested, and constructing the sequences. He performs two levels of test selection. One is identifying and selecting the test purposes to be tested. The other is the selection of the specific sequences needed for each purpose. It is not difficult to imagine that subtle scenarios are overlooked, or that the preamble contains errors or are too simple. Further, constructing test sequences is a time consuming and often tedious job.

Fully automatic testing is the extreme opposition to manual testing. The vision is to automatize testing completely, as illustrated by the schematics in Figure 1.2b. A test case generation tool takes as input a formal specification of the required behavior and systematically generates all relevant tests. Because exhaustive testing is impractical, it must select the most important ones for execution. A test execution tool takes the produced test cases as input, interprets them, and exercises the implementation under test accordingly and writes the test results to a log file. Additionally, the test execution tool may generate diagnostic information that can help the system developers in locating the cause of a detected discrepancy.

Between the completely manual testing and fully automatic testing approaches outlined above, there is plenty of room for various degrees of automatization and engineerer (expert user) intervention.

1.2. TESTING 7

#### 1.2.3 Test Selection

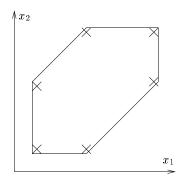

Even modest sized systems are so large that it is generally impossible to test them exhaustively, i.e., under all possible sequences of inputs. It is therefore necessary to select and execute only a subset of these. The goal of this procedure, known as test selection, is to find the 'best' test suite that can be executed within the allotted time frame and resources. A good test suite is usually one that has a high probability of finding so far unknown errors, or of finding the most serious errors. Rather than stimulating the system at random, it may prove better to systematically check as many truly different parts of the system as possible.

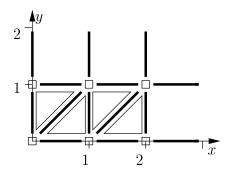

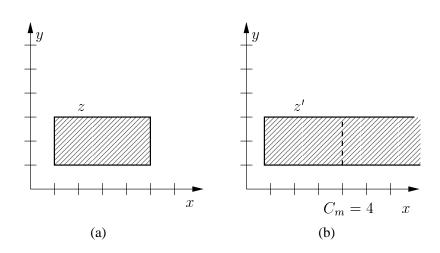

To make this point clear, consider the 'maxPositive' function specified and implemented in Figure 1.3. The function returns the maximum positive value of two arbitrary integers, x and y. If both arguments are less than zero the function is to return zero. Obviously, this function cannot be tested with all possible pairs of integers as inputs. A systematic strategy for dealing with this problem is to partition the input variables into input domains, i.e., sets of inputs that the program is expected to treat "identically" (e.g., pass through the same program path), and choose only a few representatives from each domain.

In the 'maxPositive' example there are four domains, one for each of the four cases in the specification. The resulting domains, tabulated in Table 1.4, are described as inequations of x and y. Test input data can be derived from the inequations that define each domain. Thus, at least four test cases should be generated, but usually several interior and extreme values are chosen.

| domain | condition                                   | expected output |

|--------|---------------------------------------------|-----------------|

| 1      | $x < 0 \land x > y$                         | 0               |

| 2      | $y < 0 \land x \le y$ $x \ge 0 \land x > y$ | 0               |

| 3      | $x \ge 0 \land x > y$                       | x               |

| 4      | $y \ge 0 \land x \le y$                     | y               |

**Table 1.4.** Domains for the maxPositive specification.

Returning our attention to real-time systems, it should be clear that the implementation cannot be stimulated at all possible time instances with all possible input actions. Thus, we are faced with a choice of when to stimulate the system. This choice need not be arbitrary, but can and should be made based on some notion of specification partitioning. This thesis will analyze the values of clocks in real-time specifications, and partition them, and use this as basis for time instance selection.

```

\max \text{Positive}(x,y) =_{\text{def}} \max(0, \max(x,y)) \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_{\text{def}} \begin{cases} x, & \text{if } x > y \\ y, & \text{otherwize} \end{cases} \\ \max =_

```

**Figure 1.3.** Specification of the maxPositive function (a), and C-program implementation (b)?

#### 1.2.4 Testing and Verification

A legitimate concern is whether testing will ever be an effective validation technique. It is well known that testing can only prove the presence of errors, not their absence. A proof would require exhaustive testing which is only possible for small systems, and under a particular set of assumptions. It therefore appears futile and irrational to exercise the system more or less at random. It would be much better to prove that the system behaves correct under all possible conditions!

This rationale has dominated the formal methods research community, and most researches focus on proving system correctness, i.e., on *verification*. The major benefit from this priority is that verification technology has matured significantly. Efficient algorithms and data structures have been developed to an extend that permits verification of systems of industrial relevance. One kind of verification technology is *model checking* where a (fully) automatic tool examines whether the states of a behavioral description of a system satisfies a given property. Another approach is *theorem proving* where a proof assistant tool helps the system developer to prove that the system has a given property.

The downside is that testing has been treated somewhat stepmotherly: It is viewed an academically unsound activity carried out by pragmatic people who are not true believers in formal methods. Testing technology has therefore been unable to keep up with the verification technology. Fortunately, many of the developed verification techniques also seem applicable to testing, as we shall try to demonstrate in this thesis.

1.2. TESTING 9

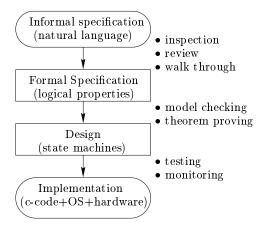

From the preceding discussion one might get the impression that one should decide on using either testing or verification as the prefered validation technique. However, in our view testing and verification are complementary techniques solving different problems. Therefore both should be used. The relation between different validation techniques and the (idealized) phases of software development is shown in Figure 1.5. Based on this observation we propose a development methodology where formal verification and testing are integral and complementary activities.

Figure 1.5. Testing and verification are complementary techniques (inspired by Rushby [95]).

The system analysts capture the informal requirements by interviewing customers, users, and domain experts about the requirements and expectations they have to the system. The formal requirements can then be formulated as logical properties or propositions. Completeness and soundness are achieved by reviews, inspections, and walk troughs.

The analysis and design activities result in an abstract model of the system to be implemented: its components, the behavior of these components, and their interaction. The central parts of the model can be specified in detail using a formal behavioral description language such as state machines or process algebra. Model checking can then be used to ensure that this formal model satisfies the desired properties.

Finally, the programmers take over and implement the design using a particular programming language, operating system, and hardware components. Automatic code generation from the formal model can be used in special cases. However, with the current state of the art, system construction is largely an informal step carried out by humans. Therefore, the final physical system may

be faulty even if its design is correct. It should also be mentioned here that many public safety boards require extensive testing of safety critical systems. It is insufficient, although important, to show that the design is correct: It must be demonstrated that the actual physical system is safe. However, the (verified) design or specification can now be used as a basis for generating test cases.

An interesting but open question is whether it ever will be possible to formalize and automatize the implementation process entirely such that implementations can be verified. This would require faithful formal models of the operating system and hardware components, formal semantics of programming languages, verified compilers, and translators from the design specification. At least, the resulting model will be so large that it cannot be verified with the technology available in the near future.

The fundamental goal of testing, which cannot be done by model checking, is to check if an actual running physical system of which we have incomplete knowledge conforms to a specification.

#### 1.3 The Thesis

Having presented the problem domain and motivated our work, this section introduces our contributions. We outline the main problems that should be solved, and present our approach to this. We summarize our contributions and present the structure of the remainder of the thesis.

#### 1.3.1 Specification of Real-Time Systems

The starting point for automatic testing of real-time system, and indeed for most automated tool support for their analysis, is a clear and unambiguous specification of the systems desired behavior. Such specifications tend to be complex and non-trivial to write. The particular specification language used, and the methodology used to derive specifications, is therefore of great importance. It should be possible to specify systems with a reasonable effort. Further, the generated tests or other analysis results will only be as good as the specifications on which they are based. Therefore, the correctness of these models is therefore also a concern.

Specification languages are presently given as somewhat low level and mathematically oriented formalisms such as state machines or automata specifications, or as lengthy process algebraic expressions. However, in the long run, as specifications grow in size and complexity, it becomes increasingly important

how to give and manage them. In particular we believe that making *modular* and *reusable* specifications becomes essential.

It is our thesis that reuse of specifications and implementations can be facilitated by a component based approach that separates specification of time constraints and functional behavior.

We propose a real-time specification and modeling language in which a specification consists of two parts. The first part is a set of concurrent *untimed components* describing the functional behavior of the system. The second part is a set of *constraint patterns* describing and enforcing the timing and synchronization constraints that should exist between components. Both components and constraint patterns are reusable. This enables key properties to be easily maintained in one system and re-established in future ones.

Another issue is how to derive the implementation from a specification. In some cases, it may be possible to execute a specification directly with little or no extra programming effort. We show how this sometimes is feasible from our modular specifications for soft real-time systems.

#### 1.3.2 Testing of Real-Time Systems

While a significant body of research exist on languages, theories, algorithms and tools for automatic testing of untimed systems, relatively little work deals explicitly with real-time systems. It is the aim of this thesis to develop techniques for automatically generating test cases for real-time systems.

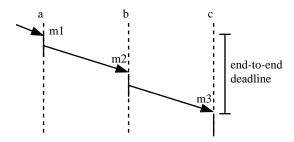

The emphasis on real-time implies that the entire automatic testing setup must be extended to accommodate real-time. The specification language must permit specification of real-time constrains, and must be suited for the type of analysis required for generating test cases. The underlying testing theory which deals with observation of events, the precise definition of conformance, and the necessary structure of the test cases etc. must be revised and be extended to include real-time. Test cases would no longer only be sequences of inputs and expected outputs, but would also need to include when input is to be delivered and when output is expected. Because it is generally impossible to test the system exhaustively, test selection becomes even more imperative. Effective algorithms and tools for generating and selecting timed test cases must therefore be devised. Effective here means ability to handle systems with a size of practical relevance. Finally, the execution of real-time test cases must also be changed such that it precisely exercises the implementation at the time instances dictated by the test case. This requires special care, particular in a distributed system where clocks cannot be perfectly synchronized.

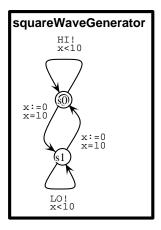

In the following we describe our approach to each of these challenges. We propose timed automata as specification language. This automata based formalism is very expressive, and has become a popular modeling language for real-time systems. In essence, a *timed automata* is a classical state machine augmented with clocks, enabling conditions on actions, and resets of clocks when actions occur.

We employ a testing theory that is a timed extension of Hennessy's classical testing theory [75]. In this theory, two systems are deemed equivalent if no test case exist that one system passes, but the other fails. The theory also defines the exact structure of the test cases required to determine testing equivalence.

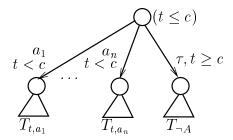

We address the important test selection issue by proposing a coarse grained state space partitioning of the specification. In each partition the specification behaves the same independently of the actual clock values. This approach is related to the domain test selection strategy commonly employed in the testing of sequential programs [116]. Our basic hypothesis is that it is more important to systematically test many different situations as represented by the partitions, than it is to blindly select time instances within the same narrow part of the state space.

To represent the state space of the specification and to compute the reachable parts of the state partitions, we propose to employ the symbolic techniques that has resulted from the last decade's research in verification of real-time systems; in particular we have the UPPAAL approach [119, 13, 64] in mind. This tool performs reachability analysis to prove bounded liveness properties of a collection of concurrent time automata. It has been successfully applied to verification of industrially relevant systems. Because test case generation also involves exploration of the state space, the data structures and algorithms behind this success could potentially also prove advantageous to testing.

It is our thesis that the symbolic techniques developed for reachability analysis of real-time systems also can be used to generate test suites, and that application thereof results in a practical technique for systematic and automatic testing of real-time systems.

We evaluate this thesis through the construction of a prototype tool that implements our ideas. The tool will be applied to a number of specifications. Our evaluation also includes thoughts on the specification language, the algorithms, the number and kinds of generated tests. The many and important practical problems of executing tests, in particular on a distributed system shall not be our main concern here.

#### 1.3.3 Contributions

The following summarizes our main contributions:

- 1. We propose a set of basic algorithms for testing of *untimed* communicating state machines, and implement these algorithms in a test case generator.

- 2. We propose a framework for selecting real-time test cases. The framework is based on a partitioning of the state space. We make several instantiations of this framework, and choose one for further study.

- 3. We design algorithms that generate tests using the above state space partitioning. The proposed algorithms are applicable to a restricted, but determinizable, class of timed automata termed event recording automata.

- 4. The test generation algorithms are implemented in a tool capable of generating test cases automatically from an event recording automata specification.

- 5. We show how our approach can be applied to generate test cases from a set of practically relevant specifications.

- 6. Our final contribution concerns reuse of program components operating under real-time constraints. We propose a specification language that supports reuse through separate and modular specification of functional behavior and time constraints.

#### 1.3.4 Structure of the Thesis

The remainder of the thesis is organized as follows.

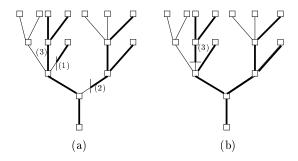

In Chapter 2 we present the testing fundamentals necessary to understand our approach. We lay down the classical untimed testing theory. Also, to understand how a test generation tool could operate, we study test generation algorithms in the simpler untimed setup before addressing the much more challenging real-time case. This work results in a test case generation tool for untimed communicating state machines.

Chapter 3 introduces the real-time dimension. We propose a specification language based on timed automata, and define its semantics as a timed labeled transition system. We show how to derive tests from such a timed transition system. This approach is however unideal because it gives no guidance for systematically choosing the time instance where the implementation should be

tested. We also present a framework for test selection based on partitioning the state space of the specification.

Our main contribution is contained in Chapter 4 where we describe our symbolic approach to selection and generation of test cases. We present our prototype tool and describe the relevant implementation details.

In Chapter 5 we apply our tool to a set of small cases and one larger, and evaluate the applicability of our approach. We relate and compare our work to other research in the field of automated test generation in Chapter 6. Finally, Chapter 7 concludes and discuss topics for future work.

To give a natural flow of topics in the thesis, our contribution regarding reuse of real-time components is contained in Appendix A.

### Chapter 2

## **Untimed Testing**

The goal of this chapter is to lay down the fundamental definitions and test generation techniques before addressing the more general and challenging real-time case. We apply the techniques to an automata based specification language termed communicating state machines. However, this particular choice is not essential for the goal of this chapter since the essential definitions and algorithms are stated in terms of the underlying semantic model, labeled transition systems, which applies to a large family of languages. Specification and semantics of concurrent systems is discussed in Section 2.1.

An important issue is to define exactly when a system is a correct implementation of a specification, and when it is not. The adopted testing theory defines this by a formal relation between two labeled transitions system. The definition of this, the so called implementation relation, also depends on the type of observations that the tester assumes can be made about the implementation, and these must be stated explicitly. Because implementations are concurrent and non-deterministic, it is especially important that the theory checks that the deadlock properties of the implementation comply with those of the specification. Non-determinism also requires a delicate assumption to be made about the execution of tests to achieve exhaustiveness. However, we postpone the general discussion of observations and non-determinism until Chapter 6. The testing theory is presented in Section 2.2.

Given a well defined testing theory, the next issue becomes how to automatically generate tests which can be used to determine whether the implementation is correct. This involves defining precisely which tests should be generated, and finding good algorithms and data structures. We develop and present two techniques in Section 2.3. The first is based on a direct interpretation of the specification, and the second is based on a data structure called a success graph.

The success graph has several nice properties for automatic test generation, but is potentially costly to construct. To study how this data structure can be implemented, and to evaluate its cost, we have implemented it in an prototype tool described in Section 2.4. Finally, Section 2.5 discuss the advantages and disadvantages of the success graph, and the lessons learned.

#### 2.1 Specification of Concurrent Systems

One broadly distinguishes between two different specification language paradigms, the logical languages, and the behavioral description languages. Logical languages such as temporal logics specify the requirements by a set of properties that should always or eventually hold. Behavioral languages such as process algebras and state machines specify requirements by a model that defines how the system changes state depending on current state and event.

According to the system development methodology outlined in Section 1.2.4, tests should be derived from an abstract model of the system under test, and henceforth, we shall focus on behavioral languages.

#### 2.1.1 Communicating State Machines

We propose an automata based specification language, Communicating State Machines, or  $\mathcal{L}_{csm}$  for short. In the forthcoming Chapter 3 we shall propose a generalized timed version, timed automata, that has become popular for specifying real-time systems. We first present  $\mathcal{L}_{csm}$  informally here, and postpone the formal semantics until Section 2.1.3.

We use a graphical notation of state machines. A state machine is a directed graph whose nodes represent the different locations the machine can occupy, and whose edges represent the possible transitions between locations.

An edge is labeled with one of three kinds of actions: The machine can perform an *internal action* where it internally changes from one location to another. It can also enable an *observable action* to permit synchronization with the environment. Finally, two state machines can synchronize on complementary actions without involving the environment. When a *synchronization* occurs, both state machines change location. A pair of actions with the same name, but one suffixed with an exclamation mark, and the other with a question mark, indicates complementary actions which may synchronize. Although there is no semantic difference the exclamation mark typically indicates output and the question mark input<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>In languages with value passing they designate actual and formal parameters.

A specification consist of a *network* of state machines. A network represents a collection of concurrently executing and synchronously communicating machines. The concurrent execution is based on an interleaving semantics. A state machine may also access a number of shared integer variables. Its transitions can be guarded by a predicate over these variables such that a false guard disables the transition. When an action is executed, the variables can be updated using assignment expressions. Other finite discrete variable types could be permitted for convenience, but are adequately modeled by integeres.

A final feature is *committed* locations. If a machine enters a committed location, the next action performed by the network must be an action leaving that location, i.e., committed states must be left immediately. Committed locations are useful for modeling atomic sequences of actions, e.g., atomic broadcast or multi-way synchronization. We use the term *location* of an automaton to refer to the node that it currently occupies, and reserve the term state to denote a semantic state configuration consisting of locations and variable values.

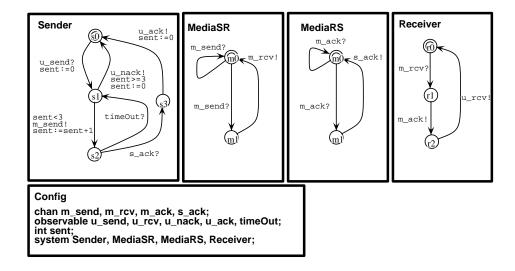

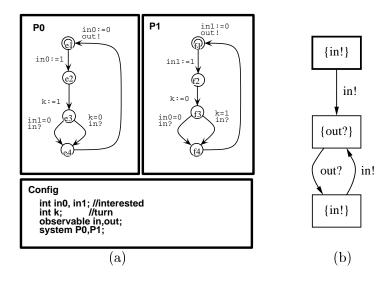

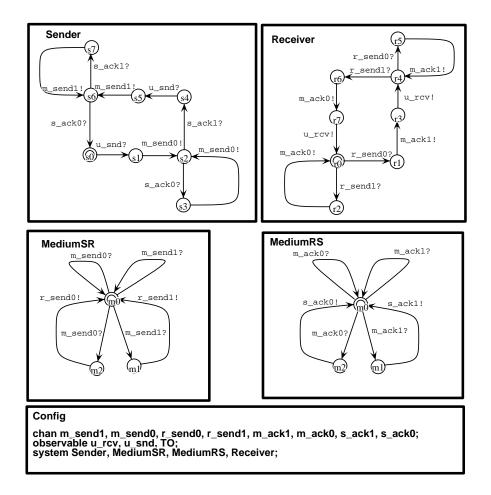

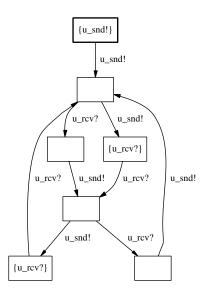

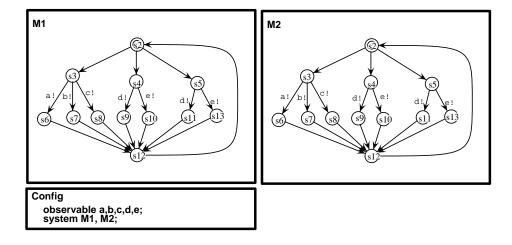

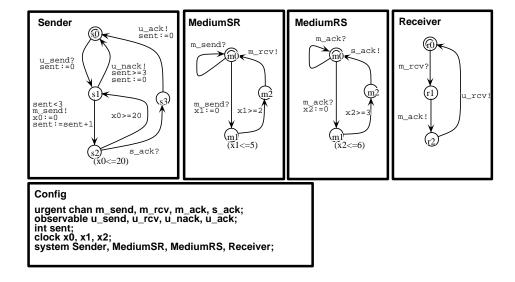

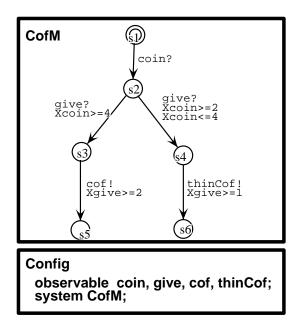

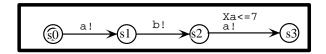

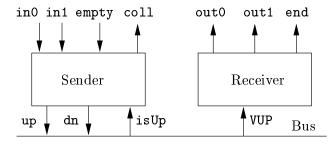

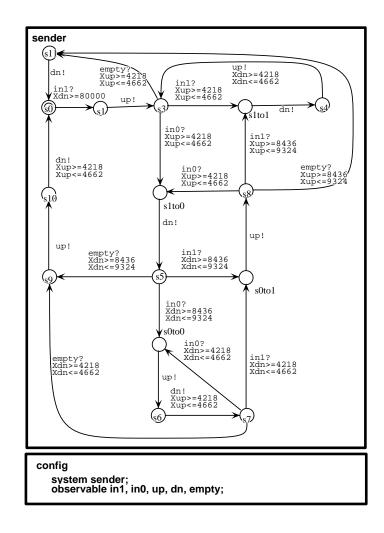

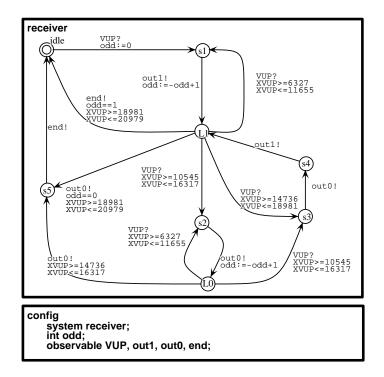

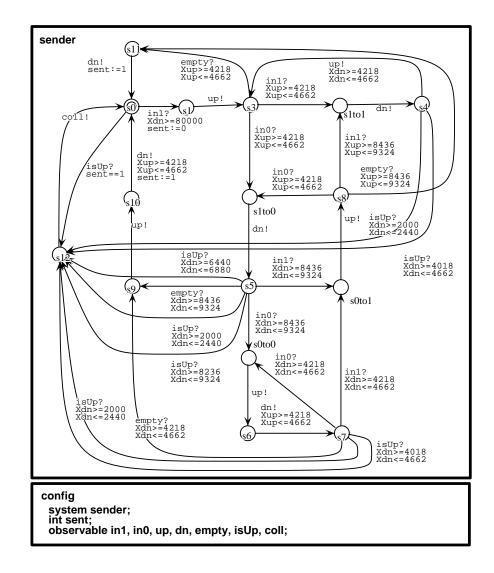

Figure 2.1. Specification of a communication protocol.

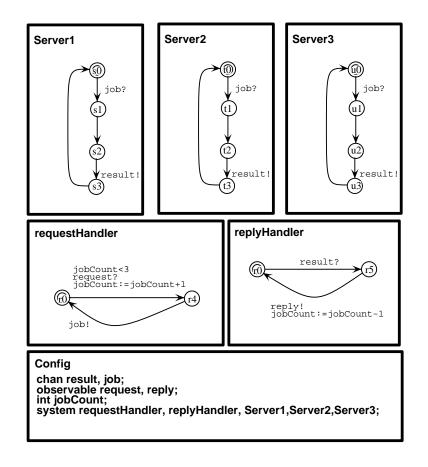

The example shown in Figure 2.1 demonstrates the most important features of  $\mathcal{L}_{csm}$ . The example is a model of a simple stop and wait transport layer communication protocol with bounded retransmission. The purpose is to establish reliable communication. The network consists of four machines; a sender (Sender), a receiver (Receiver), and two machines modeling the communication media: MediaSR models the communication of data from sender to receiver, and MediaRS the communication of acknowledgments from the receiver to the sender. Table 2.2 summarizes the actions used by the protocol.

| Action   | Description                                            |

|----------|--------------------------------------------------------|

| u_send   | data from upper layer                                  |

| $u\_ack$ | ack to upper layer: data has been received             |

| u_nack   | failure indication to upper layer: data unacknowledged |

| u_rcv    | data to upper layer                                    |

| timeOut  | give up wait for acknowledgment                        |

| m_send   | data to media from sender                              |

| m_rcv    | data from media to receiver                            |

| $m_ack$  | ack from receiver to media                             |

| s_ack    | ack from media to sender                               |

Table 2.2. Protocol actions.

The configuration box in Figure 2.1 declares the network of state machines (the system line), the actions used for communication internally (the chan line) and externally (the observable line), and the used integer variables (the int line). We use the Autograph [92] developed at INRIA, France, to edit state machine networks; Autograph is a graph editing tool with a graphical user interface. The protocol specification presented here can be fed to the automatic test generation tool to be presented later in Section 2.4.

Because the media may drop data packets and acknowledgments, the sender is prepared to time out and attempt retransmission three times. If the data is still unacknowledged, the protocol gives up and signals error to the user. The number of transmission attempts is modeled using an integer variable (sent), and by guarding the m\_send and u\_nack edges appropriately.

A final aspect of the specification worth pointing out is the modeling of timeouts. Because  $\mathcal{L}_{csm}$  is untimed, it does not permit specification of concrete timeout values. Instead, the possibility of timeouts is modeled by the observable timeOut action. The resulting model can be viewed as an overapproximation of the real protocol behavior since the timeout action is always enabled after a message has been sent, not only after a certain delay. An alternative is the timeout statement in the Promela protocol specification language [53] which only executes when no other statements are possible. This can thus be seen as an under approximation. However, such approximations are not always possible or sufficient. We therefore need a specification formalism with explicit timing.

#### 2.1.2 Labeled Transition Systems

We use labeled transition systems (LTS) as the underlying semantic model. Sometimes it is also convenient to give small specifications directly as LTSs.

#### **Definition 2.3** Labeled Transition System ( $\mathcal{L}_{lts}$ ):

An LTS is a 4-tuple  $\langle S, s_0, Act_\tau, \rightarrow \rangle$ , where

- 1. S is the set of states,

- 2.  $s_0 \in S$  is the initial state,

- 3. Act is the set of observable actions, and  $Act_{\tau} = Act \cup \{\tau\}$  the actions including the distinguished internal action  $\tau$ ,

- 4.  $\rightarrow \subseteq S \times Act_{\tau} \times S$  is the transition relation.

- 5. We assume that Act is equipped with a mapping<sup>-</sup>:  $Act \mapsto Act$  such that for all actions  $\bar{a} = a$ .  $\bar{a}$  is said to be the complementary action of a.

Intuitively, S represents the possible states of a computation. An edge from state s to s' labeled with action  $\alpha \in Act_{\tau}$  represents that s' is a state that can result by executing action  $\alpha$  in state s. Some convenient notation is summarized in Definition 2.4.

**Definition 2.4** LTS notation. Let  $a \in Act$  and  $\alpha \in Act_{\tau}$ :

```

Definition

s \xrightarrow{\alpha} s'

(s, \alpha, s') \in \rightarrow

s \xrightarrow{\alpha}

\exists s'.\ s \xrightarrow{\alpha} s'

\exists s_1, s_2 \dots s_n . \ s \xrightarrow{\alpha_1} s_1 \xrightarrow{\alpha_2} s_2 \dots \xrightarrow{\alpha_n} s_n \text{ and } s_n = s',

where \sigma = \alpha_1 \cdot \ldots \cdot \alpha_n

\exists s'.\ s \xrightarrow{\sigma} s'

the reflexive and transitive closure of \xrightarrow{\tau}

s \stackrel{\epsilon}{\Rightarrow} s'

s = s' \text{ or } s \stackrel{\tau}{\rightarrow}^* s'

s \stackrel{a}{\Rightarrow} s'

\exists s_1, s_2. s \stackrel{\epsilon}{\Rightarrow} s_1 \stackrel{a}{\rightarrow} s_2 \stackrel{\epsilon}{\Rightarrow} s'

\exists s_1, s_2 \dots s_n . \ s \xrightarrow{a_1} s_1 \xrightarrow{a_2} s_2 \dots \xrightarrow{a_n} s_n \text{ and } s_n = s',

s \stackrel{\sigma}{\Rightarrow} s'

where \sigma = a_1 \cdot \ldots \cdot a_n

s \stackrel{\sigma}{\Rightarrow}

\exists s'. \ s \xrightarrow{\sigma} s'

\{a \in Act \mid s \stackrel{a}{\Rightarrow} \}

sort(s)

\{\sigma \in Act^* \mid s \stackrel{\sigma}{\Rightarrow} \}

Tr(s)

Tr(s_0)

Tr(\mathcal{S})

\{s' \mid s \stackrel{\sigma}{\Rightarrow} s'\}

s after \sigma

\mathcal{S} after \sigma

s_0 after \sigma

```

We shall furthermore use a set of CCS [74] inspired operators on LTSs to enable their construction using algebraic notation, see Definition 2.5.

**Definition 2.5** Construction of LTSs:

Let  $S_1 = \langle S_1, s_{01}, Act_1, \rightarrow_1 \rangle \in \mathcal{L}_{lts}$ ,  $S_2 = \langle S_2, s_{02}, Act_2, \rightarrow_2 \rangle \in \mathcal{L}_{lts}$ ,  $a \in Act$ , and  $\alpha \in Act_{\tau}$ .

- 1. The LTS  $nil = \langle \{s_0\}, s_o, \{\tau\}, \emptyset \rangle$

- 2. The action prefix  $\alpha$ ;  $S_1 = \langle S_1 \cup \{s'\}, s', Act_1 \cup \{\alpha\}, \rightarrow_1 \cup \{s' \xrightarrow{\alpha} s_{01}\} \rangle$ ,  $s' \notin S_1$ .

- 3. The summation  $S_1 + S_2 = \langle S_1 \cup S_2 \cup \{s'\}, s', Act_1 \cup Act_2, \rightarrow_1 \cup \rightarrow_2 \cup \{s' \xrightarrow{\alpha} s'' \mid s_{01} \xrightarrow{\alpha}_1 s'' \lor s_{02} \xrightarrow{\alpha}_2 s''\} \rangle, s' \notin S_1 \cup S_2$

- 4. The parallel composition  $S_1 \parallel S_2 = \langle S_1 \times S_2, (s_{01}, s_{02}), Act_1 \cup Act_2, \rightarrow \rangle$  where the transition relation  $\rightarrow$  is defined as:

$$\frac{s_1 \xrightarrow{\alpha} s_1'}{(s_1, s_2) \xrightarrow{\alpha} (s_1', s_2)} \quad \frac{s_2 \xrightarrow{\alpha} s_2'}{(s_1, s_2) \xrightarrow{\alpha} (s_1, s_2')} \quad \frac{s_1 \xrightarrow{a} s_1'}{(s_1, s_2) \xrightarrow{\tau} (s_1', s_2')}$$

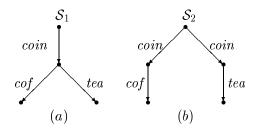

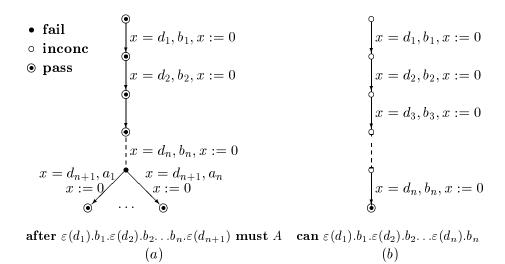

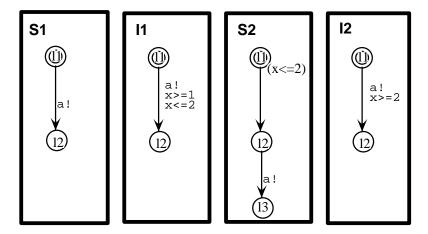

An LTS is deterministic iff  $s \not\to f$  for any s, and whenever  $s \xrightarrow{a} s'$  and  $s \xrightarrow{a} s''$  then s' = s''. Thus, in a deterministic LTS, the execution of an action in a given state results in a unique successor state; in a non-deterministic LTS there may be several such successor states. Figure 2.6 illustrates the difference between deterministic and non-deterministic LTSs.

**Figure 2.6.** A deterministic (a) and a non-deterministic (b) labeled transition system.

### 2.1.3 Semantics of Communicating State Machines

Next we provide the definitions for a network of communicating state machines. The formal structure of a state machine over a set of variables V and actions  $\mathcal{A}$  is given in Definition 2.7. The formal semantics given as an LTS follows in Definition 2.8.

#### **Definition 2.7** State machine:

- 1. The guards G(V) over a set of integer variables V is generated by the syntax  $g ::= \gamma \mid g \land g$  where  $\gamma$  is a constraint of the form  $v \sim c$  with  $\sim \in \{\leq, <, =, >, \geq\}$  and c an integer constant, and  $v \in V$ .

- 2. R(V) is the set of variable assignments of the following forms: v := v' op c; or v := c; where  $op \in \{+, -, *\}$ , and  $v, v' \in V$ .

- 3. A state machine  $\mathcal{M}$  over actions  $\mathcal{A}_{\tau}$  and integer variables V is a tuple  $\langle N, l_0, E, N_C \rangle$  where

- (a) N is a (finite) set of locations,

- (b)  $l_0$  is the initial location,

- (c)  $N_C \subseteq N$  the set of committed locations, and

- (d)  $E \subseteq N \times G(V) \times \mathcal{A}_{\tau} \times 2^{R(V)} \times N$  is the set of edges where G(X) is the set guards, and R(X) is the set of assignments. We write  $l \xrightarrow{g,a,r} l'$  if  $\langle l,g,a,r,l' \rangle \in E$  to represent a transition from location l to location l' with guard g, action a, and set of assignments r.

- (e) Let  $\overline{a}$  denote the complement of action  $a \in \mathcal{A}$  such that  $\overline{a!} = a$ ? and  $\overline{a?} = a!$ .

A network of communicating state machines  $\overline{\mathcal{M}} = (\mathcal{M}_1 \parallel \cdots \parallel \mathcal{M}_n)$  is a collection of machines  $\mathcal{M}_1 \dots \mathcal{M}_n$  operating concurrently. The actions are classified in two categories. The network synchronizes with the environment via a set of distinguished observable actions  $\mathcal{O} \subseteq \mathcal{A}$ , and can synchronize internally only via the hidden actions  $\mathcal{A} - \mathcal{O}$ . That is, no internal communication is permitted over observable actions. Because we offer no explicit restriction operator, this distinction allows a simple means of hiding the required actions from the environment.

Semantically, the state of a network is modeled by a state configuration:  $\langle \bar{l}, \bar{v} \rangle$ . The location vector  $\bar{l}$  is a vector of locations that represent the joint control location of the network;  $l_i$  is the location of machine  $\mathcal{M}_i$ . We write  $\bar{l}[l'_i/l_i]$  to denote the vector where the *i*th element of  $\bar{l}$  has been replaced by  $l'_i$ . The second component  $\bar{v}$  represents the current variable valuation. Let  $\bar{v}(v)$  denote the value of variable  $v, r(\bar{v})$  the valuation resulting by simultaneously updating  $\bar{v}$  with the assignments in r, and finally,  $g(\bar{v})$  the outcome of evaluating guard g in variable valuation  $\bar{v}$ . In the initial state  $\langle \bar{l}_0, \bar{0} \rangle$  all machines are in their respective initial location, and all variables are zero. Let  $N_{C_i}$  be the set of committed locations for machine  $\mathcal{M}_i$ .

**Definition 2.8** Transition rules for  $\mathcal{L}_{csm}$ :

$$\frac{l_i \xrightarrow{g,a,r} l_i' \quad g(\bar{v}) \quad a \in \mathcal{O} \cup \{\tau\}}{\langle \bar{l}, \bar{v} \rangle \xrightarrow{a} \langle \bar{l}[l_i'/l_i], r(\bar{v}) \rangle}, \forall k \in [1, n]. \text{ if } l_k \in N_{C_k} \text{ then } i = k$$

$$\frac{l_i \xrightarrow{g_1,a,r_1} l_i' \qquad l_j \xrightarrow{g_2,\overline{a},r_2} l_j' \qquad (g_1 \wedge g_2)(\overline{v}) \quad i \neq j \quad a \in \mathcal{A} - \mathcal{O}}{\langle \overline{l}, \overline{v} \rangle \xrightarrow{\tau} \langle \overline{l}[l_i'/l_i, l_j'/l_j], (r_1 \cup r_2)(\overline{v}) \rangle}, \\ \forall k \in [1, n]. \text{ if } l_k \in N_{C_k} \text{ then } k = i \vee k = j$$

The transition rules are defined in Definition 2.8. The first rule concerns observable and internal actions. The second rule defines internal synchronization between to automata. In both cases, the side condition ensures that when an automaton is in a committed location, a transition away from this location will be taken next.

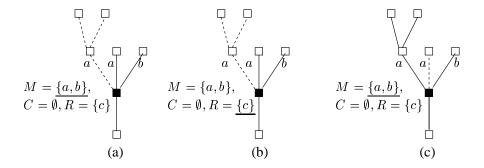

# 2.2 Testing Theory for Non-deterministic Systems

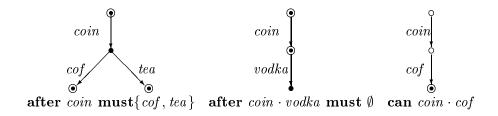

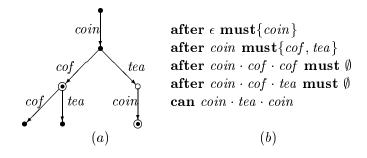

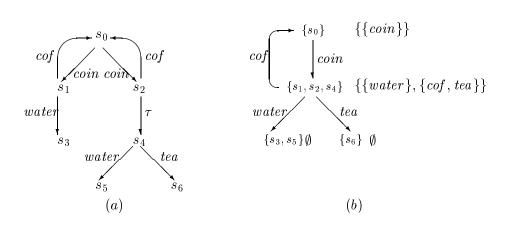

In this section we review the theory underlying our testing approach. We adopt the classical testing methodology developed by de Nicola and Hennessy in [75, 49]. Their proposal states that a specification and an implementation are to be considered equivalent if no external observer can distinguish between them by performing "button" pressing experiments, i.e., if they pass exactly the same tests. Moreover, their work also characterizes the precise kind of tests needed to determine whether two systems are testing equivalent. This is obviously of great importance for automatic testing. These ideas and their application to conformance testing of communication protocols were further developed by Brinksma [21]. Our presentation of the testing theory and its definitions is derived from [75, 49].

# 2.2.1 Goals and Assumptions

Systematic and well founded test generation presumes a formalized implementation relation **implements** which defines when a system is a correct implementation of the specification. It also presumes a definition of tests, and a relation **passes** which defines when a system passes a test. The goal of (automated) testing is to construct a suite of tests  $\Pi$  from the specification S such that the correctness of the implementation  $\mathcal{I}$  can be determined precisely from the results of executing these tests:

$\mathcal{I}$  implements  $\mathcal{S}$  iff  $\forall \mathcal{T} \in \Pi$ .  $\mathcal{I}$  passes  $\mathcal{T}$

This requirement has two implications. The test suite should reject all incorrect implementations (soundness), and it should never reject correct implementations (completeness). These definitions of soundness and completeness, stated formally in Definition 2.9, are inspired by the work by Peleska and Siegel in [81] that is based on a proof theoretic view on testing, i.e, testing is viewed as a (very) special proof technique. In this setting, soundness means that no false conclusions about the relationship between implementations and specifications can be deduced. Completeness means that all true conclusions can be deduced.

**Definition 2.9** Soundness and completeness of test suites:

- 1.  $\Pi$  is sound iff  $\mathcal{I}$  ¬implements  $\mathcal{S}$  implies  $\exists \mathcal{T} \in \Pi$ .  $\mathcal{I}$  ¬passes  $\mathcal{T}$

- 2.  $\Pi$  is complete iff  $\mathcal{I}$  implements  $\mathcal{S}$  implies  $\forall \mathcal{T} \in \Pi$ .  $\mathcal{I}$  passes  $\mathcal{T}$

- 3.  $\Pi$  is exhaustive iff  $\Pi$  is sound and complete.

Exhaustive testing is normally infeasible because a huge number of tests are required. One therefore risks concluding that an implementation is correct, when it is not. The passing of a test suite should consequently be interpreted more cautiously: No evidence of errors were found.

The goal of the remainder of this section is to formalize the **implements** and **passes** relations. However, these definitions hinges on a set of basic assumptions:

- 1. The specification is given as an LTS.

- 2. The implementation can be described by an LTS.

- 3. The observable actions of the implementation are known.

- 4. The implementation under test and its environment (and tester) use synchronous rendezvous style communication.

- 5. The specification and implementation has a finite number of states.

- 6. The specification converges strongly, i.e., it has no infinite sequences of  $\tau$  actions.

We argue for each in turn. 1) The semantics of most specification languages can be expressed as LTSs. It therefore suffices to develop the theory for this basic language. 2) To formulate the implementation relation as a mathematical relation between two formal objects it is necessary to assume that the

implementation can be described as an LTS. It is important to note that we only assume existence of such an LTS model, not explicit knowledge of one, i.e., the implementation remains unknown. This assumption is referred to as the test hypothesis [111]. 3) Knowing the observable actions of the implementation is necessary to claim or prove algorithms to be sound and complete, even in theory. 4) The necessary theory is well established for synchronously communicating systems. Further, other styles can be modeled with reasonable effort. 5) Infinite state systems causes algorithmic problems that are best disregarded at first. 6) The convergence assumption is not strictly necessary as the presented theory can be extended to also handle divergence, but absence thereof eases the technical presentation.

#### 2.2.2 Tests and Test Execution

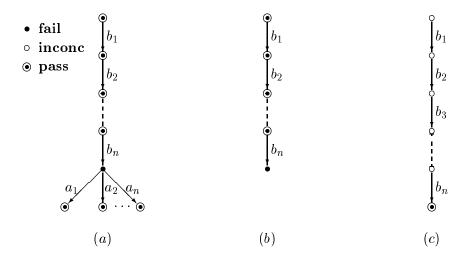

Tests can be modeled by using an extended type of LTSs where each state has been assigned a **pass** or a **fail** verdict. Intuitively, if the execution of a test stops in a state with a **fail** verdict, the implementation will be declared to fail that test, and is consequently considered incorrect.

### **Definition 2.10** Test LTS ( $\mathcal{L}_{tlts}$ ):

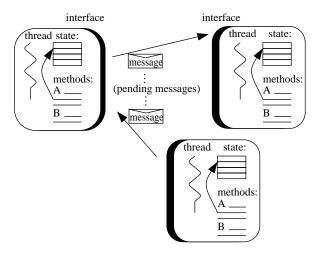

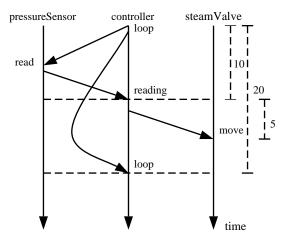

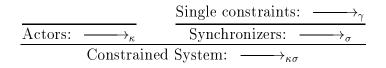

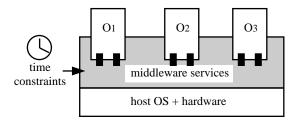

A test  $\mathcal{T}$  is an extended LTS  $\langle S, s_0, Act_{\tau}, \to, \mathcal{V} \rangle$ , where S is the set of states,  $s_0$  the initial state,  $Act_{\tau}$  the set of actions,  $\to$  the transition relation—all as previously defined in Definition 2.3, and  $\mathcal{V}$  is the verdict assignment function:  $\mathcal{V}: S \mapsto \{\mathbf{pass}, \mathbf{fail}\}.$