## Design techniques for safe, reliable, and trustworthy analog circuits

by

## **Matthew Strong**

A dissertation submitted to the graduate faculty

in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Major: Electrical Engineering (Very Large Scale Integration)

Program of Study Committee: Degang Chen, Major Professor Randall Geiger Nathan Neihart Ratnesh Kumar Zhengdao Wang

The student author, whose presentation of the scholarship herein was approved by the program of study committee, is solely responsible for the content of this dissertation. The Graduate College will ensure this dissertation is globally accessible and will not permit alterations after a degree is conferred.

Iowa State University

Ames, Iowa

2023

Copyright © Matthew Strong, 2023. All rights reserved.

# TABLE OF CONTENTS

| LIST OF FIGURES                                             | . iv |

|-------------------------------------------------------------|------|

| LIST OF TABLES                                              | . vi |

| ACKNOWLEDGMENTS                                             | vii  |

| ABSTRACT                                                    | viii |

| CHAPTER 1. INTRODUCTION                                     |      |

| Research Overview                                           | 3    |

| Organization of Dissertation                                | 4    |

| CHAPTER 2. INTEGRATING AMS CIRCUIT TESTS IN ON-CHIP SYSTEMS |      |

| Defect-Oriented Testing                                     |      |

| Analog & Mixed-Signal Design-for-Test (DfT)                 |      |

| PCB Demonstration & Measurements of Analog DfT Circuits     |      |

| Handling Defects in Test Circuit Components                 | 24   |

| Summary                                                     | 27   |

| CHAPTER 3. MONITORING AGING WITH ONLINE MEASUREMENTS        | -    |

| Bias & Temperature Instability                              | 29   |

| Simulating and Measuring BTI                                |      |

| Monitor for In-Field Statistical Characterization of BTI    | 36   |

| Sizing the Transistors of the Monitor                       | 40   |

| Aging-Related Errors from Other Components                  |      |

| $\Delta VT$ Comparison and Data Conversion                  |      |

| Sampling BTI from Multiple Devices                          |      |

| Discussion.                                                 |      |

| Summary                                                     |      |

| CHAPTER 4. HARDWARE TROJAN THREATS TO ANALOG CIRCUITS       | .51  |

| Threat Model                                                |      |

| Trojan Taxonomies & Detection Methods                       |      |

| Analog Hardware Trojans                                     |      |

|                                                             |      |

| PAAST Trojan Classification                                 |      |

| Summary                                                     | 60   |

| CHAPTER 5. TRIGGERING A PAAST TROJAN                        |      |

| Coupled Oscillator Applications                             |      |

| The Trojan Design                                           |      |

| Measurements of Trojan Activation                           | 75   |

| Discussion                                                  | 79   |

| CHAPTER 6. CONCLUSIONS |  |

|------------------------|--|

| REFERENCES             |  |

## LIST OF FIGURES

|                                                                                                   | Page |

|---------------------------------------------------------------------------------------------------|------|

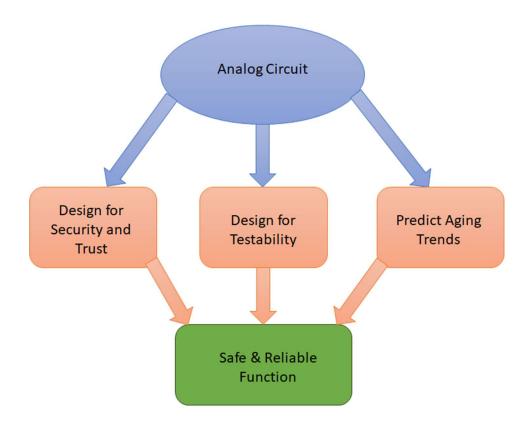

| Figure 1.1. Multi-faceted research thrust for safe and reliable analog circuit function           | 4    |

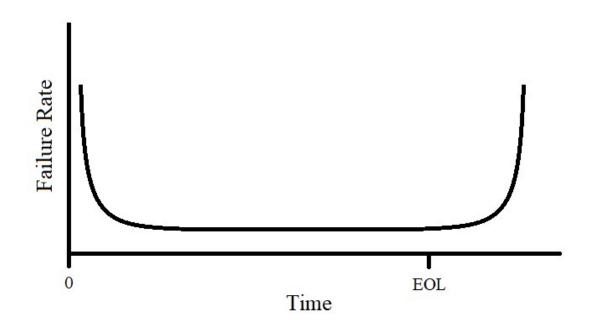

| Figure 2.1. Typical failure rate of a part population after fabrication.                          | 7    |

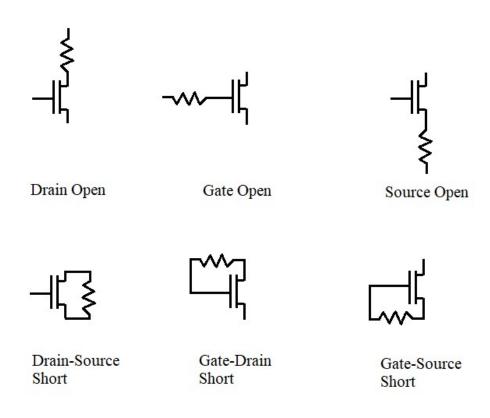

| Figure 2.2. Modeling hard defects in MOSFETs                                                      | 10   |

| Figure 2.3 Analog test PCB and FPGA board for injecting analog faults and validating BISTs.       | 15   |

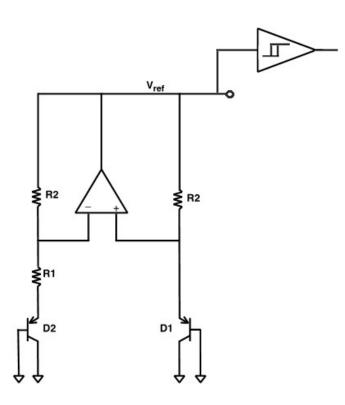

| Figure 2.4 Kuijk bandgap reference with window comparator for testing                             | 17   |

| Figure 2.5 DfT LDO in test mode                                                                   | 18   |

| Figure 2.6 PGA schematic(a) and the amplifier's transfer curve(b)                                 | 20   |

| Figure 2.7 Concurrent sampling method using unary data.                                           | 23   |

| Figure 2.8 High-resolution concurrent sampling method.                                            | 23   |

| Figure 2.9 Bandgap reference circuit with window comparator observer                              | 24   |

| Figure 2.10 Gate modification that prevents observer defects from loading the circuit             | 25   |

| Figure 2.11 Switch architectures with varying resiliency to faults                                | 27   |

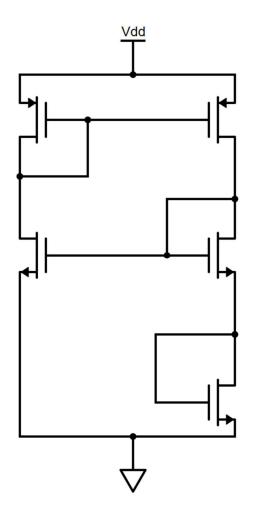

| Figure 3.1 Threshold voltage difference circuit                                                   | 38   |

| Figure 3.2 Proposed BTI Monitor                                                                   | 39   |

| Figure 3.3 Comparator input stage with power-disabling capability                                 | 47   |

| Figure 3.4 An array of aged devices compared to a reference device.                               | 49   |

| Figure 4.1 Production flow and points of Trojan insertion                                         | 53   |

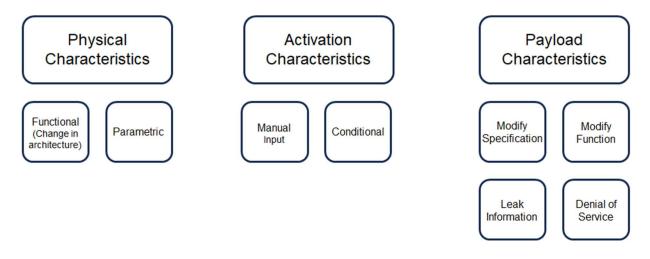

| Figure 4.2 Summary of existing hardware Trojan taxonomies                                         | 54   |

| Figure 4.3 Widlar current reference with Trojan equilibrium.                                      | 61   |

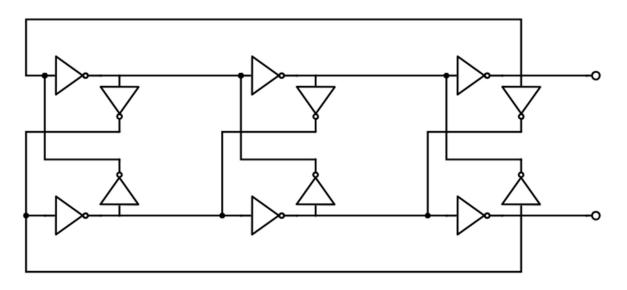

| Figure 4.4 Coupled ring oscillator with Trojan equilibria or Trojan limit cycle.                  | 62   |

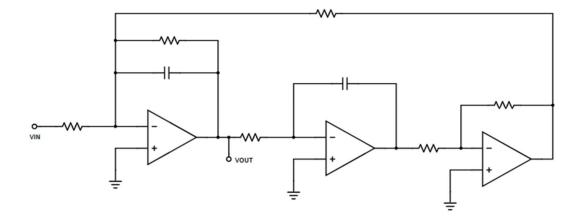

| Figure 4.5 Active filter that is not input-to-state stable but has a globally stable equilibrium. | 64   |

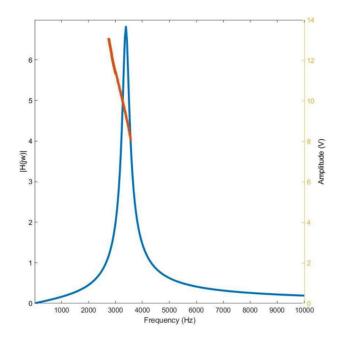

| Figure 4.6 | Jump resonance in the active filter. The blue curve plots gain for the sweep in the increasing direction and the orange curve plots gain for the decreasing |    |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|            | direction                                                                                                                                                   | 64 |

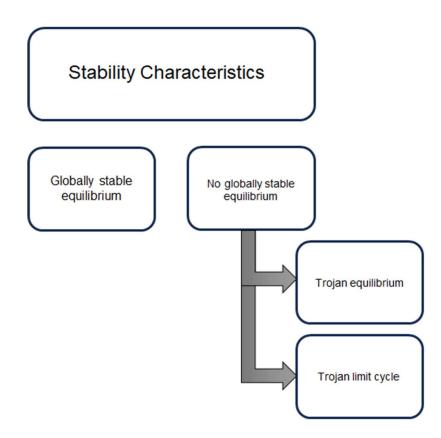

| Figure 4.7 | Stability characteristics for PAAST Trojans.                                                                                                                | 66 |

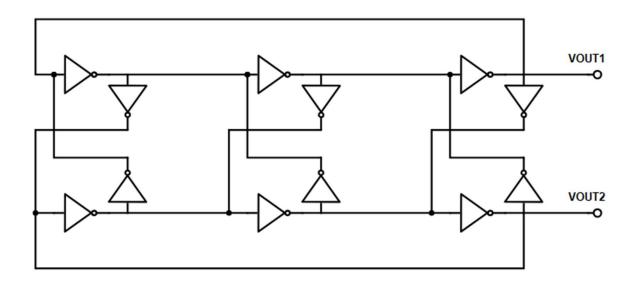

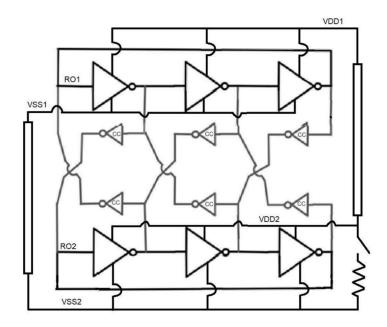

| Figure 5.1 | The coupled oscillator architecture to be designed with a PAAST Trojan                                                                                      | 69 |

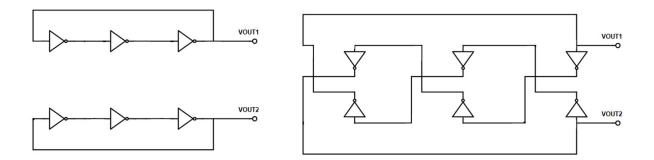

| Figure 5.2 | The coupled oscillator's feedback loops.                                                                                                                    | 72 |

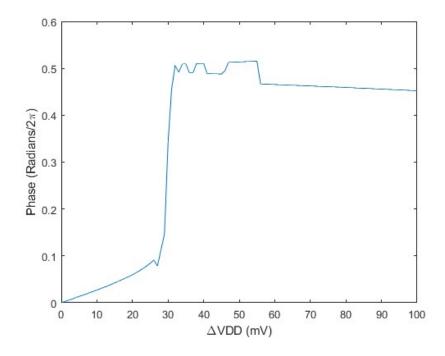

| Figure 5.3 | Coupled oscillator's output phase difference vs. VDD mismatch.                                                                                              | 73 |

| Figure 5.4 | Modeling power bus delay to create trigger the Trojan.                                                                                                      | 74 |

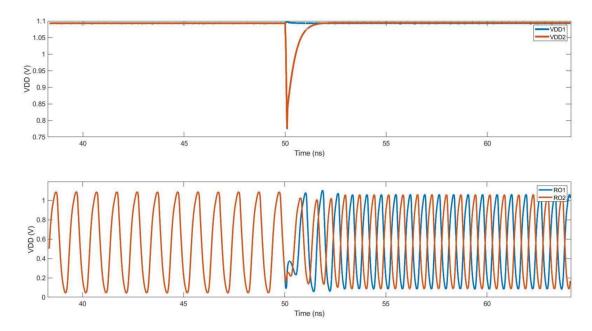

| Figure 5.5 | A localized power supply glitch triggering the PAAST Trojan                                                                                                 | 74 |

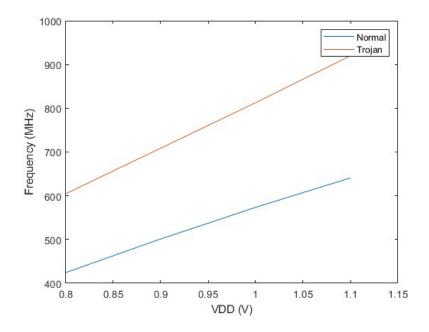

| Figure 5.6 | Free-running frequency vs. control voltage for the normal and Trojan limit cycles.                                                                          | 78 |

## LIST OF TABLES

|           | I                                                                                                    | Page |

|-----------|------------------------------------------------------------------------------------------------------|------|

| Table 2.1 | LDO input voltage measurements.                                                                      | 18   |

| Table 2.2 | LDO IOI test results                                                                                 | 18   |

| Table 2.3 | Truth table for PGA test when the input voltage requires a gain of 16                                | 22   |

| Table 5.1 | Measurements of the frequency and phase difference for the oscillator's nominal and Trojan function. | 76   |

| Table 5.2 | Summary of if the trigger successfully activated the Trojan                                          | 76   |

| Table 5.3 | Summary of if Trojan deactivation was successful.                                                    | 78   |

#### ACKNOWLEDGMENTS

I would first like to thank my major professor, Dr. Degang Chen. His thoughtful advice and careful guidance through the years have been invaluable in my research and studies, and he helped me get the most out of my time at Iowa State. I consider myself lucky to have had such a dedicated mentor helping me make this experience one of the most rewarding of my life.

I would also like to thank Dr. Randall Geiger for his help and direction. As principal investigator in my first research project, he taught me many of the fundamental skills required in academic research. His advice as one of my committee members has been immensely helpful as well.

Thank you to my other committee members, Dr. Nathan Neihart, Dr. Ratnesh Kumar, and Dr. Zhengdao Wang. Each provided unique insights that helped me maintain perspective in my work.

The Electrical and Computer Engineering department has a wonderful and extremely helpful staff, and I want to thank them for their dedication to the students.

I was very fortunate to work with many gifted students during my journey. Our discussions and exchange of ideas have been tremendously helpful, and I am extremely grateful to my past and present colleagues.

Finally, none of this would have been possible without the support of my family who I love very much.

vii

#### ABSTRACT

Rapid developments in communication, automation, and smart technologies continue to drive the trend of increasingly large-scale integration of electronics. The number of ICs embedded in various systems continues to rise to realize more sophisticated functions and capabilities, and as a result we rely more and more on the smooth, safe, and secure operation of ICs. Quality assurance of ICs is of paramount importance in critical missions because faults can incur heavy consequences. To ensure reliability, IC designs undergo a thorough verification process prior to fabrication and comprehensive testing and measurements before distribution. These steps provide confidence in parts shortly after their deployment into operation. Many critical ICs also embed functions to detect abnormal or faulty behavior in the field and add another layer of safety to the operation. The methodology for creating these built-in self-tests (BISTs) for digital circuits is fairly mature, yet analog and mixed signal (AMS) circuits still present a significant challenge for verification and testing.

The development of in-field tests for AMS circuits is relatively new. Part of the difficulty is the many constraints that define satisfactory function. Complicated signal generators and observers are usually required to stimulate the circuit and measure its response in order to accurately determine if it meets specifications. These are available in a production test environment in the form of external equipment, but the amount of hardware, power, and other resources required for these tests make it impractical for in-field operation. To address this issue, some simple, low-resource test circuits have been developed to test some fundamental AMS blocks. The test results allow one to infer faulty behavior of circuit rather than explicitly confirming specifications are not met, which makes the design of test inputs and observers significantly easier. These test circuits use simple analog-digital interfaces which aid the

integration of the designs into existing digital test architectures. The AMS test circuits were implemented on a PCB to demonstrate their feasibility.

For ICs targeting high reliability, the parts are designed such that the probability of a fault occurring is extremely low, at least for a time. BISTs for in-field testing are intended to detect faults originating from a single source because of a defect or some other unpredictable event. But every IC will reach a time when devices start to fail independently of each other because of normal wear from use. The physical mechanisms causing transistor degradation, called transistor aging, have a predictable trend for a given history of use. On-chip monitors that track device aging over the life of a part can provide warnings before widespread failure occurs and allow confident operation of IC right up to its effective end of life (EOL). A bias and temperature instability (BTI) monitor was designed to estimate the evolving probability of BTI degradation in a device or devices during its operation.

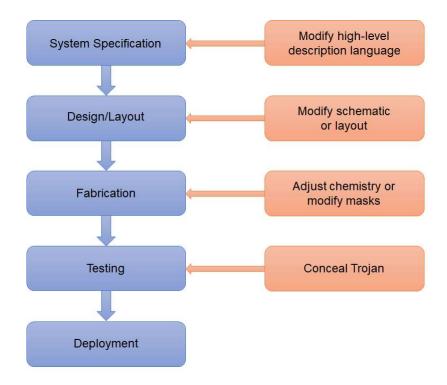

In addition to the chance of random failures in critical ICs, designers and customers must also concern themselves with intentionally induced failures. The important role these parts play in their respective systems makes them potential targets of attack by third parties whose goal is contrary to the parts' primary missions. One potential class of threats is the hardware Trojan horse, a hidden and malicious function physically embedded in the design. These are highrisk/high-reward attacks because insertion of the Trojan is generally considered difficult but successful activation is potentially devastating. Much research and resources have been dedicated to developing threat models, identifying potential means of insertion and operation, and detection of Trojans during production tests. However, these efforts are almost entirely focused on the security of digital circuits while threats to AMS circuits have been ignored. One of the main reasons for this is the inherent sensitivity of AMS circuits, which leads to the assumption that any tampering would be obvious. This assumption falls short when a wellknown problem in AMS circuit design is considered: multi-stable operation. A definitive taxonomy of this sub-class of hardware Trojans was constructed to complement existing definitions and efforts on Trojan classification. An example of an AMS circuit with such a Trojan is provided to validate the threat this class of Trojans poses.

### **CHAPTER 1. INTRODUCTION**

Continued progress in circuit integration techniques has allowed increasingly sophisticated electronic products to be developed for use in a wide range of systems. Many systems rely on integrated circuits to perform critical functions, meaning that a failure of the IC would cause system-wide failure. With automation and smart technologies advancing, ICs are having a broader impact than ever before on day-to-day life. The growth rate of critical IC deployment makes it inevitable that faults will occur at inopportune times of operation. This is why it is necessary to add safeguards to designs that facilitate graceful failure of a system, such as a safe shutdown or giving time for manual intervention.

These ICs targeting functional safety and reliability need effective means of self-testing. The continually increasing variety of applications and scale of integration has resulted in very diverse testing methodologies and growing amount of data that must be processed to perform diagnostics. This is spurring efforts for efficient test data collection and transmission. Expansive test architectures are being integrated into designs to optimize this process, and newly developed built-in self-tests need to be compatible with these architectures to maintain a continuously high level of functionality and safety.

In addition to creating reliable ICs, designers must ensure their parts remain safe from a security standpoint. Due to the critical role that these ICs play in some systems, they may be targeted for attack by adversaries who wish to sabotage the larger system and/or compromise its mission. One avenue of attack is the hardware Trojan, a secret function within an IC that forces it to act contrary to its intended use. To offset this vulnerability, researchers have proposed potential architectures and methods on how a hardware Trojan may be realized, as well as many testing strategies to identify the presence of a hardware Trojan within a part. By continuously

anticipating different forms of security breaches, companies can continue developing defenses to stay a step ahead of attackers.

The onset of a fault and the activation of a hardware Trojan both result in a sudden and undesirable change in system behavior. The steps to prevent either, or at least reduce the harm they cause, are also similar: meticulous design, rigorous verification and testing, and the inclusion of detectors and controllers that correct failures or allow the system to fail safely. With these similarities, it is appropriate to discuss hardware security and reliability within the same setting as concepts and solutions from one topic often apply to the other.

#### **Background and Motivation**

Research and development of tests and functional safety measures is an ongoing process for both analog and digital circuits, but the progression of digital circuit solutions has far outpaced that of analog circuits. A report published in 2014 compared the number AMS ICs and digital ICs returned due to faults escaping testing and found that, at best, the defective parts per million of the AMS ICs were 10 times higher than the digital ICs[1]. This represents a significant gap in the effectiveness of AMS testing. Since this report, there has been a massive overhaul of how AMS ICs are tested and how the test methods are validated, including more efficient BIST simulation and standardized models for defect-oriented testing[2], [3]. There have also been a growing number of proposed BIST solutions to improve the testability and functional safety of AMS designs, with widely varying levels of sophistication. With the increase in testing options and the fact that analog tests are typically costly in terms of resources, the efficiency and coverage of these tests must be carefully considered.

Producing and testing safe and reliable ICs for mission-critical applications is expensive, a motivating reason to try and extend the lifetime of the chip for as long as possible. As feature sizes grow smaller, on-chip components have become more sensitive to aging effects that impede

the goal of long IC lives[4]. Continued efforts to measure, characterize, and model aging effects have increased the reliability of ICs as they approach their end. In a similar manner to in-field BISTs, aging sensors and monitors have been suggested to personally track chip-specific aging to provide closer estimations of the time-to-failure. Like the AMS BISTs, the online sensors need to efficient with their resources to be attractive inclusions.

Like AMS testing, the hardware security field's progress on anticipating attacks to analog circuits has lagged the development of digital circuit countermeasures. Examples of potential analog hardware attacks continue to be sparse, and the cases that have been presented often cannot be adequately defended against with existing methods[5]. Efforts in this field cannot be allowed to stagnate, otherwise it is only a matter of time before adversarial efforts overcome the existing safeguards and a viable attack is conceived.

### **Research Overview**

This dissertation presents a multi-faceted outlook on the challenges involved in integrating an analog circuit into a large-scale mission-critical system and the considerations that must be made for continued safe and reliable operations. Fig. 1.1 illustrates the three-pronged approach taken in this research. The three different factors shown primarily take place at different points of an IC's life. Most steps that need to be taken to secure the circuit happen at the design phase or during production testing. In-field testing using BISTs continuously or periodically scans for randomly occurring faults in the circuit throughout its life. Finally, aging prediction provides data needed for the system to prepare for shutdown at the end of its life. The combination of these approaches effectively supervises the development and function of the circuit from conception to decommissioning.

Figure 1.1. Multi-faceted research thrust for safe and reliable analog circuit function.

### **Organization of Dissertation**

Chapter 2 discusses in-field BIST architectures for AMS circuits and compares their defect coverage, complexity, and relative cost. A PCB capable of injecting faults to test a set of efficient BISTs is presented. Measurements show integration of the simple and efficient analog BISTs into digital test architectures can be done with relative ease. The testability and reliability of circuit additions enabling test are discussed as well as how these modifications to the circuit under test can be improved to continue safe operations.

Chapter 3 reviews the effects of transistor aging and how they reduce reliability of a circuit. The methods for measuring and characterizing bias and temperature instability (BTI) are covered, and the challenges involved with accurately modeling and predicting BTI are discussed. An integrated in-field BTI monitor design and its benefits are presented[6].

Chapter 4 investigates the limitations of existing hardware Trojan classifications and detection methods with respect to security breaches in analog circuits. A survey of analog hardware Trojans to date has been conducted. PAAST Trojans are formally defined and classified to fit within existing hardware Trojan taxonomies. The challenges of analyzing and detecting PAAST Trojans is discussed.

Chapter 5 presents a case study of a PAAST Trojan in a coupled oscillator circuit. The numerous applications of coupled oscillators are reviewed. Details of the oscillator design and the Trojan design are covered. A practical trigger mechanism for this and other PAAST Trojans is discussed. Measurements of the fabricated PAAST Trojan are reported and the implications of the measurements and Trojan effectiveness are analyzed.

Chapter 6 summarizes the contributions and concludes the dissertation.

#### CHAPTER 2. INTEGRATING AMS CIRCUIT TESTS IN ON-CHIP SYSTEMS

Mass production of ICs inevitably results in a few parts being produced with faults. These parts are filtered out of the population during production testing leaving only the functional parts to be sold to customers. These parts will eventually fail too as normal use causes wear on the components within the part. Due to variations in the fabrication process, some parts will contain components that are closer to failure than others. Recording the failures-in-time of a typical part population, the failure rate curve with respect to time will resemble the curve in Fig. 2.1. The relatively high failure rate shortly after production is attributed to latent defects within the parts, where individual component parameters only marginally pass specification. To be clear, the latent defects do not necessarily result in marginal function of the whole part, so the parts with latent defects may not be identified during the production tests. When the parts in question are critical to a mission demanding high reliability, additional tests are performed to weed out latent defects. Burn-in tests typically involve running a part at temperatures and voltages higher than the nominal range for which the part was designed and ran with inputs and functional operations that engineers know will cause maximal degradation at the component level. The purpose of these tests is to cause enough wear on the parts with latent defects such that they fail and can be detected by testing the parts' functions.

Removing the parts with latent defects from the population effectively changes the curve in Fig. 2.1 so that the failure rate of active parts is at its minimum when they are first put to use. The failure rate will steeply increase after a time referred to as the End of Life (EoL) for the part, and this will be discussed further in the next chapter. The period of time between initial deployment to EoL has a low and relatively constant failure rate for the population. In some applications, even infrequent failure of parts can have dire consequences, and further steps must

be taken to mitigate failures. To this end, testing must continue throughout a reliable part's lifetime so that faulty behaviors can be identified and corrected. Sometimes this is done manually by experienced technicians. In power plants, technicians perform periodic maintenance to test and recalibrate the electronic systems that monitor and regulate plant operations. Power plants also employ operators that continuously monitor plant parameters and are trained to identify faults shortly after they occur and take action to keep the plant in the safest condition possible. Typically, there is an on-call staff of technicians available to start repairs on faulty systems when operators identify them as well. This approach requires many man-hours be spent supervising the electronics, and it is not feasible for every application. An additional concern is that some faults cause reactions in the system that are too fast for any person to respond. Quick and catastrophic failures require an automated response to minimize casualties and damage.

Figure 2.1. Typical failure rate of a part population after fabrication.

To initiate an automated response to failure, a system needs a way to diagnose internal faults through self-testing to determine proper operation. The challenge in designing BISTs is the limited resources available to generate test stimuli and sample outputs, especially if the testing method is fully integrated into a single part. To meet budgets for area, power, and other IC resources, designers must create tests that efficiently use measurements from the circuit under test to evaluate its performance.

## **Defect-Oriented Testing**

Since direct measurement of a particular circuit specification is often impractical for a BIST, the tests must instead create responses from which a fault may be inferred. Such tests must be validated to confirm the designer's assumptions about the faulty behavior of the circuit by defining specifications for the BIST. Defect-oriented testing is a validation method used to standardize specifications on a BIST's effectiveness across many test scenarios and circuit types. The basic concept of defect-oriented testing is that the cause of a fault can be isolated to a single defective component in the circuit, and if a circuit with a defect causes a test's results to differ from those of the nominal circuit then the resulting fault can be detected. The definitions of a defect have varied among articles published by members of academia and industry. A proposal for a standard definition of defects and faults as they relate to analog testing was described in [3]: "... a defect is defined as an unexpected permanent change in a circuit element or connection that is not within fabrication specifications for the element; a fault is an unexpected (temporary or permanent) change in a primitive circuit or circuit module that causes it to fail one of its specifications." Companies create a library of likely defects for the defect-oriented testing, then they simulate a test's response to each defect within the library to obtain a metric called the defect coverage, the percentage of defects detected by the test.

Defects that result in a change in a circuit connection by open- or short-circuit are often termed hard defects. Many different hard defects are possible in ICs, like a metal bridge forming between interconnects or pinholes in the dielectric of a MOS transistor. The similarity in effects allows these defects to be collectively modeled by simple schematic changes in a component cell. For example, a popular method for modeling defects in the 3-terminal MOSFET is shown in Fig. 2.2. The open-circuit defects use a high resistance looking into the terminal while the short-circuit defects use a low resistance to connect two terminals. Modeling the defects using schematic changes like in Fig. 2.2 allows for efficient changes to a circuit netlist so that many simulations of the self-test may be run[3], [7], [8]. The defect coverage obtained from the simulation results determines the effectiveness of the test. Some circuits must also consider a parametric defect, which is a defect that changes one or more process parameters of a circuit element[3]. These defects can also be efficiently modeled in a schematic by modifying component cells.

The type of defects included in a library for defect-oriented testing will vary based on the circuit application. For many digital applications that are robust to parametric variations, simulating parametric defects would give unnecessary or redundant information about the self-test. On the other hand, some AMS circuits are extremely sensitive to variations and the simulation of parametric defects is important to validating the test. Ultimately, the goal of defect-oriented testing is to validate a test method using every defect that is likely to cause a fault in a circuit and achieve a high defect coverage. A high defect coverage means the test will detect most faults and improve the reliability and functional safety of the circuit.

Figure 2.2. Modeling hard defects in MOSFETs.

## Analog & Mixed-Signal Design-for-Test (DfT)

Digital signals offer many advantages over analog signals in terms of maintaining the integrity of the information and flexibility in processing. Analog BISTs should have a means to translate the analog signals measured by the tests into a digital format. This is a relatively simple task for DC reference circuits since the most important specification, the static output, can be measured passively by routing the output to an ADC. Other circuits require an input-output response which may require more extensive modifications to the initial architecture to make the circuit testable. In order to select analog blocks to test, a method of digital control should be available in the test to exercise the circuit by a central control unit. The use of digital control signals and simple data converters is essential in analog circuits designed for testability.

DC voltage measurements of circuit nodes give information on how a circuit is biased. Most reference circuits use high-gain feedback to regulate their output to the desired value, and hard defects within the circuit have dramatic effects. For these cases, a low-resolution measurement of the sensitive node conserves a chip's resources while still providing a lot of information about the circuit. A single comparator can be used to indicate if a signal is higher or lower than the reference signal. An even simpler solution would be an inverter whose switching threshold is set at design by its physical size and the supply voltage. Similar approaches are already used for sequencing power management circuits to indicate when the supply voltage is sufficiently high to power the next device, and the method is readily adoptable for power-on testing.

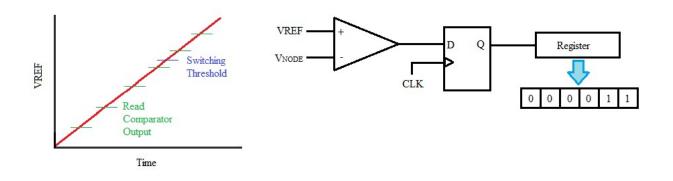

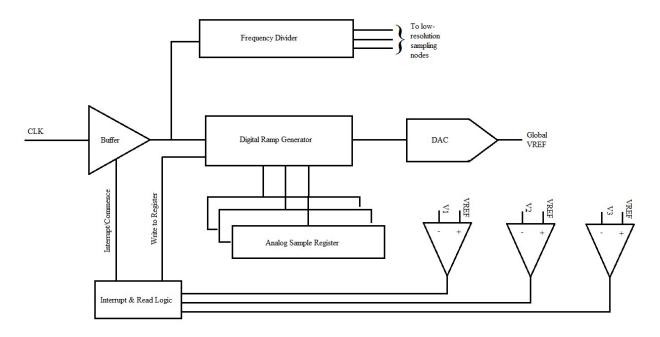

Low-resolution sampling may not be enough to detect parametric defects, though, and tracking the subtle changes in a bias voltage may give clues to impending failure. A more accurate data conversion is required for these cases. Since the cost of in-field testing must remain practical, a test design should use a limited number of high-resolution data converters capable of measuring multiple analog nodes. The legacy method, the Analog Test Bus (ATB), routes analog voltages to a high-resolution ADC to perform the data conversion, and an analog multiplexer addresses which analog signal on the ATB is converted. Reference [9] discussed some of the limitations to this approach, including signal degradation that occurs on long routing paths and the bottleneck of using a multiplexer for conversions, and proposed a different solution. Their concurrent sampling method uses a global ramp reference signal to be compared with various analog node voltages using comparators at each node. The analog measurement is taken when the comparator transitions; noting the time of transition relative to the reference ramp quantifies the measurement, and the number of times the comparator is evaluated during the

ramp signal sets the resolution. The highlight of [9] is the efficiency of test data collection. The sampling resolution is tailored for each analog node to eliminate extraneous data, and the simultaneous measurements combined with compatibility to existing test architectures (IJTAG boundary scan chain) mean that determinations of faults can be made quickly. As was noted previously, reaction time is critical for functional safety.

Another aspect to consider when designing BISTs is the time until availability. For circuits that require a test stimulus and response, the test mode prevents the circuit from performing its normal function. If the circuit under test is the sole signal channel for the system and the system requires its continuous operation, this restricts the available testing time to directly after startup, in which case the test time must be included in the budget for acceptable startup time. Even if the system has redundant channels allowing one channel to be taken offline for testing, the testing time should be limited in case a fault occurs on an operational channel and a quick switchover becomes necessary. A motivating example is a comparison of test methods for evaluating an operational amplifier. The oscillation test method of [10] takes an analog circuit that would normally have a stable equilibrium and introduces feedback components to force oscillation. The defect-free circuit will oscillate at a frequency related to its pole frequencies, so defects will either cause a deviation in oscillation frequency or prevent oscillation altogether. This method has been used to test opamps, active filter, and ADCs with a high coverage for both hard and parametric defects. Generally, frequency measurements on-chip are done by counting the number of cycles in a fixed time interval. This test requires a test time interval dependent on the nominal oscillation frequency and the necessary resolution of the measurement, with higher resolution frequency measurements needing a longer time interval.

Now the oscillation test method for opamps is compared to the intentional offset injection (IOI) test of [11]. The IOI test uses the fact that an operational amplifier has a high gain and only requires a small input magnitude to cause output saturation, and then assumes that many defects will diminish the gain of the amplifier or otherwise fundamentally alter its performance. The example in [11] changes the input-referred offset voltage by effectively skewing the size ratio of the differential input pair through a switched parallel branch, which in turn causes the output to either a high or low voltage depending on the sign of the offset voltage when the differential input voltage is 0 V. The output is converted to a digital signal using a CMOS inverter and produces two bits of information, one bit for the positive offset injection and one for the negative offset injection. Deviation from the nominal truth table indicates a defect. For each half of the IOI test, the maximum time required for testing is the most conservative estimate for how long the defect-free opamp will take to slew from supply rail to the other.

For a given opamp, the IOI test takes significantly less time than oscillation test method. The IOI test also has superior test data consolidation compared to all but the coarsest frequency measurements using the oscillation test method. However, comparisons between the simulations of [10] and [11] indicate that the oscillation test method has a higher defect coverage. The IOI simulations still report a high defect coverage, 95% of the hard defects simulated, and it could be argued that the difference in coverage is negligible compared to the time-savings. But some missions may require the additional confidence provided by the oscillation test method. A possible compromise is to integrate both test methods for the opamp (at the cost of more area) but run the oscillation test less frequently than the IOI test since the majority of defects can be detected by either method.

A similar comparison can be made for two types of low dropout regulator (LDO) BISTs. The use of pseudorandom bit sequences (PRBS) has recently been gaining popularity to infer the impulse response of dynamic systems. The PRBS is used to manipulate voltages or currents in an analog circuit to create an input similar to white noise, then the output of the system is sampled and correlated to the PRBS for the test. This test was used in [12] to find the loaddependent phase margin of a LDO, and it was used in [13] as a defect-oriented test for a LDO. The input bit sequence must be made longer and/or more samples of the output must be taken to improve the accuracy of parameter estimations in this test, which increases both the duration of the test and the amount of data that must be processed. Like the oscillating test method, designers must carefully consider the tradeoff between more information versus shorter test times. The IOI test was used to test a LDO in [14], where the feedback loop was disconnected during testing to achieve the desired open-loop response, and achieved a high coverage of 97.5% for the hard defects considered. Reference [13] reported a higher defect coverage than [14], but the latter report has significant test time savings and needs only two test stimuli and two corresponding output samples for the test, each signal only requiring one digital bit.

BISTs require efficient operation to be a worthwhile inclusion to a system. Designers must consider the likelihood of a fault escaping detection during testing and the consequences of an escape, but overdesigning a BIST also has consequences like limiting a systems performance, and even its safety if resources are diverted from other circuits requiring testing. With this in mind, simple DfT architectures that still have a high defect coverage such as the one used for the IOI test are the best solution for most applications to ensure reliable and safe function.

#### PCB Demonstration & Measurements of Analog DfT Circuits

A proof of concept for digitally controlled analog BISTs was implemented on a PCB using commercial components and means to inject faults in the circuit. The main portion of the

circuits consists of an LDO, a programmable gain amplifier (PGA), and a DAC. The procedure for this experiment is a testing sequence of the analog blocks directly after power-on of the system. An Altera DE2-115 board with the Cyclone IV FPGA was used to send test control signals and read the results of the analog tests.

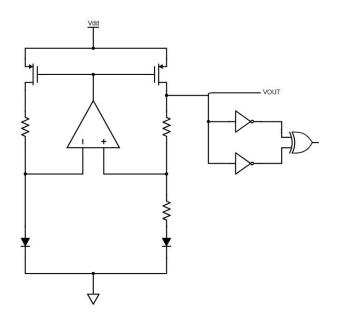

Figure 2.3 Analog test PCB and FPGA board for injecting analog faults and validating BISTs.

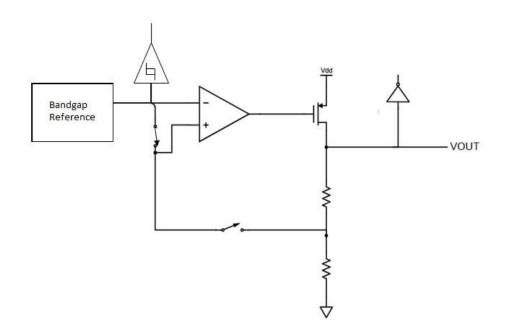

BISTs assume the power supply of the circuit is within a valid range so that the test results are valid. To meet this requirement for subsequent tests, the LDO must be tested before the circuit it powers (the DAC and PGA) can be tested. The LDO output voltage is regulated to a factor of its input reference voltage which also must be verified. The input voltage is usually generated by a bandgap voltage reference so that the input voltage is invariant to temperature changes. The DAC's output cannot be verified before the reference voltage, so a high-resolution sample using the concurrent sampling method of [9] is not possible. However, hard defects disrupt the high-gain feedback paths in reference circuits and often cause significant changes in their outputs. Simulations of the Kuijk bandgap reference in Fig. 2.4 showed that the output voltage deviated from the nominal 1.2 V when hard defects were present, either to a high voltage near the positive supply voltage or to a low voltage near ground. A low-resolution sample of the output using a window comparator is sufficient to test the reference voltage. The comparison window needs to include the nominal output voltage and be sufficiently narrow to exclude voltages that would appear if a defect were present, but the edges of the comparison window do not need to be precisely set to a particular voltage. This relaxes the accuracy requirements of the comparator to the point where the switching thresholds can be set by sizing CMOS logic gates, which eliminates the need for an accurate voltage reference to test the other voltage reference.

Once the input reference voltage is confirmed, the LDO can be tested using the IOI method. The IOI test requires an open-loop response of the opamp, so the feedback path must be broken for testing. The opamp's input must also be set so that its common mode input voltage is within the design range of the circuit and its differential input voltage set to 0 V. The former requirement is met if the bandgap reference voltage is functional as confirmed by the window comparator. The differential input voltage is set to 0 V by closing a switch to connect the inverting and non-inverting input. The response is observed at the output of the LDO. The output is expected to drop to a low voltage near ground when offset forces the opamp output to a high voltage and turns off the pMOS pass transistor. The opposite offset injection is expected to

set the LDO output to a high voltage. The binary response of the test makes a simple CMOS inverter a suitable choice for an observer.

Figure 2.4 Kuijk bandgap reference with window comparator for testing.

A simplified schematic of the LDO configured in test mode is shown in Fig. 2.5. The switches setting the opamp input voltage and disconnecting the feedback loop are digitally controlled by the FPGA board. A select set of faults were manually injected into the voltage reference and LDO circuits by through switches on the FPGA board and mounted on the PCB, then the test response was measured to determine if the faults were detected. The transistor defect models of Fig. 2.2 were considered for the pMOS pass FET. For the bandgap reference, the fault effects were consolidated to three possible outcomes based on where the reference voltage is with respect to the comparison window. The opamp faults were also consolidated to three possible outcomes: normal operation, the output stuck at a high voltage (not responding to

the input), and the output stuck at a low voltage. Tables 2.1 and 2.2 summarize the results of the test.

Figure 2.5 DfT LDO in test mode.

| Table 2.1 | LDO input voltage measurement | ts. |

|-----------|-------------------------------|-----|

|           |                               |     |

|         | Expected | Observed |

|---------|----------|----------|

| < 1.0 V | 0        | 0        |

| > 1.4 V | 0        | 0        |

| 1.2 V   | 1        | 1        |

Table 2.2 LDO IOI test results.

|                    | Negative Offset Injection | Positive Offset Injection |  |

|--------------------|---------------------------|---------------------------|--|

| No fault 0         |                           | 1                         |  |

| Opamp stuck high   | 1                         | 1                         |  |

| Opamp stuck low    | 0                         | 0                         |  |

| Pass FET gate open | 1                         | 1                         |  |

| Table 2.2 | Continued |

|-----------|-----------|

|-----------|-----------|

|                             | Negative Offset Injection | Positive Offset Injection |  |

|-----------------------------|---------------------------|---------------------------|--|

| Pass FET drain open         | 1                         | 1                         |  |

| Pass FET source open        | 1                         | 1                         |  |

| Pass FET drain-gate short   | 1                         | 1                         |  |

| Pass FET source-gate short  | 1                         | 1                         |  |

| Pass FET drain-source short | 0                         | 0                         |  |

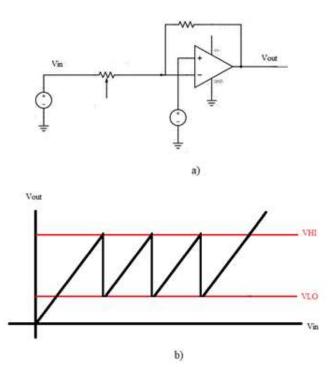

After the LDO and voltage reference are verified functional, the other analog circuits powered and biased by these can be tested. The PGA is next in the sequence of analog tests. The experiment scenario uses the PGA to amplify incoming signals within a desired envelope for sampling and data conversion. This preamplifier increases the sampling resolution for small signals while also preventing amplifier saturation from larger input signals by adjusting the gain of the amplifier. A simplified schematic of the PGA as well as an example of the transfer curve with gain-folding is shown in Fig. 2.6. The gain of the amplifier is adjusted by making parallel resistor connections to the input resistor using digitally controlled switches. Referencing the amplifier's input voltage to the opamp's reference voltage,

$$V_{IN} = V_{REF} + V_{SIGNAL},$$

(2.1)

the output voltage of the amplifier is related to the input voltage by

$$V_{OUT} = V_{REF} - V_{SIGNAL} \frac{R_{FB}}{R_{IN}}.$$

(2.2)

The input resistance is actually the equivalent resistance of n parallelly connected resistors of equal resistance to the feedback resistor,

$$R_{IN} = rac{1}{rac{1}{R_{FB}} + \dots + rac{1}{R_{FB}}} = rac{R_{FB}}{n}.$$

(2.3)

Substituting (2.3) into (2.2) yields

$$V_{OUT} = V_{REF} - nV_{SIGNAL}.$$

(2.4)

The value of *n* is set by a 3-bit binary code. The code 000 is reserved for disabling the amplifier by disconnecting the input voltage to the amplifier. The remaining codes follow the pattern of one code increment resulting in a doubling of the gain, where code 001 relates to n=1 and 111 to n=64.

Figure 2.6 PGA schematic(a) and the amplifier's transfer curve(b).

The PGA needs a way to detect when the output voltage leaves the desired envelope so that the gain can be automatically adjusted. This can be accomplished with a pair of window comparators, one with a narrow window and one with a wide window. The narrow window comparator determines when the output is too small and the gain must be increased, and the wide window comparator detects when the output is too large and the gain must be decreased. These window comparators' outputs along with the gain control code can be used to diagnose faults in the PGA. A given input voltage to the amplifier will have only one gain setting that will appropriately set the output voltage within the desired envelope. If a known input voltage is applied to the amplifier and the digital feedback from the window comparators is disconnected, the response of the PGA can be tested by setting the gain through independent signals and observing the gain adjustment signals.

For example, suppose the appropriate gain setting for the input voltage was n=16. The gain-too-high signal (labeled G2H) sends a logic 1 when the output is outside the wide window indicating the gain should be decreased while the gain-too-low signal (labeled G2L) sends a logic 1 when the output is inside the narrow window indicating the gain should be increased. The fault-free performance of the PGA in this case is described by the truth table of Table 2.3.

The PGA requires only a few input voltages as reference for the test. The valid input voltage range of this PGA includes the power supplies, so the DfT architecture includes a 4-to-1 multiplexer to select 1 of 3 voltages (positive supply, negative supply, or opamp reference voltage) for testing or the input voltage for normal function. Like the IOI test, the PGA BIST completes its tests quickly allowing for faster fault detection and return to service.

| n   | Α | В | С | G2H | G2L |

|-----|---|---|---|-----|-----|

| OFF | 0 | 0 | 0 | 0   | 1   |

| 1   | 0 | 0 | 1 | 0   | 1   |

| 2   | 0 | 1 | 0 | 0   | 1   |

| 4   | 0 | 1 | 1 | 0   | 1   |

| 8   | 1 | 0 | 0 | 0   | 1   |

| 16  | 1 | 0 | 1 | 0   | 0   |

| 32  | 1 | 1 | 0 | 1   | 0   |

| 64  | 1 | 1 | 1 | 1   | 0   |

Table 2.3 Truth table for PGA test when the input voltage requires a gain of 16.

At the satisfactory conclusion of the PGA test, the analog system can be placed into normal service and background testing can commence. The PCB includes a DAC controlled by the FPGA to generate a ramp signal used for concurrent sampling. Three analog voltages derived from LDO were sampled during the testing to demonstrate the method. The authors of [9] use a unary data format for the concurrent sampling method that is illustrated in Fig. 2.7. The authors note that this method becomes inefficient when the DC node sampled requires a higher resolution. Fortunately, most applications will have only a few nodes needing this level of accuracy. This experiment shows an alternative sampling approach that can be used in conjunction with the original method described in [9]. At a given analog node, the comparator output transitions from logic 0 to logic 1 when the reference ramp signal reaches the switching threshold. The rising edge of the comparator output sends an interrupt signal to the clock that increments the digital ramp into the DAC and loads the input code into a register addressed to the analog node. Once the DAC input code is loaded, the ramp recommences. This temporary interruption is transparent to the sampling operation of the other nodes making it possible for a combination of low- and high-resolution samples to be taken concurrently with only a small additional delay of data to the processor. This alternative sampling method is illustrated in Fig. 2.8.

Figure 2.7 Concurrent sampling method using unary data.

Figure 2.8 High-resolution concurrent sampling method.

The analog BISTs and DfT architectures implemented on this board demonstrate that digitally controlled test stimuli and local digitization of analog signals offers a great deal of

flexibility and function for testing the AMS circuits. The simplicity of the tests performed in this experiment makes it easier to integrate these tests into the large test architectures already deployed in digital systems.

## Handling Defects in Test Circuit Components

The inclusion of test input points and observers increases the testability of a circuit, but it also increases the probability of a fault occurring. It is possible for defects to manifest in the components used to test a circuit, such as the switches and comparators described in the previous sections, which can lead to either a misdiagnosis of the condition of the circuit under test or an actual fault in the circuit. Fortunately, there are some simple techniques that can be used to make a circuit hardy to defects in the test components.

Figure 2.9 Bandgap reference circuit with window comparator observer.

Consider the bandgap reference in Fig. 2.9 that uses a window comparator to quantize the output voltage. The nominal output voltage of the reference is 1.22 V and the window edges are set at approximately 1.0 V and 1.4 V. When the reference is operating normally, the window

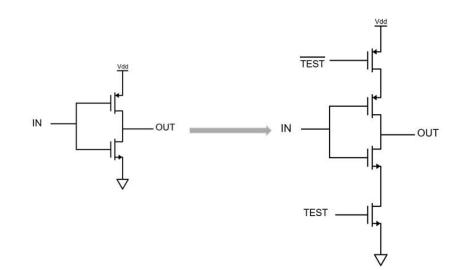

comparator's output is logic 1. The window comparator consists of two inverters and an XOR gate that adds 16 transistors to the circuit. Assuming 6 possible hard defects per transistor, the window comparator has 96 defects that must be considered. Simulations of the circuit after injecting defects into the window comparator only revealed that 8 defects caused faults in the bandgap reference, specifically shorts in the inverters' gates caused the output voltage to deviate. The influence these defects have on the reference can be eliminated by modifying the inverters to be enabled only during testing. Fig. 2.10 shows the inverter modification where the top and bottom transistors enable operation only when the signal TEST is logic 1. The circuit was simulated again with the inverters disabled and no single defect in the window comparator affected the reference's output voltage.

Figure 2.10 Gate modification that prevents observer defects from loading the circuit.

This solution only prevents circuit faults when the observer is disabled, but the circuit becomes vulnerable to observer defects again when the observer is enabled to sample the reference's output. There is also the issue of observer defects that do not affect the circuit under test but misdiagnose its status. Both problems can be addressed with redundancy techniques widely used in digital self-tests. Logic gates with complementary outputs have two valid output combinations: "0 1" or "1 0". Many transistor defects in logic gates cause a gate output to either be stuck high or stuck low, and it is a common practice for defect-oriented tests to only consider these two defects for each logic gate. In a gate with complementary outputs, the stuck high or stuck low defect on one output can result in a forbidden output state of "0 0" or "1 1". Observing one of these forbidden outputs indicates a defect is present, and this principle was used as the self-checking capability for the family of logic gates proposed in [15]. A similar approach can be taken to include defect coverage of the observers used in analog BISTs. The conversion of a single analog voltage to a digital signal requires some of the digital outputs in the observer to be single ended rather than complementary. Defects early in the signal chain where the digital outputs are single ended can cause output errors even when complementary outputs are used later in the signal chain. The use of multiple observers and majority voting can be used to determine which of the observers have valid outputs. Looking back at Fig. 2.9, three window comparators can be connected to the reference's output instead of one for a 2 of 3 voting method. If a defect in one of the window comparators causes its output to be contrary to the circuit under test's condition, its output will differ from the other two window comparators. With majority voting, the two observers that agree are considered functional while the remaining observer is assumed to have a defect. Majority voting further improves the defect coverage of the observers. The redundant observers also solve the issue of a fault occurring when a defective observer is enabled. Activating and sampling the window comparator outputs one at a time ensures the defective comparator is disabled and cannot cause a fault in the circuit under test while the other comparators are performing their evaluations.

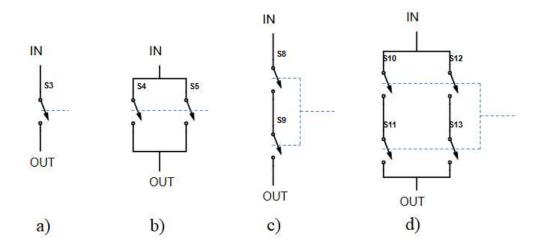

Using redundant components can also benefit the reliability of the test input circuitry. The analog test inputs used to stimulate a circuit under test are enabled using digitally controlled switches. For this discussion, an analog switch is modeled as a single throw switch shown in Fig. 2.11a. This model has two possible defects, stuck ON and stuck OFF. Either of these defects makes a change to the circuit structure that can prevent testing or prevent normal function. The series-parallel connection of multiple component switches to form a single composite switch can ensure continuity of function in the presence of a single defect. In Fig. 2.11b, the composite switch can still be turned OFF even when one of the component switches is stuck ON. In Fig. 2.11c, the composite switch can be turned ON even when one of the component switches is stuck OFF. The composite switch in Fig. 2.11d combines the advantages of Figs. 2.11b and 2.11c and can be turned ON or OFF even when a single defect is present. This method improves the fault resilience of the circuit containing the switch.

Figure 2.11 Switch architectures with varying resiliency to faults.

### **Summary**

In-field AMS testing methods are vital to a mission of safer and more reliable parts. The efficient tests described in this chapter infer proper circuit operations with simple test signals and

sampling techniques that reduce the overhead of expensive precision circuits normally required to test analog systems. Autonomous diagnostics allows fast fault response and system correction for safer and more reliable designs, a critically important feature considering the IC market growth in safety-centric industries. The concept of defect-oriented testing standardizes the benchmarks and goals of BISTs. Handling test coverage at lower levels of abstraction like the opamps, amplifiers, reference circuits, etc. enables many of the test strategies to be transferred to different circuit topologies and process technologies; the agreement between PCB measurements of the analog tests with simulations in different semiconductor technologies effectively demonstrates the transferability.

### **CHAPTER 3. MONITORING AGING WITH ONLINE MEASUREMENTS**

Over the course of part's use, component aging creates parametric defects that increase the probability of failure. The most likely cause of a fault after a part has reached it EoL (the time when failure rate dramatically increases, Fig. 2.2) is from aging; unlike defects that occur at the beginning or middle of a part's life, aging defects have a degree of predictability. Estimating how aging defects evolve and when they will cause a fault is critical to long-term mission planning. Functional safety applications also require a method of detecting faults in order to place the system in a safe condition. Ideally, a system would take action shortly before a fault occurs to prevent system damage. Sensors that track aging and predict trends are needed to determine imminent failure and enact precautionary measures. Among the different aging effects for silicon MOSFETs, bias and temperature instability (BTI) is generally considered the most severe. This chapter covers the cause and effects of BTI and techniques to measure and respond to BTI in integrated circuits.

### **Bias & Temperature Instability**

BTI is the decrease in transconductance of a MOSFET over time caused by strong gate bias voltages and exacerbated by temperature. The decrease in transconductance is attributed to the accumulation of charge carriers in the gate dielectric creating an electric field that opposes channel formation. The most common way of quantifying BTI is through a change in a transistor's threshold voltage, though the mechanism also degrades charge carrier mobility and gate capacitance. The effect is most prominent in pMOS transistors with a largely negative gate bias (NBTI). Early experiments of NBTI dynamics in silicon MOSFETs show a trend consistent with the rate of molecular diffusion in a solid, specifically hydrogen[16]–[18]. Hydrogen is used during fabrication to improve charge carrier mobility in the channel. The interface between the

body of a transistor and its gate dielectric marks an abrupt change in crystalline structure, and the body silicon at the interface is left with "dangling" bonds. The mobility of charge carriers interacting with the dangling bonds is significantly lower compared with the rest of the channel, effectively trapping the charge carriers, so hydrogen is used to passivate the bonds. However, a strong electric field can cause channel holes to displace the hydrogen and the hole becomes trapped. The concentration of free hydrogen at the interface increases as this reaction continues at other sites. At a high enough concentration, hydrogen near the interface will begin to react in the reverse direction and reform some of the passivation bonds. The back reaction limits the net rate of hole trapping. Over time, the hydrogen diffuses away from the dielectric-body interface to equalize the concentration throughout the dielectric. The diffusion process lowers the interface concentration allowing the hole-trapping reaction to continue. The back reaction of hydrogen to passivate traps means that recovery of the threshold voltage is also possible. The hole-trapping rate is also a function of the electric field strength drawing in carriers from the channel. If the gate bias is reduced or removed altogether, the back reaction rate will overcome the hole-trapping rate causing the threshold voltage trend to reverse direction. The reduced hydrogen concentration from the back reaction also causes hydrogen located further in the dielectric to diffuse back towards the interface.

The Reaction-Diffusion model cannot entirely predict NBTI. Fast measurements of NBTI recovery have shown recovery rates faster than a diffusion-based limit on reaction rates[19]. The widely accepted theory for this fast recovery is the existence of permanent defects in the dielectric that trap holes[20], [21]. The interface traps are formed by the displacement of hydrogen by a channel hole, so the trap is immediately occupied after it is formed. In contrast, permanent traps can either be occupied or vacant leading to very different NBTI and recovery

rates as holes are captured or emitted. The implications of fast NBTI recovery by hole emission from permanent traps is that the degradation of threshold voltage is also more significant than the diffusion model prediction for a given interval of time and bias voltage. Permanent traps can originate from flaws in the fabrication process, but it has also been theorized that traps can form from chemical reactions of hydrogen with the dielectric material[22], [23]. These secondary reactions further compound the complexity in accurately predicting NBTI.

BTI can also occur in nMOS transistors with large positive gate bias voltages, which is called PBTI. The nMOS transistor is less sensitive to PBTI than the pMOS is to NBTI, and PBTI has been considered a negligible effect for older processes. Newer processes with smaller feature sizes have exhibited enough PBTI to be significant and worth modeling. The mechanism for PBTI is believed to be similar to NBTI except electrons are the contributing charge carrier. Processes using high-κ metal oxides have been reported to show more significant PBTI, and the suspected cause is a higher number of permanent defects in the metal oxide during fabrication compared to other dielectric materials[24], [25].

Timing faults are usually the primary concern for BTI defects. Reductions in transconductance of switching transistors reduces the current that charges the load capacitors, which lengthens the transitions time. The shift in threshold voltage also means the transistors turn on later with respect to a transitioning input, which increases the propagation delay. This can lead to hold time violations in latches and memory circuits. In addition to the sensitivity of switching circuits to BTI-induced delays, the transistors in these circuits generally degrade faster as well. The charge trapping reaction is related to the strength of the electric field in the dielectric. Switches and digital circuits use the full supply voltage to either turn on or turn off the switch, whereas transistors in analog circuits typically have a much smaller gate bias voltage.

The combination of effects makes high-speed digital communications and memory the most vulnerable circuits for BTI-related faults.

## **Simulating and Measuring BTI**

The rate of BTI varies for different process technologies, feature size, and biasing voltages. Measurements of BTI are necessary to characterize aging in a given process, but the effects of aging usually take years to create a fault when a part is operated within its design constraints. The aging process is accelerated by operating devices at elevated voltages and temperatures so that relevant measurements can be taken in a matter of hours. There are several commonly used measurement techniques to determine the shift in threshold voltage caused by BTI. During the accelerated aging process, measurements of a transistor's drain current while regulating the terminal voltages constant can be used to track the decrease in transconductance. Alternatively, a transistor can be connected such that its gate-source voltage is a function of its drain current and threshold voltage and the drain current is held constant, called a gate-diode connection[26]. The results of these experiments have been used to derive predictive models for BTI using process constants found empirically to fit the theorized equations. Reference [18] found a concise equation to fit experimental results for the generation of interface traps using the Reaction-Diffusion model. This equation was used as the basis for compact equations in [27] to calculate the change in threshold voltage from the trap generation equation.

Compact models like these are commonly used in industry to simulate BTI and other aging effects in their circuits to see if they will reach a target EoL. Compact aging models fail to capture aging behavior for every scenario, though. For example, the equations in [27] used to calculate the threshold voltage are derived from interface trap generation and does not account for the fast capture/emission of charge carriers in permanent traps. Another detail that is often neglected in aging models is the random aspect of the physical process. Theoretical mechanisms supported by experimental measurements show the charge trap formation and charge capture/emission to be stochastic processes creating a variability for BTI[28]–[30].

Companies will typically defer to the simpler deterministic models for simulation, which is understandable considering the complexity of the circuits that require simulation and the multiple combinations of process and operating corners that must be simulated just to see if the circuit will work when it is new. ICs are often conservatively designed with respect to aging so that only a few worst-case scenarios need to be considered. This strategy errs on the side of caution, but there is usually a significant overlap of mission-critical parts and parts that need aging estimates. The mission-critical parts are usually expensive because of the amount of time it takes to thoroughly test them as well as the additional BISTs that need to be integrated into the design for functional safety. Discarding these parts at a conservative estimate of their EoL means that most of the parts are decommissioned long before an aging fault would have occurred, and this is an additional cost to the mission.

Integrated sensors that measure aging in the field can provide a more realistic estimate of when an aging fault will occur for a single part and allow the part to be utilized to its full extent. Instead of directly testing circuit functions like what was described in the last chapter, separate monitors measuring representative devices' aging have been proposed to serve as a type of odometer for the chip. The devices in the monitors are assumed to age similarly to devices in the rest of the circuit, and specifications for warnings or failures are set by the amount of degradation in a critical device (change in threshold voltage for BTI) will cause a fault. Aging sensors may also provide data used to recalibrate systems and extend their life. Many designs have proposed reducing their operating frequency to avoid timing errors caused by BTI. Another

approach is to adjust the body voltage of the pMOS transistors to change their threshold voltages and compensate for NBTI[31], [32].

Most BTI monitors' operations are concisely described by the phrase "stress-measurestress." During stress, the devices in the monitor are biased to cause the desired aging scenario. Measurement requires the monitor to be reconfigured to take measurements determining the amount of BTI incurred. The device bias is usually much less during measurement than it is during stress, so the device will begin to recover from BTI. Most BTI monitors are designed for very short measurement intervals to minimize device recovery, especially from fast charge carrier emissions from permanent traps, to prevent overly optimistic estimates of BTI.

A popular architecture for integrated BTI sensors is an enabled ring oscillator. The enabled ring oscillator using CMOS inverters has alternating stages with low input voltages, which causes NBTI in those stage's pMOS transistors. NBTI causes the running frequency of the oscillator to decrease when it is enabled. Measuring the oscillator's frequency can be accomplished relatively quickly provided it has a high enough running frequency, which makes them attractive choices for measuring BTI before there has been a significant amount of recovery. Reference [33] used a sensor for accelerated aging measurements that compares the frequencies of an aged oscillator and an unaged oscillator. The unaged oscillator is used as a reference to account for variations in frequency due to voltage, temperature, and process parameters, but it also allows for fine measurements of the frequency using the beat frequency produced by the two oscillators. This architecture can be modified for in-field measurements by power gating the reference oscillator to prevent aging, but there are several limitations to this type of sensor.

In processes where PBTI is significant, the nMOS transistor aging will also contribute to the decreasing frequency of the aged oscillator making an NBTI measurement overly pessimistic. Modified ring oscillators that use inter-stage switches to force each inverter input to a low voltage while the oscillator is disabled were described [34] to prevent nMOS PBTI. A similar switch connection was used in [4] to separately analyze the effects of NBTI, hot carrier injection (HCI), and time-dependent dielectric breakdown (TDDB). An alternative approach to reduce the oscillator's sensitivity to PBTI was reported in [35]. Instead of not gates, the oscillator uses alternating NAND and NOR gates as the delay stages. The series connection of pMOS transistors and parallel connection of nMOS transistors in the NOR gate cause an increased delay for a given amount of NBTI and a reduced sensitivity to PBTI. Conversely the NAND gates are more sensitive to PBTI and less sensitive to NBTI. The authors of [35] used different oscillator configurations to separately measure NBTI and PBTI.

Another consideration for accurate BTI measurements is the biasing history. If the aging of transistors in the sensor must closely match the aging of a transistor in a critical path, then the bias conditions should closely match. The enabled ring oscillator just described use the supply voltage to cause aging in the oscillator stages; this is the worst-case bias condition for BTI and can lead to overly pessimistic estimates of aging. This issue was addressed in [36] and [37] by using current-starved ring oscillators. A single transistor with arbitrary gate bias ages similarly to a critical transistor in the circuit, then its BTI decreases the current (and frequency) of the oscillator over time. Reference [37] used a single oscillator whose frequency is first measured when current is supplied by an unaged transistor and then is measured when current is supplied by the aged transistor. This comparison allows frequency deviation from temperature, voltage, and process parameter variations to be considered.

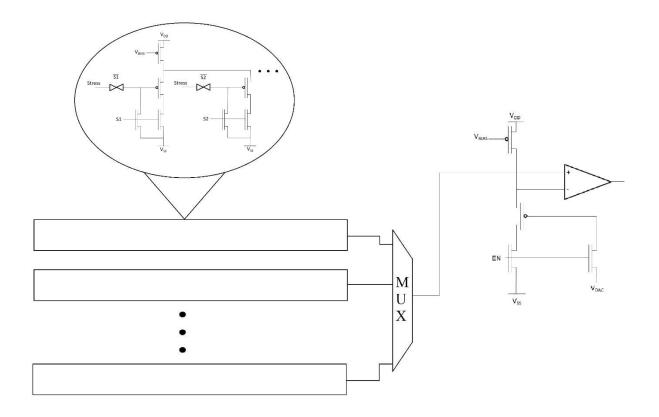

Along with the bias history dependence, the random component of BTI must be accounted for in the sensor design as well. Sampling of the NBTI distribution for experiments in these references show how the standard deviation of the threshold voltage increases with its mean. The simple enabled ring oscillator sensor averages these variations when measuring the frequency and does not provide information on the likely range of BTI that could occur in critical transistor. The current-starved ring oscillator sensors of [36] and [37] have a single aged transistor determining the output, so it is possible to create multiple copies of at least portion of the sensor to sample the BTI distribution.

Sampling the trend of a BTI distribution for part-specific operating conditions improves the estimate of when a fault is likely to occur, but it requires multiple identical devices that are identically biased to perform this measurement. BTI sensors should be compact to facilitate sampling, which was recognized in [37] and [38]. The next section describes a proposed BTI sensor meeting these requirements; additionally, the measurement is more closely related to a transistor's threshold voltage than the frequency measurements previously described.

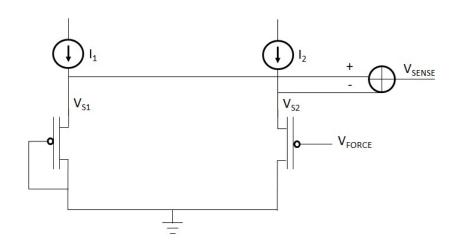

## Monitor for In-Field Statistical Characterization of BTI

The principles of this monitor's operation are as follows. Consider the circuit of Fig. 3.1; the two transistors are of identical size and type and are biased with equal currents, and both are assumed to be in strong inversion and saturated. The square-law model uses the drain current equation

$$I = \frac{1}{2}\beta(V_{SG} + V_T)^2,$$

(3.1)

where the threshold voltage is a negative quantity. Rearranging (3.1) to solve for the source voltage with respect to ground yields

$$V_S = \sqrt{\frac{2I}{\beta}} + V_G - V_T.$$

(3.2)

Now assume that the voltage  $V_{FORCE}$  in Fig. 3.1 is set such that the source voltages of the two transistors are equal. Substituting the appropriate gate voltages for each transistor in (3.2) and equating the source voltages produces the relationship

$$\sqrt{\frac{2I_1}{\beta_1}} - V_{T1} = \sqrt{\frac{2I_2}{\beta_2}} + V_{FORCE} - V_{T2}.$$

(3.3)

Since the transistors are of identical type and size (identical  $\beta$ ) and the bias currents are equal, (3.3) can be simplified and rearranged to

$$V_{FORCE} = V_{T2} - V_{T1} = \Delta V_T.$$

(3.4)

If  $V_{T2}$  remains constant while  $V_{T1}$  decreases due to NBTI then the quantity  $\Delta V_T$  is the amount of NBTI in M1 of Fig. 3.1. Therefore,  $V_{FORCE}$  is equal to the NBTI in M1 when the source voltages are equal.

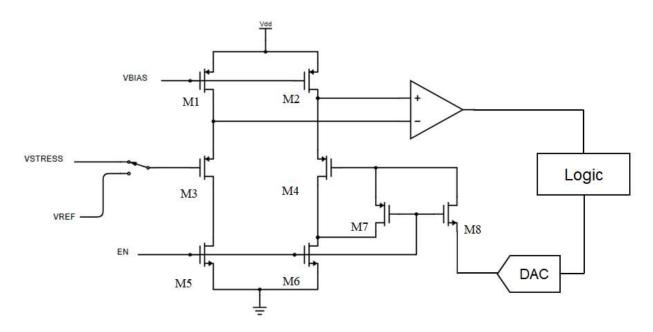

Figure 3.1 Threshold voltage difference circuit.

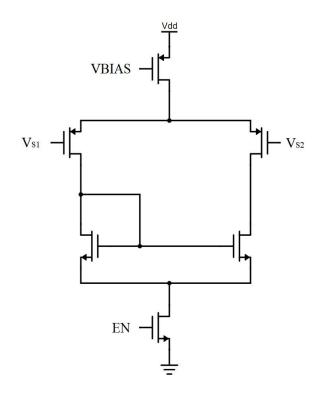

A simplified schematic of the proposed monitor measuring NBTI is shown in Fig. 3.2. The monitor uses the stress-measure-stress type of operation which temporarily interrupts the aging bias using switches to measure BTI. During the stress phase, M5 and M6 act as OFF switches preventing current from flowing in either of the branches. The transistors M1 and M2 operate in strong inversion saturation during the measurement and in the linear region during the stress phase with an almost zero drain-source voltage. This means that the sources of M3 and M4 will be nearly VDD during the stress phase. M4 is diode connected during the stress phase by turning M7 ON and M8 OFF with almost zero current flowing from drain to source, so it will be operating in deep subthreshold with almost zero gate-source voltage. This will mean that M4 will experience no NBTI during the stress phase. M3's gate voltage will be whatever desired stressing voltage the designer chooses, static or dynamic. The architecture allows a designer to choose how various devices under test are biased during stress to best represent devices of interest in the system. During the measurement phase, M5 and M6 are turned ON to allow current to flow in each branch. M3's gate is biased with a static reference voltage such that is operating in strong inversion saturation. M4's gate is biased with the voltage output of a DAC. The measurement operation occurs by searching for the DAC code that will cause the source

voltages of M3 and M4 to be matched. This is done by evaluating the comparator output in a successive approximation algorithm. When the source voltages of M3 and M4 are equal, M1 and M2 will have identical gate-source and drain-source voltages. If M1 and M2 are perfectly matched, then the currents in the M3 and M4 will be identical. At this point, all assumptions required for (3.4) to be valid are met with the DAC's output voltage being  $V_{FORCE}$ . The monitor effectively acts as an aging-to-digital converter where the DAC code is sent off to be processed at the completion of the algorithm.

Figure 3.2 Proposed BTI Monitor.

Fig. 3.2 shows a monitor for measuring NBTI in pMOS transistors, but it is simply modified if it is desired to measure PBTI in nMOS transistors instead. The aged device and unaged device are replaced with the representative nMOS transistors, the current cutoff switches remain on the drain side of the devices being measured, and the current sources remain on the source side of these device with nMOS transistors sinking current instead. Equations similar to (3.1)-(3.4) exist for the nMOS version of the monitor making the relationship of the DAC's output voltage to BTI the same.

# Sizing the Transistors of the Monitor

Referencing the device numbers of Fig. 3.2, the design flow for the monitor is described next. The transistors M3 and M4 are chosen so they are the same size and type of devices as a critical transistor within the circuit that is likely the first to fail due to BTI. M3 and M4 should be in strong inversion during the measurement to improve the signal to noise ratio. The gate-source voltage of M3 is set by its bias current and threshold voltage, so the bias current should be chosen large enough that M3's gate-source voltage exceeds its threshold voltage for the maximum amount of BTI to measured. The current is supplied by M1 and M2, both of which should be biased with a low overdrive voltage to avoid NBTI; otherwise, a random time-varying offset could develop in the monitor. Sizing M1 and M2 with larger aspect ratios lowers their matching. During the measurement phase, M1 and M2 should be in saturation. This is a relatively easy requirement to meet provided the designed overdrive voltage of M3 and reference voltage are not too large. The maximum source voltage of M3/M4 is determined by the maximum aging measured before the part is decommissioned,

$$V_{S(Max)} = V_{REF} + V_{OD,M3/M4} - V_{T(Aged)},$$

(3.5)

where

$$V_{OD} = \sqrt{\frac{2I}{\beta}}.$$

(3.6)

The requirement to maintain M1/M2 in saturation is

$$V_{D,M1/M2} \le VDD - V_{OD,M1/M2}.$$

(3.7)

Substituting (3.5) into (3.7) and rearranging the inequality yields

$$V_{REF} + V_{OD,M3/M4} \le VDD - V_{OD,M1/M2} + V_{T(Aged)}.$$