This is a repository copy of *Dynamic Resource Allocation in Embedded, High-Performance and Cloud Computing*.

White Rose Research Online URL for this paper: https://eprints.whiterose.ac.uk/106984/

Version: Published Version

#### Book:

Soares Indrusiak, Leandro orcid.org/0000-0002-9938-2920, Dziurzanski, Piotr orcid.org/0000-0001-9542-652X and Singh, Amit Kumar (2016) Dynamic Resource Allocation in Embedded, High-Performance and Cloud Computing. River Publishers, Delft, (178pp).

## Reuse

Items deposited in White Rose Research Online are protected by copyright, with all rights reserved unless indicated otherwise. They may be downloaded and/or printed for private study, or other acts as permitted by national copyright laws. The publisher or other rights holders may allow further reproduction and re-use of the full text version. This is indicated by the licence information on the White Rose Research Online record for the item.

#### **Takedown**

If you consider content in White Rose Research Online to be in breach of UK law, please notify us by emailing eprints@whiterose.ac.uk including the URL of the record and the reason for the withdrawal request.

# Dynamic Resource Allocation in Embedded, High-Performance and Cloud Computing

Leandro Soares Indrusiak, Piotr Dziurzanski and Amit Kumar Singh

Dynamic Resource Allocation in Embedded, High-Performance and Cloud Computing

# RIVER PUBLISHERS SERIES IN INFORMATION SCIENCE AND TECHNOLOGY

Series Editors

K. C. CHEN

SANDEEP SHUKLA

National Taiwan University Taipei, Taiwan

Virginia Tech USA

#### CHRISTOPHE BOBDA

University of Arkansas USA

The "River Publishers Series in Information Science and Technology" covers research which ushers the 21st Century into an Internet and multimedia era. Multimedia means the theory and application of filtering, coding, estimating, analyzing, detecting and recognizing, synthesizing, classifying, recording, and reproducing signals by digital and/or analog devices or techniques, while the scope of "signal" includes audio, video, speech, image, musical, multimedia, data/content, geophysical, sonar/radar, bio/medical, sensation, etc. Networking suggests transportation of such multimedia contents among nodes in communication and/or computer networks, to facilitate the ultimate Internet.

Theory, technologies, protocols and standards, applications/services, practice and implementation of wired/wireless networking are all within the scope of this series. Based on network and communication science, we further extend the scope for 21st Century life through the knowledge in robotics, machine learning, embedded systems, cognitive science, pattern recognition, quantum/biological/molecular computation and information processing, biology, ecology, social science and economics, user behaviors and interface, and applications to health and society advance.

Books published in the series include research monographs, edited volumes, handbooks and textbooks. The books provide professionals, researchers, educators, and advanced students in the field with an invaluable insight into the latest research and developments.

Topics covered in the series include, but are by no means restricted to the following:

- Communication/Computer Networking Technologies and Applications

- Queuing Theory

- Optimization

- Operation Research

- Stochastic Processes

- Information Theory

- Multimedia/Speech/Video Processing

- Computation and Information Processing

- Machine Intelligence

- Cognitive Science and Brian Science

- Embedded Systems

- Computer Architectures

- Reconfigurable Computing

- Cyber Security

For a list of other books in this series, www.riverpublishers.com

# Dynamic Resource Allocation in Embedded, High-Performance and Cloud Computing

**Leandro Soares Indrusiak**

Piotr Dziurzanski

**Amit Kumar Singh**

Published, sold and distributed by: River Publishers Alsbjergvej 10 9260 Gistrup Denmark

River Publishers Lange Geer 44 2611 PW Delft The Netherlands

Tel.: +45369953197 www.riverpublishers.com

ISBN: 978-87-93519-08-4 (Hardback) 978-87-93519-07-7 (Ebook)

©2016 Leandro Soares Indrusiak, Piotr Dziurzanski and Amit Kumar Singh

Cover design by Andrea Monteiro and Leandro Soares Indrusiak

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, mechanical, photocopying, recording or otherwise, without prior written permission of the authors.

# **Contents**

| Pı | reface   | :             |                                             | xi    |

|----|----------|---------------|---------------------------------------------|-------|

| A  | cknov    | vledgen       | ients                                       | xiii  |

| Li | ist of F | igures        |                                             | XV    |

| Li | ist of T | <b>Tables</b> |                                             | xix   |

| Li | ist of A | Algorith      | ims                                         | xxi   |

| Li | ist of A | bbrevi        | ations                                      | xxiii |

| 1  | Intr     | oductio       | on                                          | 1     |

|    | 1.1      | Applic        | cation Domains                              | . 2   |

|    | 1.2      | Relate        | ed Work                                     | . 4   |

|    |          | 1.2.1         | Allocation Techniques for Guaranteed        |       |

|    |          |               | Performance                                 | . 4   |

|    |          | 1.2.2         | Allocation Techniques for Energy-efficiency |       |

|    | 1.3      | Challe        | enges                                       | . 7   |

|    |          | 1.3.1         | Load Representation                         | . 7   |

|    |          | 1.3.2         | Monitoring and Feedback                     | . 8   |

|    |          | 1.3.3         |                                             |       |

|    |          | 1.3.4         | Distributed Allocation                      | . 9   |

|    |          | 1.3.5         | Value-based Allocation                      | . 9   |

| 2  | Loa      | d and F       | Resource Models                             | 11    |

|    | 2.1      | Relate        | ed Work                                     | . 12  |

|    | 2.2      | Requi         | rements                                     | . 13  |

|    |          | 2.2.1         | Requirements on Modelling Load Structure    | . 13  |

|    |          |               | 2.2.1.1 Singleton                           |       |

|    |          |               | 2.2.1.2 Independent jobs                    | . 14  |

|     |         | 2.2.1.3                                                                                                      | Single-dependency jobs 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|---------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |         | 2.2.1.4                                                                                                      | Communicating jobs 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |         | 2.2.1.5                                                                                                      | Multi-dependency jobs 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     | 2.2.2   | Requirer                                                                                                     | nents on Modelling Load Temporal                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |         | Behavior                                                                                                     | ur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |         | 2.2.2.1                                                                                                      | Single appearance 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |         | 2.2.2.2                                                                                                      | Strictly periodic 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |         | 2.2.2.3                                                                                                      | Sporadic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |         | 2.2.2.4                                                                                                      | Aperiodic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |         | 2.2.2.5                                                                                                      | Fully dependent 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |         | 2.2.2.6                                                                                                      | N out of M dependent 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 2.2.3   | Requirer                                                                                                     | nents on Modelling Load Resourcing                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     |         | Constrai                                                                                                     | nts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |         | 2.2.3.1                                                                                                      | Untyped job 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |         | 2.2.3.2                                                                                                      | Single-typed job 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |         | 2.2.3.3                                                                                                      | Multi-typed job 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | 2.2.4   | Requirer                                                                                                     | nents on Modelling Load                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |         | Characte                                                                                                     | risation 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |         | 2.2.4.1                                                                                                      | Fixed load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |         | 2.2.4.2                                                                                                      | Probabilistic load 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |         | 2.2.4.3                                                                                                      | Typed fixed load 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |         | 2.2.4.4                                                                                                      | Typed probabilistic load 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2.3 | An Inte |                                                                                                              | bra for Load and Resource Modelling 17                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 2.3.1   | Modellir                                                                                                     | ng Load Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 2.3.2   | Modellir                                                                                                     | ng Load Temporal Behaviour 19                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | 2.3.3   | Modellir                                                                                                     | ng Load Resourcing Constraints 20                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 2.3.4   | Modellir                                                                                                     | ng Load Characterisation                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     | 2.3.5   | Stochast                                                                                                     | ic Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2.4 | Summ    | ary                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |         |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|     |         |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.1 |         |                                                                                                              | nd Problem Formulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |         |                                                                                                              | Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2.2 |         |                                                                                                              | ion Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |         |                                                                                                              | back Control Real-Time Allocation 27                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3.3 | _       |                                                                                                              | sults                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|     |         |                                                                                                              | er Tuning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |         |                                                                                                              | ests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     | 3.3.3   | Kandom                                                                                                       | Workloads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     | 2.4     | 2.2.3  2.2.4  2.3.1  2.3.2  2.3.3  2.3.4  2.3.5  2.4 Summ  Feedback-B  3.1 System  3.1.1  3.1.2  3.2 Distrib | 2.2.1.4 2.2.1.5 2.2.2 Requirer Behavior 2.2.2.1 2.2.2.2 2.2.2.3 2.2.2.4 2.2.2.5 2.2.2.6 2.2.3 Requirer Constrair 2.2.3.1 2.2.3.2 2.2.3.3 2.2.4 Requirer Characte 2.2.4.1 2.2.4.2 2.2.4.3 2.2.4.4 2.3 An Interval Alge 2.3.1 Modellir 2.3.2 Modellir 2.3.2 Modellir 2.3.3 Modellir 2.3.4 Modellir 2.3.4 Modellir 2.3.5 Stochast 2.4 Summary  Feedback-Based Adn 3.1 System Model an 3.1.1 Platform 3.1.2 Applicat 3.2 Distributed Feed 3.3 Experimental Ref 3.3.1 Controlle 3.3.2 Stress Te |

|   |             |             | Conte                                             | nts vii |

|---|-------------|-------------|---------------------------------------------------|---------|

|   | 3.4         | Dvnam       | nic Voltage Frequency Scaling                     | . 35    |

|   | 3.5         |             | ng Controllers to Steer DVFS                      |         |

|   | 3.6         |             | mental Results                                    |         |

|   |             | 3.6.1       | Controller Tuning                                 |         |

|   |             | 3.6.2       | Random Workloads                                  |         |

|   | 3.7         | · · · · · - | d Work                                            |         |

|   | 3.8         |             | ary                                               |         |

| 4 | Feed        | back-B      | ased Allocation and Optimisation                  |         |

|   | Heu         | ristics     |                                                   | 51      |

|   | 4.1         | System      | Model and Problem Formulation                     | . 52    |

|   |             | 4.1.1       | Application Model                                 | . 53    |

|   |             | 4.1.2       | Platform Model                                    | . 53    |

|   |             | 4.1.3       | Problem Formulation                               | . 54    |

|   | 4.2         | Perform     | ming Runtime Admission Control and Load Balancing | g       |

|   |             |             | e with Dynamic Workloads                          | _       |

|   | 4.3         |             | mental Results                                    |         |

|   |             | 4.3.1       | Number of Executed Tasks, Rejected Tasks          |         |

|   |             |             | and Schedulability Tests                          | . 60    |

|   |             |             | 4.3.1.1 Periodic workload                         |         |

|   |             |             | 4.3.1.2 Random workload                           | . 62    |

|   |             | 4.3.2       | Dynamic Slack, Setpoint and Controller Output     |         |

|   |             |             | 4.3.2.1 Periodic workload                         |         |

|   |             |             | 4.3.2.2 Light workload                            |         |

|   |             | 4.3.3       | Core Utilization                                  |         |

|   |             | 4.3.4       | Case Study: Industrial Workload Having            |         |

|   |             |             | Dependent Jobs                                    | . 68    |

|   | 4.4         | Related     | d Work                                            |         |

|   | 4.5         |             | ary                                               |         |

| 5 | Sear        | ch-Base     | ed Heuristics for Modal Application               | 73      |

|   | 5.1         |             | Model and Problem Formulation                     | . 74    |

|   |             |             | Application Model                                 |         |

|   |             | 5.1.2       | Platform Model                                    |         |

|   |             | 5.1.3       | Problem Formulation                               |         |

|   | 5.2         |             | ed Approach                                       |         |

| , | J. <b>_</b> | 5.2.1       | Mode Detection/Clustering                         |         |

|   |             | 5.2.2       | Spanning Tree Construction                        |         |

|   |             | 5.2.3       | Static Mapping for Initial Mode                   |         |

|   |      | 5.2.4    |             | pping for Non-Initial Modes             | 82  |

|---|------|----------|-------------|-----------------------------------------|-----|

|   |      | 5.2.5    |             | pility Analysis for Taskset During      |     |

|   |      |          |             | anges                                   | 84  |

|   |      | 5.2.6    |             | Steps                                   | 90  |

|   | 5.3  |          |             |                                         | 91  |

|   | 5.4  | Summ     | ary         |                                         | 93  |

| 6 |      |          | _           | gorithms for Dynamic Task               |     |

|   |      | llocatio | <del></del> |                                         | 95  |

|   | 6.1  | Systen   |             | d Problem Formulation                   | 96  |

|   |      | 6.1.1    |             | del                                     | 96  |

|   |      | 6.1.2    |             | Model                                   | 98  |

|   |      | 6.1.3    |             | Statement                               | 98  |

|   | 6.2  |          |             | ce for Resource Management              | 99  |

|   |      | 6.2.1    |             | romone Signalling Algorithm             | 99  |

|   |      | 6.2.2    |             | Pheromone Signalling Supporting Load    |     |

|   |      |          |             | ıg                                      | 102 |

|   | 6.3  | Evalua   |             |                                         | 108 |

|   |      | 6.3.1    |             | nt Design                               | 108 |

|   |      |          | 6.3.1.1     | Metrics                                 | 109 |

|   |      |          | 6.3.1.2     | Baseline Remapping Techniques           | 110 |

|   |      | 6.3.2    | •           | ntal Results                            | 110 |

|   |      |          | 6.3.2.1     | Comparison between clustered approaches | 110 |

|   |      |          | 6.3.2.2     | Comparison regarding video processing   | 110 |

|   |      |          | 0.3.2.2     | performance                             | 111 |

|   |      |          | 6.3.2.3     | Comparison regarding communication      | 111 |

|   |      |          | 0.3.2.3     |                                         | 112 |

|   |      |          | 6.3.2.4     | overhead                                | 112 |

|   |      |          | 0.3.2.4     | Comparison regarding processor          | 113 |

|   |      | 6.3.3    | Outlook     | utilisation                             | 115 |

|   | 6 1  |          |             |                                         | 116 |

|   | 6.4  | Sullilli | ary         |                                         | 110 |

| 7 | Valu |          | d Allocatio |                                         | 119 |

|   | 7.1  | Systen   |             | d Problem Formulation                   | 120 |

|   |      | 7.1.1    | Many-Co     | re HPC Platform Model                   | 120 |

|   |      | 7.1.2    | Job Mode    | 1                                       | 121 |

|   |      | 7.1.3    | Value Cur   | rve of a Job                            | 121 |

|   |      | 7.1.4    | Energy Co   | onsumption of a Job                     | 122 |

|   |      | 715      | Problem I   | Formulation                             | 122 |

|          |                              |                       | Contents | ix  |

|----------|------------------------------|-----------------------|----------|-----|

| 7.2      | The Solution                 |                       |          | 123 |

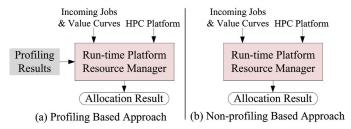

|          | 7.2.1 Profiling Based Appro  | each (PBA)            |          | 123 |

|          | 7.2.2 Non-profiling Based A  | Approach (NBA)        |          | 125 |

| 7.3      | Evaluations                  |                       |          | 128 |

|          | 7.3.1 Experimental Baseline  | es                    |          | 129 |

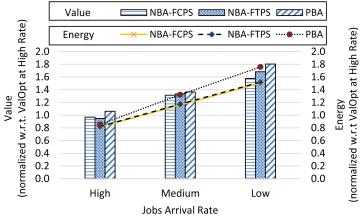

|          | 7.3.2 Value and Energy Con   | sumption at Different |          |     |

|          | Arrival Rates                |                       |          | 130 |

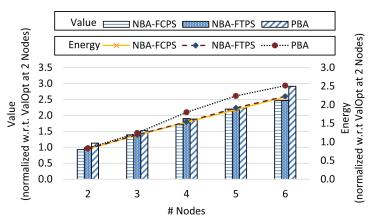

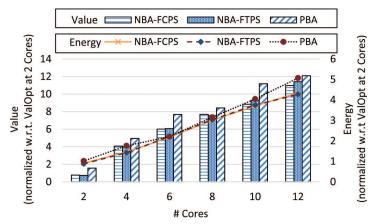

|          | 7.3.3 Value and Energy Con   | sumption with Varying |          |     |

|          | Number of Nodes              |                       |          | 131 |

|          | 7.3.4 Value and Energy Cor   | sumption with Varying |          |     |

|          | Number of Cores in E         | ach Node              |          | 131 |

|          | 7.3.5 Percentage of Rejected | d Jobs                |          | 132 |

| 7.4      | Related Works                |                       |          | 133 |

| 7.5      | Summary                      |                       |          | 134 |

| Referen  | References                   |                       |          | 135 |

| About th | About the Authors 15         |                       |          |     |

# **Preface**

The availability of many-core computing platforms enables a wide variety of technical solutions for systems across the embedded, high-performance and cloud computing domains. However, large scale many-core systems are notoriously hard to optimise. Choices regarding resource allocation alone can account for wide variability in timeliness and energy dissipation (up to several orders of magnitude). This book covers dynamic resource allocation heuristics for many-core systems, aiming to provide appropriate guarantees on performance and energy efficiency. It addresses different types of systems, aiming to harmonise the approaches to dynamic allocation across the complete spectrum between systems with little flexibility and strict performance guarantees all the way to highly flexible systems with soft performance guarantees.

Resource allocation is one of the most complex problems in large multiprocessor and distributed systems, and in general it is considered NP-hard. The theoretical evidence shows that the number of possible allocations of application tasks grows exponentially with the increase of the number of processing cores. The empirical evidence points in the same direction, with case studies showing that for a realistic multiprocessor embedded system (40–60 application components, 15–30 processing cores) a well-tuned search algorithm had to statically evaluate hundreds of thousands of distinct allocations before it finds one that meets the systems performance requirements.

In this book, we argue that the only way to cope with such complexity is to design systems that are capable to explore the allocation space during runtime. This is commonly done in cloud and high-performance computing, mainly because the workload of such systems cannot be accurately predicted in advance and static allocations are thus impossible. In embedded systems, the workload is more predictable in terms of its worst-case behaviour, but static allocations that take such characterisation into account tend to produce underutilised platforms. We therefore set the scene for dynamic resource allocation mechanisms by identifying and evaluating allocation heuristics that can be used to provide different levels of performance guarantees, and that cope with different levels of dynamism on the application workload.

The book starts with a description of the common practices and challenges in dynamic resource allocation, highlighting the peculiarities of each domain: embedded, HPC and cloud computing. Then, each of the challenges is addressed in detail within the following chapters, which are largely self-contained and therefore can be read in any order. To facilitate understanding, all of them follow the same structure: a specific challenge is motivated and the respective problem is precisely formulated; a detailed description of a solution to the problem is then given, followed by experimental work showing quantitative evidence of the strengths and weaknesses of that solution; related work is reviewed; and a summary of the chapter is given at the end.

The technical work that resulted in this book was done within the frame of the DreamCloud project, and the project website<sup>1</sup> makes available a number of reference implementations of the models and heuristics described here. Updates to this book will also be made available on that website.

Leandro Soares Indrusiak, Piotr Dziurzanski, and Amit Kumar Singh,

York, summer of 2016.

<sup>&</sup>lt;sup>1</sup>http://www.dreamcloud-project.org

# **Acknowledgements**

The research work that resulted in this book was done within the frame of the DreamCloud project, funded by the European Commission under Framework Programme 7 (Ref. 611411). The authors would like to acknowledge and thank the commission for the funding, as well as the project officers and reviewers for their suggestions and feedback on the project outcomes.

The authors would like to thank Hashan Roshantha Mendis, whose work provided most of the foundations and the experimental results reported in Chapter 6.

The authors would also like to thank all the members of the DreamCloud consortium, particularly Scott Hansen, Björn Saballus, Devendra Rai, Manuel Selva, Abdoulaye Gamatié, Gilles Sassatelli, Luciano Copello Ost, Leonardo Zordan, David Novo, Alexey Cheptsov, Dennis Hoppe, Thomas Baumann, Fridtjof Siebert, Malek Ben Salen, Raj Patel, José Miguel Montañana and Neil Audsley.

# **List of Figures**

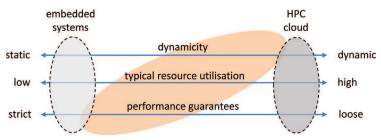

| Figure 1.1    | Application domains and their characteristics with regard to dynamicity, resource utilisation and |    |

|---------------|---------------------------------------------------------------------------------------------------|----|

|               | performance predictability                                                                        | 3  |

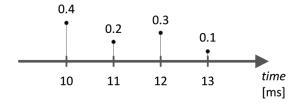

| Figure 2.1    | Example of a probability mass function of a                                                       | J  |

| 116416 2.1    | discrete random variable describing a job's                                                       |    |

|               | execution time.                                                                                   | 23 |

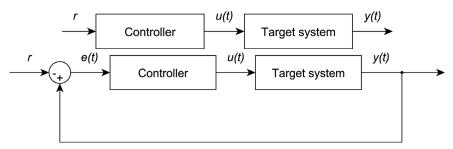

| Figure 3.1    | Block diagrams of control system architectures:                                                   | 23 |

| 116010011     | feed-forward ( <i>above</i> ) and feedback ( <i>below</i> )                                       | 26 |

| Figure 3.2    | Distributed feedback control real-time allocation                                                 | 20 |

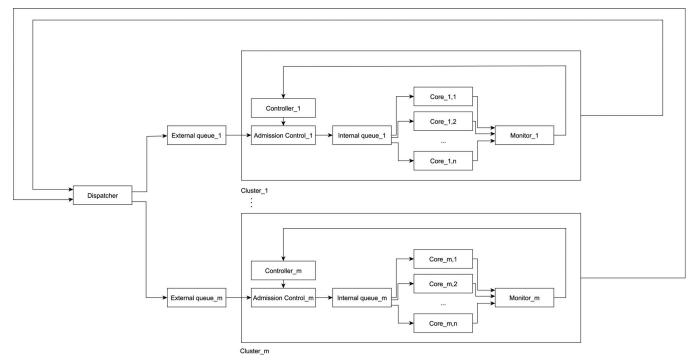

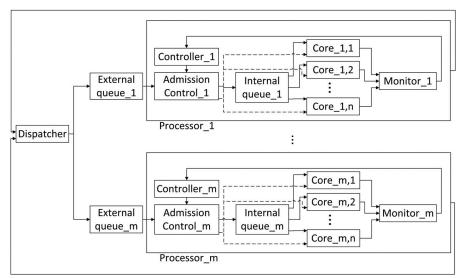

| 1 igure 3.2   | architecture                                                                                      | 28 |

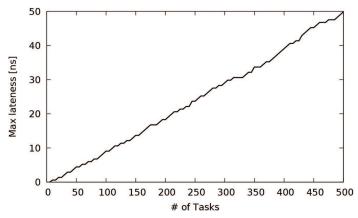

| Figure 3.3    | Maximum normalised task lateness (with execution                                                  | 20 |

| 1 iguite oile | time equal to 50,000 ns) in step responses for a                                                  |    |

|               | number of tasks (3 clusters, 3 cores in each)                                                     | 30 |

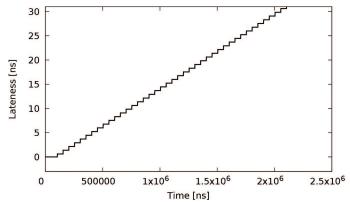

| Figure 3.4    | Maximum normalised task lateness step response for                                                | 50 |

| 1 iguit o i i | 500 tasks (with execution time equal to 50,000 ns)                                                |    |

|               | released at 5,000 ns (3 clusters, 3 cores in each)                                                | 31 |

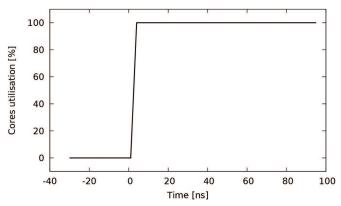

| Figure 3.5    | Cores utilisation step response for 500 tasks (with                                               | 51 |

| 1 iguite oic  | execution time equal to 50,000 ns) released at 0 ns                                               |    |

|               | (1 cluster with 3 cores)                                                                          | 31 |

| Figure 3.6    | Core utilisation measured during the first 500 ns                                                 | 51 |

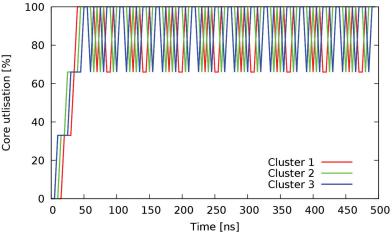

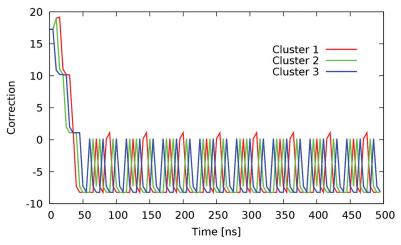

| rigure 5.0    | of the simulation.                                                                                | 33 |

| Figure 3.7    | Control signal observed during the first 500 ns of the                                            | 33 |

| i iguit ett   | simulation                                                                                        | 34 |

| Figure 3.8    | Distributed feedback control real-time allocation                                                 | ٥. |

|               | with DVFS architecture                                                                            | 37 |

| Figure 3.9    | Pseudo-code of the proposed admission controller                                                  | 5, |

|               | functionality.                                                                                    | 39 |

| Figure 3.10   | Tasks executed before their deadline in random                                                    |    |

|               | workload scenarios for DVFS with $\Gamma = 50$ ms (red),                                          |    |

|               | $\Gamma=300~{ m ms}$ (green) and $\Gamma=\infty$ (blue) – three                                   |    |

|               | processors with three cores (top) and two processors                                              |    |

|               | with four cores (bottom) systems                                                                  | 43 |

|               |                                                                                                   | _  |

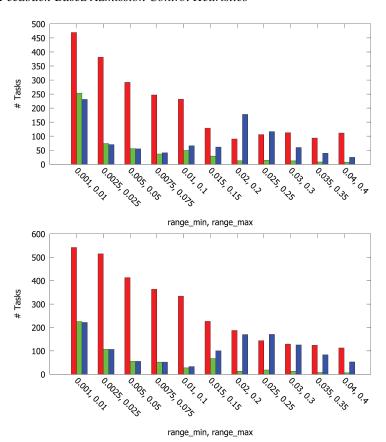

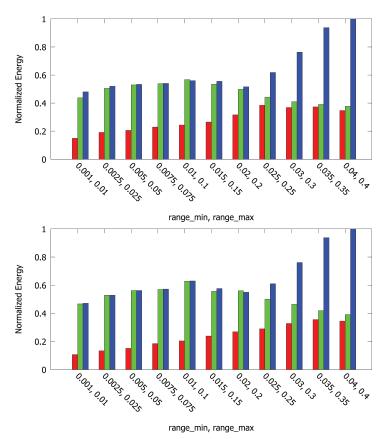

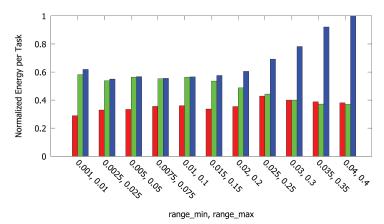

| Figure 3.11 | Tasks rejected in random workload scenarios for DVFS with $\Gamma=50$ ms (red), $\Gamma=300$ ms (green) and $\Gamma=\infty$ (blue)—three processors with three cores (top) and two processors with four cores (bottom)                                                                                         |    |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.12 | systems                                                                                                                                                                                                                                                                                                        | 44 |

| Figure 3.13 | with four cores (bottom) systems                                                                                                                                                                                                                                                                               | 45 |

|             | (green) and $\Gamma = \infty$ (blue)                                                                                                                                                                                                                                                                           | 46 |

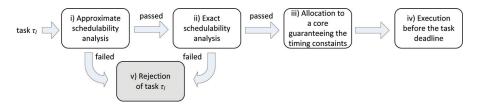

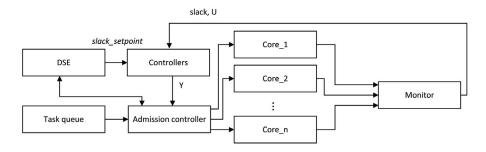

| Figure 4.1  | Building blocks of the proposed approach                                                                                                                                                                                                                                                                       | 53 |

| Figure 4.2  | A proposed many-core system architecture                                                                                                                                                                                                                                                                       | 53 |

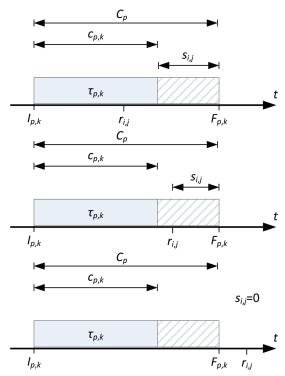

| Figure 4.3  | Illustration of task $\tau_{i,j}$ slack in three cases from                                                                                                                                                                                                                                                    | 33 |

| rigure no   | Equation (4.1)                                                                                                                                                                                                                                                                                                 | 55 |

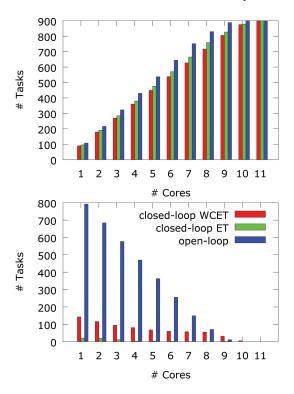

| Figure 4.4  | Number of executed tasks (top) and number of tasks rejected by the exact schedulability test (bottom) in closed-loop WCET, closed-loop ET and open-loop systems for the periodic task workload simulation                                                                                                      | 33 |

|             | scenario                                                                                                                                                                                                                                                                                                       | 61 |

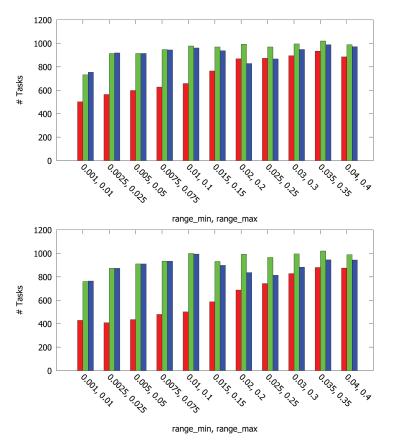

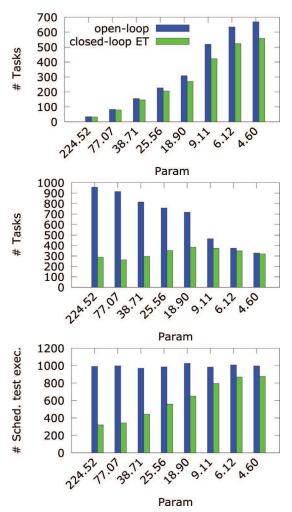

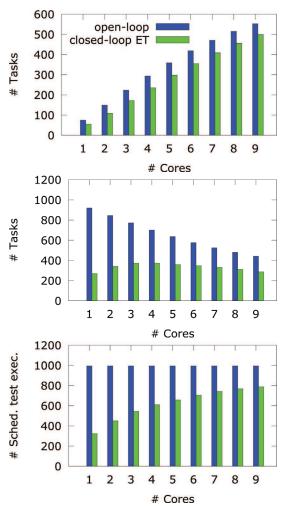

| Figure 4.5  | Number of tasks executed before their deadlines (top), the number of rejected tasks (centre) and number of the exact schedulability test executions (bottom) in baseline open-loop and proposed closed-loop ET systems for the random workloads simulation scenario with different weight of                   | 01 |

|             | workloads                                                                                                                                                                                                                                                                                                      | 63 |

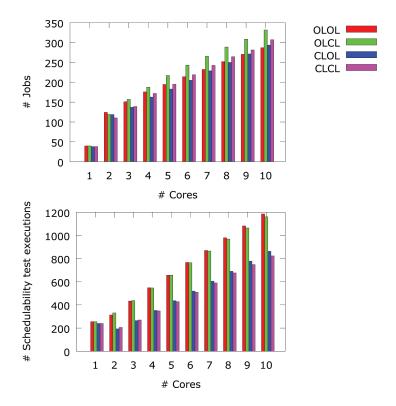

| Figure 4.6  | Number of tasks executed before their deadlines (top), the number of rejected tasks (centre) and number of the exact schedulability test executions (bottom) in baseline open-loop and proposed closed-loop ET systems with different number of processing cores for the random workloads simulation scenario. | 64 |

|             | SIIIIUIAUUII SCEIIAIIO                                                                                                                                                                                                                                                                                         | 04 |

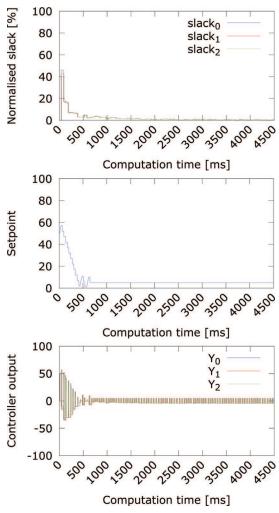

| Figure 4.7  | Dynamic slack ( <i>top</i> ), setpoint ( <i>centre</i> ) and controller output ( <i>bottom</i> ) during the simulation for the periodic task workload simulation scenario executed |     |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.8  | by a 3 core system                                                                                                                                                                 | 65  |

| Figure 4.9  | executed by a 3 core system                                                                                                                                                        | 67  |

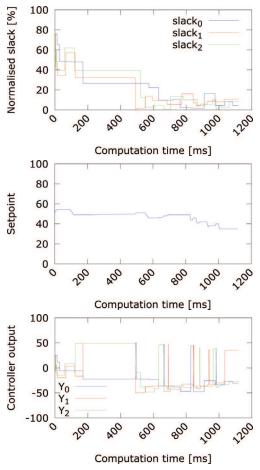

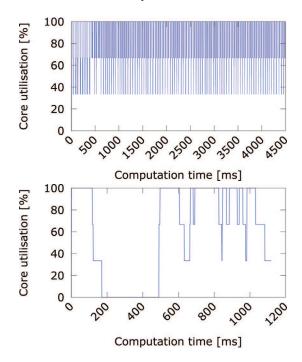

| Figure 4.10 | simulation scenario with 3 core system                                                                                                                                             | 68  |

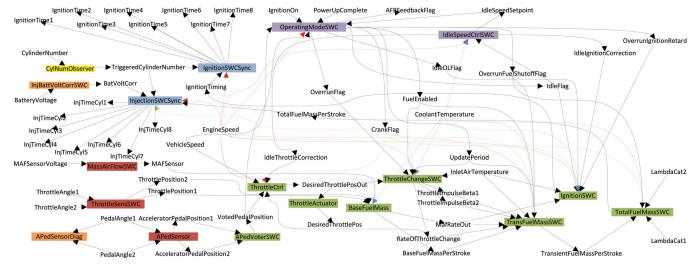

| Figure 5.1  | workloads simulation scenario                                                                                                                                                      | 69  |

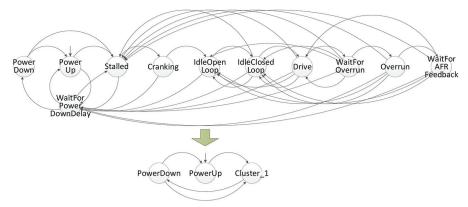

| Figure 5.2  | are drawn in different colours for readability Finite State Machine describing mode changes in DemoCar use case: before ( <i>upper part</i> ) and after                            | 76  |

|             | (lower part) the clustering step                                                                                                                                                   | 77  |

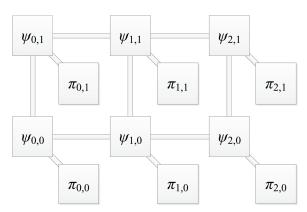

| Figure 5.3  | An example many-core system platform                                                                                                                                               | 77  |

| Figure 5.4  | Steps of dynamic resource allocation method                                                                                                                                        |     |

| 8           | benefiting from modal nature of applications                                                                                                                                       | 78  |

| Figure 5.5  | Spanning tree construction for DemoCar                                                                                                                                             | 80  |

| Figure 5.6  | Example of two different mappings $(m_{\alpha}, m_{\beta})$                                                                                                                        |     |

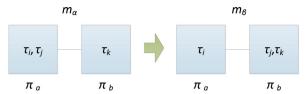

| <b>_</b>    | of runnables $\tau_i$ , $\tau_j$ , $\tau_k$ into cores $\pi_a$ and $\pi_b$                                                                                                         | 85  |

| Figure 5.7  | Tasks' stages in DemoCar: green – runnable                                                                                                                                         |     |

| 8           | execution, red – write to labels; release times and                                                                                                                                |     |

|             | deadlines are provided in ms                                                                                                                                                       | 86  |

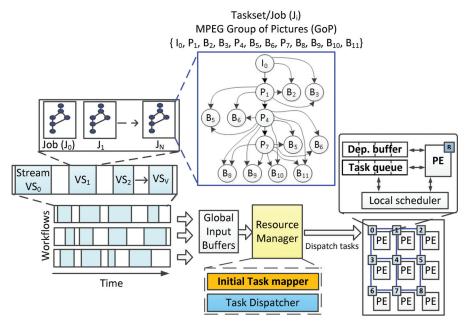

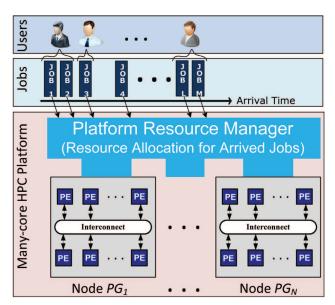

| Figure 6.1  | System overview diagram                                                                                                                                                            | 97  |

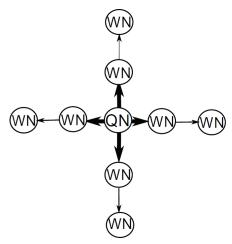

| Figure 6.2  | PS pheromone propagation                                                                                                                                                           | 102 |

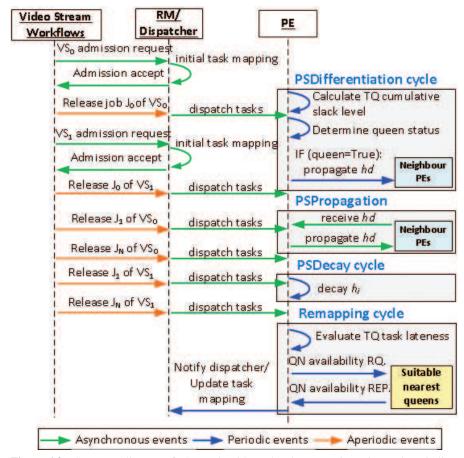

| Figure 6.3  | Sequence diagram of PSRM algorithm related                                                                                                                                         |     |

| <b>9</b> ** | events. Time triggered (periodic): <i>PSDifferentiation</i> ,                                                                                                                      |     |

|             | PSDecay and Remapping cycles; Event triggered:                                                                                                                                     |     |

|             | PSPropagation                                                                                                                                                                      | 106 |

# xviii List of Figures

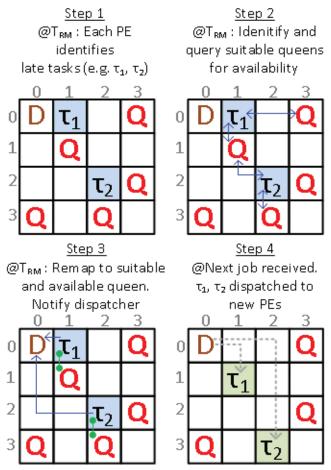

| Figure 6.4            | Task remapping example. (Q = queen nodes; D = Dispatcher; $[\tau_1, \tau_2]$ are late tasks; Blue lines |     |

|-----------------------|---------------------------------------------------------------------------------------------------------|-----|

|                       | represent communication                                                                                 | 107 |

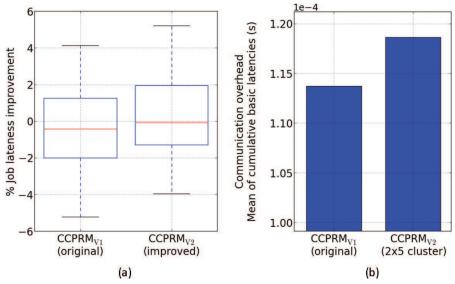

| Figure 6.5            | Comparison of CCPRM $_{V1}$ (original) and CCPRM $_{V2}$                                                | 107 |

| rigure 0.5            |                                                                                                         |     |

|                       | (improved). (a) Cumulative job lateness                                                                 | 111 |

| T1 ( (                | improvement. (b) Communication overhead                                                                 | 111 |

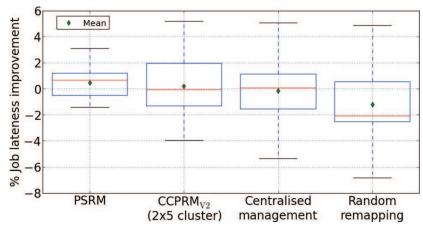

| Figure 6.6            | Distribution of cumulative job lateness improvement                                                     |     |

|                       | after applying remapping                                                                                | 112 |

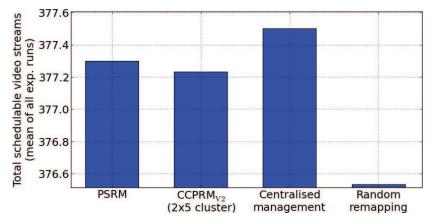

| Figure 6.7            | Comparison of fully schedulable video streams for                                                       |     |

|                       | each remapping technique                                                                                | 112 |

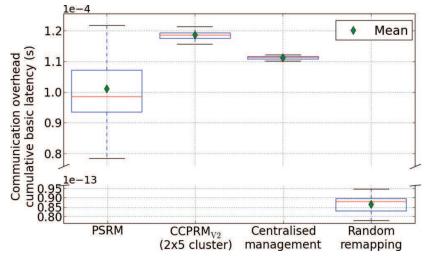

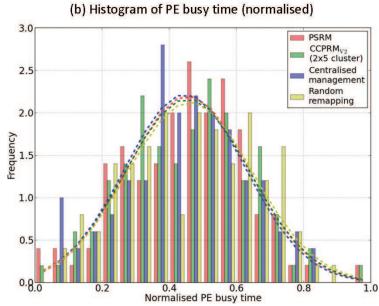

| Figure 6.8            | Communication overhead of the remapping                                                                 |     |

|                       | approaches                                                                                              | 113 |

| Figure 6.9            | Comparison of PE utilisation for all remapping                                                          |     |

| _                     | techniques. (a) Distribution of PE utilisation across                                                   |     |

|                       | a $10 \times 10$ NoC. (b) Histogram of PE busy time                                                     |     |

|                       | (normalised; 20 bins)                                                                                   | 114 |

| Figure 7.1            | System model adopted in this chapter. A cloud data                                                      |     |

|                       | center containing different nodes (servers) with                                                        |     |

|                       | dedicated cores (PEs) to execute jobs submitted by                                                      |     |

|                       | multiple users                                                                                          | 120 |

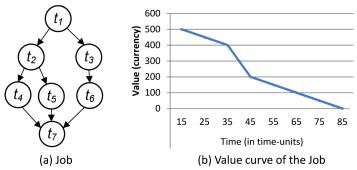

| Figure 7.2            | An example job model and its value curve                                                                | 121 |

| Figure 7.2 Figure 7.3 | Profiling and non-profiling based approaches                                                            | 123 |

| _                     |                                                                                                         | 123 |

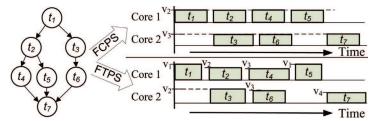

| Figure 7.4            | Voltage/frequency identification by FCPS                                                                | 120 |

| T:                    | and FTPS                                                                                                | 130 |

| Figure 7.5            | Value and energy at different arrival rates                                                             | 130 |

| Figure 7.6            | Value and energy with varying number of nodes                                                           | 131 |

| Figure 7.7            | Value and energy with varying number of cores                                                           |     |

|                       | at each node                                                                                            | 132 |

# **List of Tables**

| Table 3.1        | Number of rejected tasks, tasks executed before and after their deadlines in various controlling environment configurations for a periodic task workload simulation scenario (3 clusters, 3 cores in each): configuration parameters ( <i>above</i> ) and | 22  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3.2        | obtained results ( <i>below</i> )                                                                                                                                                                                                                         | 32  |

| 20022002         | before and after their deadlines in various controlling<br>environment configurations for 30 random bursty<br>task workload simulation scenarios (3 clusters,                                                                                             |     |

|                  | 3 cores in each): configuration parameters ( <i>above</i> )                                                                                                                                                                                               |     |

|                  | and obtained results (below)                                                                                                                                                                                                                              | 34  |

| Table 3.3        | Total number of tasks executed before and after their                                                                                                                                                                                                     |     |

|                  | deadlines and rejected tasks with various $\Upsilon$ threshold in the introductory experiment (1 processor with                                                                                                                                           |     |

|                  | 3 cores)                                                                                                                                                                                                                                                  | 42  |

| Table 4.1        | Average Param values for random workloads                                                                                                                                                                                                                 |     |

|                  | generated with different $range\_min$ and                                                                                                                                                                                                                 |     |

|                  | $range\_max$ parameters                                                                                                                                                                                                                                   | 60  |

| <b>Table 4.2</b> | Four configuration possibilities with respect to                                                                                                                                                                                                          |     |

|                  | controllers' output usage (OL and CL stands for                                                                                                                                                                                                           |     |

| m 11 #4          | open-loop and closed-loop, respectively)                                                                                                                                                                                                                  | 69  |

| Table 5.1        | Number of hyperperiods (100 ms) required for                                                                                                                                                                                                              |     |

|                  | switching between states $PowerUp$ to $Cluster\_1$ in DemoCar depending on router $(d_R)$ and one link                                                                                                                                                    |     |

|                  | latencies $(d_L)$                                                                                                                                                                                                                                         | 90  |

| Table 6.1        | PSRM algorithm parameters                                                                                                                                                                                                                                 | 108 |

| <b>Table 6.2</b> | PE utilisation distribution statistics. Lower variance                                                                                                                                                                                                    |     |

|                  | (var.) = better workload distribution                                                                                                                                                                                                                     | 115 |

| <b>Table 7.1</b> | Percentage of rejected jobs at different arrival                                                                                                                                                                                                          |     |

|                  | rates                                                                                                                                                                                                                                                     | 132 |

# **List of Algorithms**

| Algorithm 4.1 | Pseudo-code of Admission controller involving   |     |  |  |  |

|---------------|-------------------------------------------------|-----|--|--|--|

|               | DSE algorithm                                   | 57  |  |  |  |

| Algorithm 5.1 | Pseudo-code of no deadline violation with       |     |  |  |  |

|               | makespan minimisation algorithm for the initial |     |  |  |  |

|               | mode mapping                                    | 81  |  |  |  |

| Algorithm 5.2 | Pseudo-code of a migration data transfer        |     |  |  |  |

|               | minimisation algorithm                          | 83  |  |  |  |

| Algorithm 6.1 | PS Differentiation Cycle                        | 100 |  |  |  |

| Algorithm 6.2 | PS Propagation Cycle                            | 101 |  |  |  |

| Algorithm 6.3 | PS Decay Cycle                                  | 102 |  |  |  |

| Algorithm 6.4 | PSRM Differentiation Cycle                      | 103 |  |  |  |

| Algorithm 6.5 | PSRM Remapping                                  | 105 |  |  |  |

| Algorithm 7.1 | Profiling Based Resource Allocation             | 125 |  |  |  |

| Algorithm 7.2 | Non-profiling Based Resource Allocation         | 126 |  |  |  |

| Algorithm 7.3 | Voltage/frequency Identification                | 127 |  |  |  |

# **List of Abbreviations**

ACPI Advanced Configuration and Power Interface

ALU Arithmetic Logic Unit

AMIGO Approximate M-constraint Integral Gain Optimization

AT Arrival Time

AUTOSAR Automotive Open System Architecture

BCET Best Case Execution Time

CL Closed Loop

CPU Central Processing Unit DAG Directed Acyclic Graph

DBC Deadline and Budget Constraints

DSE Design Space Exploration

DSP Digital Signal Processing

DVFS Dynamic Voltage and Frequency Scaling

ECG Electrocardiogram

ECU Electronic Control Unit

EDF Early Deadline First

ET Execution Time

FCPS Fixing Cores Power States

FIFO First In First Out flit Flow control digIT

FPGA Field Programmable Gate Array

FSM Finite State Machine FTPS Fixing Tasks Power States

GA Genetic Algorithm GoP Group of Pictures

HLRS High Performance Computing Center Stuttgart

HP HPC Platform

HPC High-Performance Computing

HRT Hard Real-Time IA Interval Algebra

## xxiv List of Abbreviations

IQR Inter-Quartile Range

MMKP Multi-Choice Knapsack Problem MPSoC Multiprocessor System-on-Chip NBA Non-profiling Based Approach

NoC Network-on-Chip

OL Open Loop

OS Operating System

P Proportional

PBA Profiling Based Approach

PE Processing Element PG Platform Graph PI Proportional-Integral

PID Proportional-Integral-Derivative

PID-AC PID-based Admission Control

PMF Probability Mass Function

PS Pheromone Signalling

QoS Quality of Service RM Resource Manager

RMA Rotating Mapping Algorithm

RTA Response Time Analysis

RTM Real-Time Manager

RTS Real-Time Scheduling

SDF Synchronous Dataflow

SoC System-on-Chip ST Spanning Tree TG Task Graph

TLM Transaction-Level Modelling

ValOpt Value Optimization

VC Value Curve VM Virtual Machine VS Voltage Scaling

WCET Worst Case Execution Time WCRT Worst Case Response Time 1

# Introduction

The availability of highly parallel computing platforms based on multi and manycore processors enables a wide variety of technical solutions for systems across the embedded and high-performance computing domains. However, large scale manycore systems are notoriously hard to design and manage, and choices regarding resource allocation alone can account for wide variability in timeliness and energy dissipation, up to several orders of magnitude. For example, the allocation of many computation-centric jobs to the same processing core, or communication-intensive jobs to cores linked by a low bandwidth interconnect, can significantly impair system performance specially in applications with many dependencies between jobs.

Techniques to allocate computation and communication workloads onto processor platforms have been studied since the early days of computing. However, this problem has become significantly harder because of **scale** and **dynamicity**: compute platforms now integrate hundreds to thousands of processing cores, running complex and dynamic applications that make it difficult foresee the amount of load they can impose to those platforms.

Elementary combinatorics provides us with evidence of the problem of **scale**. For a simple formulation of the problem of allocating jobs to processors (one-to-one allocation), one can see that the number of allocations grows with the factorial of the number of jobs and processors. For example, a system with 4 jobs and 4 processing cores can have P(4,4)=24 possible allocations, but simply by doubling the number of jobs and cores the number of allocations becomes P(8,8)=40320 (where P(n,k) denotes the k-permutations of n). The empirical evidence points in the same direction, as it can be seen in [110] that for realistic manycore embedded systems (40–60 jobs, 15–30 processing cores) a well-tuned search algorithm had to statically evaluate hundreds of thousands of distinct allocations before it finds one that meets the systems performance requirements.

To cope with **dynamicity**, a dynamic approach to resource management is the most obvious choice, aiming to dynamically learn and react to changes to the load characteristics and to the underlying compute platform. The baseline, which is a static allocation decided before deployment based on the (nearly) complete knowledge about the load and the platform, is no longer viable. For example, static resource allocation in high-performance computing (HPC) has often been referred as a significant cause of low utilization of servers, which results in cost increases on hardware and energy [17]. Static allocation is also commonly used by aerospace and automotive industries to provide worst case performance guarantees that are required by certification authorities. However, it is well known that such an approach usually leads to under-utilised computing and communication resources at run-time [113].

The problems of scale and dynamicity are also made harder with the increasing density of computing and communication resources. The definition of density used here is not necessarily spatial, but rather on connectivity (i.e., dense graph). In densely connected systems, a resource allocation algorithm may have to make decisions very often due to the system dynamics, and may have to consider dozens or hundreds of potential allocation possibilities at each decision point (i.e., which processor should execute each job, which communication links should be used when those jobs exchange data). Furthermore, such algorithms have to work in a distributed way due to the difficulty to obtain the up-to-date state of the whole system. And despite such levels of complexity, the algorithms themselves are also subject to tight constraints in performance and energy. It is then evident that optimal resource allocation algorithms cannot cope with this type of problem, and that lightweight heuristic solutions are needed.

This book is therefore concerned with the kinds of resource allocation heuristics that can cover different levels of dynamicity, while coping with the scale and complexity of high-density manycore platforms.

# 1.1 Application Domains

The level of dynamicity of a system denotes how often it changes its characteristics. In this book, we are concerned with resource allocation, so dynamicity means how much variation can be found on the system workload (e.g., arrival patterns, computation and communication requirements, value to the end-user) and on the underlying compute platform (e.g., degradation or lost of performance due to faults, increase in capacity due to upgrades). Different application domains can be characterised by their typical levels of dynamicity.

For example, deeply embedded systems such as those in automotive, aerospace and medical domains have low dynamicity, and often their entire functionality and behaviour is known at design time, prior to deployment. The low dynamicity makes the performance of such systems easier to predict, and therefore guarantees regarding timeliness can be made (e.g., ECG signal of a

complete cardiac cycle will be processed in less than 10 ms). Such guarantees are often enforced by means of resource reservation and isolation, which can lead to very low levels of resource utilisation: a processing core can be exclusively allocated to a given job for the sake of performance predictability, but that job only needs the core to its full capacity for a limited period of its lifetime, leaving it subutilised for the rest of the time.