## **Dakota State University**

# **Beadle Scholar**

Masters Theses & Doctoral Dissertations

Fall 11-2023

# Bypassing Modern CPU Protections With Function-Oriented Programming

Logan Stratton

Follow this and additional works at: https://scholar.dsu.edu/theses

#### **Recommended Citation**

Stratton, Logan, "Bypassing Modern CPU Protections With Function-Oriented Programming" (2023). *Masters Theses & Doctoral Dissertations*. 433.

https://scholar.dsu.edu/theses/433

This Dissertation is brought to you for free and open access by Beadle Scholar. It has been accepted for inclusion in Masters Theses & Doctoral Dissertations by an authorized administrator of Beadle Scholar. For more information, please contact repository@dsu.edu.

# BYPASSING MODERN CPU PROTECTIONS WITH FUNCTION-ORIENTED PROGRAMMING

A doctoral dissertation submitted to Dakota State University in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

in

Computer Science

November 2023

By

Logan Stratton

**Dissertation Committee:**

Dr. Kyle Cronin, Chair

Dr. Tyler Flaagan, Committee

Dr. TJ O'Connor, Committee

# DISSERTATION APPROVAL FORM

This dissertation is approved as a credible and independent investigation by a candidate for the Doctor of Philosophy degree and is acceptable for meeting the dissertation requirements for this degree. Acceptance of this dissertation does not imply that the conclusions reached by the candidate are necessarily the conclusions of the major department or university.

| tudent Name: Logan Stratton                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | **               |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|

| Dissertation Title:  Bypassing Modern CPU Protections With Function-Oriented Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |  |

| raduate Office Verification:    Grinna Hase Feldland   Faldland   Faldland | Date: 12/05/2023 |  |

| Dissertation Chair/Co-Chair: Lyll (YOULL Print Name: Kyle Cronin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Date:            |  |

| Dissertation Chair/Co-Chair:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Date:            |  |

| Print Name:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                  |  |

| Committee Member: Tyler Flagan.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Date: 12/05/2023 |  |

| Print Name: Tyler Flaagan AAAAABAAA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  |  |

| Committee Member: TJ OConnor EIDCCZETOBEF400                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Date: 12/05/2023 |  |

| Tim Name.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  |  |

| Committee Member:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Date:            |  |

| Print Name:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                  |  |

| Committee Member:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Date:            |  |

| Print Name:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                  |  |

# **ACKNOWLEDGEMENTS**

I want to acknowledge and say thanks to my committee members for advising me through all questions I had during this process and the valuable input that you have given me. This process was made easier through the skill and feedback from my committee members. I want to give my thanks to the faculty at DSU as well, for their enthusiasm in the field of cyber has led me to where I am today. Without their guidance through my classes and the ability they have, I probably would not have gone as far as I have today.

I would be amiss to not give acknowledgement to Pepsipu and their nightmare CTF challenge. This challenge gave me the basis and building blocks to think of this research project and to apply it to a real-world scenario.

Lastly, I want to give thanks to my friends and family for their support over the years. Without their love and kindness this process would have been much more difficult to accomplish.

# **ABSTRACT**

Over the years, code reuse attacks such as return-oriented programming (ROP) and jumporiented programming (JOP) have been a primary target to gain execution on a system via buffer

overflow, memory corruption, and code flow hijacking vulnerabilities. However, new CPU-level

protections have introduced a variety of hurdles. ARM has designed the "Pointer Authentication"

and "Branch Target Identification" mechanisms to handle the authentication of memory

addresses and pointers, and Intel has followed through with its Shadow Stack and Indirect

Branch Targeting mechanisms, otherwise known as Control-Flow Enforcement Technology. As

intended, these protections make it nearly impossible to utilize regular code reuse methods such

as ROP and JOP.

The inclusion of these new protections has left gaps in the system's security where the use of function-based code reuse attacks are still possible. This research demonstrates a novel approach to utilizing Function-Oriented Programming (FOP) as a technique to utilize in such environments. The design and creation of the "FOP Mythoclast" tool to identify FOP gadgets within Intel and ARM environments demonstrates not only a proof of concept (PoC) for FOP, but further cements its ability to thrive in diverse constrained environments. Additionally, the demonstration of FOP within the Linux kernel showcases the ability of FOP to excel in complex and real-world situations. This research concludes with potential solutions for mitigating FOP without adversely affecting system performance.

#### **DECLARATION**

I hereby certify that this dissertation constitutes my own product, that where the language of others is set forth, quotation marks so indicate, and that appropriate credit is given where I have used the language, ideas, expressions or writings of another.

I declare that the dissertation describes original work that has not previously been presented for the award of any other degree of any institution.

Signed,

Logan Stratton

Logan Stratton

# TABLE OF CONTENTS

| Abstract                                   | IV |

|--------------------------------------------|----|

| Table Of Contents                          | VI |

| List Of Figures                            |    |

| List Of Tables                             | X  |

| Introduction                               | 1  |

| Background of the Problem                  |    |

| Statement of the problem with motivation   |    |

| Purpose of the research                    |    |

| Significance of the Study                  |    |

| Nature of the Study                        | 7  |

| Research Questions                         | 8  |

| Theoretical Framework                      |    |

| Acronyms                                   |    |

| Definitions                                |    |

| Assumptions                                |    |

| Scope and Limitations                      |    |

| Chapter Summary                            | 19 |

| Related Work                               | 20 |

| Memory Corruption                          | 20 |

| Symbolic execution                         | 21 |

| CPUs and Protections                       | 22 |

| ARM & Intel                                | 23 |

| ARM: Pointer Authentication                | 23 |

| ARM: PAC Bypasses                          | 24 |

| Intel: Control-Flow Enforcement Technology | 25 |

| Branch Targeting                           |    |

| Intel: CET Implementation                  |    |

| Protections                                |    |

| NX/DEP                                     | 27 |

| ASLR                                       | 28 |

| PIE                                        | 29 |

| Return-into-Libc                           | 29 |

| Code-reuse Attacks: ROP                    | 30 |

| Gadget                                     | 30 |

| JOP                                        | 32 |

| Other Code-reuse                           | 33 |

| FOP                                        | 33 |

| Chapter Summary                            | 34 |

| Research Methods                           |    |

| Hypothesis                                 | 37 |

| Research Approach                          |    |

| Design as an Artifact                      | 38 |

| Problem Relevance                          | 39 |

| Design Evaluation                          | 39 |

| Research Contributions              | 41 |

|-------------------------------------|----|

| Research Rigor                      | 40 |

| Design as a Search Process          | 43 |

| Communication of Research           | 43 |

| Objectives of the Study             | 44 |

| Objective of the Artifact           | 45 |

| Assumptions and Limitations         | 46 |

| Data Collection                     | 48 |

| Validity and Reliability            | 49 |

| Data Analysis                       |    |

| Summary                             | 52 |

| Implementation and evaluation       |    |

| Introduction                        | 53 |

| Artifact: FOP Mythoclast            | 54 |

| Artifact Design                     |    |

| Symbolic Gadget Identification      |    |

| Dispatcher Gadget Identification    | 59 |

| Symbolic Execution Engine           | 61 |

| Core File                           | 62 |

| Kernel Approach                     | 63 |

| Tooling shortfalls                  | 65 |

| Indirect Branch Handling            | 65 |

| Dispatcher Identification Looseness | 67 |

| Current Limitations with core files |    |

| Limitation to Libc and LD           | 67 |

| Kernel Memory                       | 68 |

| Unique Gadgets Approaches           | 69 |

| Speed                               | 71 |

| Tooling Evaluation                  |    |

| Outcome                             | 72 |

| Useless Gadgets                     | 73 |

| Validity and Reliability            | 73 |

| ARM and Intel Support               | 74 |

| ARM                                 | 76 |

| Test binary                         | 76 |

| Library Building                    | 76 |

| ARM Gadget Count                    | 77 |

| Dispatchers                         | 78 |

| Primitives                          | =^ |

| Register Setting                    | 80 |

| Arithmetic                          | 81 |

| Memory Operations                   | 82 |

| System Calls                        | 83 |

| Branching                           |    |

| ARM Capabilities                    |    |

| ARM Conclusion                      | 86 |

| Intel               | 88  |

|---------------------|-----|

| Test binary         | 88  |

| Intel Gadget Count  | 88  |

| Dispatcher          | 89  |

| Primitives          | 90  |

| Register Setting    | 90  |

| Arithmetic          | 91  |

| Memory Access       | 93  |

| System Calls        | 93  |

| Branching           | 95  |

| Intel Capabilities  | 95  |

| Intel Conclusion    | 97  |

| Kernel              | 0.0 |

| Environment         | 98  |

| Vulnerability       | 98  |

| Kernel Gadget Count |     |

| Dispatcher          |     |

| Kernel Impacts      | 102 |

| Kernel Capabilities | 103 |

| Conclusion          | 107 |

| Intro               |     |

| Contributions       | 107 |

| Future Work         | 108 |

| Limiting FOP        | 110 |

| Conclusion          | 112 |

| References          |     |

| Appendix 1          |     |

| Appendix 2.A        | 128 |

| Appendix 2.B        | 129 |

| Appendix 2.C        |     |

| Appendix 3.A        |     |

| Appendix 3.B        | 149 |

| <del></del>         |     |

# LIST OF FIGURES

| Figure 1: Examination of potential paths in X64                   | 56        |

|-------------------------------------------------------------------|-----------|

| Figure 2: Three possible paths from Figure 1                      | 57        |

| Figure 3: Example of a Determinable and Non-Determinable state    | 58        |

| Figure 4: Examples of two dispatcher gadgets                      | 61        |

| Figure 5: Gadget demonstrating the reading of 1 byte from memory  | 70        |

| Figure 6: Demonstration of a large memory movements               | 71        |

| Figure 7: Demonstration of the hash string function gadget        | 72        |

| Figure 8: Example of a useless gadget                             | 73        |

| Figure 9: Example of a complex gadget                             | 74        |

| Figure 10: Command used to compile the ARM test binary            | 76        |

| Figure 11: Commands for building the custom ARM library           | 77        |

| Figure 12: Assembly analysis of the fprintf function              | 78        |

| Figure 13: Examination of the dispatcher gadget assembly          | <b>79</b> |

| Figure 14: Examples of register setting through static assignment | 80        |

| Figure 15: Example of a register assignment gadget                | 81        |

| Figure 16: Arithmetic gadget examples                             | 82        |

| Figure 17: Memory operation gadget examples                       | 83        |

| Figure 18: Syscall gadget example                                 | 84        |

| Figure 19: Example of a branching gadget                          | 85        |

| Figure 20: Command used to compile the X64 example                | 88        |

| Figure 21: Static register setting gadget                         | 91        |

| Figure 22: Register setting between registers                     | 91        |

| Figure 23: Arithmetic gadget examples                             | 92        |

| Figure 24: Memory accessing gadget examples                       | 93        |

| Figure 25: Syscall gadget examples                                | 94        |

| Figure 26: Branching gadget example                               | 95        |

| Figure 27: Utilized kernel dispatcher gadget                      | 100       |

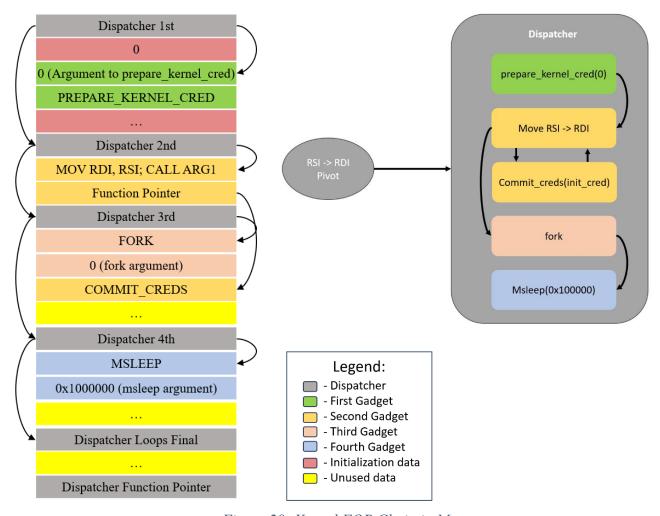

| Figure 28: Kernel FOP Chain in Memory                             | 104       |

| Figure 29: Gadget of RSI pivot to RDI                             | 105       |

|                                                                   |           |

# LIST OF TABLES

| Table 1: Timing analysis between different libraries and architectures  | 71  |

|-------------------------------------------------------------------------|-----|

| Table 2: Analysis of ARM gadgets found within various libraries         | 77  |

| Table 3: Number of functions compared to BTI landing pad functions      | 77  |

| Table 4: Number of dispatcher gadgets for different libraries           | 78  |

| Table 5: Gadget count of different libraries                            | 88  |

| Table 6: Function to valid landing pad functions count                  | 89  |

| Table 7: Number of dispatcher gadgets                                   | 90  |

| Table 8: Function checked in the kernel                                 | 99  |

| Table 9: Number of gadgets per gadget depth                             | 99  |

| Table 10: Number of identified dispatcher gadgets                       | 101 |

| Table 11: Examination of the gadgets with and without patched functions | 111 |

# **CHAPTER 1**

#### INTRODUCTION

As an attack methodology ages, the ability of organizations to detect exploitation attempts leveraging it becomes stronger. This trend can lead to a false sense of security stemming from the lack of novel methods. Identifying limitations or gaps in security mechanisms provides an opportunity to enhance existing protections, thereby fulfilling their intended purpose of ensuring the safety and security of a system. This chapter presents an overview of the current state of code-reuse attacks will explore and security protections. This chapter will then discuss an approach to bypass these protections with the Function-Oriented Programming (FOP) technique. While these protections excel in terms of their designed capabilities, there is a stark difference between being accurate to the specification and being secure. Examining these protections reveals security gaps and demonstrates areas where FOP is functional. This chapter will define the research and the approaches taken to defining FOP and its tooling in order to better examine code-reuse attacks in an age of modern CPU-based protections.

## **Background of the Problem**

Memory corruption bugs are one of the oldest issues pertaining to memory-unsafe languages such as C and C++ (Szekeres et al., 2013). The usage of lower-level languages provides benefits such as speed and portability, but can lead to major vulnerabilities that can harm companies and computers alike (Alnaeli et al., 2016). Memory corruption vulnerabilities are not new, and have had several high-profile documented instances in the late 1990s, primarily

in publications from Aleph One (1996) and Zatko (1995). These techniques typically target an aspect of vulnerable code that, under the right circumstances, can lead to malicious use. Taking advantage of memory corruption vulnerabilities can lead to the complete compromise of a system. This hazard is the main reason for memory corruption vulnerabilities becoming the leading cause of system vulnerabilities in 2022 according to MITRE (*MITRE*, 2022).

Overwriting essential values, such as the return address, of a running process may be possible depending on the type of memory corruption vulnerability. This could occur from a buffer overflow or writing out of memory in the stack. Typically, for a running process, the stack serves as a storage location for function variables and return addresses, organized in related chunks called frames for the chain of called functions. Overwriting these return addresses leads to the ability to divert execution control flow to attacker-wanted targets. An example of this would be the Return-into-Libc (Nergal, 2001) attack, in which the control flow is diverted to a Libc function for further functionality. This approach of overwriting return addresses can lead to more advanced techniques such as Return-Oriented Programming (ROP) (Shacham, 2007), which is the most common technique used today (Xu et al., 2020). ROP involves adding multiple return addresses to the stack, pointing to small sections of code known as gadgets. Chaining these gadgets together leads to the ability to create a functional program through the returns on the stack.

The increase in the use of ROP has led to real-world applicable use cases like CVE-2020-1020 (Jurczyk & Glazunov, 2021), where ROP was utilized to bypass protections and escalate privileges in a Windows environment. The need to limit the capabilities of ROP and other codereuse attacks has led to the design and implementation of hardware-based protections from both Intel and ARM. Intel's Control-Flow Enforcement Technology (CET) (Garrison, 2020) and

ARM's Pointer Authentication (PAC) and Branch Target Identification (BTI) support (Mujumdar, 2021; Qualcomm, 2017) have been designed to limit the capabilities of code-reuse attacks. To limit the attack scope, restrictions are set on a process' stack and control flow. These protections have eliminated the ability to simply overflow a buffer into developing a ROP chain.

The influence of CET and PAC/BTI comes from Control Flow Integrity (CFI) design systems. Limiting actions make it possible to restrict the path of execution in a program from an attacker-controlled flow to an acceptable flow within the compiled code (Garrison, 2020; Mujumdar, 2021). The problem arises when unidentified avenues in these acceptable code flows can still allow the same primitives available as ROP.

The design and application of new security protections exaggerate the current security in place. While the use of CET and PAC/BTI has limited the use of normal code-reuse attacks (ARM, 2022). The application of more unique and specialized techniques can show the flaws in the design of systemwide securities. Identification of a method to circumvent the security protections demonstrates the true scope of the security enhancements. These methods can lead to further design and implementation methods to build safer systems.

# Statement of the problem with motivation

The intended design of CET and PAC/BTI is to limit the ability to gain execution control from a memory corruption-based attack by hindering code-reuse attacks. The primary target of most memory corruption attacks are code-reuse techniques, but by limiting the scope and availability of such methods, there becomes a gap in the confidence a system and its actual security. The problem addressed by this research is the identification of gaps in CET and PAC/BTI where code-reuse attacks still exist. Exploring this gap leads to discovering areas of

protection that these systems are missing. Identifying and addressing these missing components leads to the ability to devise a potential solution to satisfy the original intent of the protections.

As new systems begin to implement and adhere to the designs of CET and PAC/BTI, it becomes important to confirm that all the time and effort put into the design and implementation of these protections is fruitful and does not miss any conditions. Identifying gaps in existing protections allows for the development of effective solutions to address those gaps. These definitions can lead to further implementations in current and future systems. This allows for security in the future to be more dependable as there can be less dependence on the implicit definition of security.

While ROP has led the way for code-reuse attacks since Shacham (2007) first demonstrated it, ROP has come to the point that code-reuse attacks can be limited in the fastest way with hardware-based protections. The problems occur when the designs and implementations do not cover all cases allowing for code-reuse techniques to slip through. This typically allows for the full capabilities of the techniques the protections were trying to limit to be usable regardless.

# Purpose of the research

The purpose of this research has two main goals: The first is to examine the capabilities of Function-Oriented Programming (FOP) in an environment with modern CPU protections. The second is to utilize Design Science Research (DSR) to create the FOP Mythoclast, a tool to facilitate the identification and purpose of useful FOP gadgets. With the determination of these two main goals, this research shows that FOP is of use in a modern context with far-reaching possibilities.

The performance of FOP falls under several main criteria:

- The multi-architecture support for FOP-based attacks.

- The capabilities of FOP.

- The applicable use in place of other common code-reuse attacks.

- Real-world applicable use on a modern system.

These points show the goals to prove the effectiveness of FOP. Being able to show the multi-architecture support, in this case, of ARM and Intel CPUs, demonstrates that the attack is able to work in environments with hardware protections to directly counter code-reuse-based attacks. To follow these guidelines, strict rules enforce adherence to the hardware protections. Further definitions of these guidelines appear later in the chapter and in further detail in Chapter 3. The utility of FOP can be analyzed through the additional access and capability the attack affords, in past code-reuse-based attacks, a large design aspect of determining the capabilities of a code-reuse attack is by proving the Turing complete nature, or the ability to complete any computable action within code (Shacham, 2007). To show that FOP operates in place of other code-reuse attacks, FOP needs to have the capabilities to function in the place of ROP. This research analyzes this by determining points of usage for FOP in comparison to ROP.

The decisive point of analysis for FOP is its applicable use in a real-world modern environment. In the past, FOP was shown to be useable against an application and vulnerability from 2006 (Guo et al., 2018). While this demonstrates the FOP technique is feasible, it does not give an example of a current real-world example where application design has changed in the last 15 years. To highlight improved usage in a modern design, this research uses a more complex environment and a recent CVE as the foundation for demonstrating the FOP attack. Together these criteria examine the performance of FOP for a better understanding of how the technique operates.

The second goal is the design and implementation of the FOP Mythoclast. The purpose of this tooling is to accompany and enhance the FOP technique. The identification of FOP gadgets is significantly more complex than similar code-reuse attacks such as ROP. When locating gadgets, most techniques take a backward approach. First, they identify the possible ending instruction and work backward to find instructions that would occur before building out the possible gadget. The FOP approach does not work this way as doing so would violate the hardware protections designed to stop code-reuse attacks. To implement a true FOP design, only the beginning of functions can act as the gadget, this causes an inherent reliance on an understanding of what a function does, how a function impacts memory, and what registers a function modifies. This forward approach opens the possibilities for unknown pathways to appear when locating gadgets, limiting the availability of previous techniques to find gadgets. The FOP Mythoclast solves this approach by utilizing a symbolic execution technique to determine the capabilities of a gadget.

## **Significance of the Study**

The design of CET and PAC/BTI protections limit the use of code-reuse attacks.

Demonstration of the capabilities of FOP within secure environments can reveal the gaps in these security mechanisms. This can lead to FOP having the same capabilities as other code-reuse attacks that CET and PAC/BTI limit. Showing that FOP is still useable in these environments, the identification of gaps in the protections allows for revisions to further the goal of limiting code-reuse attacks.

As previous studies have shown that FOP is feasible in an x64 context (Guo et al., 2018), the application of FOP in different architectures, such as ARM, has importance. This capability

allows for the application of FOP to be comparable to previous code-reuse attacks and their scope of usage.

Similar to other code-reuse techniques, FOP relies on the use of gadgets to execute an attack. This requires the identification of FOP gadgets to facilitate a successful attack. At the time of this writing, the FOP Mythoclast is the first of its kind to identify FOP gadgets through the use of symbolic execution. The only previous method at the time of this writing to identify FOP gadgets in an x64 environment utilized compiler plugins and static analysis to identify gadgets (Guo et al., 2018). The use of symbolic execution allows for the identification of gadgets in a timelier manner in comparison to static methods and allows for the identification of more complex gadgets in comparison to the compiler plugin approaches.

#### **Nature of the Study**

The outcome of this research is the implementation of the FOP technique and the design of tooling to support FOP gadget discovery. As previous research has shown that FOP is possible under the right circumstances (Guo et al., 2018; Lan et al., 2015), the main nature of this research centers around the utilization of FOP within modern CPU-based protection environments and the FOP Mythoclast. The implementation of the FOP Mythoclast adheres to the design science approach. Design science, as per Hevner et al. (2004), involves developing and assessing artifacts that are employed for addressing identified issues. Hevner et al. continue with defining this design approach with the statement of, new artifacts allow applying empirical and qualitative methods with the DSR methodology. The design of the FOP Mythoclast presents an original contribution to the code-reuse attack research space, as well as differentiating itself by solving all the goals associated with it. As described by Wierenga, design theories are implementations to explain how an artifact can be designed to satisfy all its requirements (2014).

The research findings enhance the credibility of the design science used by making significant research contributions. Hevner et al. describe this approach as having clear and verifiable contributions relating to the field of use (2004). Not only does the FOP Mythoclast fit this ideal, but the implementation also covers this. This research shows a novel approach to defining the use of FOP in a unique environment by defining a new target for the design of FOP in the form of modern CPU-based protections. This research further expands this ideal by designing an implementation of FOP in an ARM context, the first of its kind. These factors further cement the approaches defined in this research and the nature of this research.

#### **Research Questions**

This research defines the usage of FOP in modern CPU contexts and the creation and evaluation of FOP Mythoclast. As part of this, the main research question addressed in this research is, do FOP-based attacks work in a modern context with hardware-based protections in place of typical code-reuse attacks such as ROP? This research splits this main question into unique aspects to demonstrate the original aspects of this research:

Is FOP feasible in an ARM context?

Can FOP operate in a simplistic environment with a restricted gadget range?

Is the approach to locating FOP gadgets possible?

Can FOP be implemented in a real-world use case?

This paper aims to address a variety of objectives to answer the main question above. The first of which is by demonstrating that FOP is implementable in simple "toy" binaries. This demonstration defines the use of FOP for attacking an application. This question is the foremost important as the simplistic nature of a toy binary allows for finer control of FOP under ideal conditions. The term "toy binary" in this research refers to a sample program intentionally

designed with a vulnerability to facilitate the practice of its execution. If the FOP framework cannot stand on its own in an environment with ideal conditions, there is no ground for the continuation of the attack.

Continuing with the sub-questions is the approach of implementing FOP in an ARM context, as previous research has shown FOP to be possible in Intel x64 environments; at the time of this writing, no previous research has investigated the approach within ARM. This is of importance as ARM has a major market share in modern CPUs; for example, the ARM architecture was used as the architecture for one of the world's fastest supercomputers (Matsuoka, 2021). Researching this question can help demonstrate that FOP is not architecture-dependent and has capabilities across environments.

The second sub-question is defined to show the capabilities of FOP, as shown in previous examples of FOP by Guo et al. (2018) the approach taken relied on convenient gadgets found in third-party libraries or the binaries themselves. To improve upon this, the FOP framework needs to show that it is usable in a wide variety of test cases and the simplest way to define this is to have a singular target found across multiple binaries. In a Linux environment, this is known as Libc, this is the defacto library loaded in most binaries at runtime to facilitate basic system functionality and binary loading. Demonstration of the full capabilities of FOP within this sole library makes FOP more akin to that of ROP, which has been shown to be Turing complete with Libc alone (Shacham, 2007).

As defined as one of the artifacts of this research, the FOP Mythoclast design is meant to determine FOP gadgets and the applicable use of each gadget. To make this tool, a symbolic execution (Baldoni et al., 2018) approach has been determined to be the best way to implement this discovery of FOP gadgets. Through the use of symbolic execution of instructions, it becomes

possible to follow a flow of data between the registers, stack, and memory. Symbolic execution can determine if a current gadget is useable or feasible given a list of constraints that can occur while processing a gadget. This approach is well suited for the complex nature of FOP and contributes to the definition of FOP in modern contexts.

Lastly is the question of if FOP is usable in a real-world context. While defining FOP to work in special instances, such as simplistic binaries and environments, shows that the attack is feasible, it does not prove the ability of FOP to replicate the capabilities of ROP in modern environments. To answer this question, an example FOP chain targets a unique real-world case where similar code-reuse attacks are functionally impossible to implement. The FOP Mythoclast supplements the design of this FOP chain with gadget detection and usage. Combining both factors of this FOP research displays FOP as a meaningful technique in the place of other code-reuse techniques where modern CPU protections would eliminate their usage.

#### Theoretical Framework

Previous studies have been published about the approach of FOP, the main being from Guo et al. (2018) which coined the term FOP and implemented a design within a 64-bit context. While this is the first FOP-based research in a 64-bit context, two previous studies apply to FOP's history.

The first is a research by Tran et al. (2011), which was published to directly contradict a statement made by Shacham (2007) in the original proposal of ROP. The claim is that,

In a Return-into-Libc attack, the attacker can call one Libc function after another, but this still allows him to execute only straight-line code, as opposed to the branching and other arbitrary behavior available to him with code injection.

To prove this statement wrong Tran et al. were able to prove the complete nature of a Return-into-Libc attack by chaining functions together with no use of supporting gadgets (2011). This approach as defined, was to utilize the side effects of functions inherently to show the corruption of values and register states in a useful manner. Continuing in this approach, Tran et al. demonstrated the capabilities to chain functions together to gain confidence in demonstrating that the technique was Turing complete. Even with several different classifications for gadgets, Tran et al. did not give a clear definition of how they determined the usefulness of functions as gadgets. This research has a few drawbacks in comparison to modern systems. The first drawback is that Tran et al. instrumented this technique on a 32-bit system. This limitation originates from the use of 64-bit applications having vastly different applicable internal mechanisms. The first limitation is the number of general-purpose registers and the use of registers as function arguments. The second limitation is that Tran et al. (2011) utilized the stack as a framework to facilitate sequential function calls, this approach violates the main principle designs behind the hardware protections. Thus, the comparison of FOP and this advanced Return-into-Libc attack ends with the use of functional-based side effects. Even so, this was the first step in showing the conditions necessary for the FOP attack framework.

Following this research, Lan et al. (2015) adapted this approach to further coincide with the current implementation of FOP as known in this research. Lan et al. designed their approach around utilizing a looping gadget to call a list of functions, they then named this technique after the looping gadget (2015). The name Lan et al. coined to define the technique is Loop-Oriented Programming (LOP). Lat et al. designed the technique around a 32-bit environment, but instead of directly using the stack as Tran et al. had done, their approach was to utilize a section of memory controlled by the user and an available looping gadget. In their approach, Lan et al. were

able to show the true first example of FOP. As mentioned, the attack shown by Lan et al. falls short when comparing a 32-bit instance to a 64-bit instance.

Lan et al. claim that, as Tran et al. have already shown the use of functions to be Turing complete, that this instance was also Turing complete and continued to use similar gadgets as employed in Tran et al. While this claim may be technically correct, without truly showing that it is Turing complete in its own instance, there could be scrutiny over its veracity. This is based on the propagator of each attack, as Tran et al. utilized the stack to chain functions together they are able to better control arguments to functions. Lan et al. on the other hand, would need to supplement their function calls with their own parameters either by gadgets or during the looping gadget, both of which add larger degrees of difficulty to the attack. To help supplement this, Lan et al. utilized stack pivoting techniques to move the stack pointer around, which allowed the researchers to control the arguments of called functions to a better degree.

The last aspect of the research by Lan et el. is to identify the impact of CFI on this attack framework. The main result is that this attack is possible in CFI implementations that can limit ROP and JOP-based attacks. While Lan et al. reference this, the proof from these claims is lacking as only descriptions of avoiding unbased returns and jumps are the basis of their approach to following coarse-grained CFI implementations.

The most recent research was conducted by Guo et al., who coined the term Function-Oriented Programming (FOP) (2018). Their approach is similar to the work of Lan et al., with the utilization of a loop-based gadget to call a chain of functions. This looping gadget is known as a dispatcher gadget. These functions then alter the state of a program through side effects to modify registers and memory in meaningful ways. Guo et al. displayed this technique against a 64-bit application, but overall, the implementation has less impact than the previous two studies

in 32-bit environments. Guo et al. were able to demonstrate that FOP was possible in a test case with a vulnerability from 2006. This technique utilized several outside factors to load a secondary payload limiting the capabilities shown by FOP. The research by Guo et al. also describes the uses of FOP to bypass CFI implementations and mentions the capabilities against a shadow stack implementation by bypassing the corruption of return addresses that the shadow stack would track.

The problems with the research done by Guo et al. derives from their identification of gadgets. The use of hypothetical gadgets weakens the demonstration of the gadgets by Guo et al., compared to gadgets found naturally within the environment. This approach overshadows the ability to show gadgets existing for use in a FOP-based attack and hinders the proof of useability. The other critique stems from the use of gadgets as mentioned earlier. Designing an attack around gadgets found in third-party libraries or applications limits the scope of FOP to a particular use case. While using all useful gadgets is more important in an environment during the demonstration of an exploit, this still limits the universal proof of FOP utilization and the ability to not need to depend on specific use cases where highly refined gadgets exist. Guo et al. did positively describe an algorithm to locate dispatcher gadgets for use in a FOP-based attack. Overall, this research is lacking in context to the previous two studies done in this category as well.

# Acronyms

**ROP:** Return-Oriented Programming

JOP: Jump-Oriented Programming

(P)COP: (Pure) Call-Oriented Programming

*FOP:* Function-Oriented Programming

*CFI*: Control Flow Integrity

CFG: Control Flow Graph

CPU: Central Processing Unit

CET: Control-Flow Enforcement Technology

PAC: Pointer Authentication Code

PA: Pointer Authentication

BTI: Branch Target Identification

IBT: Indirect Branch Targeting

*PoC:* Proof of Concept

*UAF*: Use After Free

GLIBC: GNU Libc

#### **Definitions**

Code-Reuse Attack: A code-reuse attack implies gaining control flow in a process and reusing compiled code as either intended or unintended. The ability to chain sections of code together under the right conditions gives this the ability to execute any command given a correct set of gadgets. ROP, JOP, and FOP are all examples of code-reuse attacks.

*ROP*: Return-Oriented Programming is one of the original code-reuse attacks designed around the ability to utilize sections of code before a return instruction. Chaining gadgets together allows for a flow of execution to take place. Chains commonly require control of the stack or the stack register to hold the chain.

JOP: Jump-Oriented Programming is the use of small sections of code before jump register instructions. Chaining gadgets together allows for execution to occur. JOP chains are

typically more complex than ROP chains and mostly depend on a dispatcher to load the next gadget from memory.

*PCOP:* Pure Call-Oriented Programming is a code-reuse attack that uses gadgets built around register call instructions to chain instructions together.

*FOP:* Function-Oriented Programming is the use of entire functions as the gadget in a code-reuse attack. This allows for the ability to bypass CFI implementations and other system protections. This attack relies on a dispatcher to load subsequent function calls.

Gadget: A gadget is typically a section of code utilized to accomplish a goal. These goals can range from moving values between registers or memory to loading a value into a register for future use.

*Dispatcher:* The dispatcher is the main runner of certain code-reuse attacks. The dispatcher oversees loading the next gadget in a chain and controls the entire flow of the attack.

*CET:* Control-Flow Enforcement Technology is a CFI-based security approach designed by Intel. This includes the shadow stack and IBT implementations in Intel CPUs.

Shadow Stack: The Shadow Stack is a secondary hardware-based stack to keep track of function return values. During a return instruction, identification of discrepancies between the process stack and shadow stack will cause a fault to occur. The technique limits code-reuse attacks that target the stack such as ROP.

*IBT*: Indirect Branch Targeting is Intel's approach to limiting code-reuse attacks that avoid returns, such as JOP and PCOP. Any indirect call or jump needs to land on an *endbr* instruction to avoid throwing a fault in the program.

*PAC:* Pointer Authentication Codes, sometimes referred to as Pointer Authentication, is ARM's implementation of CFI-based security. This approach is to limit memory corruption

vulnerabilities from escalating to more severe vulnerabilities. PAC is the use of using a cryptographic hash to sign and verify values in memory to confirm integrity.

*BTI:* Branch Target Identification is ARM's approach for dealing with branching codereuse, such as JOP and PCOP. This protection requires all indirect branches to land on a *bti* instruction.

*PoC:* Proof of Concept is an example of the capabilities claimed. This can range from a wide range of capabilities based on the original claim.

*UAF:* Use After Free is a heap vulnerability where a process can (re)use a piece of memory after it is freed. This can lead to further vulnerabilities and code execution under the correct circumstances.

*LIBC*: The main library utilized by a Linux system to handle low level interactions with the system.

Toy Binary: A sample program intentionally designed with a vulnerability to facilitate the practice of its execution.

# **Assumptions**

The assumptions made in developing the FOP attack framework revolve around three main aspects. The first is the approach to deal with modern CPU protections, the second deals with the initial PoC to demonstrate the use of FOP against modern CPU protections, and the third is the environment for FOP in the initial PoC. These three assumptions will be the three main recurring principles that appear within the research of FOP and the FOP Mythoclast.

The first assumption is based on the CPU protections of CET for Intel systems and PAC/BTI for ARM systems. The assumption focus on the use of gadgets found and utilized during FOP-based attacks. As both protection systems are in their infancy and have a limited

implementation compared to the theoretical full capabilities, this research only uses gadgets that work as if the testing system has all protections enabled at full capabilities. To oversee the two architectural protections, this research manages them separately. Regarding Intel, the shadow stack and IBT protection are the two main protections to consider. To address the shadow stack, all gadgets used in a FOP-based attack avoid modifying stack return values or the stack register. To address IBT, all FOP gadgets must begin with the ENDBR instruction, this is important as the dispatcher gadget used for FOP is reliant on an indirect call in an Intel environment. These two factors should be compliant with CET even in an environment that does not have full CET capabilities. ARM also has two restrictions, the first will be in relation to PAC. The assumption is that any PAC-verified values must pass correctly. This limits the attack from modifying the stack's return address, as most return addresses utilize this authentication scheme after a function call. The second is based on BTI and is similar to the constraints imposed by Intel's IBT. To limit our exposure to BTI violations, all gadgets must begin with the BTI instruction. These two factors in combination should allow for FOP to bypass the ARM-based protections identified in this research. These four restrictions make up the first assumption.

The second assumption is based on the PoC and the "toy" binary used to demonstrate the initial capabilities of FOP. In this research, the toy binary has a Use After Free (UAF) vulnerability within the heap. Accordingly, this approach assumes that an attacker has the capabilities of an address leak and an arbitrary write into memory; the utilization of the UAF vulnerability allows for the ability to leak values of both the heap and of Libc, this UAF can also lead to the allocation of a chunk of memory at any address. This allows an attacker to write data to a controlled buffer. This assumption is only for the PoC to define the capabilities of FOP in a test environment and not be directly involved in the real-world example.

The final assumption involves the environment of the PoC. To demonstrate the capabilities of FOP and the ability for FOP to stand as its own attack framework, the FOP attack must show that it is versatile enough to work in many different environments. To quickly determine this, this research uses a common environment instead. This research defines a common environment as Libc and its loader. This definition means that all FOP-based gadgets must originate from this library. This restriction extends the attack to not only be possible within one Linux environment, but most, as Libc is the base library loaded at runtime for most dynamic binaries.

## **Scope and Limitations**

The scope of this research is to determine the capabilities of FOP in modern systems while also designing a tool to enhance the capabilities of locating FOP gadgets for further research capabilities. This is determined by focusing on Linux-based environments operating with 64-bit CPUs and programs. This research demonstrates a PoC against the previously discussed vulnerable binary for both Intel and ARM instances to illustrate the capabilities of FOP. The demonstration is in a simplistic environment consisting of FOP gadgets only derived from Libc and its accompanying loader. This is further adapted to work with a real-world target to display the capabilities of FOP for use in a modern CPU context.

As for the tooling, the goal is to further enhance FOP-based gadget finding. The design utilizes a symbolic execution framework to determine gadgets, which allows for the ability to include gadgets that include conditions as a basis of inputs. Having a better understanding of the underlying mechanisms that a gadget could employ leads to more useful gadgets and to faster FOP chain designs.

The limitations of this research revolve around the ability to evaluate systems that fully implement modern CPU protections. The strict restrictions on gadget use and emulation of CPU protection designs alleviate these limitations. Combining these two aspects allows for an approach to align with modern CPU protections.

#### **Chapter Summary**

This chapter has defined the context of the research and the approaches necessary to define FOP as a successful substitute for similar code-reuse attacks. Additionally, it determined the basis for what FOP shall accomplish and how to implement tooling to find FOP-based gadgets. As mentioned earlier in this chapter, there is a gap in reliable declarations of FOP in modern 64-bit CPU-based protection environments. This lack of knowledge of FOP attacks allows for better approaches to finding FOP gadgets and testing in simplistic Linux environments to better define the capabilities of FOP. The restrictions this research implements demonstrate the direct relation between FOP and CPU protections offered by both Intel and ARM. This defines the project as the research done to expand FOP-based attacks.

The next chapter will begin to further refine the history and use of code-reuse attacks along with FOP. This conveys an understanding of how history has influenced the approaches needed to limit code-reuse attacks in the modern age.

# **CHAPTER 2**

#### RELATED WORK

Chapter 1 gave an introduction and overall guidance on this dissertation while defining the main topic of this research: Examining the use of Function-Oriented Programming in environments with modern CPU protections. Chapter 1 defined the motivation and background of the research and the intended approaches to satisfy the solution.

Chapter 2 is the literature review of the main components related to this research. This chapter will start with a review of memory corruption, leading to code-reuse attacks, examine protections and designs to circumvent code-reuse attacks, and end with a further in-depth look at FOP. These topics together will culminate in an understanding of the background for the subject as well as giving a review of previous solutions and the history of the subject.

# **Memory Corruption**