The Vault

https://prism.ucalgary.ca

Open Theses and Dissertations

2023-12-08

# Energy-Efficient Workload Placement with Bounded Slowdown in Disaggregated Datacenters

### Sefati, Amirhossein

Sefati, A. (2023). Energy-efficient workload placement with bounded slowdown in disaggregated datacenters (Master's thesis, University of Calgary, Calgary, Canada). Retrieved from https://prism.ucalgary.ca. https://hdl.handle.net/1880/117679 Downloaded from PRISM Repository, University of Calgary

#### UNIVERSITY OF CALGARY

Energy-Efficient Workload Placement with Bounded Slowdown in Disaggregated Datacenters

by

Amirhossein Sefati

A THESIS

## SUBMITTED TO THE FACULTY OF GRADUATE STUDIES IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

GRADUATE PROGRAM IN COMPUTER SCIENCE

CALGARY, ALBERTA DECEMBER, 2023

© Amirhossein Sefati 2023

#### Abstract

Disaggregated Data Center (DDC) is a modern datacenter architecture that decouples hardware resources from monolithic servers into pools of resources that can be dynamically composed to match diverse workload requirements. While disaggregation improves resource utilization, it could negatively impact workload slowdown due to the latency of accessing disaggregated resources over the datacenter network. To this end, we consider CPU and memory disaggregation and conduct measurements to experimentally profile several popular datacenter workloads in order to characterize the impact of disaggregation on workload execution slowdown. We then develop a workload placement algorithm, called Iterative Rounding-based Placement (IRoP), that given a set of workloads, determines where to place each workload (*i.e.*, on which CPU) and how much local and remote memory is allocated to it. The key insight in designing IRoP is that the impact of remote memory latency on slowdown can be substantially masked by assigning workloads to higher-performing CPUs, albeit at the cost of higher power consumption. As such, IRoP aims to find a workload placement that minimizes the DDC power consumption while respecting a bounded slowdown for each workload. We provide extensive simulation results to demonstrate the flexibility of IRoP in providing a wide range of trade-offs between power consumption and workload slowdown. We also compare IRoP with several existing baselines. Our results indicate that IRoP can reduce power consumption and slowdown in the considered scenarios by up to 8% and 12%, respectively.

# Preface

This thesis is an original work by the author. Parts of this research have been published in the 19th International Conference on Network and Service Management (CNSM) in October 2023.

All plots in this thesis were created using the Matplotlib library in Python. All other figures are either original works by the author or adaptations or inspired by other works that are cited in the figures' captions.

# Acknowledgements

I would like to express my sincere appreciation to my supervisor, Professor Majid Ghaderi, for his invaluable guidance and insights throughout this research. His expertise has been instrumental in shaping the outcome of this project. Additionally, I am deeply grateful for the support and encouragement I have received from my friends, colleagues, and family. Their input and motivation have played a significant role in the successful completion of this thesis.

I would also express my gratitude to Dr. Mahdi Dolati, my mentor, for his support and guidance on multiple occasions.

Since we're using  $LAT_EX$  and the memoir package, we should thank Don Knuth, Leslie Lamport, and Peter Wilson.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>These are the authors of [26, 28, 56].

To my parents and to my wife, who always supported me.

# **Table of Contents**

| Abstra                                                                   | let                                                                                                                                                                                                                                                    | ii                                                                                                                                  |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Prefac                                                                   | e                                                                                                                                                                                                                                                      | ii                                                                                                                                  |

| Ackno                                                                    | wledgements                                                                                                                                                                                                                                            | v                                                                                                                                   |

| Dedica                                                                   | tion                                                                                                                                                                                                                                                   | $\mathbf{v}$                                                                                                                        |

| Table (                                                                  | of Contents v                                                                                                                                                                                                                                          | ii                                                                                                                                  |

| List of                                                                  | Figures vi                                                                                                                                                                                                                                             | ii                                                                                                                                  |

| List of                                                                  | Tables                                                                                                                                                                                                                                                 | x                                                                                                                                   |

| List of                                                                  | Symbols, Abbreviations, and Nomenclature                                                                                                                                                                                                               | x                                                                                                                                   |

| <ol> <li>Intr<br/>1.1<br/>1.2</li> <li>1.3</li> <li>1.4</li> </ol>       | MotivationMotivationThesis Objective1.2.1Study Workload Slowdown in DDCs1.2.2Develop a Workload Placement AlgorithmThesis Contribution1.3.1Workload Profiling Framework1.3.2Workload Placement Algorithm1.3.3Evaluation and ResultsThesis Organization | $\begin{array}{c} 1 \\ 1 \\ 5 \\ 5 \\ 6 \\ 6 \\ 7 \\ 8 \\ 9 \end{array}$                                                            |

| <ul> <li>2 Bac<br/>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> </ul> | Datacenter Architectures12.1.1 Traditional Datacenters (TDCs)12.1.2 Logically Disaggregated DCs12.1.3 Physically Disaggregated DCs1Networking Protocols in Datacenters2DDC Interfaces2Related Works22.4.1 Power Consumption22.4.2 Workload Slowdown2   | 2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>2<br>3<br>2<br>4<br>2<br>6<br>2<br>2<br>3<br>2<br>4<br>2<br>6<br>2<br>8 |

| 3  | <ul> <li>3.1 Datacenter Model</li></ul>                                                                                                               | <b>31</b><br>32<br>35<br>37<br>39<br>41      |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|    |                                                                                                                                                       | 43                                           |

| 4  | 4.1Workload Placement                                                                                                                                 | <b>46</b><br>49<br>50<br>52                  |

| 5  | <ul> <li>5.1 Fixing Memory Ratios</li> <li>5.2 Workload Placement Phase</li> <li>5.3 Algorithm Analysis</li> <li>5.3.1 Approximation Ratio</li> </ul> | 55<br>58<br>60<br>62<br>62<br>64             |

| 6  | <ul> <li>6.1 Methodology</li></ul>                                                                                                                    | 67<br>68<br>68<br>70<br>74<br>78<br>83<br>83 |

| 7  | 7.1       Conclusion                                                                                                                                  | <b>91</b><br>91<br>93<br>94                  |

| Bi | bliography                                                                                                                                            | 96                                           |

# List of Figures

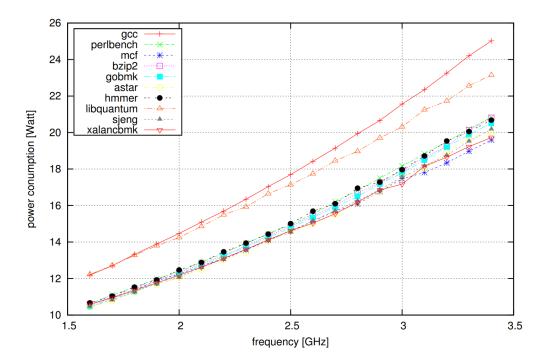

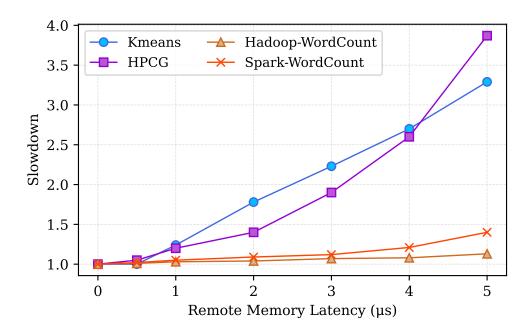

| $1.1 \\ 1.2$                                                                              | Power consumption of SPEC Integer benchmarks on Core i7 SandyBridge. [47] Workload slowdown as remote memory access latency increases. The local memory ration is fixed at 25%. The x-axis shows the amount of additional latency when accessing remote memory compared to local memory | 3<br>4         |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| $2.1 \\ 2.2$                                                                              | Different Architectures of Data Centers                                                                                                                                                                                                                                                 | 13             |

| $2.3 \\ 2.4$                                                                              | tional DC comprised of servers and a storage area network. [3]                                                                                                                                                                                                                          | 15<br>19<br>20 |

| $3.1 \\ 3.2 \\ 3.3$                                                                       | Disaggregation model used in this paper                                                                                                                                                                                                                                                 | 33<br>34       |

|                                                                                           | the switch. [33]                                                                                                                                                                                                                                                                        | 35             |

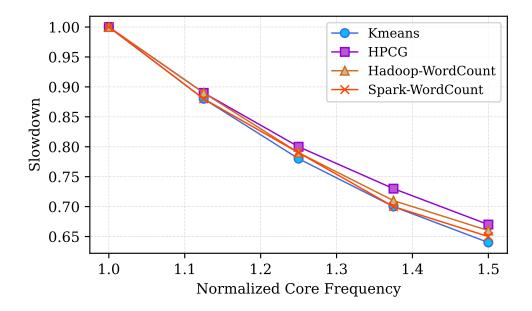

| 3.4<br>3.5                                                                                | Workload slowdown as the assigned remote memory ratio increases. The injected latency for remote memory is fixed at 5 $\mu$ s                                                                                                                                                           | 41             |

| 5.5                                                                                       | slowdown means faster execution                                                                                                                                                                                                                                                         | 44             |

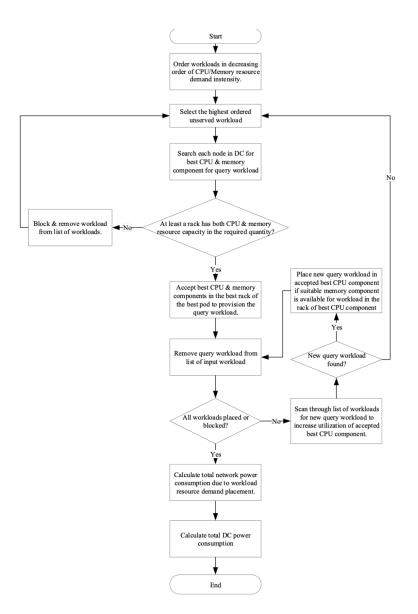

| $     \begin{array}{r}       6.1 \\       6.2 \\       6.3 \\       6.4     \end{array} $ | Flowchart of HEEP                                                                                                                                                                                                                                                                       | 70<br>71<br>72 |

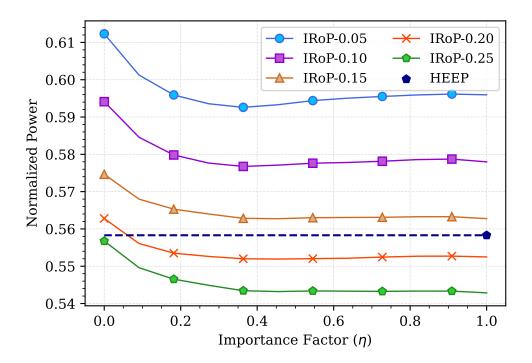

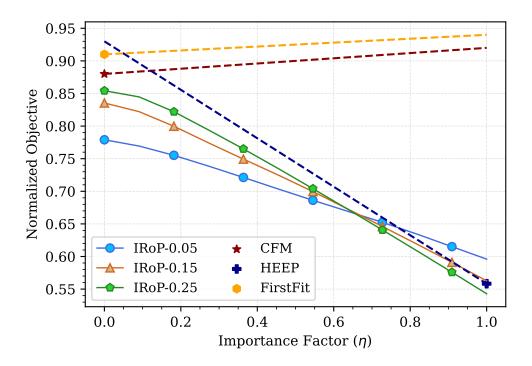

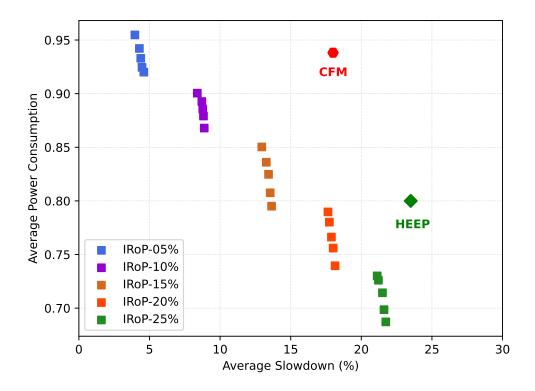

| 6.5                                                                                       | to CFM                                                                                                                                                                                                                                                                                  | 76<br>77       |

| 6.6                                                                                       | Power consumption of IRoP for different values of slowdown threshold com-                                                                                                                                                                                                               |                |

| 6.7                                                                                       | pared to HEEP                                                                                                                                                                                                                                                                           | 80<br>82       |

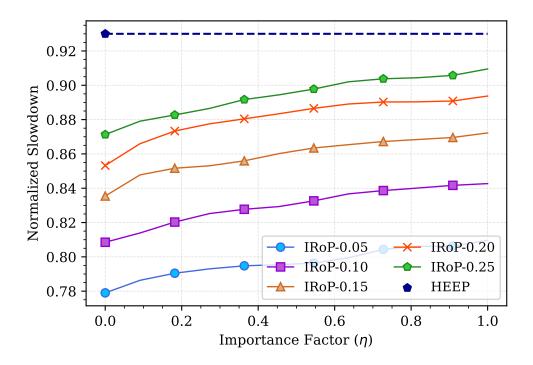

| 6.8                                                                                       | Weighted sum of slowdown and power of IRoP for different values of slowdown                                                                                                                                                                                                             |                |

| 6.9                                                                                       | threshold compared to baselines                                                                                                                                                                                                                                                         | 85<br>86       |

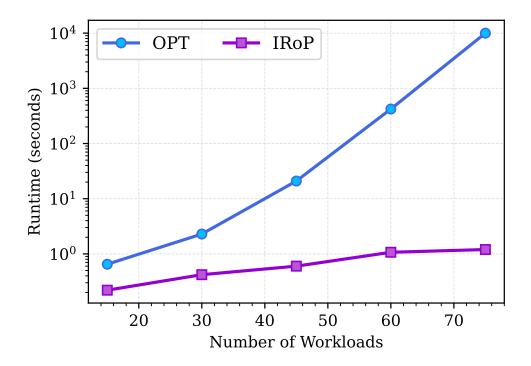

| 6.10                                                                                      | Impact of the number of workloads on the run-time of IRoP and OPT. The number of CPU modules is fixed at 30                                                                                                                                                                             | 87             |

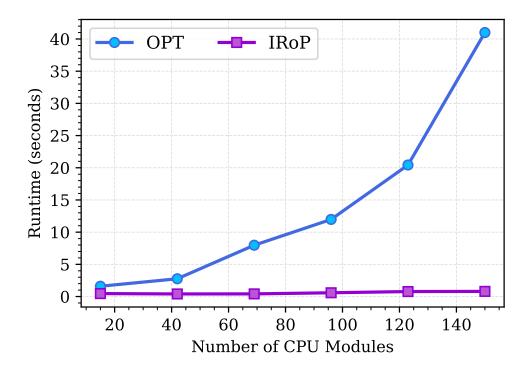

| 6.11                                                                                      | Impact of the number of CPU modules on the run-time of IRoP and OPT.<br>The number of workloads is fixed at 30.                                                                                                                                                                         | 88             |

# List of Tables

| 2.1 | Network Requirements in DDCs [13]                                                                                             | 21 |

|-----|-------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Important Notations.       Profiled Workloads.         MSE of Piece-Wise Linear Approximation for the Impact of Remote Memory |    |

|     | Model                                                                                                                         |    |

| 4.1 | Decision Variables.                                                                                                           | 46 |

|     | CPU Modules Used in Evaluations                                                                                               |    |

# List of Symbols, Abbreviations, and Nomenclature

| Symbol        | Definition                                                               |

|---------------|--------------------------------------------------------------------------|

| $\mathcal{C}$ | Set of all computation-cable modules                                     |

| $F_c$         | Frequency of CPU cores in module $c$                                     |

| $N_c$         | Number of CPU cores in module $c$                                        |

| $L_c$         | Amount of local memory in module $c$                                     |

| $I_c^s$       | Static power consumption of module $c$                                   |

| $I_c^d$       | Dynamic power consumption of module $c$                                  |

| M             | Total amount of remote memory in DDC                                     |

| $\mathcal{W}$ | Set of all workloads                                                     |

| $ u_w$        | Number of cores requested by workload $w$                                |

| $\phi_w$      | Processor frequency requested by workload $w$                            |

| $\mu_w$       | Total amount of memory requested by workload $\boldsymbol{w}$            |

| $P^f_w(.)$    | Model to show the frequency effect on workload slowdown $\boldsymbol{w}$ |

| $P_w^m(.)$    | Model to show the memory effect on workload slowdown $\boldsymbol{w}$    |

| $\Delta_w$    | Maximum acceptable slowdown of workload $\boldsymbol{w}$                 |

| $z_c$         | Activation of module $c$                                                 |

| $y_{w,c}$     | Assignment of workload $w$ to module $c$                                 |

| $x_w$         | Fraction of local to total requested memory of workload $\boldsymbol{w}$ |

| $f_w$ | Frequency of allocated CPU to workload $\boldsymbol{w}$ |

|-------|---------------------------------------------------------|

| $u_c$ | CPU utilization of module $c$                           |

| Abbreviations | Definition                           |  |

|---------------|--------------------------------------|--|

| DC            | Data Center                          |  |

| DDC           | Disaggregated Data Center            |  |

| CPU           | Central Processing Unit              |  |

| RAM           | Random Access Memory                 |  |

| NIC           | Network Interface Card               |  |

| ToR           | Top of Rack                          |  |

| DIMM          | Dual In-line Memory Module           |  |

| QoS           | Quality of Service                   |  |

| SLA           | Service Level Agreement              |  |

| IRoP          | Iterative Rounding-based Placement   |  |

| HPCG          | High Performance Conjugate Gradients |  |

| MILP          | Mixed-Integer Linear Problem         |  |

| SAN           | Storage Area Network                 |  |

| NAS           | Network-Attached Storage             |  |

| SoC           | System-on-Chip                       |  |

| RDMA          | Remore Direct Memory Access          |  |

| API           | Application Programming Interface    |  |

| OS            | Operating System                     |  |

| VM            | Virtual Machine                      |  |

| CR            | Contention Ratio                     |  |

| BFS           | Breadth-First Search                 |  |

| DRAM          | Dynamic Random Access Memory         |  |

| DWLP          | Disaggregated Workload Placement     |  |

|               |                                      |  |

F-DWLP

DWLP with Fixed Memory Ratios

### Chapter 1

# Introduction

#### 1.1 Motivation

Today's data centers (DCs) are designed based on a server-centric model. The building block of this model is a monolithic server that includes all necessary hardware resources such as CPU, RAM, and NIC to run typical datacenter workloads. One of the main limitations of the server-centric model is the difficulty to achieve full resource utilization due to *resource stranding*, where a server that has used up one type of resource cannot run more workloads even though it may still have large amounts of other resources available. Server virtualization helps improve the utilization of hardware resources, but it cannot eliminate the problem completely as stranded resources on one server cannot be allocated to virtual machines running on other servers.

Indeed, measurements in production DCs show that the average utilization of hardware resources is relatively low. For example, a recent report [31] reveals that 80 percent of the time datacenter clusters utilize 10 - 30% of their CPU capacities and more than half of the time the average memory utilization is around 50%. Also, Google and Alibaba report that the memory utilization of their clusters is around 60% [51, 32]. In addition to equipment costs, this under-utilization results in elevated power consumption, as static power consumption of fixed-ratio servers is significant [3], which has financial and environmental consequences.

For example, data centers consumed around 1.5% of the total power consumed in the U.S. in 2018, amounting to \$4.5 billion [9]. Addressing the stranded resource problem has become even more critical as the model of computing is evolving in response to emerging datacentric workloads such as those in Machine Learning/Artificial Intelligence. These workloads require large amounts of processing capacity as well as memory to work efficiently. Simply over-provisioning servers with more hardware resources not only exacerbates the stranded resource problem but faces practical limitations (*i.e.*, limited DIMM slots for memory on the server board).

To overcome the limitations of the server-centric model, a *resource-centric* model is proposed for datacenters based on resource disaggregation. In a disaggregated datacenter (DDC), server hardware resources are physically or logically disaggregated into homogeneous resource pools from which resources can be allocated to workloads on demand. The scale of disaggregation can be within a single rack, a group of racks (*i.e.*, a cluster), or the entire datacenter. One of the most crucial components of a disaggregated architecture at any scale is the network interconnecting resource pools. Recent advances in low-latency networking demonstrate that microsecond-scale host-to-host latency is achievable in datacenters [14], with sub-microsecond latency within the host networking stack [21]. Nevertheless, even such network latencies are still high when accessing remote disaggregated memory, noting that accessing local memory on the same server box takes the order of tens of nanoseconds [13]. As memory access latency increases, execution slows down for those workloads that are memory intensive.

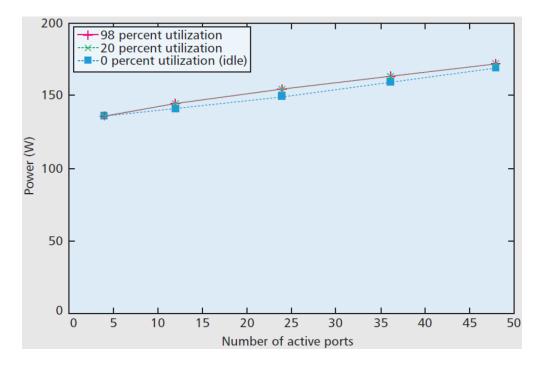

To compensate for the slower memory access, workloads can be assigned to higherperforming CPUs, *e.g.*, CPUs with higher compute capacity or higher clock frequency. However, based on the work of the authors in [47], this strategy increases datacenter power consumption (the higher the frequency, the higher the power consumption), and consequently, infrastructure costs increase. Fig. 1.1 shows how increasing the frequency of a Core i7 CPU module increases its power consumption.

Different workloads have different levels of sensitivity to memory access latency. In

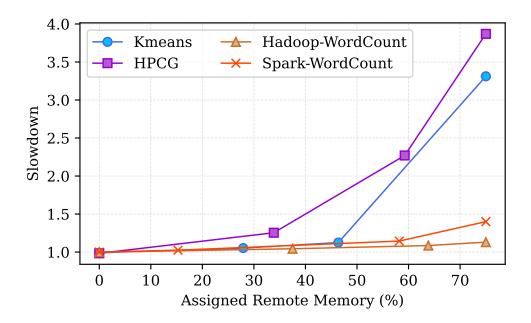

Figure 1.1: Power consumption of SPEC Integer benchmarks on Core i7 SandyBridge. [47] Fig. 1.2, we have plotted measured *slowdown* for several popular datacenter workloads (see Section 3 for details). The slowdown of a workload is defined as below:

$$Slowdown = \frac{\text{Workload completion time when executed in a disaggregated DC}}{\text{Workload completion time when executed in a traditional DC}}$$

(1.1)

The figure clearly shows that some workloads such as Kmeans [50] are highly sensitive to memory access latency, while others such as WordCount [42] show negligible sensitivity. This behavior can be exploited to minimize the impact of memory disaggregation on workload slowdown. Recently, a few works have considered optimizing workload slowdown through run-time management [24, 34]. However, run-time management alone is not sufficient as it cannot help during the startup time. For example, workloads with a low ratio of hot to cold pages severely suffer from insufficient low-latency memory at startup [35]. Moreover, when the starting resource configuration of a workload is far from optimal, it suffers from workload slowdown while the run-time management tries to transition the workload to an optimal resource configuration. Such approaches incur substantial run-time management. Admissible placement of such jobs requires information about their sensitivity to different types

Figure 1.2: Workload slowdown as remote memory access latency increases. The local memory ration is fixed at 25%. The x-axis shows the amount of additional latency when accessing remote memory compared to local memory.

of memory at deployment time. Therefore, methods that follow a run-time management paradigm and do not provide a mechanism to incorporate performance-related information at the deployment time can not guarantee a consistent quality of service (QoS). As such, in addition to run-time management, careful workload placement at the time of deployment is needed to ensure workload slowdown is not unacceptably degraded due to remote memory access latency while minimizing datacenter power consumption. The workload placement determines: i) which CPU should we choose to run the workload on, and ii) how much local and remote memory should we allocate to it. Several works have considered workload placement in DDC. However, these works focus on either optimizing workload slowdown [57, 4, 14] or minimizing datacenter power consumption [38, 37, 40, 43, 3, 45], without considering the trade-off between the two. In this thesis, we aim to study workload placement with bounded slowdown, *i.e.*, guaranteeing slowdown does not exceed a pre-specified target level based on service-level agreements (SLAs), while minimizing DDC power consumption.

#### 1.2 Thesis Objective

The primary objective of this thesis is to explore the impact of resource disaggregation on workload slowdown in disaggregated datacenters. Specifically, we focus on CPU and memory disaggregation and conduct measurements to experimentally profile various data center workloads. This profiling enables us to characterize the impact of disaggregation on workload execution slowdown. Then, we propose a novel workload placement algorithm, called IRoP, which aims to minimize DDC power consumption while ensuring a bounded slowdown for each workload. The algorithm optimizes the placement of workloads on CPUs and determines how much local and remote memory should be allocated to each workload, ultimately helping data center owners reduce their power costs while respecting the servicelevel agreements (SLAs). We emphasize achieving a balance between power consumption and slowdown to enhance data center efficiency. The specific objectives of this thesis are explained in the following subsections.

#### 1.2.1 Study Workload Slowdown in DDCs

We consider CPU and memory disaggregation in DC, where each CPU is provisioned with a fixed (small) amount of local memory but can access remote memory modules, which are considerably larger, over the datacenter network. As it will introduce significantly higher latency for accessing memory, the first objective is to devise a technique to accurately profile workloads in order to comprehensively model the impact of remote memory latency and CPU processing capacity on the workload slowdown. Specifically, we consider several popular workloads and run each of them in isolation on a modified Linux system which allows us to change the local and remote memory ratios as well as scale the CPU frequency. We then measure the completion time of each workload and approximate the impact of remote memory latency and CPU frequency on workload slowdown using piece-wise linear functions.

#### 1.2.2 Develop a Workload Placement Algorithm

In the pursuit of optimizing datacenter operations, two crucial objectives stand at the forefront: reducing power costs and ensuring timely completion of workloads. Conventional datacenters often suffer from *resource stranding*, where certain resources remain underutilized, leading to increased power consumption. On the other hand, the advent of disaggregated datacenters introduces a new challenge - the *slowdown* of workloads caused by the higher latency associated with accessing remote memory. Given these critical concerns, our thesis aims to address this dilemma by devising a rapid algorithm for power-efficient workload placement in disaggregated datacenters, all while ensuring that each workload operates within a predefined threshold of slowdown. This innovative approach seeks to strike a balance between power consumption and workload slowdown, offering a practical and effective solution for enhancing the efficiency and adaptability of datacenter infrastructures.

#### **1.3** Thesis Contribution

In this section, we will provide a comprehensive overview of the significant contributions made in this research thesis, which addresses the challenges of optimizing resource allocation in Disaggregated Data Centers (DDCs). Our contributions involve the development of a novel Workload Profiling Framework and the proposal of an efficient Workload Placement Algorithm, both aimed at minimizing power consumption while ensuring performance objectives for each workload.

#### 1.3.1 Workload Profiling Framework

The first major contribution of this thesis is the introduction of a robust Workload Profiling Framework. In modern DDC environments, the performance of workloads can be significantly impacted by remote memory access latency and CPU processing capacity. To tackle this challenging issue, we designed a profiling framework that accurately models the sensitivity of various workloads to memory access latency and CPU frequency. We define *workload slowdown* as the ratio of completion time when the workload is executed under a disaggregated environment compared to a traditional data center. The key innovation of our approach lies in the use of piece-wise linear functions to represent the relationship between workload slowdown and these two critical factors.

We embarked on an in-depth exploration to develop the Workload Profiling Framework. Our research involved studying and analyzing a diverse range of workloads representative of real-world applications and scenarios. By carefully capturing the slowdown characteristics of these workloads under varying conditions of remote memory access and CPU frequency, we formulated piece-wise linear models that accurately depict the impact of these factors on workload slowdown.

To validate the effectiveness of our profiling models, we conducted extensive experiments in a controlled environment. For this purpose, we made intricate modifications to the latest version of the Linux Kernel (version 6.1), allowing us to inject artificial delays when accessing the swap area. These delays closely mimic the real-world remote memory latency experienced in a DDC. The experimental results showcased the high accuracy and reliability of our profiling models in characterizing real-world workload slowdown. By enabling us to understand the sensitivity of different workloads to remote memory and CPU frequency variations, this framework lays the foundation of an efficient workload placement algorithm in DDCs.

#### 1.3.2 Workload Placement Algorithm

The second major contribution of this research is the proposal of an innovative Workload Placement Algorithm. Armed with the valuable insights gained from our Workload Profiling Framework, we formulated the workload placement problem in DDCs as a mixed-integer linear problem (MILP). We recognized that while minimizing workload slowdown is crucial, we must also take into account the overarching objective of reducing power consumption in the DDC.

The formulation of the MILP is an essential step in addressing the workload placement

problem effectively. To this end, we built upon the comprehensive MILP model proposed in a prior work [3], which accurately represents and models the power consumption of resources within the DDC. However, we acknowledged that directly solving the MILP would be computationally expensive, as it is inherently NP-hard. As a result, we focused on devising a fast polynomial-time algorithm, which we named IRoP, to efficiently solve the workload placement problem while considering both power consumption and workload slowdown.

The design of IRoP is based on transforming the MILP problem into a modified variant of the multi-dimensional bin packing problem [8]. Leveraging the framework of deterministic rounding of relaxed integer programs, we ensured that IRoP provides high-quality approximations while being computationally efficient. By striking an optimal balance between power consumption and workload slowdown, IRoP efficiently allocates resources in the DDC and delivers near-optimal solutions to the workload placement problem.

#### 1.3.3 Evaluation and Results

We recognized the paramount importance of evaluating the performance and effectiveness of our proposed IRoP algorithm. Therefore, we conducted extensive experiments, evaluating its utility across a wide range of realistic scenarios and workloads. Our evaluation metrics revolved around power consumption and workload slowdown, both of which are critical aspects of DDC resource allocation.

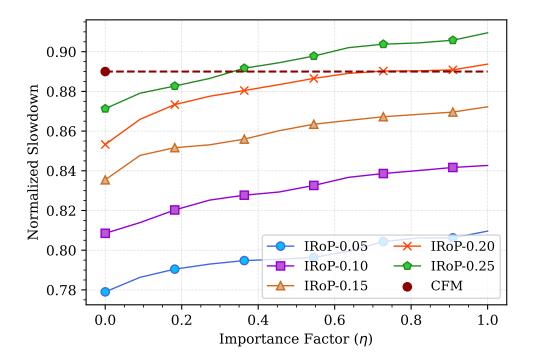

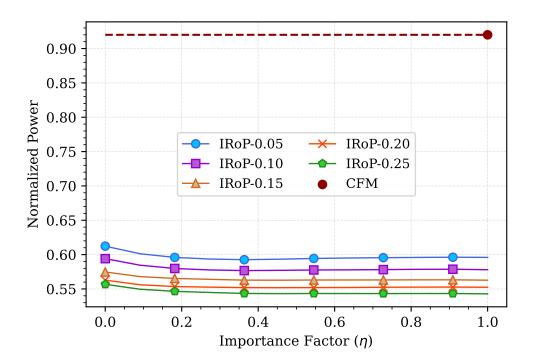

The results of our experiments were highly promising, further affirming the strength of our contributions. The IRoP algorithm demonstrated significant reductions in both power consumption and workload slowdown, achieving impressive improvements of up to 8% and 12%, respectively, in the considered scenarios. These results not only highlighted the efficacy of our proposed algorithm but also showcased its practical applicability in real-world DDC environments.

In summary, the main contribution of this thesis can be summed up as follows:

• We present a framework for profiling workload slowdown with respect to remote memory and CPU processing capacity using simple piece-wise linear functions. We empirically show that the proposed functions provide a highly accurate estimation of real-world workload slowdown.

- We formulate workload placement in DDCs as a MILP problem whose objective is to minimize a combination of total power consumption and workload slowdown. We then design an efficient approximation algorithm, called IRoP, to solve the MILP problem based on the deterministic rounding framework and analyze its theoretical performance.

- We conduct extensive experiments to evaluate the performance and utility of IRoP in terms of power consumption and workload slowdown in a variety of realistic scenarios. Our results indicate that IRoP reduces both power consumption and slowdown in the considered scenarios by up to 8% and %12, respectively.

#### 1.4 Thesis Organization

The remainder of this thesis is organized as follows:

Chapter 2: Background and Related Works provides a comprehensive overview of networking protocols, data center interfaces, and related research works in the context of physically disaggregated data centers. It highlights the challenges posed by high latency and CPU load in such environments and explores the evolution of networking protocols, including RDMA and InfiniBand, to address these issues. Additionally, it discusses the categorization of interfaces into clean-slate and swap-based designs, emphasizing their impact on workload management. The chapter also delves into the extensive research efforts aimed at optimizing resource allocation in disaggregated data centers, focusing on minimizing workload slowdown, power consumption, and maximizing utilization. This wealth of information forms a foundational understanding of the key concepts and challenges in the field of resource disaggregation within data centers.

Chapter 3: Profiling Datacenter Workloads provides a comprehensive overview of the datacenter model under consideration and focuses on developing workload profiles that capture the impact of resource disaggregation on workload slowdown. It introduces the key elements of the datacenter model, including resource disaggregation, power consumption modeling, and workload characteristics. The chapter then dives into the detailed profiling of popular datacenter workloads, analyzing the effects of remote memory access and CPU frequency on workload performance. This profiling equips datacenter operators with valuable insights for optimizing resource allocation, enhancing datacenter efficiency, and meeting the unique requirements of diverse workloads.

**Chapter 4:** Workload Placement Problem Formulation introduces a thorough exploration of the fundamental elements and constraints involved in formulating the Disaggregated Workload Placement (DWLP) problem. It introduces essential decision variables, constraints, and the objective function that underpins the optimization framework for allocating workloads to CPU modules in a disaggregated data center. Furthermore, it highlights the critical considerations related to workload slowdown, power consumption modeling, and optimization objectives, emphasizing the trade-off between workload performance and power efficiency. This chapter serves as the foundational framework upon which subsequent chapters will build to address the efficient operation of disaggregated data centers.

Chapter 5: Proposed Algorithm for Workload Placement presents a novel algorithm, named "Iterative Rounding-based Placement" (IRoP), designed to address the complex problem of workload placement in disaggregated data centers. It presents a comprehensive theoretical analysis of IRoP, including its approximation ratio and runtime complexity. The algorithm's theoretical guarantees, such as a bounded approximation ratio and polynomial-time complexity, underscore its effectiveness and efficiency in providing nearoptimal solutions for data center resource allocation challenges. This chapter equips data center operators and researchers with a powerful tool to optimize performance, power consumption, and resource utilization in modern data center infrastructures.

**Chapter 6: Performance Evaluation** provides a comprehensive methodology and analysis framework for assessing the efficacy of different workload allocation strategies within a large-scale disaggregated data center environment. It describes the environment setup, alternative algorithms for comparison, and evaluates performance based on various metrics such as total slowdown, total power consumption, and a weighted sum of both. Additionally, it explores the runtime scalability of the proposed algorithm (IRoP) in comparison to an optimization benchmark (OPT). Overall, this chapter offers a detailed foundation for understanding and optimizing data center operations in a complex and dynamic context.

Chapter 7: Conclusion and Future Works offers a recapitulation of the key findings and contributions of the research, emphasizing the effectiveness of the IRoP algorithm in optimizing workload placement within Disaggregated Data Centers (DDCs). Additionally, it outlines promising avenues for future research, including the expansion of the power consumption model, development of orchestration strategies, real-world implementation, profiling of different workloads, and the integration of AI and machine learning techniques. This chapter serves as both a summary of the accomplishments and a roadmap for continued advancements in the field of DDC resource allocation and management.

### Chapter 2

# **Background and Related Works**

This chapter provides the background knowledge required for understanding the proposed solutions in this thesis. First, we provide an overview of disaggregation in the datacenters, networking protocols, and interfaces. Then, we elaborate on the requirements that a resource allocation algorithm should respect when used in a DDC. Finally, related works are studied and investigated in this chapter.

#### 2.1 Datacenter Architectures

In this section, we review the main architectures of datacenters and we bring the benefits of using a disaggregated datacenter over a traditional one.

#### 2.1.1 Traditional Datacenters (TDCs)

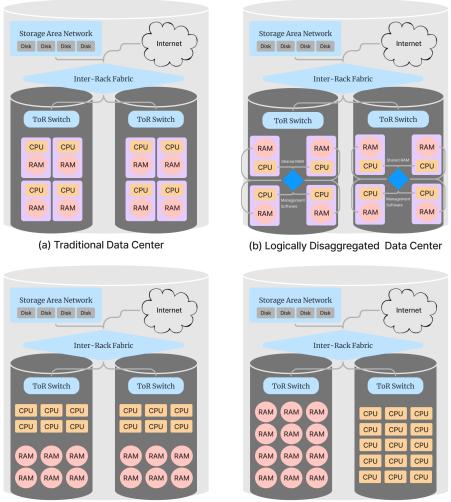

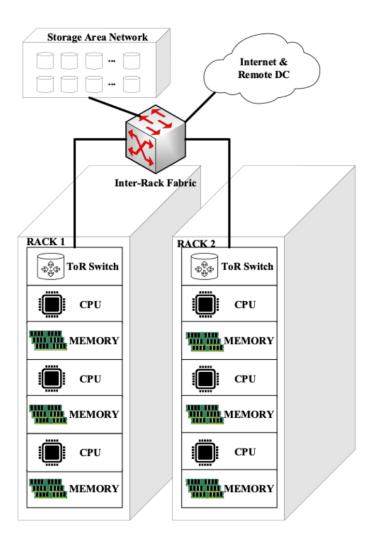

TDCs, an abbreviation for traditional data centers, are distinct for their utilization of monolithic servers, where different components such as CPU and memory are densely integrated into a single hardware unit. This architectural paradigm, clearly illustrated in Fig. 2.1a, gives rise to a series of limitations that warrant a deeper examination to uncover the potential for improvement and innovation.

The first noteworthy limitation that arises in this traditional server-centric model is the

(C) Physically Disaggregated DC: Rack-Scale (D) Physically Disaggregated DC: Cluster-Scale

Figure 2.1: Different Architectures of Data Centers.

challenge of low resource utilization, particularly considering the diverse and varying nature of workload requests. To elucidate this concern, envision a scenario where a single server is equipped with an impressive 16 CPU cores and an abundant 64 GB of memory. However, suppose a specific job only necessitates 16 CPU cores and a modest 16 GB of memory to fulfill its requirements. In this case, the remaining 48 GB of memory remains largely untapped and unutilized, representing an inefficiency that translates into increased power consumption and higher maintenance costs [45].

The second limitation lies in the inherent challenges associated with incorporating or

updating individual components within this server design. Due to the tightly coupled nature of these monolithic servers, introducing changes or advancements often entails modifying the entire server unit. As a result, embracing new and more effective technologies that may enhance efficiency and optimization becomes cumbersome and cost-prohibitive [11]. The lack of flexibility in the face of technological advancements poses a substantial obstacle for data centers seeking to stay on the cutting edge of innovation.

Additionally, the tightly coupled architecture in traditional data centers can lead to significant consequences if any of the integrated components within a server encounter a malfunction or failure. In such instances, the entire server becomes adversely affected, resulting in downtime and service disruptions [7]. The lack of fault tolerance and redundancy in this setup poses reliability challenges that may hinder seamless operations in critical situations.

Moreover, the limitations of traditional data centers extend beyond their architectural design and resource utilization challenges. Another significant concern is their environmental impact and power consumption. As data centers continue to grow in scale and complexity to accommodate the escalating demand for digital services, their power requirements have surged. The power consumption of TDCs not only contributes to higher operational costs for data center operators but also raises environmental concerns, given the substantial carbon footprint associated with traditional power sources.

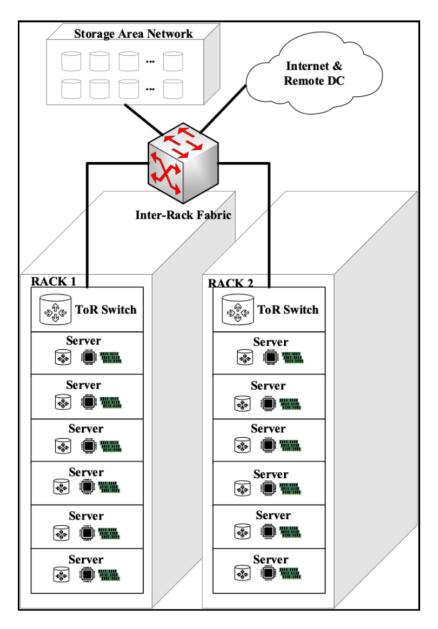

In conclusion, as data centers strive to evolve and adapt to meet the ever-growing demands of modern applications and services, especially with the rapid rise of resource-intensive technologies such as artificial intelligence (AI) and machine learning (ML) applications, addressing these limitations becomes imperative. By finding innovative solutions to enhance resource utilization, improve flexibility, and ensure robustness in the face of potential hardware failures, data centers can aim to achieve higher efficiency, cost-effectiveness, and adaptability in their operations. The exploration of alternative data center architectures, such as logically or physically disaggregated models, presents promising avenues to overcome these challenges and embrace a more dynamic and agile approach to meet the diverse needs of modern computing workloads. Fig. 2.2 shows a more detailed traditional datacenter that uses standalone servers in each rack and does not require external communication between CPU and memory modules. In this architecture, networking is only used for external applications and it is generally not a vital component for the servers to execute workloads. Also, as a result of accessing only local memory, there is no slowdown for the workloads running in TDCs.

Figure 2.2: Traditional datacenter infrastructure. The figure shows two racks in a traditional DC comprised of servers and a storage area network. [3]

#### 2.1.2 Logically Disaggregated DCs

Logically disaggregated data centers, akin to traditional ones, retain servers as the fundamental unit of computation, interconnected through low-latency network technologies, as depicted in Fig.2.1b. Within this architectural model, one global software plays a vital role in effectively managing access to remote memory, facilitating the utilization of unutilized memory from other servers by various jobs. Consequently, this logical disaggregated design enables the software to intelligently allocate the remaining available memory, which would otherwise go to waste, to cater to other jobs in need of additional memory resources. Additionally, the fault tolerance and redundancy offered by logically disaggregated data centers address the reliability challenges of TDCs. With resources distributed across separate units, a failure in one component does not lead to the collapse of the entire system. Instead, the affected resource unit can be quickly isolated and replaced, ensuring continuous operations and maintaining the availability of critical services. The industry has shown increasing interest in this architecture, owing to its promising advantages [27, 16, 2], with previous studies also having delved into its potential [12].

Despite the benefits it offers, this architecture does not completely eliminate the challenges faced by traditional data centers. The tightly coupled nature of servers introduces certain hurdles related to adoption and reliability. As data centers strive to keep pace with the escalating demands of modern applications and services, tackling these challenges becomes imperative to achieve heightened efficiency, scalability, and fault tolerance in disaggregated data center operations. To this end, exploring innovative solutions that optimize resource utilization, streamline software management, and enhance server interconnectivity will play an important role in shaping the future of logically disaggregated data centers.

In conclusion, logically disaggregated data centers represent a promising evolution in data center architecture, maintaining servers as the core units of computation while enhancing memory allocation through global software management. While this approach addresses some utilization concerns faced by traditional data centers, the journey toward realizing its full potential necessitates overcoming challenges related to server coupling. By strategically exploring and implementing innovative solutions, data centers can aspire to achieve higher levels of efficiency, scalability, and reliability, thereby laying a robust foundation for the seamless execution of modern computing workloads in the digitally transformative landscape.

#### 2.1.3 Physically Disaggregated DCs

Unlike the other two architectures discussed previously, physically disaggregated data centers take the separation of hardware components to a whole new level. This approach marks a notable departure from the traditional monolithic server-centric model and the logically disaggregated architecture. In the case of physically disaggregated data centers, significant advancements have been made historically in disaggregating data storage, leveraging technologies such as storage area networks (SANs) and network-attached storage (NAS) systems. For instance, in a seminal work by the authors of [25], they proposed a flash storage disaggregation method to address complex scenarios where jobs require diverse compute-to-storage resources. Moreover, as far back as 2015, Facebook introduced Yosemite [30], an innovative disaggregated system-on-chip (SoC) that harnessed the power of interconnecting storage components to optimize data handling. Consequently, these architectures, just like the previously mentioned ones, still utilize SANs as an integral part of their design to effectively decouple storage from computation resources, as shown in Fig 2.1.

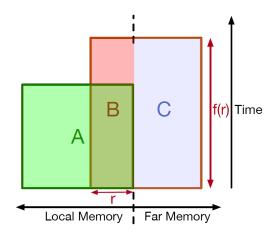

However, the real challenge lies in the disaggregation of CPU and memory components, which forms the struggle of implementing physically disaggregated data centers. In this architecture, the CPU and memory are physically decoupled while remaining interconnected via a fast, low-latency network. Within this dynamic setup, the memory modules are commonly referred to as far [4, 27] or remote [13, 54, 7, 3] memory. This arrangement introduces a novel concept where CPU modules operate in tandem with remote memory, which may be situated on separate servers. The notion of remote memory in this context implies that certain portions of the memory are geographically distant from the CPU, requiring the efficient orchestration of data transfer and access to ensure seamless performance. In many studies (i.e., [49, 7]), it is assumed that the CPU modules should retain at least some amount of local memory, acting as a cache to the remote memory, while the remote memory primarily hosts the main workload codes and datasets. Furthermore, to avoid the undesirable impact of high workload slowdown due to the relatively high access latency of remote memory, the system may intelligently assign available local memory to workloads. By doing so, the total number of accesses to remote memory regions can be minimized, contributing to enhanced overall performance and efficient resource utilization.

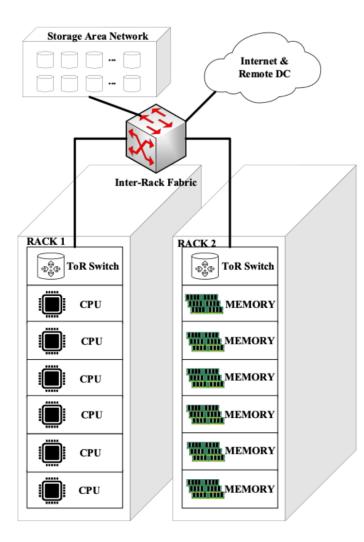

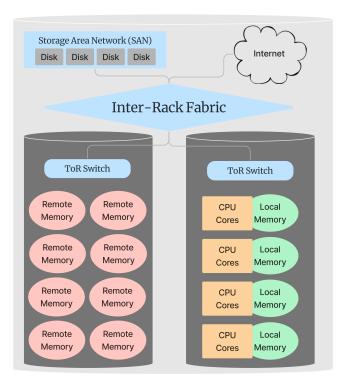

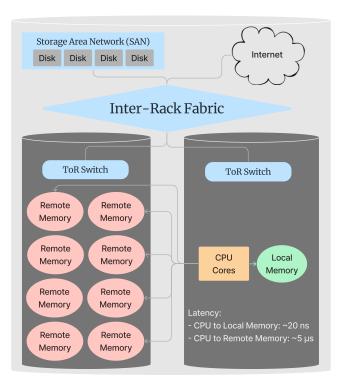

The concept of physically disaggregated data centers manifests itself in two distinct scopes, commonly known as rack-scale and cluster-scale, both depicted in Fig.2.1c and Fig.2.1d, respectively. In the rack-scale model, homogeneous resources (i.e., different modules) are allocated to single-type resource pools within a rack, and each module remains exclusively available to other modules situated within the same rack. A notable example of a rack-scale disaggregated platform is detailed in [19], wherein Huawei presented a novel architecture tailored for big data applications. This design features single-type pools of each module (e.g., CPU, memory, I/O) interconnected by a high-throughput network, enhancing communication and data exchange between components. Fig. 2.3 shows a more detailed rack-scale disaggregated data center that separates CPU and memory modules in each rack.

While the rack-scale approach undoubtedly offers some advantages, such as localized resource management, it does present certain limitations concerning scalability, which might become more apparent as data center demands continue to grow. As a result, researchers and data center operators have sought alternative solutions to address scalability concerns effectively. Cluster-scale architectures adopt a more encompassing approach, where the disaggregation extends across the entire data center. However, in the past, these cluster-scale architectures faced practical challenges due to the inherent complexity of managing network requirements and facilitating efficient traffic between CPU and memory modules located in different racks. This complexity introduced bottlenecks that hindered the widespread adoption of cluster-scale architectures. Nonetheless, recent advancements in high-throughput low-latency network protocols have proven instrumental in making the cluster-scale architecture more practical and viable. These improved protocols enable robust communication

Figure 2.3: Rack-scale Disaggregated DC Infrastructure [3]

and data exchange between various components, mitigating potential bottlenecks and facilitating seamless coordination across the entire data center. Therefore, for the purposes of this thesis and the proposed resource allocation algorithm, we adopt a cluster-scale physically disaggregated model. The cluster-scale approach aligns well with the demands of modern data centers, offering increased flexibility, scalability, and potential for future growth. Fig. 2.4 shows a more detailed cluster-scale disaggregated data center that separates CPU and memory modules cluster-wide.

Figure 2.4: Cluster-scale Disaggregated DC Infrastructure [3]

#### 2.2 Networking Protocols in Datacenters

In a physically disaggregated data center, where CPU and memory are decoupled, the completion time of workloads, especially high latency-sensitive memory-intensive workloads, can suffer significantly due to the inherent high latency associated with accessing remote memory [3]. Recognizing the importance of addressing this issue, recent research has extensively explored the evolution of networking protocols to mitigate the impact of high latency and improve overall system performance.

One notable study [20] extensively reviewed the evolution of networking protocols, particularly in traditional data centers where Ethernet technology and TCP/IP are commonly

| Communication Type  | Latency (ns)  |

|---------------------|---------------|

| CPU - CPU           | 10            |

| CPU - Local Memory  | 20            |

| CPU - Remote Memory | $5\cdot 10^3$ |

| CPU - Disk          | $10^4 - 10^5$ |

Table 2.1: Network Requirements in DDCs [13].

used for data transmission. TCP/IP, being an OS-based networking protocol, imposes tens of microseconds of delay and leads to high server CPU load, which can adversely affect workload slowdown. In an interesting observation made in [60], it was pointed out that dedicating a core to handle high throughput TCP/IP connections, to enhance the workload slowdown, would render that core unusable as a virtual machine, limiting the overall resource utilization.

To address these latency and CPU load challenges, researchers have explored alternative network protocols such as RDMA (Remote Direct Memory Access) over Converged Ethernet (RoCE). RoCE provides lower access latency and significantly reduces the CPU overhead compared to traditional TCP/IP-based solutions. Furthermore, InfiniBand [6], as a dedicated networking stack, offers lower latency, efficient flow control, and reliable lossless transportation of packets, making it a compelling alternative specifically designed for RDMA applications [10, 4, 13].

Recent works in the field have demonstrated impressive achievements in hardware-based memory disaggregation solutions. For instance, the Clio [17] project reported an end-to-end latency of 2.5  $\mu s$  at the median and 3.2  $\mu s$  at the 99th percentile, showcasing its effectiveness in reducing access latencies. Additionally, Google's Aquila [14] proposed an extraordinary 4  $\mu s$  (median) end-to-end latency for Remote Memory Access (RMA) operations within a high-scale cluster of up to 1152 interconnected hosts. This breakthrough was attributed to Aquila's highly integrated NIC (Network Interface Card) and network, enabling ultra-low latency communication.

In addition to these protocols, there is an important study authored by Peter X. Gao and his team *et al.* [13]. This study outlines specific network requirements crucial for resource disaggregation, and you can find a concise summary of these requirements in Table 2.1. After conducting a thorough review of various network protocols and recent advancements, it is evident that the network prerequisites needed to support resource disaggregation are either already in place or expected to be available in the near future.

For the purposes of this thesis, we are working with the assumption of an end-to-end latency of 5  $\mu s$  for accessing remote memory. This assumption sets the stage for our evaluation of the resource disaggregation model and its performance in line with these network requirements. By making the most of these cutting-edge networking solutions, our goal is to attain efficient power consumption and optimize workload slowdown within the context of cluster-scale physically disaggregated data centers.

#### 2.3 DDC Interfaces

In a cluster-scale disaggregated data center, the utilization of local and remote memory by workloads relies on the interface provided by the system. Interfaces in a resource disaggregated model can be broadly categorized into two types [53]. First, we have the *clean-slate* designs that offer application programming interfaces (APIs) to developers, enabling them to exert control over local and remote memory access within the cluster. This approach is known for its efficiency, as it bypasses the operating system (OS) and reduces the CPU load. However, it necessitates developers to modify their workload implementations to accommodate the new interface. Notable examples of clean-slate interface providers include Kona [7], AIFM [48], and Remote Regions [2].

On the other hand, *swap-based* systems extend swap techniques to the virtual address of remote memory modules. In this design, the OS takes charge of controlling and managing memory accesses and instructions, such as Load and Store operations. While this approach introduces some latency overhead, the interface remains transparent and readily accepts workloads in their existing form, without requiring extensive modifications. Notably, several research efforts, including LegoOS [49], FastSwap [4], InfiniSwap [16], and Semeru [52], have advocated for the adoption of swap-based interfaces, offering their practicality and costeffectiveness.

In conclusion, the choice of interface in a cluster-scale disaggregated data center plays a pivotal role in determining how workloads leverage both local and remote memory resources. The clean-slate designs provide developers with direct control and increased efficiency but at the cost of requiring modifications to workloads. On the other hand, swap-based systems offer a more transparent and readily adaptable interface, making them a practical and cost-effective choice. In this thesis, while our proposed models may still remain valid using a clean-slate interface, we have opted for the latter category, the swap-based approach.

#### 2.4 Related Works

Resource allocation in disaggregated data centers presents a unique set of challenges distinct from traditional data centers. While conventional data centers focus mainly on minimizing network power consumption (e.g., Network-Aware Algorithm [36] and MCRVMP [5]), resource allocation in disaggregated data centers necessitates consideration of various additional factors. In this context, efficient resource allocation requires addressing the impact of remote memory latency, CPU processing capacity, and workload characteristics on overall performance and power consumption.

Unlike traditional data centers, where allocating resources to jobs is relatively straightforward, disaggregated data centers introduce complexities due to the physical separation of resources like memory from compute nodes. This separation results in increased latency for remote memory access, which can significantly impact the performance of memory-intensive workloads. Additionally, assigning workloads to CPUs with inadequate processing capacity can lead to slowdowns and resource inefficiencies.

Power efficiency is another crucial concern in modern data centers, given the substantial power costs associated with data center operations. Resource allocation strategies in disaggregated data centers must aim to minimize power consumption while ensuring that performance objectives are met.

To tackle the resource allocation problem in disaggregated data centers, researchers have taken a diverse range of approaches. These efforts can be neatly grouped into three primary categories: i) Minimizing Workload Slowdown, ii) Minimizing Power Consumption, and iii) Maximizing Utilization. Each of these categories explores specific aspects of resource allocation, all with the shared aim of elevating the overall performance and efficiency of disaggregated data centers.

In the following sections, we will delve into these three categories and examine the different efforts made by researchers to achieve efficient resource allocation in disaggregated data centers. Through these efforts, we aim to gain a comprehensive understanding of the stateof-the-art techniques and their respective contributions to the field of resource allocation in this evolving and critical domain.

### 2.4.1 Power Consumption

Authors in [45] proposed a novel algorithm with the primary goal of minimizing power consumption while simultaneously maximizing resource utilization in a rack-scale physically disaggregated DDC. They consider the presence of optical and electrical interconnects as fast and generic backplanes, respectively, within the DDC architecture. The proposed model for power consumption takes into account the utilization of CPU modules and network resources, attributing 85% of the total power consumption to CPUs and 15% to the network. Despite its efficacy in optimizing power usage, this algorithm neglects to consider the potential slowdown of workloads using the mentioned resource allocation algorithm, which may lead to SLA violations, particularly when allocating more remote memory to latency-sensitive workloads causing high degradation in performance.

In [38], researchers tackle the power consumption optimization challenge using a mixedinteger linear programming (MILP) model. Their study encompasses three types of workloads: memory-intensive, IO-intensive, and processor-intensive. The results demonstrate impressive power savings of 42%, 24%, and 11% for memory, IO, and processor-intensive applications, respectively, compared to traditional data centers. As the problem scales up, EERPVMM-DS [37] comes into the picture as a scalable heuristic solution. Employing a greedy approach, this heuristic tackles the challenge of minimizing power consumption while assuming a time-slotted model for the arrival of virtual machine (VM) workloads. However, a potential drawback of this approach lies in the possibility of multiple migrations for long-life-cycle VMs due to the allocation process in each time slot which causes delays in workload execution. This means a higher slowdown for the workloads that have a longer life-cycle which affects the fairness of the algorithm.

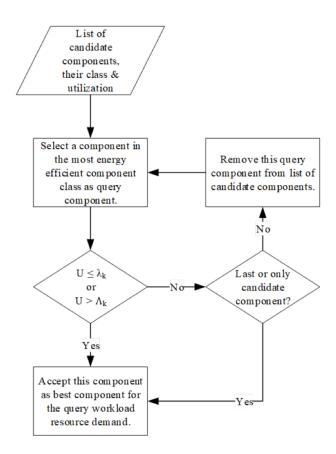

Building upon the work of EERPVMM-DS, EERP-DSCF [40] extends the previous heuristic by dropping the time-slotted assumption while maintaining the same underlying model. The authors aim to address the issue of multiple migrations by optimizing VM allocation across time slots, resulting in a more stable allocation strategy. Furthermore, the work in [3] presents a more sophisticated MILP model that accounts for the complex characteristics of disaggregated architectures, seeking to minimize power consumption more realistically. To complement the MILP model, the authors propose HEEP, a heuristic that embraces a greedy approach. This heuristic involves sorting workloads and CPUs in descending order based on their resource demands and power consumption efficiency, respectively, for optimal allocation.

Adding to the array of research efforts, [45] introduces another variant of the power consumption model for CPUs, this time considering a physically disaggregated DC with optical and electrical interconnects as backplanes. In this model, CPUs undergo an iterative filtering and prioritizing process, incorporating predefined weights associated with power efficiency, utilization, and communication delay. This iterative process aims to strike a delicate balance between minimizing power consumption and maximizing resource utilization. Nonetheless, one common limitation across all these works is the absence of consideration for the potential slowdown of jobs, which could have significant implications on SLA compliance.

As the research in the domain of power consumption in DDCs continues to unfold, the quest for comprehensive and efficient solutions remains ongoing. The identified research endeavors present valuable contributions to understanding and optimizing power usage, but the aspect of workload slowdown and its impact on SLA compliance needs further investigation. As data centers endeavor to meet the ever-increasing demands of modern applications and services, addressing power consumption challenges becomes a critical aspect in ensuring sustainable and cost-effective data center operations. Novel solutions that strike a balance between power efficiency and workload slowdown will undoubtedly pave the way for the next generation of power-efficient and resilient data center architectures.

### 2.4.2 Workload Slowdown

In the context of slowdown in disaggregated data centers (DDCs), several innovative approaches have been investigated to optimize system performance and minimize the impact of workload slowdown on critical applications. As the demand for higher computational power and memory capacity increases, DDCs have gained popularity due to their scalability and flexibility. However, the separation of resources in DDCs, mainly memory and CPU, can introduce communication delays which results in workload slowdown. Researchers and industry experts have devoted considerable efforts to address this challenge and enhance the overall efficiency of DDCs.

One notable approach proposed by Nvidia in [57] involves the development of an integrated system within the operating system (OS) to efficiently optimize workload slowdown. By minimizing the time spent on data transfers and streamlining memory access, this approach aims to reduce workload slowdown and improve the responsiveness of workloads running in a disaggregated environment. Also, the authors propose four additional optimizations: native support for transparent huge page migration, multi-threaded migration of a page, concurrent migration of multiple pages, and symmetric exchange of pages. Through experimental evaluations using x86, Power, and ARM64 systems, Nvidia demonstrates the potential benefits of their approach, reducing kernel software overheads and improving raw page migration throughput over  $15 \times$  leading to lower workload slowdown by up to 40%.

Another research effort, highlighted in [4], focuses on examining the impact of the remote

memory to local memory ratio in DDCs and its correlation with workload slowdown. First, a faster swapping mechanism that makes it possible to support remote memory at rack-scale is proposed as an RDMA-based swapping system which is called *FastSwap*. Then, the authors also develop a polynomial model and introduce a latency-based workload placement algorithm called CFM. By carefully allocating an appropriate amount of local memory to meet the slowdown requirements (*i.e.*, SLAs) of workloads, CFM aims to proactively address slowdown concerns before they significantly impact critical tasks. They review different memory allocation policies including uniform policy (*i.e.*, using a fixed local memory ratio for all the jobs), variable policy (*i.e.*, using a variable ratio), and memory-time policy (*i.e.*, using a memory-time product to determine the best local memory ratio for each job). They use the last configuration as the main policy to decide how much of local and remote memory should be assigned to each workload. This intelligent resource allocation strategy also improves success rates in meeting future demand, contributing to enhanced system stability and responsiveness.

In addition to software-level optimizations, architectural proposals have also emerged to address slowdown challenges in DDCs. One such proposal is Aquila, presented by Google in [14], an experimental data center network fabric that prioritizes ultra-low latency. Aquila incorporates the GNet protocol and custom ASIC with low-latency Remote Memory Access (RMA), achieving remarkable sub-10  $\mu$ s execution times for data transfers. By reducing communication delays and optimizing data access, Aquila effectively minimizes workload slowdown, making it an attractive solution for high-performance DDCs.

Following a similar approach to [4], HoPP [29] proposes a revised operating system for DDCs that significantly improves memory management. The novel operating system decouples address capture from page faults by recording all memory access logs in the memory controller. This design optimizes memory access and reduces unnecessary overhead, leading to potential reductions in workload slowdown and improved workload slowdown.

While the aforementioned approaches have demonstrated promising results in minimizing slowdown and enhancing the efficiency of DDCs, it is essential to consider the broader implications of such optimizations. For instance, some of the explored approaches, including those mentioned in [4] and [49], have primarily focused on optimizing performance without considering the implications of power consumption. In DDCs, where resource allocation and usage directly affect power efficiency, overlooking the power aspect can have significant financial and environmental impacts.

In summary, the increasing demand for computational power and memory capacity has led to the widespread adoption of Disaggregated Data Centers (DDCs) due to their scalability and flexibility. However, the separation of resources within DDCs, particularly memory and CPU, can result in communication delays and subsequent workload slowdowns. To mitigate this, innovative approaches have been investigated, such as Nvidia's integrated system within the operating system, aimed at optimizing data transfer and memory access to minimize workload slowdown. Additionally, research efforts have focused on examining the impact of remote memory to local memory ratios, proposing intelligent resource allocation strategies to proactively address slowdown concerns. Architectural proposals like Aquila and HoPP have also emerged, prioritizing ultra-low latency and optimizing memory management to reduce unnecessary overhead and improve workload responsiveness. While these approaches demonstrate promising results in enhancing DDC efficiency, it's crucial to consider broader implications, including power consumption, to ensure sustainable and cost-effective operations.

#### 2.4.3 Utilization

In the quest for optimizing resource utilization and performance in data centers, researchers have explored various algorithms and models to efficiently allocate resources and meet the demands of modern workloads. In [59], the authors propose two algorithms, namely NULB and NALB, aimed at realizing globally optimized IT (i.e., CPU, memory, and storage) resources in disaggregated data centers. NULB introduces the concept of Contention Ratio (CR), which specifies the demand for each resource type. The algorithm then initiates a search for IT resources based on their CR scores and utilizes a breadth-first search (BFS) algorithm to find other compatible IT resources surrounding the allocated one. Building on this foundation, the improved algorithm, called NALB, incorporates a modified version of BFS that also considers available network bandwidth when searching for network resources after allocating IT modules. By considering both IT and network resources, NALB aims to achieve even higher levels of resource utilization and performance optimization. However, it is worth noting that in these algorithms and research, the authors focused on workload rejection rates and resource utilization, while other important aspects such as power consumption of the resources or the workload slowdown (*i.e.*, Service Level Agreements) were not explicitly taken into account.

In [44], another approach to resource allocation is presented, employing a simulated annealing-based algorithm within a rack-scale architecture. The primary objective of this algorithm is to minimize the rejection rate of workloads while maximizing overall resource utilization. By simulating the annealing process, the algorithm explores different resource allocation configurations, allowing it to gradually reach an optimal solution. Through this approach, it aims to strike a balance between accommodating as many workloads as possible while making efficient use of available resources. By considering both workload rejection rates and resource utilization, this method strives to enhance data center efficiency while ensuring a lower rejection rate.

Furthermore, in [1] and [41], a more comprehensive model based on Mixed Integer Linear Programming (MILP) is proposed to address resource allocation challenges in a cluster-scale architecture. The model considers multiple objectives, including the power consumption of the data center (*i.e.*, the total cost of the data center maintenance) and the utilization of individual resources including memory, CPU, and networking modules. By formulating the resource allocation problem as a MILP, the authors can optimize resource allocation across the entire data center infrastructure while considering various constraints and objectives simultaneously. This approach allows for more holistic decision-making, where the trade-offs between power efficiency and resource utilization can be carefully balanced.

In summary, researchers have explored a diverse range of algorithms and models to tackle

the resource utilization challenges in data centers. From contention-based algorithms that optimize IT and network resource allocation to simulated annealing techniques that minimize workload rejection rates, each approach contributes to enhancing the efficiency and performance of data centers. Additionally, MILP-based models provide a comprehensive and systematic approach to resource allocation, considering multiple objectives and constraints simultaneously.

### Chapter 3

## **Profiling Datacenter Workloads**

In this section, first, we present the datacenter model considered in our work. Then, we focus on developing workload profiles that succinctly capture the impact of resource disaggregation on workload slowdown. Table 6.2 summarizes the main notations used throughout the paper.

### 3.1 Datacenter Model

Datacenters play a critical role in supporting a wide range of applications and services, from cloud computing to big data analytics. As the demand for data processing and storage continues to grow, datacenter operators are constantly seeking ways to improve efficiency, performance, and resource utilization. One promising approach that has garnered significant attention is resource disaggregation, which involves physically separating computing and memory resources, offering greater flexibility in resource allocation.

In this section, we present the datacenter model considered in our work, with a particular focus on developing a workload model that captures the impact of resource disaggregation on workload slowdown. Understanding the interplay between resource allocation, workload characteristics, and power consumption is essential for optimizing datacenter operations and delivering enhanced performance.

| Datacenter Notations  |                                                                   |  |

|-----------------------|-------------------------------------------------------------------|--|

| Symbol                | Definition                                                        |  |

| $\mathcal{C}$         | Set of all computation-cable modules                              |  |

| $F_c$                 | Frequency of CPU cores in module $c$                              |  |

| $N_c$                 | Number of CPU cores in module $c$                                 |  |

| $L_c$                 | Amount of local memory in module $c$                              |  |

| $\frac{I_c^s}{I_c^d}$ | Static power consumption of module $c$                            |  |

| $I_c^d$               | Dynamic power consumption of module $c$                           |  |

| M                     | Total amount of remote memory in DDC                              |  |

|                       | Workload Notations                                                |  |

| Symbol                | Definition                                                        |  |

| $\mathcal{W}$         | Set of all workloads                                              |  |

| $\nu_w$               | Number of cores requested by workload $w$                         |  |