# Análise de Frameworks para Seleção das Técnicas de Mitigação de Falhas Causadas pela Radiação Espacial em FPGAs COTS

# Framework Analysis for Selecting Techniques to Mitigate Failures **Caused by Space Radiation in COTS FPGAs**

DOI:10.34117/bjdv7n3-758

Recebimento dos originais: 08/02/2021 Aceitação para publicação: 01/03/2021

#### Adilson Luiz Barbosa

Doutorando em Engenharia e Tecnologia Espaciais - Instituto Nacional de Pesquisas Espaciais (INPE) -

Av. dos Astronautas, 1.758 - Jardim da Granja, São José dos Campos - SP, CEP 12227-010

E-mail: eng.adilsonlb@gmail.com

### **Geilson Loureiro**

Doutor Tecnologista - Instituto Nacional de Pesquisas Espaciais (INPE) -Av. dos Astronautas, 1.758 – Jardim da Granja, São José dos Campos - SP, CEP 12227-010

E-mail: geilson.loureiro@inpe.br

#### Silvio Manea

Doutor Tecnologista - Instituto Nacional de Pesquisas Espaciais (INPE) -Av. dos Astronautas, 1.758 - Jardim da Granja, São José dos Campos - SP, CEP 12227-

E-mail: silvio.manea@inpe.br

## Giuliani Paulineli Garbi

Doutor Tecnologista - Instituto Nacional de Pesquisas Espaciais (INPE) -Rua Carlos Serrano, 2073, Lagoa Nova, Natal - RN, CEP 59076-740 E-mail: giuliani.garbi@gmail.com

#### José Marcelo Lima Duarte

Doutor Pesquisador - Instituto Nacional de Pesquisas Espaciais (INPE) – Rua Carlos Serrano, 2073, Lagoa Nova, Natal, RN, CEP 59076-740 E-mail: jose.duarte@inpe.br

## **RESUMO**

Os sistemas espaciais exigem componentes eletrônicos com qualificação espacial, ou seja, "endurecidos" contra radiação. Devido a fatores relacionados à redução de custos dos projetos de sistemas espaciais e ao embargo comercial de componentes e materiais "endurecidos", os dispositivos eletrônicos do tipo COTS (Commercial Off-The-Shelf) tornaram-se relevantes para a engenharia de componentes, principalmente os FPGAs (Field Programmable Gate Array). Entretanto, os engenheiros de componentes precisam aplicar técnicas de mitigação de falhas nos FPGAS COTS que serão utilizadas nos projetos de sistemas espaciais. Portanto, o artigo possui como objetivo analisar os dois principais

frameworks disponíveis na literatura para seleção das técnicas de mitigação de falhas causadas pela radiação espacial em FPGAs COTS, comentando os pontos fracos e fortes de cada um deles, e especificar o que é necessário para aperfeiçoá-los.

Palavras-chave: COTS, Falhas, FPGA, Mitigação, Seleção.

#### **ABSTRACT**

Space systems require electronic components with spatial qualification, i.e., hardened against radiation. Due to factors related to the cost reduction of space system projects and the commercial embargo of hardened components and materials, the COTS electronic devices (Commercial Off-The-Shelf) become relevant for component engineering, especially the FPGAs (Field Programmable Gate Array). However, component engineers need to apply fault mitigation techniques to the COTS FPGAS that will be used in space system projects. Therefore, the objective of this article is to analyze the two main frameworks available in the literature for the selection of fault mitigation techniques for space radiation in COTS FPGAs, commenting on the strengths and weaknesses of each of them and specifying what is required to perfect them.

**Keywords**: COTS, Faults, FPGA Mitigation, Selection.

# 1 INTRODUÇÃO

O espaço é um desafio para área científica, sendo considerado estratégico em diversas áreas e resultando em benefícios econômicos, tecnológicos e sociais. Porém, a pesquisa na área espacial possui algumas características particulares, pelo fato de envolver tanto os aspectos civis como de defesa, desta forma implicando na restrição do comércio de componentes, dispositivos e materiais utilizados nos sistemas espaciais [1]. Os dispositivos eletrônicos que possuem aplicações na área espacial requerem componentes com qualificação espacial ou de defesa, rad- hard ou "endurecidos" contra radiação, e algumas aplicações também requerem dispositivos com alta taxa de processamento. Neste contexto destacam-se os COTS, que são os componentes disponíveis no mercado para aquisição, porém não foram fabricados para aplicações espaciais; estes dispositivos apresentam como a principal vantagem custos menores em relação aos componentes "endurecidos" (processo de fabricação) . Assim, os COTS apresentam-se como uma alternativa para atender as demandas de projetos de sistemas espaciais, desde que sofram um processo de adaptação ao ambiente espacial, com a adoção de determinadas técnicas de mitigação de falhas. Além disso, os FPGA COTS apresentam diversos tipos de vantagens técnicas como computação de desempenho avançado, pois apresentam capacidade elevada de paralelização do processamento aritmético, transceivers com alta

taxa de transferência, baixo consumo de energia e baixo custo, quando comparados com CPUs (*Central Process Unit*) convencionais [2] e [3].

Entre os desafios relacionados ao ambiente espacial, para os componentes eletrônicos, a radiação é um dos fatores mais relevantes, pois as missões são realizadas fora do campo magnético protetor da Terra, proporcionando efeitos nocivos devido ao efeito desta radiação, ao penetrar em um sistema espacial. Estes efeitos nocivos podem prejudicar o funcionamento e/ou causar danos em diversos tipos de componentes eletroeletrônicos como circuitos de processamento de sinais, de comunicação, células solares e materiais semicondutores [3] e [4]. No caso de FPGA COTS, podem ocorrer danos nos dispositivos eletrônicos que implementam a lógica digital, levando a problemas temporários ou permanentes como Single Event Effects (SEE) e Total Ionizing Dose (TID) [3] e [5].

Os FPGAs COTS podem ser utilizados com as devidas técnicas de mitigação de falhas, tais como os circuitos de proteção [6], careful COTS [7], TMR (Triple Module Redundancy), quadruplicação, reconfiguração [8], redundância de FPGAs [9], detecção e correção de erros [10], duplicação [11], e detector de radiação [12].

Qualquer sistemas espacial que necessite utilizar FPGAs COTS deve funcionar adequadamente com as aplicações da missão e superar as adversidades do espaço, principalmente relacionadas com o efeito da radiação. Qualquer pesquisa sobre o assunto deve servir como uma orientação para os engenheiros de componentes iniciarem o trabalho e estabelecer um caminho que aborde a grande maioria das técnicas de mitigação de falhas, a fim de selecionar a que mais se adapte à missão requerida. No entanto, o resultado final de escolha sempre será da responsabilidade dos engenheiros de acordo com seu próprio julgamento e conclusões devido à diversidade de técnicas disponíveis [13] e [14].

# 2 METODOLOGIA DA ANÁLISE DOS FRAMEWORKS PARA SELEÇÃO DAS TÉCNICAS DE MITIGAÇÃO DE FALHAS CAUSADAS PELA RADIAÇÃO ESPACIAL EM FPGAS COTS

Para analisar os frameworks que abordam a seleção das técnicas de mitigação das falhas, este trabalho utilizou como referência uma pesquisa bibliográfica a respeito das principais técnicas utilizadas em FPGAs COTS. Os trabalhos científicos pesquisados foram publicados em periódicos acadêmicos, associações de profissionais e bibliotecas digitais especializadas em ciências, tecnologia espacial, eletrônica e telecomunicações. A partir de técnicas pesquisadas nos últimos dez anos, este artigo se propõe a avaliar os resultados de dois outros trabalhos científicos considerados relevantes, os quais apresentam frameworks

para facilitar a escolha de uma determinada técnica que se adapte melhor à sua aplicação e missão. A análise foi realizada tendo por base os seguintes parâmetros:

- Informações sobre FPGAs, tipos de radiação e técnicas de mitigação utilizadas.

- Informações sobre o período de coleta de dados e sobre banco de dados.

- Modelos de radiação, métricas para seleção e metodologias de decisão.

- Abrangência e flexibilidade do *framework* em permitir a atualização constante de novos dados obtidos, após a publicação do trabalho, de forma a refletir as tendências e avanços tecnológicos.

- Informações sobre testes e simulações.

### **3 RESULTADOS E DISCUSSÕES**

Considerando todos os trabalhos científicos pesquisados, dois se aproximaram do framework necessário para ajudar no trabalho dos engenheiros de componentes.

### A) FRAMEWORK APRESENTADO EM [13]

O primeiro framework considerado em [13] e ilustrado na Figura 1, apresenta informações sobre tipos de FPGAs de determinados fabricantes (Xilinx/Microsemi), os principais tipos de efeitos da radiação (SEE/TID) e algumas técnicas de tolerância a falhas, relacionadas com TMR, detecção e correção de erros, reconfiguração e duplicação. As informações são obtidas de uma revisão bibliográfica com um período total de dez anos, deixando de considerar os resultados mais antigos. Este trabalho apresenta detalhadamente (com diagramas em blocos) os circuitos de alguns exemplos de técnicas e suas aplicações.

Para efeito de projetos, o framework enfatiza apenas as técnicas de mitigação envolvendo os conceitos de TMR, duplicação (DWC - Duplication With Compare) e reconfiguração (scrubbing), com um fluxo de decisões que apontam tentativas e não processos de seleção baseados em métricas ou métodos de decisão. Comenta a utilização do CREME96 para efeitos de modelo de radiação, sendo os dados obtidos de revisão bibliográfica.

O framework possui um comentário maior relativo à interação entre as técnicas de mitigação abordadas, e não estabelece uma ligação com as métricas como missão, potência, confiabilidade e tempo de vida. Este trabalho ressalta a importância de simular a operação do dispositivo e das técnicas de mitigação com injeção de falhas, citando os sistemas FLIPPER e FT-UNSHADES, desenvolvidos sob financiamento da ESA (Europe Space

Agency). Não comenta a possibilidade de o *framework* ser flexível e necessitar de atualizações com a inserção de mais técnicas ou dados atualizados.

A seguir, na Figura 1, é apresentado o framework completo de [13].

Figura 1: Framework adaptado de [13].

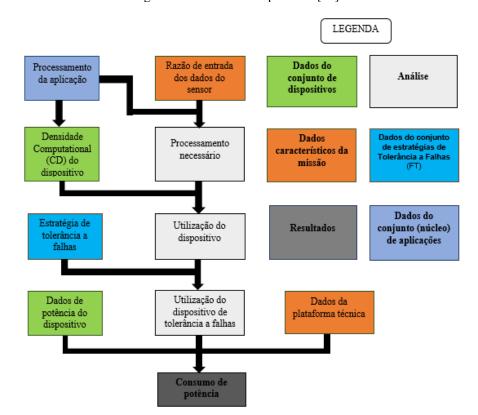

## B) FRAMEWORK APRESENTADO EM [14]

O segundo *framework* apresentado em [14] e ilustrado na Figura 2, possui como objetivo avaliar e otimizar a utilização de FPGAs na área espacial e não se configurar como um *framework* completo para a seleção dos mesmos. Este artigo apresenta como estudo de caso FPGAs da Xilinx, menciona os principais tipos de efeitos da radiação (SEE/TID) e algumas técnicas de tolerância a falhas, principalmente relacionadas à TMR, detecção e correção de erros e reconfiguração.

Há informações de que utiliza bancos dados obtidos da literatura, porém não há detalhes sobre o período de coleta de dados e nem sobre esta fonte de informações. O *framework* deste artigo apresenta detalhamento maior sobre a utilização de métricas e uma

metodologia de seleção (Pareto-ótimo), porém não esgota o assunto, provavelmente devido a fatores de pesquisa como finalidade e tamanho do artigo. Há informações estanques sobre o fluxo de informações, porém há cálculos específicos das métricas utilizadas para: potência, confiabilidade e vida útil. Faz menção a vários modelos de radiação e alguns exemplos de gráficos obtidos com: CREME96, SHIELDOSE, AE8MAX, AP8MAX e SPENVIS, sem maiores explicações.

Há uma ênfase no estudo de TID, a fim de caracterizar melhor a métrica relacionada com o tempo de vida útil. Apresenta um estudo de caso com FPGAs da Xilinx em uma missão de imagem hiperespectral (HSI - *Hyperspectral Imaging*). Somente mencionada à possibilidade de injeção de falhas para testes, não fornecendo mais detalhes sobre o assunto. Porém, ressalta que os dados obtidos dos parâmetros poderão ser complementados com novos dados à medida que as pesquisas evoluam, ou seja, há a possibilidade de atualizações do *framework*.

A Figura 2 apresenta um *framework* parcial apresentado [14], e utilizando como exemplo a métrica de potência.

Figura 2: Framework adaptado de [14].

## 4 CONCLUSÃO

Os dois frameworks apresentaram resultados parciais em termos de fornecer um apoio aos engenheiros de componentes quanto à seleção da técnica mitigação de falhas em FPGAs COTS, causadas pela radiação espacial. Ambos os trabalhos [13] e [14] abordam os dois principais tipos de efeitos da radiação espacial (SEE e TID), porém cada um apresenta ênfase em apenas um deles.

O primeiro framework apresentado em [13] expõe uma revisão da literatura mais abrangente, abordando detalhes de FPGAs de dois fabricantes, algumas técnicas de mitigação, principalmente relacionadas com SEE. O framework apresentado possui o mérito de ser sequencial e didático, porém aborda somente três tipos de técnicas de mitigação (TMR, duplicação e reconfiguração). Também relata um período relativamente reduzido de avaliação bibliográfica de dez anos, deixando de informar se a pesquisa é recente ou não e menciona apenas um tipo de modelo de radiação.

O segundo framework apresentado em [14] possui a vantagem de apresentar métricas para avaliação e otimização de FPGAs, mas não as utiliza para a seleção dos mesmos. Por sua vez, este artigo aborda um FPGA específico (Xilinx) e algumas técnicas de tolerância a falhas (TMR, detecção e correção de erros e reconfiguração). Não há detalhes sobre o banco de dados obtido da literatura, a fonte e o período de coleta de dados. Uma vantagem relevante deste *framework* é que detalha métricas (potência, confiabilidade e vida útil) e fornece metodologia de seleção. Faz menção a vários modelos de radiação e seus gráficos e a ênfase no estudo de TID, a fim de caracterizar melhor a métrica relacionada com o tempo de vida útil. Apresenta um estudo de caso com o FPGA analisado e menciona a possibilidade de injeção de falhas para testes.

Assim, pode-se concluir que o engenheiro de componentes ainda não possui um framework completo abrangendo as diferentes famílias de FPGAs COTS, todas as técnicas de mitigação de falhas, e que indiquem todos os passos sequenciais para a escolha destas técnicas, compatíveis com a aplicação e missão espacial. E então fica a sugestão para trabalhos futuros para o desenvolvimento de um único framework com todas as técnicas de mitigação pesquisadas, em um período maior que dez anos, e que considere as métricas definidas como mais relevantes, principalmente a missão espacial. Finalmente, deverão considerar a possibilidade de simulações, testes e atualizações constantes.

## REFERÊNCIAS

- [1] Organisation for Economy Cooperation and Development (OECD), "The Space Economy at a Glance 2014", Paris, France, 2014.

- [2] V. W. C. Medeiros, "fastRTM: Um ambiente Integrado para Desenvolvimento Rápido da Migração Reversa no Tempo (RTM) em Plataformas FPGA de Alto Desempenho", tese na Universidade Federal do Pernambuco, Pernambuco, Brasil, 2013.

- [3] B. C. Junqueira, S. Manea, "Utilização de COTS em nano satélites", Brazilian Journal of Development, vol. 6, n° 1, pp. 1476-1490, 2021.

- [4] M. V. Pinho, F. Kraeamer, F. e I. Soares, I, "FPGAs em aplicações espaciais", Instituto Federal de Santa Catarina (IFSC), Santa Catarina, Brasil, 2016.

- [5] Europe Space Agency (ESA), "Space Engineering Methods for the calculations of radiation received and its effects, and a policy for design margins (ECSS-E-ST-10-12C)", Paris, France, 2008.

- [6] L. M. Reyneri, C. Sansoè, C. Passerone, S. Speretta, B. M. Tranchero, e D. D. Corso, "Design Solucion for Modular Satellites Architectures", Aeroespace Technologies Advancementes, Book edited by Dr. Thawar T. Arif, pp. 492, Croatia, 2010.

- [7] D. Sinclair, e J. Dyer, "Radiation Effects and COTS Parts in SmallSats". In: Conference on Small Satellites, 27, Logan U.T., U.S.A., 10-15 August 2013. Proceeding Logan, 2013.

- [8] L. S. Parobeck, "Research, Development and Testing of a Fault-Tolerant FPGA-Based Sequencer for Cubesat Lauching Applications", thesis (MSc) in Naval Postgraduate Schoool, California, U.S.A, 2013.

- [9] C. Carmichael, E. Fuller, P. Blain, e M. Caffrey, "SEU Mitigation Techniques for Virtex FPGAs in Space Applications", in Proc. Military and Aerospace Programmable Logic Device (MAPLD) International Conferences, 1999.

- [10] P. P. Shirvani, N. R. Saxena, E. j. McChuskey, "Software Implemented EDAC Protect Against SEUs", IEEE Transactions on Reability, vol. 49, n° 3, pp. 273-284, 2000.

- [11] F. G. L. Kastensmidt, G. Neuberger, C. R. F. Hentschke, e R. Reis, "Design Fault Tolerant Technique for SRAM Based FPGAs", in Proc. IEEE Design & Test of Computers, pp. 552-562, 2004.

- [12] B. LaMeres, T. Kaiser, E. Gowens, T. Buerkle, J. Price, K. Helsley, B. Peterson, R. Ray, "Position Sensitive Radiation Detector Integrated with an FPGA for Radiation Tolerant Computing", in Proc. IEEE Sensors, pp. 208-213, 2010.

- [13] F. Siegle, "Fault Detection, Isolation and Recovery Schemes for Spaceborne Reconfigurable FPGA-Based Systems", PhD Thesis in University of Leicester, Leicester, United Kingdom, 2015.

- [14] N. Wulf, A. D. George, e A. Gordon-Ross, "A Framework for Evaluating and Optimizing FPGA-Based SoCs for Aerospace Computing", University of Florida, Flórida, E.U.A, 2016.