## ANALYSIS OF CARRIER INJECTION UNDER HIGH TEMPERATURE AC OPERATION IN TOP GATE IGZO TFTs

Kuan-Ju Zhou, Department of Physics, National Sun Yat-Sen University mark3352@g-mail.nsysu.edu.tw Ting-Chang Chang, Department of Physics, National Sun Yat-Sen University Po-Hsun Chen, Department of Physics, Military Academy Bo-Shen Huang, Department of Physics, National Sun Yat-Sen University Simon M. Sze, Institute of Electronics, National Yang Ming Chiao Tung University

Key Words: IGZO TFTs, Double-layer oxide, SiH4 flow rate, Hydrogen residue, Alternating current (AC) stress

Abstract– With the development of high-quality displays, metal oxides gradually become a popular active layer in TFTs [1]. In this work, InGaZnO thin film transistors with double-layer oxide are investigated. The oxide layer is divided into top and bottom layers. We improve the characteristics and reliability of the device through the design of double-layer oxide stack structure. The bottom oxide layer is deposited with a lower SiH<sub>4</sub> flow rate, and the top oxide layer is deposited with a higher SiH<sub>4</sub> flow rate. By increasing the SiH<sub>4</sub> flow rate of the top oxide layer, two effects can be achieved. Firstly, it is beneficial for speeding up the film deposition process. Furthermore, the hydrogen residue passivates the dangling bonds in the oxide layer and increases the bonding amount of silanol groups, SiO-H, and achieve hydrogen channel doping [2]. By modulating the SiH<sub>4</sub> flow rate of the top oxide layer, the basic characteristics of the devices and the reliability under alternating current (AC) operation are improved. In this work, we use three waveform types of switch process to analyze the degradation under AC stress, and the physic mechanism is proposed subsequently [3-4]. After AC stress, the top oxide layer with higher SiH<sub>4</sub> flow rate has a smaller threshold voltage right shift, and the reliability is significantly improved.

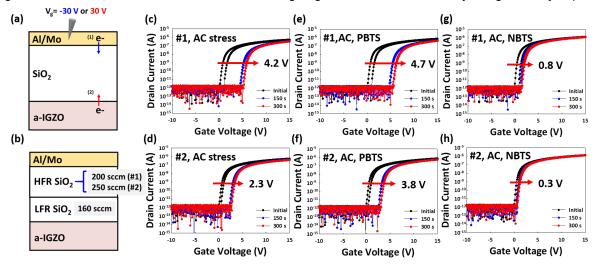

Figure 1 – The Physic Models For (a) Positive Bias Temperature Stress (pbts) And Negative Bias

Temperature Stress (nbts). (b) The Design Of Double Stacks Sio2, Higher Flow Rate (hfr) Sio2, And

Low Flow Rate (lfr) Sio2, Respectively. The Ac Stress For (c) #1 Devices And (d) #2 Devices,

Respectively. The Ac Pbts For (e) #1 Devices And (f) #2 Devices, Respectively. The Ac Nbts For (g)

#1 Devices And (h) #2 Devices, Respectively.

## References

[1] T. Kamiya. et al. "Present status of amorphous In–Ga–Zn–O thin-film transistors," *Sci. Technol. Adv. Mater.*, vol. 11, no. 4, p. 044 305, Aug. 2010, doi: 10.1088/1468-6996/11/4/044305

[2] Hsieh, H. H. et al. (2010). Influence of channel-deposition conditions and gate insulators on performance and stability of top-gate IGZO transparent thin-film transistors. *Journal of the Society for Information Display*, 18(10), 796-801.

[3] Lee, S. et al. (2009). Electrical stress-induced instability of amorphous indium-gallium-zinc oxide thin-film transistors under bipolar ac stress. *Applied Physics Letters*, 95(13), 132101.

[4] Zhou, X. et al. (2017). Oxygen interstitial creation in a-IGZO thin-film transistors under positive gate-bias stress. *IEEE Electron Device Letters*, 38(9), 1252-1255