# Design of an FPGA Based High-Speed Data Acquisition System for Frequency Scanning Interferometry Long Range Measurement

Sivagunalan Sivanathan, Mohammed Ali Roula, Kang Li, Dun Qiao and Nigel Joseph Copner

Abstract Frequency Scanning Interferometry (FSI) has become a popular method for long-range, target based, distance measurements. However, the cost of developing such systems, particularly the electronic components required for high-speed data acquisition, remains a significant concern. In this paper, we present a cost-effective, FPGA-based real-time data acquisition system specifically designed for FSI, with a focus on long absolute distance measurements. Our design minimizes the use of third-party intellectual property (IP) and is fully compatible with the Xilinx FPGA 7 series families. The hardware employs a 160 MS/s, 16-bit dual-channel ADC interfaced to the FPGA via a Low Voltage Differential Signal (LVDS). The proposed system incorporates an external sampling clock, referred to as the K- clock, which linearizes the laser's tuning rate, enabling optical measurements to be sampled at equal optical frequency intervals rather than equal time intervals. Additionally, we present the design of a high-speed, 160 MS/s ADC module for the front-end analogue signal interface and the LVDS connection to the chosen FPGA. We demonstrate that the digitized data samples can be efficiently transmitted to a PC application via a USB interface for further processing.

Index Terms— Data Acquisition, FPGA, High-Speed DAQ, FIFO, Frequency Scanning Interferometry Hardware, LIDAR

#### I. INTRODUCTION

ptical-based distance measurement systems utilizing tunable optical sources have gained popularity in recent years. Frequency Scanning Interferometry (FSI) also known as, Frequency Modulated Continuous-wave (FMCW) reflectometry, has found applications in various scientific and engineering fields [1]. FSI is primarily used in Swept Source Optical Coherence Tomography (SS-OCT) for medical imaging applications [2, 3], relying on the observation of optical interference phenomena. The scope of FSI applications has expanded to large science projects, such as alignment and deformation monitoring of the CERN ATLAS detector [4], and improving manufacturing efficiency and accuracy, such as large airplane wing assembly requiring 40 µm precision [5]. Light source modulation techniques can achieve uncertainties of up to 1 Part Per Million (PPM) [5-8] over distances spanning several tens of metres [5, 9]. Certain implementations also enable simultaneous detection of multiple targets or objects, significantly advancing metrology and its applications.

If the optical path difference (OPD) between an object and sensor changes during an FSI measurement, the Doppler

This research work was supported by the National Physical Laboratory, Optimum Laboratory, Teddington, UK under the research collaboration program between University of South Wales and National Physical Laboratory.

effect causes a magnified change in the result. The error magnitude depends on the laser tuning bandwidth. For a laser sweeping from 1530 nm - 1560 nm, the magnification factor is  $\sim\!\!50$ . If the OPD changes by 1  $\mu m$  during a measurement, the system detects a movement of 50  $\mu m$ . This effect dramatically reduces the precision of FSI measurements and presents a significant drawback for industrial use.

The Doppler effect can be minimized during an FSI measurement by generating a secondary laser sweep in the opposite direction and multiplying the two signals together [8]. Generating a secondary, opposite laser sweep perfectly synchronized with the primary sweep source using Four Wave Mixing (FWM) is possible. The FWM technique is an effective method for improving measurements on vibrating targets, employing dual laser sweeps in opposite directions without needing laser synchronization, and using a single primary Tunable Laser Source (TLS) [10]. Detecting dual FSI measurements simultaneously requires two ADC channels per sensor head.

The signal quality of FSI-based measurements also depends on the tuning rate of the TLS, which should be linear during the measurement. In reality, the tuning rate of a laser

is not particularly linear. Several techniques have been proposed to address laser source nonlinearity, including preprocessing to resample the measured data and eliminate sweep nonlinearity [11-13]. One common method involves using an auxiliary interferometer, which generates a sampling clock known as the K-clock [14]. Typically, a fiber-based Mach-Zehnder interferometer serves as this auxiliary interferometer [15].

These complex measurements demand high-performance real-time electronic systems. To meet these requirements, several challenges must be addressed. The signal generated by the measurement interferometer has an extremely high frequency (several hundred MHz), proportional to the target distance. To satisfy the Nyquist theorem, the sampling clock or K-clock frequency must be twice the maximum frequency of the signal detected by the measurement arm. This is typically achieved by increasing the OPD of the auxiliary interferometer, which is twice the OPD of the measurement interferometer.

The FSI system measures distance over tens of metres, and certain implementations can measure multiple objects simultaneously. High-resolution, long-distance measurements result in a large number of samples. Real-time data processing requires high-speed ADCs with high data transfer rates. Additionally, a vast number of data points must be retained on-board during the measurement for further signal processing to achieve micrometre resolution [13].

It is possible to use commercially available high performance Data Acquisition (DAQ) systems; however, often, the specifications are not optimally matched for the application and can often include unwanted additional functionality not required for a particular usage. For example, a 16 GHz bandwidth high-speed oscilloscope with a sampling rate of 50 GS/s was used as DAQ hardware for Optical Coherence Tomography (OCT) measurements [16-17]. Adapting similar off the shelf components for our FSI application would result in non-optimised sampling and equipment more suited to a laboratory than manufacturing environments. Furthermore, the cost of such systems are often prohibitive for many commercial applications.

Recent advancements in electronic systems and devices have enabled the design of flexible, cost-effective, high-bandwidth, and low-noise devices. The real-time DAQ system for the long-range FSI measurement requires multichannel ADCs with an external sampling clock, and is required to contains large data memory, with a high sampling rate. These requirements cannot be met using low profile real-time systems such as embedded systems. High-performance systems such as FPGAs are required. FPGA based real-time hardware acquisition systems can now be developed at a cost 10% of that of commercial models [18, 19]. Custom designed DAQs require more effort in initial

design and testing.

In this paper, we describe the development of a cost-effective FPGA-based real-time DAQ hardware for FSI measurement systems. We propose the development of a 150 MS/s ADC module and an external clock driver circuit to drive the ADC sampling. Section II explains the theoretical background of FSI systems and the effect of the K-clock sampling method. Sections III and IV discuss the design and development of hardware for the ADC module and digital design for FPGA-based DAQ systems, respectively. Section V covers the experimental configuration for interfacing FSI systems with the DAQ measurement system. Finally, Sections VI and VII present the results and conclusions, along with closing remarks.

#### II. FSI-BASED MEASUREMENT SYSTEM

#### A. Principles of the Frequency Scanning Interferometry

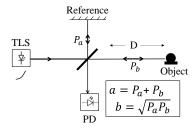

FSI systems use a tunable light source to measure the OPD between an object and a reference path. The actual implementation varies depending on the application. The simple Michelson interferometer optical setup is shown in Fig. 1.

Fig. 1. Michelson interferometry optical arrangement

The FSI system utilises the tunable laser source, with an optical frequency that changes over the sweep period  $(t_p)$ . The light from TLS is split into two beams. One is focused on the reference mirror, whereas the other is on the object at a distance D. Both reflected lights are coherently detected by the Photo Detector (PD). Here  $a = P_a + P_b$  is the sum of the optical power directly from both interferometric arms,  $b = \sqrt{P_a P_b}$  is the amplitude of the signal detected by the PD.

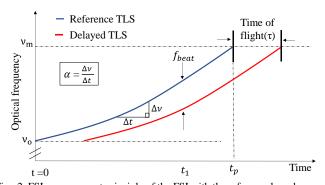

Fig. 2. FSI measurement principle of the FSI with the reference laser beam and reflected beam.

Fig. 2 illustrates the simple measurement principles using this technique. The optical frequency swept from  $v_0$  to  $v_m$  over a period of time  $t_p$  (blue) and the delayed optical signal which is reflected from the object (red) are shown. The delay  $\tau$  between reference and delayed tunable laser signal creates an oscillating intermediate optical frequency  $f_{beat}$ . For a given rate of change in optical frequency,  $\alpha \left(\frac{Hz}{s}\right)$ , the signal detected by the PD creates alternating voltages as the optical frequency changes over the sweep period, causing a phase change between the reference and delayed optical signals. The voltage detected by the PD, which is sampled by the ADC at a sampling interval k can be given as

$$S(ki) = a + b\cos(\omega ki + \theta) \tag{1}$$

Where i=1,2,...N is the ADC sample number,  $\theta=2\pi dn\nu_0/c$  is the initial phase of the optical interference signal at an optical frequency  $\nu_0$  and d is the OPD and n is the refractive index. However, it is assumed n=1 throughout this paper for simplicity. Here  $\omega=2\pi f_{beat}$  is the angular frequency. The relative difference between the measurement and reference optical path delay  $\tau$  is proportional to the OPD d, which is twice the distance D to the object, this is given as

$$D = \frac{\tau c}{2n} \tag{2}$$

where c is the speed of light. Here,  $\alpha(r) = \frac{\delta v}{\delta t}$ , and the intermediate beat frequency  $f_{\text{beat}}$  given as

$$f_{beat} = \alpha(t)\tau \tag{3}$$

Further, from (2) and (3) the beat frequency can be expressed in terms of the object distance given as

$$f_{beat} = \frac{D}{c} 2\alpha(t) \tag{4}$$

Here, for a given constant  $\alpha(t)$ , the distance D is proportional to the  $f_{beat}$ . Hence the direct measurement of the beat frequency reflects the absolute distance to the object. However, if  $\alpha$  is not constant a measurement error occurs.

The discrete function of the output voltage from the PD can be obtained by substituting (4) into (1) for  $\omega$  yield the object distance D given as

$$S_m(k,i) = a + b \cos\left(4\pi \frac{D}{c}\alpha(t)ki + 4\pi \frac{D}{c}\nu_0\right)$$

(5)

Here, the absolute distance to the object is half the optical path distance. From (4) the object distance D corresponding to the group delay  $\tau$  can be determined by obtaining the Fourier transform of the signal detected by the PD. Further, the approximate spatial resolution,  $\Delta D$  can be described as  $\Delta D = \frac{c}{2n\Delta\nu}$ , [12]. For example, for  $\Delta\nu = 3.77074$  THz and n = 1,  $\Delta D = 39.77~\mu m$ .

#### B. Measurement Error and implementation of K-clock

The tuning rate of the TLS influences the direct measurement of the object distance. In practice, TLSs suffer from the nonlinear effect [20, 21], reducing the measurement resolution and accuracy, and introducing a distance measurement error.

Many methods using hardware and software have been used to correct the nonlinear effects of the laser. The software approaches mostly use digital signal processing techniques to eliminate the nonlinear components [11, 15]. This method includes using the Fourier transform to extract the phase information, which is treated as an auxiliary interferometer for post-processing. This post-processing software approach usually limits or compromises the real-time measurement capability due to the computational intensity.

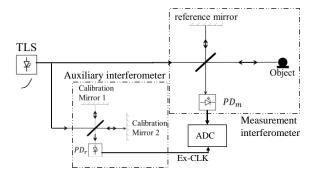

The feedforward method is another common method that uses hardware resources to linearise the laser tuning rate [2, 8, 9]. The method uses the reference interferometer to actively or passively correct the variations in the tuning rate. The active linearisation utilises the feedback from the auxiliary interferometer to adjust the tuning rate error caused by the laser diode, therefore the laser diode drivers can be adjusted. However, passive linearisation uses the auxiliary interferometer as a sampling clock to resample the signal detected by the PD. Such use of an auxiliary interferometer using K-Space resampling methods is shown in Fig. 3 below.

Fig. 3. Principle of measurement setup showing passive linearisation using an auxiliary interferometer.

Here, two interferometers are used for measurement. One of the measurement arms is focused on the object and another to the fixed reference mirror. The auxiliary interferometer contains two fixed arms of different lengths, generating a periodic fringe pattern as the laser sweeps. The oscillating fringe pattern generated by the auxiliary interferometer is used as the K-clock, which satisfies the Nyquist frequency. In this arrangement the sampling interval (*k*) is varies during the measurement.

## C. The output of the measurement interferometer as a function of the auxiliary interferometer

When passive linearisation method (K- Clock) is used, the sampling interval k becomes a non-constant value can be expressed as function of time. From (5), the signal detected by the  $PD_m$  can be rewritten as

$$S_m(k_a, i) = a + b \cos \left(4\pi \frac{D_m}{c} \alpha(t) k_a(t) i + 4\pi \frac{D_m}{c} \nu_0\right)$$

(6)

here,  $D_m$  is the absolute distance to the object (measurement arm),  $k_a(t) = \frac{1}{f_{beat(a)}}$  is the sampling interval defined by the auxiliary interferometer, which can also be expressed as

$$k_a(t) = \frac{c}{D_a \alpha(t)} \tag{7}$$

Here,  $D_a$  is the OPD created by the auxiliary interferometer. Substituting  $k_a(t)$  from (7) in (6) results:

$$S_m(i) = a + b \cos\left(4\pi \frac{D_m}{D_a} i + 4\pi \frac{D_m}{c} \nu_0\right) \tag{8}$$

Equation (8) is not only a function of sample number but also independent of the tuning rate of the TLS  $(\alpha)$ ; in fact, the oscillating frequency now depends on the ratio between OPD created by the auxiliary  $(D_a)$  and measurement  $(D_m)$  interferometers. Further, the tern  $\frac{D_m}{D_a}$  is constant, assuming that the measured target is kept at vibration-free during the measurement. Equation (8) also can be expressed in terms of measurement and auxiliary group delay  $\tau_m$  and  $\tau_a$  respectively, as shown in (9).

$$S_m(\tau_m, \tau_a) = a + b \cos(2\pi \frac{\tau_m}{\tau_a} i + 2\pi \nu_0 \tau_m)$$

(9)

From (9) we could find that the signal detected by the measurement interferometer is not affected by the variation in  $\alpha$  but by time delay created by the auxiliary and measurement interferometers. To satisfy the sampling theorem,

$$d_a \ge 2d_m \tag{10}$$

Here  $d_a$  and  $d_m$  are OPD created by the auxiliary and measurement interferometers respectively. However,  $d_m = 2D_m$  this results:

$$d_a \ge 4D_m \tag{11}$$

Therefore, the auxiliary interferometer OPD,  $d_a$  must be four times the maximum FSI absolute target distance,  $D_m$ .

### III. DESIGN OF AN ANALOGUE TO DIGITAL CONVERTER MODULE

We have demonstrated the need for a custom data acquisition system for the FSI system. The requirements are dual ADCs per sensor, an external time variable clock (external sampling clock), ADC acceptance of laser trigger signals, and real-time data processing capability using FPGA or similar high-performance hardware systems.

High-performance hardware systems, such as FPGAs, are typically used to achieve real-time measurements. However, achieving optimal performance, such as high-resolution and long-distance measurements (tens of meters), necessitates the collection of a larger number of samples. Digital Signal Processing (DSP) techniques, like Fast Fourier Transform

(FFT), are used to compute spectral information to determine the distance to multiple objects. Moreover, using FWM to minimize the Doppler effect has garnered increased interest in real-time signal processing [22]. This process is computationally intensive and must be executed in real time. It requires a dual-channel ADC with a common external sampling clock (K-clock). Furthermore, most TLSs provide feedback about their current operations, such as valid and non-valid tuning information, referred to as "Trigger."

To address these complex demands, commercially available hardware systems are often expensive or require significant modifications to accommodate FSI-based measurement requirements. This renders such systems less appealing and affordable for commercial applications.

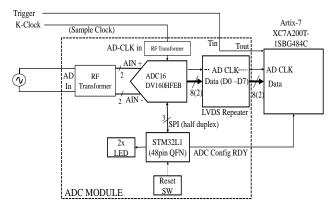

#### A. Custom-designed ADC Module

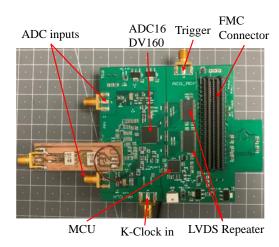

Fig. 4 presents the block diagram of the custom-designed ADC module for FSI measurement. This 16-bit, dual-channel, 160 MS/s ADC is designed to operate with an input voltage range of ±2.4 V and an external sampling clock. A low-power 32-bit microcontroller (MCU) is integrated into the circuit, making the ADC highly configurable for various operations during and after DAQ development. These operations include selecting the ADC input voltage range, adjusting the ADC's internal operating clock, and optimising the module for various power modes such as sleep and power-down. Fig. 5 displays the custom-designed four-layer PCB containing populated components for the ADC modules. SMA connectors are chosen to interface high-frequency external signals.

#### ADC (ADC16DV160)

The ADC16DV160, a 68-pin VQFN package 16-bit CMOS ADC with a maximum sampling rate of 160 MS/s, is used for the design. A significant feature of this device is its configurability via a 3-wire Serial Bus Interface (SPI). The dual input channel with an external sampling clock feature has a data interface between an external device, such as an FPGA, via Dual Data Rate (DDR) LVDS output. The input channels are protected against overvoltage beyond  $\pm 2.6~\rm V$  and can achieve more than 75 dB SNR. The 8-bit differential data output can capture odd and even bits at the falling and rising edges of the respective output clock before decomposing the bits to form 16- bit data per channel.

Fig. 4. Block diagram of the customised ADC module and its interface to Artix-7 FPGA.

Fig. 5. Custom Designed four-layer PCB with the fully populated components and connectors for the ADC modules.

#### LVDS Repeater and the Trigger

Low Voltage Differential Signalling (LVDS) is a general-purpose interface standard for efficient high-speed signal transmission. Sixteen differential data lines (eight differential repeaters per data channel) and a clock are buffered through the LVDS repeater. The repeater's input terminals are terminated with external 100  $\Omega$  resistors, while the output differential terminals are expected to be terminated with internal 100  $\Omega$  resistors as part of the FPGA buffer resources for improved signal conditioning and power consumption. The repeater is externally powered by 3.3 V for a typical differential output swing of 330 mV.

#### Microcontroller (MCU)

It is essential to develop an embedded system to configure the ADC for its precise operation. The ARM Cortex M3-based stm32L1 ultra-low power 32-bit MCU was selected to configure the ADC. The firmware was developed to self-contain configuration parameters. The MCU was designed to interface with two LEDs, a reset switch, and a 3-wire SPI interfaced to ADC. The developed firmware configures the ADC's internal registers, such as operating modes, data format, input voltage range, sampling clock, and output clock phase. The custom-developed firmware also supports the calibration and diagnoses for the ADC. A single MCU port pin is also interfaced with the FPGA, called "ADC Config RDY," for the power-on reset handshake mechanism.

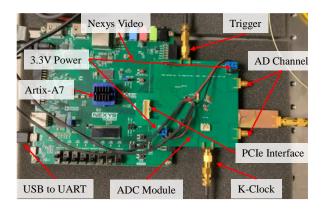

#### **FPGA**

The Artix-7 family XC7A200T-1SBG484C FPGA was selected for the DAQ design. This high-performance FPGA has 33k logic slices and 1.625 Megabytes of block RAM. The device includes a 3.75 Gbps transceiver module that can potentially develop a PCIe interface for extended applications. To minimize the effort in developing complex PCB design, the Nexys Video from Digilent was selected for initial application development. The Nexys development board features a USB to UART bridge and 160-pin FMC connector for external interfacing. FMC connectors are interfaced with the ADC module via the FPGA IOs. The UART interface within the Nexys video is used to stream

data from the DAQ system for further processing and digital design validation.

#### RF Transformer

Three ADT1-1WT+ RF transformers are interfaced with two ADC input channels and the K-clock interfaces. They provide excellent amplitude and phase unbalance of 0.1 dB and 1 degree, respectively. Eliminating DC from the input signal is essential for both the ADC input signal and the input to the k-clock; this also ensures that the sampling clock is triggered at the zero crossing to maintain consistent sampling. The operating frequency range for the RF transformer is between 0.4 MHz – 800 MHz, which is well within the external input signal bandwidth requirement.

### IV. DEVELOPMENT OF A DIGITAL HARDWARE SYSTEM FOR $\mathsf{DAQ}$

#### A. Digital Hardware design

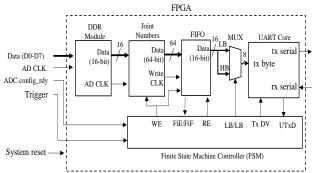

Fig. 6 shows the block diagram of the designed and developed DAQ hardware for Artix7 FPGA. The modules shown in the block diagram have been designed and developed using the Xilinx Vivado IDE with VHDL. The design aims to limit the use of IP to increase portability and design reuse. A Finite State Machine (FSM) has been designed and interfaced with each module to ensure smooth data flow control. Fig. 7 shows the ADC module interfaced with the Nexys video FPGA trainer boad showing the external connections to FSI system

$Fig.\ \ 6.\ Block\ diagram\ shows\ the\ hardware\ architecture\ of\ the\ DAQ\ system.$

Fig. 7. ADC module interfaced with the Nexys Video FPGA trainer board.

DDR interface and data decoding using sampling clock

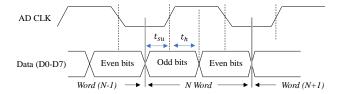

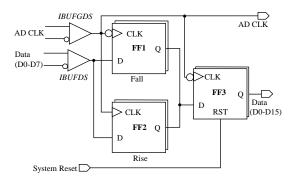

The asynchronous signals, such as Data and clock (K-clock), from the ADC must be synchronized with the FPGA clock domain. This is a significant step to avoid timing violations such as metastability. Further, the parallel input data (8 bits) is sampled at both edges of the ADC clock for odd and even bits. Fig. 8 explains such timing behaviour to sample the ADC data.

Fig. 8. ADC output timing diagram shows 8-bit LVDS data and the clock (AD CLK).

The 8-bit data is sampled at the rising and falling edge of the AD CLK for odd (D0) and even (D15) bits, respectively. The clock and data signal integrity are ensured by not violating the setup (t<sub>su</sub>) and hold (t<sub>h</sub>) times for the input constraint, while the FPGA differential input buffer samples the signal. This is achieved by configuring the ADC's internal synchronization mode register via SPI by adjusting the phase of the output clock during the initial power-up sequence.

Fig. 9. RTL arrangement of the DDR interface for capturing data at the rising and falling edge of the ADC sampling clock.

Simple differential signalling input buffers "IBUFDS" and "IBUFGDS" are used for both Data and AD CLK inputs, respectively. The input termination for the buffers is configured for LVDS termination with 2.5 V, improving signal integrity and reducing the use of external components such as a  $100~\Omega$  termination resistor at the receiver end. The Fig. 9 shows the RTL arrangement of a DDR interface. The two flip-flops (FF) FF1 and FF2 sample the 8-bit data at the clock's falling and rising edges, respectively. The data from FF1 and FF2 are concatenated and captured by FF3 at the falling edge of the clock. This arrangement ensures that the 16-bit data from FF3 is validated at the rising edge of the AD CLK.

#### Increase FIFO Data Depth

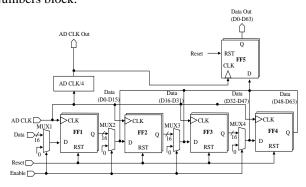

Crossing the clock domain is particularly challenging and could result in metastability if care is not taken. The Block RAM (BRAM) based FIFO has been selected to cross the clock domains and to buffer the data received from the DDR block. This is the only module that utilizes the IP to generate an independent clock FIFO with eight synchronization stages, especially when sampling and the onboard system clocks lie in different clock domains. The eight-stage synchroniser ensures a high Mean Time Between Failures (MTBF) when the clock domains are crossed. However, the Xilinx IP is limited to generating the maximum write FIFO depth of 131,072. This limits the number of 16-bit data that could be written into the FIFO regardless of the BRAM capacity. To overcome the limitation to increase the data depth, the write word length has increased from 16-bit to 64bit for 131,072 data depth. This increases the total 16-bit data depth to 524,288, sufficient for the application's buffer requirement without configuring external RAM. The "joint numbers" block combines four 16-bit data to form a 64-bit word before it is written into the FIFO. Below, Fig. 10 shows the Register Transfer Level (RTL) schematic for such Joint Numbers block.

Fig. 10. RTL arrangement for the Joint number block to increase the word size to 64-bit.

The FF1-FF4 are daisy-chained to sample the 16-bit serial data at the rising edge of the AD CLK. The four FF's outputs are combined to form the 64-bit word. The FF5 then samples the concatenated words. The divided by 4 AD CLK samples the data for FF5 at the rising edge. Further, the divided clock is used as the FIFO write clock (Write CLK). The Multiplexers MUX1-MUX4 are used to clear the FF(s) during the acquisition process at the start of each new measurement. Moreover, the FIFO is controlled by the FSM using four control I/Os named FIFO Empty (FiE), FIFO Full (FiF), Read Enable (RE), and Write Enable (WE).

#### Data Transmissions over UART

As shown in Fig. 6, the UART module contains two control signals: Transmit Data Valid (TxDV) and Transmit Done (UTxD). Further, the module is pre-configured at a baud rate of 460800. The FSM controls these handshaking signals. Further, the UART reads 16-bit data from the FIFO, which is multiplexed for Lower Byte (LB) and Higher Byte (HB) before being transmitted via serial transmission.

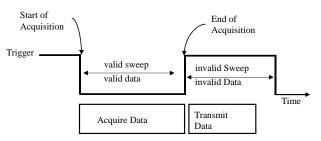

#### Finite State Machine for Controller

The sequence of module operations must be controlled via a handshaking sequence. The entire sequential process of the operations of the DAQ was simplified using a FSM. The initial sequence begins with the trigger signal from the TLS, which must be continuously monitored for valid laser sweep and, thus, valid data measurement by the FSI system. The DAQ is designed to acquire data during the valid sweep period and then transmit data via UART during the invalid sweep period. The diagram below Fig. 11 illustrates its principal operation.

Fig. 11. The timing sequence of DAQ process with respect to the Trigger signal from the TLS.

After the four-stage synchroniser, the FSM monitors the falling and rising edges of the trigger signal to determine the start and end of the acquisition process. Further, the state machine was designed to handle handshaking sequences to generate further control signals for the FIFO and UART modules to ensure smooth data flow.

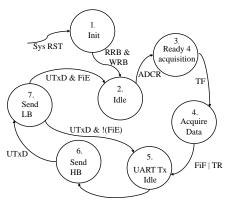

The state diagram in Fig. 12 shows the seven state transitions for the FSM. After issuing a system reset, the Initialisation state (1) waits for the read reset busy (RRB) and write reset busy signal (WRB) from the FIFO before it transitions to Idle (2). The ADC configuration ready (ADCR) signal is monitored at the Idle state, which is asserted soon after the MCU completes the ADC configuration. This is done during the initial power-up sequence. The state moves to Ready for acquisition (3) and waits to detect the falling edge from the trigger (TF) signal before moving to Acquire Data (4) state to begin the acquisition. The FIFO Write Enable (WR) signal is asserted to begin acquiring data from the ADC as the transition takes place from (3) to (4). Assertion of either the rising edge (TR) of the trigger signal or the FIFO full (FiF) signal terminates the data acquisition, and the state will be transitioned to UART transmit Idle (5), where the FIFO read enable (RE) is asserted. After the following clock cycle, the state transitions to Send Higher Byte (6), where the Tx Data valid (TxDV) is asserted while the FIFO Read Enable (RE) is de-asserted, and the state transmits the higher byte via UART serial bus. State 6 monitors for the UART transmit done (UTxD) signal, which confirms the successful UART transmission, before transitioning to Send Lower Byte (7) where UTxD is monitored again before the state returns to 5. This sequence continues until the FIFO is empty before the state returns to 2.

Fig. 12. FSM state transition diagram for the DAQ sequence.

#### V. FSI EXPERIMENTAL SETUP

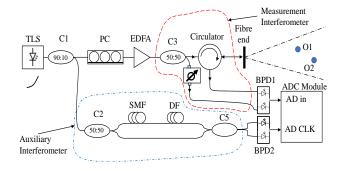

In this paper, the performance of the FSI system with the custom-developed DAQ is compared with the commercially available real-time acquisition system: a National Instruments NI5752 and FlexRIO. The optical setup for FSI system is shown in Fig. 13. The TLS with the output power of 1 mW and a tuning range of 30 nm (1530 nm -1560 nm) was used. The tuning rate of the laser was set to 2000 nm/s throughout the experiment. The trigger signal from the TLM-8700 is interfaced with the ADC module(s) to synchronise the valid measurement cycle.

Fig. 13. The arrangement of a fibre-based optical system for FSI measurement.

In this proposed configuration, the measurement and auxiliary interferometers receive respective power of 90% and 10% from the TLS after coupler C1. The light to the measurement interferometer is passed through the polarisation controller (PC) and then via Erbium-Doped Fibre Amplifier (EDFA) to the coupler C3. The 3 dB coupler C3 splits the light, where one end inputs to the circulator, focusing on objects O1 and O2. Another output from the C3 is fed through a variable optical attenuator. Both the circulator and the variable optical attenuator outputs are connected to the balanced photo detector1 (BPD1). The circulator acts as a sensor head that transmits and receives light to the objects (O1, O2) where O1 and O2 are retroreflecting spheres with a refractive index of n~1.955 at a wavelength of 1550 nm. The output from the BPD1 is interfaced to one of the ADC channels. The auxiliary interferometer has been adapted to the Mach-Zehnder type with a mismatch path length of 22.44 m. The auxiliary

interferometer is illuminated using the 10% optical power from C2. The Single Mode Fibre (SMF) is used in series with the matching dispersion compensation fibre to minimise the fibre dispersion [23]. The coupler C5 creates an interference pattern which the BPD2 detects. The signal detected by the BPD2 generates the oscillating voltage created by the interference pattern. The sinusoid signal generated by BPD2 is converted to a suitable clock signal for the external ADC clock using the clock-generating circuit discussed in [20].

#### VI. RESULTS AND DISCUSSION

The comparison between NI5752 and the custom-designed DAQ (C-DAQ) was performed by comparing FSI measurements taken simultaneously by both systems. Both National Instruments vertex-5 based PXIe-7966R and the Artix-7-based Nexys video FPGA development board are designed with similar digital design methods including the state machine. The total manufacturing cost of a customised ADC module is estimated to be £280, including PCB and the electronic components. The average cost comparison for such DAQ containing programable FPGA and the ADC module is listed in Table 1. The table compares the two commercially available DAQ systems. The XA-160M has been identified as a potential commercial DAQ for the FSI long-range measurement system.

TABLE I AVERAGE COST COMPARISON

| Compact DAQ<br>System | Average<br>Cost (£) | Sample<br>rate<br>(MS/s) | Interface | Number<br>of ADC<br>Channels |

|-----------------------|---------------------|--------------------------|-----------|------------------------------|

| Custom Designed       | 830                 | 160                      | USB       | 2                            |

| DAQ                   |                     |                          |           |                              |

| NI5752&FlexRIO        | 25,468              | 50                       | PXIe      | 16                           |

| XA-160M               | 7,700               | 160                      | PCIe      | 2                            |

The custom designed DAQ systems utilise the USB interface, which has adapted to a virtual COM at a baud rate of 460,800, limiting the data being transferred to the host application. However, the chosen FPGA has an integrated block for the PCIe core, this feature allows the development of a PCIe endpoint application with little or no cost to the DAQ system.

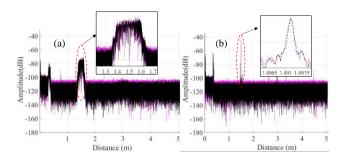

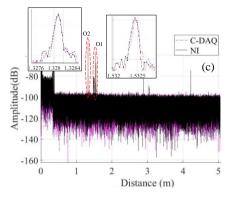

The FSI results obtained by the custom designed DAQ are shown in Fig. 14. The host application processor has been used to compute the FFT. As it can be seen in Fig. 14(a), the detected peak is broadened due to the nonlinear tuning of TLS, where DAQ uses the constant sampling clock for the measurement. However, Fig. 14(b) shows the narrow peak showing the object distance with the resolution of 40 µm when it uses a K-clock for sampling. It also should be noted that the unwanted frequency components at the lower distance between 0 and 0.380257 m are also detected. The Rayleigh backscattering in the length of the fibre end and the reflections inside the circulator is responsible for the unwanted multiple peaks [24]. Since these unwanted signals are constant across the measurement and they could be easily removed using signal processing techniques. Fig. 14(c) also shows the simultaneous detection of objects O1 and O2 at distances of 1.53244 m and 1.32810 m, respectively.

Fig. 14. The FSI measurement results comparison between C-DAQ and NI. (a) The distance measurement of a single object at a distance of 1.49115 m using a constant sampling clock; (b) The same object at a distance measured using the K-clock method; (c) Two objects O1 and O2 are simultaneously detected at a distance of 1.53244 m and 1.32810 m respectively.

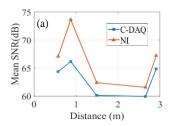

The SNR summary of simultaneous FSI measurement results between C-DAQ and NI FlexRIO-based DAQ are shown in Fig. 15. The NI system outperformed with SNR over C-DAQ. This is due to the non-ideal configurations in the analogue ground plane for ADC16DV160. The PCB can be further improved by extending the ground plane between ADC16DV160 exposed pad and the analogue ground. For a given set of laser sweep parameters, the number of samples for each scan is expected to be constant. However, variations in the number of data points between two DAQ systems were found in each of the ten samples over five corresponding object distances at 0.575736 m, 0.874762 m, 1.49091 m, 2.65118 m and 2.90585 m. The standard deviation of variations in sample number for the NI Flex RIO based systems and the C-DAQ was 6.1905 and 4.6077, respectively. This is due to the asynchronous trigger interface to both DAQ systems, where C-DAQ has four fourstage synchronisers, causing less variability of samples compared to the two-stage synchronisers NI FlexRIO-based DAQ. The results show that the C-DAQ has shown fewer sample number variations over NI FlexRIO, showing that the selection of hardware and the design method can potentially improve measurement quality as well as the cost of the systems.

Fig. 15. The FSI SNR performance between NI and C-DAQ.

#### VII. CONCLUSION

This study presents the design and implementation of a costeffective dual-channel ADC module, in conjunction with an FPGA-based DAQ system, that is fully compatible with FSI measurements. It further underscores the crucial role of the external K-Sampling clock in linearising the behaviour of the TLS. The resulting systems, while being 10% the cost of comparable commercial alternatives, don't compromise on functionality. Important considerations for developing such a system to measure FSI signals using FPGA are also detailed, providing insights into key aspects of the design process. We have compared the performance of our developed FPGA-based DAQ system with the commercial NI PXIe-based FlexRIO equipped with NI5752, which shares a very similar design to our custom DAQ (C-DAQ). Additionally, we have elaborated on the discrete mathematical model that aids in mitigating the nonlinearity behaviours of the TLS by employing the K-Clock sampling method. One limitation observed in the C-DAQ was the data transfer throughput to the host application, which is recognized as an area for improvement. The FPGA chosen for this project, integrated with a Gen 2 PCIe hard IP core, holds the potential to replace the USB with a 4-lane PCIe for improved performance for extended applications. This is a recommended upgrade for future iterations of the system.

#### ACKNOWLEDGEMENT

Our sincere thanks to Ben Hughes, Giovanni Mattia Lazzerini and Michael A. Campbell from Dimensional Metrology, National Physical Laboratory (NPL) for their guidance and support.

#### REFERENCES

- [1] A. Reichold, "Absolute distance measurement using frequency scanning interferometry," *Modern Interferometry for Length Metrology*: IOP Publishing, 2018, pp. 8-1-8-54. [Online]. Available: <a href="http://dx.doi.org/10.1088/2053-2563/aadddcch8">http://dx.doi.org/10.1088/2053-2563/aadddcch8</a>

- [2] J. P. Domingues, S. F. Silva, C. F. M. Loureiro, R. Bernardes, A. M. Morgado and F. M. C. Clemêncio, "Data acquisition and laser scanning synchronism in SS-OCT An experimental apparatus," 2017 IEEE 5th Portuguese Meeting on Bioengineering (ENBENG), Coimbra, Portugal, 2017, pp. 1-4, doi: 10.1109/ENBENG.2017.7889426.

- [3] N. A. Bartley C. Johnson, MA (US); Dale C. Flanders, Lexington, MA (US) "OCT system with tunable clock system for flexible data acquisition," United States Patent Appl. US 2014/0125986 A1.

- [4] Fox-Murphy A.F, Howell D.F, Nickerson R.B, Weidberg A.R, "Frequency scanned interferometry (FSI): the basis of a survey

- system for ATLAS using fast automated remote interferometry" Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, 1996, vol. 383, no. 1: p. 229-237.

- [5] J. Dale, B. Hughes, A. J. Lancaster, A. J. Lewis, A. J. H. Reichold, and M. S. Warden, "Multi-channel absolute distance measurement system with sub ppm-accuracy and 20 m range using frequency scanning interferometry and gas absorption cells," *Opt. Express*, vol. 22, no, pp. 24869-24893, 2014, doi: 10.1364/OE.22.024869.

- [6] M. Campbell, B. Hughes, and D. Veal, "A novel co-ordinate measurement system based on frequency scanning interferometry," *Quality Digest*, 2016.

- [7] J. A. Stone, A. Stejskal, and L. Howard, "Absolute interferometry with a 670-nm external cavity diode laser," *Appl. Opt.*, vol. 38, no. 28, pp. 5981-5994, 1999, doi: 10.1364/AO.38.005981.

- [8] R. Schneider, P. Thürmel, and M. Stockmann, "Distance measurement of moving objects by frequency modulated laser radar," Opt. Eng., vol. 40, no. 1, pp. 33–37, Jan. 2001, doi: 10.1117/1.1332772.

- [9] C. Lu, G. Liu, B. Liu, F. Chen, and Y. Gan, "Absolute distance measurement system with micron-grade measurement uncertainty and 24 m range using frequency scanning interferometry with compensation of environmental vibration," *Opt. Express*, vol. 24, no. 26, pp. 30215-30224, 2016, doi: 10.1364/OE.24.030215.

- [10] J. J. Martinez, M. A. Campbell, M. S. Warden, E. B. Hughes, N. J. Copner, and A. J. Lewis, "Dual-Sweep Frequency Scanning Interferometry Using Four Wave Mixing," *IEEE Photonics Technology Letters*, vol. 27, no. 7, pp. 733-736, 2015, doi: 10.1109/LPT.2015.2390779.

- [11] B. Mudabbir, L. Ping, B. Michael, and R. O. Paul, Jr., "Self-correction of nonlinear sweep of tunable laser source in OFDR," in *Proc.SPIE*, 2019, *Fiber Optic Sensors and Applications XVI*, vol. 11000, doi: 10.1117/12.2518394. [Online]. Available: https://doi.org/10.1117/12.2518394

- [12] J. Song, W. Li, P. Lu, Y. Xu, L. Chen, and X. Bao, "Long-Range High Spatial Resolution Distributed Temperature and Strain Sensing Based on Optical Frequency-Domain Reflectometry," *IEEE Photonics Journal*, vol. 6, no. 3, pp. 1-8, 2014, doi: 10.1109/JPHOT.2014.2320742.

- [13] M. Badar, P. Lu, M. Buric, and P. Ohodnicki, "Integrated Auxiliary Interferometer for Self-Correction of Nonlinear Tuning in Optical Frequency Domain Reflectometry," *Journal* of *Lightwave Technology*, vol. 38, no. 21, pp. 6097-6103, 2020, doi: 10.1109/JLT.2020.3007703.

- [14] K. Takada, "High-resolution OFDR with incorporated fiber-optic frequency encoder," *IEEE Photonics Technology Letters*, vol. 4, no. 9, pp. 1069-1072, 1992, doi: 10.1109/68.157152.

- [15] S. Jiang, B. Liu, H. Wang, and B. Zhao, "Absolute Distance Measurement Using Frequency-Scanning Interferometry Based on Hilbert Phase Subdivision," *Sensors*, vol. 19, no. 23, p. 5132, 2019, doi: 10.3390/s19235132.

- [16] Z. Wang et al., "Cubic meter volume optical coherence tomography," Optica, vol. 3, no. 12, pp. 1496-1503, 2016, doi: 10.1364/OPTICA.3.001496.

- [17] C. A. Pallikarakis, J. M. Huntley, and P. D. Ruiz, "High-speed range and velocity measurement using frequency scanning interferometry with adaptive delay lines [Invited]," *J. Opt. Soc. Am. A*, vol. 37, no. 11, pp. 1814-1825, 2020, doi: 10.1364/JOSAA.403858.

- [18] C. Moreno, A. González, J. L. Olazagoitia, and J. Vinolas, "The Acquisition Rate and Soundness of a Low-Cost Data Acquisition System (LC-DAQ) for High Frequency Applications," *Sensors*, vol. 20, no. 2, p.524, 2020, doi: 10.3390/s20020524.

- [19] F.-C. Gu, H.-C. Chang, Y.-M. Hsueh, C.-C. Kuo, and B.-R. Chen, "Development of a High-Speed Data Acquisition Card for Partial Discharge Measurement," in *IEEE Access*, vol. 7, pp. 140312-140318, 2019, doi: 10.1109/ACCESS.2019.2943484.

- [20] S. Sivanathan, M. A. Roula, N. J. Copner, and B. Copner, "Development of a Hardware for Frequency Scanning Interferometry for Long Range Measurement," in 2022 IEEE International Instrumentation and Measurement Technology

- Conference (12MTC), Ottawa, ON, Canada, 2022, pp. 1-6, doi: 10.1109/I2MTC48687.2022.9806618.

- [21] T. Zhang, X. Qu, and F. Zhang, "Nonlinear error correction for FMCW ladar by the amplitude modulation method," *Opt. Express*, vol. 26, no. 9, pp. 11519-11528, 2018, doi: 10.1364/OE.26.011519.

- [22] Q. Dun *et al.*, "Dual-frequency sweeping light source based on four-wave mixing in silicon-on-insulator nano-waveguide," in *Proc.SPIE*, 2023, vol. 12334, p. 1233407, doi: 10.1117/12.2647370. [Online]. Available: https://doi.org/10.1117/12.2647370

- [23] M. A. Campbell, B. Hughes, J. Blanchard and J. Heaps, "Frequency Scanning Interferometry and K-space Clocking with Dispersion Compensating Fibre," 2023 IEEE International Instrumentation and Measurement Technology Conference (I2MTC), Kuala Lumpur, Malaysia, 2023, pp. 01-06, doi: 10.1109/I2MTC53148.2023.10175979.

- [24] M. S. Warden, "Precision of frequency scanning interferometry distance measurements in the presence of noise," *Appl. Opt.*, vol. 53, no. 25, pp. 5800-5806, 2014, doi: 10.1364/AO.53.005800.

Sivagunalan Sivanathan (Student Member, IEEE) received his MEng degree in Electronic and Communication Engineering (Distinction) and postgraduate certificate in Learning and Teaching in Higher Education (PgCLTHE) from the University of South Wales 2014 and 2018. He is currently pursuing his part time Ph.D. degree in electronic engineering at university of South Wales. Sivagunalan is an associate professor at the Faculty of Computing and Engineering and

Science at the University of South Wales. His research interests include realtime embedded systems, Advanced digital systems design, Laser LiDAR technology for Metrology applications and advanced Novel Data acquisitions Systems.

Ali Roula is an IEEE member and a Professor in Biomedical Engineering with a degree in Electronic Engineering and PhD in computer science from Queen's University of Belfast, on research looking at applying Machine Learning to quantitative pathology and cancer diagnosis. He has taken up various roles as head of Electronics department at the University of South Wales, and previously as head of medical Electronics and signal processing research unit.

Currently he is a university innovation champion working with businesses to bring biomedical innovation to market. His area of expertise around electronics, signal processing and pattern recognition where he has published extensively. He has worked on a wide range of research and commercial projects in areas around Quantitative Pathology, Magnetic Induction Tomography, Brain Computer Interfacing and Molecular Diagnostics.

Kang Li was born in Xianyang, China, in 1980. He received the B.S. degree in optoelectronics from the Changchun University of Science and Technology, Changchun, China, in July 2002, and the Ph.D. degree in optics from the University of Chinese Academy of Sciences, Xi'an Institute of Optics and Precision Mechanics, Chinese Academy of Sciences, Xi'an, in July 2007. From July 2007 to July 2009, he was a Research Officer at the Institute of Advanced Telecommunications,

Swansea University, U.K. From July 2009 to July 2011, he was a Research Assistant at the Faculty of Advanced Technology, University of South Wales (Glamorgan University), UK. From January 2011 to June 2015, he was a Research Fellow at the Wireless and Optoelectronics Research and Innovation Centre (WORIC), Faculty of Computing, Engineering and Science, University of South Wales. Since 2015, he has been a Lecturer and

Senior Research Fellow within Faculty of Computing, Engineering and Science, University of South Wales. He has authored more than 50 articles and more than 10 inventions. His research interests include solid state lasers, optical fiber lasers, nonlinear optics, new wavelength, novel applications laser sources, and nano waveguide and potential applications of these technologies in areas such as FSI absolute distance measurement, biomedical optical coherence tomography, fast modulation, wavelength conversion, and all-optical metrology.

**Dun Qiao** received the Ph.D. degree from University of South Wales, Treforest, United Kingdom, in 2023. He is currently a research associate at Cardiff University, Cardiff, United Kingdom, and develops wide-tunable lasers and integrated photonic devices based on Quantum Dots (QD) on silicon platforms.

Nigel Copner received a First Class Physics B.S. (Hons.) degree from Reading University (1988) and a Ph.D. degree in laser physics from Swansea University (1992). He then undertook various research and managerial roles both with industry and academia. As a senior manager at JDS Uniphase (San Jose) he innovated and developed many new telecom concepts/devices leading to over 20 patents being filed. Some of these innovations such as the optical switch,

dispersionless interleaver, blue note laser etc are still collectively generating revenues in excess of £50m/year with the optical switch being the best-selling mechanical optical switch. Within Academia he has won over £10m in research grants over 14 years and innovated many new concepts with many being assigned to companies and institutions (increasing total number patents >40). This includes concepts on pivot point independent tuneable laser, TIR elimination in LED emission, four wave mixing to eliminate vibration in metrology, efficient infrared emission etc. He has recently left his optoelectronic chair role at the University of South Wales to undertake a welcome challenge of building a new Engineering Department at Aberystwyth University. His research interests include tuneable lasers, laser metrology, photonics sensing, metamaterial, and nano plasmonics.