# PERFORMANCE MODELLING AND HIGH PERFORMANCE BUFFER DESIGN FOR THE

### SYSTEM WITH NETWORK ON CHIP

By

JIN LIU

A dissertation submitted in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

WASHINGTON STATE UNIVERSITY School of Electrical Engineering and Computer Science

DECEMBER 2007

© Copyright by JIN LIU, 2007 All Rights Reserved To the Faculty of Washington State University:

The members of the Committee appointed to examine the dissertation of JIN LIU find it satisfactory and recommend that it be accepted.

Chair

### ACKNOWLEDGMENT

I would like to offer my sincerest appreciation to my department and my committee members: Dr. José G. Delgado-Frias, Dr. Kung-Chi Wang, and Dr. Sirisha Medidi for their support, guidance, willingness to work with me, and the suggestions each has offered throughout this process. In particular, I would like to thank my major advisor, Dr. José G. Delgado-Frias, for his consistent support, many helpful discussions that guide me through my whole graduate study and research. I could not have asked for more in terms of his never-ending encouragement and support in this study and make my graduate experience an extremely rewarding and positive one.

I would also like to thank the School of Electrical Engineering and Computer Science which has excellent scholars and students. The School has provided me a great environment and experience through my whole study and life at WSU.

Finally, I must also acknowledge the support and encouragement from my wife and my parents. Words can never express my thankfulness for their love and support.

iii

# PERFORMANCE MODELLING AND HIGH PERFORMANCE BUFFER DESIGN FOR THE SYSTEM WITH NETWORK ON CHIP

Abstract

by Jin Liu, Ph.D. Washington State University DECEMBER 2007

Chair: José G. Delgado-Frias

High performance novel dynamically allocated multi-queue (DAMQ) buffer schemes for systems with network on chip (NoC) have been proposed and evaluated in this dissertation. An analytical model to predict performance of a NoC where wormhole switching technique and fully adaptive routing protocols has been developed and compared with simulations.

In this dissertation, a novel analytical model for NoC which makes use of simple close form calculations is presented. This model provides accurate network performance prediction in the network stable region. The validity of this model is demonstrated by comparing analytical prediction with simulation results obtained on high-radix *k*-ary 2-cube networks.

Three novel switch buffer schemes, DAMQ<sub>all</sub>, DAMQ<sub>min</sub> and DAMQ<sub>shared</sub>, for system on chip with an interconnection network are also reported. The proposed schemes are based on a DAMQ self-compacting buffer hardware design. These schemes outperform existing approaches. DAMQ<sub>all</sub> have similar performance using only half of the buffer size used in traditional SAMQ implementations. DAMQ<sub>min</sub> provides an excellent approach to optimize buffer management providing a good throughput when the network has a larger load. DAMQ<sub>shared</sub> scheme lets virtual channels from different physical channel share free buffer space. While providing similar performance, DAMQ<sub>shared</sub> scheme uses only around sixty percent of the buffer size that is used in

traditional implementation for NoCs. In addition, using same size buffers,  $DAMQ_{shared}$  outperforms existing approaches such as SAMQ and  $DAMQ_{all}$  by 1% to 2% in throughput. The proposed schemes also make a better utilization of the available buffer space.

## TABLE OF CONTENTS

|                                                | Page |

|------------------------------------------------|------|

| ACKNOWLEDGEMENTS                               | iii  |

| ABSTRACT                                       | iv   |

| LIST OF TABLES                                 | vii  |

| LISTOF FIGURES                                 | viii |

| CHAPTER                                        |      |

| 1. INTRODUCTION                                | 1    |

| 1.1 System with Network on Chip                | 1    |

| 1.2 Dissertation Outline                       | 3    |

| 2. BACKGROUND                                  | 5    |

| 2.1 Network Topology                           | 5    |

| 2.2 Switching Techniques                       | 10   |

| 2.3 Virtual Channel                            | 13   |

| 2.4 Buffer Schemes                             | 15   |

| 2.4.1 Linked list buffer scheme                | 15   |

| 2.4.2 Self-compacting buffer scheme            | 18   |

| 2.5 Routing Algorithms and Analytical Models   | 18   |

| 2.5.1 Deterministic routing protocols          | 18   |

| 2.5.2 Adaptive routing protocols               | 19   |

| 3. ANALYTICAL MODEL FOR WORMHOLE SWITCHING NOC | 21   |

| 3.1 Network Configuration                      | 21   |

| 3.2 Pertinent Assumptions                   |                      |

|---------------------------------------------|----------------------|

| 3.3 Notations                               |                      |

| 3.4 Calculation of Average Message Latency  |                      |

| 3.5 Validation                              |                      |

| 3.6 Apply model to multiple flit buffer     |                      |

| 3.7 Conclusion                              |                      |

| 4. HIGH PERFORMANCE DAMQ BUFFER SCH         | HEMES42              |

| 4.1 DAMQ with Reserved Space for All Virtua | l Channels42         |

| 4.2 DAMQ with Minimum Reserved Space for    | Virtual Channels47   |

| 4.3 Shared DAMQ with Reserved Space for Al  | l Virtual Channels51 |

| 4.4 Performance Evaluation                  | 60                   |

| 4.4.1 Simulation Experiments Setup          | 60                   |

| 4.4.2 Examined Performance Metrics          |                      |

| 4.4.3 Simulation Results                    | 64                   |

| 4.5 Conclusion                              |                      |

| 5. CONCLUSION AND FUTURE STUDY              |                      |

| 5.1 Major Contributions                     |                      |

| 5.2 Future Research Directions              |                      |

| REFERENCES                                  |                      |

## LIST OF TABLES

| 3.1 | The Parameter Notations | 25 |  |

|-----|-------------------------|----|--|

|-----|-------------------------|----|--|

| 4.1 The Performance 4-ary, 2-cube network composed of block switches. Shown is the |

|------------------------------------------------------------------------------------|

| throughput obtained from simulations where 4 virtual channels used                 |

| 4.2 The Performance 4-ary, 2-cube network composed of block switches. shown is the |

| message latency obtained from simulations where 4 virtual channels used            |

| 4.3 The Performance 4-ary, 2-cube network composed of block switches. Shown is the |

| throughput obtained from simulation where 8 virtual channels used                  |

| 4.4 The Performance 4-ary, 2-cube network composed of block switches. Shown is the |

| message latency obtained from simulations where 8 virtual channels used73          |

| 4.5 The Performance of 8-Ary, 2-Cube Network Composed Of Block Switches. Shown     |

| is the Throughput Obtained for Simulations Where 4 Virtual Channels per Physical   |

| Channel Used When Uniform Traffic is applied76                                     |

| 4.6 The Performance of 8-ary, 2-cube Network Composed of Block Switches. Shown     |

| is the Message Latency Obtained from Simulations Where 4 Virtual Channels per      |

| Physical Channel Used When Uniform Traffic is Applied77                            |

| 4.7 The Performance of 8-ary, 2-cube Network Composed of Block Switches. Shown     |

| is the Buffer Usage Obtained from Simulations Where 4 Virtual Channels per         |

| Physical Channel Used When Uniform Traffic is Applied78                            |

| 4.8 The performance 8-ary, 2-cube Network Composed of Block Switches. Shown        |

| is the Throughput Obtained from Simulations Where 4 virtual Channels per           |

| Physical Channel Used When Hotspots Traffic is Applied                             |

| 4.9 The performance of 8-ary, 2-cube Network Composed of Block Switches. Shown     |

is the Message Latency Obtained from Simulations Where 4 virtual Channels per

|      | Physical Channel Used When Hotspots Traffic is Applied                            |   |

|------|-----------------------------------------------------------------------------------|---|

| 4.10 | The performance of 8-ary, 2-cube Network Composed of Block Switches. Shown        |   |

|      | is the Buffer Usage Obtained from Simulations Where 4 virtual Channels Per        |   |

|      | Physical Channel Used When Hotspots Traffic is Applied                            |   |

| 4.11 | The performance of 8-ary, 2-cube Network Composed of Block Switches. Shown        |   |

|      | is the Throughput Obtained from Simulations Where 4 virtual Channels Per          |   |

|      | Physical Channel Used When Hotspots Traffic is Applied                            |   |

| 4.12 | The performance of 8-ary, 2-cube Network Composed of Block Switches. Shown        |   |

|      | is the Message Latency Obtained from Simulations Where 4 virtual Channels Per     |   |

|      | Physical Channel Used When Hotspots Traffic is Applied                            |   |

| 4.13 | The Performance of 4-ary, 2-cube Network Composed of Block Switches. Shown        |   |

|      | is the Throughput Obtained from Simulations Where 4 Virtual Channels Per Physical | ļ |

|      | Channel Used When Uniform Traffic is Applied                                      |   |

| 4.14 | The Performance of 4-ary, 2-cube Network Composed of Block Switches. Shown        |   |

|      | is the Message Latency Obtained from Simulations Where 4 Virtual Channels Per     |   |

|      | Physical Channel Used When Uniform Traffic is Applied97                           |   |

| 4.15 | The Performance of 4-ary, 2-cube Network Composed of Block Switches. Shown        |   |

|      | is the Buffer Usage Obtained from Simulations Where 4 Virtual Channels Per        |   |

|      | Physical Channel Used When Uniform Traffic is Applied                             |   |

## LIST OF FIGURES

| 2.1  | Examples of NoC topologies                                                 | 8  |

|------|----------------------------------------------------------------------------|----|

| 2.2  | Blocked message in a wormhole network                                      | 12 |

| 2.3  | Virtual channels multiplexing a physical channel                           | 13 |

| 2.4  | Use virtual channel to reduce blocking                                     | 14 |

| 2.5  | Input buffer schemes                                                       | 17 |

| 3.1  | 64 nodes torus message exchanging system                                   | 22 |

| 3.2  | Switch to switch path                                                      | 23 |

| 3.3  | Queuing model for an input channel                                         | 29 |

| 3.4  | Reduced queuing model for an input channel                                 | 31 |

| 3.5  | Comparison of Model against simulation in 64 nodes torus network           |    |

| 3.6  | Comparison of Model against simulation in 256 nodes torus network          | 37 |

| 3.7  | Comparison of Model against simulation in 1024 nodes torus network         | 37 |

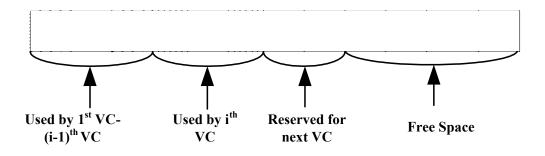

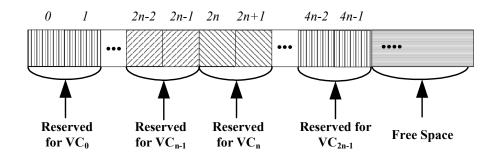

| 4.1  | DAMQ <sub>all</sub> Buffer space at the initial state                      | 43 |

| 4.2  | DAMQ <sub>all</sub> Buffer space status in operations                      | 44 |

| 4.3  | Pseudo-code for in buffer operations                                       | 45 |

| 4.4  | Pseudo-code for out buffer operations                                      | 46 |

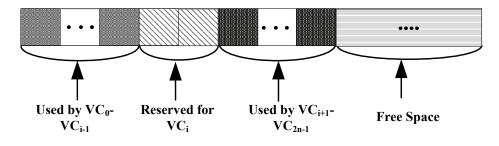

| 4.5  | DAMQ <sub>min</sub> Buffer space status in operations                      | 48 |

| 4.6  | Pseudo-code of in buffer operations for DAMQ <sub>min</sub>                | 49 |

| 4.7  | Pseudo-code of out buffer operations for DAMQ <sub>min</sub>               | 50 |

| 4.8  | DAMQ <sub>min</sub> Buffer space status in operations                      | 51 |

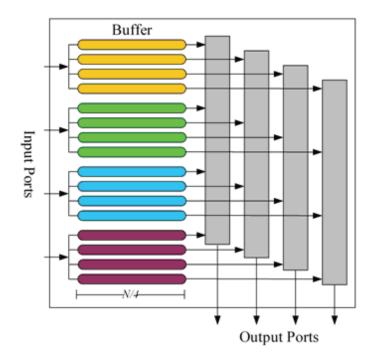

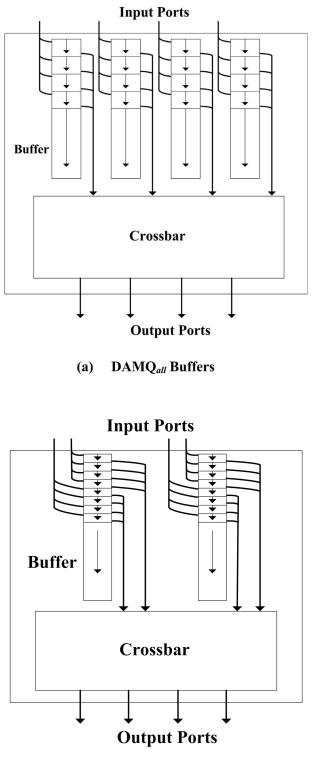

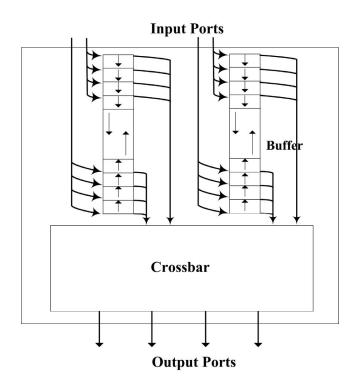

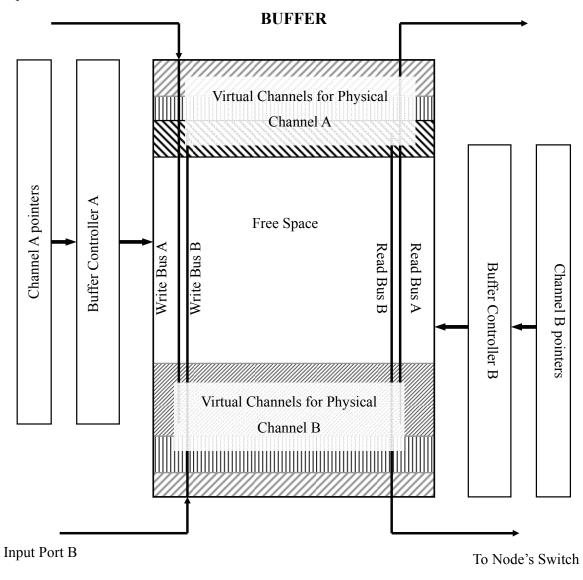

| 4.9  | Switches with DAMQ <sub>all</sub> buffer and DAMQ <sub>shared</sub> buffer | 54 |

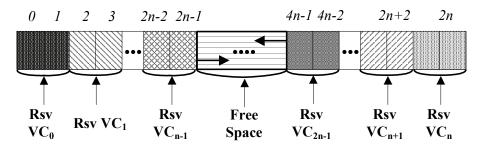

| 4.10 | 0 DAMQ <sub>shared</sub> buffer organization                               | 56 |

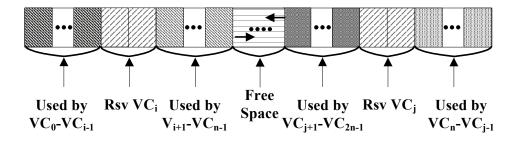

| 4.11 | 1 DAMQ <sub>shared</sub> buffer statuses in initial state and operation    | 58 |

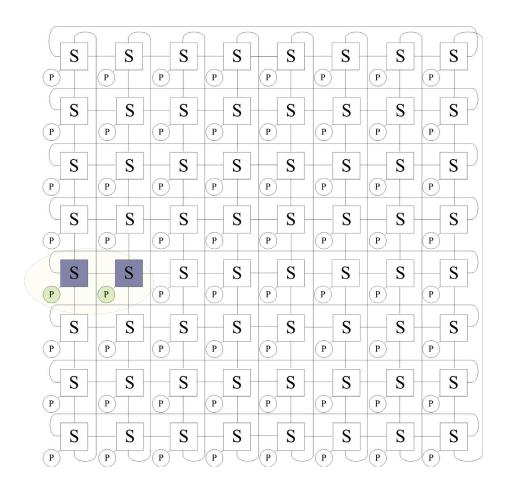

| 4.12 | 2 The base system for our simulations                                      |    |

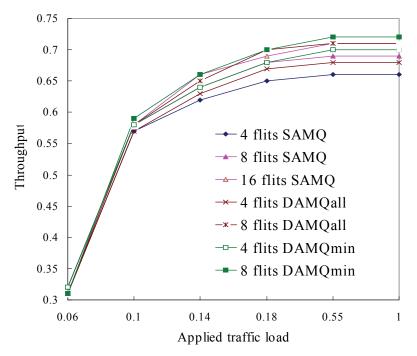

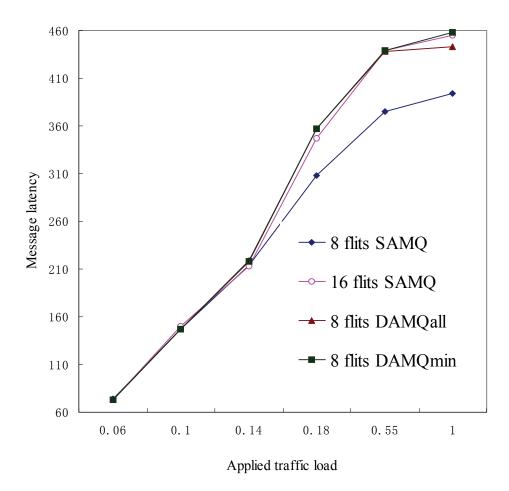

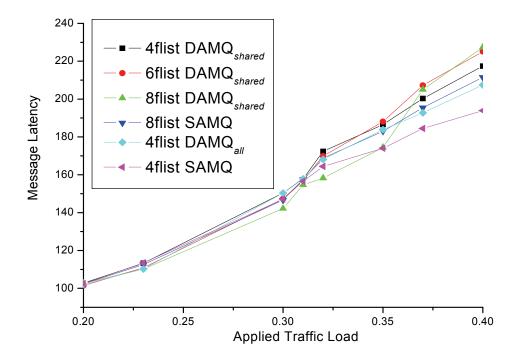

| 4.13 Comparison on throughput between 4/8 flit-buffer $DAMQ_{all} / DAMQ_{min}$ and                |

|----------------------------------------------------------------------------------------------------|

| 4/ 8/ 16 flit-buffer SAMQ                                                                          |

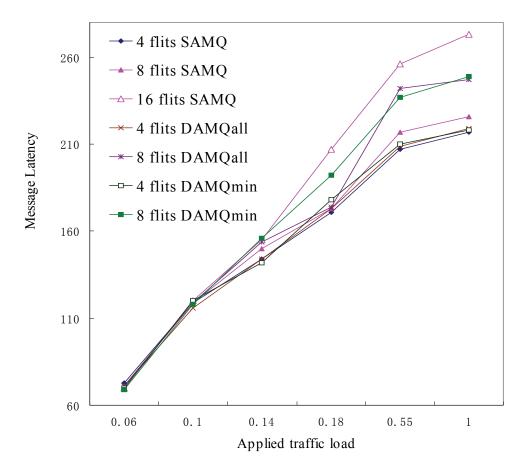

| 4.14 Comparison on Latency between 4/8 flit-buffer $DAMQ_{all}$ / $DAMQ_{min}$ and                 |

| 4/ 8/ 16 flit-buffer SAMQ                                                                          |

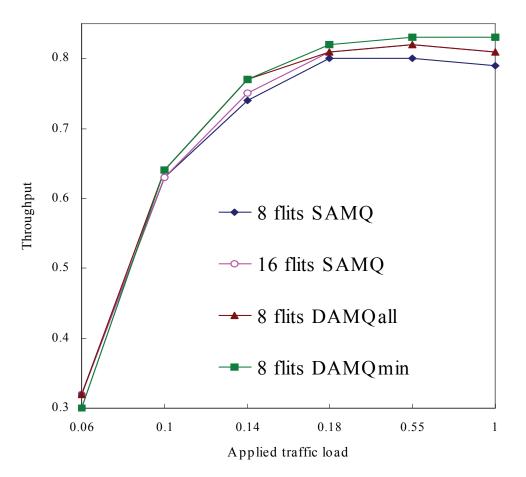

| 4.15 Comparison on Throughput between 8 flit buffer $DAMQ_{all} / DAMQ_{min}$ and                  |

| 8/16 flit-buffer SAMQ70                                                                            |

| 4.16 Comparison on Latency between 8 flit-buffer $DAMQ_{all} / DAMQ_{min}$ and                     |

| 8/16 flit-buffer SAMQ71                                                                            |

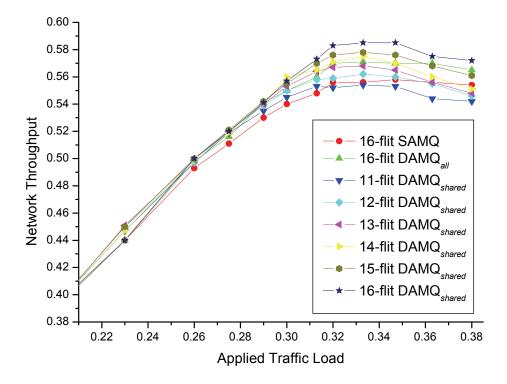

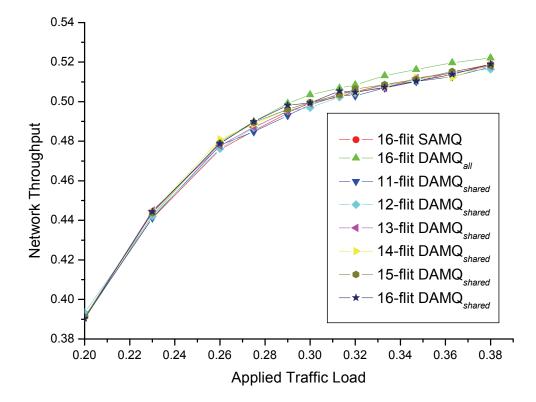

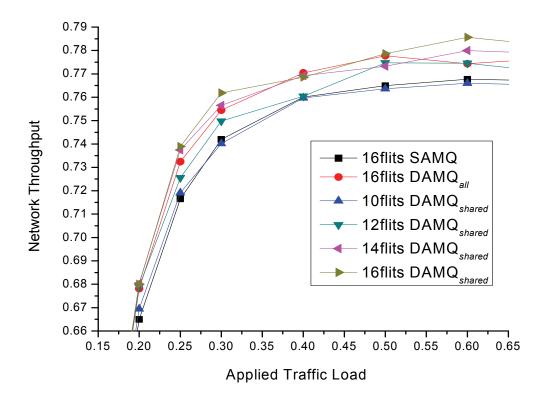

| 4.17 Comparison on throughput between 11-16 flit buffer DAMQ <sub>shared</sub> , 16 flit-buffer    |

| DAMQ <sub>all</sub> and 16 flit-buffer SAMQ under uniform traffic                                  |

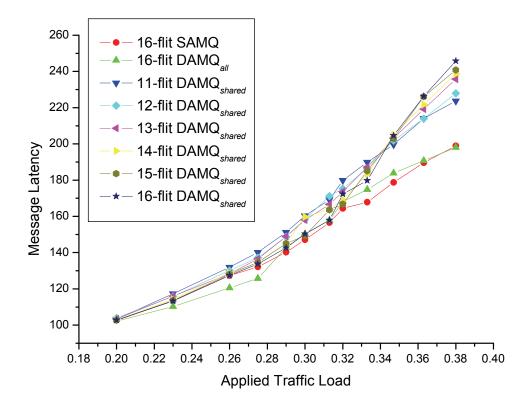

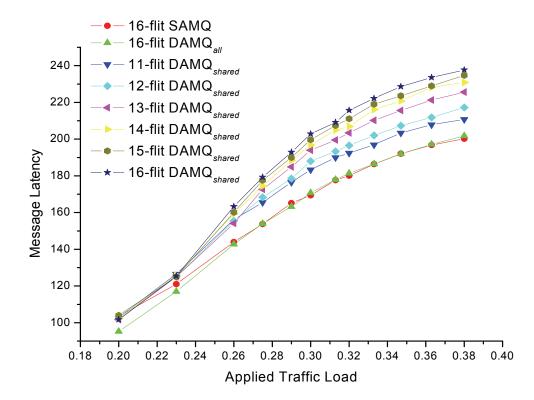

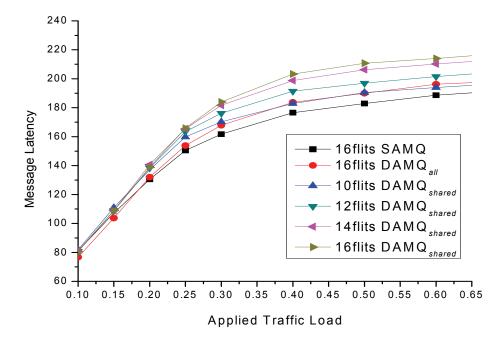

| 4.18 Comparison on latency between 11-16 flit-buffer DAMQ <sub>shared</sub> , 16 flit-buffer       |

| DAMQ <sub>all</sub> and 16 flit-buffer SAMQ under uniform traffic                                  |

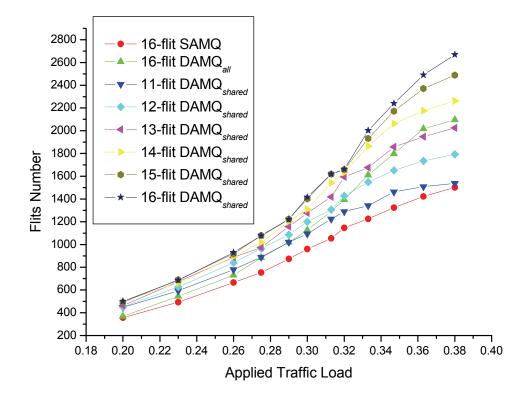

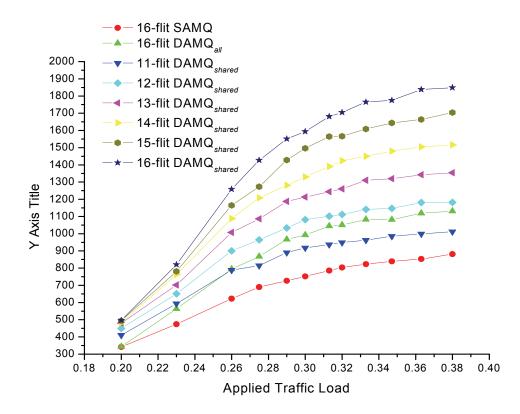

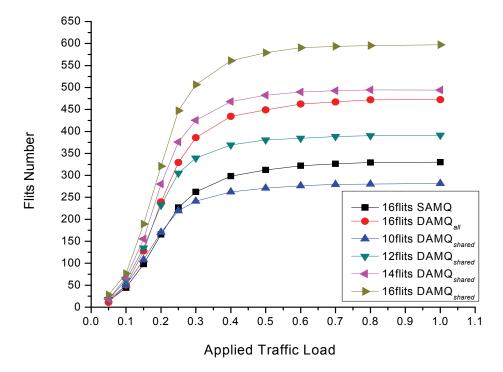

| 4.19 Comparison on buffer usages between 11-16 flit-buffer DAMQ <sub>shared</sub> , 16 flit-buffer |

| DAMQ <sub>all</sub> and 16 flit-buffer SAMQ under uniform traffic                                  |

| 4.20 Comparison on throughput between 11-16 flit-buffer DAMQ <sub>shared</sub> , 16 flit-buffer    |

| DAMQ <sub>all</sub> and 12/16 flit-buffer SAMQ under Hotspots traffic                              |

| 4.21 Comparison on latency between 11-16 flit-buffer DAMQ <sub>shared</sub> , 16 flit-buffer       |

| DAMQ <sub>all</sub> and 12/16 flit-buffer SAMQ under hotspots traffic                              |

| 4.22 Comparison on buffer usages between 11-16 flit-buffer DAMQ <sub>shared</sub> , 16 flit-buffer |

| DAMQ <sub>all</sub> and 12/16 flit-buffer SAMQ under Hotspots traffic                              |

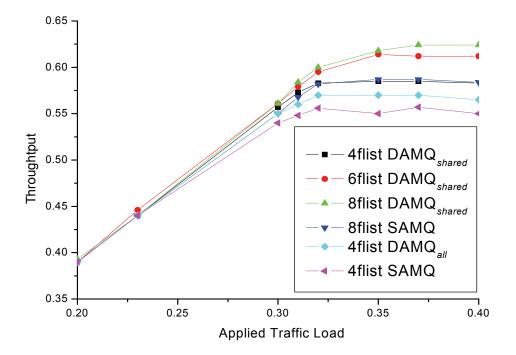

| 4.23 Comparison on throughput between 4/6/8 flit-buffer DAMQ <sub>shared</sub> , 4 flit-buffer     |

| DAMQ <sub>all</sub> and 4/ 8 flit-buffer SAMQ92                                                    |

| 4.24 Comparison on Latency between 4/6/8 flit-buffer DAMQ <sub>shared</sub> , 4 flit-buffer        |

| DAMQ <sub>all</sub> and 4/8 flit-buffer SAMQ93                                                     |

| 4.25 Comparison on throughput between 10-16 flit buffer DAMQ <sub>shared</sub> , 16 flit-buffer    |

|                                                                                                    |

| 4.26 | Comparison on latency between 10-16 flit-buffer DAMQshared, 16 flit-buffer       |    |

|------|----------------------------------------------------------------------------------|----|

|      | DAMQall and 16 flit-buffer SAMQ under uniform traffic                            | 99 |

| 4.27 | Comparison on buffer usages between 10-16 flit-buffer DAMQshared, 16 flit-buffer | er |

|      | DAMQall and 16 flit-buffer SAMQ under uniform traffic1                           | 00 |

# **Chapter 1**

# Introduction

This chapter provides an overall perspective of the research work presented in this dissertation. Section 1 introduces network on chip which is the major topic of this study. Section 2 provides the outline of this dissertation.

### 1.1 System with Network on Chip

System on chip (SoC) designs are becoming widely used in telecommunication, consumer electronics and multimedia areas. As technology allows greater integration, they are being investigated in greater detail. By the end of this decade SoCs will grow up to four billion transistors [24]. SoCs incorporate a number of components (or modules) including processors, controllers and memory arrays. These components need to communicate to pass data and/or control information. Thus, a successful SoC design largely relies on the ability to interconnect these components to compute a solution efficiently.

One of the major problems for future SoC designs is the non-scalable global wire delays [31]. Global wires can carry signals across a chip, but the wire delays typically increase exponentially or at least linearly by inserting repeaters. Therefore SoC design has to rely on networking paradigms. The shared medium arbitrated bus is the most commonly used on-chip interconnect architecture, here all communicating modules share the same transmission medium. Although the bus architecture features simple topology and low area cost, the relatively long bus

to which a number of components are connecting has a quite high parasitic resistance and capacitance [31]. For SoCs consisting of tens or hundreds of IP blocks, the bus-based interconnect architecture will lead to serious bottleneck problems [38]. Another alternative is to have dedicated connections between any given modules, but this design could be extremely complex as the number of modules increases.

To overcome these problems, the use of an interconnection network (direct or indirect network) within a chip has been advocated by researchers. Direct network consists of a set of nodes; each node directly connects to a limited number of other nodes in the network. Two neighboring nodes are connected by a pair of unidirectional channels in opposite directions or a bidirectional channel. Usually these on-chip computational units contain a network interface block called router (switch), which handles communication and connects to neighbor nodes' routers. Thus overlapped computation and communication are realized within each unit. As the total number of nodes in the system increases, the total communication bandwidth, memory bandwidth and processing capability of the system also increase [2]. Therefore direct networks have been a prevalent interconnection architecture.

Similar to the wide area network design, the on-chip interconnection network is proposed to be viewed as a hierarchy of services starting from the physical layer that synchronizes the transfer of bit streams to higher-level protocols layers that perform functions such as packetization, routing etc. [24]. While there is currently no consensus on a standard set of layers for the whole communication system, a three layer model to abstracting the operation of interconnection network is proposed in [2]: the routing layer, the switching layer and the physical layer. Physical layer refers to link-level wiring protocols for transferring messages and managing the physical channels between adjacent routers. Switching layer implements

2

mechanisms for forwarding messages through the network; it determines when and how to connect router inputs to outputs and the time at which message components may be transferred along these paths. Switching layer utilizes flow control mechanisms to synchronize the message transfer; and flow control is tightly coupled with buffer management algorithms that determine how the buffers are used, i.e. how messages are handled when blocked in the network. Routing layer is responsible to make routing decision, determine the output channels at intermediate nodes.

Due to the constraints of being in a single chip, using an interconnection network on chip needs be restricted in terms of area. Thus, it is extremely important to design the schemes that require less hardware resources and still provide a good performance.

The research presented in this dissertation focuses on direct network architecture of NoC. The first part explored the ways to model a directed connected k-ary n-cube. The second part researched the methods to efficiently organize input buffer of switches used in the NoC modules.

### **1.2 Dissertation Outline**

Chapter 2 provides a background on topics related to this dissertation. It describes network topology, switching techniques, flow control, routing algorithms and analytical models for NoC. It also introduces the virtual channel concept and buffer schemes used in NoC switch.

In Chapter 3 a novel analytical model for NoC with wormhole switching and fully adaptive routing is presented. To confirm its validity, the model is compared with results obtained from simulations. Three novel DAMQ input buffer schemes are presented in Chapter 4. Their performance is determined by means of simulations.

Finally, chapter 5 includes a summary, some conclusion remarks, and a list of contributions of this study as well as directions for future research.

# **Chapter 2**

# Background

This chapter provides background on topics related to this dissertation work. The related NoC background information includes: network topology, switching techniques, flow control, routing algorithms, analytical models, virtual channel concept and buffer schemes for switch.

### 2.1 Network Topology

Interconnection networks are usually classified into four major classes based on network topology: shared-medium network, direct network, indirect network, and hybrid network. In shared medium networks, the communication medium is shared by all connected devices. As it was mentioned in chapter 1 the shared bus is an example of this class. Although this architecture is simple, it is not suitable for future NoCs with an increasing number of modules. In direct network, communicating devices are linked to each other by transmission channels. To transmit a message from one device to another, this message needs to traverse through several intermediate devices if the source and destination are not neighboring. On the other hand, an indirect network connects devices by one or more switches, thus any message exchanging requires information transmitting through one or more switches. Finally, hybrid network is also possible by using elements of the previous three paradigms. This research focuses on direct network as most network on chip architectures based on this design. We introduce the common direct network topology used in NoC below.

Network topology can be depicted by a graph in which nodes represent switching points and edges represent communication links [36]. Many direct network topologies have been proposed based on their graph properties. Most of the implemented networks have an orthogonal topology [2]. If every node is connected to every other node then the network is a completely connected network. The completely connected network can use simple routing algorithm and achieves high network performance. However, the cost of the complex architecture makes it impractical for network with large numbers of nodes. In terms of cost and performance, many other orthogonal network topologies such as mesh/torus and hypercube have received more attention. There are a number of network designs with different topology for network on chip reported in the literatures [27-30], among which k-ary n-cubes have been studied and used the most because of their desirable properties, such as ease of implementation, recursive structures, and ability to exploit communication locality to reduce message latency [5].

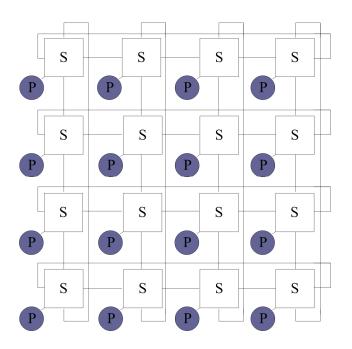

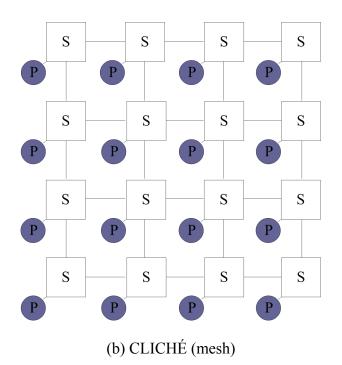

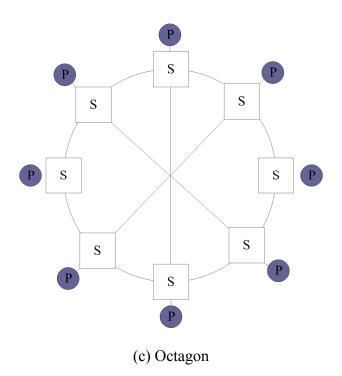

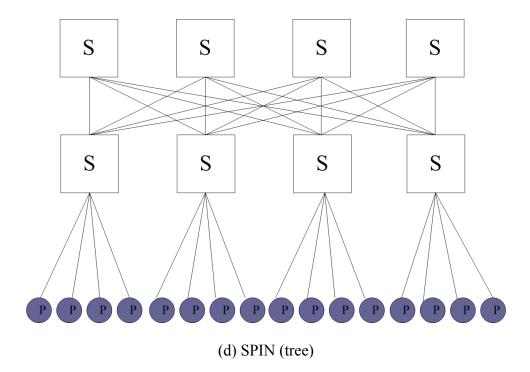

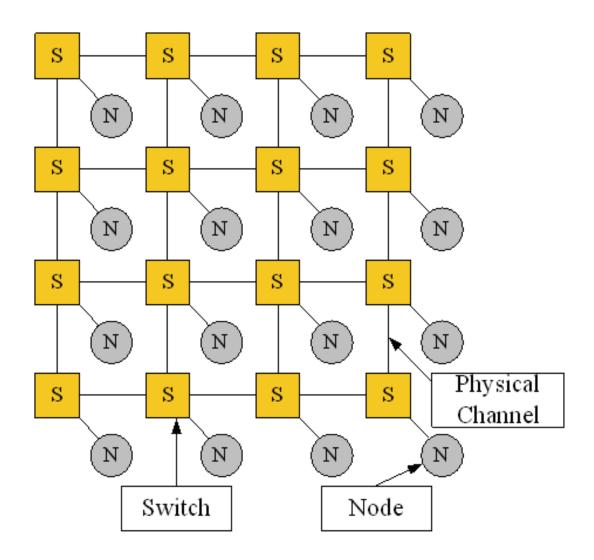

The most commonly used direct network topologies are shown in Fig 1. Each node in these networks is composed of a routing element (switch) and a process element (PE), except the tree like architecture SPIN. In the following, we briefly describe the different NoC topologies proposed recently in the literature.

(a) 2D torus (4-ary 2-cube)

Figure 2.1: Examples of NoC topologies.

Dally and Towles [29] have proposed a 2D torus as NoC architecture as shown in Fig. 2.1a. The torus architecture is basically same as a regular mesh [2] except that the switches at the edges are connected to the switches at the opposite edge through wrap-around channels. Every switch has five ports, one connected to the local resource and the others connected to the closest neighboring switches. The long end-around connections can yield excessive delays. However, this can be avoided by folding the torus.

Kumar et al. [28] proposed a mesh-based interconnect architecture, CLICHÉ (Chip-Level Integration of Communicating Heterogeneous Elements). This architecture is based on an  $m \ge n$  mesh network where every switch, except those at the edges, is connected to four neighboring switches and one computation resource (PE) through communication channels. A channel consists of two unidirectional links between two switches or between a switch and a PE. Shown in Fig. 2.1b is a16 functional IP blocks network.

Guerrier and Greiner [27] proposed a tree like generic interconnect template called SPIN (Scalable, Programmable, Integrated Network) for on-chip packet switched interconnections network. A fat-tree architecture is used to interconnect IP blocks. Fig. 2.1d shows the basic SPIN architecture with 16 nodes, representing the number of functional IP blocks in the system. Every node has four children and the parent is replicated four times at any level of the tree. The size of the network grows at (*NlogN*)/8. The functional IP blocks reside at the leaves and the switches reside at the vertices. In this architecture, the number of switches converges to S = 3N/4, where *N* is the system size in terms of number of functional.

Karim et al. proposed the OCTAGON MP-SoC architecture in [30]. Shown in Fig. 1c is an octagon unit consisting of eight nodes and 12 bidirectional links. According to topology, exchanging message between any pair of nodes takes at most two hops. To design a system consisting of more than eight nodes, the octagon can be extended to multidimensional space on a significantly increased wiring complexity.

#### **2.2 Switching Techniques**

The switching techniques employed in on-chip interconnection networks initially followed those techniques employed in local and wide area communication networks, e.g. circuit and packet switching.

In circuit switching, a physical path from source to destination must be reserved prior to the data transmission. Physical path is set up by routing header flit which contains destination address and some other information. Once a routing header flit reaches the destination, a complete path is set up and an acknowledgement is transmitted back to the source. Physical path is reserved for the duration of message and may be idle for a period and block other messages. Thus circuit switching is only good for long and infrequent messages.

As an alternative to circuit switching, a message can be partitioned and transmitted as fixed-length packets by packet switching. Packets are individually routed from source to destination. A packet is stored at each intermediate node then forward to next node. Packet switching is good for short and frequent messages [2]. However, unlike in circuit switching where a physical path is reserved for the whole message, each packet of a message has to be routed at each intermediate node. Moreover, splitting a message into packets also makes overhead.

As the applications of the systems spread into more compute-intensive areas, the traditional designs borrowed from LANs become a limiting performance bottleneck. Some new

10

switching techniques, such as virtual cut-through switching (VCT) and wormhole switching, are evolved to practical use.

In packet switching, a packet must be received in the whole at an intermediate node before making a routing decision and forwarding to the destination. However the header of a packet usually arrives to an intermediate node earlier than the tail of a packet by multiple cycles. This is because of the message length and available bandwidth. Thus even a node already knows the needed information to make a routing decision after receiving the header of a message; it still cannot forward the received part of the message to destination. To overcome this drawback, virtual cut-through switching is proposed to forward package immediately after routing decision is made. In absence of blocking, message can be cut through to input port of next node without buffering and the package transmission is pipelined through successive switches. In case a header is blocked at a busy output port, the whole message will be received and buffered at this node.

The requirement to buffer entire packets at a node makes it difficult to build compact and fast routers by using VCT switching technique. To construct small router which resides in an on-chip component, wormhole switching is used.

Wormhole switching has been widely used in practical multi-computer and network on chip where small and faster router is needed [31]. In wormhole switching, message packets are broken up into flits for message transmission flow control. Header flit contains routing information, once a header is received at intermediate node, the routing decision is made and the header is forwarded to next node in absence of blocking. The remaining data flits just follow the route that is determined by the header.

11

Input or output buffers of a wormhole router only need to be able to store a few flits. For example, message buffer in the Cray T3D are 1 flit deep [2]. The flits are pipelined through the network in a similar manner as VCT in absence of blocking. Because a message is typically too large to be completely stored in a router, in case the required output port is busy, all the flits of the message are stored in situ which implies that a block message occupies buffers in several routers along the path.

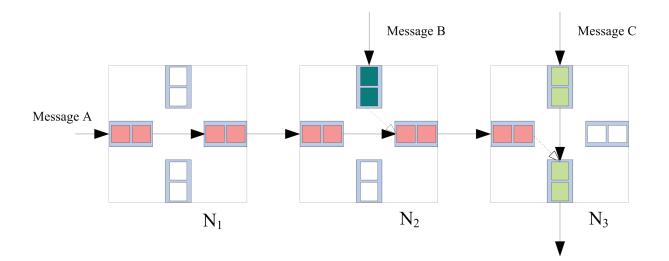

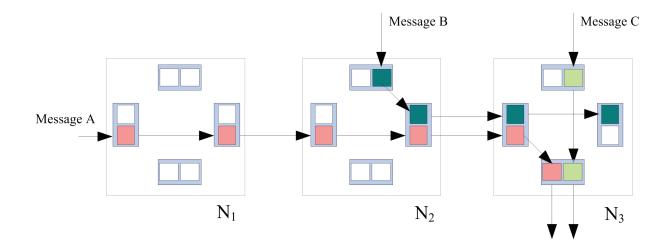

An example of a blocked message in wormhole switching network is shown in Fig 2.2 where message A is blocked because message C has occupied south port of node 3 and message B is blocked due to message A's occupancy of west port at node 2. Furthermore, Fig 2 shows that the flits of blocked message A are stored in situ.

This research work is focusing on wormhole switching network.

Figure 2.2: Blocked message in a wormhole network

### 2.3 Virtual Channel

The simple wormhole switching introduced in previous section has a drawback that different messages cannot be interleaved or multiplexed over a physical channel. Once a message starts to be transferred on a channel, this channel will be occupied till the entire message crossing it. During this time period, the occupied channel can not be used by other messages. Virtual channel [2] mechanism is introduced to increase channel utilization.

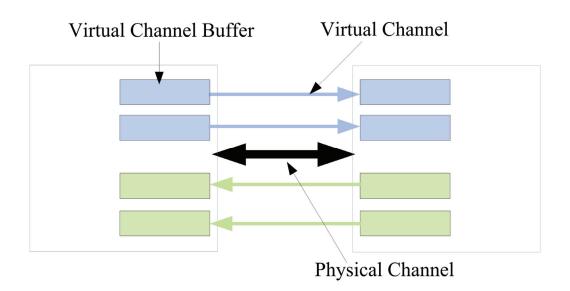

Multiple virtual channels can multiplex a physical channel. They are implemented by an independently managed pair of buffers at two adjacent nodes as illustrated in Fig 2.3 where we can see two unidirectional virtual channels multiplex one direction of the physical channel. Logically each virtual channel in Fig 2.3 operates as if a distinct physical channel which operates at half the original bandwidth.

Figure 2.3: Virtual channels multiplexing a physical channel

Virtual channel can be used to improve message latency and network throughput; however it was first introduced to solve the problem of deadlock in wormhole switching network. [2] As shown in Fig 2.4, message A and message B that are blocked in Fig 2.2 can now advance to their next hop node with the help of virtual channel.

Using virtual channels may improve network performance by reducing blocking probability. However the increased channel multiplexing reduces the data transfer rate of messages, thus increases message latency. Therefore, the increase of message latency may eventually overshadow the improvement brought by virtual channels [2]. Moreover, virtual channels also introduce overhead in hardware support for this mechanism. Additional hardware blocks need to be used to make arbitration between multiple virtual channels and allocate buffer space among the virtual channels. Thus, when using virtual channels for a switch, these tradeoffs need to be taken into considerations.

Figure 2.4: Use virtual channel to reduce blocking.

### 2.4 Buffer Schemes

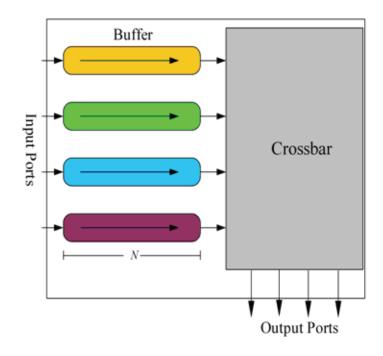

The switch buffers can be associated with input or output ports. Because buffering packets at the input ports can reduce hardware complexity [3], it is preferred over output ports buffering designs [37].

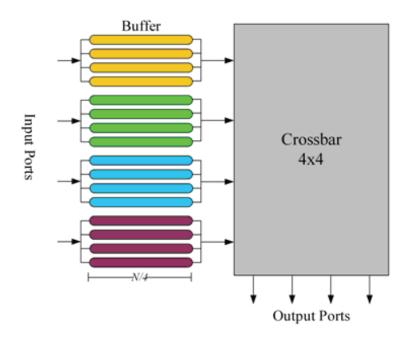

Input buffering schemes can be divided into four categories, namely FIFO (First in First out), SAFC (Statically Allocated Fully Connected), SAMQ (Statically Allocated Multi-Queue), and DAMQ (Dynamically Allocated Multi-Queue). They are illustrated in Fig 2.5.

Among these designs, DAMQ efficiently utilized buffer space by dynamically allocating buffer to incoming flits. It has been proved to be a better scheme than others. [3] Following is the DAMQ buffer schemes reported in the literatures.

#### 2.4.1 Linked list buffer scheme

In order to let multiple queues of packets share a DAMQ buffer, linked lists can be used to implement the buffer scheme [37] [39] [40]. The basic idea of this approach is to maintain (k+1) linked lists in each buffer: one list of packets for each one of the (k-1) output ports, one list of packets for the end node interface and one list of free buffer blocks. Corresponding to each linked list there is a head register and a tail register. The head register points to the first block in the queue and the tail register points to the last block. In each output queue, next block information also must be stored in each buffer block to maintain the FIFO ordering.

(a) First in First out (FIFO)

(B) Statically Allocated Fully Connected (SAFC)

(c) Statically Allocated Multi-Queue (SAMQ)

(d) Dynamically Allocated Multi-Queue (DAMQ)

Figure 2.5: Input buffer schemes.

### 2.4.2 Self-compacting buffer scheme.

To reduce the hardware complexity of the linked list scheme, an efficient DAMQ buffer design self-compacting buffer (SCB) was proposed by [40] [41]. The idea for this buffer scheme is to divide the buffer dynamically into regions with every region containing the data associated with a single output channel. If two channels are denoted as *i*, *j* with i < j, then the addresses of buffer regions for the two channels  $A_i A_j$  will be  $A_i < A_j$ . There is no reserved space dedicated for any channel. Data is stored in a FIFO manner within the region for each channel. When an insertion of the packet requires space in the middle of the buffer, the required space will be created by moving down all the data which reside below the insertion address. Similarly, when a reading operation conducted from the top of a region, data removed from the buffer may result in empty space in the middle of the buffer, then the data below the read address is shifted up to fill the empty space. Our new buffer schemes are based on the SCB scheme.

#### 2.5 Routing algorithms and analytical models

Routing algorithms are used to specify the path from source to destination for each message. They can be implemented in two ways which are either deterministic or adaptive.

#### 2.5.1 Deterministic routing protocols

Deterministic routing protocol chooses the path for a message only by its source and destination. All packets with the same source and destination pair will follow one single path. The packet will be delayed if any channel along this path is loaded with heavy traffic, and if a channel along this path is faulty the packet cannot be delivered. Thus the deterministic routing protocols are prone to suffer from poor use of bandwidth, blocking when alternative paths are available. They are particularly susceptible to component failures. [16] A common deterministic

18

routing algorithm is dimension-order routing [22], in which the packet is routed in one dimension at a time, arriving at the proper coordinate in each dimension before proceeding to the next dimension. We use a dimension-order routing protocol E-Cube to conduct our simulation for two new buffer schemes.

Deterministic routing has been widely used in multi-computers due to its simplicity. [32] [33] [34] and its analytical model has been widely reported in the literature [3] [6] [7] [9] [10] [11] [35].

#### 2.5.2 Adaptive routing protocols

Adaptive routing protocols are proposed to make more efficient use of bandwidth and to improve fault tolerance of interconnection network. In order to achieve this, adaptive routing protocols provide alternative paths for communicating nodes. Thus it can overcome the congested areas in the network. Several adaptive routing algorithms have been proposed, showing that message blocking can be considerably reduced, thus strongly improving throughput.[23] Among them, routing algorithms based on Duato's design methodology [16] are very popular. These routing algorithms split each physical channel into two virtual channel sets, the adaptive and the deterministic channels. When the paths of adaptive channels are blocked, a message uses an escape channel at the congested node. If there is any free adaptive channel available at subsequent nodes, the message can go back to the adaptive channels. Adaptive routing algorithms can be further categorized to progressive and backtracking algorithms. Progressive routing algorithms move the message header forward by reserving a new channel. Backtracking algorithms needs more complex hardware support [2] because they allow the message header to be routed backtrack releasing previously reserved channels. In our model, we assume the routing algorithm is progressive, no backtracking is allowed.

19

Two analytical models for wormhole switching network using fully adaptive routing protocols are reported in the literature [4] [5]. Y.Boura et al. proposed an analytical model for adaptive routing Hypercube in [4]. In Hypercube network a message traverses at most one channel along a dimension. Due to this topology nature, at an intermediate node, the number of remaining hops for a message to arrive at destination is known in Hypercube. However, *k*-ary *n*-cubes do not have this property. Thus, at a given intermediate node the number of remaining hops that remains on current dimension is not clear. M. Khaoua proposed a model for Duato's fully adaptive routing algorithm in k-ary n-cubes in [5]. Its key idea was to compute the blocking probability at a given node by deriving the blocking probability of the two virtual channel groups in Duato's algorithm i.e. adaptive and deterministic virtual channels groups respectively.

In this dissertation we present a novel performance analysis model for *k*-ary *n*-cubes network on chip with wormhole routing and fully adaptive routing. We use a 2D torus network as the analysis example to compute the average message latency using our new model. The model is based on general queuing theory and probability analysis. The blocking probability for a message at a given channel is derived by the arrival traffic rate and the service rate the message receives. It's simple and yields satisfactory predictions in the network's steady state region.

# **Chapter 3**

# **Analytical Model for Wormhole Switching NoC**

This chapter presents a novel analytical model for easily predicting average message latency of traffics in a network on chip where wormhole switching and fully adaptive routing protocols is used. The model has simple close-form calculations and produces very accurate results in the network stable regions. To validate this model a comparison between analytical prediction and simulation results is performed on high-radix *k*-ary 2-cube networks.

### 3.1 Network Configuration

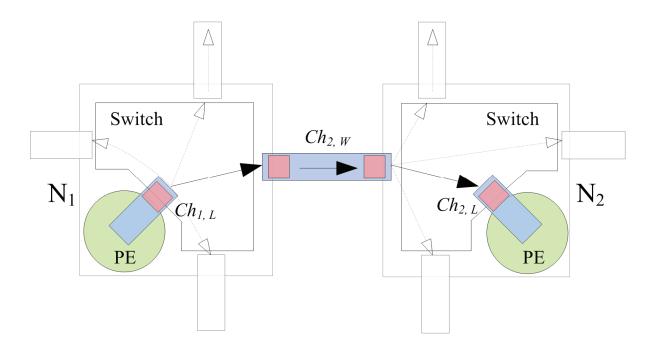

We use a 2*D* torus network as our analysis target to illustrate the model for simplicity. Fig. 3.1 shows an 8-ary 2-cube (torus) message exchanging network. Each node consists of a processing element (PE) and a switch. PE is responsible for generating message and consuming message from other nodes. Each switch has 5 input and output channels. PE is connected to switch by the local injection/ejection channel. A node is connected to 4 adjacent neighbouring nodes by bi-directional network channels.

As introduced in chapter 2, virtual channels multiplexing one direction of a duplex physical channel are used in network on chip to enhance throughput and avoid deadlock. Due to the

nature of limited hardware resource and to facilitate our model calculation, we assume the buffer size for each end of a virtual channel is 1 flit deep.

Figure 3.1: 64 nodes torus message exchanging system

A message which is generated from a nodes PE will first be transmitted to the switch by local injection channel. Then, this message will be routed toward its destination. At the destination node, the message is transmitted to PE through local ejection channel. Thus a message has to travel through at least 3 links from the source to destination. For instance, as shown in Fig. 3.2, the message generated in node  $N_I$  has to traverse channels  $Ch_{1,L}$ ,  $Ch_{2,W}$  and  $Ch_{2,L}$  to arrive at its destination PE in  $N_2$ .

Figure 3.2: Switch to switch path

### **3.2.** Pertinent Assumptions

For this model the following assumptions have been made; these assumptions are commonly accepted in the literature [2-13].

1) Independent traffic generation. Each node generates traffic independently with the traffic following a Poisson process on a mean rate of  $M_{gen}$  messages per cycle.

*2)* Uniform distribution of destinations. Message destinations are uniformly distributed across the network nodes. Although for an actual application, if node *A* sends a message to node *B* it's highly possible that *B* will send back a message to *A*.

*3) Messages of constant length L flits.* A message is long enough so that its data flits span from source to destination nodes. Moreover, the message lengths can be designated according to any probability distribution where expectation and variance of message lengths are known.

4) One clock cycle transmission between adjacent nodes. Each flit requires one cycle to be

transmitted from one node to the next over the physical link between them. Two cycles are needed for a flit to cross a node, i.e. from an input buffer to an output port, in absence of blocking.

5) Infinite capacity in local injection queue. The local queue at the injection channel in the source node has infinite capacity. Messages at the destination node are transferred to the local PE one flit at a time through the ejection channel.

6) Duplex physical channels between any two adjacent nodes. More than two virtual channels are used for each direction of a physical channel. In Duato's algorithms [15] [16], if there are adaptive virtual channels available, a message can use a random one; for the deterministic virtual channels, although there are two of them, a message uses only one at a time. Therefore we adopt the same strategy as described in [4] to make no distinction between the deterministic and adaptive virtual channels when computing the different virtual channels occupancy probabilities. This simplification also reflects the idea of fully adaptive routing.

### **3.3 Notations**

There are a number of notations involved in this model. We list all of them into Table 3.1 to facilitate the name look up.

Table 3.1. The Parameter Notations

| Parameter            | Description                                                                                               |

|----------------------|-----------------------------------------------------------------------------------------------------------|

| Mgen                 | Average message generation rate at each node                                                              |

| $T_{msg}$            | The mean latency for all the delivered messages                                                           |

| $T_s$                | Routing (Switching) delay across a node                                                                   |

| $T_w$                | Propagation delay across the physical channel                                                             |

| L                    | Average message length(not including header)                                                              |

| D                    | Average path length for all the delivered messages                                                        |

| $N_q$                | Average number of intermediate nodes along the path                                                       |

| $W_q$                | Average waiting time for a message at each intermediate nodes along<br>the message's routing path         |

| $W_{ej}$             | Average waiting time for a message on ejection node channel                                               |

| λ                    | The average message arrival rate at a channel                                                             |

| μ                    | The service rate for a message at a physical channel                                                      |

| S                    | The service time for a message at a channel without contention.                                           |

| SR                   | The service rate for a message at a channel without contention                                            |

| $W_{eq}$             | Average waiting time for a message on last node of the routing path.                                      |

| $\mu_r^{dir}$        | The service rate that a channel observes from the immediate downstream channel on <i>dir</i> direction.   |

| $\mu_r$              | The service rate that a channel observes from all its immediate downstream channels at nodes on the path. |

| $\mu_{rE}$           | The service rate that a channel observes from all its immediate downstream channels at destination node.  |

| P'Q                  | The blocking probability for a message at a physical channel without contention.                          |

| $P_O$                | The blocking probability for a message at a physical channel                                              |

| v                    | The virtual channel number of each direction of a physical channel                                        |

| 0                    | In/output ports number of a node (not including local channel port), in our network, it's 4.              |

| dir                  | Direction. Each nodes has ports on 5 directions, <i>i.e.</i> East, South, West, North and Local           |

| Ch <sub>n, dir</sub> | Physical channel in <i>dir</i> direction of a message's <i>n</i> th hop node.                             |

### **3.4 Calculation of Average Message Latency**

Average message latency is a key metric to evaluate a network's performance. It's defined

as the time elapsed since the message transmission is initiated until the message is received at the

destination node [2]. In the following, we present how to calculate the average message latency. First we present the notations used in the computing process, and then we describe the calculation process.

The average message latency  $T_{msg}$  comprises of the message transmission delay across the network channel  $t_w$ , the intrarouter delay  $t_s$ , [2] the average contention delay  $W_q$  at the network channels and the average delay  $W_{ej}$  at nodes' local ejection channel. It can be computed as follows:

$$T_{msg} = \left(N_{q} - 1\right) \cdot W_{q} + W_{eq} + D \cdot T_{r} + L \cdot T_{r} + W_{ej}$$

$$\tag{1}$$

Where  $T_{tr}$  is given by  $\max(t_s, t_w)$ . It demonstrates the nature of pipelined flits transmission of wormhole switching in absence of contention.  $DT_{tr}$  denotes the mean time that a message's header flit needs to travel from source to destination and  $LT_{tr}$  denotes the travel time for the data payload of a message.  $(N_q - I)W_q$  shows the waiting time that header flit experienced at the  $N_q - I$ channels of intermediate nodes. Queuing system at the destination node of a messages routing path,  $W_{eq}$ , is separated from other queues on previous nodes because of the different service rate offered by last node. We will discuss the detail later. As the minimum link number that a message travels is 3, the average hops that messages take, D, can be obtained by:

$$D = \sum_{i=3}^{k} p_i \cdot i \tag{2}$$

Where *k* is the diameter of the network, and  $p_i$  denotes the probability that a message's travel path is *i* links long. Another simple and commonly used estimation of *D* is:

$$D = \frac{k+3}{2} \tag{3}$$

However, in a low radix network, Eq. (3) is prone to produce error. For example, D of the 4 nodes Torus network is 3.33, while Eq. (3) yields 3.5 in this case.

Under the uniform traffic pattern, the average traffic arrival rate  $\lambda$  for each channel is determined by the message generating rate  $M_{gen}$ , average routing hops D and output channels number of each node o [4].

$$\lambda = \frac{M_{gen} \cdot D}{4} \tag{4}$$

In order to receive service from a link, the message's header flit needs to acquire a virtual channel. Once a virtual channel is assigned to a message, it keeps serving this message and will not be released until all the data flits flow across this node. Because each virtual channel has one flit depth buffer, once it is assigned to a message, no other message can use the same virtual channel till it's free again. When the traffic rate is light, there is no congestion; the service time at each channel can be defined as:

$$S = t_s \cdot (L+1) \tag{5}$$

And the service rate can be derived accordingly:

$$SR = \frac{1}{S} \tag{6}$$

When traffic rate is high enough, congestion appears in the network and waiting queues build up at corresponding bottleneck links. In this case, the service that one channel can provide to the incoming messages is not only determined by its own service capacity, but also by the blocking state of its immediate downstream channels.

In our network, the traffic arrival rates for the four input channel of a node are equal to each other because of the following reasons:

- 1. Torus network with wrap around links is a strictly symmetric topology.

- 2. Every node is identical in terms of capacity of generating and consuming message.

- 3. Traffic is generated randomly from all the nodes.

- 4. The routing protocol is fully adaptive algorithm.

- 5. The input channels all have equal service capacity.

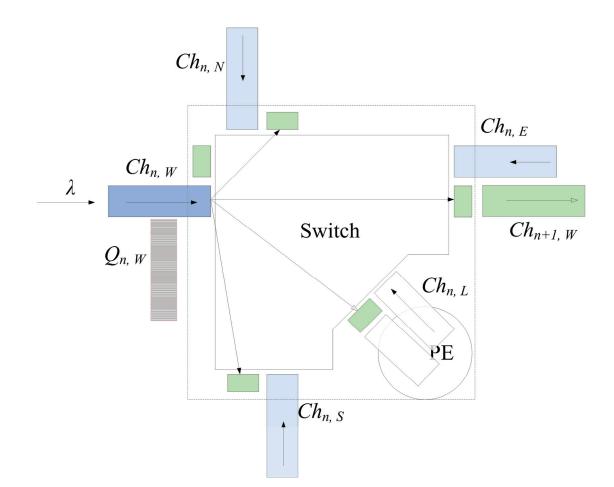

So we can treat the queuing systems at each of these channels as identical. Without loss of generality, suppose the node that we analyze is at *n*th hop of a messages routing path. We derive the queuing system model of the channel  $Ch_{n,W}$  on the west input port as shown in Fig. 1.

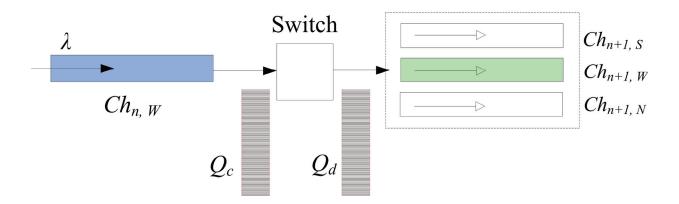

We follow the suggestion in [11] to treat the waiting queue  $Q_{n,W}$  at channel  $Ch_{n,W}$  as two distinct queues  $Q_c$  and  $Q_d$ . As shown in Fig. 5,  $Q_c$  is result from the delay involved in router (switch) service delay observed by  $Ch_{n,w}$ , while  $Q_d$  is due to the contention that a message may experience when it's to be accepted by a downstream input channels.

Figure 3.3: Queuing model for an input channel

$Q_c$  is determined by the traffic arrival rate  $\lambda$  and the router self's service rate *SR*. To model it, we use an *M/M/m* queuing system. The first two "*M*"s stands for the Poisson distribution traffic arrival process and the exponential distributed service time respectively. The third "*m*" means there are *m* servers and a message at the head of the queue is routed to any server that is available. Accordingly we have *v* virtual channels per physical link in our network configuration, which are treated as the *v* servers in the queuing model.

The probability that an arrival message will find all virtual channels are busy and will be forced to wait in queue can be obtained by [1]:

$$P_{\mathcal{Q}}^{'} = \frac{p_0 \cdot (\nu \cdot \rho)^{\nu}}{\nu! \cdot (1 - \rho)} \tag{7}$$

Where  $p_0$  is given by:

$$p_{0} = \left(\sum_{n=0}^{\nu-1} \frac{(\nu \cdot \rho)^{n}}{n!} + \frac{(\nu \cdot \rho)^{\nu}}{\nu! \cdot (1-\rho)}\right)^{-1}$$

(8)

And  $\rho$  is given by:

$$\rho = \frac{\lambda}{v \cdot SR}$$

For the second queue  $Q_d$ , the traffic arrival rate is still  $\lambda$ , and the service rate,  $\mu_r$ , is the service rate that offered by all the immediate downstream channels to  $Ch_{n,w}$ . However  $\mu_r$  at destination node is different from those at intermediate nodes along the path. This is because at destination, the message is bound to be delivered into local ejection channel, thus other three possible immediate downstream channels cannot contribute service to  $\mu_{rE}$  in this case. Correspondingly, at other nodes along the path, local ejection channel won't offer service to a message. We first show how to compute  $\mu_r$  at intermediate nodes and use it to get the average waiting time for a message at these nodes when contention is taken into consideration. After that, we'll show the calculation for  $\mu_{rE}$  and the corresponding waiting time at the destination node.

Figure 3.4: Reduced queuing model for an input channel

To obtain  $\mu_r$  at intermediate nodes, we can further divide  $Q_d$  to three queues, each of which is associated with an immediate downstream channel in one of the three possible downstream directions, *i.e.* east, south and north in this case. Note, the routing algorithm that we assume in the model is progressive algorithm, so we don't treat the backtracking channel as an immediate downstream channel. However, if the model needs to be used to model a backtracking routing algorithm, then service from one more possible downstream channel (*Ch<sub>n-1,E</sub>* in this case) in the reverse direction can be easily added in.

As we mentioned before, the traffic arrival rates for the three queues on each direction of next hop are equal to each other. Moreover, these downstream network channels have same service capacity, so we can get the analysis results for all these queues by analyzing any one of them. Without loss of generality, let's consider the waiting queue residing at the west downstream channel  $Ch_{n+1,W}$ . The channel can accept a new message when it has free virtual channel available, while no messages can be accepted when all the virtual channels are occupied. Furthermore,  $Ch_{n+1,W}$ 's service capability, *i.e.* the number of flits that can be processed within a unit time (clock cycle) is fixed, so with more traffic generated in the network, the probability of

one message to be served is less; in another word, the waiting time for this message is longer. Since we can get the average waiting time for a message by: [1]

$$W_{q_d} = \frac{P_Q \cdot \rho}{\lambda \cdot (1 - \rho)} \tag{9}$$

Then the average time that a message spends at the queuing system of  $Ch_{n+1,W}$  is  $W_{qd} + S$ . In addition, there are *v* virtual channels in  $Ch_{n+1,W}$  and  $Ch_{n+1,W}$  has *o* possible inputs(including local injection channel), therefore we can get  $\mu_r^w$  as :

$$\mu_r^w = \frac{v}{o \cdot \left(S + W_{qd}\right)} \tag{10}$$

Hence, we get  $\mu_r$  as:

$$\mu_{r} = p_{w}\mu_{r}^{w} + p_{s}\mu_{r}^{s} + p_{N}\mu_{r}^{N}$$

(11)

Because of the symmetry of our network, we know that  $p_w = p_s = p_N$ , therefore  $\mu_r = 3 \mu_r^w$ . For networks with different topology or traffic pattern, we can get  $\mu_r$  by deriving the probabilities of the traffic flows to downstream links on different direction. Using Little's Theorem, the average number of messages in the whole queuing system at  $Ch_{n,W}$  can be derived as:

$$N = \lambda \cdot T = \frac{\lambda}{\mu} + \frac{\lambda \cdot P_{\varrho}}{v \cdot \mu - \lambda}$$

(12)

Note that  $\mu$  in Eq. (12) is the overall service rate that  $Ch_{n,W}$  provides to its incoming traffic. It takes into consideration of both with and without contention cases on downstream channels. Also by Little's Theorem, the average number of messages in  $Q_d$  is:

$$N_d = \frac{\lambda}{\mu_r - \lambda} \tag{13}$$

And the average number of messages in  $Q_c$  is:

$$N_c = \frac{\lambda}{SR} + \frac{\lambda \cdot P_{\varrho}}{v \cdot SR - \lambda}$$

(14)

As  $Q_{n, E}$  comprises of  $Q_c$  and  $Q_d$ , combine Eq. (12), (13) and (14), we get:

$$\frac{\lambda}{\mu} + \frac{\lambda \cdot P_{\varrho}}{\nu \cdot \mu - \lambda} = \frac{\lambda}{SR} + \frac{\lambda \cdot P_{\varrho}}{\nu \cdot SR - \lambda} + \frac{\lambda}{\mu_r - \lambda}$$

(15)

From Eq. (7) and (8), we already knew that  $P_Q$  in Eq. (15) can be expressed in terms of  $\lambda$  and  $\mu$ :

$$P_{\varrho} = \frac{\left(\sum_{n=0}^{\nu-1} \frac{\left(\nu \cdot \rho\right)^n}{n!} + \frac{\left(\nu \cdot \rho\right)^{\nu}}{\nu! \left(1 - \rho\right)}\right)^{-1} \cdot \left(\nu \cdot \rho\right)^{\nu}}{\nu! \left(1 - \rho\right)}$$

(16)

Where  $\rho$  is given by:

$$\rho = \frac{\lambda}{v \cdot \mu}$$

Replace  $P_Q$  in Eq. (15) using Eq. (16), solve the nonlinear equation, we can get the service rate  $\mu$  at channel  $Ch_{n,W}$ .

Then, by Little's Theorem again, we can obtain the average time  $W_q$  that a message has to wait in queuing system at the intermediate nodes of a message's traveling path:

$$W_q = \frac{P_{\varrho} \cdot \rho}{\lambda \cdot (1 - \rho)} \tag{17}$$

At the destination node, say  $N_{des}$ ,  $\mu_{rE}$  is solely determined by the local ejection channel.

But we cannot apply Eq. 9 and 10 directly, because there may be more than one message choose  $N_{des}$  as its destination node which implies that local ejection channel has a different arrival traffic rate than network channels. We can derive the message arrival rate from other sources by:

$$\lambda' = \sum_{i=1}^{o-1} \lambda \cdot (n-i)^i \tag{18}$$

Where *n* is the total nodes number of the network. Since the node's local ejection channel doesn't have any downstream channel dependency; we treat it as an independent *M/M/m* queuing system, where "*m*" also equals to virtual channel number *v*. Thus we can use Eq. (8) to calculate the average waiting time for a message,  $W_{qde}$ , in absence of contention by replacing  $\lambda$  to  $\lambda + \lambda'$ . So we obtain  $\mu_{rE}$  as:

$$\mu_{rE} = \frac{v}{S + W_{qde}} \cdot \frac{\lambda}{\lambda + \lambda'}$$

(19)

Repeating the computing process expressed in Eq. 12, 13, 14, 15, 16, 18, by providing the  $\rho$  for this case:

$$\rho = \frac{\lambda + \lambda'}{v \cdot \mu}$$

We can obtain the waiting time at the input channel of destination node,  $W_{eq}$ .

Finally, as we mentioned that the nodes local ejection channel is treated as independent M/M/m queuing system; the average waiting time on ejection node channel can be obtained by:

$$W_{ej} = \frac{P_{Q_{ej}} \cdot \rho_{ej}}{\left(\lambda + \lambda'\right) \cdot \left(1 - \rho_{ej}\right)}$$

(20)

Where  $P_{Q_{ei}}$  can be obtained by Eq. (16) with

$$\rho_{ej} = \frac{\lambda + \lambda'}{v \cdot SR} \tag{21}$$

At this point, the message delay  $T_{msg}$  defined in Eq. (1) can be easily calculated out as all the unknown variables at the right hand side of the equation are all obtained now.

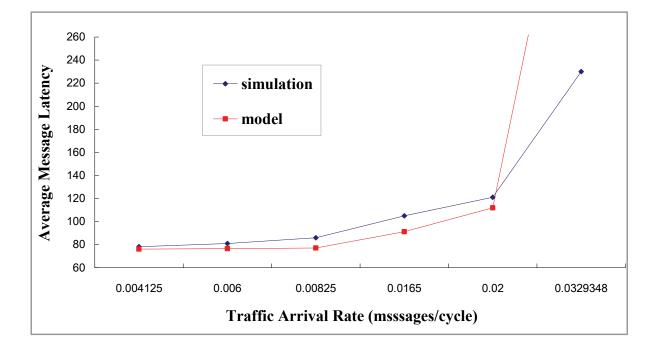

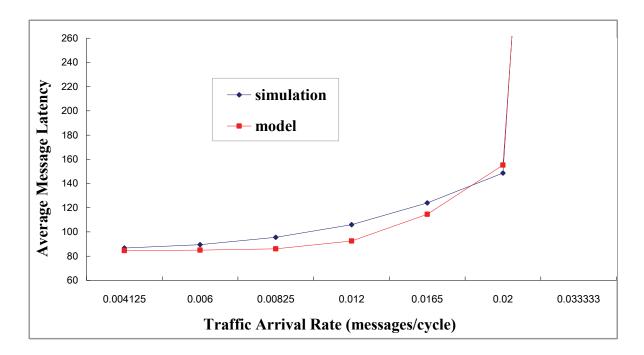

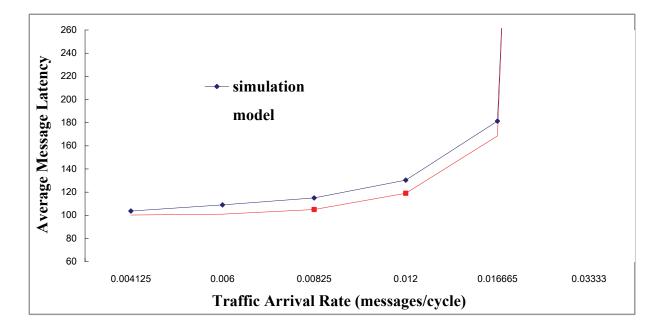

#### 3.5 Validation

We carried out a number of simulations to validate the proposed model. The simulator we used is flexsim1.2 [18] [20], which is a flit level simulator for Torus/Mesh network adopting wormhole switching. In flexsim1.2, when uniformly distributed traffic is used in simulations, the source of a message is equally randomly picked among nodes in the network. Thus we can treat the traffic that arrives at a given channel follow Poisson distribution. Parameters of the simulated network are set to conform to the assumptions described in section 3. Validation experiments are carried out on many different combinations of network size, message length and virtual channel number per physical channel. In order to facilitate the illustration of our model's validity, the messages' data payload is set to 32 flits and the number of virtual channels per physical channel is set to 4. All the simulation results are obtained from simulations running for over 1 million cycles simulating time to rule out exceptional results. In the follows, we present average message latency results obtained from both model and simulations on three different size networks, 64, 256 and 1024 nodes two dimensional Torus network. Figures 3.5, 3.6 and 3.7 demonstrate average message latency results predicted by the model against those obtained from the

simulations. These results are obtained from 8-ary 2-cube, 16-ary 2-cube and 32-ary 2-cube networks respectively. The figures reveal that simulation results and predictions of our model match well from a very light usage of a network channel to about 50% average utilization, after which point discrepancies are apparent as the network gets into saturation state.

Figure 3.5: Comparison of Model against simulation in 64 nodes torus network

Figure 3.6: Comparison of Model against simulation in 256 nodes torus network

Figure 3.7: Comparison of Model against simulation in 1024 nodes torus network

### **3.6 Apply model to multiple flit buffer**

We have presented the detailed calculation process to use the proposed analytical model predicting performance of a *k*-ary 2-cube network in section 3.4. In section 3.5 a comparison with simulation results is shown. In that calculation process, to make it simpler to illustrate the core idea of the model we assume the buffer size at each virtual channel end is 1 flit deep. Although there are machines that implement 1 flit buffer, it is also possible to have larger virtual channel buffers. In this section we introduce an approach to apply our model to Statically Allocated Multi-Queue (SAMQ) buffers which are more than 1 flit deep.

The following are notations that are needed in this extension of the model:

- 1. Buf: Buffer Size of each virtual channel

- 2.  $D_{sm}$ : Number of nodes needed to store message in virtual channel buffer when message is blocked. It is obtained by *L/Buf* where L is message length

- 3.  $D_i$ : Distance between *i*th intermediate node to destination node.

Due to the pipelined transmission nature of wormhole switching, if there is no congestion in the network, then buffer size has no impact on flowing message because all the flits are cut through to next hop channel without storing in current node's channel buffer.

In case the message is blocked in an intermediate node's channel, all the flits will be stored in the intermediate node buffers. Thus, if there is more buffer space available at each intermediate node's channel, then more flits can be stored in these channels. Therefore, for a channel that are near the source node, its  $D_{sm}$  may be smaller than its  $D_i$ . In contrast, if each virtual channel has 1 flit buffer, then  $D_{sm}$  is equal to  $D_i$ . This is to say that the channels near the source node side may be freed right after transmitting flits and the possible congestions of message M in subsequent nodes have no impacts to this channel after it finishes transmitting all the flits of M. This is because all the flit can be stored in  $D_{sm}$  virtual channels that precede the congested node.

In wormhole switching, once a virtual channel is assigned to a message, this virtual channel cannot be used for other messages no matter what's the size of the virtual channel buffer. Therefore, although more buffer space means more data flits can be stored in the channel buffer, the service rate that a channel can provide to the incoming traffic still remains same. In another words, using the notations of analysis in section 3.4, the service rate of a physical channel is still determined by the *v* servers that are the virtual channels multiplexing it. Therefore we can use the average waiting time for a message at each intermediate node,  $W_q$ , which is obtained in section 3.4 to estimate the message waiting time in the multiple flit buffer case.

Using the notations in section 3.4, for multiple flit buffer virtual channels, we can obtain the average time that one virtual channel may be occupied by a flowing message M as:

$$(L+1) \cdot T_{tr} + \min(D_{sm}, D_i) \cdot W_q \tag{1}$$

where  $(L+1)T_{tr}$  denotes the time that this channel spends to transfer the header and data payload flits of a message *M* and min $(D_{sm}, D_i)W_q$  shows the time span that flits of *M* stay in this virtual channels buffer. As mentioned earlier, we know that if 1 flit buffer is used, then  $D_{sm} = D_i$ , therefore, the average time that one virtual channel may be occupied by a flowing message *M* in this case is:

$$(L+1) \cdot T_{tr} + D_i \cdot W_a \tag{2}$$

Subtract (1) from (2), we get difference between the time that a flowing through message spent in a 1 flit buffer channel and the time it spent in multiple flit buffer channel:

$$(D_i - \min(D_{sm}, D_i)) \cdot W_q \tag{3}$$

Using equation (2) and (3), together with the parameters of a analysis target network, we can obtain the percentage of the average time reduction of message M staying in a virtual channel, which in turn can be used to estimate the improvement in terms of the physical channel service rate. Then we can apply the model presented in section 3.4 to predict the performance of networks with multiple flit virtual channel buffer.

As to apply the model to predict network with Dynamically Allocated Multi-Queue buffer, we need to analyze the pattern of how the buffer space is partitioned among the competing virtual channels. It is more complex than the previously mentioned SAMQ case. However it would be a very good topic for future extension of this research.

### **3.7 Conclusion**

We have presented an analytical model for predicting network performance in this chapter. This model can be applied to wormhole switching network to predict network performance measures, such as average message latency and average link waiting time in a torus network using fully adaptive routing algorithms such as Duato's method. Unlike previously proposed models, this model is based on general queuing theory and probability analysis. It's simple and yields rather accurate predictions in network's steady state region. Compared with the model [5] in the literature for wormhole switching *k*-ary *n*-cubes network with adaptive routing, our model computes the blocking probability using message arrival rate and service rate provided by network channels and can predict network performance accurately from very light traffic load to the saturation point where about 0.2 messages are received/sent at each network node per cycle. While the model proposed in [5] conducted the calculation based on virtual

channel groups in Duato's routing algorithm and predicted network performance in the traffic load region from 0 to about 0.002 messages per node per cycle.

By applying close-form calculations of this model, we can correctly predict high-radix *k*ary *n*-cubes in steady state regions with a short code snippet. It can be concluded that our model provides an effective and practical evaluation tool. In addition, since this model obtains message waiting time at each queuing system at channels of a routing path, it can be easily adapted for networks with other topologies. For instance, mesh network. The only required information is message arrival rate and service rate at the related channels. These two measures can be computed based on the specific network topology property and routing algorithm.

## **Chapter 4**

# **High Performance DAMQ Buffer Schemes**

In this chapter three novel DAMQ buffer schemes based on self compacting buffer (SCB) are presented. These schemes are proposed to let traffic flow make an efficient use of input buffer that resides in each communicating node. For each of the three schemes, we first describe their organization; then present the simulation results and some concluding remarks.

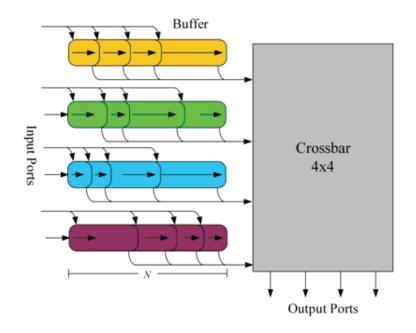

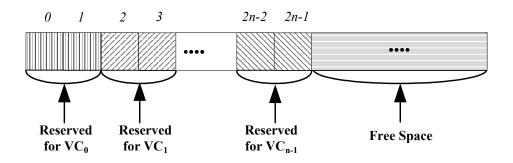

### 4.1 DAMQ with Reserved Space for All Virtual Channels

DAMQ dynamically allocate buffer blocks according to the packet received. Compared with statically allocated buffer scheme, the advantage of DAMQ is that it uses efficiently the buffer space by applying free space to any incoming packet regardless its destination output port. Since there is no reserved space dedicated for each output channel, the packets destined to one specific output port may occupy the whole buffer space thus the packets destined to other output ports have no chance to get into the buffer. This is the case especially for small and compact routers with limited buffer space where wormhole switching technique and virtual channel mechanism are commonly used. A unidirectional virtual channel is implemented by an independently managed pair of buffers at two adjacent nodes.

Figure 4.1: DAMQ<sub>all</sub> Buffer space at the initial state

When several virtual channels multiplex across the physical channel and share a common buffer, the virtual channels which have packets accepted in the buffer prior to other virtual channels may hold the whole buffer space when the output port to next hop node that it destines to is busy. In order to overcome this shortcoming of DAMQ buffer schemes, we implement a new buffer organization scheme, DAMQ with reserved space for all virtual channels (DAMQ<sub>all</sub>). DAMQ<sub>all</sub> is based on the self-compacting buffer (SCB) scheme. It inherits most features of the SCB. Similarly, the virtual channels multiplexing one direction of a physical channel share a buffer. The new feature is that there is reserved space dedicated for each virtual channel, therefore at any time there is free space for the packets of "late" virtual channels which has not received packet and one virtual channel can never consume the whole buffer. As shown in Figure 4.1, two buffer slots are reserved for each virtual channel before the buffer accepts any incoming flit. The reserved spaces for each virtual channel are arranged sequentially according to the sequence numbers of the virtual channels.

Figure 4.2: DAMQall Buffer space status in operations

One register is used to point to the head of each reserved space, i.e. the head of the buffer region for each virtual channel. If two channels are denoted as  $V_{i}$ ,  $V_{j}$  with i + 1 = j, then the reserved region for  $V_{j}$  will be placed right after the reserved region for  $V_{i}$ .

The size of reserved space for each virtual channel can be adjusted, however, we have chooses two flits because, according to our simulation experiments statistics, two reserved flits scheme yields satisfactory performance while keeps more free space for sharing. When there is an incoming flit to the buffer, the DAMQ<sub>*all*</sub> operates as shown in Figure 4.3. When a flit is leaving the buffer, the DAMQ<sub>*all*</sub> operates as illustrated in Figure 4.4:

. Also as shown in Figure 4.2, the reserved space for each virtual channel is always kept if there is no flit or only one flit in the buffer region for a specific virtual channel.

```

if (first flit for current VC){

```

put it into buffer;

increment counters;

```

}

```

```

else if

```

(current VC doesn't fill reserved space for it) or

```

(there is free slot left in buffer){

```

*if* (last flit of current VC is next to first slot of next VC buffer space) {

shift down all the flits and reserved space of the lower virtual channels one slot;

increment head pointer for lower VCs;

```

}

```

put flit into buffer;

increment counters;

}

Figure 4.3: Pseudo-code for in buffer operations

```

if (last flit in current VC){

write flit to output port;

decrement counters;

}

else {

write flit to output port;

decrement counters;

shift up remaining flits of current VC;

if (number of remaining flits of current VC >= reserved space number){

shift up all the flits and reserved space of following VC one slot;

decrement head pointer for following VC;

}

}

```

### Figure 4.4: Pseudo-code for out buffer operations

When the buffer performs shift up or shift down operations, the reserved spaces are treated same as the slots which are holding flits. Thus the order of the buffer space for virtual channels is kept conforming to the sequence of virtual channels. And once the number of current flits in buffer plus the number of reserved slots equals to the total amount of buffer slots, no more flit will be accepted unless this flit belongs to a virtual channel which has any reserved space available. Therefore, one or more virtual channels which have the flits come into the buffer at earlier time can never deprive the chance for other virtual channels which get flits later than

46

them to get buffer. Moreover, once the earlier coming packets are blocked in the buffer, since there is still reserved space for other virtual channels, the network traffic will keep flowing, so the performance of the switch is also enhanced. This is the key improvement of  $DAMQ_{all}$ scheme over SCB scheme.

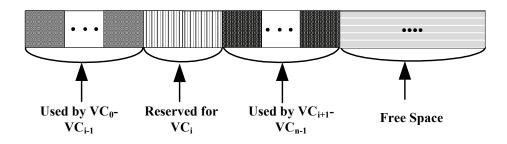

#### 4.2 DAMQ with Minimum Reserved Space for Virtual Channels

DAMQ<sub>all</sub> improved SCB by reserving buffer space for each virtual channel to avoid the situation that a few virtual channels consume the whole buffer then other virtual channels can not get buffer even when those virtual channels which get buffer are blocked. In the simulation experiments, we found that DAMQ<sub>all</sub> is not the most efficient way to reserve space for virtual channels. In a specific time interval, there may be no packets destined for some virtual channels. Even worse situation is that there may be no packets destined for some virtual channels for a very long time. In either case, the reserved spaces for these idle virtual channels are wasted. In order to reserve the buffer space more efficiently and provide more space for flowing traffic, we implement another buffer organization scheme, DAMQ with minimum reserved space for all virtual channels (DAMQ<sub>min</sub>). DAMQ<sub>min</sub> is also based on SCB scheme and the virtual channels of one direction of a physical channel still share a buffer. And based on the simulation results, we still set the number of reserved buffer space to two slots. The difference to DAMQ<sub>all</sub> is that at any time there is at most one reserved space for all the virtual channels. And if every virtual channel have flit present in the buffer, no reserved space will be kept in the buffer anymore. Thus DAMQ<sub>min</sub> use minimum space for reserve purpose. As shown in Figure 4.5, two buffer slots are reserved for the virtual channel which may firstly claim for buffer.

Figure 4.5: DAMQ<sub>min</sub> Buffer space status at the initial state.

Once a virtual channel has one flit come into the buffer, it will occupy two buffer slots which were reserved space before it comes in, thus there is actually still one slot reserved for it. As shown in Figure 4.8, this virtual channel will hold at least these two buffer slots unless it has no flit left in the buffer any more. Once every flits of a virtual channel moves out the buffer, the header pointer of this virtual channel will be reset to empty and there are no more buffer slots belong to it. Another two slots reserved buffer region may be created if possible. The operations that DAMQ<sub>min</sub> performs for incoming and leaving flit are shown in Figure 4.6 and 4.7 respectively.

*if* (first flit for current VC) *and* (there is a reserved space){

put it into buffer;

increment counters;

set head pointer for current VC;

if ( have enough free space in buffer ) and (not every VC are present)

set the reserved space pointer to the slot next to current VC reserved space;

}

### else if

(current VC doesn't fill reserved space for it) or

(there is free slot left in buffer){

*if* (last flit of current VC is next to first slot of next VC buffer space) {

shift down all the flits and reserved space of the lower virtual channels one slot;

increment head pointers for lower VCs;

}

put flit into buffer;

increment counters;

}

J ;

```

if (last flit in current VC){

```

write flit to output port;

decrement counters;

reset head pointer for current VC;

}

$else\{$

write flit to output port;

decrement counters;

shift up remaining flits of current VC;

*if* (number of remaining flits of current VC >= reserved space number){

shift up all the flits and reserved space of following VC one slot;

decrement head pointer for following VC;

- }

- }

if ( no reserved space is present in buffer ) and (not every VC are present) {

if (there are enough free buffer slots)

set the reserved space pointer to the slot next to last VC reserved space;

}

Figure 4.7: Pseudo-code of out buffer operations for DAMQ<sub>min</sub>