This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e. g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

- This work is protected by copyright and other intellectual property rights,

which are retained by the thesis author, unless otherwise stated.

- A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

- This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

- The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

- When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

# TANDEM: Taming Failures In Next-Generation Datacenters With Emerging Memory

Mahesh Dananjaya

Doctor of Philosophy

Institute of Computing Systems Architecture

School of Informatics

University of Edinburgh

2023

## **Abstract**

The explosive growth of online services, leading to unforeseen scales, has made modern datacenters highly prone to failures. Taming these failures hinges on fast and correct recovery, minimizing service interruptions. Applications, owing to recovery, entail additional measures to maintain a recoverable state of data and computation logic during their failure-free execution. However, these precautionary measures have severe implications on performance, correctness, and programmability, making recovery incredibly challenging to realize in practice.

Emerging memory, particularly non-volatile memory (NVM) and disaggregated memory (DM), offers a promising opportunity to achieve fast recovery with maximum performance. However, incorporating these technologies into datacenter architecture presents significant challenges; Their distinct architectural attributes, differing significantly from traditional memory devices, introduce new semantic challenges for implementing recovery, complicating correctness and programmability. Can emerging memory enable fast, performant, and correct recovery in the datacenter? This thesis aims to answer this question while addressing the associated challenges.

When architecting datacenters with emerging memory, system architects face four key challenges: ① how to guarantee correct semantics; ② how to efficiently enforce correctness with optimal performance; ③ how to validate end-to-end correctness including recovery; and ④ how to preserve programmer productivity (Programmability).

This thesis aims to address these challenges through the following approaches: ⓐ defining precise consistency models that formally specify correct end-to-end semantics in the presence of failures (consistency models also play a crucial role in programma-bility); ⓑ developing new low-level mechanisms to efficiently enforce the prescribed models given the capabilities of emerging memory; and ⓒ creating robust testing frameworks to validate end-to-end correctness and recovery.

We start our exploration with non-volatile memory (NVM), which offers fast persistence capabilities directly accessible through the processor's load-store (memory) interface. Notably, these capabilities can be leveraged to enable fast recovery for Log-Free Data Structures (LFDs) while maximizing performance. However, due to the complexity of modern cache hierarchies, data hardly persist in any specific order, jeop-ardizing recovery and correctness. Therefore, recovery needs primitives that explicitly control the order of updates to NVM (known as persistency models). We outline the precise specification of a novel persistency model – Release Persistency (RP) – that provides a consistency guarantee for LFDs on what remains in non-volatile memory upon

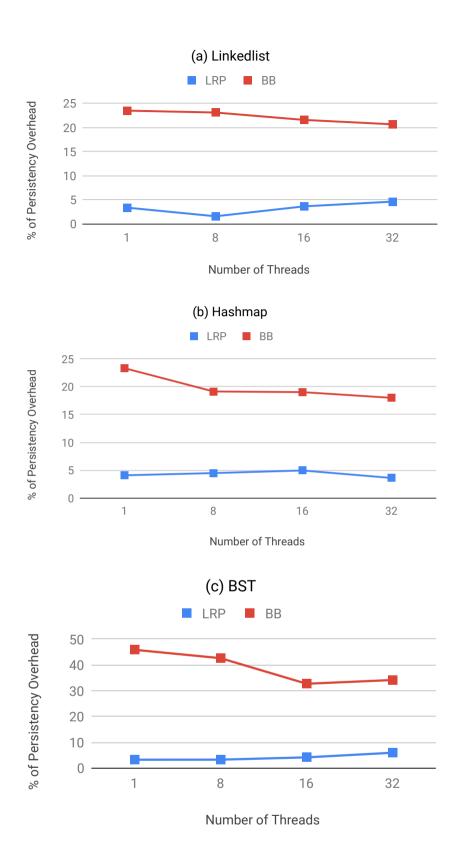

failure. To efficiently enforce RP, we propose a novel microarchitecture mechanism, lazy release persistence (LRP). Using standard LFDs benchmarks, we show that LRP achieves fast recovery while incurring minimal overhead on performance.

We continue our discussion with memory disaggregation which decouples memory from traditional monolithic servers, offering a promising pathway for achieving very high availability in replicated in-memory data stores. Achieving such availability hinges on transaction protocols that can efficiently handle recovery in this setting, where compute and memory are independent. However, there is a challenge: disaggregated memory (DM) fails to work with RPC-style protocols, mandating one-sided transaction protocols. Exacerbating the problem, one-sided transactions expose critical low-level ordering to architects, posing a threat to correctness. We present a highly available transaction protocol, Pandora, that is specifically designed to achieve fast recovery in disaggregated key-value stores (DKVSes). Pandora is the first one-sided transactional protocol that ensures correct, non-blocking, and fast recovery in DKVS. Our experimental implementation artifacts demonstrate that Pandora achieves fast recovery and high availability while causing minimal disruption to services.

Finally, we introduce a novel target litmus-testing framework – DART – to validate the end-to-end correctness of transactional protocols with recovery. Using DART's target testing capabilities, we have found several critical bugs in Pandora, highlighting the need for robust end-to-end testing methods in the design loop to iteratively fix correctness bugs. Crucially, DART is lightweight and black-box, thereby eliminating any intervention from the programmers.

# Lay summary

Modern datacenters have continued to grow in size and complexity, with failures becoming more common than exceptions. The frequency of these failures and their complexity and impact have dramatically escalated in recent years. These failures, unfortunately, disrupt critical services and reduce the datacenters' ability to respond to users online (i.e., availability). Such disruptions not only incur significant costs but also tarnish the reputation of cloud operators.

Addressing failures requires fast recovery algorithms to restore components and avoid service interruptions. However, achieving fast recovery involves trade-offs in performance, correctness, and programmability. Emerging non-volatile and disaggregated memories promise opportunities for efficient recovery but also introduce correctness and programmability challenges due to their unique architectures.

In addressing these challenges, this thesis tackles three key aspects of architecting modern datacenters with emerging memory: defining precise correctness semantics (i.e., consistency), developing performant low-level primitives for efficiently enforcing correctness, and creating robust testing frameworks to validate end-to-end correctness.

This thesis makes significant contributions in three key areas: Firstly, we propose a novel consistency model, Release Persistency, along with an efficient microarchitecture mechanism, Lazy Release Persistency. These innovations are designed to enable fast, correct, and performant recovery in non-volatile-memory data structures. Secondly, leveraging the benefits of disaggregated memory, we introduce Pandora, the first fast, correct, and recoverable one-sided transaction protocol specifically designed for disaggregated data stores. Finally, we introduce DART, a framework that validates end-to-end correctness of transaction protocols with recovery.

Overall, this thesis exemplifies a holistic approach addressing recovery (availability), performance, consistency, and programmability tensions using emerging memories. The specifications, mechanisms, and techniques unlock potential for reliable, efficient recovery, avoiding catastrophic failures in next-generation datacenters. Despite limitations, it provides promising directions for continued research on next-generation datacenter architectures.

# **Acknowledgements**

This PhD thesis would not have been possible without the support of many individuals.

First and foremost, I express my deepest gratitude to my supervisors, Vijay Nagarajan, Murray Cole, Pramod Bhatotia, and Vaishak Belle. Their invaluable guidance, mentorship and unwavering belief in my abilities have been instrumental throughout my PhD journey. I am immensely grateful for the knowledge and wisdom they have imparted. I also wish to extend profound thanks to my thesis committee members, Yuvraj Patel and Haris Volos, for their constructive feedback and steadfast support in shaping this thesis.

I extend special thanks to Vasilis Gavrielatos for being an amazing collaborator and mentor from day one. His support and guidance throughout my PhD was pivotal for its successful completion. I am also thankful to my other collaborators and mentors, including Arpit Joshi, Antonis Katsarakis, Rodrigo Rocha, Sukarn Agarwal, and Andres Goens, for their support and encouragement throughout this journey.

I am thankful to my academic colleagues and friends, whose camaraderie, intellectual exchanges, and shared passion for research have made this academic pursuit both challenging and enjoyable. Their diverse perspectives and stimulating discussions have enriched my understanding and inspired new ideas. I cherish the friendships formed during this time and appreciate the collaborative spirit that permeates our academic community. (There are so many to mention, this is for all of you.)

I am indebted to my family and Tharu for their unconditional love, unwavering support, and constant encouragement. Their belief in my dreams and their sacrifices have been a constant source of strength and motivation. Their presence in my life has been a beacon of light during the most challenging times, and I am profoundly grateful for their unwavering faith in me. Additionally, I am blessed to have found an extended family in Edinburgh — Pete, Matt, Rado, Muyang, Roger, Roberta, and all my CDT friends. They have always been a constant source of inspiration to me.

Finally, I dedicate this thesis to my beloved mother, whose love, guidance, and sacrifices have been the foundation of my life's journey. Her unwavering belief in my potential, even during moments of self-doubt, has instilled in me the courage to pursue my dreams relentlessly. Her love and encouragement have been a driving force behind my academic achievements, and I am forever grateful for her presence in my life. This thesis is a testament to her unwavering support and a humble token of my love and appreciation.

# **Declaration**

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified.

- M. Dananjaya, "Release Persistency", Master of Science by Research Thesis, The University of Edinburgh.

- M. Dananjaya, V. Gavrielatos, A. Joshi, V. Nagarajan, "Lazy Release Persistency", 2020 ACM 25th International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), 2020, Lausanne, Switzerland. doi: 10.1145/3373376.3378481.

(Mahesh Dananjaya)

| To my loving mother for instilli | ng the value of consistency, persistency, and                     | d taming |

|----------------------------------|-------------------------------------------------------------------|----------|

| To my loving mother for instilli | ng the value of consistency, persistency, and failures in my life | d taming |

| To my loving mother for instilli |                                                                   | d taming |

| To my loving mother for instilli |                                                                   | d taming |

| To my loving mother for instilli |                                                                   | d taming |

| To my loving mother for instilli |                                                                   | d taming |

| To my loving mother for instilli |                                                                   | d taming |

# **Contents**

| 1 | Intro | oductio | n                              | 1  |

|---|-------|---------|--------------------------------|----|

|   | 1.1   | Motiva  | ation                          | 2  |

|   |       | 1.1.1   | Failures and Availability      | 2  |

|   |       | 1.1.2   | Recovery                       | 3  |

|   |       | 1.1.3   | Recovery Trade-Offs            | 3  |

|   | 1.2   | Impact  | t of Emerging Memory           | 5  |

|   |       | 1.2.1   | Non-Volatile Memory (NVM)      | 5  |

|   |       | 1.2.2   | Disaggregated Memory (DM)      | 6  |

|   | 1.3   | This T  | hesis                          | 8  |

|   |       | 1.3.1   | Problem Statement              | 8  |

|   |       | 1.3.2   | Research Objectives            | 10 |

|   |       | 1.3.3   | Scope                          | 11 |

|   | 1.4   | Thesis  | Contributions                  | 11 |

|   |       | 1.4.1   | Lazy Release Persistency (LRP) | 11 |

|   |       | 1.4.2   | Pandora                        | 12 |

|   |       | 1.4.3   | DART                           | 12 |

|   | 1.5   | Summa   | ary                            | 13 |

| 2 | Bacl  | kground | d                              | 15 |

|   | 2.1   | The Da  | atacenter Architecture         | 15 |

|   |       | 2.1.1   | Recovery                       | 16 |

|   | 2.2   | Emerg   | ing Memory Systems             | 18 |

|   |       | 2.2.1   | Non-Volatile Memory (NVM)      | 18 |

|   |       | 2.2.2   | Disaggregated Memory (DM)      | 19 |

|   | 2.3   | Consis  | stency Models                  | 20 |

|   |       | 2.3.1   | Linearizability                | 21 |

|   |       | 2.3.2   | Sequential Consistency         | 21 |

|   |       |         |                                |    |

|   |      | 2.3.3    | Release Consistency                                         | 22 |

|---|------|----------|-------------------------------------------------------------|----|

|   | 2.4  | Memo     | ry Persistency Models                                       | 23 |

|   | 2.5  | Transa   | actional Consistency Models                                 | 24 |

|   |      | 2.5.1    | Strict Serializability                                      | 25 |

| 3 | Lazy | y Releas | se Persistency                                              | 29 |

|   | 3.1  | Introdu  | uction                                                      | 29 |

|   |      | 3.1.1    | Contributions                                               | 31 |

|   | 3.2  | Prelim   | inaries                                                     | 32 |

|   |      | 3.2.1    | Release Consistency                                         | 32 |

|   |      | 3.2.2    | Persistency Models                                          | 33 |

|   |      | 3.2.3    | Log-free data structures (LFDs)                             | 34 |

|   | 3.3  | Limita   | tions of ARP                                                | 35 |

|   |      | 3.3.1    | ARP semantics                                               | 36 |

|   |      | 3.3.2    | ARP implementation                                          | 36 |

|   |      | 3.3.3    | Why not simply fix ARP?                                     | 37 |

|   | 3.4  | Releas   | se Persistency                                              | 38 |

|   |      | 3.4.1    | Formal Specification                                        | 38 |

|   |      | 3.4.2    | Specification implications                                  | 39 |

|   | 3.5  | Lazy F   | Release Persistency                                         | 40 |

|   |      | 3.5.1    | LRP Overview                                                | 40 |

|   |      | 3.5.2    | LRP: Microarchitecture                                      | 42 |

|   | 3.6  | Experi   | mental Evaluation                                           | 47 |

|   |      | 3.6.1    | Workloads                                                   | 47 |

|   |      | 3.6.2    | Comparison Points                                           | 48 |

|   |      | 3.6.3    | Simulator                                                   | 49 |

|   |      | 3.6.4    | Results                                                     | 50 |

|   | 3.7  | Summ     | ary                                                         | 53 |

| 4 | Pane | dora: H  | Highly Available, Recoverable Transactions on Disaggregated | I  |

|   | Data | Stores   |                                                             | 57 |

|   | 4.1  | Introdu  | uction                                                      | 57 |

|   |      | 4.1.1    | Pandora                                                     | 59 |

|   |      | 4.1.2    | Contributions                                               | 60 |

|   | 4.2  | Prelim   | inaries                                                     | 61 |

|   |      | 4.2.1    | Disaggregated KVS (DKVS)                                    | 61 |

|   |      |          |                                                             |    |

|   |      | 4.2.2    | Recoverable Transaction Protocol                               | 63  |

|---|------|----------|----------------------------------------------------------------|-----|

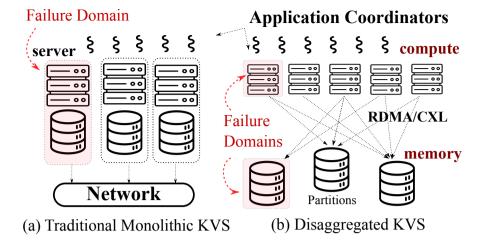

|   |      | 4.2.3    | FORD                                                           | 64  |

|   | 4.3  | Pandor   | a                                                              | 65  |

|   |      | 4.3.1    | Making FORD Efficiently Recoverable                            | 65  |

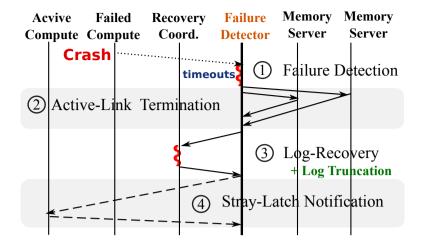

|   |      | 4.3.2    | Recovery Protocol                                              | 69  |

|   | 4.4  | Evalua   | ting Pandora: Goals and Methodology                            | 72  |

|   |      | 4.4.1    | Methodology                                                    | 73  |

|   | 4.5  | Experi   | mental Evaluation                                              | 74  |

|   |      | 4.5.1    | Recovery Latency                                               | 74  |

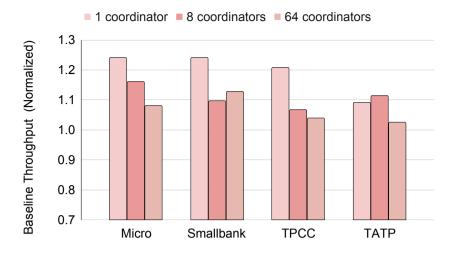

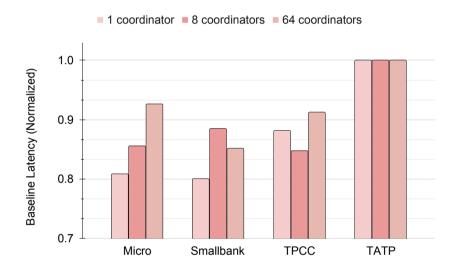

|   |      | 4.5.2    | Steady-State Throughput                                        | 76  |

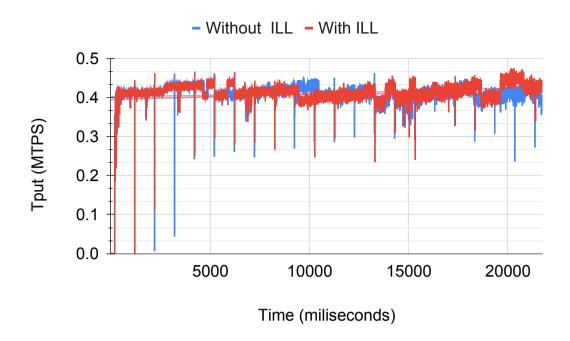

|   |      | 4.5.3    | Fail-Over Throughput                                           | 79  |

|   | 4.6  | Summa    | ary                                                            | 82  |

| 5 | DAR  | T: Valid | dating Transactional Databases with Target Application-Centric |     |

|   | Recu | ırrent T | Testing                                                        | 85  |

|   | 5.1  | Introdu  | action                                                         | 85  |

|   | 5.2  | Metho    | d                                                              | 86  |

|   |      | 5.2.1    | Application-Centric Assertions                                 | 87  |

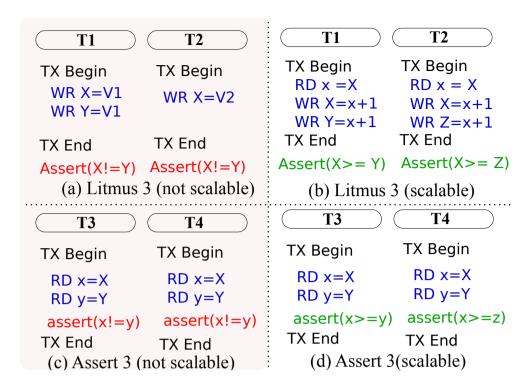

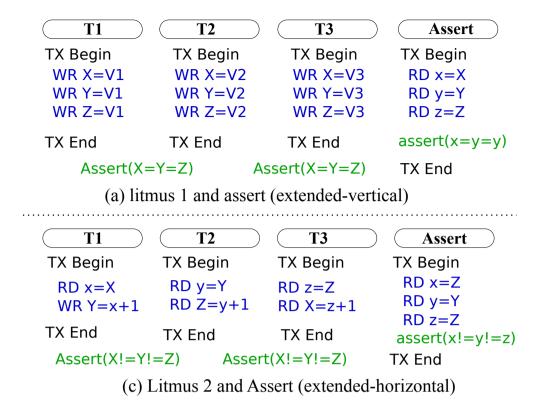

|   | 5.3  | Litmus   | Tests, Bugs, and Fixes                                         | 88  |

|   |      | 5.3.1    | Litmus 1                                                       | 88  |

|   |      | 5.3.2    | Litmus 2                                                       | 89  |

|   |      | 5.3.3    | Litmus 3                                                       | 90  |

|   |      | 5.3.4    | More Bugs and Fixes                                            | 90  |

|   | 5.4  | Test Co  | overage                                                        | 91  |

|   | 5.5  | Summa    | ary                                                            | 92  |

| 6 | Con  | clusion  |                                                                | 95  |

|   | 6.1  | Summa    | ary                                                            | 95  |

|   | 6.2  | Critica  | l Analysis                                                     | 97  |

|   | 6.3  | Lesson   | as Learned                                                     | 99  |

|   |      | 6.3.1    | Lesson 1: Formal Methods vs Testing                            | 99  |

|   |      | 6.3.2    | Lesson 2: Inherent Complexity of Consistency                   | 100 |

|   | 6.4  | Future   | Work                                                           | 101 |

|   |      | 6.4.1    | Formal Proof                                                   | 101 |

|   |      | 6.4.2    | Verifiably Correct Transaction Protocols                       | 101 |

|   |      | 6.4.3    | Incorporating New Emerging Memory Technologies                 | 102 |

| 6.4.4        | Final Remarks | <br> | 102 |

|--------------|---------------|------|-----|

| Bibliography |               |      | 103 |

# **Chapter 1**

# Introduction

From shopping to socializing, our everyday activities are increasingly reliant on a wide range of online services, including e-commerce, self-driving, banking, streaming, social media, and online gaming. These services run in a shim layer, known as Cloud [19, 20] or Sky [196], functioning over datacenters.

The unprecedented growth of online services has led to previously unseen demand for datacenters. To meet such a proliferating demand, modern data centers have become increasingly large, complex, and heterogeneous, making failures the norm rather than the exception. Unfortunately, failure disrupts critical services implemented in modern datacenters [27, 85].

The cost of service downtime is substantial, resulting in significant financial losses for businesses and negatively impacting overall quality of service (QoS). A typical service outage of a few minutes can cost millions of dollars for companies [125]. Therefore, it is critically important to architect data centers with fault tolerance [71, 57].

Tolerating failures in modern data centers requires fast recovery to minimize interruptions to the services (i.e., high availability). However, fast recovery gives rise to new challenges in performance, correctness, and programmability.

In this chapter, we closely examine failures, recovery, and their crucial trade-offs in the data center while outlining the problem statement, research objectives, and the scope of this thesis (§1.1). Furthermore, we describe our approach and the contributions of this thesis (§1.4).

#### 1.1 Motivation

The modern datacenter has created an abstract machine—which is referred to as the Cloud, or Sky [19, 20, 196]— to store, retrieve, and process petabytes of application data. Such abstraction allows for seamless management of online services while hiding the underlying scale and complexity from application developers. However, the reality is that modern datacenters consist of countless numbers of hardware and software resources (CPU, memory, storage, network and OS libraries, application software) that fail all the time [109, 27]. In this section, we discuss the importance of taming failures in modern datacenters.

#### 1.1.1 Failures and Availability

In 2013, a study conducted by Google revealed that a typical datacenter server experiences 1.2 to 2 crashes per year [26]. Even at these rates, the mean time to failure (MTTF) of the datacenter, comprising tens of thousands of servers, was estimated to be in the order of minutes. For instance, consider a datacenter with 10,000 servers, each having an MTTF of 365 days (equivalent to one crash per year). The calculated MTTF for this datacenter would be approximately 50 minutes, which is significantly low (calculated as 365 days \* 24 hrs/day \* 60 mins/hr \* 1/10,000 = 50 mins). The today's reality, however, is considerably more challenging, as modern datacenters have continued to scale up to tens of thousands to millions of servers, and the complexity of failures has substantially increased [26, 24, 149].

Failures can disrupt a service in two ways. First, the failed servers stop responding to service requests until the damage is recovered. Second, a failed server can abruptly disrupt the functioning of the remaining servers in the service. Availability in the presence of such failures is measured as a fraction of time that the service remains operational [102]. For instance, consider a service operating on a datacenter with mean time to failures (MTTF) of 60 min and mean time to recover (MTTR) of 500 ms. The calculated availability is 0.99 or two nines (using equation 1.1). Crucially, datacenter operators prioritize offering high availability, ideally five nines and more [49], as it directly affects the client's online experience and profits.

Additionally, failures are not the sole factor affecting availability; high client traffic and limited resource availability can adversely impact overall availability. While these aspects are important, they are not the focus of this thesis.

1.1. Motivation 3

$$Availability = \frac{MTTF}{MTTF + MTTR} \tag{1.1}$$

#### 1.1.2 Recovery

A typical service involves multiple applications that are implemented over numerous servers, each responsible for computation and storage functionalities. Clients interact with the services by sending requests to these servers. Unfortunately, crashed servers lose data, stop responding to clients, and disrupt the operation of other servers. Maintaining service availability in the face of failures requires quickly and correctly recovering failed segment of the application.

System architects typically use different terms such as recovery and fault tolerance interchangeably to describe a system's ability to operate through failures. While their textbook definitions have subtle nuances, the lines between these concepts have increasingly blurred in real-world usage, largely owing to intricate modern datacenter designs and complex application logic [38]. Therefore, before delving into recovery, let's first explore what it entails.

Traditionally, recovery refers to steps taken after a failure to bring back the failed components to life. However, modern datacenters demand high availability, making it no longer feasible to wait for all the failed components to be fully recovered. Thus, applications incorporate redundancy mechanisms like replication to minimize downtime by relaying the application over redundant resources [38, 198, 202]; clients experience no interruptions. While minimal, these redundancy mechanisms still require a form of recovery which can be as little as resending client requests to a redundant application server [38]. In this thesis, we categorize all these different aspects as recovery.

Broadly, we define recovery as the ability to restore a failed segment of the application – data and computation logic – regardless of whether the application remains on the same physical devices. This definition enables us to reason about recovery in a system-agnostic way.

#### 1.1.3 Recovery Trade-Offs

Given the unpredictable nature of failures, which can occur at any point during application execution, recovery requires implementing additional measures to maintain a recoverable state throughout the failure-free execution of applications.

First, it is vital to store application data in a fail-safe manner, as there is a risk of permanent loss in the event of failures. System architects must ensure that data remains stored and accessible over time, even in the face of various failures or disasters (durability). Durability requires persistence or replicating of data [83, 96, 76]. Persistence ensures that failed servers can restart with a consistent data state, while replication allows the failed portion of the application to continue functioning on a backup server [39, 14].

Second, the consequences of server failures extend beyond data losses to disrupting computation logic. Recovery must ensure that each request appears to execute exactly once in an all-or-nothing manner with no partial effects on data (*Failure Atomicity*). This is because, typically, client requests trigger multiple actions within application servers, hence failures can unpredictably disrupt the execution at any point. In particular, system architects ensure atomicity through write-ahead logging [160, 159, 180], a technique that involves preemptively saving copies of data before making actual changes.

Crucially, additional recovery measures to implement data durability and failure atomicity have severe implications on performance, correctness, and programmability.

Correctness Implications. Recovery complicates the end-to-end correctness of applications. Additional recovery measures introduce significant complexity into the protocols and implementation, making it incredibly difficult to validate against the abstract correctness properties of the applications [98, 197, 46, 142]. Rare corner cases and the non-deterministic nature of failures further exacerbate this problem. Designing recovery protocols and validating their correctness remains a notoriously challenging problem [151, 103, 173, 214, 213].

**Performance Implications.** Implementing precautionary measures for recovery negatively impacts performance; Since datacenter performance is measured by the number of client requests completed within a fixed time frame (also referred to as throughput), introducing more recovery measures results in higher CPU usage for processing client requests, thereby reducing overall performance.

**Programmability Implications.** Alternatively, if system architects choose to expose low-level complexities like handling failures to programmers for performance reasons [179, 136, 78], the subtle complexities in recovery can diminish programmer productivity (programmability), and usability in the datacenter.

**Design Goals.** Achieving fast and correct recovery, while critically important, is a significantly challenging task. Architects focus on four key aspects when designing

datacenter recovery:(i) minimizing recovery time or downtime (High Availability), (ii) reducing performance overhead to a minimum (High Performance), (iii) enforcing end-to-end correctness as if no failures occurred (Consistency), and (iv) preserving programmer productivity (Programmability). However, achieving these objectives remains challenging despite years of research, mainly due to their inherent conflicts and ever-increasing failures. State-of-the-art recovery methods often prove slow, incorrect, or require significant correctness and programmability trade-offs [211, 66].

## 1.2 Impact of Emerging Memory

Two key innovations in the memory subsystem (known as emerging memory) – non-volatile memory (NVM) and hardware-disaggregated memory (we will simply refer to it as *disaggregated memory* or *DM* from here on) – have radically changed the way in which datacenters are built and operated. Crucially, we observe that these new memory technologies offer a promising pathway for enabling fast recovery with minimal performance overhead. In this section, we provide an intuitive overview of this opportunity. First, we start our discussion with non-volatile memory (NVM) and then continue it with disaggregated memory.

#### 1.2.1 Non-Volatile Memory (NVM)

Datacenter applications largely rely on memory for low latency and high performance. Historically, the content of this memory was lost when servers failed by crashing (volatile). In contrast, the content of NVM survives server failures, hence offering persistent storage. What does this mean for recovery?

In the case of volatile memory, the application must constantly backup data in persistent storage for durability. However, traditional persistent storage devices such as hard disks, accessible only through the I/O interface, introduce significant latency, typically ranging from hundreds of microseconds to tens of milliseconds, thereby inducing prohibitively large overhead on performance [210]. On the contrary, nonvolatile memory (NVM) provides fast persistence within a few hundred nanoseconds, significantly faster than traditional disk-based storage [112]. This fast persistence capability of NVM can enable recovery with minimal performance overhead.

**Opportunity.** In-memory data structures are pivotal components in modern datacenters, facilitating ultra-fast storage and retrieval of client and management data for appli-

cations [43]. However, these data structures lack persistence, which means that their contents can be vulnerable to loss in the event of failure. To mitigate the risk of data loss, conventional approaches involve persisting data on slower storage media, such as hard disks. Unfortunately, this method often leads to significantly reduced throughput [215].

Non-volatile memory (NVM) presents an alternative solution for in-memory data structures by eliminating the need for slow persistent storage mediums like hard disks (as memory itself is inherently persistent). This offers the opportunity to achieve maximum performance for applications relying on in-memory data structures [43].

Log-free data structures (LFDs) are a special class of in-memory data structures that can recover fast in the presence of failures (Null Recovery) [111]. This is achieved by preserving their happens-before order, in which concurrent operations are visible, in persistent storage without incorporating additional techniques such as logging [56, 111]. However, LFDs often suffer from high overhead on performance for maintaining a recoverable state during failure-free execution (because they have to backup data on a disk in the critical path of execution). Thus, LFDs coupled with NVM can offer fast recovery with maximum performance [56].

#### 1.2.2 Disaggregated Memory (DM)

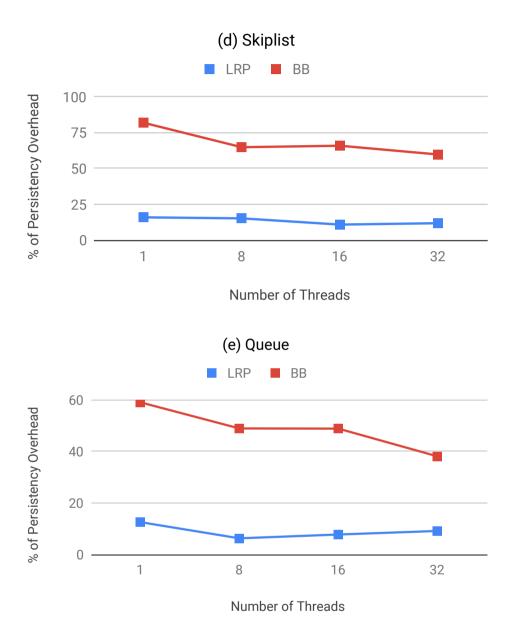

Memory disaggregation decouples memory from traditional monolithic servers [144, 145]. In this new setting, *compute servers* execute the application logic while *memory servers* store the application data. Direct communication between compute and memory servers is facilitated by fast Remote Direct Memory Access (RDMA) [119], or future technologies such as Compute eXpress Link (CXL) [139, 90].

While disaggregation is not a novel concept and has been previously applied to various components within datacenters, such as storage [25, 84, 155], power [172], and cooling systems [171], the advent of fully-fledged hardware-disaggregated memory has rekindled the interest of system architects for several compelling reasons. First, memory, despite its cost [139], often remains underutilized due to over-provisioning based on peak load estimations. Second, the demand for memory is experiencing exponential growth as big data processing increasingly relies on memory for faster execution. However, the capacity of individual server memory is limited by vendor-specific interconnection technologies and other hardware constraints [9]. This trend is driving datacenters toward resembling distributed shared memory systems (DSMs) [59, 120]. Unlike traditional DSMs that heavily rely on Remote Procedure Calls (RPCs), which

are no longer viable in next-generation data centers [177, 216], memory disaggregation provides a way to tightly couple remote memory with application logic.

In addition, DM offers significant advantages in terms of cost savings, energy efficiency, scalability, and manageability in the datacenter [99, 130].

#### **Opportunity.** What does memory disaggregation mean to recovery?

Disaggregation isolates failures on the compute and memory servers, enabling fast compute recovery. On the one hand, memory servers neither contain a CPU nor run any complicated software, hence they rarely fail and do not disrupt compute servers. On the other hand, a failed compute server need not stop the application entirely, as memory is available to the other compute servers. In addition to fast recovery, maintaining a recoverable state in DM is significantly faster with direct RDMA accesses or CXL (as opposed to RPCs), thereby maximizing performance.

Disaggregation proves crucial for key-value data stores (KVSes) that seek high availability. Typically, KVSes are partitioned, and these partitions are distributed between numerous servers within the datacenter, akin to a distributed shared memory system [59]. Crucially, the increasing rate of failures in modern datacenters poses a substantial challenge to the availability of these data partitions, necessitating fast recovery. Recovery, however, relies on fault-tolerant transaction protocols that replicate data across multiple servers for durability while ensuring the atomicity of data changes across replicated partitions (meaning that changes applied to one replica will be consistently visible in all other replicas [59, 30, 39]).

Traditionally, KVS data replicas are co-located within monolithic servers that handle both computation and data. However, this approach has a drawback: Memory failures can occur whenever a server crashes, thus reducing replica availability. One of the consequences of this is that, upon detecting a failure, recovery often necessitates stopping the data store entirely to update the new configurations of replicas (which is not conducive to achieving fast recovery). In contrast, disaggregated memory eliminates these limitations by isolating memory failures, allowing for fast recovery from compute failures, which are the predominant cause of failures in data stores [26]. Consequently, memory disaggregation can be leveraged to design performant key-value data stores that offer high availability (we refer to these data stores as *disaggregated key-value stores* or *DKVSes* here onward).

#### 1.3 This Thesis

#### 1.3.1 Problem Statement

We have thus far argued that emerging memory technologies surprisingly offer the opportunity to achieve fast recovery with maximum performance. However, these new memory devices come with different architectural attributes. Consequently, architecting datacenters with emerging memory introduces new semantic challenges. First, architects need precise semantics for end-to-end correctness, including recovery (Consistency Models). Then, architects need new low-level primitives to correctly and efficiently enforce these prescribed models. Failure to specify or enforce the precise consistency semantics not only complicates correctness but also hampers programmability and performance. In this section, we discuss the challenges associated with each emerging memory technology.

#### 1.3.1.1 Non-Volatile Memory

Applications access non-volatile memory (NVM) through processor's load/store memory interface (as opposed to traditional I/O-based disks). Therefore, architecting datacenters with NVM requires new abstractions to reason about *persistent memory accesses*.

Regular memory accesses, due to complexities such as caching and concurrency in modern processors, require ordering that is governed by traditional shared-memory consistency models [79]. These models further bridge the gap between system architects and programmers by acting as a contract, wherein the architects guarantee specific correctness properties if programmers follow a set of rules defined by the model. However, traditional shared-memory consistency models, or the protocols that enforce them in server CPUs, fail to work with failures, posing a significant threat to correctness.

**Ordering Challenges.** NVM necessitates precise consistency models to control the order of memory updates to NVM (often referred to as Persistency Models). These models ensure end-to-end correctness of applications including recovery in the presence of failures. Introduced by Pelly et al [87, 175], persistency models remain an active area of research. Owing to recovery, these models introduce additional ordering, which further complicates programmability, or otherwise leads to significant performance losses [88].

**Problem:** Persistency For LFDs. Recall that coupled with NVM, log-free data structures (LFDs) can provide fast recovery. Alas, we observed that state-of-the-art per-

1.3. This Thesis 9

sistency models are neither sufficient nor optimal for recovering LFDs in NVM. These models lead to correctness bugs, making LFDs unrecoverable, and induce prohibitively large performance overhead.

#### 1.3.1.2 Disaggregated Memory

Recall that disaggregated memory (DM) presents the opportunity for enabling fast recovery in key-value data stores (KVSes). Correct and fast recovery in these data stores rests on transaction protocols that ensure atomicity of a group of operations (like insert, delete, update, search), while hiding underlying complexity like replication from the application programmers. However, transaction protocols in this setting can only operate with one-sided RDMA messages, as RPC-style protocols do not work with passively disaggregated memory.

**Ordering Challenges.** One-sided accesses, in the absence of RPCs, expose critical low-level ordering of macro operations in transaction protocols to the high-level architectural interface. Therefore, system architects should carefully enforce transactional semantics with one-sided accesses, which otherwise pose a threat to correctness. Moreover, one-sided ordering is not only crucial for ensuring correctness but also plays a critical role in harnessing the performance potential of these new memory technologies. It allows architects to optimize performance based on the specific characteristics of one-sided accesses.

**Problem: One-Sided Transactions.** We have observed that there are no correct and recoverable one-sided transaction protocols. The only state-of-the-art one-sided protocol, FORD [219], which was developed in parallel to this thesis, has overlooked recovery, thereby leading to recovery bugs, while inducing prohibitively large recovery time.

(Additionally, previous disaggregation approaches, such as storage disaggregation, while addressing a similar availability problem, still rely on software Remote Procedure Calls (RPC) and have not been extensively studied with transaction or one-sided protocols due to various limitations [182]; These approaches are primarily tailored to distributed file systems or disk-based block storage, and therefore cannot be directly applied to the context of disaggregated memory or key-value stores [155, 25, 84].)

#### 1.3.1.3 **Summary**

Emerging memory technologies are promising but share one challenge in common: Their unique architectural attributes, which drastically differ from traditional memory devices, expose critical low-level ordering to high-level application (or software) interfaces, presenting a semantic challenge. System architects typically understand end-to-end correctness through consistency models. Although abstract specifications of these models are well-understood, realizing them in practice with emerging memory is an incredibly hard challenge. This complexity affects not only correctness but also performance and programmability, presenting a significant challenge in harnessing the full potential of these technologies.

#### 1.3.2 Research Objectives

The primary goal of this thesis is to investigate and address the challenges of achieving fast, correct, and performant recovery in modern datacenter architectures. We focus on leveraging two emerging memory technologies, nonvolatile memory (NVM) and disaggregated memory (DM). While these technologies offer opportunities for fast recovery and high performance, they also introduce new semantic challenges, which present significant barriers to the realization of their full potential. Our objective is to address these challenges that arise when architecting datacenters with emerging memory technologies. Our specific objectives are as follows.

**Consistency Specification.** We aim to define precise consistency models that formally specify end-to-end correctness guarantees for applications using emerging memory technologies within datacenters.

**Low-Level Mechanisms.** We seek to explore low-level primitives tailored to emerging memories that efficiently enforce the prescribed consistency models.

**Testing and Validation.** We aim to create robust testing frameworks to validate overall correctness, including recovery mechanisms.

**Programmability.** We aim to maintain programmer productivity (programmability) by minimizing exposure to low-level complexities in the consistency models, as subtle complexities in consistency models often introduce new ordering rules, hindering programmability.

These objectives collectively aim to unlock the potential of emerging memory for achieving fast, performant, and correct recovery in the datacenter architectures of the

next generation.

#### 1.3.3 Scope

We further limit the discussion of this thesis to the following aspects.

First, we assume fail-stop failures (non-byzantine) [184]. A failed process or server is not allowed to continue with the failed components. This is the most common failure model in modern datacenters.

Second, we assume that there is one single datacenter rather than multiple datacenters. This approach allows us to concentrate on common failure scenarios, as fault tolerance complexity does not significantly increase with multiple datacenters. In fact, fault tolerance techniques developed for a single datacenter serve as foundational building blocks for similar techniques across datacenters.

#### 1.4 Thesis Contributions

In this thesis, we explore the datacenter architecture with two emerging memory technologies, non-volatile memory (NVM) and disaggregated memory, to achieve our research objectives. In this section, we discuss our approach and its contributions. First, we start our discussion with non-volatile memory (NVM), and then we extend the discussion to disaggregated memory.

## 1.4.1 Lazy Release Persistency (LRP)

We address the challenges of architecting datacenters with NVM with the following approach: First, we rectify the critical ordering requirements for correct and recoverable lock-free data structures (LFDs). Second, we show that state-of-the-art persistency models are neither sufficient nor optimal for enforcing correct LFD semantics in the presence of failures. Third, strengthening the existing models, we introduce precise specifications of a novel persistency model –Release Persistency (RP) [55, 54] – that provides a consistency guarantee for LFDs on what remains in non-volatile memory upon failure. Next, to efficiently enforce RP, we propose a novel microarchitecture mechanism - Lazy Release Persistency (LRP) [55]. Finally, through extensive evaluation with standard LFD benchmarks, we demonstrate that LRP achieves fast recovery while incurring minimal overhead on performance.

**Programmability.** New consistency semantics (or persistency models) impact programmability as they introduce new ordering rules. One of the key advantages of Release Persistency is its compatibility with an already established programming model: Sequential Consistency for Data Race Freedom (DRF-SC). These models are already supported in popular programming languages like Java and C++. For instance, the programs written using standard C++ libraries can be directly compiled into their RP-based recoverable version without compromising programmability.

#### 1.4.2 Pandora

We continue our contributions with disaggregated memory. Recall that disaggregation enables the possibility of rendering high availability, but achieving high availability hinges on correct and recoverable one-sided transaction protocols. First, we rectify one-sided ordering in disaggregated memory systems and their impact on transaction protocols. Second, we show that the state-of-the-art one-sided transaction protocol has overlooked one-sided ordering, leading to critical correctness and recovery bugs. Third, we present a highly available and recoverable transaction protocol—Pandora—which is specifically designed to achieve fast recovery in disaggregated key-value stores (DKVSes).

Pandora is the first one-sided transactional protocol that ensures correct, non-blocking, and fast recovery in DKVSes. Pandora's fast recovery is based on two key innovations: (i) Implicit Latch Logging (ILL) and (ii) end-to-end RDMA-based idempotent recovery algorithm. We implement Pandora using fully one-sided RDMA operations while avoiding other hardware complexities associated with disaggregation. Our implementation artifacts show that Pandora achieves fast recovery while incurring minimal interruption to the services.

**Programmability.** Pandora does not compromise programmability in the datacenter as we comply with the transactional semantics. Transactions are the de facto programming model in many state-of-the-art data store applications.

#### 1.4.3 **DART**

One of the key challenges of designing one-sided transaction protocols is validating their end-to-end correctness, including recovery. For instance, how do we know that Pandora's recovery is correct? Existing techniques for testing generic applications 1.5. Summary 13

and transaction protocols are often limited to random testing and significantly impact programmability and scalability.

We propose a novel target litmus-testing framework–DART–for validating end-toend correctness of transaction protocols with recovery. We use DART's target-testing abilities to find several critical bugs in Pandora, which we fix iteratively, highlighting the need for efficient testing methods for transaction protocols. Crucially, DART operates as a black-box testing framework, eliminating the need for programmers to invest additional effort or possess knowledge of the underlying complexities.

### 1.5 Summary

Emerging memory technologies, specifically non-volatile memory and disaggregated memory, offer a promising pathway to address increasing failures in modern datacenters with fast and performant recovery. However, this opportunity comes with new design and semantic challenges. When architecting datacenters with emerging memory, first, we need precise consistency models to reason about end-to-end correctness under failures, second, we need efficient architectural primitives (low-level mechanisms) to implement these models in the datacenter, and third, we need new methods for validating the end-to-end correctness, including recovery. In this thesis, we address the challenge while taking advantage of the opportunity for performance and availability.

This thesis is organized as follows. In Chapter 2, we establish the required background material. In Chapter 3, we present a new consistency model and an efficient microarchitecture implementation for NVM-based datacenter architecture. In Chapter 4, we describe a recoverable and highly available one-sided transaction protocol targeting disaggregated memory data stores. In Chapter 4, we introduce a new litmus-testing framework for validating the end-to-end correctness of transaction protocols. Our artifacts based on standard benchmarks demonstrate that the proposed solutions achieve fast and correct recovery while incurring minimal performance overhead. Finally, in Chapter 6, we summarize the dissertation and present some lessons that we learn during the course of this dissertation.

# **Chapter 2**

# **Background**

In this chapter, we lay the foundation by introducing the background materials essential to this thesis. First, we offer an overview of modern datacenter architecture, the failure model, and fault tolerance(§2.1). Second, we examine emerging memory and its influence on modern datacenter architecture (§2.2). Finally, we present a concise overview of relevant consistency models and how they respond to failures. (§2.3).

#### 2.1 The Datacenter Architecture

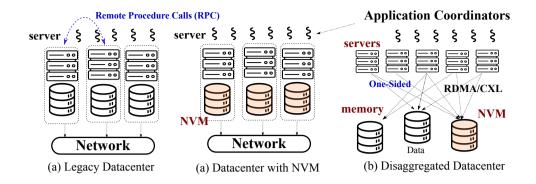

In this section, we outline the key assumptions underlying our study, focusing on the architecture of datacenters and the failure model. A datacenter consists of interconnected servers, each equipped with CPU, memory, and storage resources (as depicted in Figure 2.1(a)). These servers run standard operating systems and software libraries to manage their resources and are interconnected through a network of switches and routers [27]. Datacenters are often spread across a large geographical area or even multiple global sites. Additionally, to enhance reliability and efficiency, datacenters deploy backup power supplies and cooling systems.

**Network.** Datacenter servers primarily communicate with each other using Remote Procedure Calls (RPCs). Each server is equipped with a Network Interface Card (NIC) that connects it to the datacenter network fabric. These servers employ standard transport layer protocols such as TCP/IP or RDMA (Remote Direct Memory Access) to send messages via the NICs. While protocols like TCP/IP enable send-receive (two-sided) message exchanges, RDMA-based technologies provide both two-sided and direct one-sided messages, enabling direct memory access to remote servers. In this thesis, we focus primarily on RDMA-based networking due to the significance of

Figure 2.1: The Datacenter Architecture

RDMA's one-sided API, particularly in the context of exploring disaggregated memory, which is discussed in subsequent sections.

**Failure Model.** Failures can occur in any part of the datacenter. For this thesis, we have adopted a fail-stop failures model [184], where a process or server is assumed to have failed without exhibiting *Byzantine* behavior. Additionally, we consider a partially synchronous network model [63], where message transmission latency has an upper limit, albeit unknown in advance. This model strikes a balance between fully synchronous (where message delays and processing times are strictly bounded) and fully asynchronous (where there are no timing assumptions) network models. It further acknowledges the practical constraints of real-world networks, where messages may experience variable delays due to factors like network delays, system load, and other unpredictable factors.

#### 2.1.1 Recovery

Failures disrupt datacenter servers, tapering their ability to respond to service requests (Availability). Recovery is the mechanism through which architects maximize availability in the datacenter. For instance, high availability consequently ensures responsiveness even amid server failures in the datacenter. Recovery is challenging, as it requires additional measures.

**Durability.** First, it's essential to store application data in a fault-tolerant manner to prevent permanent loss (Durability) '[30, 100]. Architects typically deploy two techniques for durable data storage in the datacenter: *persistence* and *replication* [30, 193, 65, 96, 97, 76]. With persistence, data is retained in a persistent storage medium like a Hard-Disk, while with replication, data is duplicated across multiple servers. In the case of persistence, the application can restart the failed server while

temporarily blocking other servers. Conversely, replication allows the failed portion of the application to migrate to an active server and continue serving client requests [40, 135, 77, 202, 198].

There are also various replication approaches, including two-phase commit [30, 31, 94], primary-backup replication [39, 14, 202, 198], and quorum-based replication [133, 140, 170, 21, 116]. The selection of the best approach depends on the real world setting and the application requirements.

**Failure Atomicity.** Second, recovery mandates failure atomcity [30, 69, 194], because, just like data, computational logic also fail in the event of server failures, resulting in partial effects on the data. Recovery ensures that every client request is processed with exactly-once semantics, in all-or-nothing style, avoiding any partial effects on data (*Failure Atomicity*) [30, 29].

For example, imagine a seemingly trivial example of a banking application running on a data store. Lets assume Mary want to transfer 1000\$ to her friend Bob. When the data store receives this request, the application logic should first check if Mary has enough balance to carry out the transaction, then reduce the amount from Mary's bank account, and finally add the amount to Bob's bank account. If the server fails after the amount is deduced from Mary's bank account, the money will be lost forever. Crucially, there should be a mechanism to rollback the effects of operations executed before the failures (Failure Atomicity). Such a semantic is achieved by recovery algorithms that reinstate the data to a consistent state in execution.

Achieving such robust recovery is complex and has traditionally been tackled through two fundamental methods: *re-execution* and *logging*. This section provides a concise overview of these techniques, laying the foundation for a more detailed exploration in the following main chapters of this thesis.

Firstly, applications may choose to rerun client requests multiple times, even when faced with failures. However, not all applications can rely on this recovery approach. Specifically, only a specialized class of applications that adhere to idempotence can truly take advantage of re-execution [179, 114, 41]. It is important to note that this technique might introduce challenges to concurrency and programmability, which is why we refrain from adopting it.

Secondly, an alternative approach to failure atomicity is logging, where a set of operations is treated as executed in an all-or-nothing manner [100, 93, 160, 159]. Logging is widely accepted within the datacenter context. Applications use mechanisms such as write-ahead-logging (WAL) or checkpointing to restore or progress the application to

its last consistent state. There are two primary WAL schemes: undo logging, designed to roll back partial updates from interrupted executions, and redo logging, which rolls forward when an execution is disrupted before its completion. This atomicity-based recovery plays a pivotal role in important programming models such as transactions in the datacenter.

**End-to-End Correctness.** In addition to durability and failure atomcity, application must ensure the isolation between concurrent requests in the presence of failures. For instance, recovering from a failures should not lead to incorrect execution of other requests. These correctness properties are typically defined as a part of the consistency models in the datacenter. We will discuss consistency models in the Section 2.3.

## 2.2 Emerging Memory Systems

In this thesis, we use two types of emerging memory technologies: non-volatile memory (NVM) and disaggregated memory (DM). In this section, we provide an overview of their fault-tolerant attributes and impact on datacenter architecture. First, we discuss nonvolatile memory, outlining its impact on persistence-based recovery (§2.2.1), and second, we discuss memory disaggregation and its impact on high availability in data stores (§2.2.2).

#### 2.2.1 Non-Volatile Memory (NVM)

In this section, we outline our assumptions about non-volatile memory (NVM) technology we use in this thesis.

Various classes of NVMs are available in the market: Phase-change memory (PCM), resistive random-access memory (ReRAM), or magnetoresistive RAM (MRAM), and ferroelectric RAM (FRAM). In this thesis, we focus on PCM-based NVM, specifically Intel's Optane DC Persistent Memory Module (or just "Optane DC PMM") which can provide up to 512GB memory capacity. Crucially, these new memory devices retain data even when power is interrupted (persistent), therefore, they can be used as a fast alternative to disk-based storage, or as an additional memory tier between volatile memory and disk-based storage [212, 112].

Typical disk-based storage in the datacenter, such as hard disk drives (HDD) or solid state disk drives (SDD), provides terabytes of capacity, but can only be accessible through the CPU's I/O (Input/Output) interface which has significantly high access

latency, typically ranging from a hundreds of microseconds to tens of milliseconds. Conversely, NVM provides fast persistent memory accessible within a few hundred nanoseconds, which is on par with regular volatile memory access latency [212, 112].

For instance, PMEM latency of sequential reads (random reads) and regular writes is 179 ns (304 ns) and 94 ns respectively, while its 81 ns and 86 ns for DDR5-based DRAM [112]. Additionally, Optane DC PMM provides caching within the NVM, further minimizing these latencies. This shows that NVM, though still at an early stage, can be purposefully leveraged as an alternative to slow storage devices. As we will discuss later in Chapter 3, this fast persistence can be used to enable efficient fault tolerance techniques that rely on persistence for recovery.

#### 2.2.2 Disaggregated Memory (DM)

The other memory technology used in this thesis is disaggregated memory (DM). Memory disaggregation decouples memory from traditional monolithic servers, enabling memory sharing across server boundaries [191, 15, 145, 47, 164, 205]. State-of-the-art hardware technologies, RDMA or CXL [90, 139], provide network support for connecting passive memory to the servers' CPU cores through either I/O subsystems or direct load/store interface respectively. After careful consideration, we have chosen an RDMA-based passive disaggregated memory system for this thesis. This choice is based on RDMA's sub-microsecond latency with 100Gbps technology, offering flexibility in programming (this latency is anticipated to decrease further with the adoption of 400G networks and faster PCIe devices in the near future). On the contrary, CXL-based systems are still in the early development stage, and architects are unaware of potential performance challenges and programming complexities [9, 139]. At the time of this thesis, there is only one CXL-based product readily available on the market [183].

In this thesis, we assume an RDMA-based disaggregated memory system. In our setting, each server is dedicated to either compute or memory, referred to as compute node or memory node, respectively. Each compute node consists of a CPU and a small amount of local memory (a few MBs) for caching purposes and other OS functionalities, while the program memory is stored entirely in the memory nodes, typically holding terabytes of data. All compute nodes can access and share each memory node through RDMA connections established over a 100Gbps Ethernet network (i.e., RoCE).

A typical memory node neither has a CPU nor runs any software like OS; Therefore, memory is accessed only through the Network Interface Card (NIC) or special hardware.

Figure 2.2: Consistency Models

However, since there are no actual memory nodes available in the market, in this thesis, we use regular servers for memory nodes while keeping their CPU idle, which does not violate our assumptions. In addition, RDMA offers a rich one-sided API that includes Read, Write, and Read-Modify-Write (RMW) commands, which is order of magnitude faster than traditional two-sided Remote Procedure Calls (RPCs).

Figure 2.1(c) illustrates the architecture we have discussed so far. Later, in Chapter 4, we leverage this RDMA-based disaggregated memory to achieve efficient fault tolerance in the datacenter.

## 2.3 Consistency Models

A consistency model plays a crucial role in abstracting the end-to-end correctness of the underlying architecture to application programmers, simplifying the complexity of low-level primitives. This implementation-agnostic nature allows programmers to reason about the correctness of their programs without delving into low-level implementation aspects like concurrency, replication, and recovery. Historically, consistency models have been pivotal in datacenters, acting as a contract between architects and programmers [5, 79].

In this section, we discuss several consistency models that are relevant to the discussion of this thesis. We start the discussion with traditional (shared-memory) consistency models: linearizability, sequential consistency, and release consistency [5, 79, 80]. These consistency models are the essence of high concurrency present in

today's CPUs.

#### 2.3.1 Linearizability

Linearizability [108] is the most intuitive consistency model for programmers, ensuring that concurrent operations appear as if they occurred instantaneously at a single point in time (linearization point) in relation to other operations. This means that the effect of each operation becomes atomically visible in real-time somewhere between its invocation and response. Typically, coherence protocols deployed in modern CPUs are variants of linearizability. However, for shared-memory programs, linearizability represents a stricter consistency model.

#### 2.3.2 Sequential Consistency

Sequential consistency (SC) [132] guarantees that the execution of operations on shared data appears in some sequential order (total order) that respects the program order for each concurrent operator. As opposed to linearizability, SC does not enforce the real-time order, striking a good balance between performance and programmability in shared-memory systems. A successor of SC dubbed Total Store Order (TSO) found in Intel's X86 CPUs further maximum performance by relaxing local happens-before order, specifically reads-after-writes order. Such models, however, complicates programmability and will be absorbed by more weaker models we discuss later.

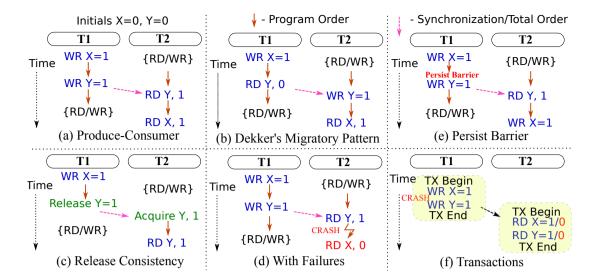

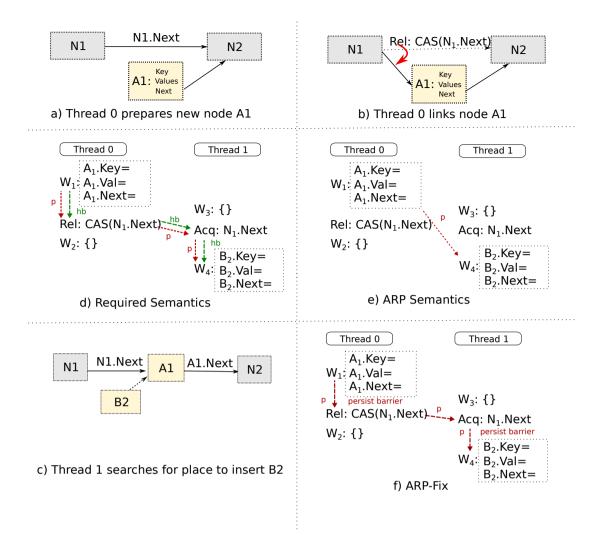

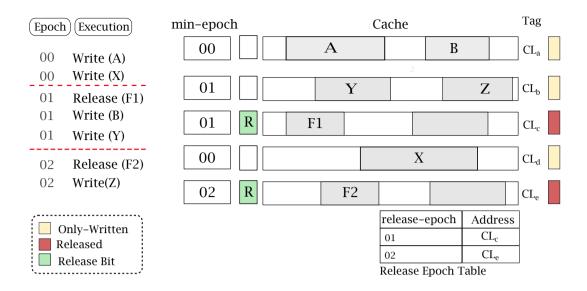

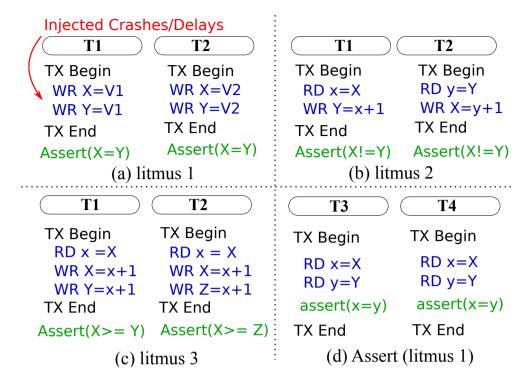

Consistency semantics are typically discerned through well-constructed litmus tests. Consider the litmus tests depicted in Figure 5.1(a) and (b). These tests exemplify Sequential Consistency (SC) semantics with two prevalent shared-memory programming patterns: producer-consumer (Figure 5.1(a)) and migratory patterns with Dekker's algorithm (Figure 5.1(b)).

In these litmus tests, SC rigorously enforces both program order and total order. For instance, in the producer-consumer illustration, one thread (T1) first sets X to one, followed by setting Y to 1 to indicate the alteration in X. Until Y is assigned the value of 1, the concurrent thread T2 cannot read the updated value of X, which is 1. This mechanism aligns with the typical behavior of producer-consumer patterns, which necessitate enforcing read-to-read and write-to-write order to capture the underlying causality, which SC effectively accomplishes. Similarly, migratory litmus tests necessitate write-to-reads order to ensure critical sections, a requirement prevalent in synchronization algorithms like Dekker's, which SC strictly enforces.

One advantage of SC is that programmers are oblivious to the underlying ordering. However, SC is somewhat strict in enforcing all local happens-before order (program order), which might not be as performance-friendly. However, well-written (i.e., race-free) shared memory programs using proper synchronization do not require such tight ordering [6, 82]. The golden rule is that operations should be consistent by synchronization boundaries. This understanding has led to the development of more performant models, such as release consistency, which we will describe next.

#### 2.3.3 Release Consistency

Release Consistency (RC) [82] is a fundamental shared memory consistency model that guarantees that if the programmer annotates all synchronization accesses, it mimics SC semantics [6, 82, 78]. For architects, RC is essential, as it allows reordering regular accesses, relaxing the local happens-before order (as opposed to SC). Additionally, RC provides one-sided synchronization accesses that can be distinguished from regular accesses, allowing for a more relaxed happens-before order between regular access and synchronization accesses.

Languages like C++ enable programmers to expose RC through language-level consistency models, such as the "Sequential Consistency for Data Race Free" (DRF-SC) [153, 36], which captures the semantics of RC-like synchronization accesses. Additionally, CPU vendors like ARM provide RC semantics in the ISA. For instance, ARMv8 has two one-sided barrier instruction, release and acquire, that can be used to annotate synchronization load/store accesses.

Consider the example in Figure 5.1(c), which provides the RC-compatible (annotated) version of the producer-consumer litmus test discussed earlier. In this scenario, the release store operation in T1 enforces the order with previous loads and stores, but not with subsequent instructions. Similarly, the acquire operation in T2 enforces the order with following loads and stores, but not with preceding instructions. It is important to note that operations before the release, as well as after acquire, can potentially be reordered, although that is not depicted in the example.

**Formal Model.** In the following, we provide a simplistic RC memory model for this thesis.

We use the following notation for memory events:

•  $\mathbf{M_x^i}$ : a memory operation (of any type) to address x from (hardware) thread i. The operation can be further specified as a read:  $R_x^i$ , a write  $W_x^i$  or with an identifier (e.g.

$M1_r^i$

- $Rel_x^i$ : a release (release write or release-RMW) to address x from thread i.

- $Acq_x^i$ : an acquire (acquire read or acquire-RMW) to address x from thread i.

We use the following notation for ordering memory events:

- $\mathbf{M}_{\mathbf{x}}^{\mathbf{i}} \xrightarrow{\mathrm{po}} \mathbf{M}_{\mathbf{v}}^{\mathbf{i}}$ :  $M_{\mathbf{x}}^{i}$  precedes  $M_{\mathbf{v}}^{i}$  in program order.

- $\mathbf{M_x^i} \xrightarrow{\mathrm{hb}} \mathbf{M_y^j}$ :  $M_x^i$  precedes  $M_y^j$  in the global history of memory events, which we refer to as happens-before order  $(\xrightarrow{\mathrm{hb}})$ .

- $\mathbf{Rel}_{\mathbf{x}}^{\mathbf{i}} \xrightarrow{\mathrm{sw}} \mathbf{Acq}_{\mathbf{x}}^{\mathbf{j}}$ :  $Acq_{x}^{j}$  synchronizes with the  $Rel_{x}^{i}$ , i.e.,  $Acq_{x}^{j}$  reads the value from  $Rel_{x}^{i}$  and  $i \neq j$ .

We formalize Release Consistency using the following rules:

- $\succ$  **Release one-way barrier semantics.** A memory access that precedes a release in program order appears before the release in happens-before:  $M_x^i \xrightarrow{\text{po}} Rel_y^i \Rightarrow M_x^i \xrightarrow{\text{hb}} Rel_y^i$ .

- $\succ$  **Acquire one-way barrier semantics.** A memory access that follows an acquire in program order appears after the acquire in happens-before:  $Acq_y^i \xrightarrow{po} M_x^i \Rightarrow Acq_y^i \xrightarrow{hb} M_x^i$ .

- $\succ$  **Program order address dependency.** Two memory accesses to the same address ordered in program order preserve their ordering in happens-before:  $M1_x^i \xrightarrow{\text{po}} M2_x^i \Rightarrow M1_x^i \xrightarrow{\text{hb}} M2_x^i$ .

- $\succ$  **Release synchronizes with acquire.** A release that synchronizes with an acquire appears before the acquire in happens-before:  $Rel_v^i \xrightarrow{\text{sw}} Acq_y^j \Rightarrow Rel_v^i \xrightarrow{\text{hb}} Acq_y^j$ .

- $\succ$  **RMW-atomicity axiom.** An RMW appears atomically (consecutively) in happensbefore:  $R_x^i \xrightarrow{RMW} W_x^i \Rightarrow R_x^i \xrightarrow{hb} W_x^i$  and there can be no memory operation from any thread  $M_y^j$  such that  $R_x^i \xrightarrow{hb} M_y^j \xrightarrow{hb} W_x^i$ .

- $\succ$  **Read value axiom.** A read to an address always reads the latest write to that address before the read in happens-before: if  $W_x^j \xrightarrow{\text{hb}} R_x^i$  (and there is no other intervening write  $W_x^k$  such that  $W_x^j \xrightarrow{\text{hb}} W_x^k \xrightarrow{\text{hb}} R_x^i$ ), the read  $R_x^i$  returns the value written by the write  $W_x^j$ .

# 2.4 Memory Persistency Models

Traditional shared-memory consistency models that we have discussed are primarily designed to handle concurrent accesses in the presence of caching but are not explicitly designed to handle failures. Therefore, these models are not sufficient to ensure end-to-end correctness of new technologies like NVM.

As an example, consider the litmus test in Figure 5.1(e), depicting the producer-consumer pattern under SC semantics but with potential failures. Suppose that T2 reads Y's updated value as part of the consumer, but the server crashes before it can complete the subsequent operation. After restarting, T2 resumes execution. In this situation, T2 could pathologically read the initial value of X (or zero) because X's value, which is kept in either cache or memory, is lost, revealing that SC is insufficient to handle such failures.

Persistence models [175, 87] are a new class of consistency models that are specifically designed to address the complexities introduced by persistent memory and guarantee the desired correctness properties, including recovery even in the face of failures. In this section, we briefly look at the concept of persistency models.

Memory persistency is still an active research area. Persistence models guarantee the correctness of application programs with persistent memory accesses [88]. In particular, these models govern the memory order that ensures correct execution and recovery in the presence of failures. However, these new models have severe implications on performance and programmability [37, 165].

Strict persistency models either bypass CPU caches using non-temporal instruction or use a new instruction to durably send every store to NVM before being released into CPU caches, which can significantly deteriorate concurrency and performance [87, 175]. On the other hand, relaxing the persist order, though performant, can severely complicate correctness and programmability [175]. The complexity of the latter approach is significantly higher, so architects have opted to go with strict persistency models [87].

Architects must carefully examine new persistence models with minimal ordering to unleash fast persistence in NVM, a crucial factor in designing efficient fault tolerance in datacenters. We will discuss more about the challenges in memory persistency in Chapter 3.

# 2.5 Transactional Consistency Models

Transactions combine multiple standard operations, such as insertions, deletions, updates, and search (reads), into atomic units. SS is subsequently designed to maintain the atomic view of data under any circumstance, ensuring end-to-end correctness, including recovery of transactions in the event of failures.

Consider the final example shown in Figure 5.1(f). In this example, we use the same producer-consumer pattern that we used with sequential consistency (SC) but

as a transaction. Application programmers can annotate a group of operations as a transaction with  $tx\_begin$  and  $tx\_end$ , and the atomicity of the transaction is preserved in the presence of failures. Now assume that the server crashes during execution; as shown in the figure, SS guarantees that T2 sees either the old values of X and Y (all zeros) or new values (all ones), but nothing in between.

# 2.5.1 Strict Serializability

Strict serializability (SS) [174, 187] is a rigorously formalized consistency model widely used in production data stores. It operates as a transactional consistency model, offering strong ACID (Atomicity, Consistency, Isolation and Durability) properties in the presence of failures.

In formal terms, *serializability* ensure that all transactions appear to occur in total order (i.e., serial) as if they were executed one at a time in isolation. Serializability, however, does not guarantee real-time ordering. In contrast, a stronger version of serilizability – Strict Serializability(SS) – ensures that the effects of transactions appear atomically in real time. In this section, we provide a formalization of *strict serializability* with two important properties: total ordering (i.e., serializability) and real-time ordering.

#### 2.5.1.1 Serializability

Serializability [31, 174, 7] guarantees that the outcome of concurrent transactions is equivalent to a serial execution (total order) of those transactions, ensuring that the final state of the database remains consistent and reflects a valid sequential order of execution. In this thesis, we use Adya's history-based formalism of serializability [7, 53].

**Definition 2.5.1.** A history H over a set of transactions consists of two parts: (i) a partial order of events E that reflects the operations (e.g., read, write, abort, commit) of those transactions; and (ii) a version order, <<, that totally orders committed object versions.

**Definition 2.5.2.** We consider three kinds of direct read/write conflicts:

- **Directly write-depends**  $T_i$  writes a version of x and  $T_j$  writes the next version of x ( $T_i \xrightarrow{ww} T_j$ )

- **Directly read-depends**  $T_i$  writes a version of x that  $T_j$  then reads  $(T_i \xrightarrow{wr} T_j)$

- **Directly anti-depends**  $T_i$  reads a version of x, and  $T_j$  writes the next version of x  $(T_i \xrightarrow{rw} T_j)$

**Definition 2.5.3.** We say that  $T_j$  start-depends on  $T_i$  (denoted as  $T_i \xrightarrow{sd} T_j$ ), if  $c_i <_t b_j$ , where  $c_i$  denotes  $T_i$ 's commit timestamp and  $b_j$   $T_j$ 's start timestamp, i.e., if  $T_j$  starts after  $T_i$  commits.

**Definition 2.5.4** (Direct Serialization Graph). Each node in the direct serialization graph DSG(H) arising from a history H corresponds to a committed transaction in H. Directed edges in DSG(H) correspond to different types of direct conflicts. There is a read/write/anti-dependency edge from transaction  $T_i$  to transaction  $T_j$  if  $T_j$  directly read/write/antidepends on  $T_i$ .

**Definition 2.5.5.** The Started-ordered Serialization Graph SSG(H) contains the same nodes and edges as DSG(H) along with start-dependency edges.

**Definition 2.5.6.** Adya's thesis identifies the following phenomena:

- **G0:** Write Cycles DSG(H) contains a directed cycle consisting entirely of write-dependency edges.

- G1a: Dirty Reads H contains an aborted transaction T<sub>i</sub> and a committed transaction T<sub>j</sub> such that T<sub>j</sub> has read the same object (maybe via a predicate) modified by T<sub>i</sub>.

- **G1b:** Intermediate Reads H contains a committed transaction  $T_j$  that has read a version of object x written by transaction  $T_i$  that was not  $T_i$ 's final modification of x.

- **G1c:** Circular Information Flow DSG(H) contains a directed cycle consisting entirely of dependency edges.

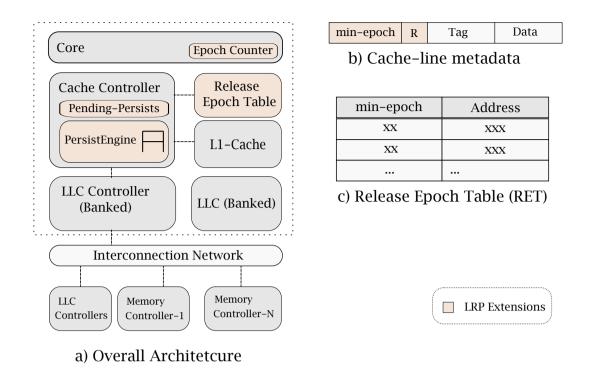

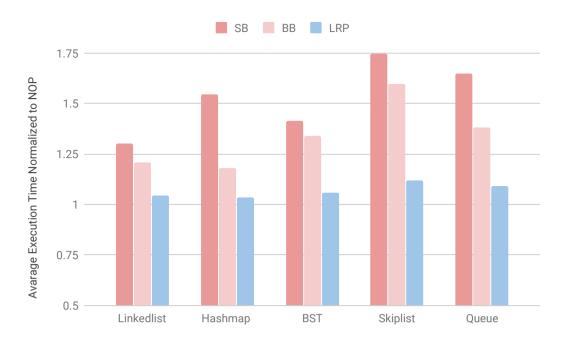

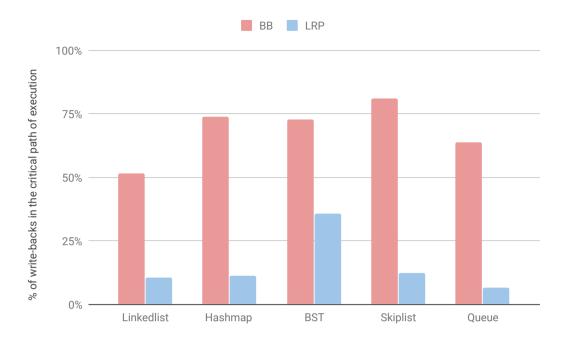

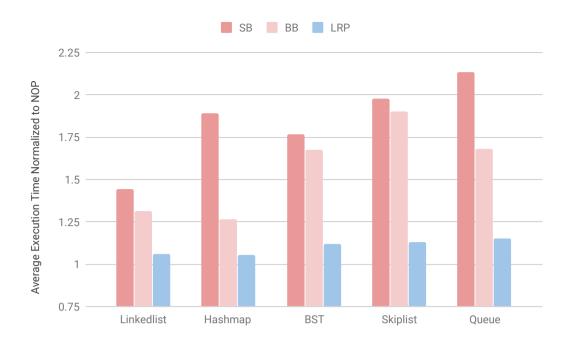

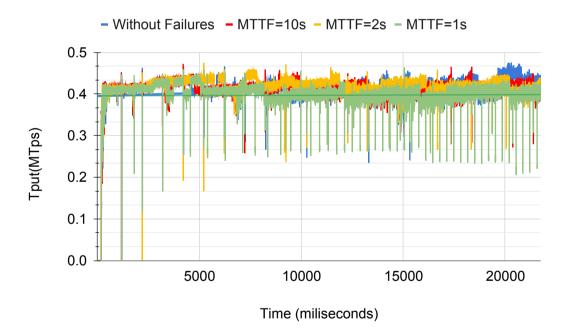

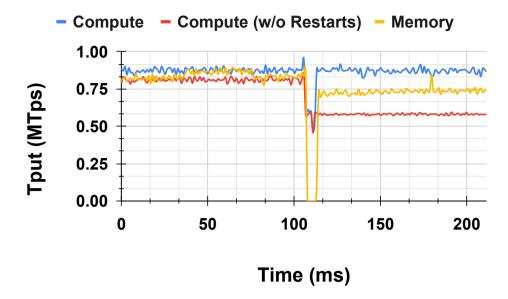

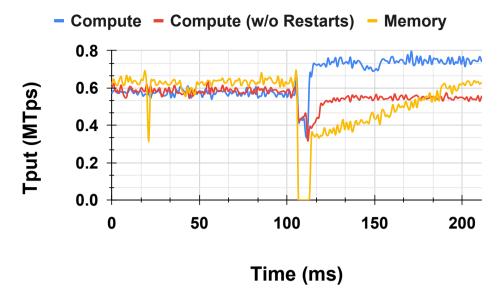

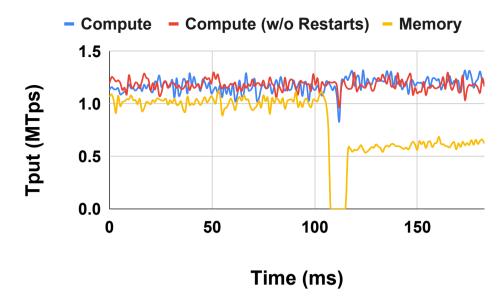

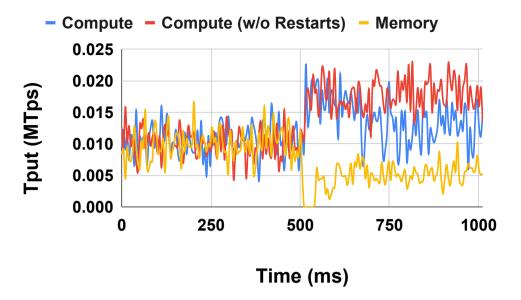

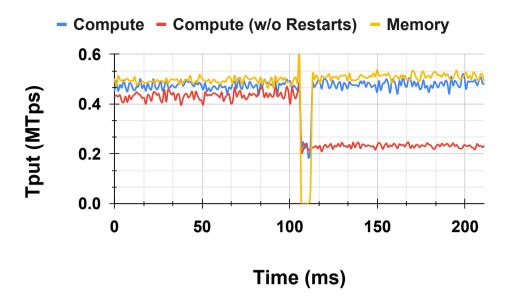

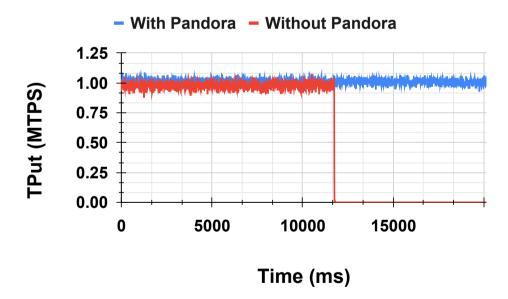

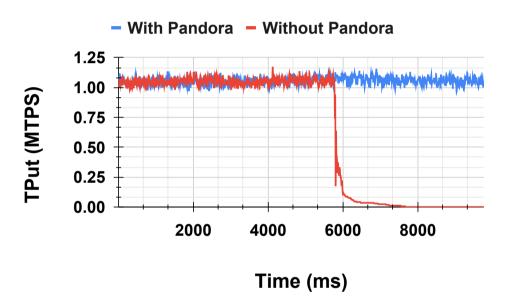

- **G1**:  $G1a \vee G1b \vee G1c$ .