## Evidence-enabled verification for the Linux kernel

by

## Ahmed Yousef Tamrawi

A dissertation submitted to the graduate faculty in partial fulfillment of the requirements for the degree of  ${\tt DOCTOR\ OF\ PHILOSOPHY}$

Major: Computer Engineering

Program of Study Committee:

Suraj C. Kothari, Major Professor

Srikanta Tirthapura

Manimaran Govindarasu

Yong Guan

Robyn R. Lutz

Iowa State University

Ames, Iowa

2016

Copyright © Ahmed Yousef Tamrawi, 2016. All rights reserved.

# **DEDICATION**

I would like to dedicate this thesis to my parents, sisters, wife, son Yusuf, and to my daughter Nawwar without whose support I would not have been able to complete this work. I would also like to thank my friends and family for their loving guidance during the writing of this work.

# TABLE OF CONTENTS

| LIST ( | OF TABLES                                                                      | vii  |

|--------|--------------------------------------------------------------------------------|------|

| LIST ( | OF FIGURES                                                                     | viii |

| ACKN   | IOWLEDGEMENTS                                                                  | X    |

| ABST   | RACT                                                                           | xi   |

| CHAP   | TER 1. OVERVIEW                                                                | 1    |

| 1.1    | State-Of-The-Art Formal Verification Techniques                                | 1    |

| 1.2    | A Different Approach to Software Verification                                  | 2    |

| 1.3    | Thesis Contribution                                                            | 4    |

| 1.4    | Thesis Organization                                                            | 4    |

| CHAP   | TER 2. MAJOR CHALLENGES AND MOTIVATION                                         | 6    |

| 2.1    | Challenges Overview                                                            | 6    |

| 2.2    | Path Explosion                                                                 | 7    |

| 2.3    | Inter-procedural Analysis                                                      | 8    |

| 2.4    | Feasibility Analysis                                                           | 8    |

| 2.5    | Pointer Analysis                                                               | 9    |

| 2.6    | A Concrete Example to Illustrate the Need for Verification-Critical Evidence . | 10   |

| СНАР   | TER 3. LITERATURE REVIEW                                                       | 13   |

| 3.1    | Data Races and Deadlocks Detection                                             | 13   |

| 3.2    | Static Memory Leak Detection                                                   | 15   |

| 3.3    | Evidence-Enabled Verification                                                  | 16   |

| 3.4    | Linux Kernel Verification                                                      | 17   |

| CHAP | PTER 4. VISUAL MODELS AS VERIFICATION-CRITICAL EVI- |    |

|------|-----------------------------------------------------|----|

| DE   | ENCE                                                | 19 |

| 4.1  | Matching Pair Graph (MPG)                           | 20 |

| 4.2  | Memory Taint Graph (MTG)                            | 21 |

| 4.3  | Points-To Graph (PtG)                               | 22 |

| 4.4  | Event Flow Graph (EFG)                              | 24 |

| 4.5  | Enabling Technology & Interactive Reasoning         | 24 |

| CHAP | PTER 5. EVENT FLOW GRAPH FOR PROGRAM COMPREHEN-     |    |

| SIC  | ON                                                  | 27 |

| 5.1  | Introduction                                        | 27 |

| 5.2  | Motivation                                          | 29 |

|      | 5.2.1 A Linux Example                               | 29 |

|      | 5.2.2 Loop Call Graph                               | 31 |

| 5.3  | Application: Verify Pairing                         | 32 |

|      | 5.3.1 Correct Lock-Unlock Pairing                   | 33 |

|      | 5.3.2 Lock-Unlock Pairing Bug                       | 34 |

|      | 5.3.3 Pairing Includes Loop                         | 34 |

|      | 5.3.4 An EFG Quirk                                  | 35 |

|      | 5.3.5 Comprehension-Driven Verification             | 36 |

| 5.4  | Application: Find Vulnerability                     | 37 |

| 5.5  | EFG Tool Support                                    | 40 |

|      | 5.5.1 Programmed EFG Construction                   | 41 |

|      | 5.5.2 Interactive EFG Construction                  | 42 |

|      | 5.5.3 Gradual EFG Expansion                         | 43 |

| 5.6  | Event Flow Graph                                    | 44 |

|      | 5.6.1 Step 1: Marking Event Nodes                   | 44 |

|      | 5.6.2 Step 2: T-Irreducible Graph                   | 44 |

|      | 5.6.3 Step 3: Non-Event Condensation Graph          | 45 |

|      | 5.6.4 Step 4: Event Condensation Graph              | 46 |

|      | 5.6.5 Step 5: Condensed EFG                                     | 46         |

|------|-----------------------------------------------------------------|------------|

|      | 5.6.6 Step 6: Final EFG                                         | 46         |

|      | 5.6.7 Algorithm Complexity                                      | 46         |

|      | 5.6.8 Observations                                              | 46         |

|      | 5.6.9 EFG Minimality                                            | 48         |

| 5.7  | An Assessment of EFGs                                           | 50         |

|      | 5.7.1 An Empirical Study                                        | 50         |

|      | 5.7.2 Quantitative Assessment of EFGs                           | 51         |

| 5.8  | Related Work                                                    | 53         |

| 5.9  | Conclusion                                                      | 53         |

| CHAP | TER 6. L-SAP: EVIDENCE-ENABLED LINUX VERIFICATION               |            |

| FO   | R LOCK/UNLOCK PAIRING ANALYSIS                                  | 55         |

| 6.1  | Introduction                                                    | 55         |

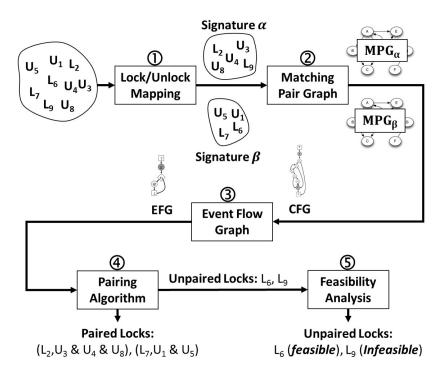

| 6.2  | L-SAP Approach                                                  | 58         |

|      | 6.2.1 Step 1: Lock/Unlock Mapping                               | 60         |

|      | 6.2.2 Step 2: Matching Pair Graph                               | 60         |

|      | 6.2.3 Step 3: Event Flow Graph                                  | 61         |

|      | 6.2.4 Step 4: Pairing Algorithm                                 | <b>62</b>  |

|      | 6.2.5 Step 5: Feasibility Check for Potential-Error Paths       | 65         |

| 6.3  | Evidence-Enabled Verification Using $\mathcal{L}	ext{-SAP}$     | 67         |

|      | 6.3.1 Automated Verification                                    | 67         |

|      | 6.3.2 Interactive Verification                                  | 69         |

|      | 6.3.3 Visual Models for Evidence                                | 69         |

|      | 6.3.4 Team Verification                                         | 71         |

| 6.4  | Empirical Evaluation & Results                                  | 72         |

|      | 6.4.1 $\mathcal{L}$ -SAP: The Lock/Unlock Pairing Analysis Tool | <b>72</b>  |

|      | 6.4.2 Case Studies & Qualitative Assessment of Visual Models    | 75         |

|      | 6.4.3 Current Limitations of $\mathcal{L}$ -SAP                 | <b>7</b> 9 |

| 6.5  | Conclusions                                                     | 30         |

| CHAP   | TER '             | 7. $\mathcal{M}$ -SAP: EVIDENCE-ENABLED LINUX VERIFICATION |     |

|--------|-------------------|------------------------------------------------------------|-----|

| FO     | R ALI             | LOCATION/DEALLOCATION PAIRING ANALYSIS                     | 82  |

| 7.1    | Introd            | luction                                                    | 82  |

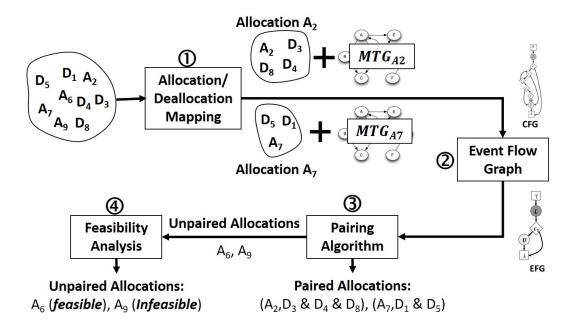

| 7.2    | $\mathcal{M}$ -SA | AP Approach                                                | 85  |

|        | 7.2.1             | Step 1: Allocation/Deallocation Mapping                    | 87  |

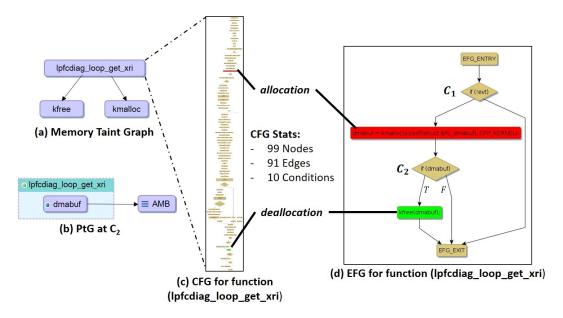

|        | 7.2.2             | Step 2: Event Flow Graph                                   | 95  |

|        | 7.2.3             | Step 3: Allocation/Deallocation Pairing                    | 95  |

|        | 7.2.4             | Step 4: Feasibility Check for Potential-Error Paths        | 99  |

| 7.3    | Enabl             | ing Evidence for Human-Machine Collaboration               | 100 |

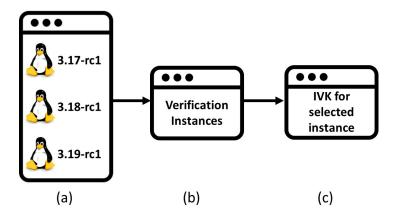

|        | 7.3.1             | Creating Verification Instances                            | 100 |

|        | 7.3.2             | Instance Verification Kit (IVK)                            | 101 |

| 7.4    | Empir             | rical Evaluation & Results                                 | 101 |

|        | 7.4.1             | Implementation and Experimental Setup                      | 101 |

|        | 7.4.2             | $\mathcal{M}	ext{-SAP}$ : Experimental Results             | 102 |

|        | 7.4.3             | Case Studies & Qualitative Assessment of Visual Models     | 103 |

|        | 7.4.4             | Current Limitations of $\mathcal{M}\text{-SAP}$            | 107 |

|        | 7.4.5             | Off Limits Allocation Instances                            | 109 |

| 7.5    | Concl             | usions                                                     | 109 |

| CHAP   | TER 8             | 8. CONCLUSIONS AND FUTURE DIRECTIONS                       | 111 |

| ртрт т | OCDA              | DUV                                                        | 119 |

# LIST OF TABLES

| Table 5.1 | mutex/spin Locks/Unlocks                                                              | 51  |

|-----------|---------------------------------------------------------------------------------------|-----|

| Table 5.2 | Linux kernel CFG and EFG stats                                                        | 52  |

| Table 5.3 | A comparison of CFG vs. EFG                                                           | 52  |

| Table 6.1 | Lock/Unlock function calls for mutex/spin synchronization mechanisms                  |     |

|           | in Linux kernel                                                                       | 58  |

| Table 6.2 | Linux Kernel Artifacts                                                                | 73  |

| Table 6.3 | Comparison of $\mathcal{L}\text{-SAP}$ and LDV                                        | 74  |

| Table 6.4 | Breakdown of instances in $\mathcal{C}3$ category across different limitation facrtos | 80  |

|           |                                                                                       |     |

| Table 7.1 | Linux Kernel (v 3.17-rc1) Artifacts                                                   | 102 |

| Table 7.2 | Allocation/deallocation pairing results on Linux kernel version (3.17-rc1)            | 103 |

|           |                                                                                       |     |

# LIST OF FIGURES

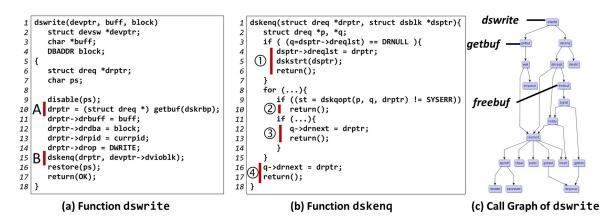

| Figure 2.1  | An example to illustrate the need for evidence to reason about the pos- |    |

|-------------|-------------------------------------------------------------------------|----|

|             | sibility of a memory leak in the function dswrite                       | 10 |

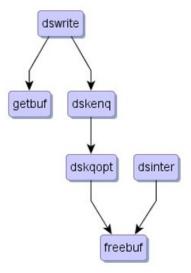

| Figure 4.1  | MPG evidence for the allocated memory in dswrite                        | 20 |

| Figure 4.2  | MTG evidence for the allocated memory in dswrite                        | 22 |

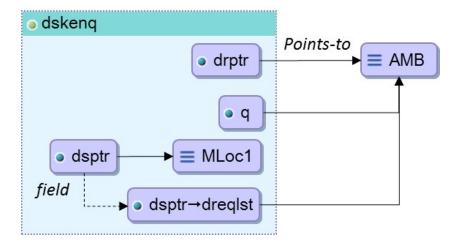

| Figure 4.3  | PtG evidence for the allocated memory in dswrite at line 4 of function  |    |

|             | dskenq                                                                  | 23 |

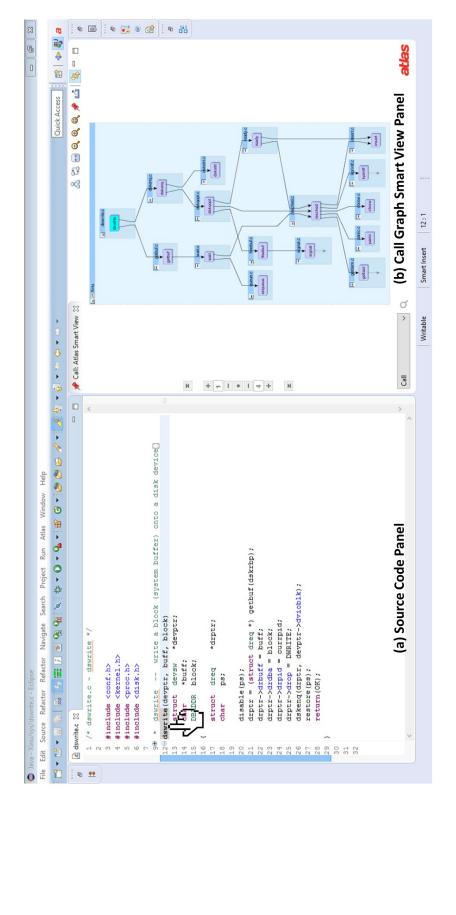

| Figure 4.4  | Call graph smart view for selected function dswrite                     | 26 |

| Figure 5.1  | CFG and EFG for the function hwrng_attr_current_store                   | 30 |

| Figure 5.2  | Loop Call Graph for TimSort Algorithm                                   | 32 |

| Figure 5.3  | CFG with marked loop headers                                            | 33 |

| Figure 5.4  | Loop-based EFG                                                          | 33 |

| Figure 5.5  | An example of correct pairing                                           | 34 |

| Figure 5.6  | A bug discovery using EFGs                                              | 35 |

| Figure 5.7  | EFG points to a missing lock preceding a loop                           | 36 |

| Figure 5.8  | An EFG Quirk                                                            | 37 |

| Figure 5.9  | Taint flows from the secret and the user-controlled input               | 39 |

| Figure 5.10 | EFG with respect to Thread.sleep(25)                                    | 41 |

| Figure 5.11 | EFG with respect to Thread.sleep(25) and data flow events               | 42 |

| Figure 5.12 | Gradual EFG Expansion Interface                                         | 43 |

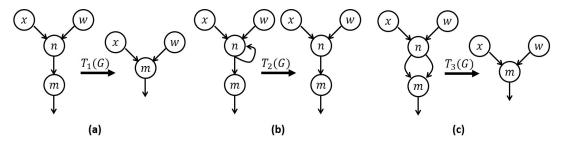

| Figure 5.13 | T-irreducible graph transformations: (a) $T_1$ , (b) $T_2$ , (c) $T_3$  | 45 |

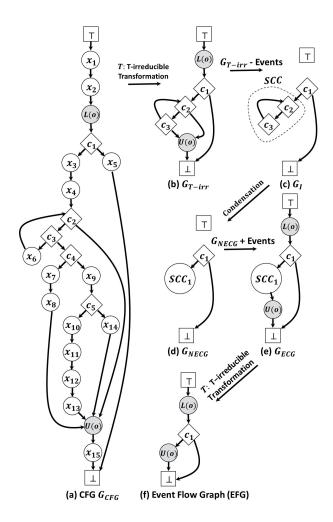

| Figure 5.14 | CFG to EFG Transformation Illustration                                  | 47 |

| Figure 5.15 | An example of irrelevant branch node $c \dots \dots \dots \dots$        | 48 |

| Figure 6.1  | An Overview of $\mathcal{L}$ -SAP Pairing Analysis                                       | 59  |

|-------------|------------------------------------------------------------------------------------------|-----|

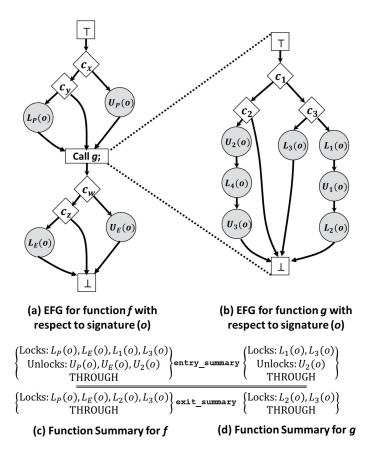

| Figure 6.2  | Compact function summaries for caller $(f)$ and callee $(g)$                             | 63  |

| Figure 6.3  | The $\mathcal{L}\text{-SAP}$ tool and the automated verification of the selected lock in |     |

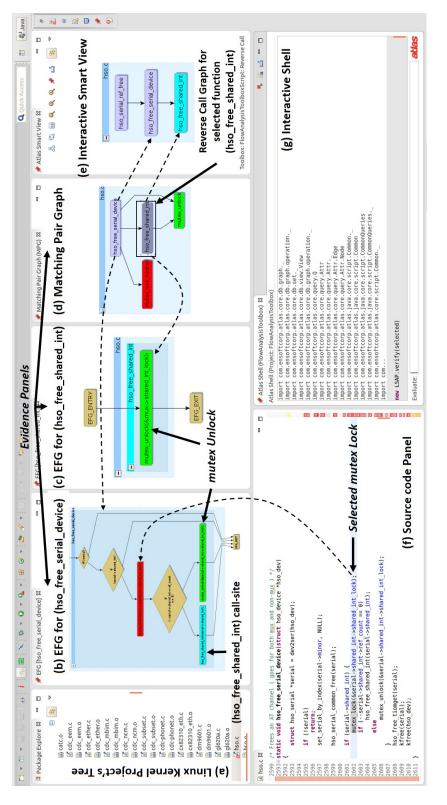

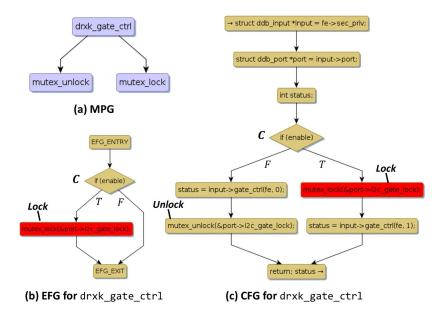

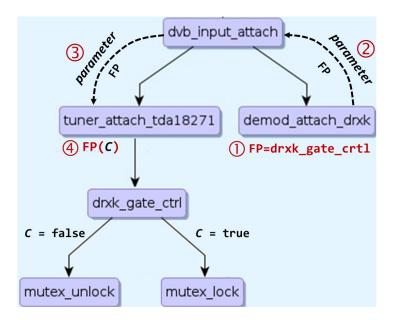

|             | function hso_free_serial_device                                                          | 68  |

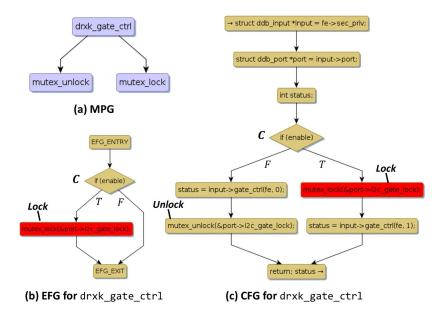

| Figure 6.4  | Visual models for drxk_gate_crtl hint to presence of calls via function                  |     |

|             | pointers                                                                                 | 71  |

| Figure 6.5  | Website hierarchy                                                                        | 72  |

| Figure 6.6  | Visual models for an automatically verified instance                                     | 76  |

| Figure 6.7  | A bug discovery using visual models                                                      | 77  |

| Figure 6.8  | Visual models for drxk_gate_crtl pointing to presence of calls via function              |     |

|             | pointers                                                                                 | 78  |

| Figure 6.9  | The augmented MPG for drxk_gate_crtl after resolving calls via function                  |     |

|             | pointers                                                                                 | 79  |

| Figure 6.10 | The EFG for function ucma_lock_files shows incorrect automatic verifi-                   |     |

|             | cation                                                                                   | 81  |

| Figure 7.1  | An Overview of $\mathcal{M}$ -SAP Pairing Analysis                                       | 86  |

| Figure 7.2  | Modifying the PtG with respect to the called function formal parameter                   |     |

|             | names                                                                                    | 93  |

| Figure 7.3  | Compact function summaries for caller $(f)$ and callee $(g)$                             | 96  |

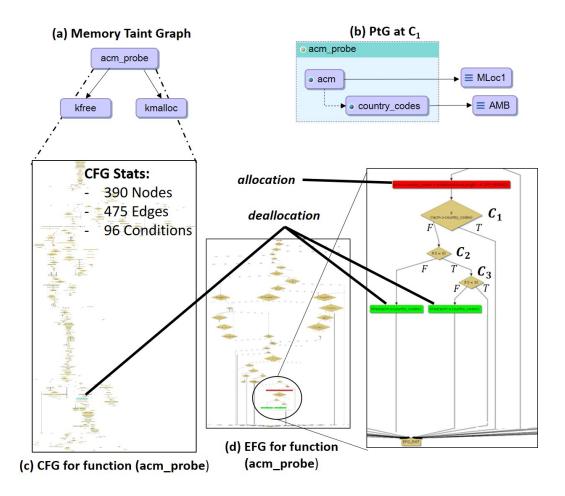

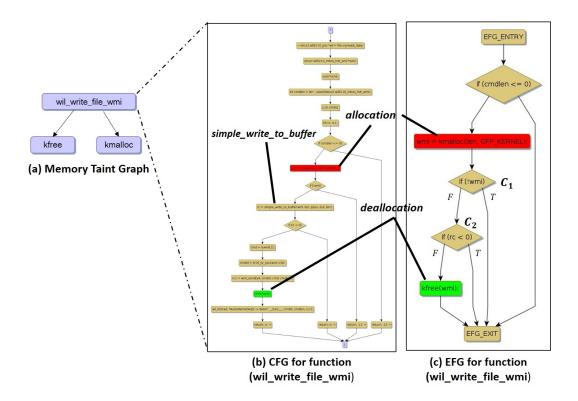

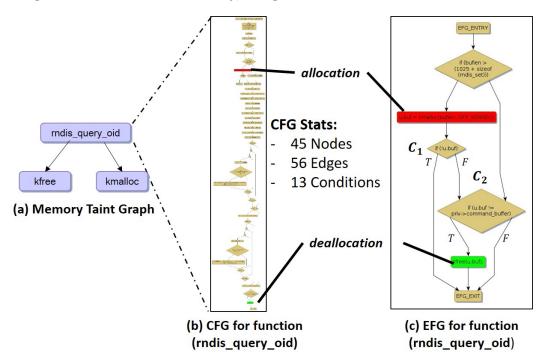

| Figure 7.4  | Visual models for an automatically verified instance                                     | 104 |

| Figure 7.5  | A bug discovery using visual models                                                      | 106 |

| Figure 7.6  | A bug discovery using visual models                                                      | 107 |

| Figure 7.7  | An Example from $C3$ category                                                            | 108 |

#### **ACKNOWLEDGEMENTS**

I would like to take this opportunity to express my thanks to those who helped me with various aspects of conducting research and the writing of this thesis. First and foremost, Dr. Suraj Kothari for his guidance, patience, inspirational thoughts, and support throughout this research and the writing of this thesis. His insights and words of encouragement have often inspired me and renewed my hopes for completing my graduate education. I would also like to thank Jeremiäs Sauceda, Jon Mathews, and Nikhil Ranade from EnSoft for their guidance and help throughout my graduate study. I would additionally like to thank my committee members for their efforts and contributions to this work: Dr. Srikanta Tirthapura, Dr. Manimaran Govindarasu, Dr. Yong Guan, and Dr. Robyn R. Lutz.

#### ABSTRACT

Formal verification of large software has been an elusive target, riddled with problems of low accuracy and high computational complexity [22,26,82,95]. With growing dependence on software in embedded and cyber-physical systems where vulnerabilities and malware can lead to disasters, an efficient and accurate verification has become a crucial need. The verification should be rigorous, computationally efficient, and automated enough to keep the human effort within reasonable limits, but it does not have to be completely automated. The automation should actually enable and simplify human cross-checking which is especially important when the stakes are high. Unfortunately, formal verification methods work mostly as automated black boxes with very little support for cross-checking.

This thesis is about a different way to approach the software verification problem. It is about creating a powerful fusion of automation and human intelligence by incorporating algorithmic innovations to address the major challenges to advance the state of the art for accurate and scalable software verification where complete automation has remained intractable. The key is a mathematically rigorous notion of verification-critical evidence that the machine abstracts from software to empower human to reason with. The algorithmic innovation is to discover the patterns the developers have applied to manage complexity and leverage them. A pattern-based verification is crucial because the problem is intractable otherwise. We call the overall approach Evidence-Enabled Verification (EEV).

This thesis presents the EEV with two challenging applications: (1) EEV for Lock/Unlock Pairing to verify the correct pairing of mutex lock and spin lock with their corresponding unlocks on all feasible execution paths, and (2) EEV for Allocation/Deallocation Pairing to verify the correct pairing of memory allocation with its corresponding deallocations on all feasible execution paths. We applied the EEV approach to verify recent versions of the Linux kernel. The results include a comparison with the state-of-the-art Linux Driver Verifi-

cation (LDV) tool, effectiveness of the proposed visual models as verification-critical evidence, representative examples of verification, the discovered bugs, and limitations of the proposed approach.

#### CHAPTER 1. OVERVIEW

With growing dependence on software in embedded and cyber-physical systems where vulnerabilities and malware can lead to disasters, efficient and accurate verification has become a crucial need for safety and cybersecurity. The challenges of verifying our software infrastructure are daunting, in part because of the complexity of the software, but also due to the sheer volume of it. The Linux kernel alone, which provides the basis for so many devices (web servers, routers, smart phones, desktops), is over 12 MLOC.

# 1.1 State-Of-The-Art Formal Verification Techniques

Formal verification has been the holy grail of software engineering research [44]. Automated software verification methods have led to advances in data and control flow analyses, and applications of techniques such as Binary Decision Diagrams (BDDs) to analyze large software [58]. However, there are two fundamental limitations: (A) a completely automated and accurate analysis encounters NP hard problems [32,79,87], and (B) formal verification methods work mostly as automated black boxes with little support for cross-checking [1,2,5,39,41,83,89,98].

The current formal verification approaches are not geared to produce evidence to empower and integrate human reasoning into the verification process. Consider the Matching Pair Verification (MPV) problem: it involves verifying the correct pairing of two events on all feasible execution paths. Specific examples of such events can be: allocation and deallocation of memory, locking and unlocking of mutex, or sensitive source and malicious sink of sensitive information in the context of cybersecurity. MPV is broadly applicable to problems of software safety and cybersecurity. State-of-the-art research and commercial tools for MPV produce either very little evidence, voluminous evidence, or evidence that refers to the intermediate representation

for the verification machinery but not to the source code. Such evidence is hard to decipher; it does not simplify cross-checking.

## 1.2 A Different Approach to Software Verification

This thesis is about a different approach to software verification. It is about targeting automation to amplify human intelligence and solve a hard problem by integrating automation with human reasoning. The verification should be automated wherever possible, and complemented by human reasoning wherever needed. The key is a mathematically rigorous notion of verification-critical evidence that the machine abstracts from software to empower human to:

(a) cross-check an automatically verified instance, and (b) complete the verification where automation falls short. The goal is to create a powerful fusion of automated evidence abstraction, evidence-based reasoning, and pattern-based automated verification. The machine and human have different strengths and weaknesses to complement each other. Even for automatically completed verification, we advocate human cross-checking. This is especially important for critical systems where failures of software can be catastrophic. The cross-checking should be simplified by automation to conserve human effort.

We propose an Evidence-Enabled Verification (EEV) approach for the MPV problem. EEV conserves human effort and empowers reasoning by facilitating it with machine-produced evidence which not only makes automation computationally efficient but also simplifies human reasoning. The automation part of the EEV approach partitions the problem into verification instances, produces the verification-critical evidence for each instance, and wherever possible performs the verification automatically. When the automatic verification falls short, the evidence provides significant help to the analyst to understand the complications surrounding the particular instance so that the analyst can decide what additional evidence to gather and what reasoning to apply to complete the verification. With a better understanding, it is sometimes possible to define a pattern to encapsulate a barrier and advance the automation so that it can address the particular barrier.

This thesis presents two EEV tools for the Linux kernel: (1)  $\mathcal{L}$ -SAP: an EEV tool for Lock/Unlock Pairing (Chapter 6) to verify the correct pairing of mutex lock and spin lock

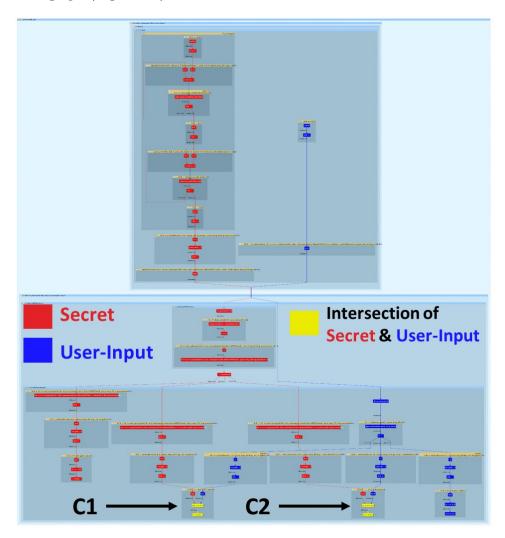

with their corresponding unlocks on all feasible execution paths, and (2)  $\mathcal{M}$ -SAP: an EEV tool for **Allocation/Deallocation Pairing** (Chapter 7) to verify the correct pairing of memory allocation with its corresponding deallocations on all feasible execution paths. The tools produce three categories of results: ( $\mathcal{C}1$ ) automatically verified instances with correct pairings, ( $\mathcal{C}2$ ) automatically verified instances with violations, i.e. a feasible path with a lock/allocation not followed by unlock/deallocation, and ( $\mathcal{C}3$ ) instances where the automated verification is inconclusive.

L-SAP produces for each verification instance the following verification-critical evidence: the Matching Pair Graph (MPG) (Section 4.1) to assist with the inter-procedural reasoning by identifying relevant functions and their interactions, and the Event Flow Graph (EFG) (Chapter 5) to assist with intra-procedural reasoning for each relevant function. Similarly, M-SAP produces for each verification instance the following evidence: the Memory Taint Graph (MTG) (Section 4.2) to assist with the inter-procedural reasoning by identifying relevant functions and their interactions, the Event Flow Graph (EFG) (Chapter 5) to assist with intra-procedural reasoning for each relevant function, and the Points-To Graph (PtG) (Section 4.3) to assist with data flow reasoning by identifying the points-to relations between the pointers of interest at different locations in source code. In addition, we have developed smart views to enable interactive reasoning where the analyst can interact visually and programmatically to augment or refine the produced evidence.

We applied the  $\mathcal{L}$ -SAP tool to verify three recent versions of the Linux operating system (i.e., 3.17-rc1, 3.18-rc1, and 3.19-rc1) with altogether 37 MLOC and 66,609 verification instances. We applied the  $\mathcal{M}$ -SAP tool to verify version (3.17-rc1) of the Linux operating system with 12 MLOC and 2,963 verification instances. We developed our EEV tools using Atlas [3,37], a graph database platform for program analysis and comprehension. The query language and the interactive visualization capabilities of Atlas are crucial to build and apply visual models for software verification.

The results (Sections 6.4 and 7.4) include a comparison with the state-of-the-art Linux Driver Verification (LDV) tool [5], effectiveness of the proposed visual models (MPG, MTG, PtG, and EFG) as verification-critical evidence through representative examples of the three

result categories produced by  $\mathcal{L}$ -SAP and  $\mathcal{M}$ -SAP, the discovered bugs, and a website [6] for public cross-checking of verification results with evidence for all the verification instances.

#### 1.3 Thesis Contribution

The key contributions are:

- 1. A rigorous notion of verification-critical evidence using visual models. The evidence enables human-machine collaboration to achieve high efficiency and accuracy without exorbitant manual effort (Chapter 4).

- 2. A novel linear time control flow graph pruning algorithm to compute a compact derivative of control flow graph (CFG) called Event Flow Graph (EFG) (Chapter 5).

- 3. A scalable and accurate evidence-enabled verification approach for lock/unlock pairing and its implementation in  $\mathcal{L}$ -SAP tool (Chapter 6).

- 4. A scalable and accurate evidence-enabled verification approach for allocation/deallocation pairing and its implementation in M-SAP tool (Chapter 7).

- 5. A comprehensive empirical study and evaluation on recent versions of the Linux kernel to showcase the scalability and accuracy of the evidence-enabled verification tools: \(\mathcal{L}\)-SAP (Section 6.4) and \(\mathcal{M}\)-SAP (Section 7.4).

#### 1.4 Thesis Organization

The remainder of the thesis is organized as follows. We first present the motivation and major challenges of static software verification in Chapter 2. Next, Chapter 3 describes the related work on static verification techniques for lock/unlock pairing and allocation/deallocation pairing. Chapter 4 presents software visual models as verification-critical evidence used in lock/unlock pairing and allocation/deallocation pairing. Chapter 5 describes in details the Event Flow Graph (EFG) and the linear time algorithm for deriving the EFG from its corresponding CFG. Chapters 6 and 7 present the automated verification algorithms used in  $\mathcal{L}$ -SAP tool for lock/unlock pairing and  $\mathcal{M}$ -SAP tool for allocation/deallocation pairing, respectively.

Chapters 6 and 7 also present the empirical assessment of  $\mathcal{L}$ -SAP and  $\mathcal{M}$ -SAP, the produced evidence, and the discovered bugs. Chapter 8 concludes with an overall summary of the benefits of the EEV approach and a discussion of the extensibility of the EEV approach.

#### CHAPTER 2. MAJOR CHALLENGES AND MOTIVATION

In this chapter, we discuss the major challenges for lock/unlock pairing and allocation/deallocation pairing analyses that motivated the design of our evidence-enabled verification approaches.

#### 2.1 Challenges Overview

Synchronization problems and memory leaks can be catastrophic - a business-transaction server can crash resulting in a big financial loss, or a safety-critical control system can halt causing loss of lives. With multi-threading and event-driven processing, it is challenging to ensure resilience of software systems to such problems. These problems can elude dynamic analyses and regression testing because their occurrence often depends on intricate sequences of low-probability events [41]. Performing multiple runs of a program to examine all possible behaviors is prohibitively expensive and time-consuming. Thus, automated static analyses are crucial to complement testing and dynamic analyses.

Consider the allocation/deallocation pairing analysis: an allocation event A is paired with a deallocation event D iff D can deallocate the memory block allocated by A. The existence of unpaired allocations on feasible execution paths results in memory leaks. The lock/unlock pairing analysis is similar where the lock event L is paired with an unlock event U iff U can release the lock acquired by L. The existence of unpaired locks on feasible execution paths results in synchronization problems. This pairing of an allocation (lock) with its corresponding deallocations (unlock) on all feasible execution paths requires the following: (a) a data flow analysis to map each allocation (lock) to corresponding deallocations (unlocks), (b) a control flow analysis to pair each allocation (lock) with corresponding deallocations (unlocks), and

(c) a feasibility analysis to check the feasibility of an execution path on which an allocation (lock) is not ensued by a deallocation (unlock). A general-purpose, completely automated, and accurate analysis is intractable for each of the above three requirements.

The current formal verification approaches are *not* geared to produce evidence to empower and integrate human reasoning into the verification process. State-of-the-art research and commercial tools for MPV problems produce either very little evidence, voluminous evidence, or evidence that refers to the intermediate representation for the verification machinery but not to the source code. Such evidence is hard to decipher; it does not simplify cross-checking. Thus, another challenge is to formulate the evidence and build tools that can produce evidence.

# 2.2 Path Explosion

A Control Flow Graph (CFG) [14] is a graph representing all paths that the program may traverse during its execution. CFGs are central to any static analysis of the flow of execution and data-relationships in a computer program. The number of control flow paths grows exponentially with non-nested branch nodes. Our empirical study of the Linux kernel shows many functions with very large number of execution paths. For example, function register\_cdrom<sup>1</sup> has 20 non-nested branch nodes. This path explosion increases with interprocedural analysis as a path from the caller function splits into multiple paths in the called function.

To address the path-explosion challenge, this thesis presents a novel CFG pruning technique that produces a compact derivative of CFG called Event Flow Graph (EFG) (Chapter 5). This is achieved by introducing an equivalence relation on the CFG paths to partition/group them into equivalence classes. It is then sufficient to perform the verification or pairing analysis on these equivalence classes (i.e., paths in EFG) rather than on the individual paths in a CFG. We have adopted the graph algorithm by Tarjan et al. [86] to come up with a graph compaction algorithm to form the equivalence classes efficiently. Although the number of paths in a CFG is very large, the number of path equivalence classes is quite small, as seen from our results of the Linux kernel, and that enables an efficient and accurate path-sensitive analysis.

http://lxr.free-electrons.com/source/drivers/cdrom/cdrom.c?v=3.19#L586

## 2.3 Inter-procedural Analysis

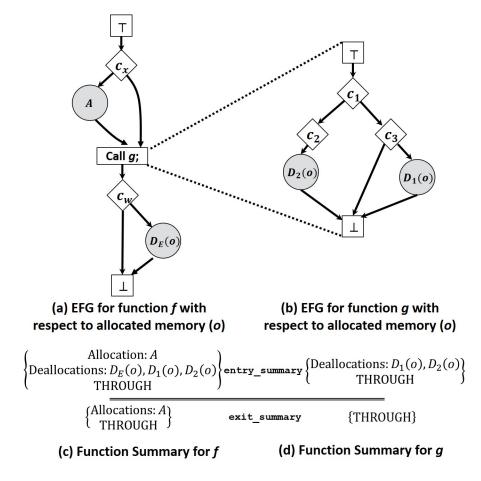

In several lock/allocation instances in the Linux kernel, the corresponding unlocks/deallocations occur across multiple functions, thus requiring inter-procedural analysis. The pairing algorithm must handle the following cases: (1) the locking/allocation function A calls the unlocking/deallocation function D through a call sequence, (2) the locking/allocation function A is called by the unlocking/deallocation function D through a call sequence (the reference to the lock object (allocated memory block) is returned upward the reverse call sequence from A to D), (3) A and D are called by a common parent, or (4) A and D are called asynchronously sharing the lock object (allocated memory block) as a heap object. A combination of these cases can happen where one instance of locking/allocation in A is paired with multiple unlocking/deallocation instances in several multiple functions  $D_1, D_2, ..., D_k$  on different paths. The pairing algorithm (Chapters 6 and 7) addresses the inter-procedural analysis challenge by generating compact function summaries to enable efficient inter-procedural and context-sensitive analysis.

# 2.4 Feasibility Analysis

A path on which a lock (allocation) is not paired with an unlock (deallocation) may or may not be an error depending on whether the path is feasible or not. Thus, analyzing feasibility of paths is important to avoid false positives. Analyzing path feasibility can incur exponential computation [23, 39, 64, 67, 88] because it involves checking satisfiability of branch conditions governing a path. Typical complications for path feasibility analysis are correlations between branch conditions, loops, and inter-procedural paths.

To address the feasibility analysis challenge, first, our pairing algorithm (Chapters 6 and 7) minimizes the need for performing feasibility analysis by sequencing the analysis steps to produce at the end, exactly those path equivalence classes on which a lock (allocation) is not paired with an unlock (deallocation). The feasibility analysis is required only for these cases to avoid false positives. Second, the EFG (Chapter 5) optimizes the path feasibility analysis by identifying a small necessary set of branch conditions relevant for path feasibility. Third, the analysis

calculates Boolean expressions that express the conditions under which each lock (allocation) is not paired with unlock (deallocation). Finally, our pairing analysis uses BDDs [92] to check the satisfiability of these expressions to determine whether the paths that contain the unpaired locks (allocations) are infeasible. We perform a simple automated check for path feasibility by applying an intra-procedural textual equality based analysis. The cases that are not amenable to the simple check are reported as inconclusive so that the human analyst can examine them further.

#### 2.5 Pointer Analysis

Despite the advances in pointer analysis algorithms, they cannot be completely accurate because of the fundamental limitation. Typical accuracy hurdles for pointer analysis are pointer arithmetic operations on pointers, heap objects, function pointers, aggregate structures, offset-references, complex pointer references. For example, a highly accurate bit representation to track a pointer loses accuracy when a pointer is passed to a linked list. Further complications are library and system calls. Godefroid and Lahiri [46] from Microsoft Research note "Indeed, in practice, symbolic execution of large complex programs is rarely fully precise due to external library or system calls, un-handled program instructions, pointer arithmetic, floating-point computations, etc."

To provide scalable and sound analyses and conservatively mitigate inaccuracies of pointer analyses, the lock/unlock pairing analysis (Chapter 6) uses type-based analysis (Section 6.2.1). Our evaluation on multiple versions of the Linux kernel shows that only a tiny percentage (0.2%) of the lock instances cannot be paired using our type-based analysis. To achieve accuracy and scalability of the type-based analysis, the lock/unlock pairing analysis leverages an innovative algorithm [47]) (Section 4.1) to compute the minimum set of functions for the above four variants of inter-procedural analysis.

For allocation/deallocation pairing analysis, our goal is not to advance state-of-the-art pointer analysis, but rather to provide a working analysis that supports our verification-critical evidence framework. Our pairing analysis (Chapter 7) uses a conservative pointer analysis (Section 7.2.1) that is limited to handling cases and implementation patterns found in the

Linux kernel such as the cases where the allocated memory blocks do not escape through function pointers or heap objects.

# 2.6 A Concrete Example to Illustrate the Need for Verification-Critical Evidence

The current formal verification approaches [1,2,5,39,41,83,89,98] are not geared to produce evidence to empower and integrate human reasoning into the verification process. They work mostly as automated black boxes with very little support for cross-checking. The following example brings out the need for verification-critical evidence to reason about and solve complex software verification problems. The example in Figure 2.1 is from the XINU [12] operating system. XINU is a small system with about five thousand lines of code and 200 functions. However, XINU is complex enough to bring out key verification challenges. This example involves pairing an allocation with corresponding deallocations. In XINU, getbuf and freebuf are respectively the allocation and the deallocation functions.

Figure 2.1 An example to illustrate the need for evidence to reason about the possibility of a memory leak in the function dswrite

Consider the following verification instance: function dswrite (Figure 2.1(a)) calls getbuf but it does not call freebuf. The verification problem is to match the getbuf function call in dswrite with its corresponding freebuf function call(s). As seen from the dswrite code in Figure 2.1(a), dswrite calls and passes the pointer drptr to the allocated memory to function dskenq. As shown in Figure 2.1(b), function dskenq has four paths with different exits from the function.

To the best of our knowledge, all the existing static analysis would either fail or report a memory leak for this example. Moreover, these tools produce very little evidence or voluminous evidence which is hard to decipher. With only one exception [83], the evidence refers to the intermediate representation for the verification machinery but not to the source code. Let us improvise and consider a hypothetical tool that produces the following evidence: (1) a call graph of function dswrite (Figure 2.1(c)), (2) markings for the relevant source code line numbers (Figure 2.1(b)) in function (dskenq) where the tool detects the leak.

Let us now understand the difficulties the analyst would face even with this improvised evidence. We will discuss the difficulties along each of the four paths as shown in function dskenq (Figure 2.1(b)).

- 1. Path 1: drptr is passed to function dskstrt; it does not deallocate the allocated memory. But, the analyst cannot conclude that it is a memory leak because on the same path drptr is assigned to dsptr->dreq1st where dsptr (passed as a parameter to dskenq from dswrite). The analyst would then need to go back to dswrite and figure out that dsptr points to a global data structure. The verification becomes very challenging for the analyst once the pointer is globally accessible. Any function could accesses the pointer to deallocate the memory. The call graph (Figure 2.1(c)) does not help at this point. Without any more evidence, the analyst faces the arduous task of sifting through all functions to complete the verification.

- 2. Path 2: The pointer to the allocated memory drptr is passed to function dskopt. This tells the analyst that there is a problem in dskopt. The corresponding code to dskopt is not shown but we point out that it has 7 paths including paths on which the pointer to the allocated memory drptr is assigned to a global structure. Thus, the analyst has a lot more work to do to complete the verification. However, there is no additional evidence to help the analyst with the remaining work.

- 3. Paths 3 and 4: The analyst faces similar challenge as in Path 1 because the pointer to the allocated memory drptr is assigned to a global structure. The analyst also has to manually trace the data flow through dskenq to figure it out.

**Summary.** This example exhibits multiple challenges due to global accessibility of the pointer to the allocated memory. It poses a monumental task for the analyst to complete the verification.

This is also an example of an interesting pattern that should be leveraged for a tractable verification. On several execution paths in dskenq, there is a consistent pattern of the allocated memory pointer drptr being assigned to a global structure. Moreover, it is the same global structure on all paths. It looks like that the developer has done so on purpose with a design in mind. The design is not documented and the improvised evidence does not provide a clue. The call graph evidence in Figure 2.1(c) is problematic because: (1) there are functions irrelevant to the verification called by getbuf and freebuf, and (2) there are functions relevant to the verification but not captured. If the analyst does not figure out that the allocated memory pointer on some paths in dskenq becomes globally accessible, the analyst could conclude that it is a memory leak which is incorrect.

To address these difficulties, the evidence must simplify human reasoning: (1) by identifying relevant functions and their interactions, (2) by assisting with intra-procedural reasoning for each relevant function, and (3) by assisting with data flow reasoning by identifying the points-to relations between the pointers of interest at different locations in source code. In Chapter 4, we revisit the motivation example and present multiple visual models as inter-procedural, intra-procedural, and data flow evidence to help the analyst reason, complete, and cross-check the verification instance.

#### CHAPTER 3. LITERATURE REVIEW

In this chapter, we first survey previous static verification approaches for lock/unlock and allocation/deallocation pairing analyses and reflect on the shortcoming of their results, scalability, and accuracy, then we discuss their produced evidence. Next, we present previous work on Linux kernel verification.

#### 3.1 Data Races and Deadlocks Detection

Detecting data races and deadlocks is a well-known challenging problem [41]. Although not directly related, there are many papers on dynamic verification techniques to detect race conditions and deadlocks [27,31,40,49,50,61,62,71,75,80,96]. However, Performing multiple runs of a program to examine all possible behaviors is prohibitively expensive and time-consuming. Thus, automated static verification techniques are crucial to complement testing and dynamic verification techniques.

Warlock [81], Extended Static Checking [38] (ESC) and ESC/Java [57] are static race detection approaches for C, Modula-3 and Java respectively. These approaches utilize a theorem prover to find race conditions. However, these approaches require annotations to inject knowledge into the analysis and to reduce the number of false positives. Thus, applying these approaches to large code bases such as the Linux kernel would require time-consuming and tedious annotation effort and at the end annotations can be erroneous and checking their correctness would be a daunting task for millions of lines of complex code.

RacerX [41] and Relay [89] are static lockset based analyses for C code that scale to large real world programs including the Linux kernel. RacerX [41] uses a top-down approach to compute absolute locksets (the set of locks held by the program) at each program point. RacerX is able to run on an older version of the Linux kernel (v2.5.62 - 1.8 MLOC) in tens of minutes. In

contrast, Relay [89] uses a bottom-up approach to compute relative locksets, which describes the changes in the locks being held relative to the function entry point, at each program point. Relay was able to analyze an older version of the Linux kernel (v 2.6.15 - 4.5 MLOC) in 72 hours. RacerX reports that in order to scale, the analysis discards valuable information, such as truncating the function summaries. Consequently, discarding possible races. Moreover, both approaches (RacerX and Relay) require significant post-processing of large volume of warnings/false positives.

Saturn [39] is considered a scalable static analysis engine that is both sound and complete with respect to the user-provided analysis script (abstraction), written in its Calypso language. ESP [36] is a path-sensitive analysis tool that scales to large programs by merging superfluous branches leading to the same analysis state. However, the lock analysis script bundled with Saturn and ESP is neither sound nor complete, most notably because of its lack of global alias analysis and incomplete function summaries for inter-procedural analyses.

Locksmith [73,74] is a sound static race detector for C. It uses a constraint based technique to infer the correlation of memory locations to the locks that protect them. If a shared location is not consistently protected by the same lock, a race is reported. Locksmith analyzes source code fast. However, it finds superficial errors and it produces a number of false alarms, which is about 90% on the device drivers of an older version of the Linux kernel and about 98% on some POSIX applications.

Cho et al. [29] proposed a lock/unlock pairing analysis that combines an inter-procedural analysis and dynamic checking for better detection of races and deadlocks. Their analysis uses dynamic checking to compensate for imperfections in their static analysis. However, the proposed dynamic analysis introduces an overhead for the overall analysis. Moreover, the lock/unlock pairing mechanism has been only applied to code orders of magnitude smaller than the Linux kernel.

The Linux Driver Verification tool (LDV) [5] is currently the top-rated tool in the software verification competition (SV-COMP) [18–20] in the Linux device drivers verification category. LDV uses Blast [21] model checker to check for memory leaks and synchronization problems. However, LDV takes 60 hours for lock/unlock pairing in a recent version of the Linux kernel.

## 3.2 Static Memory Leak Detection

Memory leak detection is a well-known challenging problem. Although not directly related, there are number of reported attempts on memory leak detection using dynamic analysis [24,33, 66,69,100,101]. There has been a lot of research devoted to checking memory leaks statically [1, 5,52,55,83,97].

Saturn [97] models the memory-leak detection problem as a boolean satisfiability problem, then uses a SAT solver to identify memory-leaks. Its analysis is context-sensitive and intraprocedurally path-sensitive. Saturn checks for specific type of memory leaks: a memory block that is allocated in function p and is never escaped and deallocated in p is considered a memory leak. Thus, Saturn handles a very small subset of the allocations in the Linux kernel. Saturn is able to run on an older version of the Linux kernel (v2.6.10 - 5MLOC) in 23 hours without parallelization.

FastCheck [28] uses guarded value-flow analysis to detect memory leaks. It tracks the flow of values through top-level pointers only. It is fast but limited to analyzing allocation sites whose values escapes to (flow into) top-level pointers only. Through our study in the Linux kernel, most of the memory leak cases reported in this thesis will go undetected with FastCheck.

Athena [55] finds inter-procedural path-sensitive faults (including memory leaks) guided by user specifications. Sparrow [52] is a static analyzer that relies on abstract interpretation to detect memory leaks in C programs. It separately analyzes each function's memory behavior into a parameterized summary that is used in analyzing its call-sites. Both approaches (Athena and Sparrow) have been applied to programs order of magnitude smaller than the Linux kernel and it is not clear how scalable these tools are to larger code bases.

Clang [1] finds memory leaks in C and Objective-C programs based on symbolic execution. Being intra-procedural, it assumes unknown or symbolic values for the formal parameters of a function and the returned values from its call-sites. Therefore, all inter-procedural leaks can go undetected. Clang does not scale-well to large code bases. Moreover, LLVM [7], its core compiler, does not succeed in compiling the recent versions of the Linux kernel.

Saber [83] is a static detector for memory leaks in C programs. It performs a sparse value-flow analysis to track flow of values (escapes), from allocation to deallocation sites, through top-level and address-taken pointers. Saber does not track escapes (values-flows) to global variables. Although, Saber is the most recent memory leak detector, it cannot be applied to large code bases as the Linux kernel due to the following challenges: (1) Saber uses Open64 [8] compiler which cannot link the whole program static single assignment intermediate representation of the Linux kernel in its inter-procedural optimization module due to some non-trivial compilation issues (e.g., assembly language mixed with C), and (2) Saber uses Andersen's pointer analysis [15] for building value-flow dependencies. Although Andersen's analysis is well-studied algorithm, it is hard to scale to whole pointer analysis of large code bases as the Linux kernel (12 MLOC). Some heuristics may be applied to speed up and scale Saber's pointer analysis by performing field-insensitive analysis or mixing with unification-based [35] analysis, however, this will drastically affect the detection accuracy.

The Linux Driver Verification tool (LDV) [5] is also used to check for memory leaks. However, LDV takes 30 hours for allocation/deallocation pairing in a recent version of the Linux kernel.

#### 3.3 Evidence-Enabled Verification

Saturn [39, 98] provides a minimalist evidence that consists of the source correspondence (i.e., file path and line numbers) for the checked instances. For example, if a memory leak is detected, Saturn will point-out the source correspondence for the allocation site only. This would require a huge effort of cross-verification, especially, if the corresponding deallocation calls for the allocated memory occur many levels down the call chain from the allocation function.

RacerX [41] and Relay [89] require significant post-processing of large volume of proofs/reports to produce comprehensible evidence for manual validation.

The Linux Driver Verification tool (LDV) [5] produces a monumental amount of non-visual complex evidence that require significant processing to produce the source correspondence of where the problem occurs.

Clang [1] finds memory leaks in C and for each detected memory leak, Clang generates an evidence that consists of multiple HTML pages. Each HTML page corresponds to the source code of a function related to the detected memory leak. Clang also draws segments between the different statements corresponding to the execution path where the detected memory leak occurs. In this case, the cross-verification process is tedious and error-prone, especially with inter-procedural memory leaks given that the analyst is limited to one function at a time.

Saber [83] produces a set of graphs, for each detected memory leak, that includes: program assignment graph, constraint graph, and value-flow graphs. However, this evidence corresponds to the intermediate representation of source code (i.e., static single assignment). Moreover, the evidence is difficult to read given that it has no source correspondence to the actual source code where the memory leak occurs.

Coverity [2] is a well-known commercial tool that offers static source code analysis technology that finds critical defects and security vulnerabilities in C/C++ and Java source code. For detected memory leaks and synchronization problems, Coverity annotates the source code with the events leading to the error. This produced evidence poses a usability barrier to the analyst, especially for inter-procedural errors the occur across multiple source files.

To the best of our knowledge, we are not aware of any evidence-based verification platform that is geared to produce comprehensible, compact, and visual evidence to empower and integrate human reasoning into the verification process.

#### 3.4 Linux Kernel Verification

Linux dominates the server operating systems market. Many embedded devices such as smart phones run Linux as kernel. There is an increasing need for automatic verification of Linux components.

Microsoft had identified the device drivers as the most important source of failures in Windows. Therefore, the company has integrated the Static Driver Verifier (SDV) tool in the Windows Driver Development Kit that uses the SLAM [17] verification engine. For Linux, an industry-funded verification project of the size of SDV does not exist. Linux verification has become an important research topic using program analysis, SMT solvers, model checking, and

other software verification techniques [43,48,53,54,63,70,72,94]. Despite many new advances, the recent competitions on software verification (SV-COMP) [18–20] show that state-of-the-art tool implementations have problems analyzing Linux.

This Thesis proposes EEV as an alternative approach to software verification of MPV problems. Our comparison results on recent versions of the Linux kernel (Sections 6.4 and 7.4) with the top-rated Linux Driver Verification (LDV) [5] tool proves the practicality, accuracy, and scalability of EEV.

# CHAPTER 4. VISUAL MODELS AS VERIFICATION-CRITICAL EVIDENCE

The complexity of software is rooted in its own version of the butterfly effect [45,59]. A small change at one point can impact many parts of the software and cause an unforeseen effect at a very distant point of the software. This impact propagation is hard to decipher from software viewed as lines of code; it makes program comprehension and reasoning tedious, error-prone, and almost impossible to scale to large software. In addition, the current formal verification approaches work mostly as automated black boxes with very little support for cross-checking [1,2,5,39,41,83,89,98].

In this chapter, we propose visual software models as the key enablers for integrating automation with human intelligence to solve software verification problems where complete automation has remained intractable. The key innovation is a mathematically rigorous notion of verification-critical evidence that the machine abstracts from software to empower human to reason with. The machine and human have different strengths and weaknesses to complement each other. Even for automatically completed verification, we advocate human cross-checking. This is especially important for critical systems where failures of software can be catastrophic. The cross-checking should be simplified by automation to conserve human effort.

Specifically, we will present four visual software models:

- 1. The Matching Pair Graph (MPG) (Section 4.1) and Memory Taint Graph (MTG) (Section 4.2) for managing inter-procedural complexity due to impact propagation.

- 2. The Points-To Graph (PtG) (Section 4.3) to assist with data flow reasoning by identifying the points-to relations between the pointers of interest at different source code locations.

- 3. The Event Flow Graph (EFG) (Section 4.4) (derived from the Control Flow Graph (CFG)) for managing intra-procedural complexity of control paths explosion.

# 4.1 Matching Pair Graph (MPG)

By design, the matching pair graph (MPG) [47] is a directed graph with edges representing function calls and the roots of MPG are asynchronous functions; they either belong to different threads or some of them may be called through interrupts. The MPG captures the functions that are needed for verifying the correct pairing of lock/unlock and allocation/deallocation. The functions in the MPG are sufficient for the pairing analysis if the type of the pointer referencing the lock object or the allocated memory block is preserved and never changes (i.e., not casted to a different type). Now, let us discuss how the MPG can serve as valuable evidence and significantly simplify work for the analyst by revisiting the motivation example in Figure 2.1. Figure 4.1 shows the MPG corresponding to the allocated memory in function dswrite. From the several hundred XINU functions, the MPG has narrowed down the relevant functions to 6.

Figure 4.1 MPG evidence for the allocated memory in dswrite

Besides producing a small set of functions, the MPG provides other very valuable pieces of evidence. The MPG shows a call chain from dswrite to freebuf which indicates the possibility of execution paths on which the pointer to the allocated memory is passed as a parameter, eventually to function dskopt which deallocates the memory. More importantly, the MPG includes function dsinter which turns out to be a crucial clue. Function dsinter is not connected to dswrite by forward or reverse call chains. Strangely, dsinter calls freebuf but not getbuf. It is actually a critical clue.

The analyst can hypothesize that freebuf in dsinter can potentially pair with the getbuf in dswrite and since dsinter and dswrite are roots of the MPG, they work asynchronously and communicate with each other by sharing a global data structure D. To prove the hypothesis the analyst must locate D and complete the verification. The analyst has a good suspect for D, namely the data structure to which the allocated memory pointer drptr is assigned. This makes it quite easy for the analyst to complete the verification.

This example of the memory allocation instance in dswrite illustrates how the evidence from MPG can be of tremendous assistance to the analyst. It presents a case not amenable to automation because of the invisible control due to asynchronous processing. The data flow is also invisible because the allocated memory pointer drptr is inserted in a global linked list D. Function dsinter draws the pointers from the list and deallocates the memory for each pointer. And the fact that it does so until the list becomes empty shows that it is not a memory leak.

This is not a wayward example. It stems from the well-known *producer-consumer* pattern [85], a classic example of a multi-process synchronization. In Section 6.2.2, the MPG is used in our lock/unlock pairing analysis.

#### 4.2 Memory Taint Graph (MTG)

The Memory Taint Graph (MTG) is a directed graph where the nodes correspond to functions and the edges are call relations. The MTG captures the set of functions where the object of interest associated with the MPV instance has been referenced, communicated or escaped. There are three communication ways: passing a reference through a parameter, returning a reference to the parent via a return statement or through a parameter, or referencing it though a global variable. Unlike the MPG, the MTG works with the MPV instances where the type of the pointer referencing the object of interest is not preserved while communicating or escaping the object. That means, the object is referenced by pointers of different types than the initial type. The MTG for allocation/deallocation pairing of object o contains the set of functions visited/analyzed while tracking references to o via pointer analysis. Nevertheless, the MTG will not be able to capture functions that are involved in obscure flows through interrupt driven.

The MTG can serve as valuable evidence and significantly simplify work for the analyst by capturing how the object of interest has been communicated/escaped through the program. Figure 4.2 shows the MTG corresponding to the allocated memory in function dswrite. The analyst can easily see that the allocated memory block in dswrite has been passed as a parameter to dskenq and then to dskqopt and finally to freebuf. In Section 7.2.1.13, we will use the concept of MTG in our allocation/deallocation pairing analysis.

Figure 4.2 MTG evidence for the allocated memory in dswrite

# 4.3 Points-To Graph (PtG)

The Points-To Graph (PtG) is a directed graph where the nodes and edges are as follow: The nodes are:

- Pointer node that represents a program pointer. In our node representation, the pointer node can be one of the following:

- An id pointer (IDP) node denotes a directly accessed pointer with no field references.

For example, the pointers ptr and q are IDPs in the expression ptr = q.

- A field-reference pointer (FRP) denotes a pointer that is being referenced/accessed through its containing structure using the pointer/structure de-reference operations:

→ or •. For example, the pointer a->b->c is a FRP and its containing structure is a->b. In turn, a->b is a FRP pointer and its containing structure is a which is an IDP.

• Memory Location (MLoc) node that represents a location in memory that can be referenced or pointed-to by pointer nodes. The MLoc node can also represent an Allocated Memory Block (AMB) that corresponds to an allocated memory block via an allocation call. The AMB node is associated with an address corresponding to the source code location of the allocation callsite.

There are two kinds of directed edges:

- Points-to Edge: A points-to edge  $(a \to b)$  from node a to node b represents that the pointer represented by a points-to the pointer represented by b.

- Field Edge: A field edge  $(C \dashrightarrow k)$  from node C to node k denotes that the pointer represented by k is a field in the structure represented by the pointer C.

Section 7.2.1 describes the details of mining, building, and the transformation of points-to graphs. Now, let us discuss how the PtG can serve as valuable evidence and significantly simplify work for the analyst by revisiting the motivation example in Figure 2.1. Figure 4.3 shows the PtG after processing line 4 in function dskenq with respect to the allocated memory block AMB at line 10 in function dswrite.

Figure 4.3 PtG evidence for the allocated memory in dswrite at line 4 of function dskeng

The PtG provides valuable pieces of evidence. The PtG shows the allocated memory block at line 10 of dswrite represented by the AMB node. It also shows all the pointers that directly and indirectly point to that block. The analyst can check whether any of the pointers at line 4 of function dskenq points-to the AMB. For example, the analyst can see that pointers q and dsptr->dreqlst point-to the allocated memory block and may be able to deallocate it. The analyst can also see that dsptr can be used to deallocate the memory block through the field dreqlst. This makes it quite easy for the analyst to complete or validate the verification. This example illustrates how the evidence from PtG can be of tremendous assistance to the analyst.

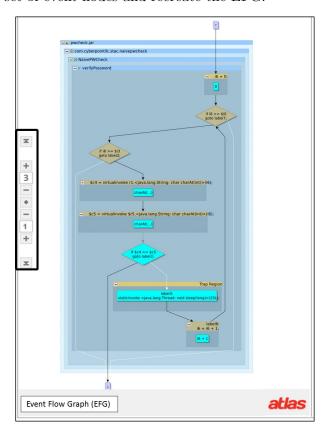

# 4.4 Event Flow Graph (EFG)

The CFG is valuable for understanding program behaviors. However, in real-world software the CFG can be very large and complex. This thesis presents a compact derivative of the CFG, called the EFG. Mathematically, the EFG defines an *equivalence relation* on CFG paths, where each path in the EFG corresponds to a multitude of CFG paths with identical traces of events of interest. The EFG has two major advantages over CFG: (a) although the number of paths in a CFG can be exponentially large, the essential information to be analyzed is captured by a small number of equivalence classes, and (b) checking path feasibility becomes simpler.

In Chapter 5, we present two important applications to show the use of the EFG as a powerful program comprehension tool: (a) a verification problem for the Linux kernel, and (b) a side-channel vulnerability detection problem for Java bytecode. We have built an interactive tool for creating EFGs for C, Java, and Java bytecode. While CFGs can be complex with exponentially many paths, we have developed an efficient algorithm to transform a CFG to an EFG. The algorithm is linear with respect to the number of CFG nodes and edges.

# 4.5 Enabling Technology & Interactive Reasoning

Interactive reasoning can be performed using visual models and their source correspondence. The interactions can go from one visual model to another one, go from a visual model node to its corresponding source code, or go from source code to a corresponding visual model. One can click on a function node in a visual model (e.g., MPG) to open up the EFG for the selected function in MPG and observe the control flow paths within the function. The EFG nodes

correspond to statements in the source code. One can click on a EFG node to observe the corresponding source code. Similarly, one can click on a pointer in source code to show the corresponding PtG. Clicking a points-to relation takes the user to the source code expression where the points-to relation has been created.

To enable such interactive reasoning, we built our EEV machinery on top of Atlas [3, 37] which is a graph database platform for program analysis and comprehension. It provides a shell and one can interactively (i.e., visually and/or programmatically) query and mine programs to gather additional evidence. Atlas also provides *Smart Views* to provide instant feedback and interactive software graph visual models as the analyst clicks on code artifacts or other visual models. A number of out-of-the-box smart views are provided for common queries for building call graphs, data flow graphs, type hierarchies, dependency graphs, and many other useful results. For example, when the analyst clicks on a function either in a visual model or source code, the call graph smart view (if selected) will instantly produce the call graph for the selected function. The produced smart view appears on a side tab that does not interfere with the analyst and keeps him focused on the current task. Figure 4.4(b) shows the call graph smart view for the selected function dswrite in the source code panel (Figure 4.4(a)).

Figure 4.4 Call graph smart view for selected function dswrite

## CHAPTER 5. EVENT FLOW GRAPH FOR PROGRAM COMPREHENSION

The Control Flow Graph (CFG) is valuable for understanding program behaviors. However, in real-world software the CFG can be very large and complex. This chapter presents a compact derivative of the CFG, called the Event Flow Graph (EFG). Mathematically, the EFG defines an equivalence relation on CFG paths, where each path in the EFG corresponds to a multitude of CFG paths with identical traces of events of interest. We present two important applications to show the use of the EFG as a powerful program comprehension tool: (a) a verification problem for the Linux kernel, and (b) a side-channel vulnerability detection problem for Java bytecode. Using the Atlas platform, we have built an interactive tool for creating EFGs for C, Java, and Java bytecode. While CFGs can be complex with exponentially many paths, we have developed an efficient algorithm to transform a CFG to an EFG. The algorithm is linear with respect to the number of CFG nodes and edges.

## 5.1 Introduction

The CFG [14] is a graph representing all paths that the program may traverse during its execution. CFGs are central to any static analysis of the flow of execution and data-relationships in a computer program. The number of control flow paths grows exponentially with non-nested branch nodes. Our empirical study of the Linux kernel shows many functions with very large number of execution paths. For example, function register\_cdrom<sup>1</sup> has 20 non-nested branch nodes. This path explosion increases with inter-procedural analysis as a path from the caller function splits into multiple paths in the called function.

<sup>1</sup>http://lxr.free-electrons.com/source/drivers/cdrom/cdrom.c?v=3.19#L586

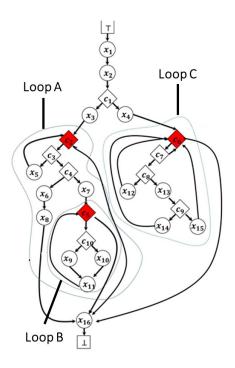

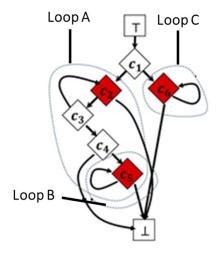

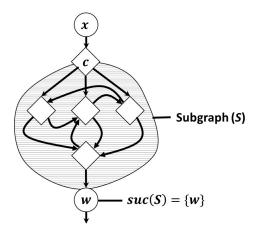

We define a compact derivative of the CFG called the Event Flow Graph (EFG). The purpose of the EFG is to simplify the corresponding CFG as much as possible while retaining all relevant execution traces for a given problem. We call a relevant execution trace an event trace. Defined for each CFG path, it is the sequence of nodes corresponding to events relevant for a given problem. Two CFG paths are equivalent if they have the same event trace. The EFG retains all event traces from the CFG but it has only one path for each distinct event trace. The non-branch nodes not relevant to the problem and the branch nodes not leading to distinct event traces are elided by the CFG to EFG transformation. We describe an efficient linear-time algorithm for this transformation.

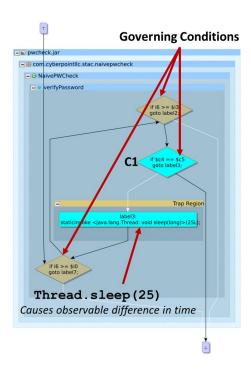

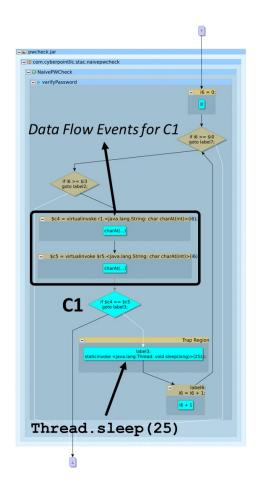

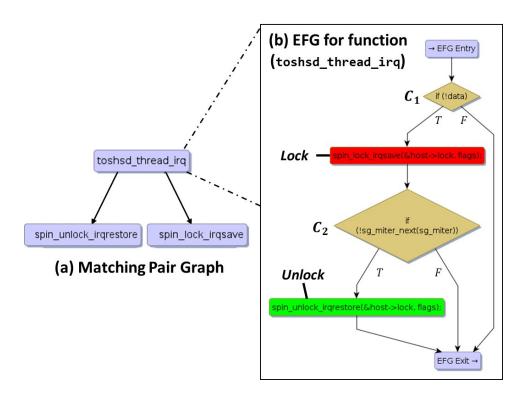

We present two applications to show the fundamental importance of EFGs for program comprehension. The first application is lock/unlock pairing: verify that each lock event L is paired on all feasible execution paths with unlock events U that release the lock acquired by L. For this application, the relevant events are Lock, Unlock, and other program statements that pass the pointer to the lock object. The CFGs and EFGs, for pairing analysis of 66,609 Lock instances in three recent Linux versions, are posted on a website [6]. The second application is detecting sophisticated vulnerabilities that can lead to algorithmic complexity (AC) or sidechannel (SC) attacks [10]. For this application, the relevant events are loops with differential time or space behaviors.

The program comprehension scenarios for the two applications are as follows. For verifying the pairing between Lock and Unlock, program comprehension support is important for: (a) cross-checking results of automated pairing, and (b) human-in-the-loop pairing for difficult cases where automated pairing is intractable. For detecting AC or SC vulnerabilities, program comprehension support is important for: (i) hypothesizing potential AC or SC attacks, and (ii) proving or refuting each attack hypothesis. Apart from being a compact graph, the EFG is important for focusing on critical branch nodes. For the first application, it brings out the branch nodes critical for determining the feasibility of paths where a Lock is not followed by a corresponding Unlock. For the second application, it brings out the branch nodes critical for selecting paths for AC or SC attacks.

This chapter has the following key research contributions:

- A rigorous formulation of the EFG as a fundamental concept for reducing the cognitive burden by simplifying the CFG while retaining problem-specific execution behaviors.

- Two important applications to show the use of the EFG as a powerful program comprehension tool.

- A quantitative study of reductions afforded by the CFG to EFG transformation for realworld software.

The remainder of the chapter is organized as follows. We first present the motivation in Section 5.2. Next, Sections 5.3 and 5.4 present two applications to show the fundamental importance of EFGs for program comprehension. Section 5.5 describes the tool capabilities for constructing EFGs. Section 5.6 presents the linear-time algorithm for constructing the EFG from its corresponding CFG. Our empirical assessment of EFGs using three recent versions of the Linux kernel is presented in Section 5.7. Section 5.8 describes the related work. Finally, we conclude in Section 5.9.

## 5.2 Motivation

We present two examples to show the simplifications achieved by EFGs.

#### 5.2.1 A Linux Example

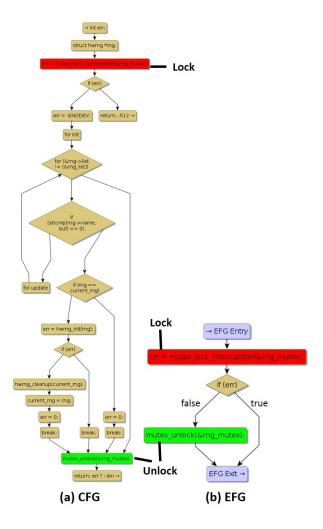

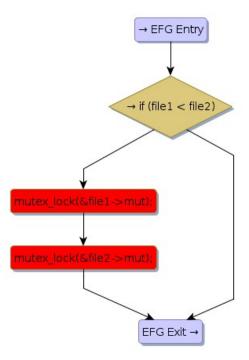

The following example from the Linux kernel (v3.19) illustrates how an EFG greatly simplifies the verification of pairing between Lock and Unlock. Figure 5.1 shows an example of a CFG and its corresponding EFG. The EFG is constructed with respect to Lock and Unlock events. The CFG has 5 branch nodes resulting in 8 paths after the lock. Some of these paths go through a complex loop with two exits. 4 out of 5 branch nodes are irrelevant to the verification because all the paths branching from them lead to the Unlock and are thus equivalent. These 4 branch nodes get eliminated in the EFG and the 7 paths are represented by a single path in the EFG. Thus, the EFG simplifies the verification task by compacting the CFG.

Figure 5.1 CFG and EFG for the function hwrng\_attr\_current\_store

The EFG also simplifies the path feasibility check. As seen from the EFG in Figure 5.1(b), there is a path with missing Unlock and the feasibility of that path must be checked. If feasible, it is a bug. Otherwise the particular Lock is correctly paired. The EFG has retained only the condition that is necessary to verify the path feasibility, the other 4 conditions from the CFG are not retained in the EFG. If the lock is granted, then the particular condition is false. So, the true path in Figure 5.1(b) is not feasible and thus the pairing is correct.

Similar to this example, our empirical observation on real-world software shows that the set of problem-specific events is usually sparse and consequently EFGs are typically significantly smaller compared to the corresponding CFGs. A quantitative study of the Linux kernel is presented later in Section 5.7.

## 5.2.2 Loop Call Graph

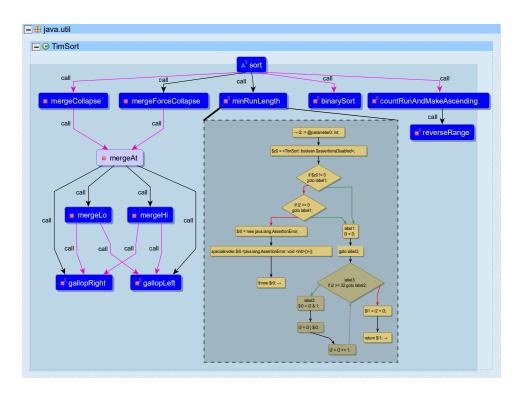

The following example illustrates how EFGs can be used to focus on loops. As mentioned earlier, loops are important for detecting AC and SC vulnerabilities.

The Loop Call Graph (LCG) is a directed graph whose nodes are methods that contain intra-procedural loops and methods that reach loops through call chains. There is an edge from method  $m_1$  to  $m_2$  in the LCG if method  $m_1$  calls method  $m_2$ . Further, an edge is colored if the callsite of method  $m_2$  in method  $m_1$  is located within an intra-procedural loop.

The LCG is an example of extending the EFG to capture relevant behaviors across methods. Within each method, we can have the EFG that captures loops by treating loop headers and callsites which may reach a method with a loop. The LCG enables us to explore and understand loops nested across methods. We have developed interactive tool support so that one can navigate through inter-procedural loops using the LCG and click on a method to view the intra-procedural EFG.

Figure 5.2 shows the LCG for TimSort [11], a defacto sorting algorithm implemented in several languages including Java and Python. In Java bytecode, TimSort contains 20 loops that are distributed among 11 different methods. When a method in the LCG is selected, the intra-procedural EFG shows loops shaded darker for each level of nesting (shown within a dashed callout in Figure 5.2. To recover loops in bytecode, we leverage the Decompiled Loop Identification algorithm presented by Wei et al. [91].

TimSort has many pieces to it with variants of sorting algorithms working together to achieve highly optimal performance depending on the size and ordering of the data to be sorted. The complex internal structure of TimSort is revealed by the EFG that focuses on loops.

## 5.2.2.1 Loop-based Intra-procedural EFG

An LCG helps to navigate through inter-procedural loops. By clicking on a LCG node, we can view the intra-procedural EFG. Figure 5.3 shows the CFG and Figure 5.4 shows the loop-based EFG. The highlighted branch points are the loop headers. The EFG retains three

Figure 5.2 Loop Call Graph for TimSort Algorithm

other branch points because they are differential branch points with branches that are distinct with respect to loops. As discussed later, loops are important for detecting SC vulnerabilities. In a SC attack, the attacker controls a differential branch point using inputs to observe the difference in space or time behavior and learns a secret (e.g., a password).

## 5.3 Application: Verify Pairing

We present four instances to show different program comprehension scenarios. The first scenario is to verify correct pairing of Lock and Unlock. The second scenario is to argue that the pairing is not correct and thus it is a bug. The third scenario is to reason about a case when the Lock happens inside a loop, looks like a bug at a cursory glance but it is not a bug on a thoughtful review of the EFG. The fourth scenario is an EFG quirk due to a peculiar programming pattern. These instances are drawn from the *Matching Pair Graphs* (MPGs) [47] and the EFGs posted on our website [6] for each of the 66,609 Lock instances from three recent versions (3.17-rc1, 3.18-rc1, and 3.19-rc1) of the Linux kernel. The MPG, defined for each Lock

Figure 5.3 CFG with marked loop headers

Figure 5.4 Loop-based EFG

instance, provides the call graph of relevant functions for the Lock. The EFGs are given for all the relevant functions.

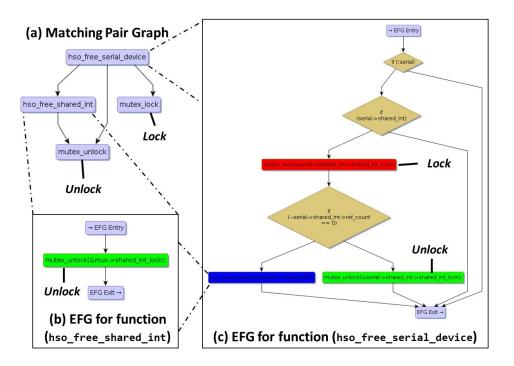

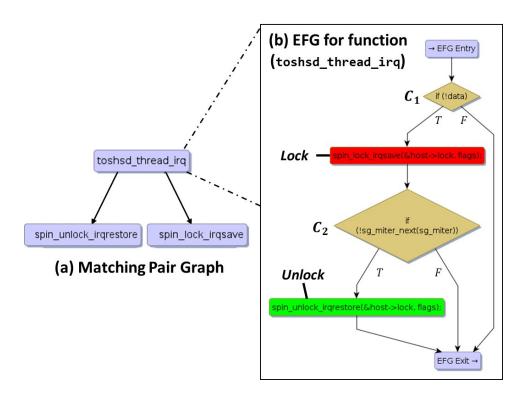

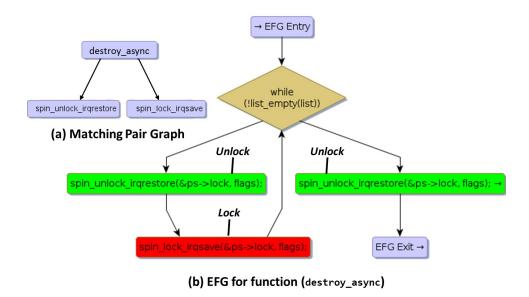

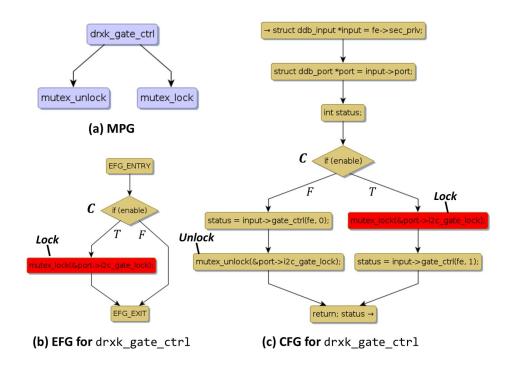

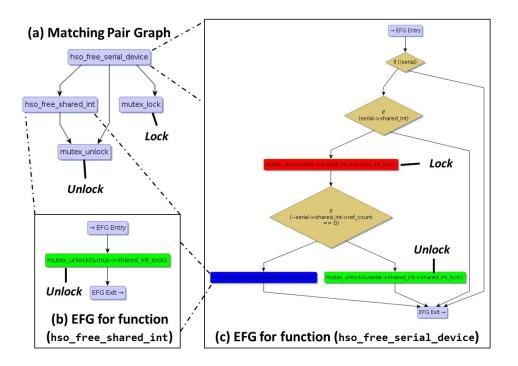

#### 5.3.1 Correct Lock-Unlock Pairing

Figure 5.5(a) shows the MPG for the lock in function hso\_free\_serial\_device. Figures 5.5(b) and 5.5(c) show the EFGs for the MPG functions hso\_free\_shared\_int and hso\_free\_serial\_device, respectively.