# Air Force Institute of Technology

# **AFIT Scholar**

Theses and Dissertations

Student Graduate Works

3-1995

# Formal Foundations for the Specification of Software Architecture

Mark J. Gerken

Follow this and additional works at: https://scholar.afit.edu/etd

Part of the Software Engineering Commons

### **Recommended Citation**

Gerken, Mark J., "Formal Foundations for the Specification of Software Architecture" (1995). Theses and Dissertations. 6308.

https://scholar.afit.edu/etd/6308

This Dissertation is brought to you for free and open access by the Student Graduate Works at AFIT Scholar. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AFIT Scholar. For more information, please contact AFIT.ENWL.Repository@us.af.mil.

AFIT/DSG/ENG/95M-01

FORMAL FOUNDATIONS

FOR THE

SPECIFICATION OF

SOFTWARE ARCHITECTURE

DISSERTATION Mark James Gerken Captain, USAF

AFIT/DSG/ENG/95M-01

19950811 050

DTIS QUALITY INSPECTED 5

Approved for public release; distribution unlimited

166

# FORMAL FOUNDATIONS FOR THE SPECIFICATION OF SOFTWARE ARCHITECTURE

# DISSERTATION

Presented to the Faculty of the Graduate School of Engineering

of the Air Force Institute of Technology

| Accesio  | n For          |       | 1        |  |

|----------|----------------|-------|----------|--|

| NTIS     | CRA&I          | •     | <b>y</b> |  |

| DTIC     | TAB            |       |          |  |

| Unanno   | unced          |       |          |  |

| Justific | ation          |       |          |  |

| By       |                |       |          |  |

| A        | vailabilit     | у Сос | les      |  |

| Dist     | Avail a<br>Spe | -     | r        |  |

| A-1      |                |       |          |  |

Air University

In Partial Fulfillment of the

Requirements for the Degree of

Doctor of Philosophy

Mark James Gerken, B.S., M.S.

Captain, USAF

March, 1995

Approved for public release; distribution unlimited

# FORMAL FOUNDATIONS FOR THE SPECIFICATION OF SOFTWARE ARCHITECTURE

Mark James Gerken, B.S., M.S.

Captain, USAF

Approved:

| Paul D. Bailor, Chairman                      | 10 MAR 95 |

|-----------------------------------------------|-----------|

| Thomas C. Hartrum                             | 10 mar 95 |

| Eugene Santo J. Eugene Santos, Jr             | 10 MAR95  |

| Mak E. Oxley                                  | 10 Mar 95 |

| Mark E. Oxley  Sary B. Lamont  Gary B. Lamont | 10 MAR 95 |

| [6h 4h                                        | leh L     |

Robert A. Calico, Jr

Dean, Graduate School of Engineering

# Acknowledgements

I would like to thank my advisor, Dr. Paul Bailor, for his insight, guidance, and encouragement — it was instrumental to the successful completion of this research. I would like to thank my committee, Dr. Eugene Santos, Dr. Thomas Hartrum, and Dr. Mark Oxley, for their advice given during the course of the investigation and for their suggestions for improving this document. I am indebted to several other researchers, especially Dr. Douglas Smith, Dr. Richard Jüllig, and Dr. Yellamraju Srinivas of the Kestrel Institute for answering my multiple questions concerning category theory and specification construction techniques. I would also like to thank a fellow graduate student, Captain Frank Young, for the many hours we spent discussing specification techniques.

I especially wish to thank my wife, Debora, for her patience and understanding.

Mark James Gerken

# $Table\ of\ Contents$

|                                          | Page  |

|------------------------------------------|-------|

| Acknowledgements                         | iii   |

| List of Figures                          | x     |

| List of Tables                           | xv    |

| List of Symbols                          | xvi   |

| List of Abbreviations                    | xviii |

| List of Definitions                      | xix   |

| Abstract                                 | xxiii |

| I. Introduction                          | 1-1   |

| 1.1 Purpose and Motivation               | 1-1   |

| 1.2 Investigation Overview               | 1-2   |

| 1.3 Related Work                         | 1-4   |

| 1.3.1 Software Development Systems       | 1-4   |

| 1.3.2 Architecture Description Languages | 1-10  |

| 1.3.3 Summary of Related Work            | 1-14  |

| 1.4 Assumptions                          | 1-14  |

| 1.5 Contributions                        | 1-16  |

| 1.6 Summary                              | 1-17  |

|                                          |       |

| II. Software Development Framework       | 2-1   |

| 2.1 Overview of the Framework            | 2-1   |

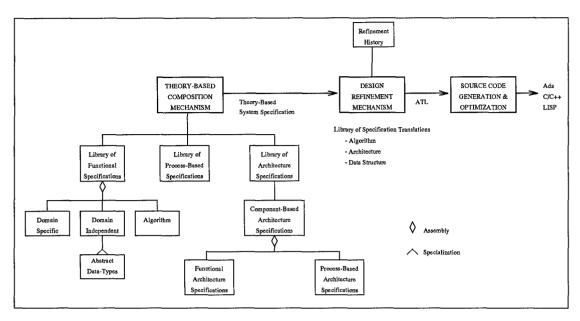

| 2.2 Composition Mechanism                | 2-2   |

| 2.2.1 Eunctional Specifications          | 9.9   |

|      |          |           |                                                     | $\mathbf{Page}$ |

|------|----------|-----------|-----------------------------------------------------|-----------------|

|      |          | 2.2.2     | Architecture Specifications                         | 2-7             |

|      |          | 2.2.3     | Using the Composition Mechanism                     | 2-8             |

|      | 2.3      | Design    | Refinement Mechanism (DRM)                          | 2-11            |

|      | 2.4      | Summa     | ry                                                  | 2-11            |

| III. | Combinin | g Theorie | es to Make Theories                                 | 3-1             |

|      | 3.1      | Introdu   | ction                                               | 3-1             |

|      | 3.2      | Basic D   | efinitions                                          | 3-3             |

|      |          | 3.2.1     | The Category Sign                                   | 3-4             |

|      |          | 3.2.2     | The Category Spec                                   | 3-11            |

|      | 3.3      | Specific  | ation Construction                                  | 3-18            |

|      |          | 3.3.1     | Basic Specification                                 | 3-18            |

|      |          | 3.3.2     | Translate                                           | 3-19            |

|      |          | 3.3.3     | Import                                              | 3-21            |

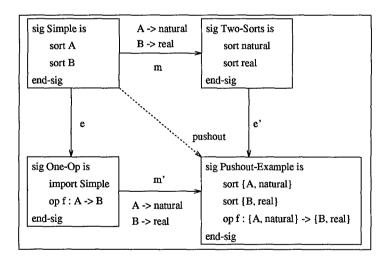

|      |          | 3.3.4     | Colimit                                             | 3-22            |

|      |          | 3.3.5     | Specification Interpretation                        | 3-25            |

|      |          | 3.3.6     | Summary of Specification Building Operations        | 3-26            |

|      | 3.4      | Institut  | ion-Based Specification Development                 | 3-27            |

|      | 3.5      | Summa     | ry                                                  | 3-32            |

| IV.  | Combinin | g Functio | onal and Process Specifications                     | 4-1             |

|      | 4.1      | Introdu   | ction                                               | 4-1             |

|      | 4.2      | Develop   | ment of a Specification for a Pipeline Application  | 4-2             |

|      |          | 4.2.1     | Introduction                                        | 4-2             |

|      |          | 4.2.2     | Problem Description                                 | 4-2             |

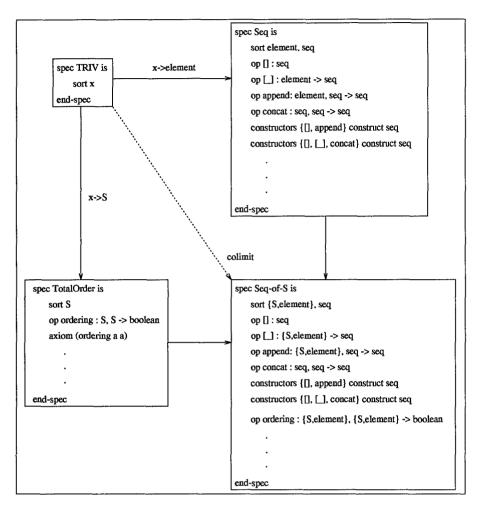

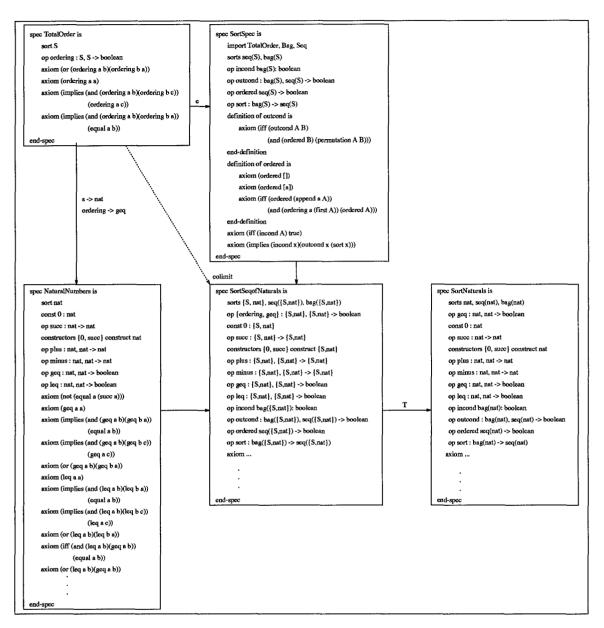

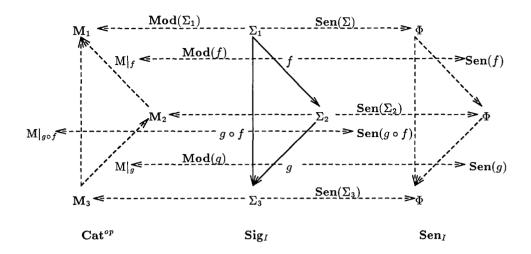

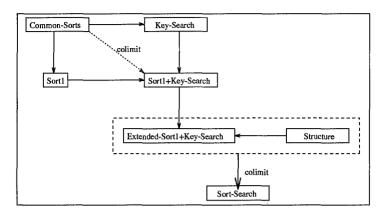

|      |          | 4.2.3     | Development of the Sort-Search Specification        | 4-3             |

|      |          | 4.2.4     | Observations                                        | 4-6             |

|      | 4.3      | Develop   | ment of the Four Sum Moving Average Unit Specifica- |                 |

|      |          | tion      |                                                     | 4-7             |

|     |            |                |                                                    | P |

|-----|------------|----------------|----------------------------------------------------|---|

|     |            | 4.3.1 Intro    | oduction                                           |   |

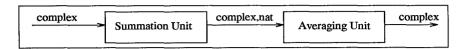

|     |            | 4.3.2 Prob     | olem Description                                   |   |

|     |            |                | elopment of a Specification for the Moving Average |   |

|     |            | 4.3.4 Obse     | ervations                                          |   |

|     | 4.4        | Summary        |                                                    |   |

| v.  | Mathema    | ical Foundatio | ns                                                 |   |

|     | 5.1        | Introduction   |                                                    |   |

|     | 5.2        | A Theory Pre   | esentation for CSP                                 |   |

|     | 5.3        | CSP Structur   | res                                                |   |

|     |            | 5.3.1 Synt     | ax                                                 |   |

|     |            | 5.3.2 Sema     | antics                                             |   |

|     |            | 5.3.3 Sum      | mary of CSP Structures                             |   |

|     | 5.4        | The Category   | of Process Signatures and Process Signature Mor-   |   |

|     |            | phisms         |                                                    |   |

|     |            | 5.4.1 Sum:     | mary                                               |   |

|     | 5.5        | The Category   | of Process Specifications and Process Specifica-   |   |

|     |            | tion Morphisi  | ms                                                 |   |

|     | 5.6        | -              | Between Functional and Process-Based Specifica-    |   |

|     |            |                | • • • • • • • • • • • • • • • • • • • •            |   |

|     |            | 5.6.1 Com      | ponents                                            |   |

|     |            | 5.6.2 The      | Category App                                       |   |

|     | 5.7        | Summary        |                                                    |   |

| VI. | Software . | architecture . |                                                    |   |

|     | 6.1        | Introduction   | • • • • • • • • • • • • • • • • • • • •            |   |

|     | 6.2        | Architecture   | Defined                                            |   |

|     |            | 6.2.1 Func     | tional Architecture Theory                         |   |

|      |            |           |                                                                   | Page        |

|------|------------|-----------|-------------------------------------------------------------------|-------------|

|      |            | 6.2.2     | Process Based Architecture Theory                                 | 6-13        |

|      |            | 6.2.3     | Component-Based Architecture Theory                               | 6-16        |

|      |            | 6.2.4     | Summary                                                           | 6-18        |

|      | 6.3        | Process   | Based Architecture Theories                                       | 6-19        |

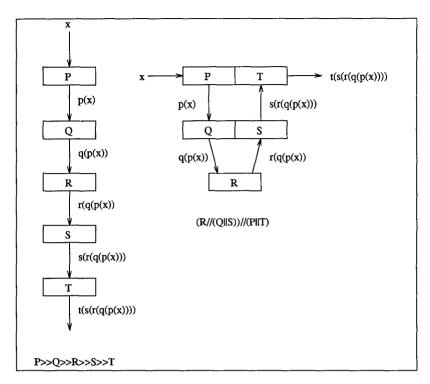

|      |            | 6.3.1     | Structuring Specifications                                        | 6-20        |

|      |            | 6.3.2     | General Parallel Structures                                       | 6-24        |

|      |            | 6.3.3     | Batch Architectures                                               | 6-49        |

|      |            | 6.3.4     | Composite Architectures                                           | 6-57        |

|      |            | 6.3.5     | Constraint-Based Architectures                                    | 6-60        |

|      | 6.4        | Summa     | ry                                                                | 6-63        |

| VII. | Analysis o | of Proces | s-Based Architecture Theories                                     | 7-1         |

|      | 7.1        | Introdu   | ction                                                             | 7-1         |

|      | 7.2        | Mather    | natical Foundations                                               | 7-1         |

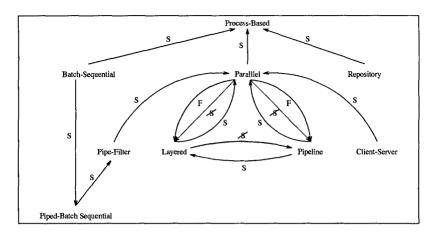

|      | 7.3        | Relatio   | nship Between Parallel and Layered Designs                        | 7-6         |

|      |            | 7.3.1     | Translating Layered Designs to Parallel Designs                   | 7-6         |

|      |            | 7.3.2     | Translating Parallel Designs to Layered Designs                   | 7-7         |

|      |            | 7.3.3     | Summary of the Relationship Between Parallel and Layered Designs  | <b>7-</b> 9 |

|      | 7.4        | Relatio   | nship Between Parallel and Pipeline Designs                       | 7-10        |

|      |            | 7.4.1     | Translating Parallel Designs to Pipeline Designs                  | 7-10        |

|      |            | 7.4.2     | Translating Pipeline Designs to Parallel Designs                  | 7-13        |

|      |            | 7.4.3     | Summary of the Relationship Between Parallel and Pipeline Designs | 7-14        |

|      | 7.5        | Relatio   | nship Between Layered and Pipeline Designs                        | 7-15        |

|      |            | 7.5.1     | Translating Layered Designs to Pipelined Designs                  | 7-15        |

|      |            | 7.5.2     | Translating Pipeline Designs to Layered Designs                   | 7-16        |

|      |            | 7.5.3     | Summary of the Relationship Between Layered and Pipeline Designs  | 7-19        |

|      |            |           | ripomiio Dosiglis                                                 | 1-T9        |

|       |             |          |                                                       | Page |

|-------|-------------|----------|-------------------------------------------------------|------|

|       | 7.6         | Other I  | Relationships                                         | 7-20 |

|       | 7.7         | Summa    | xy                                                    | 7-21 |

| VIII. | Feasibility | Demons   | stration                                              | 8-1  |

|       | 8.1         | Introdu  | ction                                                 | 8-1  |

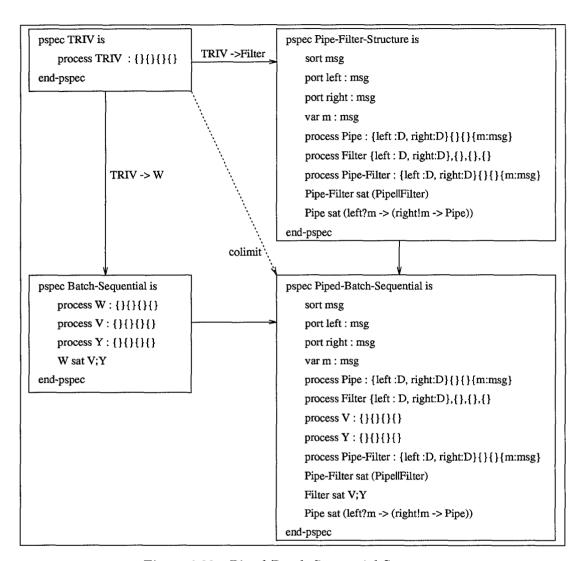

|       | 8.2         | Creatin  | g a Piped-Batch Sequential Design                     | 8-2  |

|       |             | 8.2.1    | Introduction                                          | 8-2  |

|       |             | 8.2.2    | Adding Communication                                  | 8-2  |

|       | 8.3         | Feature  | Selection Problem Description                         | 8-5  |

|       |             | 8.3.1    | Introduction                                          | 8-5  |

|       |             | 8.3.2    | Skeleton Problem Description                          | 8-5  |

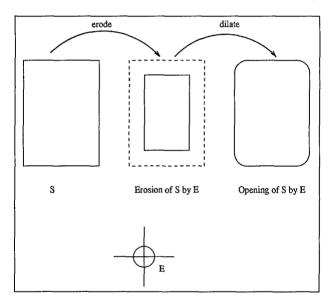

|       |             | 8.3.3    | Erode                                                 | 8-9  |

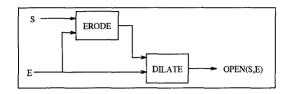

|       |             | 8.3.4    | Open                                                  | 8-13 |

|       |             | 8.3.5    | Summary                                               | 8-15 |

|       | 8.4         | Specific | ration Development                                    | 8-15 |

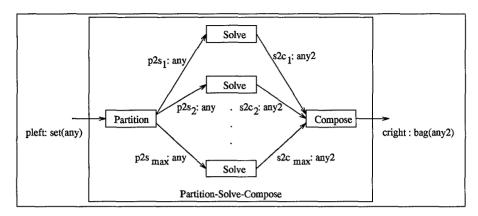

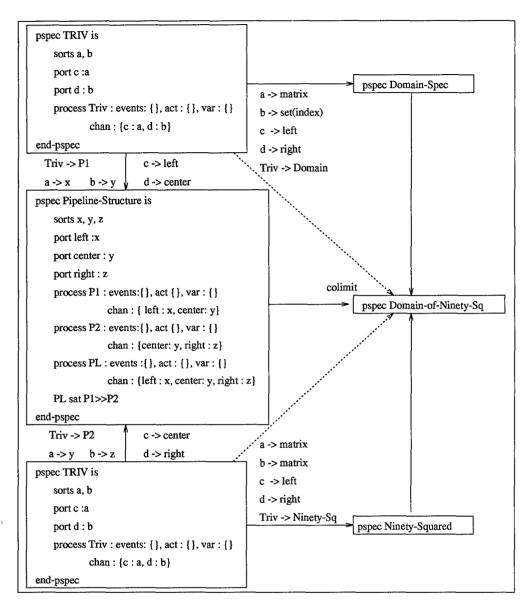

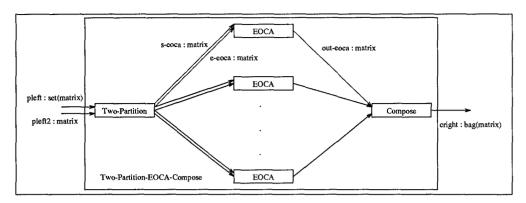

|       |             | 8.4.1    | Specification Development for Partition-Solve-Compose | 8-16 |

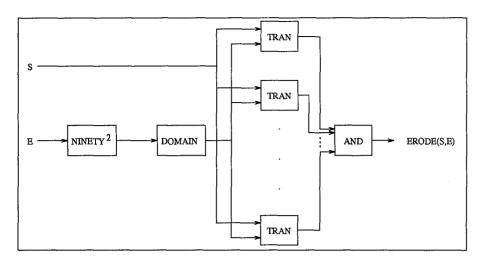

|       |             | 8.4.2    | Specification of Erosion                              | 8-22 |

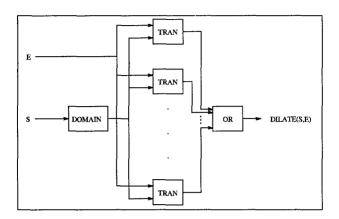

|       |             | 8.4.3    | Specification of Open and Dilate                      | 8-32 |

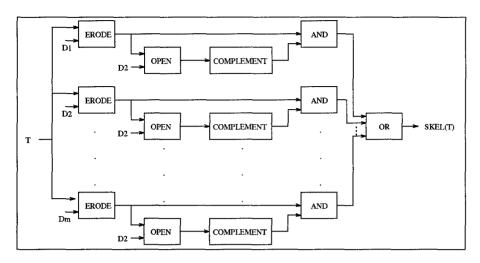

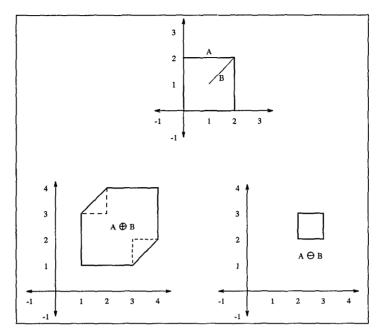

|       |             | 8.4.4    | Specification of Skeleton                             | 8-36 |

|       |             | 8.4.5    | Using Skeleton for Feature Selection                  | 8-45 |

|       | 8.5         | Summa    | ry                                                    | 8-47 |

| IX.   | Conclusion  | ns and R | ecommendations                                        | 9-1  |

|       | 9.1         | Conclus  | sions and Results                                     | 9-2  |

|       | 9.2         | Future   | Work                                                  | 9-3  |

|       | 9.3         | Summa    | ry                                                    | 9-7  |

|              |                                                       | Page   |

|--------------|-------------------------------------------------------|--------|

| Appendix A.  | Category Theory                                       | A-1    |

| A.1          | Initial and Terminal Objects                          | A-1    |

| A.2          | Homomorphisms                                         | A-1    |

| A.3          | Types of Morphism                                     | A-3    |

| Appendix B.  | Refinement of a Global Search Algorithm Theory        | B-1    |

| B.1          | Derivation of a Specialized Algorithm Theory          | B-1    |

| B.2          | Derivation of a Feasibility Filter                    | B-6    |

|              | B.2.1 Key-Search Feasibility Filter                   | B-6    |

|              | B.2.2 Find-Location Feasibility Filter                | B-7    |

| B.3          | Summary                                               | B-9    |

| Appendix C.  | An Informal Introduction to Components and Connectors | C-1    |

| C.1          | Components                                            | C-1    |

|              | C.1.1 Component Functional Specification              | C-1    |

|              | C.1.2 Component Interface Specification               | C-4    |

|              | C.1.3 Summary of Components                           | C-6    |

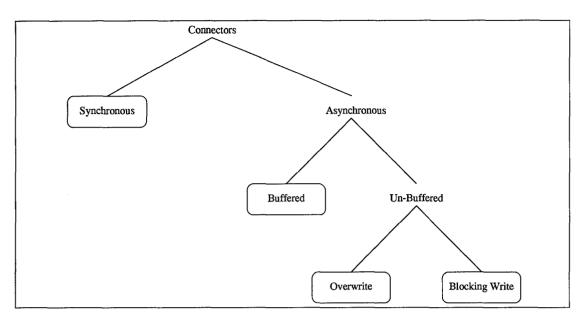

| C.2          | Connectors                                            | C-6    |

| C.3          | Summary                                               | C-10   |

| Appendix D.  | Constraints                                           | D-1    |

| D.1          | Introduction                                          | D-1    |

| D.2          | Constraints over operations                           | D-1    |

| D.3          | Constraints over process expressions                  | D-5    |

| D.4          | Recommendations for Future Research                   | D-6    |

| Bibliography |                                                       | BIB-1  |

| Vita         |                                                       | VITA_1 |

# List of Figures

| F | igure |                                                            | Page |

|---|-------|------------------------------------------------------------|------|

|   | 2.1.  | Software Development Using Architecture Specifications     | 2-2  |

|   | 2.2.  | Problem Theory                                             | 2-4  |

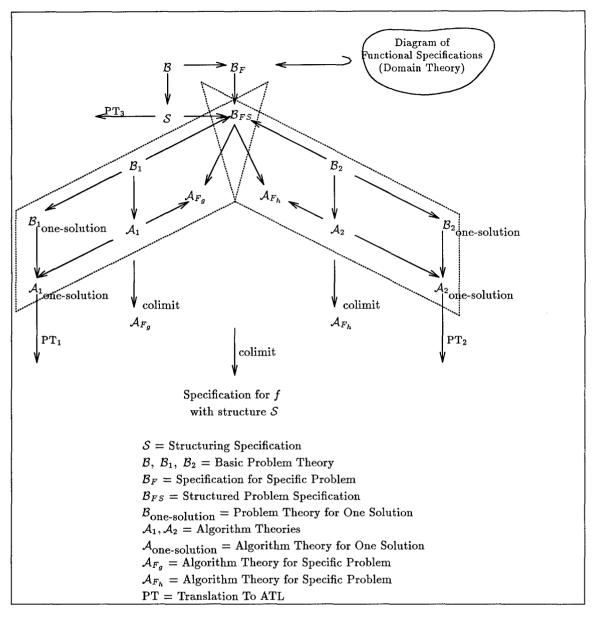

|   | 2.3.  | Global Search Theory                                       | 2-6  |

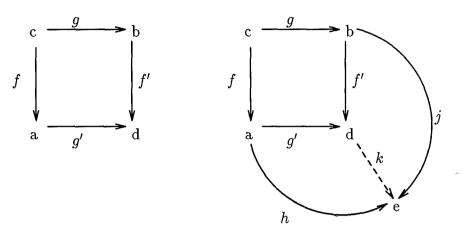

|   | 3.1.  | Definition of a Pushout                                    | 3-7  |

|   | 3.2.  | Example of a pushout involving signatures                  | 3-7  |

|   | 3.3.  | Using Pushouts to Instantiate Parameters                   | 3-8  |

|   | 3.4.  | Instantiation of a Signature for a List of Natural Numbers | 3-8  |

|   | 3.5.  | Definition of a Cone                                       | 3-10 |

|   | 3.6.  | Definition of a Colimit                                    | 3-11 |

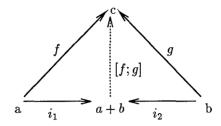

|   | 3.7.  | Coproduct Definition                                       | 3-12 |

|   | 3.8.  | Product Definition                                         | 3-12 |

|   | 3.9.  | A Specification for a Ring (106)                           | 3-14 |

|   | 3.10. | Definition of $seq(S)$                                     | 3-22 |

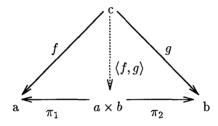

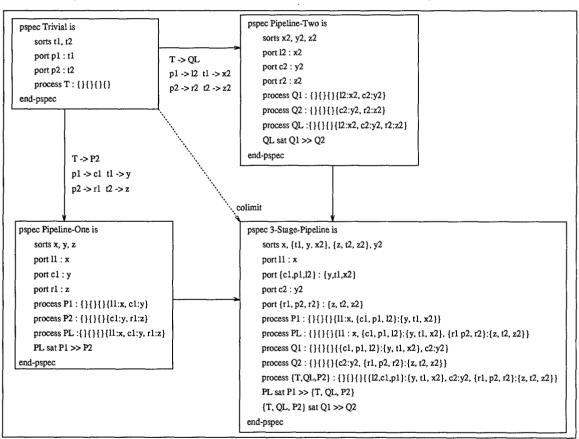

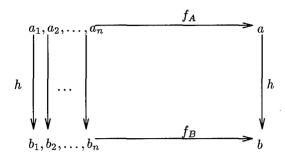

|   | 3.11. | Specification Building using the Colimit Operation         | 3-24 |

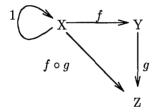

|   | 3.12. | Covariant and Contravariant Functors                       | 3-28 |

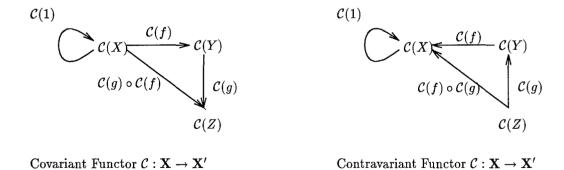

|   | 3.13. | An institution                                             | 3-30 |

|   | 4.1.  | Specifications for Searching an Ordered Sequence           | 4-2  |

|   | 4.2.  | Specification for Sorting a Sequence of Integers           | 4-2  |

|   | 4.3.  | Block diagram of the sort-search problem                   | 4-4  |

|   | 4.4.  | Problem Specification for Find-Location                    | 4-5  |

|   | 4.5.  | Structuring specification                                  | 4-7  |

|   | 4.6.  | Defining structure using a structuring specification       | 4-8  |

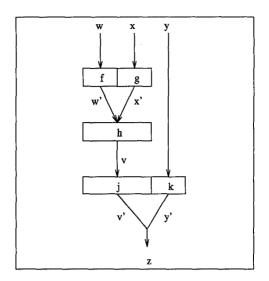

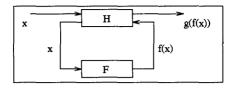

|   | 4.7.  | Block diagram for the moving average problem               | 4-9  |

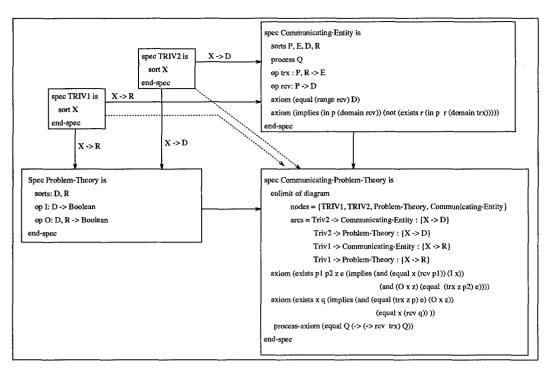

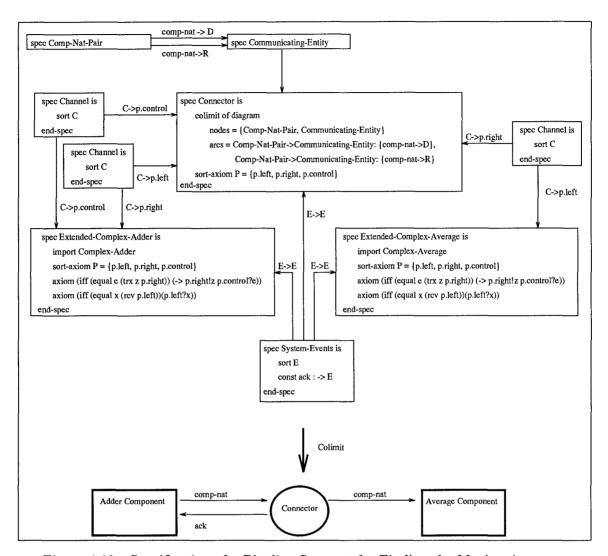

|   | 4.8.  | Communicating Entity Specification                         | 4-10 |

| F | igure |                                                                                                                                                                                                          | Page |

|---|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

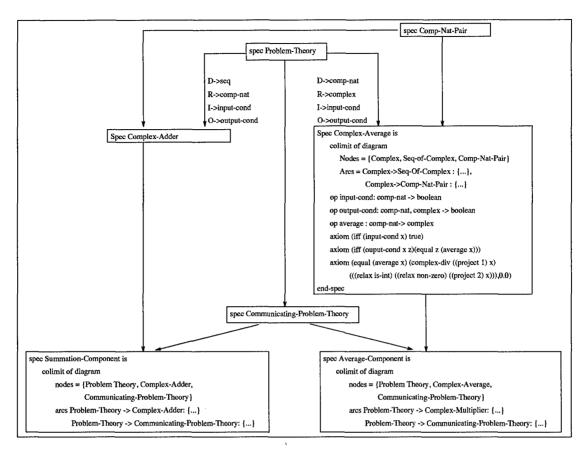

|   | 4.9.  | Specification of the Summation and Averaging Components                                                                                                                                                  | 4-12 |

|   | 4.10. | Specification of a Pipeline Segment for Finding the Moving Average                                                                                                                                       | 4-14 |

|   | 5.1.  | Mathematical Overview                                                                                                                                                                                    | 5-3  |

|   | 5.2.  | Signature of CSP Event Operators                                                                                                                                                                         | 5-7  |

|   | 5.3.  | Signature of CSP Process Operators                                                                                                                                                                       | 5-7  |

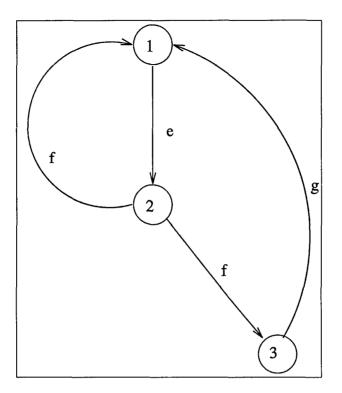

|   | 5.4.  | Pictorial Representation of the Process Defined by the Expression $P = e \xrightarrow{CSP} ((f \xrightarrow{CSP} P) \sqcap (f \xrightarrow{CSP} (g \xrightarrow{CSP} P))) \dots \dots \dots \dots \dots$ | 5-13 |

|   | 5.5.  | A Simple Process Signature                                                                                                                                                                               | 5-20 |

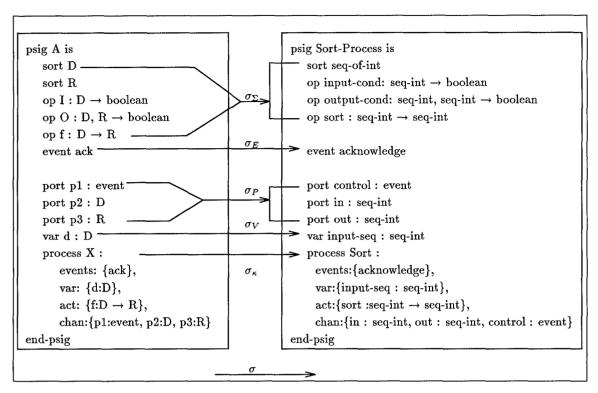

|   | 5.6.  | Process Signatures and Process signature Morphisms                                                                                                                                                       | 5-22 |

|   | 5.7.  | A Simple Process Specification                                                                                                                                                                           | 5-27 |

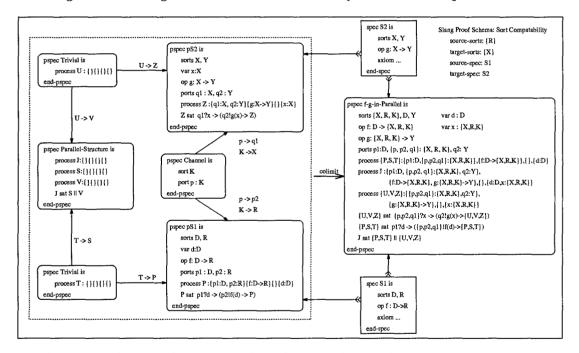

|   | 5.8.  | Proof Schemas                                                                                                                                                                                            | 5-34 |

|   | 5.9.  | A Simple Component                                                                                                                                                                                       | 5-35 |

|   | 5.10. | Mathematical Summary                                                                                                                                                                                     | 5-39 |

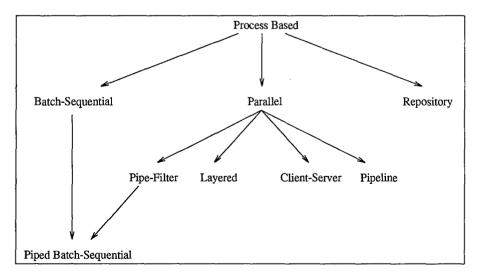

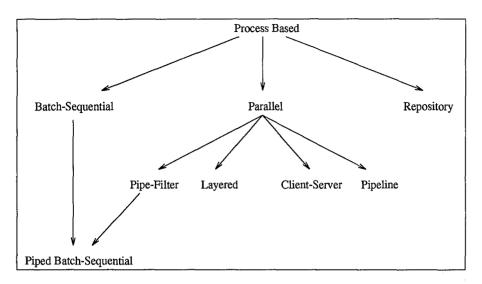

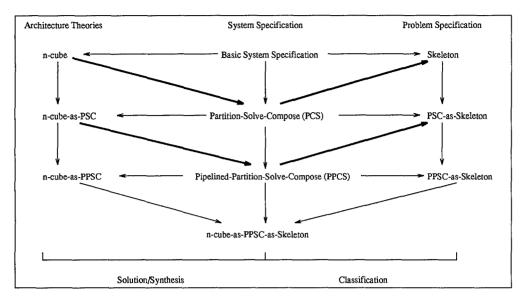

|   | 6.1.  | Architecture Taxonomy                                                                                                                                                                                    | 6-1  |

|   | 6.2.  | Operation Composition Using a Functional Architecture                                                                                                                                                    | 6-7  |

|   | 6.3.  | Using Functional Architecture Theory to Decompose an Operation (Based on (57))                                                                                                                           | 6-12 |

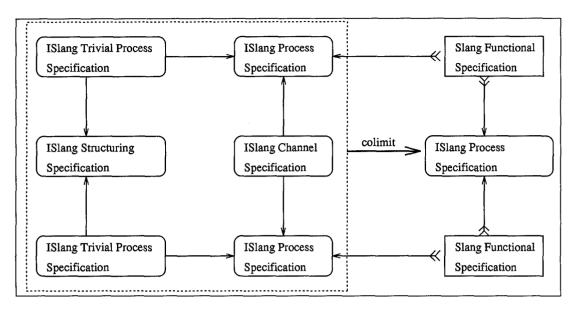

|   | 6.4.  | Using Process Specifications to Define Structure                                                                                                                                                         | 6-22 |

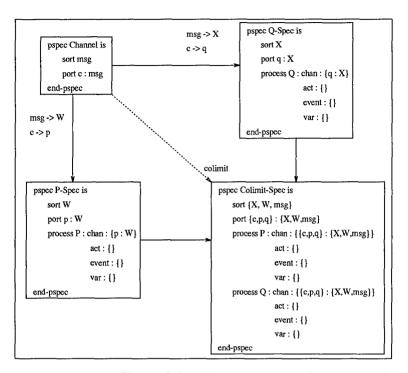

|   | 6.5.  | Using Channel Specifications to Unify Port Symbols                                                                                                                                                       | 6-23 |

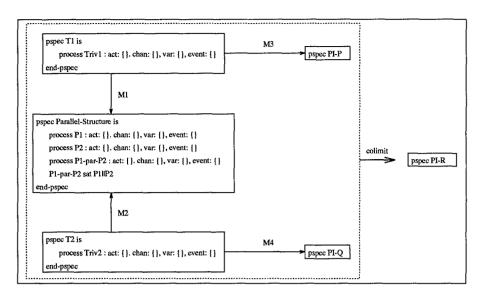

|   | 6.6.  | Using Parallel Architecture Theory to Construct Specifications                                                                                                                                           | 6-27 |

|   | 6.7.  | Using a Structuring Specification of a Parallel Architecture Theory                                                                                                                                      | 6-27 |

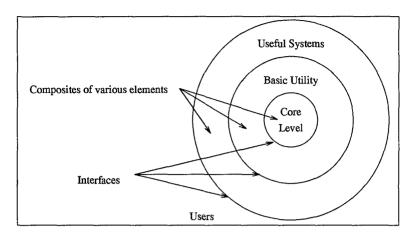

|   | 6.8.  | Layered Systems (Based on (38))                                                                                                                                                                          | 6-29 |

|   | 6.9.  | Simple Layered Processes                                                                                                                                                                                 | 6-33 |

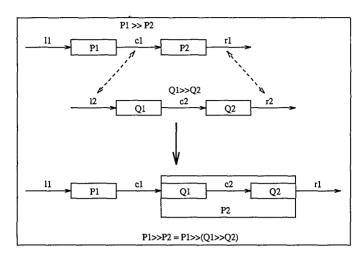

|   | 6.10. | Recursive Application of Pipeline Structuring Specification                                                                                                                                              | 6-38 |

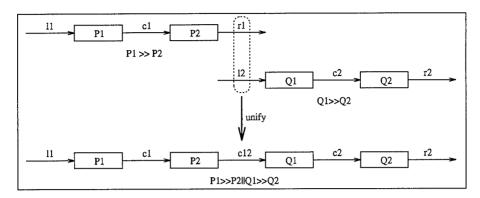

|   | 6.11. | ISlang Diagram Depicting Recursive Application of Structuring Specifications                                                                                                                             | 6-38 |

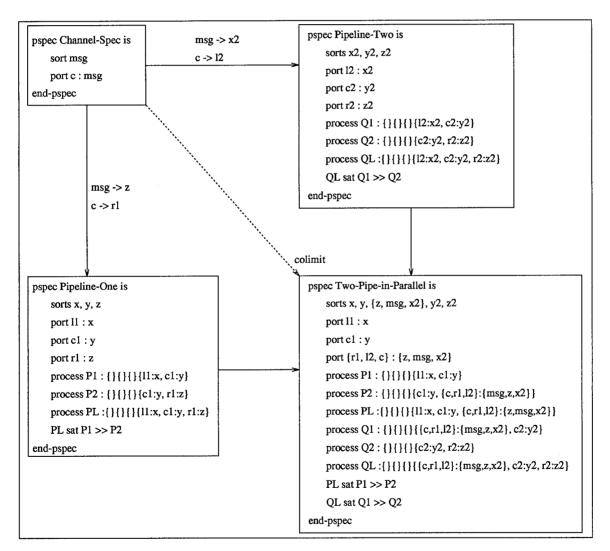

|   | 6 19  | Channel Specifications and Pipeline Structure                                                                                                                                                            | 6-40 |

|   | 0.14. | Charlier production and I ipointe but detaile                                                                                                                                                            | 0-40 |

| Figure |                                                                  | Page |

|--------|------------------------------------------------------------------|------|

| 6.13.  | An ISlang Diagram for Two 2-Stage Pipelines in Parallel          | 6-40 |

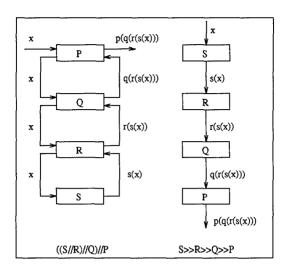

| 6.14.  | Comparison of Layered versus Pipelined Operation                 | 6-42 |

| 6.15.  | Client-Server Structuring Specification                          | 6-45 |

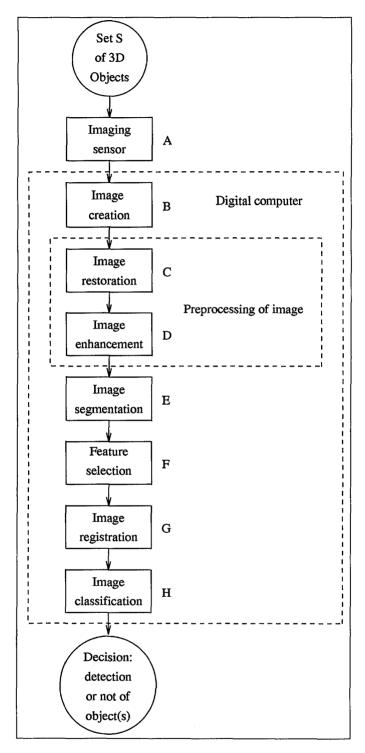

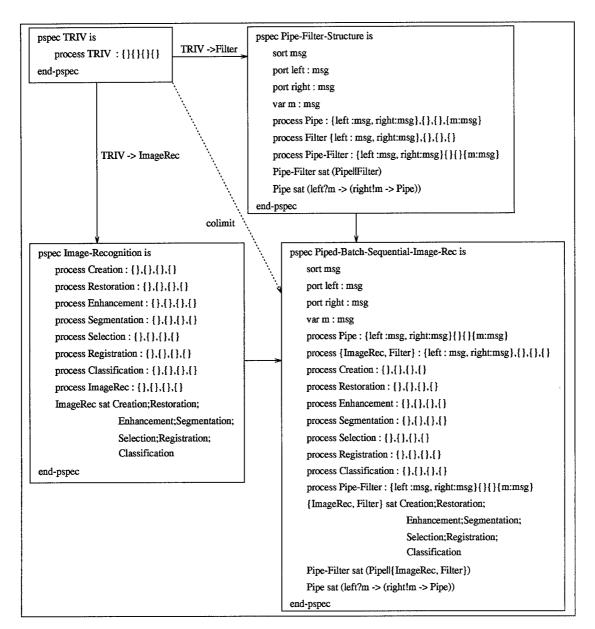

| 6.16.  | Some Stages for Image Recognition Systems (33:295)               | 6-52 |

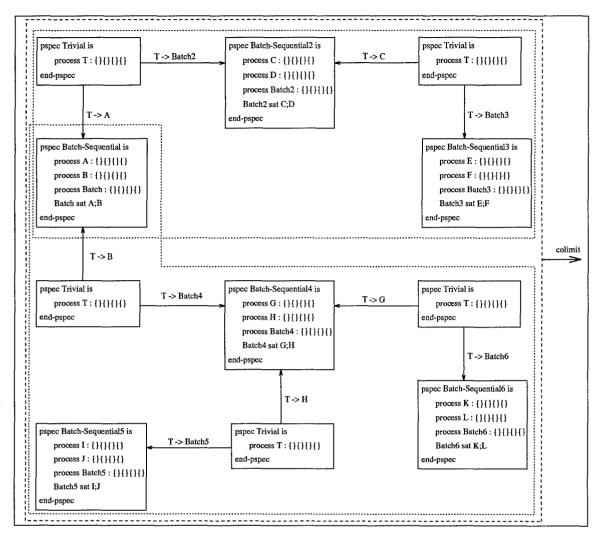

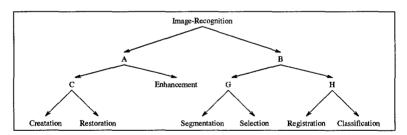

| 6.17.  | Creation of a Seven Segment Batch-Sequential Design              | 6-54 |

| 6.18.  | A Batch-Sequential Specification for Image Recognition           | 6-56 |

| 6.19.  | Source of Process Symbols                                        | 6-56 |

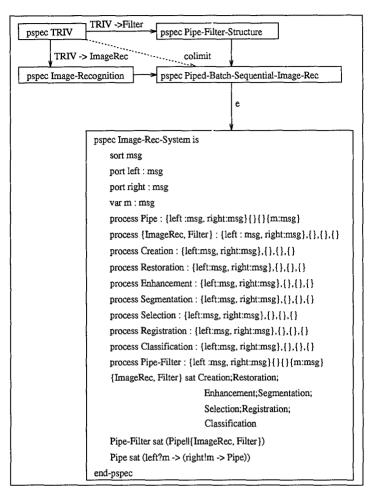

| 6.20.  | Piped Batch-Sequential Structure                                 | 6-59 |

| 6.21.  | Architecture Taxonomy                                            | 6-64 |

| 7.1.   | Translating a Pipeline Design to a Layered Design                | 7-17 |

| 7.2.   | Design Translation                                               | 7-22 |

| 7.3.   | Relative Expressive Power of Process Based Architecture Theories | 7-23 |

| 8.1.   | Piped-Batch Sequential Image Recognition                         | 8-3  |

| 8.2.   | Image Recognition Extended with Communication                    | 8-4  |

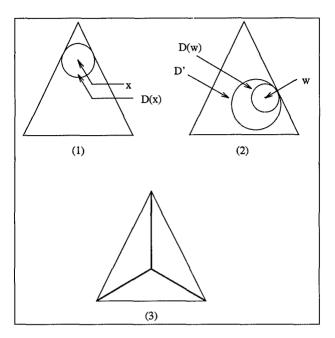

| 8.3.   | Determining skeleton for isosceles triangle (33:352)             | 8-6  |

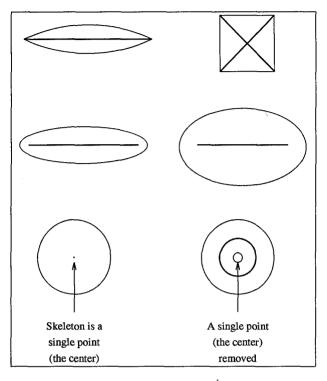

| 8.4.   | Skeleton for various pictures (33:352)                           | 8-7  |

| 8.5.   | Square disks of increasing size (33:353)                         | 8-8  |

| 8.6.   | Block diagram of SKEL (33:355)                                   | 8-9  |

| 8.7.   | Minkowski addition and subtraction                               | 8-11 |

| 8.8.   | Block diagram of DILATE (33:342)                                 | 8-12 |

| 8.9.   | Block diagram of ERODE (33:345)                                  | 8-13 |

| 8.10.  | Opening in terms of dilation and erosion (33:334)                | 8-13 |

| 8.11.  | Block diagram of OPEN (33:347)                                   | 8-14 |

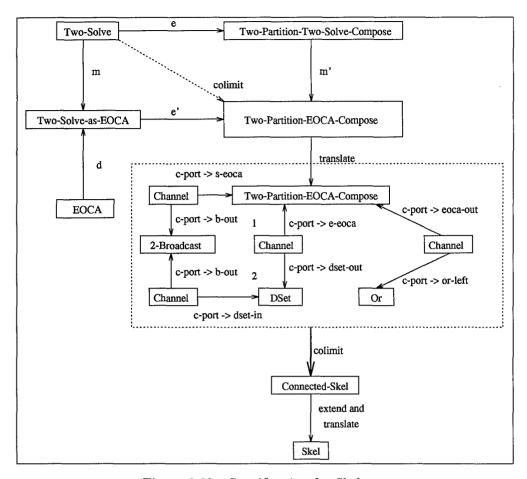

| 8.12.  | Block diagram of Partition-Solve-Compose                         | 8-17 |

| 8.13.  | Specification for Partition-Solve-Compose                        | 8-18 |

| 8.14.  | Specification for Two-Partition-Solve-Compose                    | 8-21 |

| Figure |                                                                          | Page |

|--------|--------------------------------------------------------------------------|------|

| 8.15.  | Specification for Ninety <sup>2</sup>                                    | 8-23 |

| 8.16.  | Specification for Domain                                                 | 8-23 |

| 8.17.  | Specification for Translate                                              | 8-24 |

| 8.18.  | Specification for the Logical Operations And and Or                      | 8-24 |

| 8.19.  | Specification Construction for Domain $\gg$ Ninety-Sq                    | 8-25 |

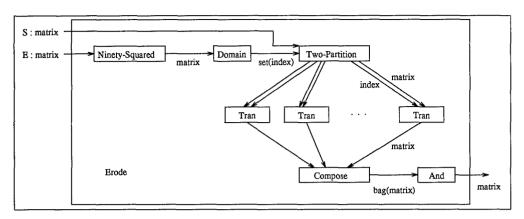

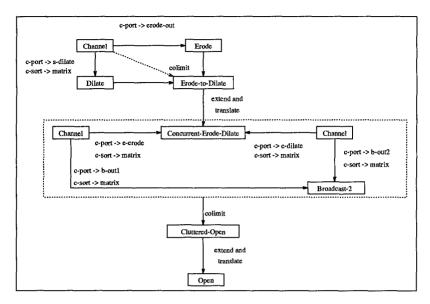

| 8.20.  | Structure of Erode                                                       | 8-26 |

| 8.21.  | Specification for Ninety <sup>2</sup> -Domain Pipeline                   | 8-27 |

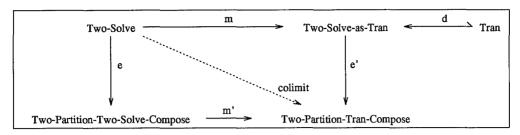

| 8.22.  | Specification for Two-Solve-as-Tran                                      | 8-28 |

| 8.23.  | Specification Diagram for Two-Partition-Tran-Compose                     | 8-29 |

| 8.24.  | Specification for Two-Partition-Tran-Compose                             | 8-30 |

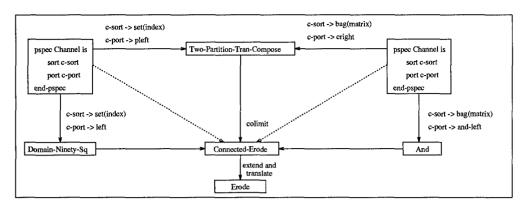

| 8.25.  | Specification for Erode                                                  | 8-32 |

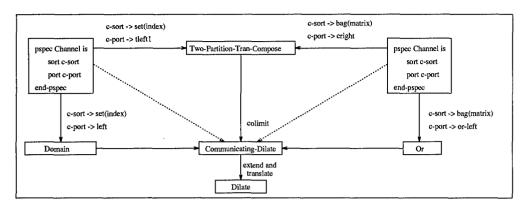

| 8.26.  | Specification for Dilate                                                 | 8-33 |

| 8.27.  | Specification for Open                                                   | 8-36 |

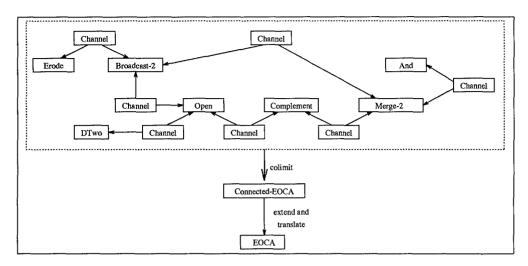

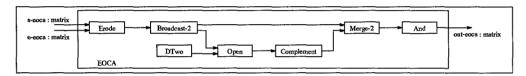

| 8.28.  | Specification for EOCA                                                   | 8-39 |

| 8.29.  | Communication Network for EOCA                                           | 8-39 |

| 8.30.  | Communication Network for Two-Partition-EOCA-Compose                     | 8-41 |

| 8.31.  | Specification for DSet                                                   | 8-43 |

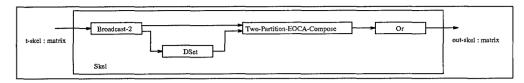

| 8.32.  | Specification for Skeleton                                               | 8-44 |

| 8.33.  | Process Communication in Skeleton                                        | 8-45 |

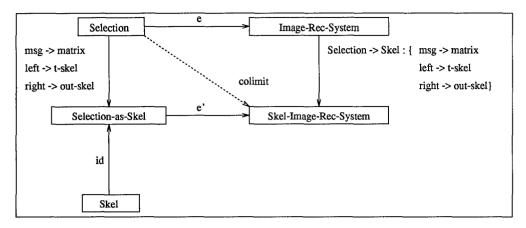

| 8.34.  | Selection as Skeleton in Image Recognition                               | 8-47 |

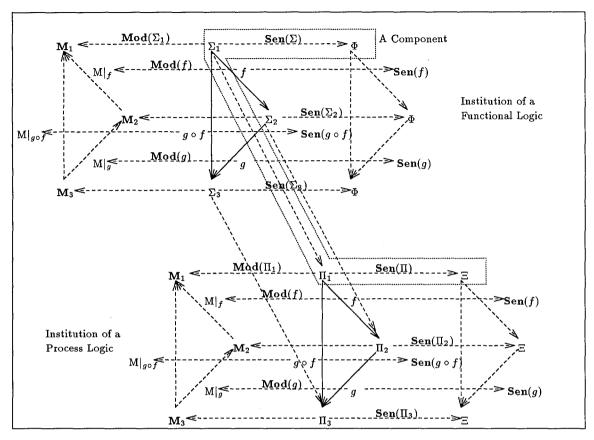

| 9.1.   | Formalizing the Relationship Between Functional and Process Institutions | 9-4  |

| 9.2.   | Using Architecture Theories                                              | 9-6  |

| 3.2.   | Osing Architecture Theories                                              | 9-0  |

| A.1.   | Homomorphism                                                             | A-2  |

| B.1.   | Problem Specification for Find-Location                                  | B-1  |

| B.2.   | Global Search Algorithm Theory Morphism                                  | B-2  |

| B.3.   | Global Search Theory                                                     | B-3  |

| Figure |                                            | Page |

|--------|--------------------------------------------|------|

| B.4.   | Specialized Global Search Algorithm Theory | B-5  |

| B.5.   | Key-Search Problem Specification           | B-6  |

| B.6.   | Domain Specific Rules                      | B-7  |

| B.7.   | Domain Specific Rules Incorporating Sort1  | B-10 |

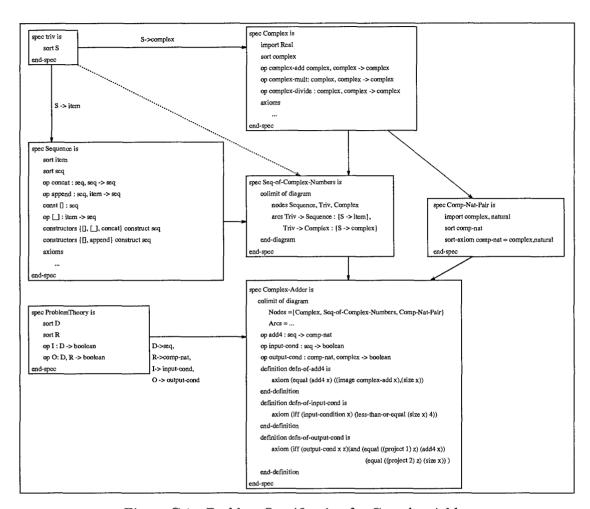

| C.1.   | Problem Specification for Complex Adder    | C-5  |

| C.2.   | Communication Taxonomy (based on (112))    | C-6  |

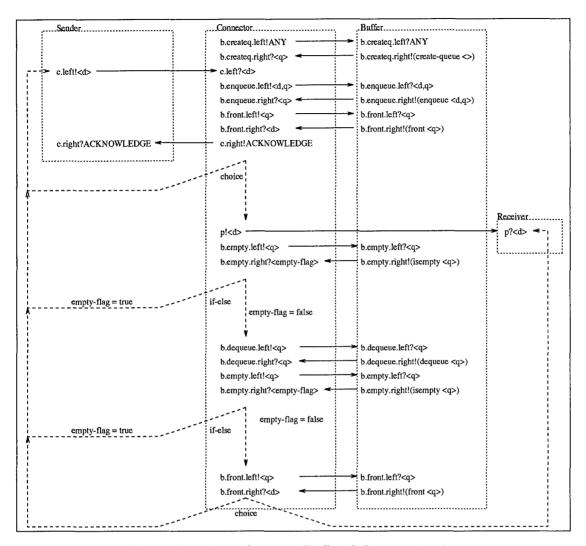

| C.3.   | Asynchronous Buffered Communication        | C-8  |

# $List\ of\ Tables$

| $\operatorname{Table}$ |                                                                                           | Page |

|------------------------|-------------------------------------------------------------------------------------------|------|

| 4.1.                   | Output of the Four Sum Moving Average                                                     | 4-9  |

| 6.1.                   | Properties of the Operations $\cdot$ and $\circ$                                          | 6-10 |

| B.1.                   | Derivation of Additional Terms                                                            | B-5  |

| B.2.                   | Generation of Terms for the Key-Search Feasibility Filter                                 | B-8  |

| B.3.                   | Generation of Terms for the Find-Location Feasibility Filter                              | B-9  |

| B.4.                   | Generation of Feasibility Filter Terms for Find-Location using the Enhanced Domain Theory | B-11 |

| D.1.                   | Proof of Input Condition Satisfaction                                                     | D-3  |

# List of Symbols

| Symbol                                                                                                                                                                                                     | Page |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| D  Objects of a Category D                                                                                                                                                                                 | 3-4  |

| $D^{op}$ Opposite Category                                                                                                                                                                                 | 3-4  |

| $\Sigma = \langle S, \Omega \rangle$ Signature                                                                                                                                                             | 3-4  |

| Sign Category of Signatures                                                                                                                                                                                | 3-5  |

| = Logical Consequence                                                                                                                                                                                      | 3-11 |

| $\langle \Sigma, \Phi \rangle$ Specification, Theory $\dots \dots \dots \dots \dots \dots \dots \dots \dots \dots$                                                                                         | 3-12 |

| Sen[ $\Sigma$ ] $\Sigma$ -sentences                                                                                                                                                                        | 3-12 |

| Mod[SP] Models of a Specification SP                                                                                                                                                                       | 3-12 |

| $A = \langle A_S, F_A \rangle$ A $\Sigma$ -Algebra                                                                                                                                                         | 3-12 |

| $A'\mid_{\sigma} \mathrm{Reduct}$                                                                                                                                                                          | 3-15 |

| $	ilde{=}$ Isomporphic                                                                                                                                                                                     | 3-16 |

| $\overline{\Phi}$ Closure                                                                                                                                                                                  | 3-17 |

| $\hookrightarrow$ Importation                                                                                                                                                                              | 3-21 |

| $A \xrightarrow{s} A$ -as- $B \xleftarrow{d} B$                                                                                                                                                            | 3-25 |

| $\mathcal{F}:\mathbf{X} \to \mathbf{X}'$ Functor                                                                                                                                                           | 3-27 |

| $\langle \mathbf{Sig}_I,  \mathbf{Sen}_I,  \mathbf{Mod}_I, \models \rangle$ Institution                                                                                                                    | 3-29 |

| $\mathbf{Sig}_I$ Category of signatures and signature morphisms                                                                                                                                            | 3-29 |

| $\mathbf{Sen}_I: \mathrm{Sig}_I 	o \mathbf{Set}$ Functor from the category $\mathbf{Sig}$ to the category $\mathbf{Set}$                                                                                   | 3-29 |

| $\mathbf{Mod}_I : \mathrm{Sig}_I \to \mathrm{Cat}^{op}$ Contravariant functor from the category $\mathbf{Sig}$ to the category $\mathbf{Cat}^{op} \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 3-29 |

| $\models_{I,\Sigma}$ Satisfaction Relation                                                                                                                                                                 | 3-29 |

| $T_\Sigma(X)$ Terms                                                                                                                                                                                        | 5-5  |

| $T_{CSP}(X)$                                                                                                                                                                                               | 5-6  |

| $\Pi = \langle \Sigma, E, P, V, \kappa \rangle$ Process signature                                                                                                                                          | 5-17 |

| $\equiv_T$ Trace equivalence                                                                                                                                                                               | 5-27 |

| chan <sub>internal</sub> (P) Internal channels of a process P                                                                                                                                              | 6-34 |

| Symbol                                                                                          | Page |

|-------------------------------------------------------------------------------------------------|------|

| $\operatorname{chan}_{\operatorname{external}}(P)$ Internal channels of a process structure $P$ | 6-34 |

| $\sqsubseteq$ External compatibility                                                            | 7-2  |

| $\equiv_c$ External equivalence                                                                 | 7-2  |

| $\mathcal{D}(A,B)$ Dilation                                                                     | 8-10 |

| $\mathcal{E}(A,B)$ Erosion                                                                      | 8-10 |

| $D_A$ Domain of A                                                                               | 8-10 |

| O(A,B) Opening                                                                                  | 8-13 |

| OPEN(A,B) Digital opening                                                                       | 8-14 |

# List of Abbreviations

| Abbreviation                                             | Page |

|----------------------------------------------------------|------|

| CARDS Comprehensive Approach for Reusable Software       | 1-2  |

| DSSA Domain Specific Software Architecture               | 1-4  |

| ADAGE Avionics Domain Application Generation Environment | 1-4  |

| OCU Object-Connection-Update                             | 1-5  |

| SEI Software Engineering Institute                       | 1-5  |

| J-MASS Joint Modeling and Simulation System              | 1-7  |

| LEAP Lockheed Environment for Automatic Programming      | 1-8  |

| GUI Graphical User Interface                             | 1-8  |

| CIDL Common Intermediate Design Language                 | 1-8  |

| KIDS Kestrel Interactive Development System              | 1-8  |

| ADL Architecture Description Language                    | 1-10 |

| MIL Module Interconnection Language                      | 1-11 |

| CM Composition Mechanism                                 | 2-3  |

| DRM Design Refinement Mechanism                          | 2-11 |

| ATL Abstract Target Language                             | 2-11 |

| LTS Labeled Transition System                            | 5-11 |

| FAT Functional Architecture Theory                       | 6-5  |

| PAT Process Based Architecture Theory                    | 6-13 |

| CAT Component-Based Architecture Theory                  | 6-17 |

# List of Definitions

| Definition                        | Page |

|-----------------------------------|------|

| Category                          | 3-3  |

| Signature and signature morphisms | 3-4  |

| Extension                         | 3-5  |

| Pushout                           | 3-6  |

| Diagram                           | 3-10 |

| Cone                              | 3-10 |

| Colimit                           | 3-10 |

| Coproduct                         | 3-11 |

| Product                           | 3-11 |

| Logical Consequence               | 3-11 |

| Specification                     | 3-12 |

| Algebra                           | 3-12 |

| Homomorphism                      | 3-15 |

| Reduct                            | 3-15 |

| Specification Morphism            | 3-16 |

| Closure, Closed                   | 3-17 |

| Theory presentation               | 3-17 |

| Interpretation                    | 3-25 |

| Functor                           | 3-27 |

| Contravariant Functor             | 3-28 |

| Institution                       | 3-29 |

| Indexed collection of sets        | 5-4  |

| Terms                             | 5-5  |

| Value                             | 5-5  |

| CQP.                              | 55   |

| Definition                                                 | Page |

|------------------------------------------------------------|------|

| $T_{CSP}(X)$                                               | 5-6  |

| CSP structure                                              | 5-9  |

| Labeled transition system                                  | 5-11 |

| Automaton                                                  | 5-11 |

| CSP process state                                          | 5-13 |

| Initial State                                              | 5-14 |

| Final State                                                | 5-14 |

| Next-State Relation                                        | 5-14 |

| CSP Automaton                                              | 5-15 |

| Process signatures                                         | 5-17 |

| Relationship between CSP structures and Process Signatures | 5-18 |

| Process signature morphisms                                | 5-21 |

| Process specification                                      | 5-25 |

| Satisfaction                                               | 5-27 |

| Process specification morphisms                            | 5-29 |

| Component                                                  | 5-34 |

| Consistency                                                | 5-35 |

| Component Models                                           | 5-37 |

| Component Morphisms                                        | 5-37 |

| Architecture Theory                                        | 6-3  |

| Design                                                     | 6-3  |

| Functional Architecture Theory                             | 6-5  |

| Syntactically well-formed                                  | 6-5  |

| Semantically well-formed                                   | 6-6  |

| Process-Based Architecture Theory                          | 6-13 |

| Component-Based Architecture Theory                        | 6-17 |

| Structuring specification                                  | 6-21 |

|                                      | D    |

|--------------------------------------|------|

| Definition                           | Page |

| Parallel processes                   | 6-24 |

| Parallel Architecture Theory         | 6-25 |

| Layered processes                    | 6-30 |

| Layered Architecture Theory          | 6-31 |

| Internal and External channels       | 6-34 |

| Pipelined processes                  | 6-34 |

| Pipeline Architecture Theory         | 6-35 |

| Server                               | 6-43 |

| Client                               | 6-43 |

| Client-Server processes              | 6-43 |

| Client-Server Architecture Theory    | 6-44 |

| Pipe                                 | 6-46 |

| Filter                               | 6-46 |

| Pipe-Filter processes                | 6-46 |

| Pipe-Filter Architecture Theory      | 6-47 |

| Batch-Sequential processes           | 6-50 |

| Batch-Sequential Architecture Theory | 6-50 |

| Piped-Batch Sequential Processes     | 6-57 |

| Piped-Batch Sequential Architecture  | 6-58 |

| Constraint-Based Architecture Theory | 6-60 |

| Repository processes                 | 6-61 |

| Repository Architecture Theory       | 6-62 |

| External Compatibility               | 7-2  |

| External Compatibility               | 7-4  |

| Euclidean skeleton                   | 8-6  |

| Translate                            | 8-7  |

| Skeleton                             | 8-8  |

| Definition           | Page |

|----------------------|------|

| Complement           | 8-9  |

| Minkowski difference | 8-10 |

| Minkowski sum        | 8-10 |

| Erosion              | 8-10 |

| Domain               | 8-10 |

| And, Or              | 8-11 |

| Minkowski addition   | 8-11 |

| dilation             | 8-11 |

| ERODE                | 8-12 |

| Opening              | 8-13 |

| OPEN                 | 8-14 |

| SKEL                 | 8-14 |

| Derived Antecedent   | Dз   |

# Abstract

This investigation establishes a formal foundation for software architecture that allows for the specification of large, non-trivial software systems using well founded, consistency preserving construction techniques. Two fundamental problems were addressed: how to define and express architectures formally using the concept of theories, and how architecture theories can be practically applied in specification construction. The initial stages of this investigation sought to establish a formal, mathematical relationship between functional specifications of behavior and specifications defining system structure. Experimental results lead to the conclusion that architectures defining the structure of functional operations can be defined using functional logic, but more complex architectures require a separate process logic. A process logic based on Hoare's Communicating Sequential Processes (CSP) was selected for representing and reasoning about system structure and was used in the definition of a process-based specification development system. Specifically, CSP was used to define a category of process-based specifications and specification morphisms. This allowed well-founded specification construction techniques such as specification morphisms, colimits, and interpretations to be applied to the construction of consistent software architecture. Architecture theories expressed in terms of functional and process-based specifications were defined, and translations between these architecture theories were investigated. A feasibility analysis on an image processing application demonstrated that architecture theories can be used to develop specifications for large, non-trivial applications.

### FORMAL FOUNDATIONS

## FOR THE

# SPECIFICATION OF

# SOFTWARE ARCHITECTURE

### I. Introduction

"Software Development will not become software engineering until the traditional methods of engineering are incorporated." Richard D'Ippolito. (30:256)

### 1.1 Purpose and Motivation

Traditional engineering makes extensive use of models and libraries of reusable entities; "without reusable technology, engineering could not support the level of productivity and product success that it now enjoys." (30:256) The lessons of engineering have not been lost on the software profession; software researchers and developers have been concerned about re-usability for some time. In 1967, McIlroy (71) "proposed the idea of a software components catalog from which software parts could be assembled, much as is done with mechanical or electronic parts;" (83:99) McIlroy envisioned "interchangeable source code parts." (85) Although research continues in the area of reusing source code, over time the emphasis of re-usability has changed; there is now an increased emphasis on reusing knowledge, such as domain theories and specialization information, rather than reusing the implementation.

Knowledge can be reused in several ways. One of these is to reuse knowledge about architecture. Before proceeding, the use of the term "architecture" needs to be clarified. Different authors have different definitions of architecture:

- A unifying or coherent form or structure; a method or style of building. (68)

- A selection from a set of models and rules of composition that defines the structure, performance, and use of a system relative to a set of engineering goals. (61)

• The high level packaging structure of functions and data, their interfaces and controls, to support the implementation of applications in a domain. (58)

An architecture defines the entities of a system and defines composition rules for these entities. Pipelines are an example of an architecture. The entities in a pipeline architecture are pipes and stages, and the composition rules state that stages can be connected to other stages only through a pipe such that the resulting structure is acyclic and connected.

Some developmental systems such as REACTO (124) directly incorporate architectural notions. Specifications developed in the REACTO environment are based on an implicit architecture for hierarchical state machines. Other systems, such as the Central Archive for Reusable Software (CARDS),(123, 122) use knowledge structures to explicitly represent the architecture of a collection of related applications. In CARDS, new systems are created by instantiating the architectural models defined in these knowledge structures. CARDS explicitly represents potential architectural solutions for related applications, but the definition of architecture in CARDS is informal. One of the purposes of this investigation is to make explicit and formal the definition and use of software architecture in the development of software specifications.

# 1.2 Investigation Overview

The basic premise of this investigation is that software architecture can be formally defined and used to develop specifications for complex applications where such specifications are constructed using well defined, consistency preserving techniques. Algebraic specifications are one such technique, and they form the basis of this investigation.

In general, algebraic specifications consist of three parts: (108:107)

- Signatures: Each specification has a collection of sort names and operation names.

A signature identifies the basic [elements] of the domain being described, and thus forms a vocabulary for the domain.

- 2. Axioms: These are formulas generated using the vocabulary provided by the signature. The axioms define the behavior of the operations in terms of properties of values in the sorts.

3. Models: Models are usually algebras which form the denotation of the specification.

An algebra corresponding to a signature provides a set for each sort and a function or relation for each operation. The behavior of these sets, functions, and relations are such that they satisfy the axioms.

Axioms are expressed in a logic appropriate for the domain. Functional (stateless) specifications can be expressed in first order predicate calculus. Other logics, such as modal logic, can also be used to define specifications. See, for example, (96, 62) or (77) for a treatment of reactive system specification. The interested reader can find any number of articles and texts describing algebraic specification, such as (108, 91, 119, 16, 24, 54, 34, 35, 111, 127, 128, 23, 42, 43, 40, 56, 91, 45, 41) and (49).

Algebraic specifications are used in this investigation to define architecture. Conceptual foundations for the definition of architecture were established through an investigation of the relationship between algebraic specification and architectural structure. After establishing the conceptual relationship between architecture and algebraic specification, a formal definition of architecture is developed and several architectures are defined within a specification framework. Specifically, three types of architecture are formally defined:

- 1. A functional (stateless) architecture expressed within a higher order logic;

- 2. A process-based architecture expressed within a process logic; and

- 3. A component-based architecture, where specifications are expressed using both higherorder logic and process logic.

Several process-based architecture specifications are formally defined, including pipeline, layered, repository, batch-sequential, and client-server, and relationships between various process-based architectures are investigated.

The feasibility of using architecture specifications in the development of large, non-trivial software specifications is demonstrated through the development of a specification for a portion of an image recognition application. Architecture specifications provide a mechanism through which algebraic specification can be scaled up to the specification of large, complex problems.

This investigation includes a description of a software development formalism based on the concept of software architecture. This research, like the CARDS system, places an emphasis on reusing domain knowledge. However, it is on a more formal basis than that of CARDS. Instead of composing code fragments together to define an application, our formalism can be used to create an application from algebraic specifications. The software development formalism incorporates category theory, architecture specifications, and advances in domain modeling. It allows the system developer to create application specifications, specialize algorithm specifications, explore communications issues, and translate specifications from one architecture to another.

Related work is described in the following section. The assumptions and contributions of this investigation are described in Section 1.4 and Section 1.5, respectively. Section 1.6 outlines the sequence of presentation.

### 1.3 Related Work

This section describes existing work that is either directly or indirectly related to this investigation. This section begins by taking a look at some existing software development systems such as the Domain Specific Software Architecture (DSSA) program.

### 1.3.1 Software Development Systems.

- 1.3.1.1 DSSA. There are six projects within the DSSA program; four of the projects are in military specific domains such as avionics and navigation, while two of the projects, hybrid control and prototyping technology, address underlying support technology. (69) Between these six projects, there are three distinct approaches to software architecture: (72)

- 1. The avionics project managed by Loral Federated Systems (14) and the command and control project managed by GTE (84) are based on the domain modeling approaches of Prieto-Diaz (e.g., (85, 83, 82)). That is, an architecture is drawn from a domain model of the problem class, where the architecture describes a family of solutions. The Loral project, called DSSA-ADAGE, has as a goal "to provide system development."

opers with the necessary environment to locate, adapt, compose, generate (write), integrate, and evaluate avionics applications ... by analyzing a problem domain and creating/refining a set of standardized solutions within it (114:22) (emphasis added). The emphasis is on instantiation and verification of pre-existing architectural solutions using code modules.

The Loral project uses a formal language called LILEANNA (115) to describe architectures. LILEANNA is used to specify class hierarchies (in the object oriented sense) and compose them into Ada packages.(25) The GTE approach also defines an architectural model that is instantiated with reusable code modules based on the requirements of the application. Although formal languages are used, verification is limited to type checking and simulation.(14)

This is a fundamentally different approach than the theory-based approach described in Chapter II. Instead of using a formal language to declare an architecture and populate it with reusable code fragments, our approach uses a specialization process with inference rules and soundness axioms to *compose* and *specialize* specifications using architecture theories.

- 2. The distributed intelligent control project managed by Teknowledge Federated Systems is based on a particular "architectural style" similar to the object-connection-update (OCU) model proposed by the Software Engineering Institute (SEI).(61) This project includes a "domain controller" which generates plans of action. The Teknowledge approach is based on work in robotic control,(3) wherein an architecture "... proposes a multi-level hierarchy of controllers." (72:4) Two levels of controller are used. "A 'Domain Controller' has responsibility for determining plans of action without regard to time constraints, ... [and a] 'meta-controller' directs the execution of the planned actions with the goal of maximizing the use of scarce resources, particularly time constraints." (72:4)

- 3. The intelligent guidance project managed by Honeywell (1) and the hybrid control project managed by the ORA Corporation (78) are based on formal models of the application domain where the software architecture is derived from these formal models.

- (a) The Honeywell system uses a formal language called MetaH to describe architectures. The MetaH language "...allows users to specify how source modules are combined into higher level entities such as processes and modes of operation." (121:1) Honeywell, like Loral, uses a formal language to encapsulate source code written in a traditional programming language. As noted in the MetaH language reference manual, "...an application developer must produce two things: a collection of Ada source modules that implement the functions of the application system; and an application specification that describes how these source modules communicate, share resources, and are to be scheduled in the application system." (121:5) Application specifications are written in MetaH. "A MetaH specification identifies and groups Ada source code modules into entities to be included in the application, describes interfaces for entities, [defines] resource sharing and connections between entities, and [defines] attributes of entities. Applications are specified as one or more modes of operation, where a mode of operation is a collection of processes together with a pattern of communication and resource sharing between processes. Processes are specified as groups of monitors, packages, and subprograms written in the Ada programming language." (121:6) The Honeywell approach, like the Loral and the GTE approaches, is fundamentally different than our approach. MetaH is used to describe relationships between existing source code modules where these relationships define the architecture for an application family.

- (b) The ORA Corporation is "investigating an environment for the design, implementation, and evaluation of hierarchical, distributed, intelligent, hybrid control." (78:73) The term 'hybrid control' refers to "an integrated approach to continuous physical devices (mechanical, electrical, hydraulic, etc.) being controlled by discrete computational units (digital CPUs)," where "one attempts to study the problem without ... reducing the discrete to the continuous or the continuous to the discrete." (78:74) These researchers are developing both a theoretical basis for hybrid control as well as design tools whose emphasis is on analyzing and simulating dynamic systems. They are also investigating syn-

thesis of non-linear controllers as a means of "automatically generating control algorithms and software for non-linear hybrid control." (78:75)

The DSSA projects described above contain "reusable engineering experience" (knowledge) in the form of source code modules arranged to define an architecture for a family of related systems. Each of these architectures serves as a model or blueprint for applications developed in their respective domains.

These DSSA projects each define a specific architecture for a problem domain and instantiate the architecture with existing or custom developed modules based on application requirements. In none of the projects is an architecture for an application developed as a specialization of more general architecture theories.

1.3.1.2 CARDS. The Comprehensive Approach for Reusable Defense Software (CARDS) is another code-based reuse system.(123, 122) Like the DSSA-ADAGE project, CARDS exploits architecture-based reuse of code modules. CARDS explicitly represents solution space objects using a frame-based knowledge structure, where the knowledge structure describes relationships between solution space objects. The solution space objects in CARDS are source code and object code modules. CARDS uses two processes during the creation of an application:

- 1. An elicitor that obtains the requirements and instantiates portions of the ontology for the application.

- 2. A harvester that collects instantiated objects and complies and links them into an executable form.

CARDS uses the frame-based KL-ONE language (22) to represent relationships between solution-space objects.

1.3.1.3 J-MASS. Another model-based reuse program is the Joint Modeling and Simulation System (J-MASS) Program.(47) The J-MASS system concept document (SCD) describes a software development environment based on templates which are instantiated with code fragments. The J-MASS SCD describes two libraries:

- 1. A Software/Data Structures Library containing "software structural templates used for development of software components" (47:7) as well as "data structure templates."

- 2. A Software Components Library containing pre-compiled "parts" that are ready to be assembled into simulation models.

- 1.3.1.4 LEAP. The Lockheed Environment for Automatic Programming (LEAP) is a software development environment built by the Lockheed Software Technology Center. LEAP solicits application requirements through a series of templates. Based on the requirements, a suitable architecture for the application is created. This architecture is an instantiation/specialization of an architecture description stored in the LEAP knowledge base. Constraint propagation is used to facilitate requirements acquisition and thereby facilitate instantiation of the architectural template. LEAP contains at least two features related to the research described here:

- 1. Object-based interface. LEAP allows a user to define architectural aspects of an application via a graphical user interface (GUI). Inputs to the GUI are automatically reflected in the underlying application.

- 2. A parameterized, executable theory-based language called Common Intermediate Design Language (CIDL).(80) Applications developed using LEAP are represented internally as a collection of CIDL components. The CIDL representation of an application can be compiled and executed, or it can be translated into Ada or LISP for execution. Although CIDL is theory based, the axioms of the language are not yet used,(79) nor is it used to define architecture.

- 1.3.1.5 Kestrel Interactive Development System (KIDS). KIDS is a formal and mathematically well-founded software specification and synthesis system. (100) In KIDS, a problem is specified using sorts and operations defined in an underlying domain theory.

KIDS includes a collection of algorithm theories which can be specialized for a given problem. Once an algorithm has been specialized, it is transformed from its specification representation to a representation in the REFINE language. (88) Once in REFINE, the algorithm can be optimized, compiled, and executed.

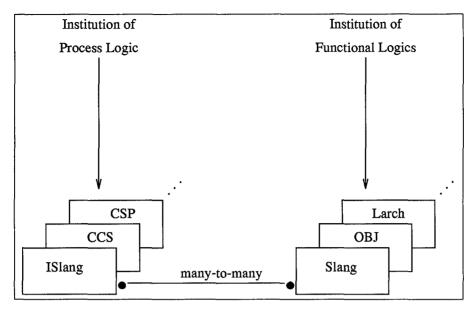

- 1.3.1.6 SpecWare. A theory-based system being developed at Kestrel Institute is SpecWare.(18, 19, 56, 55) SpecWare is based on the work of Wirsing (128) and Turski and Maibaum (117) among others where a category of specifications and specification morphisms is used to combine specifications into new specifications. One of the benefits of defining a specification development system in terms of category theory is that consistency preserving specification construction operations can be defined (see Chapter III for details). SpecWare is a higher order, functional specification development system that incorporates algorithm theories and specialization techniques. However, architecture theories are not explicitly used to define structure; there is no mechanism in SpecWare for connecting the output of one operation to the input of another outside of using nested function calls. SpecWare includes a collection of mappings from its specification language, SLANG, to compilable programming languages such as C or LISP. Because of the benefits offered by its foundation in category theory and its ability to specialize existing specifications, SpecWare was used in this investigation to define functional specifications.

- 1.3.1.7 Other Approaches. Other research related to this investigation is in area of architecture description languages and architecture definitions. Several papers attempt to formally describe either architecture classes or other aspects of software architecture, such as (74, 6, 38, 39, 76, 1, 78, 64, 114, 94, 93, 4, 5, 72, 60) and (95). Each of these papers provide some insight into the features a formal definition of architecture must support. For example:

- A pipe and filters formal model based on  $\mathcal{Z}$  in (4).

- Several classes of architecture including pipeline, object-oriented, layered hierarchy, table driven interpreters, and repositories are described in (94). Although these architecture classes are not formally defined in the paper, the author does describe their identifying characteristics and structural not semantic patterns.

- Module interaction is formally described using  $\mathcal{Z}$  in (37).

Other clues to the aspects a formal definition of architecture must address can be found by investigating architecture description languages (ADL). One such language is LILEANNA which was previously mentioned as part of the Loral DSSA work. ADLs are described in the following subsection.

### 1.3.2 Architecture Description Languages.

1.3.2.1 ADLs. An ADL called LIL is described in (43). An extension to LIL for use with Ada, called LILEANNA, is described in (115). LIL is a theory-based specification language with an emphasis on interfaces and data flow. Theories in LIL "declare properties an actual parameter must have to meaningfully substitute for the formal parameter of a generic entity." (43:127) Theories in LIL also define an entity's properties. Tracz states that specification construction operations such as colimits can be defined over LILEANNA specifications. (115) Although both LIL and LILEANNA support inheritance and parameterization, Tracz's work does not include the use of architecture theories. The specifications developed using LILEANNA are not structured to support automated code synthesis, but instead are used for "automated selection, composition, tailoring and instantiation of (existing) Ada code." (120)

Another ADL is MetaH. Although MetaH allows "no functional specification beyond a simple naming of inputs, shared objects, and outputs," (120) it has several interesting aspects. For example, MetaH has nine different types of components, such as events, ports, and processes. The language also has four different classes of "connection," an example of which is a port connection.

$\mu$ -Rapide is an ADL designed for event-driven systems.(64) One of the interesting features of  $\mu$ -Rapide is its handling of connections between components. "Connections themselves may have complex behaviors specified, and in general, the expressive power of connections and component behaviors is equivalent. In fact, there is a straight-forward way of rewriting a complex connection specification as a component specification ..."(120).

Each of the three ADLs have two classes of entity: a component and a connection. In addition, Vestal notes the following similarities:

- Component interface declarations define types of components, where there may be multiple instances of a declared component type.

- Components have distinct interface and implementation aspects.

- Connections can be made between "things" in component interfaces, not always directly between components themselves.

- Components may be defined in terms of sub-components and connections between them.

ADLs may be used to document or declare possible architectural solutions which — depending on the ADL — may be parameterized. The emphasis of ADLs is quite different than our formalism described in Chapter II. The emphasis of ADLs is on the efficient management of the structure and implementation of large applications. In contrast, our formalism described in Chapter II is concerned with the generation of a consistent architectural and behavioral definition of large applications.

1.3.2.2 Module Interconnection Languages (MIL). MILs, such as Thomas' MIL (113), state what the system modules are and how they fit together to implement the system's functions. MILs are not concerned with what the system does (specification information), how the major parts of a system are embedded into the architecture (analysis information), or how the individual modules implement their function (detailed design information).(86)

According to (86), researchers working in formal models view interconnection in two ways: as a structural model of the resource usage and as a consistency model of the construction of the system. In short, a MIL is a language for "programming in the large with a formal machine-process-able [sic] syntax that provides a means for the designer of a large system to represent the overall system structure in a concise, precise, and verifiable form." (86:309)

Polylith is a MIL used at the University of Maryland. (87) Polylith provides a "packaging system for analyzing configurations and then generating all stubs, build commands and other interfacing structures according to the developer's abstract interfacing deci-

sions," (15:82) and provides a "run-time system providing various forms of communication support." (15, 87) Polylith is used to document the architecture of a family of applications and is designed to facilitate program compilation such that they are consistent with the defined architecture. Polylith is not designed to manipulate formal algebraic specifications.

The main concepts of a MIL are:

- the use of a separate language to describe system design;

- the ability to perform static type-checking at an intermodule level description;

- the ability to consolidate the design and construction process (module assembly) in a single description; and

- the ability to control different versions and families of a system.

MILs are used to document the structure of an application; they are not used to derive the structure of an application. Although MILs typically provide static type checking, they do not typically provide semantic compatibility checks. For example, a module designed to compute the square root of an integer argument has an implicit input assumption that the argument it receives is greater than or equal to zero. MILs typically do not ensure that input assumptions such as these are satisfied.

1.3.2.3 Specification Languages and Proof Systems. Many specification languages and specification development systems exist (e.g., (2, 53, 59, 89, 92, 13, 9)). Some of the more widely known systems include KBEmacs, which is a specification development system with an emphasis on specialization of code generics, (125) and LaSSIE, which is a frame-based specification system. (29, 28) Other specification development environments include ENCORES (70), OIKOS (7), Clear (23),  $\Phi$ -nix (12), and DRACO (73). The text Automating Software Design (63) contains a description of several of these specification development systems, and (46) contains a survey of several others.

Three specification development systems or languages, *Larch*, *OBJ3*, and *Promela* are described in the following paragraphs.

- 1. Larch. Larch is a specification language which is bundled with a theorem prover. (48) Larch is a two-tiered specification language consisting of a shared language and an interface language.

- (a) The Larch Shared Language is used to specify sorts, operations, and axioms.

The Larch theorem prover can be used to prove properties of *traits*, which are the fundamental specification unit of Larch.

- (b) The Larch Interface Language is a programming language specific language that introduces terms, such as exceptions or timers, that are part of the programming language but not part of the shared language. The Larch interface language can also be used to define state. A Z-like notation is used to denote state manipulation.

- 2. *OBJ3* is a "wide spectrum functional programming language." (44:1) Two types of module are used in OBJ3:

- (a) objects encapsulate executable code, and

- (b) theories which "specify both syntactic structure and semantic properties of modules and module interfaces." (44:1)

- OBJ3 supports parameterized programming and includes a theorem prover based on an order sorted equational logic.

- 3. Promela is a process-based specification development system consisting of two back ends:(126)

- One back end generates C++ code "suitable for compilation onto an embedded controller";

- The second back-end "generates gate level designs suitable for input to conventional silicon compliers or field-programmable gate array ...tools."

In Promela, static channel definitions are used to define communication. However, the authors incorporate notions of an "unreliable" channel that may corrupt or completely lose messages. Channels are either typed or untyped, and may be declared to be external (e.g., a hardware interface).

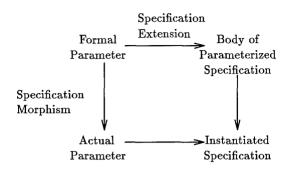

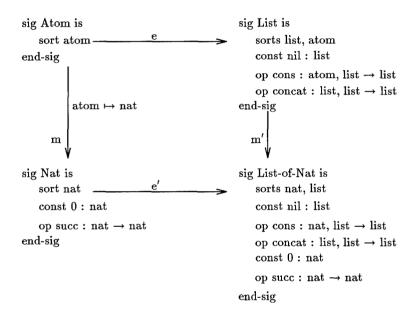

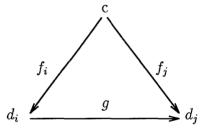

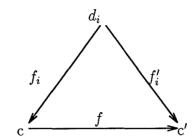

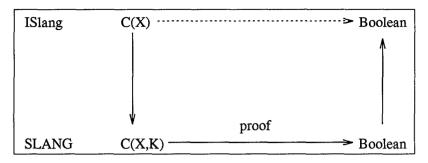

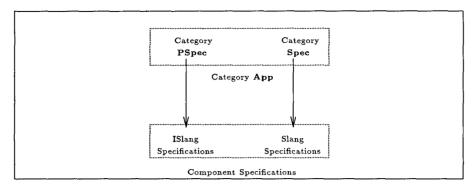

All communication in Promela is either message based or via shared data values. Communication can either be synchronous or asynchronous, but synchronous communication need not block if the other party is not ready to communicate. Instead, the communication attempt could return a "fail" value. All Promela processes are concurrent.