# Enhanced Controller for grid-connected Modular Multilevel Converters in distorted Utility Grids

Alexis B. Rey-Boué<sup>1\*</sup>, Fernando Martinez-Rodrigo<sup>2</sup>, N. F. Guerrero-Rodríguez<sup>3</sup>, Luis C. Herrero de Lucas<sup>4</sup>, and Santiago de Pablo<sup>5</sup>

- <sup>1</sup> Department of Electronics, Computers Technology and Projects, Universidad Politécnica de Cartagena, c/Dr.

Fleming, s/n, 30202 Cartagena, Murcia, Spain. Tel.: +34 968 325928; fax: +34 968 326400; alexis.rey@upct.es

- <sup>2</sup> Department of Electronics Technology, University of Valladolid, C/ Francisco Mendizábal, 1, 47014

Valladolid, Spain. Tel.: +34 983 423921; fax: +34 983 423490; fer\_mart@tele.uva.es

- <sup>9</sup> Engineering Sciences, Pontificia Universidad Católica Madre y Maestra PUCMM, Av. Abraham Lincoln Esq.

10 Romulo Betancourt, 2748 Santo Domingo, Dominican Republic. Tel.: +18095350111 ext.2314;

11 nf.guerrero@ce.pucmm.edu.do

- <sup>4</sup> Department of Electronics Technology, University of Valladolid, C/ Francisco Mendizábal, 1, 47014 Valladolid,

Spain. Tel.: +34 983 423521; fax: +34 983 423490; lcherrero@eii.uva.es

- <sup>5</sup> Department of Electronics Technology, University of Valladolid, Paseo del Cauce, 59, 47011 Valladolid, Spain.

Tel.: +34 983 423345; fax: +34 983 423310; sanpab@eii.uva.es

- 16

- 17 \* Correspondence: alexis.rey@upct.es; Tel.: +34 968 325928

18 Abstract: This paper is about the control of Modular multilevel converters, an innovative technology 19 in the design of converters, which is beginning to be included in real installations. Papers about this 20 topic include simulation models, circulating current reduction, voltage modulators, capacitor 21 voltage balancing and control issues. The scheme for current source regulation used in this article 22 includes all control loops, which are, from the outermost to innermost, DC bus voltage regulator, 23 current regulator, voltage modulator, capacitor voltage balancing, and a PLL for the 24 synchronization to the grid. Disposition-sinusoidal Pulse Width Modulation is used as the voltage 25 modulator, and an enhanced control strategy in the stationary reference frame for 3-phase MMCs is 26 used for the inner current control loops. Very detailed simulations of the complete control system 27 have been performed for both the enhanced control strategy in the stationary reference frame, and 28 the well-known control in the synchronous reference frame, as well as some experiments using the 29 Hardware-in-the-Loop Simulation technique. The validation of these control strategies is made by 30 a comparison of the capability of each one to compensate the harmonic distortions of the utility grid 31 according to the grid code. The correct operation has been tested in the case of a strong/weak grid, 32 unbalances and grid failures.

33

34 Keywords: Electric power transmission; modular multilevel converter (MMC); voltage-source

35 converter (VSC); proportional-resonant (PR) controller; harmonic compensator (HC)

36

# 37 **1. Introduction**

The types of converters used for medium (MV) and high voltage (HV) AC/DC/AC conversion are line commutated converters (LCC) [1], voltage source converters (VSC) [2,3], and lately MMC, first used by Marquardt [4]. LCC and VSC are the classical topologies used for converters, but VSC multilevel topologies have also been used [5]. The LCC topology is built with thyristors, while the VSC topology can use IGBTs, IGCTs or GTOs featuring two, three or more than three levels.

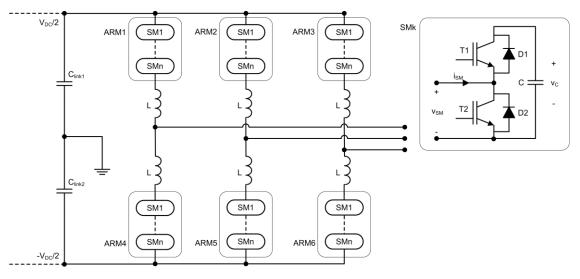

43 Modular Multilevel Converters (MMC) is a new topology that has acquired great interest for 44 researchers [6] and which has begun to be implemented in actual installations. The base is a switching

- 45 module (SM) composed by two bidirectional switches (IGBT + antiparallel diode) and a capacitor C

- 46 (see Figure 1). The converter is built using several SMs and an inductance per arm, two arms per

47 phase, and containing three phases (see Figure 1). The arm inductances L are used to couple the arm

48 voltage to the DC bus voltage.

49 50

Figure 1. MMC scheme and SM structure.

51 An MMC converter with n SMs per arm can generate a phase to midpoint of the DC voltage 52 with n + 1 levels. The number of AC output levels can be increased by increasing the number of 53 SMs.

MMC has advantages and disadvantages regarding LCC and VSC [7]. The advantages include a reduction in the need for AC filtering, easy scalability, the distribution of the capacitive energy between several capacitors, and stress reduction in the semiconductor. The main disadvantage is the increased complexity: the number of modules and drivers, the number of signals to be handled, including module trigger and SM voltage feedback. Another disadvantage is the presence of the circulating three currents (one per phase) that circulate between each phase and the DC bus.

50 Studies about MMC tackle the analysis of semiconductor losses in comparison with other 51 topologies, static and dynamic modeling, and control in balanced and unbalanced grids [8]. The SM 52 capacitor voltage changes when current flows through it, and several techniques can be used to keep 53 those capacitor voltages balanced: sorting algorithms [7,8], averaged and balanced control [9], 54 predictive control [10], methods which do not require the sign of the arm current to be known [11] 55 and methods to decrease the switching frequency [12].

66 Moreover, if the semiconductor models are very accurate, the simulation of the MMC can be 67 extremely slow because of the very high number of semiconductors. Therefore, less accurate models 68 are studied to obtain simulation with a sufficient degree of accuracy through averaged and 69 approximated models [13-16].

For the AC voltage modulator, several possibilities are described, such as PD-SPWM, multilevel PWM and current source predictive control. PD-SPWM is a type of PWM where the reference is compared with n carriers to obtain the gate signals of the SMs [8,17]. Multilevel PWM calculates the average value of the voltage over a commutation period and generates the duty cycle necessary to obtain it [7]. Predictive control evaluates a cost function that includes several parameters and selects the best combination of ON/OFF states of the SMs [10].

The upper and lower arms of a phase leg have current simultaneously; the consequence is the existence of undesired currents, the circulating currents. Their equations are calculated in [18], their suppression in [17], and their reduction in unbalanced systems in [19].

Other aspects of MMC studied are: models and control systems in unbalanced grids [20,21],

influence of the commutation frequency and the number of SMs in the harmonic content [22], DC bus

protection using thyristors included in the SMs [23] and current source control [24].

82 Regarding the 3-phase grid-connected renewable systems, several vector control strategies are 83 studied in the scientific literature. Hysteresis control [25], dead-beat predictive control [26,27], and 84 dq control [28,29], among others, have been widely used for several years with acceptable results. 85 The linear dq control approach is the cheapest strategy and uses the well-known PI regulators in 86 synchronous reference frame, which allow a zero steady-state error when dc variables are used, as 87 well as an easy digital implementation in commercial microcontrollers; its main drawbacks are a 88 lower dynamic response and a non-zero steady-state error when sinusoidal variables are used. On 89 the contrary, the dead-beat predictive control has a higher dynamic response, but it is necessary to 90 measure or estimate some variables, which increases the cost of the system, and is very sensitive to 91 model mismatches and parameters uncertainties. The hysteresis control is a non-linear strategy, 92 having the fastest dynamic response, and being very easy to implement with analog devices, 93 although enhanced more expensive signal conditioner circuits are needed due to the higher 94 bandwidth of the measured line currents, which increases its overall cost; in addition, this strategy is 95 almost insensitive to parameters uncertainties, and very robust to input and output disturbances, but 96 a variable hysteresis band is mandatory [25] because its switching frequency is not constant, making 97 the digital implementation very difficult.

98 The dq control strategy implemented in the synchronous reference frame [30] has been the 99 preferable strategy for years and for this, the Park's transformation [31,32] is applied to the 3-phase 100 line currents. However, a trade-off between the advantages and disadvantages can be noticed: 101 although its digital implementation is very easy, its main drawbacks deal when it is used in 3-phase 102 distorted grid-connected systems, where the low-order harmonic distortions of the grid voltages 103 must be compensated because they will appear in the line currents instead, reducing the power 104 quality and the power factor of the connection. The feedforward of the dq components of the grid 105 voltages and the cross-coupling terms can solve the situation, but a high bandwidth is mandatory in 106 the open loop transfer function of the line currents in order to decrease the effect of delays [33,34], 107 which firstly, increases the switching frequency and, in consequence the losses, and last but not least, 108 a programmable device such as an FPGA must be used.

109 The reduction of the power quality and the power factor can make impossible the connection of 110 the renewable system to the utility grid if the magnitude of the individual harmonic distortions 111 and/or the total harmonic distortion of the line currents are higher than the limits imposed by the 112 grid code [35,36]. For the fundamental frequency  $\omega_1$  of the 3-phase utility grid voltages with positive-113 sequence, the implementation of a harmonic compensation scheme in the synchronous reference 114 frame can be done as in [37], but the interpretation of the Park's transformation applied to the 5<sup>th</sup>, 7<sup>th</sup>, 115 11<sup>th</sup>, 13<sup>th</sup>, ... harmonics must take into account the negative- sequence for the 5<sup>th</sup> and the 11<sup>th</sup>, as well 116 as the positive- sequence of the  $7^{th}$  and  $13^{th}$  harmonics, and its transformation into the  $6^{th}$  and  $12^{th}$ 117 harmonics, respectively, in the fundamental synchronous reference frame [33]. So, a conventional PI 118 regulator can be employed for the fundamental frequency  $\omega_1$  because the d-q components of the line 119 currents are constants and a zero steady-state error is ensured. However, the perturbation of the 6<sup>th</sup>, 120 the 12th, ... harmonics will not be cancel unless several synchronous reference frames rotating at 121  $\pm 6n\omega_1$  (n=1,2,3,4,...) were applied. If so, the several constant d-q components of each synchronous 122 reference frame will allow the use of integrators to reject the harmonic pollution of the 3-phase utility 123 grid voltages by cascading its outputs to the output of the PI regulator of the fundamental 124 synchronous reference frame. It is worth noting that special care must be taken with delays for high 125 order harmonics.

126 Nowadays, an enhanced control strategy is being used to deal with distorted utility grids. Unlike 127 the control described above, it is also possible to do it in the stationary reference frame [38] avoiding 128 the use of several synchronous reference frames and reducing the computational burden. For this, 129 the Clarke's transformation is used [32,39], allowing its implementation with Proportional and 130 Resonant (PR) regulators for the fundamental frequency, as well as several resonant controllers to 131 compensate the low-order harmonics introduce by the utility grid voltages. In addition, PR regulators 132 can deal with positive- or negative-sequence systems, as it will be explained in the next sections. 133 Finally, the implementation of this strategy does not need a very high bandwidth of the open loop

transfer function of the line currents, and so, the switching frequency can be set at 10-20 KHz, allowing the use of commercial microcontrollers.

136 In this paper, a comparison of the behavior of the dq control strategy with the PR regulators plus 137 the Harmonic Compensation (HC) structure has been made, mainly in their capability for the 138 reduction of the harmonic distortions in the 3-phase utility grid currents. It is organized as follows: 139 firstly, the basic structure and the main equations of the MMC are presented in Section 2, and an 140 explanation of the fundamentals of the PR plus the HC structure, compared with the well-known dq 141 control strategy with PI regulators, is presented in Section 3; in Section 4, the elements of the vector 142 control for the 3-phase line currents (as the inner control loops) in the stationary reference frame, as 143 well as the power balance exerted in the outer DC bus voltage control loop are analyzed, and the 144 PLL, the sorting algorithm for the capacitor voltages, and the voltage modulator are also presented; 145 in Section 5 the grid code used in this paper is presented. Secondly, some simulations and 146 experiments are carried out in Sections 6 and 7, respectively, to validate the capability of each control 147 strategy for the attenuation of the harmonic distortions of the 3-phase utility grid currents and the 148 Fault-Ride-Through (FRT) operation. Finally, the conclusions are stated in Section 8.

# 149

# 150 2. Fundamentals of MMC

151 SMs are composed of two IGBTs, two diodes and a capacitor (Figure 1). The SM ON/OFF state 152 and the SM current  $i_{SM}$  sign set the following parameters: the sign of the capacitor voltage increases 153  $\Delta v_{C}$ , the semiconductor through which current  $i_{SM}$  flows and the SM voltage  $v_{SM}$  (Table 1).

| 154 |

|-----|

|-----|

Table 1. Relations among elements and variables of the SM.

| SM state | $T_1$ state | $T_2$ state | i <sub>sm</sub> | $\Delta v_c$ | <i>i<sub>SM</sub></i> flows through | v <sub>sm</sub> |

|----------|-------------|-------------|-----------------|--------------|-------------------------------------|-----------------|

| ON       | ON          | OFF         | > 0             | +            | $D_1$                               | $v_{c}$         |

| ON       | ON          | OFF         | < 0             | _            | $T_1$                               | $v_{c}$         |

| OFF      | OFF         | ON          | > 0             | 0            | $T_2$                               | 0               |

| OFF      | OFF         | ON          | < 0             | 0            | <i>D</i> <sub>2</sub>               | 0               |

155

156 The sum of the number of SMs in the ON state in the upper  $n_{up}$  and lower  $n_{low}$  arms of each 157 phase is equal to the number of SMs per arm n.

$$n_{up} + n_{low} = n \tag{1}$$

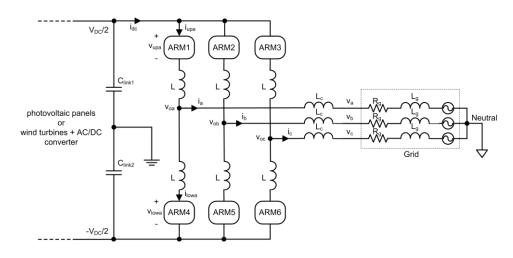

158 Regarding Figure 2, the grid-connected MMC can be fed by photovoltaic panels or wind turbines 159 + AC/DC converter, where the input power will be proportional to the irradiance at a specific 160 temperature or to the cube of the wind speed, respectively, whereas a large link capacitor C<sub>link</sub> is used 161 to transform this current into a voltage source at the input of the MMC converter. Therefore, at steady 162 state regime each SM will have an average voltage  $v_{SM} = \frac{v_{DC}}{n}$ .

163 The first phase MMC voltage v<sub>oa</sub> (Figure 2), is:

$$v_{oa} = \frac{V_{DC}}{2} - v_{upa} - L \frac{di_{upa}}{dt}$$

(2)

$$v_{oa} = -\frac{V_{DC}}{2} + v_{lowa} + L\frac{di_{lowa}}{dt}$$

(3)

165 **Figure 2.** Scheme of the MMC connected to the grid.

166 If  $S_{upak}$  and  $S_{lowak}$  are the estate 1/0 of the first phase SMs, and  $v_{cupak}$  and  $v_{clowak}$  are the 167 first phase capacitor voltages, then the upper and lower arm voltages are:

$$v_{upa} = \sum_{k=1}^{n} S_{upak} \, v_{Cupak} \tag{4}$$

$$v_{lowa} = \sum_{k=1}^{n} S_{lowak} \, v_{Clowak} \tag{5}$$

168 If i<sub>za</sub> is the first phase circulating current, then the first phase arm currents are [8,14]:

$$i_{upa} = \frac{i_a}{2} + \frac{i_{dc}}{3} + i_{za} \tag{6}$$

$$i_{lowa} = -\frac{i_a}{2} + \frac{i_{dc}}{3} + i_{za}$$

(7)

169 Adding (6) and (7), the expression of the circulating current can be obtained:

$$i_{za} = \frac{i_{upa} + i_{lowa}}{2} - \frac{i_{dc}}{3} \tag{8}$$

170 The sum of the circulating current of the three phases is zero:

$$i_{za} + i_{zb} + i_{zc} = 0 (9)$$

#### 171 **3.** Fundamentals of the PR regulator plus the HC

172 The PR regulators, unlike the PI regulators, can be used in 1- or 3-phase systems because the 173 former can track sinusoidal signals, meanwhile the latter is used for dc variables. For 3-phase signals, 174 the Clarke's transformation converts a 3-phase sinusoidal system (abc) into a 2-phase sinusoidal 175 system in orthonormal ( $\alpha\beta$ ) axes, also known as abc-> $\alpha\beta$  transformation in the stationary reference 176 frame; the inverse Clarke's transformation ( $\alpha\beta$ ->abc transformation) is also possible without losing 177 information if the 3-phase variables have two degrees of freedom. For 1-phase systems, the ac

178 sinusoidal signal is used as itself and no transformation is applied.

On the contrary, the PI regulator can only be used in 3-phase systems because the Park's transformation converts the 3-phase sinusoidal variables into a 2-phase dc variables in orthonormal dq axes, also known as abc->dq transformation in the rotating synchronous reference frame. Again, the inverse operation (dq->abc transformation) is also possible without losing information if the 3phase variables have two degrees of freedom.

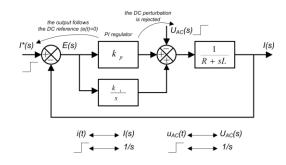

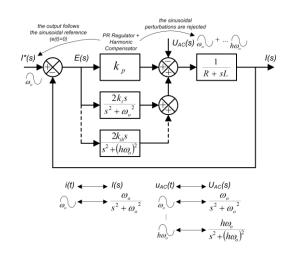

In order to understand the advantages of the PR regulator plus the HC over the PI regulators, Figures 3 and 4 are depicted bellow. First, it must be said that the internal model principle (see Appendix C of [39] for a detailed explanation) states that the output of a closed control loop will track the input reference command and will reject the disturbance (zero steady-state error) if the denominators of any block of the open loop transfer function and the Laplace transform of both the input reference command and the disturbance are the same. Then, as the plant cannot be changed, it is clear that the denominator of the transfer function of the regulator must obey this principle.

191 When a PI regulator is employed, it can only track and reject dc variables, whose Laplace 192 transform is 1/s, because the denominator of the transfer function of this regulator is s (see Figure 3). 193 For example, in the case of 3-phase systems with a positive- sequence of the fundamental frequency 194 of the 3-phase utility grid voltages, the PI regulator can only track and reject the dc variables of the 195 Park's transformation in d-q axes, corresponding to the fundamental frequency; conversely, the 5<sup>th</sup> 196 negative- and 7<sup>th</sup> positive- sequence harmonics which are transformed into the 6<sup>th</sup> harmonic, and the 197 11th negative- and 13th positive-sequence harmonics which are transformed into the 12th harmonic 198 [33,40], both in the same d-q axes, cannot be rejected by the PI regulator.

#### 200

202 On the contrary, when a PR regulator is employed, it can only track and reject sinusoidal variables, whose Laplace transform are  $\frac{\omega_0}{s^2+\omega_0^2}$  because the denominator of the transfer function of 203 204 this regulator is  $s^{2}+\omega^{2}_{0}$  (see Figure 4). In the case of 3-phase systems, the PR regulator can track and 205 reject the sinusoidal variables of the Clarke's transformation in  $\alpha$ - $\beta$  axes corresponding to the 206 fundamental frequency, but what is more important, cascading several resonant filters tunned to the 207 5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup>, 13<sup>th</sup>, etc., the Harmonic Compensator (HC) structure is easily formed and these harmonics 208 are rejected in the output  $\alpha$ - $\beta$  components of the 3-phase grid currents. In addition, it is worth noting 209 that the PR regulator plus the HC can deal with positive- or negative-sequence systems because they 210 always have a pair of conjugate poles in the complex plane for the fundamental frequency and its 211 harmonics.

212

Figure 4. Block diagram of the line current closed loop with a PR regulator plus a HC structure.

#### 215 4. Vector control

# 216 4.1. Current control loops

The vector equation that relates the converter voltage  $\vec{v}_0$ , the grid voltage  $\vec{v}$ , and the converter output current  $\vec{i}$  is (Figure 2):

$$\vec{v} = \vec{v}_o - L_c \frac{d\vec{\iota}}{dt} \tag{10}$$

where  $L_c$  is the coupling inductance, and can be expressed by the following two equations in the  $\alpha - \beta$  orthonormal axes [38]:

$$v_{\alpha} = v_{o\alpha} - L_c \frac{di_{\alpha}}{dt} \tag{11}$$

$$v_{\beta} = v_{o\beta} - L_c \frac{di_{\beta}}{dt} \tag{12}$$

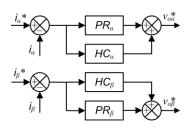

221 Two identical Proportional-Resonant (PR) regulators are employed to control the  $\alpha - \beta$ 222 components of the 3-phase output currents, forming the inner loops of a cascade control structure 223 together with the outer DC bus voltage regulator; they can be obtained from (11) and (12). As can be 224 seen, unlike the PI regulators used for the vector control of the orthonormal d - q components of the 225 3-phase output currents, these equations are not coupled and an easier implementation is achieved. 226 In addition, a cascaded Harmonic Compensator (HC) structure can be added to both PR regulators, 227 allowing the rejection of the harmonic pollution in the utility grid voltages (Figure 5) according to the 228 internal model principle. The output of the PR regulators plus the harmonic compensators are the 229 reference voltages of the converter  $v_{0\alpha}^*$  and  $v_{0\beta}^*$ , being worth noting the absence of the feedforward 230 utility grid voltages, commonly used in the dq control in the rotating synchronous reference frame.

**Figure 5.** Proportional-Resonant (PR) regulators + Harmonic Compensators (HC) in  $\alpha - \beta$  axes.

233 Definetly, the PR+HC structure are formed by a proportional regulator and a series of resonant 234 filters tunned to the fundamental, the 5th, 7th, 11th, 13th, ...low order harmonics. Each resonant filter 235 behaves as a Generalized Integrator [41] with a very high gain at its resonance frequency and a 236 narrow bandwidth. Then, the proportional and the resonant filter tunned at the fundamental 237 frequency can regulate sinusoidal reference signals: the proportional gain K<sub>P</sub> sets the dynamic of the 238 system (bandwidth, phase and gain margin), and the integral gain KI guarantees a zero steady-state 239 error, meanwhile the other resonant filters compensates (or reject) the harmonic distortion in the 240 output currents due to the harmonic pollution of the 3-phase utility grid voltages.

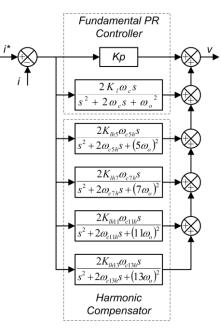

The structure of the PR+HC shown in this paper is non-ideal, and a cut-off frequency  $\omega_c$  is added to improve the stability problems and make the digital implementation easier [42]. The transfer functions of the PR and the HC are shown in (13) and (14) for the fundamental, 5<sup>th</sup>, 7<sup>th</sup>, 11,th, 13<sup>th</sup> harmonics, and the block diagram is depicted in Figure 6. An extension to other low order harmonics can be made by extrapolation, but special care must be taken with delays, mainly for high order harmonics distortion [34].

$$G_{PR}(s) = K_P + \frac{2K_I\omega_c s}{s^2 + 2\omega_c s + \omega_o^2}$$

(13)

$$G_h(s) = \sum_{h=5,7,11,13} \frac{2K_{Ih}\omega_c s}{s^2 + 2\omega_c s + (h\omega_o)^2}$$

(14)

247

248

- Figure 6. Detailed implementation of the PR Regulator + Harmonic Compensators (HC) structure for the

fundamental, 5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup>, 13<sup>th</sup> harmonics.

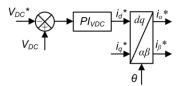

- 4.2. DC bus voltage control loop

253 The DC bus voltage  $V_{DC}$  is regulated with the outer control loop of the converter [43], allowing 254 the power balance between the incoming active power and the power delivered to the utility grid 255 (Figure 7). The reference for the DC bus voltage  $V_{DC}^*$  is compared with the measured value of the 256 DC voltage VDC, and the error is fed to a PI regulator, which output is the d component of the reference 257 line current id \* and is proportional to the maximum available power at the input; the q component of 258 the reference line current  $i_q^*$  is set as an open loop signal and is capable to control the power factor 259 of the MMC converter-grid connection. The inverse Clarke's transformation is then applied to both 260 components  $i_d^*$  and  $i_q^*$ , allowing the vector current control in the orthonormal  $\alpha - \beta$  axes, 261 explained above.

262

**Figure 7.** DC bus voltage control loop.

264 The instantaneous active and reactive powers can be calculated using the orthonormal  $\alpha$  – 265  $\beta$  components of the 3-phase line currents and the utility grid voltages according to the 266 instantaneous reactive power theory [44]:

$$p = v_{\alpha}i_{\alpha} + v_{\beta}i_{\beta} \tag{15}$$

$$q = v_{\beta}i_{\alpha} - v_{\alpha}i_{\beta} \tag{16}$$

267 268

269

270

271 or with the orthonormal d - q components [30,45]:

$$p = v_d i_d \tag{17}$$

$$q = -\nu_d i_q \tag{18}$$

272

when the utility grid voltage  $\vec{v}$  is aligned with the d axis ( $v_q = 0$ ), rotating at the fundamental angular frequency  $\omega$  of the grid. The former is known as the stationary reference frame control, and the latter is known as rotating synchronous reference frame control, where p and q can be independently controlled by the currents  $i_d$  and  $i_{q'}$  respectively (Figure 8).

277

278

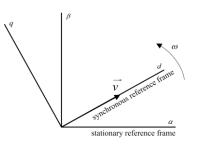

**Figure 8.** Stationary  $\alpha - \beta$  and synchronous d – q reference frames.

#### 281 4.3. Phase-Locked Loop

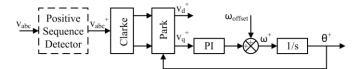

282 For synchronization between the MMC converter and the grid, the angle  $\theta$  of the grid voltage 283 vector  $\vec{v}$  must be known. A scheme for the synchronization PLL is found in Figure 9 [46]. It has a PI 284 block whose input is the quadrature component of the grid voltage v<sub>q</sub>. This block generates an output 285 that tries to reduce the value of  $v_q$  to zero. The output of the PI block  $\omega$  is the angular speed of the 286 grid voltage  $\vec{v}$ ; an initial value of the angular speed  $\omega_{offset}$  is added to reduce the time to track the 287 angle  $\theta$  and improve the PLL stability. An integrator block is used to get the angle  $\theta$  from the 288 angular speed  $\omega$ . For unbalanced systems, a Positive Sequence Detector (PSD) must be added to 289 reject the negative sequence of the 3-phase utility grid voltages [40,47], but it must be pointed out 290 that despite the presence of balanced 3-phase utility grid voltages, special care must be taken with 291 the several errors produced at the output of the data acquisition electronic card, which can also 292 introduce unbalances [48].

293

#### **Figure 9.** Block diagram of the PLL.

*295 4.4. Sorting the capacitor voltages*

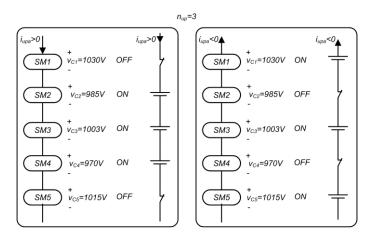

There is a last block between the voltage source modulator and the hardware, which must ensure that the capacitor voltages of every SM throughout each arm remain balanced. To achieve this, the SMs of each arm must be selected to be switched ON or OFF to balance their voltages, depending on the sign of the arm current. The objective is to increase the lowest voltages and to reduce the highest voltages.

For example, if the number of modules per arm n is 5, the converter output voltage  $v_{oa}$  can take six values, listed in Table 2. Each phase has 10 SMs (2n), 5 SMs in the upper arm and 5 SMs in the lower arm. The voltage of each SM is approximately  $\frac{V_{DC}}{5}$ , so the number of SMs of each phase in the ON state is 5 in every switching time. For every value of the converter output voltage  $v_{oa}$ , the sum of the number of SMs in the ON state in the upper  $n_{up}$  and lower  $n_{low}$  arms is n (see Table 2).

306

Table 2. Levels of output voltage voa.

| $n_{up}$ | $n_{low}$ | $v_{oa}$                              |

|----------|-----------|---------------------------------------|

| 5        | 0         | $-\frac{V_{DC}}{2}+0\frac{V_{DC}}{5}$ |

| 4        | 1         | $-\frac{V_{DC}}{2}+1\frac{V_{DC}}{5}$ |

| 3        | 2         | $-\frac{V_{DC}}{2}+2\frac{V_{DC}}{5}$ |

| 2        | 3         | $-\frac{V_{DC}}{2}+3\frac{V_{DC}}{5}$ |

| 1        | 4         | $-\frac{V_{DC}}{2}+4\frac{V_{DC}}{5}$ |

| 0        | 5         | $-\frac{V_{DC}}{2}+5\frac{V_{DC}}{5}$ |

To obtain a value of, for example,  $v_{oa} = -\frac{v_{DC}}{2} + 2\frac{v_{DC}}{5}$ , the number of SMs that must be switched ON in the upper  $n_{up}$  and lower  $n_{low}$  arms are, respectively, 3 and 2. The SMs to be switched ON must be selected to maintain the SM capacitor voltages balanced. When a SM is ON, its voltage increases or decreases depending on the positive or negative sign of the arm current (Table 1). If the SM is OFF, its voltage remains constant.

A sorting algorithm must be used to select the modules to be switched ON in an arm. The input to the algorithm is the number of SMs in the ON state,  $n_{up}$  for the upper arm and  $n_{low}$  for the lower arm. The algorithm's output are the SMs selected to be switched ON. When the arm current is positive, the SMs with the lowest voltages are selected, in order to increase their voltage by means of the arm current. When the arm current is negative, the SMs with the highest voltages are selected so as to reduce their voltage. The objective of the algorithm is to keep all the SM voltages around the value of  $\frac{V_{DC}}{r}$ . In Figure 10, an example of the sorting can be found for the cases of arm current i<sub>upa</sub>

320 positive and negative, and  $V_{DC} = 5000V$ .

321

**Figure 10.** Example of SM voltage sorting for  $n_{up} = 3$ .

#### 323 4.5. Voltage modulator

The current regulators set the references of the converter output voltages  $v_{o\alpha}^*$  and  $v_{o\beta}^*$  (Figure 325 5). Therefore, the voltage modulator is an inner loop to the current regulators.

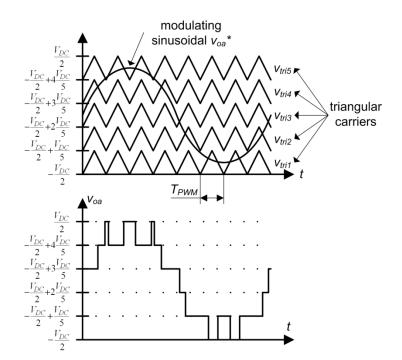

Sinusoidal PWM (SPWM) has been used to control the output voltage of various types of multilevel converters, not only MMC. SPWM is based on a comparison of the modulating signal (supposedly sine wave) with some triangular carriers whose number depends on the number of voltage levels. According to the phase shift of the triangular signals, there are several types of SPWM [49]: Alternative Phase Opposition Disposition, Phase Disposition, Phase Opposition Disposition, Hybrid, Phase Shifted. Among them, Phase Disposition (PD) is a good choice in order to obtain low levels of harmonics. For PD, the phase difference among the triangular carriers is zero.

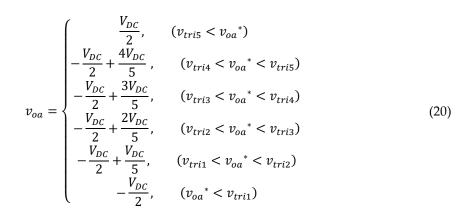

In this paper, the Phase Disposition-sinusoidal PWM (PD-SPWM) voltage modulator is used, and it is presented for the case of 5 SMs (n = 5) per arm, although a generalization for more or less SMs is straightforward; then, the converter output voltage of each phase  $v_{oabc}$  has six levels (n + 1). The relationship between this voltage and the number of ON modules in the lower arm  $n_{low}$  is:

$$v_o = -\frac{V_{DC}}{2} + n_{low} v_C \tag{19}$$

For the case of the six-level converter (Figure 11), the PD-SPWM [8] is based on the comparison of five high frequency triangular carriers and a low frequency sinusoidal modulating waveform. The converter output voltage can take the following values:  $-\frac{V_{DC}}{2}, -\frac{V_{DC}}{2}, -\frac{V_{DC$

- 341 triangular carriers, the converter output voltage  $v_{oa}$  is obtained by means of these equations (for the 342 phase a):

# 362 **5. Grid code**

On one hand, the limits of the harmonic distortion for the 3-phase utility grid medium voltages

(MV) are established according to the IEC/TR 61000-3-6 Normative [35], where the allowed Total

Harmonic Distortion (THD) is 6.5%, and the limits for each harmonic order is shown in Table 3.

| Table 3. Regulation of harmoni | c voltage limits in MV | power systems. |

|--------------------------------|------------------------|----------------|

|--------------------------------|------------------------|----------------|

| Odd harmonics     | Harmonic voltage, MV |

|-------------------|----------------------|

| non-multiple of 3 | (%)                  |

| 5                 | 5                    |

| 7                 | 4                    |

| 11                | 3                    |

| 13                | 2.5                  |

367

366

368 On the other hand, the limits of the harmonic distortion for the 3-phase grid currents are 369 established according to the IEEE Std. 519-1992 Normative [36]. The THD limit is established in 5%,

meanwhile the limits for each harmonic order are lower, as it is indicated in Table 4.

371

370

Table 4. Regulation of harmonic current injection to the grid.

| Odd harmonics | Maximum value (%) |

|---------------|-------------------|

| 3 – 9         | 4                 |

| 11 – 15       | 2                 |

| 17 - 21       | 1.5               |

| 23 - 33       | 0.6               |

372

In order to validate the outstanding features of the PR plus the HC control strategy compared with the conventional dq control one, some simulations and experiments are carried out for both, mainly doing an analysis of the capability of each one in the compensation of the low-order harmonics of the 3-phase utility grid voltages.

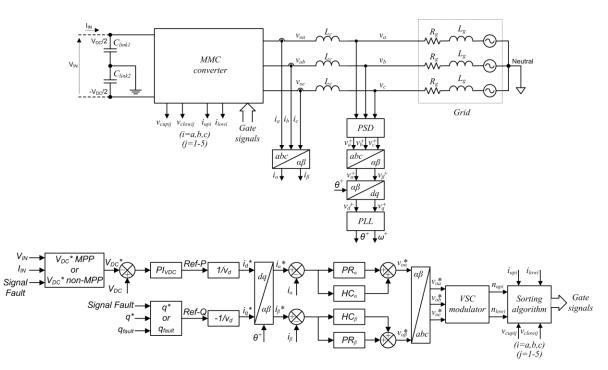

### 377 6. Simulations

378 The control scheme was explained in the previous sections divided into the main parts and the 379 whole system is depicted in Figure 12. In this case, minor changes in the control system are made to 380 allow the FRT operation. The reference line currents  $i_d^*$  and  $i_q^*$  are calculated applying (17) and (18) 381 to the outputs Ref\_P and Ref\_Q, respectively. The former follows the available maximum power 382 point (MPP) in normal operation, meanwhile the latter is set to  $q^*$  (zero for unity power factor 383 operation). Unlike, when a fault is detected in the 3-phase utility grid voltages, the input Signal Fault 384 is activated and the outputs Ref\_P and Ref\_Q will follow the non-MPP and  $q_{fault}$ , respectively. The 385 simulation of the entire MMC control scheme is performed in MATLAB/SIMULINK, using the 386 complete models of each SM and replacing the IGBT by ideal switches.

# **Figure 12.** Complete control scheme.

The 3-phase grid voltages  $v_{abc}$  and the phase currents  $i_{abc}$  are measured and a PSD [47] is applied to the former. Then,  $v_{abc}^+$  and  $i_{abc}$  are transformed to the stationary reference frame  $v_{\alpha\beta}^+$ (abc-> $\alpha\beta$  transformation), and  $v_{\alpha\beta}^+$  is transformed to the rotating grid voltage reference frame  $v_{dq}^+$ ( $\alpha\beta \rightarrow dq$  transformation). The positive sequence of the components of the grid voltages  $v_d^+$  and  $v_q^+$ are used by the PLL to obtain the phase angle  $\theta^+$  and the speed  $\omega^+$  of the rotating reference frame.

The main objective of the control system is to deliver the available maximum active power at the input of the MMC converter to the grid for normal operation with unity power factor, to reject the low-frequency harmonic distortions of the output currents produced by the utility grid voltages in order to improve the power quality of the installation, and to be able to deal with FRT operation. The actual values of the instantaneous active (p) and reactive (q) powers are calculated by means of (15) and (16).

401 The DC bus voltage regulator generates the active power reference Ref\_P (proportional to the d 402 component of the grid currents in the synchronous reference frame  $i_d^*$ ), meanwhile the quadrature 403 component Ref\_Q (proportional to  $i_q^*$ ) will depend on  $q^*$  in normal operation and on  $q_{fault}$  during 404 a fault. The reference command of the DC voltage  $V_{DC}^*$  will vary according to the normal operation 405 ( $V_{DC}^*$ MPP) or to the fault operation ( $V_{DC}^*$ non-MPP).

406 The current regulators generate the references of the direct and quadrature components of the 407 converter output voltage in the stationary reference frame,  $v_{o\alpha}^*$  and  $v_{o\beta}^*$ . The references  $v_{o\alpha}^*$  and  $v_{o\beta}^*$ 408 are transformed into  $v_{oabc}^*$  by using the inverse Clarke's transformation, which are the input of the 409 PD-SPWM voltage modulator.

410 The modulator sets the semiconductors' switching frequency  $F_{PWM}$  and its output is the 411 number of SMs to be set ON in each phase,  $n_{upi}$  and  $n_{lowi}$  (i = a, b, c).

The last block of the control system is the sorting algorithm to balance the SMs voltages. This block uses the actual SMs voltages and the sign of the arm currents. Its output is the gate signals of the SMs.

415 The main goal of the PR controllers applied to the  $\alpha$ - $\beta$  components of the 3-phase grid currents 416 is to attain a trade-off between the relative stability, the overshoot and the settling time of the 3-phase 417 output currents. So, its proportional constants are computed as in a PI regulator [42] where its 418 dynamics and stability are ensured by setting an adequate bandwidth (to reduce the voltage ripple 419 due to the switching frequency of the MMC converter) together with the proper phase margin in the 420 open loop Bode plot. Moreover a zero steady-state error is ensured by selecting the proper integral421 constants guaranteeing the stability limits [30,50].

For the outermost DC voltage loop, a similar approach is suggested for the computation of its proportional and integral constants of the PI regulator, but a very low bandwidth is mandatory in order to avoid the influence of the AC grid voltages in the loop [30].

425 The constants of the PI regulator of the PLL will be a function of the settling time ( $T_{set}$ ) and of 426 the damping factor ( $\zeta$ ) [40]. It is worth noting that these constants need to be normalized with the 427 peak value of the utility grid voltages in order to attain a proper behavior.

428 The Plant (MMC+Power system) is run at a rate of  $T_s$  seconds, meanwhile the Triggered 429 Subsystem updates its outputs at a rate of  $T_{reg}$  seconds, simulating an interrupt event used in the 430 microcontrollers for real-time control.

The simulation parameters of the power and control systems and their meaning are listed inTable 5. The constants of the regulators used in this work are highlighted in bold letters.

- 433

- 434

- 435

- 436

- -50

- 437

# 438

# Table 5. Simulation parameters.

| Number of Switching Modules SM                                | п               | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Active Power injected to the Grid                             | p*=Ref_P        | 300KW                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Reactive Power injected to the Grid                           | q*=Ref_Q        | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DC bus voltage                                                | $V^*_{DC}$      | 5KV                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| AC system                                                     | Uabc            | <ul> <li>Voltage level: 2165V(rms) line-to-line</li> <li>Frequency: 50Hz</li> <li>Harmonic Distortion: 5%,4%,3%,2.5%<br/>distortion for the magnitude of the 5<sup>th</sup>, 7<sup>ht</sup>, 11<sup>th</sup>, 13<sup>th</sup><br/>harmonics, respectively</li> <li>Strong Source: 6MVA of short circuit level<br/>(R<sub>g</sub>=0.039Ω; L<sub>g</sub>=2.48mH)</li> <li>Weak Source: 1.5MVA of short circuit level<br/>(R<sub>g</sub>=2.8Ω; L<sub>g</sub>=4.44mH)</li> </ul> |

| Arm Inductance                                                | L               | 375µН                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| The SM Capacitor                                              | С               | 30mF                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Coupling Inductance                                           | $L_c$           | 3mH                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Converter Gain                                                | Крwм            | $\frac{2}{3}V_{DC}^{*}$                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Switching Frequency                                           | <i>Fрwм</i>     | 6.104kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Current Crossover frequency<br>for open loop Bode (Bandwidth) | f <sub>cI</sub> | 800Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Current Phase Margin                                          | $PM_I$          | 60° aprox.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Cut-off frequency for the resonant filter                     | ωc              | 1rad/s                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Proportional constant of the<br>PR+HC controller              | $k_{p,Ilpha Ieta}$ | 0.0045               |

|---------------------------------------------------------------|--------------------|----------------------|

| Integral constant of the PR+HC controller                     | ki,1aIß            | 3                    |

| Voltage Crossover frequency<br>for open loop Bode (Bandwidth) | f <sub>cV</sub>    | 12.208Hz             |

| Voltage Phase Margin                                          | PMv                | 63.5°                |

| Proportional constant of the DC bus voltage regulator         | k <sub>p,Vcc</sub> | 0.1764               |

| Integral constant of the DC bus voltage regulator             | ki,Vcc             | 6.745                |

| Settling time of the PLL                                      | T <sub>set</sub>   | 20ms                 |

| Damping factor of the PLL                                     | ζ                  | $\frac{\sqrt{2}}{2}$ |

| Proportional constant of the PI regulator of the PLL          | $k_{p,PLL}$        | 0.2602               |

| Integral constant of the PI regulator of the PLL              | ki,PLL             | 59.8513              |

| Sample period of the Plant                                    | $T_s$              | 5.1196µs             |

| Sample period of the Triggered<br>Subsystem (Controller)      | T <sub>reg</sub>   | 40.957μs             |

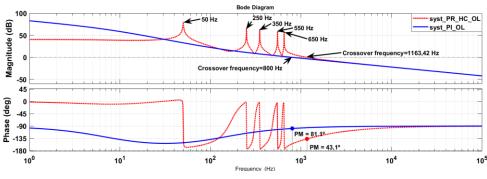

Figure 13 depicts the Bode plot for the PI and the PR+HC regulators, showing a stability behavior

for both at the selected crossover frequencies and phase margins. It is worth noting that the HC

structure does not affect the dynamics of the PR regulators because the peaks in the magnitude and

442 phase will only appear around the resonance frequencies.

# 443 444

445

For the PD-SPWM, three modulators (one per phase) were implemented using five triangular carriers (see Figure 11). The modulators compare the references of the converter voltage  $v_{oabc}^*$  with the carriers to generate the number of SMs to be switched ON in each arm (Table 2),  $n_{up}$  and  $n_{low}$ , and therefore, the three converter voltages  $v_{oabc}$ .

450 Next, several test simulations will be carried out for a Strong Grid firstly, and then for a Weak 451 Grid (see Table 5 for  $R_g$  and  $L_g$  values) in order to validate the control algorithms applied to the 452 power system. For all the tests the nominal active power injected into the grid is 300kW with unity 453 power factor in normal operation (no fault). Mainly, a comparison is made for the dq control 454 algorithm in d-q axes and the PR+HC control in  $\alpha$ - $\beta$  axes.

455 456 6

6.1 Strong Grid

459

# <u>**Test 1.</u> 5 SM**, $F_{PWM} = 6104$ Hz, $V_{DC}^* = 4200$ V</u>

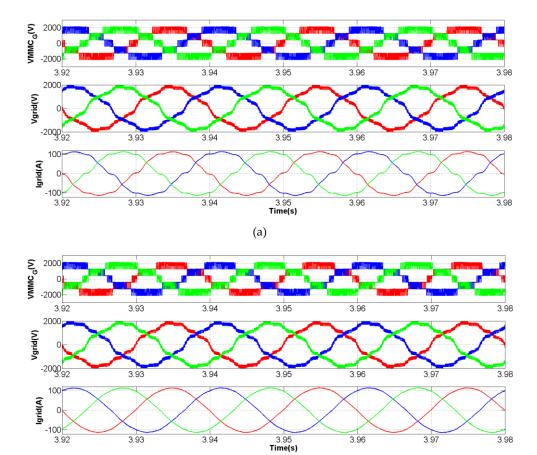

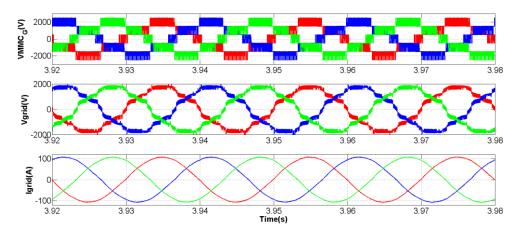

Figures 14 depicts the time evolution of the 3-phase MMC voltages, utility grid voltages and the grid currents for the dq control strategy and the PR controller plus the HC structure. For both situations, the maximum and minimum amplitude of the MMC voltages are ±2100V and a remarkable attenuation in the magnitude of the low-order harmonics of the grid currents can be seen for the PR controller + HC compared with the harmonic contamination in the dq control strategy.

- 465 466 467

- 468

- 469

- 470

- 471

- 472

- 473

(b)

- (a) dq control.

- (b) PR controller + HC.

475

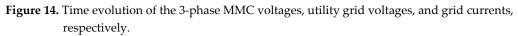

476 Figure 15 shows the time evolution of the current error in d-q and  $\alpha$ -β axes at steady- state. 477 Although there is an average zero steady-state error for both situations, a low-frequency oscillation 478 can be observed in in d-q axes due to the influence of the low-order harmonic distortions of the utility

- 479 grid voltages. However, there is no oscillation in  $\alpha$ - $\beta$  axes due to the compensation exerted by the

- 480 HC structure.

- 481

- 482

- 483

- 484

- 485

- 486

- 487

- 488

Figure 15. Time evolution of the current errors.

(a) d-q axes (dq control).

(b)  $\alpha$ - $\beta$  axes (PR controller + HC).

489 490 491

492

# <u>Test 2.</u> 7 SM, $F_{PWM} = 6104 \text{Hz}$ , $V_{DC}^* = 5000 \text{V}$

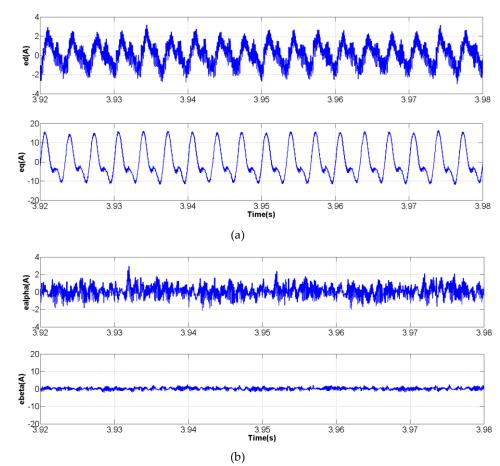

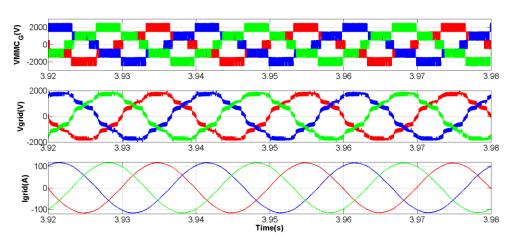

This test is similar to Test 1, but in this case 7 switching modules (7 SM) are employed and the DC bus voltage is increased to 5000V. Figure 16 depicts the time evolution of the 3-phase MMC voltages, utility grid voltages and the grid currents for both control strategies. Comparing with Figure 14, it is worth noting that the voltage levels has increased from 6 to 8 in the upper plot, whereas the maximum and minimum amplitude of the MMC voltages are ±2500V. Again, the harmonic distortion of the 3-phase grid currents is lower in the PR+HC control strategy.

- 42

- 500

Figure 16. Time evolution of the 3-phase MMC voltages, utility grid voltages, and grid currents, respectively.

- (a) dq control.

- (b) PR controller + HC.

# 502 <u>Test 3.</u> 5 SM, $F_{PWM}$ = 7630 Hz, $V_{DC}^*$ = 5000V

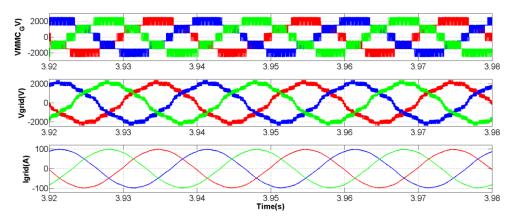

503 In this test, 5 SM are used and the switching frequency  $F_{PWM}$  is set to 7630Hz, while the DC 504 bus voltage remains in 5000V. Figure 17 shows the time evolution of the 3-phase MMC voltages, 505 utility grid voltages and the grid currents for PR controller plus the HC structure. Again, the 3-506 phase grid currents are almost sinusoidal with no distortions.

**Figure 17.** Time evolution of the 3-phase MMC voltages, utility grid voltages, and grid currents, respectively (PR controller + HC).

- 508

- 509 <u>Test 4.</u> 5 SM,  $F_{PWM} = 9156$ Hz,  $V_{DC}^* = 5000$ V

- 510

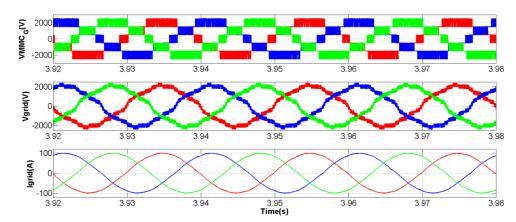

511 In this case, the switching frequency  $F_{PWM}$  is increased to 9156Hz. Figure 18 shows the time 512 evolution of the 3-phase MMC voltages, utility grid voltages and the grid currents for PR controller

513 plus the HC structure with a similar behavior as Test 3.

514

**Figure 18.** Time evolution of the 3-phase MMC voltages, utility grid voltages, and grid currents, respectively (PR controller + HC).

- 515

- 516

- 517 6.2 Weak Grid

- 518

519

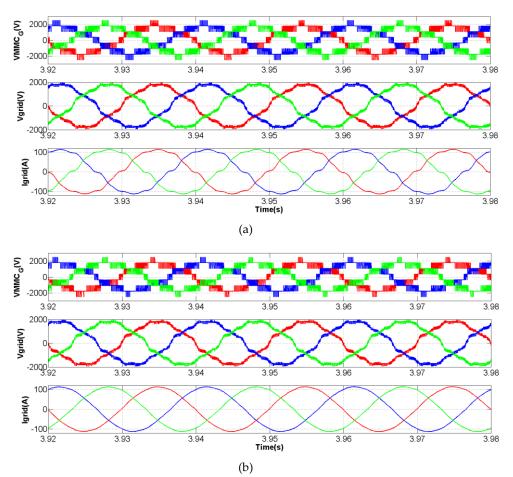

<u>**Test 5.**</u> 5 SM,  $F_{PWM}$  = 7630Hz,  $V_{DC}^*$ =5000V

520

521 For a switching frequency  $F_{PWM}$  set to 7630Hz, Figure 19 depicts a similar behavior as Figure 17 522 (Test 3, Strong Grid), although the amplitude of the 3-phase grid currents is less for this case.

Figure 19. Time evolution of the 3-phase MMC voltages, utility grid voltages, and grid currents, respectively (PR controller + HC).

<u>**Test 6.**</u> 5 SM,  $F_{PWM} = 9156$ Hz,  $V_{DC}^* = 5000$ V 525

526

524

527 In this case, the switching frequency  $F_{PWM}$  is set to 9156Hz and the time evolution of the 3-phase 528 variables are depicted in Figure 20. Comparing this Figure with Figure 18 (Test 4, Strong Grid), the 529 amplitude of the 3-phase grid currents is also less for this case.

530

Figure 20. Time evolution of the 3-phase MMC voltages, utility grid voltages, and grid currents, respectively (PR controller + HC).

531

- 532 6.3 Voltage Sags

- 533

534 Next tests are intended to deal with voltage faults at the converter terminal. In general, grid 535 codes [51,52] force the converter not only to remain connected even when severe faults occur, but 536 also to inject a certain amount of reactive power according to the depth of the voltage sag, together 537 with a limitation of the output grid currents to its nominal value, avoiding the automatic 538 disconnection due to the overcurrent protection. This feature is known as Low-Voltage-Ride-539 Through (LVRT) or Fault-Ride-Through (FRT). In short, it must be pointed out that there will be two 540 mode of operations: one mode is for normal operation with nominal values of the active (P) and 541 reactive (Q) powers, meanwhile the second mode of operation will be activated when fault events 542 occur.

543 For the next tests, there are 5 SM, the switching frequency is  $F_{PWM} = 6104$ Hz, and the DC bus 544 voltage  $V_{DC}^*$ =5000V.

- 545

- 546 <u>**Test 7.**</u> 3-phase deep voltage sag (0.1(pu))

- 547

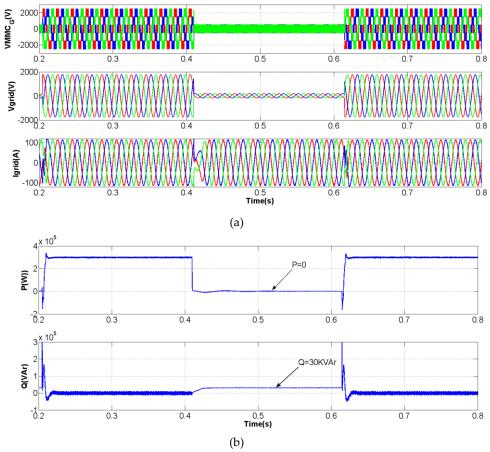

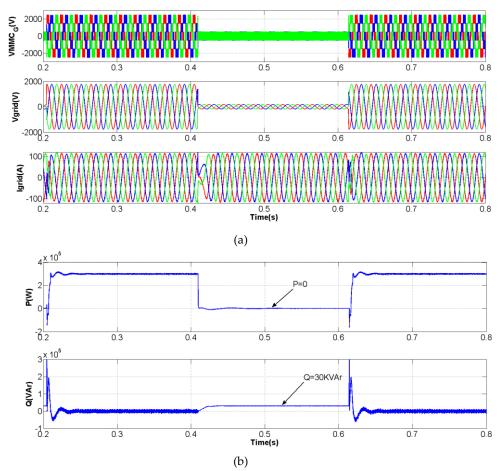

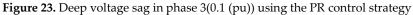

Figure 21 and 22 depict the response of the control algorithm to a 3-phase deep voltage sag (0.1 (pu)) for the dq control and the PR controller strategies, respectively. It can be observed that both strategies behave similar. The 3-phase fault event occurs at 0.42s approximately and, in the lower plot of (a) the time evolution of the 3-phase output grid currents indicates that there are no overcurrent during the event, meanwhile in (b) the plot indicates that the active power (P) is zero and the reactive power (Q) is 30KVAr. When the fault event finishes, the normal operation of the grid-connected MMC is established (P=300KW and Q=0).

555 Because of the similar behavior of both strategies when dealing with a 3-phase deep voltage sag 556 together with the capability of the PR controller + HC structure to compensate the low-order 557 harmonic distortions of the utility grid voltages, this control strategy will be evaluated in the next 558 tests.

- 559

- 560

Figure 21. 3-phase deep voltage sag (0.1 (pu)) using the dq control strategy

(a) Time evolution of the 3-phase MMC voltages, utility grid voltages, and grid currents, respectively.

(b) Time evolution of the active (P) and reactive power (Q)

561 562

- 564

- 565

- 566

- 567

- 568

- 569

(a) Time evolution of the 3-phase MMC voltages, utility grid voltages, and grid currents, respectively.

(b) Time evolution of the active (P) and reactive power (Q)

571 572

573

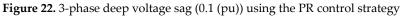

Test 8. Deep voltage sag in phase 3 (0.1(pu))

574 In this case, a deep voltage sag occurs at 0.42s approximately in phase 3 as shown in Fig. 23a. 575 During the fault the 3-phase output currents are below its nominal value, meanwhile a certain 576 amount of active power P=79KW and a reactive power Q=90KVAr are injected into the grid. The 577 negative sequence component of the 3-phase utility grid voltages during the unbalanced fault (with 578 angular speed  $\omega^{-}$  in the rotating reference frame) together with its positive sequence produce the 579 oscillating nature of the active and reactive powers at the second order harmonic of the fundamental 580 frequency around their mean values. Also, the normal operation is attained when the fault event 581 finishes.

582

583

(a) Time evolution of the 3-phase MMC voltages, utility grid voltages, and grid currents, respectively.

(b) Time evolution of the active (P) and reactive power (Q)

586

587 588

589

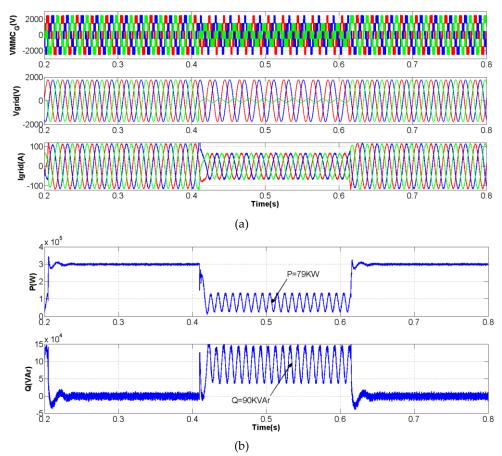

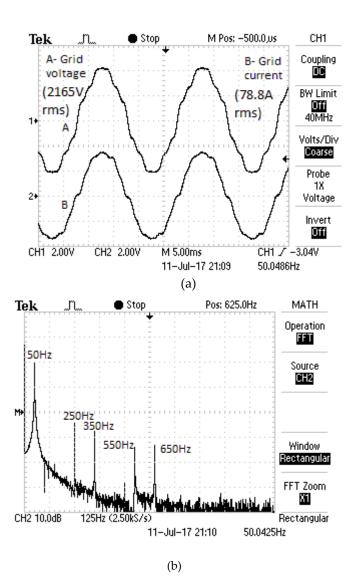

Test 9. Moderate voltage sag in phase 3 (0.5(pu))

Figure 24 depicts a moderate voltage sag in phase 3 (0.5 (pu)). Again the output grid currents are below its nominal value and, in this case, a higher amount of active power is injected into the grid (P=198KW), and the reactive power Q=31.5KVAr. Again, the negative sequence of the 3-phase utility grid voltages produces the second order harmonic oscillations around the mean value of the active and reactive powers. When the fault ends, the normal operation is reached.

- 595

- 596

- 597 598

Figure 24. Moderate voltage sag in phase 3(0.5 (pu)) using the PR control strategy

(a) Time evolution of the 3-phase MMC voltages, utility grid voltages, and grid currents, respectively.

(b) Time evolution of the active (P) and reactive power (Q)

#### 599

# 600 7. Experiments

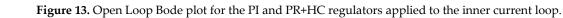

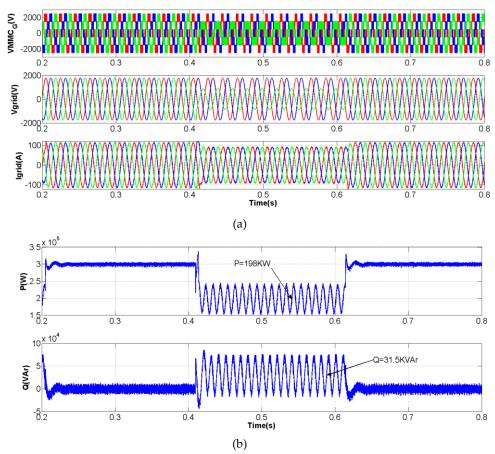

601 Some experiments are shown in this paper to reinforce the validity of the control algorithm with 602 Proportional Resonant controllers, and the Hardware-in-the-Loop (HIL) Simulation technique 603 [53,54,55] is used for this. On one hand this technique uses a Real Time Digital Simulator (RTDS) with 604 several I/O digital signals, as well as analog to digital and/or digital to analog converters (ADC and 605 DAC blocks), in order to simulate in real time the behavior of any power system, including the power 606 converter. On the other hand, an actual controller is connected to the input/output signals of the 607 RTDS in order to exert a real time control. The actual controller ignores if the control is being exerted 608 to a Simulator or to an actual power system, but the exchange of power is avoided and the safety of 609 the installation is guaranteed, as well as the possibility to impose a series of critical tests to explore 610 the response of the implemented control algorithms before the development of the prototype.

611 The RTDS platform used in this paper is built with the dSPACE DS1006 power processor, and 612 the DS5202 Electric Motor HIL Solution boards with several I/O digital signals, and ADC and DAC 613 blocks. The latter is the interface between the power processor and the controller prototype that is 614 built with the dSPACE DS1104 card (see Figures 25 and 26). The model blocks of both the RTDS and 615 the controller are built in MATLAB/SIMULINK in two Host PCs (Host PC 1: Windows 7 Professional 616 (64 bits), 4GBytes of RAM, Intel Core i3 530@2.93GHz; Host PC 2: Windows XP SP3 (32 bits), 4GBytes 617 of RAM, Intel Core 2 6300@1.86GHz), the C-code is generated automatically with Real Time 618 workshop and downloaded into both targets.

619 For the RTDS platform, the range of analog voltage of the ANALOG OUT<sub>1-6</sub> is  $\pm 10V$  (single-620 ended) and is used for the 3-phase grid voltages ( $v_{abc}$ ) and currents ( $i_{abc}$ ), meanwhile for the 621 ANALOG OUT<sub>7</sub> is +10V and is used for the DC bus voltage ( $V_{DC}$ ). The range of the analog voltage of 622 the ANALOG IN<sub>1-3</sub> is  $\pm 15V$  (single-ended) and are fed by the duty cycles ( $d_{voabc}$ ) sent by the controller 623 card. For the controller prototype, the ADCs and DACs have an analog voltage range of  $\pm 10V$  (single-624 ended). For both, the RTDS platform and the controller prototype, all voltage ranges are expressed 625 as peak values, and it is worth noting that according to these voltage levels, both electronic cards can 626 be connected directly because dSPACE ensures the compatibility [56], although additional signal 627 conditioner electronic circuits can be used to accommodate different levels of voltages and currents. 628 Finally, some measurements are displayed in an oscilloscope for monitoring purposes.

629 It must be pointed out that an average model for the MMC is used in the power system, and the 630 3-phase utility grid voltages are perturbed with the 5th, 7th, 11th, and 13th harmonics, with an amplitude 631 of 5, 4, 3 and 2.5%, respectively, compared to the magnitude of the fundamental frequency of 50Hz. 632 The time step is set to 13.65µs for the RTDS ( $T_s$ ) and to 40.96µs for the controller ( $T_{reg}$ ); the latter has 633 a delay of  $\frac{3}{2}T_{reg} = 61.44 \mu s$  in the worst case. Furthermore, the discretization of any digital filter of 634 the PSD block in the PLL, eg. the 90-degree phase-shift operator S90 [40,47], which not also reject the 635 negative sequence of the 3-phase utility grid voltages, but also reduce the unbalances produced at 636 the output of the data acquisition electronic card as said before [48], must obey the time step of the 637 controller algorithm to avoid the degradation of the power factor. Firstly, the tests are carried out 638 when the dq control strategy is used to regulate the 3-phase line currents; and secondly, the same 639 tests are carried out when the PR controller and the HC structure are used. 640

642 **Figure 25.** Block diagram of the HIL platform.

644 **Figure 26.** Photo of the HIL platform.

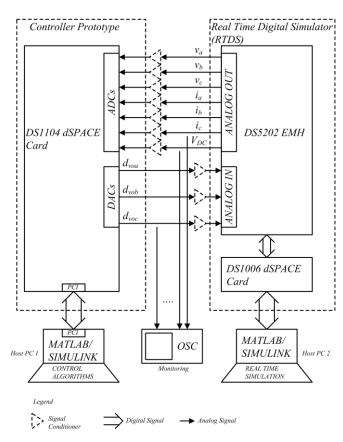

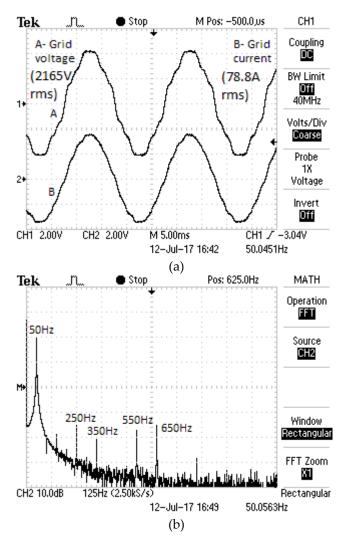

The time evolution of the grid voltage and current at phase 1 is depicted in Figure 27a, meanwhile the frequency spectrums of the grid current is depicted in Figure 27b for the dq control algorithm. In this case, the individual low-order harmonic distortions of the grid current exceeds the limits imposed by the Normative (see Table 4), except for the 11<sup>th</sup> harmonic, and the THD also exceeds the limit of the Normative, as can be seen in Table 6. So, the dq control strategy will not be valid for the connection of the renewable system to the utility grid if the 3-phase utility grid voltages were disturbed by the maximum allowed magnitude distortions in the low-order harmonics.

- 652

- 653

- 654

- 655

- 656

- 657

- 658

Figure 27. (a) Time evolution of utility grid voltage and current at phase 1 for dq control.(b) Frequency spectrum of the grid current at phase 1.

| Harmonic | Measured value (%) |   | Maximum value (%) |

|----------|--------------------|---|-------------------|

| 5        | 6.3                | > | 4                 |

| 7        | 4.47               | > | 4                 |

| 11       | 2                  | = | 2                 |

| 13       | 2.24               | > | 2                 |

| THD      | 8.29               | > | 5                 |

Table 6. Harmonic distortion for the grid current in phase 1 (dq control).

659

The same situation is shown in Figure 28a and 28b when the PR controller and the HC structure are used. In this case, both the individual harmonic distortions in the magnitude of the grid current, as well as its THD are lower than the limits imposed by the Normative, as can be seen in Table 7. So, the PR controller plus the HC are valid for the connection of the renewable system to the utility grid even for the maximum allowed distortion in the magnitude of the loworder harmonics of the 3-phase utility grid voltages.

**Figure 28. (a)** Time evolution of utility grid voltage and current at phase 1 for the PR controller and the HC structure.

(b) Frequency spectrum of the grid current at phase 1.

# 667

668

Table 7. Harmonic distortion for the grid current in phase 1 (PR Control + HC).

| Harmonic | Measured value (%) |   | Maximum value (%) |

|----------|--------------------|---|-------------------|

| 5        | 1.78               | < | 4                 |

| 7        | 0.94               | < | 4                 |

| 11       | 1.41               | < | 2                 |

| 13       | 1.78               | < | 2                 |

| THD      | 3.04               | < | 5                 |

669

670

# 671 Acknowledgments

This work has been partially supported by a grant from the Spanish Government as a part of

Project Ref. TEC2016-80136-P, entitled "Nuevas topologías para convertidores en MT para grandes

Instalaciones Fotovoltaicas" (A. B. Rey-Boué)

# 676 8. Conclusions

677 This article presents a comprehensive and detailed study of an enhanced control of an MMC, 678 mainly because a reduction in the need for AC filtering is achieved, reducing also the overall cost of 679 the installation. Its easy scalability will be useful for those who want to integrate it into a larger 680 application which may include two MMCs (one for the AC/DC conversion and one for DC/AC), or 681 into an offshore wind application. However, the use of MMCs needs more sophisticated algorithms 682 for balancing the voltages of the high number of modules, and modulators such as the PD-SPWM 683 used in this paper to generate the multilevel output voltage, yielding to the use of more powerful 684 microcontrollers.

The Proportional Resonant (PR) controllers and a Harmonic Compensator (HC) scheme, both in the stationary reference frame, are used as an enhanced controller in this paper for the inner current control loops, unlike the commonly used PI regulators in the synchronous reference frame. For both strategies, the power factor of the MMC-grid connection can be controlled in the same manner. The power balance is done with a PI regulator in the outer DC bus voltage control loop, guaranteeing the injection of the maximum available power, coming from the Renewable system at the input of the MMC, into the utility grid.

The simulations and experiments carried out validate the behavior of the enhanced controller. Regarding the experiments, it can be seen that the amplitude of the individual and total harmonic distortions of the 3-phase grid currents is below the limits imposed by the grid code when the PR plus the HC controller is used, improving the power quality and making possible the MMC-grid connection, meanwhile these distortions exceed the limits when the PI regulators are employed, which do not allow the connection.

The effects of single-phase and three-phase low voltage, single-phase and three-phase faults and

grid unbalances have been simulated. In all cases, the converter remains connected, the grid current

does not exceed the nominal value and neither active nor reactive power of the grid is demanded.

Finally, the PR plus the HC controller can be used in any other application that controls the currents in the inner loops of the power converter, i.e., Active Power Filters (APF), Voltage Source Converters (VSC) for renewables, stand-alone and grid-connected microgrids, etc. In addition, this control strategy can be applied in 1- or 3-phase systems.

705 706

# 707 References

- Montilla-DJesus, M.; Santos-Martin, D.; Arnaltes, S.; Castronuovo, E.D. Optimal reactive power allocation in an offshore wind farms with LCC-HVdc link connection. Renew. Energy 2012, 40, 157–166.

- Aragues-Penalba, M.; Egea-Alvarez, A.; Gomis-Bellmunt, O.; Sumper, A. Optimum voltage control for loss

minimization in HVDC multi-terminal transmission systems for large offshore wind farms. Electr. Power.

Syst. Res. 2012, 89, 54–63.

- A. Larruskain, D.M.; Zamora, I.; Abarrategui, O.; Iturregi, A. VSC-HVDC configurations for converting AC distribution lines into DC lines. Int. J. Electr. Power Energy Syst. 2014, 54, 589–597.

- 4. Lesnicar, A.; Marquardt, R. An innovative modular multilevel converter topology suitable for a wide

power range. In Proceedings of the Power Tech Conference, Bologna, Italy, 23-26 June 2003.

- 5. Chaves, M.; Margato, E.; Silva, J.F.; Pinto, S.F.; Santana, J.; HVDC transmission systems: Bipolar back-to-back diode clamped multilevel converter with fast optimum-predictive control and capacitor balancing strategy. Electr. Power Syst. Res. 2011, 81, 1436–1445.

- Flourentzou, N.; Agelidis, V.G.; Demetriades, G.D. VSC-based HVDC power transmission systems: an

overview. IEEE Trans. Power Electron. 2009, 24, 592-602.

- 722 7. Rohner, S.; Bernet, S.; Hiller, M.; Sommer, R. Modulation, losses, and semiconductor requirements of 723 modular multilevel converters. IEEE Trans. Ind. Electron. 2010, 57, 2633-2642.

- Saeedifard, M.; Iravani, R. Dynamic performance of a modular multilevel back-to-back HVDC system. IEEE

Trans. Power Deliver. 2010, 25, 2903-2912.

- Hagiwara, M.; Akagi, H. Control and experiment of pulsewidth-modulated modular multilevel converters.

IEEE Trans. Power Electron. 2009, 24, 1737-1746.

- 728 10. Qin, J.; Saeedifard, M. Predictive control of a modular multilevel converter for a back-to-back HVDC

729 system. IEEE Trans. Power Deliver. 2012, 27, 1538–1547.

- 730 11. Deng, F.; Chen, Z. A control method for voltage balancing in modular multilevel converters. IEEE Trans.

731 Power Electron. 2014, 29, 66-76.

- 732 12. Qin, J.; Saeedifard, M. Reduced switching-frequency voltage-balancing strategies for modular multilevel

733 HVDC converters. IEEE Trans. Power Deliver. 2013, 28, 2403-2410.

- Saad, H.; Peralta, J.; Dennetière, S.; Mahseredjian, J.; Jatskevich, J.; Martinez, J.A.; Davoudi, A.; Saeedifard,

M.; Sood, V.; Wang, X.; Cano, J.; Mehrizi-Sani, A. Dynamic averaged and simplified models for MMCbased HVDC transmission systems. IEEE Trans. Power Deliver. 2013, 28, 1723-1730.

- Peralta, J.; Saad, H.; Dennetière, S.; Mahseredjian, J.; Nguefeu, S. Detailed and averaged models for a 401level MMC–HVDC system. IEEE Trans. Power Deliver. 2012, 27, 1501-1508.

- 739 15. Gnanarathna, U.N.; Gole, A.M.; Jayasinghe, R.P. Efficient modeling of modular multilevel HVDC

740 converters (MMC) on electromagnetic transient simulation programs. IEEE Trans. Power Deliver. 2011, 26,

741 316-324.

- 16. Liu, C.; Lin, X.; Li, H.; Cheng, X.; Li, G. Sub-module component developed in CBuilder for MMC control

and protection test in RTDS. Int. J. Electr. Power Energy Syst. 2014, 56, 198–208.

- 744 17. Zhang, M.; Huang, L.; Yao, W.; Lu, Z. Circulating harmonic current elimination of a CPS-PWM-based

745 modular multilevel converter with a plug-in repetitive controller. IEEE Trans. Power Electron. 2014, 29,

746 2083-2097.

- Song, Q.; Liu, W.; Li, X.; Rao, H.; Xu, S.; Li, L. A steady-state analysis method for a modular multilevel converter. IEEE Trans. Power Electron. 2013, 28, 3702-3713.

- Moon, J.W.; Kim, C.S.; Park, J.W.; Kang, D.W.; Kim, J.M. Circulating current control in MMC under the

unbalanced voltage. IEEE Trans. Power Deliver. 2013, 28, 1952-1959.

- Guan, M.; Xu, Z. Modeling and control of a modular multilevel converter-based HVDC system under

unbalanced grid conditions. IEEE Trans. Power Electron. 2012, 27, 4858-4867.

- Ramirez D., Martinez-Rodrigo F., de Pablo S., Herrero-de Lucas L. C. Assessment of a non linear current control technique applied to MMC-HVDC during grid disturbances. Renewable Energy. 2017, 101, 945-963.

- Tu, Q.; Xu, Z. Impact of sampling frequency on harmonic distortion for modular multilevel converter. IEEE

Trans. Power Deliver. 2011, 26, 298-306.

- 23. Li, X.; Song, Q.; Liu, W.; Rao, H.; Xu, S.; Li, L. Protection of nonpermanent faults on DC overhead lines in

MMC-based HVDC systems. IEEE Trans. Power Deliver. 2013, 28, 483-490.

- 759 24. Martinez-Rodrigo, F.; de Pablo, S.; Herrero-de Lucas, L.C. Current control of a modular multilevel

760 converter for HVDC applications. Renew Energy. 2015, 83, 318-331.

- 761 25. Malesani L., Tenti P. A novel hysteresis control method for current-controlled voltage-source PWM

762 inverters with constant modulation frequency. IEEE Trans. Ind. Appl. 1990, 26(1), 88-92.

- Poundaria A., Gaubert J.P., Krim F. Design and implementation of predictive current control of three-phase

PWM rectifier using space-vector modulation (SVM). Energy Convers. Manage. 2010, 51(12), 2473–2481.

- 765 27. Malesani L., Mattavelli P., Buso S. Robust dead-beat current control for PWM rectifiers and active filters.

766 IEEE Trans. Ind. Appl. 1999, 35(3), 613–620.

- Chinchilla M., Arnalte S., Burgos J.C., Rodríguez J.L. Power limits of grid-connected modern wind energy systems. Renew. Energy. 2005, 31(9), 1455–1470.

- Zmood D.N., Holmes D.G., Bode G.H. Frequency-domain analysis of three-phase linear current regulators.

IEEE Trans. Ind. Appl. 2001, 37(2), 601–610.

- Rey-Boué A.B., García-Valverde R., Ruz-Vila F., Torrelo-Ponce J.M. An integrative approach to the design methodology for 3-phase power conditioners in Photovoltaic Grid-Connected systems. Energy Convers. Manag. 2012, 56, 80–95.

- 774 31. Park R.H., Two reaction theory of synchronous machines. Generalized method of analysis Part I, in Proc.

775 Winter Convention of AIEE. 1929, 716–730.

- Guerrero-Rodríguez N.F., Rey-Boué A.B., Herrero-de Lucas L.C., Martinez-Rodrigo F. Control and synchronization algorithms for a grid-connected photovoltaic system under harmonic distortions, frequency variations and unbalances. Renew Energy. 2015, 80, 380-395.

- 33. Limongi L., Bojoi R., Griva G., and Tenconi A. Digital current-control schemes. IEEE Ind. Electron. Mag.

2009, 3 (1), 20–31.

- 34. G. Yepes A., Freijedo F.D., Doval-Gandoy J., López O., Malvar J., and Fernandez-Comesaña P. Effects of

Discretization Methods on the Performance of Resonant Controllers. IEEE Trans. Power Electron. 2010,

25(7), 1692-1712.

- 784 35. IEC/TR 61000-3-6. Electromagnetic compatibility (EMC). Part 3-6: Limits-Assessment of emission limits for

785 the connection of distorting installations to MV, HV and EHV power systems, 2008.

- 786 36. IEEE Std. 519-1992. IEEE Recommended practices and requirements for harmonic control in electrical power systems, 1993.

- 788 37. Mattavelli P. A closed-loop selective harmonic compensation for active filters. IEEE Trans. Ind. Appl. 2001,

789 37, 81–89

- 790 38. Kazmierkowski MP, Krishnan R., Blaabjerg F. Control in power electronics, selected problems. Elsevier

791 Science, 2002.

- 792 39. Teodorescu R., Liserre M., Rodriguez P. Grid converters for photovoltaic and wind power systems. United

793 Kingdom, John Wiley & Sons, Ltd, 2011.

- 40. Guerrero-Rodríguez N.F., Herrero-de Lucas L.C., de Pablo-Gómez S., Rey-Boué A.B. Performance study of

a synchronization algorithm for a 3-phase photovoltaic grid-connected system under harmonic distortions

and unbalances. Electr. Power. Syst. Res. 2014, 116, 252–265.

- Xiaoming Y., Merk W., Stemmler H., Allmeling J. Stationary-frame generalized integrators for current control of active power filters with zero steady-state error for current harmonics of concern under unbalanced and distorted operating conditions. IEEE Trans. Ind. App. 2002, 38, 523–532.

- 42. Teodorescu R., Blaabjerg F., Liserre M., Loh PC. Proportional-resonant controllers and filters for grid connected voltage-source converters. IEE Proc Electric Power App. 2006, 153, 750–762.

- 43. Liang, J.; Gomis-Bellmunt, O.; Ekanayake, J.; Jenkins, N.; An, W. A multi-terminal HVDC transmission

system for offshore wind farms with induction generators. Int. J. Electr. Power Energy Syst. 2012, 43, 54–

62.

- 44. Akagi H., Kanazawa Y., Nabae A. Instantaneous reactive power compensators comprising switching

devices without energy storage components. IEEE Trans. Ind. App. 1984, IA-20(3), 625–630.

- 807 45. Ferrero A., Superti-Furga G. A new approach to the definition of power components in three-phase systems

808 under nonsinusoidal conditions. IEEE Trans. Instrum. Meas. 1991, 40(3), 568–577.

- 46. Arruda, L.N.; Silva, S.M.; Filho, B.J.C. PLL structures for utility connected systems. In Proceedings of the

Industry Applications Conference, Chicago, USA, 30 September 1 October 2001.

- 47. M. Karimi-Ghartemani, M.R. Iravani. A method for synchronization of power electronic converters in polluted and variable-frequency environments. IEEE Trans. Power Syst. 2004, 19, 1263–1270.

- 813 48. Chung S. A Phase Tracking System for Three Phase Utility Interface Inverters. IEEE Trans. Power Electron.

814 2000, 15(3), 431-438.

- 49. Agelidis, V.;Calais, M. Application specific harmonic performance evaluation of multicarrier PWM

techniques. In Proceedings of the IEEE Power Electronics Specialists Conference, Fukuoka, Japan, 17-22

817 May 1998.

- 818 50. Guerrero-Rodríguez N.F., Rey-Boué A.B. Modelling, simulation and experimental verification for renewable agents connected to a distorted utility grid using a Real-Time Digital Simulation Platform.

820 Energy Convers. Manag. 2014, 84, 108–121.

- Afshari, E.; Reza G.; Rahimi R.; Farhangi, B. Yang, Y.; Blaabjerg, F.; Farhangi, S. Control Strategy for ThreePhase Grid-Connected PV Inverters Enabling Current Limitation Under Unbalanced Faults. IEEE Trans.

Ind. Electron. 2017, 64, No. 11, 8908-8918.