#### AN ABSTRACT OF THE THESIS OF

Xiaoran Gao for the degree of Master of Science in

Electrical and Computer Engineering presented on March 20, 2008,

Title: A Survey on Continuous-Time  $\Delta\Sigma$  Modulators---Theory, Designs and

**Implementations**

Redacted for privacy

Abstract approved:

Gabor C. Temes

Recently, delta-sigma modulation has become a widely applied technique for high-performance analog-to-digital conversion of narrow-band signals. Most of the early designs used discrete-time structure for good accuracy and good linearity. The transfer functions are independent of the clock frequency. However, high unity-gain bandwidths of the opamps are required to satisfy the settling accuracy required in the discrete-time designs. Continuous-time structure can potentially achieve higher clock frequency with less power consumption. the antialiasing filter can also be eliminated due to the anti-aliasing property of CT  $\Delta\Sigma$  modulators. On the other hand, CT  $\Delta\Sigma$  ADC have their own problems, such as jitter sensitivity and excess loop delay.

In this thesis, the state-of-the-art of CT  $\Delta\Sigma$  modulator is reviewed. The problems in the design of CT  $\Delta\Sigma$  ADCs are analyzed and solutions to them are described. The theory, design and implementations of CT  $\Delta\Sigma$  modulator will also be reviewed.

# A Survey on Continuous-Time $\,\Delta\Sigma\,Modulators$

---Theory, Design, and Implementation

by

Xiaoran Gao

A THESIS

Submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Presented March 20, 2008 Commencement June 2008 APPROVED:

Redacted for privacy

Major Professor, representing Electrical and Computer Engineering

# Redacted for privacy

Director of the School of Electrical Engineering and Computer Science

# Redacted for privacy

Dean of the Graduate School

I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorized release of my thesis to my any reader upon request.

# Redacted for privacy

Xiaoran Gao, Author

#### **ACKNOWLEDGEMENTS**

I highly appreciate the many people who have helped me in my study and made my life at Oregon State University educational and enjoyable.

In particular, I would like to express my sincere appreciation to my advisor, Dr. Gabor C. Temes. I liked to study and research under his supervision. I greatly benefited from his intuition and extensive knowledge of system and circuit design, from his emphasis on clarity in presentation, from his invaluable teaching and research skills, and from his guidance in writing thesis.

I would like to thank Dr. Huaping Liu, Dr. Xiaoli Fern and Dr. Abdollah T. Farsoni for serving in my graduate committee.

I want to express my appreciation to my colleagues in delta-sigma group, who contributed in many ways to excellent environment. I sincerely thank Yan Wang, Weilun Shen and Wenhuan Yu who helped me a lot to gain the background knowledge on the  $\Delta\Sigma$  modulator. I want to thank to Wenhuan Yu who helped me a lot in writing my thesis.

Finally, I want to express my deepest gratitude to my wife, for her financial support and understanding. Her encouragement and caring is invaluable.

# TABLE OF CONTENTS

|    | <u>rage</u>                                                               |

|----|---------------------------------------------------------------------------|

| 1. | INTRODUCTION                                                              |

|    | 1.1 Motivation                                                            |

|    | 1.2 Thesis organization                                                   |

| 2. | OVERVIEW OF OVERSAMPLING $\Delta\Sigma$ ADC                               |

|    | 2.1 Sampling and Quantization                                             |

|    | 2.2 Oversampling and Noise Shaping                                        |

|    | 2.3 Performance Increase and Improvement in the $\Delta\Sigma$ modulators |

|    | 2.4 The Stability of $\Delta\Sigma$ A/D Converters9                       |

|    | 2.5 Comparison Between DT and CT $\Delta\Sigma$ Modulators10              |

|    | 2.6 Continuous-Time Loop Filter Synthesis                                 |

| 3. | ARCHITECTURES                                                             |

|    | 3.1 Single-Stage CT $\Delta\Sigma$ Modulator Topologies                   |

|    | 3.2 Multi-Stage CT ΔΣ Modulator Topologies                                |

| 4. | NON-IDEALITIES AND CORRECTION TECHNIQUES                                  |

|    | 4.1 Non-Idealities in the DAC (I)Excess Loop Delay35                      |

|    | 4.2 Non-Idealities in the DAC (II)Clock Jitter42                          |

|    | 4.3 Non-Idealities of CT Integrators                                      |

|    | 4.4 Error of the Internal Quantizer                                       |

| 5. | IMPLEMENTATION FO CT $\Delta\Sigma$ MODULATORS                            |

|    | 5.1 System Architecture Considerations                                    |

|    | 5.2 Circuit Designs and Implementations90                                 |

# TABLE OF CONTENTS (Continued)

|    |                     | <u>Page</u> |

|----|---------------------|-------------|

|    | 5.3 Implementations | 95          |

| 6. | SUMMARY             | 104         |

| Βľ | BLIOGRAPHY          | 105         |

# A Survey on Continuous-Time $\Delta\Sigma$ Modulators -----Theory, Designs and Implementations

#### 1 INTRODUCTION

#### 1.1 Motivation

Delta-sigma ( $\Delta\Sigma$ ) data converters have been developed since the 1960's. Nowadays it is one of the most popular architectures used in high-performance analog-to-digital and digital-to-analog converters, especially in high resolution and medium-to-low speed applications. By using oversampling and noise shaping, the stringent demand on analog circuit imperfection (matching, *etc.*) is greatly relaxed.

$\Delta\Sigma$  ADCs can be divided into two categories: discrete-time (DT) or continuous-time (CT)  $\Delta\Sigma$  ADCs. Most of the early designs used DT structure for good accuracy and good linearity. In DT designs, the transfer functions are independent of the clock frequency. However, high unity-gain bandwidths of the opamps are required to satisfy the settling accuracy required in the DT designs.

CT  $\Delta\Sigma$  ADCs can potentially achieve higher clock frequency with less power consumption. The anti-aliasing filter can also be eliminated due to the anti-aliasing property of CT  $\Delta\Sigma$  ADCs. On the other hand, CT  $\Delta\Sigma$  A/D converters have their own problems, such as jitter sensitivity and excess loop delay.

In this thesis, the state-of-the-art of CT  $\Delta\Sigma$  ADCs is reviewed. The problems in the design of CT  $\Delta\Sigma$  ADCs are analyzed and solutions to them are reviewed.

# 1.2 Thesis Organization

The thesis is organized as follows. Section 2 provides some background information on CT  $\Delta\Sigma$  modulators. Section 3 gives an introduction of the architecture of the CT  $\Delta\Sigma$  A/D converters. Section 4 gives a review of the design considerations in the CT  $\Delta\Sigma$  A/D converters. Section 5 reviews several recent implementations of CT  $\Delta\Sigma$  modulators. Finally, Section 6 concludes the thesis.

# 2. OVERVIEW OF OVERSAMPLING ΔΣ ADC

This section provides an introduction to analog-to-digital converters (A/D converter or ADC). The concepts of quantization, oversampling and noise shaping are introduced. The performance and stability of  $\Delta\Sigma$  modulators are reviewed. The discrete-time and continuous-time  $\Delta\Sigma$  modulators are compared.

#### 2.1 Sampling and quantization

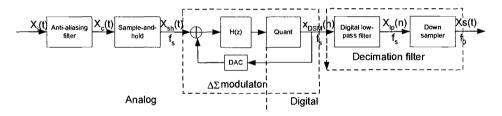

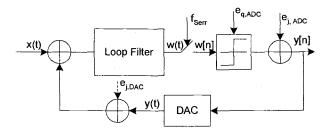

The conversion of the analog signal to the digital signal can be divided into two steps: the sampling in time and the quantization in amplitude. A typical block diagram of a  $\Delta\Sigma$  modulator is given in Fig 2.1.

Fig. 2.1 Block diagram of an oversampling A/D converter

If the signal x(t) is band-limited to  $|f| \le f_B$ , where  $f_B$  is the signal bandwidth, the sampling process is reversible as long as the Nyquist theorem is fulfilled, i.e.,  $f_S \ge 2f_B = f_N$ . Since the analog-to-digital conversion usually takes several clock periods of time, it is often necessary to hold the input signal constant until the conversion is complete. This is accomplished by the sample-and-hold (S/H) circuit. To prevent aliasing, an anti-aliasing filter (AAF) is often placed before the S/H circuit.

The quantization converts the signal with continuous amplitude into a discrete number. For *B*-bit resolution, the continuous amplitude is rounded off to the

closest level of a total of  $2^B$  levels. The quantization level is defined as  $\Delta = \frac{FS}{2^B - 1}$ , where FS is the full-scale input of the quantizer. As long as a quantizer is not overloaded, the quantization error, *i.e.* the difference between input and output, is limited to  $\frac{\Delta}{2}$ . Since quantization is a non-reversible process, one of the important objectives in A/D converter design is to reduce this error.

Under many circumstances, the quantization noise can be treated as white noise and its power and spectral density is

$$P_{q} = \sigma_{q}^{2} = \int_{-\Delta/2}^{\Delta/2} q^{2} P(q) dq = \frac{1}{\Delta} \int_{-\Delta/2}^{\Delta/2} q^{2} dq = \frac{\Delta^{2}}{12} \qquad S_{q} = \frac{\Delta^{2}}{12} \frac{1}{f_{S}}$$

(1)

For a B-bit A/D converter, the signal to quantization noise ratio (SQNR) is defined as

$$SQNR = 10\log\frac{P_x}{P_e} = 10\log(\frac{(2^{B-1})^2\Delta^2}{\frac{\Delta^2}{12}}) = 10\log(\frac{3}{2}2^{2B}) \approx 6.02B + 1.76dB$$

(2)

The SQNR is one of the most important parameters of the A/D converter.

#### 2.2 Oversampling and Noise Shaping

The main idea of oversampling ADCs is that by sampling at a much higher rate than the Nyquist frequency and filtering the out-of-band noise components, the quantization noise left in the signal band can be reduce.

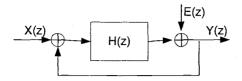

When we analyze a modulator, we will set a linear model shown in Fig. 2.2.

Fig. 2.2 A modulator's linear model

We can write the output signal as the combination of the input signal and the noise signal, with each being filtered by the corresponding transfer function. Below are the results of the output of modulator in the z-transform domain

$$Y(z) = \frac{H(z)}{1 - H(z)}X(z) + \frac{1}{1 - H(z)}E(z) = STF(z) \cdot X(z) + NTF(z) \cdot E(z)$$

(3)

where

$$STF(z) = \frac{Y(z)}{X(z)} = \frac{H(z)}{1 + H(z)} \tag{4}$$

and

$$NTF(z) = \frac{Y(z)}{E(z)} = \frac{1}{1 + H(z)}$$

(5)

where STF is the signal transfer function and NTF is the noise transfer function. The main feature of a  $\Delta\Sigma$  modulator is the different transfer behavior for the quantization error signal and the input signal.

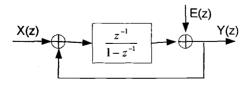

For the first order  $\Delta\Sigma$  modulator, as shown Fig. 2.3, we have

Fig. 2.3 A the one-order  $\Delta\Sigma$  modulator model

$$Y(z) = z^{-1}X(z) + (1 - z^{-1})E(z)$$

(6)

and

$$STF(z) = \frac{Y(z)}{X(z)} = z^{-1}$$

$$NTF(z) = \frac{Y(z)}{E(z)} = 1 - z^{-1}$$

This means that the STF is a one clock period delay and the NTF of the  $\Delta\Sigma$  modulator is a high-pass filter function, in which the high-pass characteristic is called "noise-shaping". In time domain, (6) may become

$$y[n] = x[n-1] + e[n] - e[n-1]$$

(7)

Therefore, the digital output contains a delayed analog input signal x, and a differentiated version of the quantization error e. Hence, the amplification of inband noise and distortion at the output does not happen. Usually, the in-band quantization noise is strongly suppressed by a high gain of loop filter in the signal band. This process is called noise shaping.

If OSR >> 1, the in-band quantization noise power (IBN) can be expressed as

$$IBN = \sigma_{q\_dsm}^2 = \frac{\sigma_q^2}{f_{so}} \iint_{-f_s/2}^{f_s/2} 1 - e^{-j2\pi f/f_{os}} \mid^2 df = \frac{\sigma_q^2 \times \pi^2}{3 \times OSR^3}$$

(8)

and its SQNR is

$$SQNR (dB) = 10 \log(\frac{P_x}{P_q \times \frac{\pi^2}{3OSR^3}})$$

$$\approx 6.02 B + 1.76 + 30 \log(OSR) - 10 \log \frac{\pi^2}{3}, (f \in [-\frac{f_s}{2}, \frac{f_s}{2}])$$

(9)

As can be seen from the above equation, we gains around 9 dB, or 1.5 bit in SQNR for the doubling of the OSR.

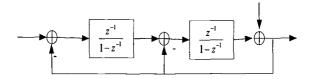

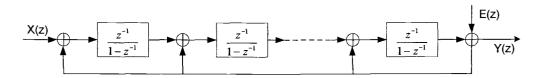

Fig. 2.4 The second order  $\Delta\Sigma$  modulator

Similarly, for the second-order  $\Delta\Sigma$  modulator shown in Fig. 2.4, the STF and NTF are

$$STF = z^{-2}, NTF = (1 - z^{-1})^2$$

For large OSR, its IBN is

$$\sigma_{q\_dsm}^{2} = \frac{\sigma_{q}^{2}}{f_{so}} \int_{f_{s}/2}^{f_{s}/2} 1 - e^{-j2\pi f/f_{os}} |^{4} df \approx \frac{\sigma_{q}^{2} \times \pi^{4}}{5 \times OSR^{5}}$$

(10)

and the SQNR can be expressed as

$$SQNR(dB) \approx 6.02B + 1.76 + 50\log(OSR) - 10\log\frac{\pi^4}{5}$$

(11)

This means we can now get 2.5 bits in SQNR for every doubling of the OSR.

Fig. 2.5  $N^{th}$ -order modulator

Similarly, for N-th order modulators, as shown in Fig. 2.5, the STF and NTF are  $STF = z^{-N}$ ,  $NTF = (1 - z^{-1})^N$ . For large OSR, the in-band integrated noise power is

$$\sigma_{q\_dsm}^2 = \frac{\sigma_q^2}{f_{so}} \int_{-f_s/2}^{f_s/2} 1 - e^{-j2\pi f/f_{os}} \left|^{2N} df \approx \frac{\sigma_q^2 \times \pi^{2N}}{(2N+1) \times OSR^{2N+1}} \right|^{2N} df \approx \frac{\sigma_q^2 \times \pi^{2N}}{(2N+1) \times OSR^{2N+1}}$$

(12)

and the SQNR can be expressed as

$$SQNR \approx 6.02B + 1.76 - 10\log(\frac{\pi^{2N}}{2N+1}) + 10 \times (2N+1)\log(OSR)$$

. (13)

In general, the SQNR will improve with the OSR at a rate of 6N + 3 dB/octave, or equivalently, N+0.5 bit/octave with  $N^{th}$ -order noise shaping.

# 2.3 Performance Increase and Improvement in the $\Delta\Sigma$ Modulators

Increasing rapidly the out-of-band gain of a high-order NTF will result in instability of  $\Delta\Sigma$  modulators. When we follow the same analysis for the first order modulator, we discover that in the second order modulator  $STF(z) = z^{-2}$  and  $NTF(z) = (1-z^{-1})^2$ . In the case of an  $N^{th}$  order modulator, the same analysis give us  $STF = z^{-N}$  and  $NTF = (1-z^{-1})^N$ .  $(1-z^{-1})$  is called the filtering function or noise transfer function. As mentioned, the operating principle of  $\Delta\Sigma$  modulators is based on shaping the quantization noise away from in-band to higher frequencies by means of a loop filter. The NTF of the  $\Delta\Sigma$  modulator is a highpass filter function. It suppresses e at a frequency of around zero, but the NTF also enhances e at higher frequencies around  $f_s/2$ . It is clear that a high order modulator and a lot of oversampling will obtain a great deal of gain. But, when the out-of-band gain of higher order NTF increases rapidly, the  $(1-z^{-1})^N$  modulator is highly prone to instability through overloading the quantizer. It will result in oscillation. In order to enhance the stability, usually the loop gain is adjusted by scaling.

Increasing the OSR of a  $\Delta\Sigma$  modulator will exponentially improve performance. However, for high signal bandwidth and high OSR, the sampling frequency increases the power consumption significantly. For  $\Delta\Sigma$  modulators with signal bandwidth up to tens of kilohertz, a large OSR, from 64 to 256, is usually used with significant noise shaping, achieving a high resolution.

For a multi-bit quantizer, the resolution is increased proportionally to  $(2^B - 1)^2$ , the loop is inherently more stable since the quantizer gain is well-defined, and the no-overload range of the quantizer is increased. Multi-bit modulators may have very high *ENOB* even at low OSR values. By using multi-bit quantization, it will be possible to solve the feedback DAC nonlinearity. Although single-bit oversampling converters can realize highly linear data conversion, they also have some shortcomings [D. A. Johns1997]. For example, single-bit oversampling modulators are prone to instability due to the high degree of nonlinearity in the feedback. Another disadvantage is the existence of idle tones.

## 2.4 The Stability of $\Delta\Sigma$ A/D Converters

The  $\Delta\Sigma$  modulator architecture is *stable* if all the internal state variables of the loop filter are bounded over time and the input to the quantizer is within specified limits, given any initial condition within a subset of state space and any input signal within certain bounds [T. Zourntos2002].

A way to ensure stability is to avoid the overload of the quantizer. This, however, is a very conservative approach, since modulators can be stable even if the quantizer occasionally overloads. Another explanation for instability [K. C.-H. Chao1990] is that as the signal at the input of the quantizer exceeds the quantizer limits, the amount of quantization noise |E(z)| increases. This excess noise is circulated through the loop and can cause an even larger signal to appear at the quantizer input, eventually causing instability. For a fourth-order loop, it has been determined through simulations that  $|H_E(z)| < 2$  for |z| = 1 at high frequencies is a necessary condition for stable operation with zero input. It should be noted that this rule is based on simulations and reduces the probability of instability rather than eliminating it.

Mathematical analysis of modulator instability in the general case is extremely difficult. Most approaches are based on state-space analysis and statistics. Zourntos applies variable-structure methods in the development of stable compensated modulators [T. Zourntos2003]. This method is based on switching methods found in variable structure control theory, provides a guarantee of stability with the "safety net" of a noise-shaped response even while the controller is active. Maeyer proposes a method based on the Nyquist stability criterion [J. D. Maeyer2006]. It uses the vector gain margin as a robust stability margin to design robustly stable modulators. Engelen proposes a design rule which is based on the describing function method, in which the nonlinear quantizer is modeled by a quasi-linear, signal-dependent transfer [J. V. Engelen1999] and [J. A. E. P.V. Engelen1999]. Thus, the commonly used "linear signal gain" model for a one-bit quantizer is extended with a phase shift, which is a phase uncertainty and represents the inaccuracy in time with which the zero-crossings of the quantizer input signal are detected. Simulation is used extensively to ensure stability in the practical design.

# 2.5 Comparison Between DT and CT $\Delta\Sigma$ Modulators

Most DT  $\Delta\Sigma$  modulators are based on switched capacitor circuit techniques for good accuracy and good linearity. In DT design, the transfer functions are independent of the clock frequency [R. Schreier2005]. However, in switched-capacitor circuits, amplifiers with high unity-gain bandwidths of the opamps are required to satisfy the settling accuracy requirements. This limits the clock frequency and thus the input signal bandwidth.

CT  $\Delta\Sigma$  modulators can potentially operate at higher clock frequencies with less power consumption. Since sampling only happens at the quantizer, there is no stringent requirement on opamp settling. Thus, the opamp specification is significantly relaxed [S. Yan2004]. However, CT  $\Delta\Sigma$  modulators are usually more

difficult to design and simulate than their DT counterparts. Circuit non-idealities, such as jitter sensitivity and excess loop delay, also limit the performance of continuous-time  $CT \Delta\Sigma$  modulators.

# 2.6 Continuous-Time Loop Filter Synthesis

We will divide design synthesis into two parts: one is single-stage ADCs; and the other is multi-stage ADCs

# The design synthesis of single-stage ADCs

The first method is Impulse-Invariant Transformation (IIT). As mentioned, a CT  $\Delta\Sigma$  modulator is a combination of continuous and discrete systems. Since the discrete-time  $\Delta\Sigma$  A/D converters have already been extensively studied and a great deal of resources and tools of design have already been developed, a simple way to design a continuous-time  $\Delta\Sigma$  modulator is to transform the design of a discrete-time  $\Delta\Sigma$  modulator into a CT  $\Delta\Sigma$  modulator.

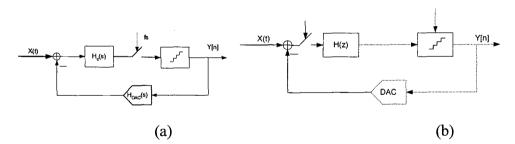

Fig. 2.6 A diagram of (a) a CT  $\Delta\Sigma$  modulator and (b) a DT  $\Delta\Sigma$  modulator

As shown in Fig. 2.6, if after the transformation the sampled impulse response of the loop filter in the CT  $\Delta\Sigma$  modulator matches its DT counterpart, i.e.,  $q(n) = q(t)|_{t=nT_s}$ , the transformation is called the impulse invariant transformation (IIT), which can be defined as

$$Z^{-1}\{H(z)\} = L^{-1}\{H_{DAC}(s)H_{c}(s)\}|_{t=nT_{r}}$$

(14)

where  $Z^{-1}$  represents the inverse z-transform,  $L^{-1}$  represents the inverse Laplace transform, and  $H_{DAC}(s)$  represents the Laplace transform of the DAC waveform. Different DAC waveforms have different effects on the performances of the  $\Delta\Sigma$  ADCs [J. Fang 2005].

The second method is a direct transformation approach [S. Paton2004] and [L. Breems2001]. Instead of matching a CT modulator to a DT modulator, a CT loop filter is designed as a starting point. Then this CT loop filter is optimized until it meets the specification.

The third approach is a transformation in state-space representation [R. Schreier1996] and [B. Zhang1996]. A set of state-space equations are used to design the CT  $\Delta\Sigma$  modulators based on the DT  $\Delta\Sigma$  modulators.

# The design synthesis of multi-stage ADCs

The first method is the impulse invariance transform (IIT). The DT-to-CT conversion requires a conversion of the loop-filter to the CT-domain and adopts the same cancellation logic or filter for the discrete time modulators [M. Ortmanns2001][H. Shamsi2006]. It is necessary to provide every integrator input of the later stages with every (weighted) CT state variable and the feedback DAC output of all previous stages [M. Ortmanns2005].

The second method is a discretization of a CT system by using the state-space approach or the modified z-transform [O. Oliaei2003]. Arbitrary feedback waveform may be used.

The third method is the direct synthesis method [R. Tortosa2005][R. Tortosa2007] [S. Paton2006]. It is based on the direct synthesis of the whole cascaded architecture in the continuous-time domain instead of using a discrete-to-

continuous time transformation, as has been done in previous approaches. In addition to placing the zeroes of the loop filter in an optimum way, the direct methodology leads to more efficient architectures in terms of circuitry complexity, power consumption and robustness with respect to circuit non-idealities[R. Tortosa2005].

The fourth method is the mixed-mode methodology [C. H. Lin1999]. It is necessary to determine the correct s-domain and z-domain recombination of individual modulator outputs. This mixed-mode expression is quite tricky but it is more convenient in analysis of cascaded system.

The fifth method is a lifting method [M. Keller2006]. It will be applied to overcome the disadvantages afflicted with DT-to-CT transformation (e.g. less ideal anti-aliasing filter performance, increased circuit complexity) and to establish a time-efficient DT simulation model for the method which is entirely performed in the CT domain.

# **3 ARCHITECTURES**

In this section we will review the topologies of the CT  $\Delta\Sigma$  modulators, which include single-stage and multi-stage structures.

# 3. 1 Single-Stage CT $\Delta\Sigma$ Modulator Topologies

# Loop filter architectures

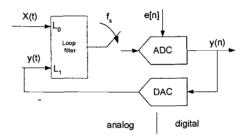

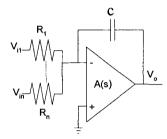

Fig. 3.1 shows the general structure of a single-stage  $\Delta\Sigma$  modulator. It is divided into two parts: the linear part (the loop filter) and the non-linear part (the quantizer).

Fig. 3.1 General structure of a single-quantizer  $\Delta\Sigma$  modulator

In order to analyze, this non-linear model may be simplified and transformed into a modified linear model, as shown in Fig. 3.2.

Fig. 3.2 Modified single-stage  $\Delta\Sigma$  modulator

The NTF and STF are derived [A. Buhmann2006]:

$$NTF[z] = \frac{1}{1 - Z\{L^{-1} \mid H_{DAC}(s) \cdot L_1(s)|_{nT.}\}} \approx \frac{1}{1 - L_1[z]}$$

(1)

$$STF = \frac{L_0(s)}{1 - Z\{L^{-1} \mid H_{DAC}(s) \cdot L_1(s) \mid_{nT}\}} \approx \frac{L_0(s)}{1 - L_1(z)}$$

(2)

where Z stands for Z-transform,  $L^{-1}$  represents the inverse Laplace transform. Note that no argument is given for the STF since it is a mixture between a CT and DT equation.

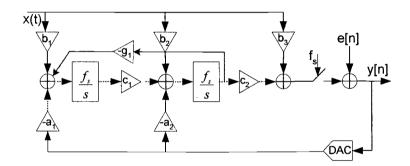

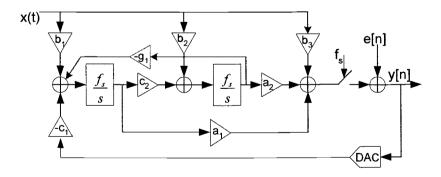

The single-loop high-order  $\Delta\Sigma$  modulators can be divided into two structures: one is the loop filter with distributed feedback and input coupling---the CIFB and CRFB, and the other is a loop filter with distributed feedforward and input coupling---the CIFF and CRFF structures, as shown in Fig. 3.3 and Fig. 3.4.

Fig. 3.3 CIFB ( $g_1 = 0$ ) and CRFB ( $g_1 \neq 0$ )

Fig. 3.4 CIFF( $g_1 = 0$ ) and CRFF( $g_1 \neq 0$ )

From equation (2), we can derive the general expression of the STF according to [N. Beilleau2004] for the different CT  $\Delta\Sigma$  modulators (CIFF, CIFB, CRFF and

CRFB). At system level, the modulator design is usually focused on maximizing the signal to noise ratio (SNR). Considering only the SNR criterion, feedforward and feedback topologies are equivalent because they can be designed to provide the same NTF. However, if we consider the STF, these topologies have different performances. First, the feedforward architectures have a filtering characteristic as a 1<sup>st</sup> order filter due to the path from the 1<sup>st</sup> integrator output to the adder before the sampling. The feedback architectures have an  $n^{th}$  order filter characteristics because the input signal passes through all the integrators. For the same NTF, the curve of CIFB amplitude falls steeper than CIFF. Second, another problem of feedforward architecture is out of band peaks. This is due to the zeros which do not exactly cancel the poles. This becomes a major drawback when the input signal is amplified by these peaks, resulting in integrator overload. Some methods may reduce the effect of the peaking, e.g., using surface acoustic wave (SAW) filter [R. Schreier2006] or adding a high-pass feedback path to a conventional  $\Delta\Sigma$ ADC [K. Philips2004].

As the STF is considered, even though the feedback architectures are better than the feedforward architectures, the feedforward architectures are often preferred to the feedback architectures due to lower distortion, easier circuit implementation and less power consumption. [N. Beilleau2004]

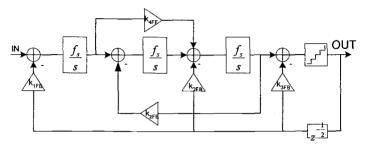

## Variations of loop filter

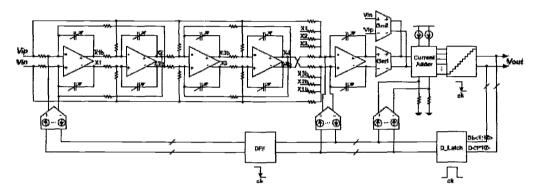

In [G. Mitteregger2006], in order to save power and to maintain a good anti-alias filter characteristic in the STF, a combination of a feedforward and a feedback stabilized loop filter is implemented as shown in Fig. 3.5. The feedback path to the second integrator input is replaced by the feedforward path  $k_{4FF}$  in order to eliminate one DAC. Another advantage of this loop filter topology is that the bandwidth of the first integrator can be large, as there is no feedback to the following stage and the output signal swing of this integrator can be scaled only

with its bandwidth. A high bandwidth of the first integrator suppresses the thermal noise of the following integrators.

Fig. 3.5 Mixed CRFF and CRFB architecture

Chao proposed another kind hybrid configuration as shown in Fig. 3.6 [K. C. –H. Chao1990]. The most important feature of this topology is the feedforward structure with coefficients  $(a_1, a_2, a_3, a_4)$  and a feedback structure with coefficients  $(b_1, b_2, b_3, b_4)$ . The large number of loop coefficients not only allows one to stabilize the modulator, but also to optimize the NTF.

Fig. 3.6 The  $a_i$  coefficients implement the poles of the quantization noise response, and the  $b_i$  coefficients produce the zeros.

Schreier proposed a modified feedforward architecture to take advantage of the characteristic low distortion and high dynamic range of a feedforward topology as shown in Fig. 3.7 [R. Schreier2006]. The first, second, and third resonators in the loop filter are signal resonators. The final resonator is the image resonator. Placing the image resonator at the end frees the preceding resonators from the

need to process image signals and thereby prevents mismatch in those resonators from reflecting image noise into the passband.

Fig. 3.7 Fourth order (SWA) continuous-time  $\Delta\Sigma$  modulator

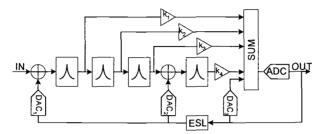

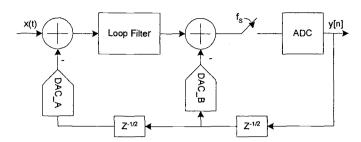

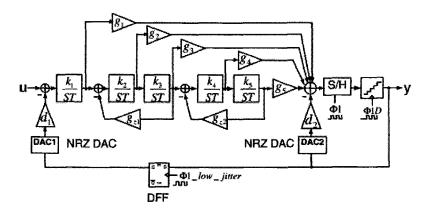

Yan proposed a 3-order CRFF architecture, as shown in Fig. 3.8 [S. Yan2004]. One clock delay is purposely introduced in front of DAC\_A in the main noise-shaping loop to accommodate the nonzero time delay of the internal DAC. To keep the output of the loop filter unchanged at the sampling instants, a feedback path is added from the output to the input of the internal ADC, formed by a half clock cycle delay and DAC\_B. This additional feedback is only one feature in this design architecture.

Fig. 3. 8 Conventional continuous-time  $\Delta\Sigma$  modulator with an additional feedback path

Cosand proposed a CRFF structure with an extra feedback path [A. E. Cosand2004]. An additional feedback path is added back to the input of the quantizer. This additional feedback path improves the overall noise transfer function and stability by allowing the high-frequency quantization noise to be fed

back around a shorter feedback path. Adding this extra feedback path allows one to improve the wide-band SNR by 10 dB and achieves a higher margin of stability.

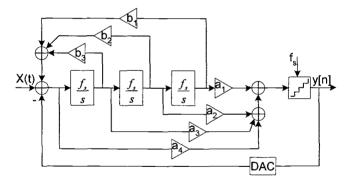

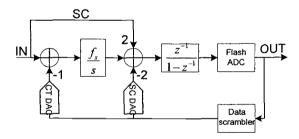

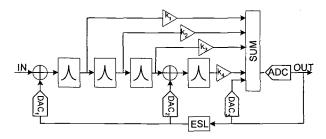

Paton proposed a conventional 4-order CRFF continuous-time  $\Delta\Sigma$  modulator topology [S. Paton2004], as shown in Fig. 3.9. A multiple feedforward topology has the advantage of requiring only one DAC, compared to its multiple feedback counterpart that needs as many DACs as the modulator order. Due to the low OSR and the circuit-imposed excess loop delay of this particular design, a second DAC is needed to partially compensate the excess loop delay. The gain of this DAC (coefficient *fbe*) is programmable such that stability can be improved for a wide range of delays. This DAC is **placed** around the quantizer to keep its linearity requirements low.

Fig. 3. 9 A 4-order CRFF CT  $\Delta\Sigma$  modulator architecture

As mentioned before, most of the implementation of  $CT \Delta\Sigma$  modulators use the modified feedforward architecture because of the low distortion and high dynamic range of the feedforward topology. The disadvantage of a feedforward topology is the out-of-band peaking of STF

## Hybrid CT $\Delta\Sigma$ modulator

A loop filter with combined CT and DT circuits is an alternative approach to realize a high-performance  $\Delta\Sigma$  modulator. The primary reason for using continuous-time stage instead of discrete-time stage is noise. The dynamic range of the converter is determined by the feedback and the first integrator noise

performance [B.D. Signore1990]. This combined loop filter structure offers several important advantages. First, since there is no sampling of the input voltage, signal-dependent clock feedthrough and noise resampling in the first integrator do not exist. Secondly, any signal-dependent glitches coupled into the first integrator are averaged out over the clock period. This averaging characteristic of the CT integrator greatly reduces the harmonic distortion due to coupling. Thirdly, the input impedance of the first integrator is purely resistive, hence, it does not emit EMI back to the input pins. Finally, the intrinsic anti-alias filtering property of the CT first stage is preserved.

Nguyen proposed a  $\Delta\Sigma$  modulator with hybrid structure [K. Nguyen2005] as shown in Fig. 3.10. A data-directed scrambler is used to spectrally shape the error caused by the feedback DAC's unit element mismatch into the out-of-band frequency region. The feedforward SC path from the analog input to the second integrator reduces the distortion and opamp output. The disadvantage of this feedforward path is that the input impedance is no longer resistive.

Fig. 3. 10 A  $\Delta\Sigma$  modulator with the loop filter implemented by Hybrid DT and CT circuits

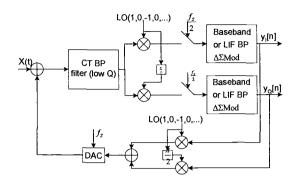

The hybrid structure is used [H. Tao1999] as well. As shown in Fig. 3.11, a four-order direct-conversion bandpass  $\Delta\Sigma$  modulator is designed. This  $\Delta\Sigma$  modulator uses a low Q CT bandpass filter in the first stage, followed by the analog I/Q modulator to translate the narrow-band signal from its carrier frequency to baseband.

Fig. 3.11 Direct-conversion bandpass  $\Delta\Sigma$  modulator with mixed CT and DT components

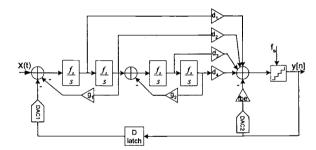

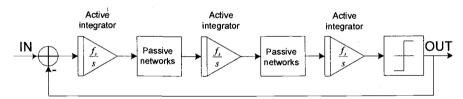

Song presented a 5<sup>th</sup>-order continuous-time  $\Delta\Sigma$  modulator with a hybrid active-passive loop filter consisting of only three amplifiers [T. Song2006-1] and [T. Song2006-2], as shown in Fig. 3.12. Passive networks do not consume power and do not introduce distortion. The active integrators provide gain and minimize internal noise contributions. It is a low power, high bandwidth continuous-time  $\Delta\Sigma$  modulator.

Fig. 3. 12 A  $5^{th}$ -order CT  $\Delta\Sigma$  modulator with a hybrid active-passive loop filter

## Complex or Quadrature Bandpass $CT \Delta \Sigma$ modulator

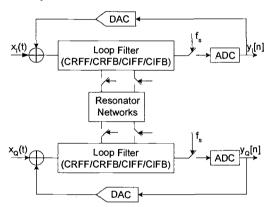

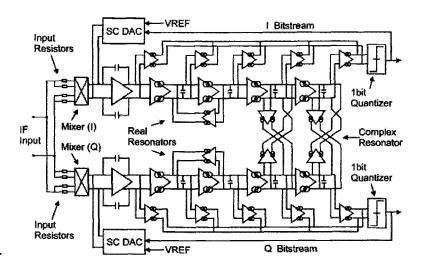

The complex or quadrature bandpass CT  $\Delta\Sigma$  modulator, as shown in Fig. 3.13, is reviewed in this section. Commonly, in the baseband receive path, low-IF (LIF), or zero-IF(ZIF) in phase and quadrature signals (I/Q) or real and complex signal from a transceiver quadrature mixer are converted to digital, bandpass or low-pass filtered and down-sampled. The architectures of these bandpass CT  $\Delta\Sigma$  modulators have usually combined two separate and independent basic topologies with pairs of resonators. It usually consists of two  $\Delta\Sigma$  modulators. For example, Baggini and

Silva proposed a bandpass CT CRFF  $\Delta\Sigma$  modulators built with real and complex resonators [B. Baggini2006] and [P. G. R. Silva2007]. Arias proposed a  $2^{nd}$ -order CT CRFB  $\Delta\Sigma$  modulator with real and complex resonators [J. Arias2006]. While two separate and independent I and Q ADCs are used in low-pass mode for heterodyne and ZIF receivers, complex (I+jQ) ADC is used in bandpass mode for LIF receivers. In low-pass mode, the cross-coupling networks are switched off. In this mode, we obtain two independent and totally equal I and Q  $m^{th}$ -order converters. The ADC operates in the complex bandpass mode, when the cross-coupling networks are activated or switched on. Therefore, we obtain a dual-mode combination I and Q  $m^{th}$ -order converters.

Fig. 3.13 a complex/quadrature basspass CT  $\Delta\Sigma$  modulators

The bandpass and quadrature modulators preserve many of the advantages of lowpass  $\Delta\Sigma$  modulation and are particularly useful in modem receiver systems where high-frequency narrowband signals are converted to digital form without down-converting to baseband. At the system level, the two primary advantages of bandpass conversion are the elimination of one or more analog downconversion operations, and the preservation of the spectral separation between the signal and various low-frequency noise and distortion components. At the circuit level, bandpass conversion is more efficient than converting the entire frequency band

between 0 and  $f_0 + f_B/2$ , since no power is wasted on the accurate conversion of unwanted signals between 0 and  $f_0 - f_B/2$ .

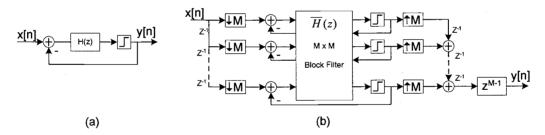

# Time-Interleaved (TI) ADC

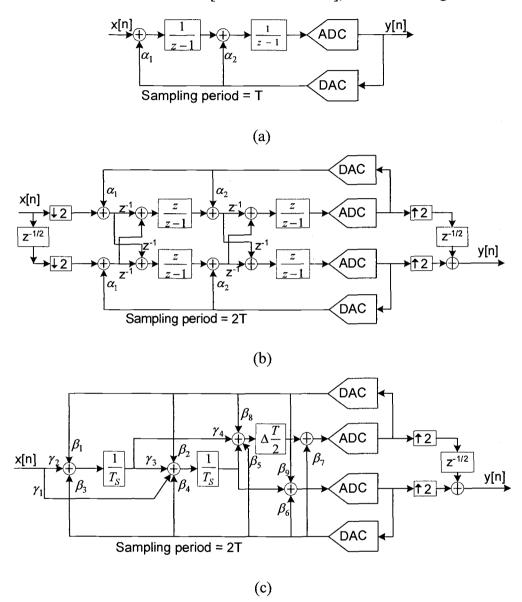

Since a  $\Delta\Sigma$  modulator oversamples the data, the signal bandwidth is limited by the maximum sampling frequency, the OSR, the opamp bandwidth and the sampling switches[K. S. Lee2007]. One method to add another degree of freedom is to use parallel  $\Delta\Sigma$  structures. The simplest method of making parallel converters is through the use of time-interleaving. Time-interleaved  $\Delta\Sigma$  modulator topologies based on block filtering theory. Block digital filtering can be used to DT TI  $\Delta\Sigma$  modulator [R. Khoini-Poorfard1997] as shown in Fig 3.14. Assuming the same initial conditions, Fig 3. 14 (a) is equivalent to Fig 3. 14 (b) from an input-output point of view. A block digital filter is a system in which parallelism is used to reduce the speed requirement on each processing element.

Fig 3. 14 DT TI  $\Delta\Sigma$  modulator

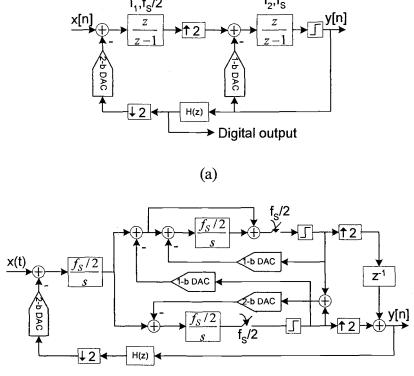

However,  $CT \Delta\Sigma$  modulators can also be time-interleaved [T.C. Caldwell2005-1] and [T. C. Caldwell2005-2]. A CT  $TI \Delta\Sigma$  modulator combines the advantages of the time-interleaving and continuous-time filter. Employing the CT loop filter instead of the DT loop filter is one way to increase the input signal bandwidth. And employing the parallelism of time-interleaving reduces the speed requirement on each processing element.

Caldwell presents the combination of these two techniques by introducing a method of CT TI  $\Delta\Sigma$  modulators[T.C.Caldwell2006], as shown in Fig. 3.15,

Fig. 3. 15 (a) A  $2^{nd}$ -order DT  $\Delta\Sigma$  modulator (b) DT to DT TI modulator transform (c)CT TI modulator with additional DAC feedback path

where the ADCs and DACs are operating at half of the original frequency. Thus, clock jitter has about half the impact on the  $\Delta\Sigma$  modulator. Furthermore, the higher bandwidth requirements on an RZ DAC operating at high speeds

(assuming the choice of an RZ DAC pulse to reduce the excess loop delay) is reduced by a factor of two by time interleaving. The characteristics of CT TI  $\Delta\Sigma$  modulator are that it may obtain more bandwidth at the cost of hardware complexity.

In the above approach, parallelism is applied to every integrator, including the first one. However, the performances of the overall modulator strongly depend on the first integrator. In [F. Colordro2006], time-interleaving is not applied to the first integrator, which leads to a reduction in the area and power consumption when compared to other TI and parallel implementations as shown in Fig. 3. 16. This is a promising technique for the design of high speed, low-power modulators. The anti-aliasing filter H(z) is required before the quantizer output is down-sampled and fed back to the modulator input.

Fig. 3.16 (a)  $2^{nd}$ -order multirate  $\Delta\Sigma$  modulator (b) DT transform to parallel-CT  $\Delta\Sigma$  modulator

This is a parallel CT  $\Delta\Sigma$  modulator. It can be concluded that the SNDR of a CT  $\Delta\Sigma$  modulator improves by using parallelism. This architecture still suffers from the quantizer domino effect so that additional work is still required to get a feasible circuit implementation for this modulator.

To conclude the considerations on single-stage modulators, it should be noted that there are numerous architectures. The implementation of the loop filter is expressed in the building of the CT  $\Delta\Sigma$  modulator. However, the effort spent on architectural optimization is always based on the same reasons: to obtain a stable modulator with maximum quantization noise and interferer suppression, while keeping the signal swing requirements as low as possible [A. Buhmann2006].

# 3. 2 Multi-Stage CT $\Delta\Sigma$ Modulator Topologies

In a single-loop  $\Delta\Sigma$  modulator, when the oversampling ratio (OSR) is low, it is difficult to obtain high SQNR by increasing the order of the loop filter, since it tends to reduce the stability of the modulator.

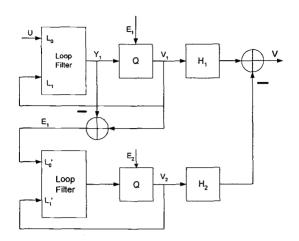

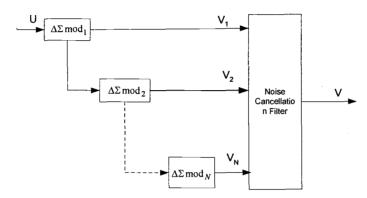

To solve this problem, the cascade, also called multi-stage or MASH (for Multi-stAge noise-Shaping) modulator structures are used. The main idea is to feed the quantization error of the previous  $\Delta\Sigma$  modulator stage into another  $\Delta\Sigma$  modulator stage and combine the outputs of both stages in digital filter. By doing this, higher-order noise shaping can be obtained. Meanwhile, because a cascaded modulator is constructed from low-order  $\Delta\Sigma$  modulators, the stability of the low-order  $\Delta\Sigma$  modulators is maintained.

#### Multi-Stage Loop Filter Structure

Fig. 3. 17 A two-stage MASH structure

As is shown in Fig.3.17, the output signal of the first stage and the second stage are given by

$$V_1(z) = STF_1(z) \cdot U(z) + NTF_1(z) \cdot E_1(z)$$

(3)

$$V_2(z) = STF_2(z) \cdot E_1(z) + NTF_2(z) \cdot E_2(z)$$

(4)

where  $STF_1(z)$ ,  $STF_2(z)$ ,  $NTF_1(z)$  and  $NTF_2(z)$  are the signal and noise transfer functions of the first and second stages, respectively. The digital filter stages  $H_1(z)$  and  $H_2(z)$  at the outputs of the two modulator loops are designed such that in the overall output V(z) of the quantization noise of the first stage  $E_1(z)$  has been completely eliminated. Thus  $H_1(z)$  and  $H_2(z)$  has to satisfy the condition as follows

$$H_1(z)NTF_1(z) - H_2(z)STF_2(z) = 0$$

(5)

The simplest (and usually most practical) choices for  $H_1(z)$  and  $H_2(z)$  are  $H_1(z) = STF_2(z)$  and  $H_2(z) = NTF_1(z)$ . The overall output is then

$$V(z) = H_1(z)V_1(z) - H_2(z)V_2(z)$$

$$= STF_1(z) \cdot STF_2(z) \cdot U(z) - NTF_1(z) \cdot NTF_2(z) \cdot E_2(z)$$

(6)

Only the filtered quantization error of the second stage remains. Similarly, we can get the general expression for the output of *n*-stage MASH structure as shown in Fig 3. 18.

Fig 3.18 A N-stages MASH structure

$$V(z) = STF_1(z) \cdot STF_2(z) \cdot ...STF_n(z) \cdot U(z) - NTF_1(z) \cdot NTF_2(z) \cdot ... \cdot NTF_n(z) \cdot E_n(z)$$

(7)

Only the filtered quantization error of the last stage remains. For instance, for 2-2 cascaded modulator,  $STF_1(z) = STF_2(z) = z^{-2}$ ,  $NTF_1(z) = (1-z^{-1})^2$  and  $NTF_2(z) = (1-z^{-1})^2$ , the overall output will be

$$V(z) = z^{-4}U(z) - (1 - z^{-1})^4 E_2(z)$$

Thus, in terms of quantization noise shaping performance, the 2-2 cascaded modulator is equivalent to a 4th-order single-stage modulator. At the same time, the stability of the 2-2 cascaded modulator is the same as that of the second-order single stage modulator. It can be shown that an m-stage cascaded  $\Delta\Sigma$  modulator with first or second order modulators has better performance than an  $m^{th}$ -order single-stage  $\Delta\Sigma$  modulator when tones are concerned [W. Chou1989].

Compared with single-stage CT  $\Delta\Sigma$  modulators, the characteristics of the cascaded continuous-time  $\Delta\Sigma$  modulators achieve the high resolution with high

OSR and ultra low voltage, lower power consumption in [C. H. Lin1999], reduce stability problems, increase the effectiveness of each integrator in quantization noise suppression, have larger modularity, offer better dynamic range at a relative low OSR, have a high-order noise-shaping characteristics, and increase the effective bandwidth. However, there is a noise leakage problem in multi-stage structure which originates from the mismatch between analog and digital transfer functions. This leakage degrades the performance, and thus, correction algorithms are necessary.

## **Multi-Stage Architectures**

The multi-stage approach relies on the cancellation of the quantization error by cascading low order single-stage modulators, i.e. first and second order, rather than on filtering as performed by single-stage modulators. We summarize papers published in Table 3.1.

Table 3.1. Cascade topologies in recent papers

| Year | Name         | Cascade Level | 1st-stage AP           | 2nd or 3rd stage AP  |

|------|--------------|---------------|------------------------|----------------------|

| 2007 | L. Breems    | cascade 2-2   | (3), (4)               | 121                  |

| 2007 | R. Tortosa   | cascade 3-2   | (3)                    | 121                  |

| 2007 | M. Keller    | cascade 2-1   | (1), (2),(4)           | 121                  |

| 2007 | M. Renedo    | cascade 2-2   | (1), (3)               | 121, 122, 123        |

| 2007 | S. Kulchycki | cascade 2-1   | Before & after ADC     | 121                  |

| 2006 | H. Shamsi    | cascade 2-1-1 | (3),(4)                | 121/131              |

| 2006 | M. Keller    | cascade 2-1-1 | (2), (3), (4)          | I21 & I31            |

| 2006 | S. Paton     | cascade 2-2   | (1), (2), (3), (4)     | 121                  |

| 2006 | R. Tortosa1  | cascade 2-2-1 | (2)                    | 121                  |

|      |              | cascade 2-1-1 |                        |                      |

| 2006 | R. Tortosa2  | & 2-1-1-1     | (3)/(2)                | 121/131, 121/131/141 |

| 2005 | R. Tortosa   | cascade 2-1-1 | (3)                    | 121/131              |

| 2005 | M.Ortmanns   | cascade 2-1-1 | (2), (3), (4)          | 121/131              |

| 2004 | M. Keller    | cascade 2-1-1 | (3), (4)/(2), (3), (4) | 121/131              |

| 2004 | L. Breems   | cascade 2-2   | (3), (4)               | I21          |

|------|-------------|---------------|------------------------|--------------|

| 2003 | P. Benabes  | cascade       | (3), (4)               | I21          |

|      |             | cascade 2-1 & |                        |              |

| 2003 | O. Oliaei   | 2-2           | (2), (3), (4)/(3), (4) | 121/121, 122 |

| 2001 | M. Ortmanns | cascade 2-1   | (2), (3), ADC          | 121          |

| 1999 | C. Lin      | cascade 2-1   | (3)                    | I21          |

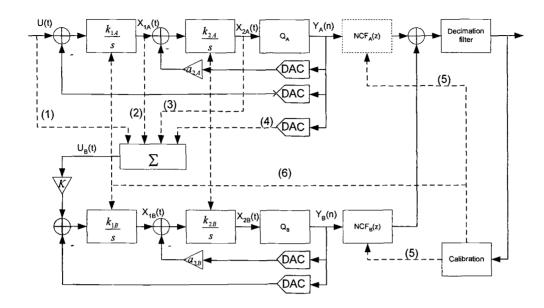

Note that the numbers of the first stage access points (AP) are the same Fig 3. 19 and the letter I and the numbers of the second- or third stage access points are the input of the first, second or third integrator in Fig 3.19. It may be seen that the order of the first stage is not more than third order, since it is not possible to achieve an ideal third order or higher order noise shaping. In order to clearly explain multi-stage architectures, we use two-stage MASH in our examples. We conclude that two-stage architectures most papers represent may be a topology to explain as shown in Fig 3. 19. Note that when we activate some dashed lines, it represents that the line is connected. Otherwise, the line is disconnected. The purpose of block  $\Sigma$  is to estimate the quantization noise of the first stage and remove or attenuate any input signal component inside the band of interest. The gain block K has been included to amplify the first quantization noise up to full scale of the second stage. The simplest choice for block  $\Sigma$  is to implement a linear combination of the incoming signals: the input signal U(t), the integrator outputs  $X_{1A}(t)$  and  $X_{2A}(t)$ , and the output of the first modulator  $Y_{DAC}(t)$  followed by a DAC. Then

$$U_{B}(t) = k_{u} \cdot U(t) + k_{1} \cdot X_{1A}(t) + k_{2} \cdot X_{2A}(t) + k_{v} \cdot Y_{DAC}(t)$$

(8)

Fig 3.19 General architecture for two-stages CT modulator

where  $k_U$ ,  $k_1$ ,  $k_2$ , and  $k_Y$  are coefficients. In order to conveniently analyze, these coefficient values may be just 0 or 1 or -1. For recent papers, we will divide them into A, B, C and D classes.

A class includes lines (2), (3) and (4) activated ( $k_U$ =0,  $k_1$ =  $k_2$ = 1 and  $k_Y$ =-1).  $U_B(t)$  is determined by  $X_{1A}(t)$ ,  $X_{2A}(t)$  and  $Y_{DAC}(t)$ . Such circuits are in [M. Keller2007], [M. Keller2004], [M. Keller2006], [M. Ortmanns2005A], [M. Ortmanns2005A], [M. Ortmanns2005B] and [O. Oliaei2003]. By employing auxiliary feedforward paths, the cascaded CT  $\Delta\Sigma$  modulator is derived. But this class architecture is complicated, involving a lot of additional feed-forward paths. These auxiliary feed-forward paths increase the input referred thermal noise and put hard conditions for the opamps of the integrators because they should drive a lot of feedforward paths, and the feedback factor of the opamp's will be small.

B class is line (3) and line (4) activated ( $k_U = k_1 = 0$ ,  $k_2 = 1$  and  $k_Y = -1$ ).  $U_B(t)$  is determined by  $X_{2A}(t)$  and  $Y_{DAC}(t)$ . References include [L. J. Breems2004], [L. J. Breems2007], [R. Rutten2006], [M. Keller2004], [P. Benabes2003], [H. Shamsi2006], [O. Oliaei2003] and [M. S. Renedo2007]. By using this structure, the loop gain of each stage is isolated from the loop gain of the other stage [H. Shamsi2006]. It has harder requirement for mismatch between the analog and digital filter coefficients due to process variations, and the amount of SQNR improvement by means of noise cancellation is limited by the accuracy of the coefficients. To compensate for mismatch between the digital NCF and the analog filter, calibration is needed. In [L. J. Breems2004], calibration compensates NCF while (5) is activated. In [L. J. Breems2007], calibration compensates integrators while (6) is activated. The quantization error signal of the first-stage, which is the difference between the sampler input or output signal and the output of the DAC, is fed to the input of the second-stage. The sampler input signal is a continuoustime signal and as a result, the quantizer error signal can become larger than half a least significant bit (LSB). Therefore, care should be taken that the error signal does not overload the second stage. Based on B class, Renedo uses the interstage feedback technique, which is that the difference between the input of ADC and the output DAC in the second-stage is fed back to the input of ADC in the first stage [M. S. Renedo2007]. The loop filter resonator is not needed to introduce an NTF zero. Interstage feedback is used to improve the loop filter stability and make possible the application of a very simple mismatch digital correction method.

C class is line (3) activated ( $k_U = k_1 = 0$ ,  $k_2 = 1$  and  $k_Y = 0$ ).  $U_B(t)$  is determined by  $X_{2A}(t)$ . This is done in [R. Tortosa2007], [R. Tortosa2006], [R. Tortosa2006], [R. Tortosa2006], The number of integrating paths can be reduced if the whole cascaded  $\Delta\Sigma$  modulator is directly synthesized in the CT domain. Then no calibration is used to compensate for

mismatch and element tolerances, thus optimizing their performance in terms of circuit complexity, power consumption and sensitivity with respect to mismatch.

D class is line (1) and line (3) activated ( $k_U = 1$ ,  $k_1 = 0$ ,  $k_2 = 1$  and  $k_Y = 0$ ).  $U_B(t)$  is determined by U(t) and  $X_{2A}(t)$ . An example is the cascade 2-2 CT  $\Delta\Sigma$  modulator [M. S. Renedo2007]. The Fig. 3.19 didn't show the lines between U(t) and  $X_{1B}(t)$  and  $X_{2B}(t)$ . The first quantization error is obtained from the quantizer input of the first stage. To remove the input signal in the second stage, feedforward coefficients going from the input signal to the second stage are applied. Through a proper selection for the values of these coefficients, the input signal at the integrator outputs is high-pass shaped. This allows the interstage gain K to be incremented, hence improving the SNR without overloading the second stage. Thus, the first quantization error is scaled by K and shaped by the STF of the second stage, which limits the practical value of K. In addition, the second-stage overload can be controlled without changing the NCFs. Hence, the tuning of the cascaded CT  $\Delta\Sigma$  modulator is simplified. The anti-aliasing functionality is also preserved.

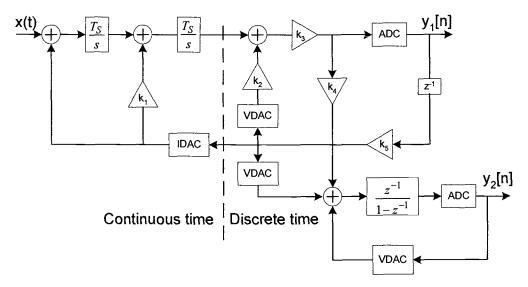

Finally, Kulchychki presents a modulator architecture that combines the benefits of CT and DT circuits [S. D. Kulchycki2007], as shown in Fig 3. 20. The second-order first stage of a two-stage cascade is implemented in CT, while the first-order second stage is a DT circuit. Calibration of the integrator time constants in the CT stage mitigates the performance impact of mismatch between the analog and digital coefficients in the cascade.

Fig 3. 20 CT/DT modulator architecture

In short, multi-stage CT  $\Delta\Sigma$  modulator architectures have stability and high resolution. However, since there is mismatch problem and complexity in multi-stage, so far it still is not popular in application.

# 4 NON-IDEALITIES AND CORRECTION TECHNIQUES

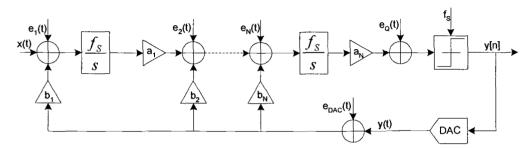

As shown in Fig.4.1 [A. Buhmann2006], the performance of the  $\Delta\Sigma$  ADC is influenced by the various non-idealities existing in the loop filter, the quantizer and the DAC. In this section, these non-idealities are discussed and the correction techniques are reviewed.

Fig. 4.1 Errors distribution in  $\Delta\Sigma$  modulator

Every error will contribute its non-ideality to  $\Delta\Sigma$  modulator. No matter which kind of architecture is used, single-stage or multi-stage, they are most sensitive to any input referred noise and distortion of the first integrator  $e_1(t)$  and the error at the feedback DAC  $e_{DAC}(t)$ . Compared to the errors entering the first integrator, errors entering the system at other points are less critical. They often are suppressed by the preceding or following integrator.

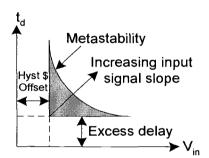

## 4.1 Non-idealities in the DAC (I)---Excess loop delay

Excess loop delay is a timing non-ideality. Excess loop delay in a CT  $\Delta\Sigma$  modulator refers to a delay between the sampling clock edge and the change in output bit as seen at the feedback point in the modulator [J. A. Cherry1999]. The loop delay occurs when the comparator response in the quantizer is a longer decision time and the propagation time in the latch and the DAC are too long. The signal-dependent delay in the quantizer can be absorbed or buffered by using an additional latching stage after the quantizer. However, this latching stage does not

absorb the delay in the feedback DAC itself and when the sampling frequency is very high, the delay introduced by the DAC will contribute more to the total loop delay and degrades the performance of the CT  $\Delta\Sigma$  modulator.

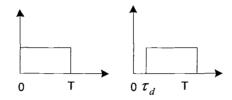

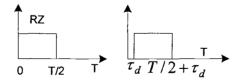

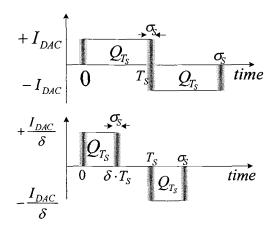

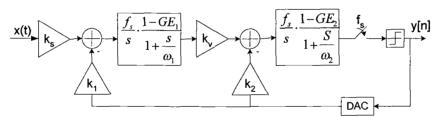

Excess loop delay can be modeled by  $t_d = \tau_d \cdot T$ , as depicted in Fig. 4.2 for an NRZ DAC pulse. The value of  $\tau_d$  is dependent on the switching speed  $f_t$  of the transistors, the quantizer clock  $f_S$ , the number of transistors  $n_t$  in the feedback path, as well as the loading on each transistor. Their relationship may be represented by  $\tau_d \approx \frac{n_t \cdot f_S}{f_t}$  [J. A. Cherry1999]

Fig. 4.2 Excess loop delay for an NRZ DAC

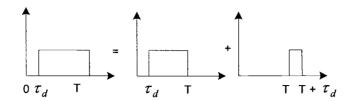

Excess loop delay can have two different effects in CT  $\Delta\Sigma$  modulators: firstly, a delay that shifts the DAC pulse but retains the entire pulse in the actual sampling instant, like an RZ DAC pulse as shown in Fig. 4.3; Secondly, a delay that shifts the DAC pulse into the next sampling instant, like an NRZ DAC as shown in Fig. 4.4.

Fig 4.3 Excess loop for a RZ DAC

Fig. 4.4 Two-pulse represents excess loop delay for an NRZ DAC

For simplicity, we assume a perfectly rectangular DAC pulse of magnitude 1 that lasts from  $\alpha$  to  $\beta$ . We consider the  $\Delta\Sigma$  modulator with NRZ DAC pulse. For this type of DAC,  $(\alpha,\beta)=(0,T)$ . Any excess loop delay  $\tau_d>0$  causes  $\beta>T$ , which means the end of the pulse extends beyond t=T. If we use a DAC pulse with  $\beta< T$ , then the pulses would extend past t=T only if the condition  $\tau_d>T-\beta$  held. If we used an RZ DAC instead of an NRZ DAC, for a given  $\tau_d\leq 0.5T$ , the order of the equivalent DT loop filter may be equal to the order of the CT loop filter by tuning the parameters. So, an RZ code is to reduce pulse distortion and avoid the excess loop delay [J. A. Cherry1999A]. He concludes that in general, in any CT modulator with enough excess delay to push the falling edge of a DAC pulse past t=T, the order of the equivalent DT loop filter is one higher than the order of the CT loop filter [J. A. Cherry1999A].

Excess loop delay will make a CT  $\Delta\Sigma$  modulator unstable, and decreases the dynamic range. The filter coefficients depend on the loop delay of the DAC feedback pulses [R. Schoof2007]. As loop delay increases, a full sample of feedback delay causes SNR loss [J. A. Cherry1999A]. Usually in CT  $\Delta\Sigma$  modulators, for an excess loop delay of 20% [R. Schoofs2007] to 22% [K. P. J. Thormas2005] of the clock period, the modulator can be stable. The effect of loop delay will tend to become more severe as clock speeds are increased. If the loop delay causes the DAC pulse to extend beyond T, then the modulator order increases by one, which may eventually make a CT  $\Delta\Sigma$  modulator unstable [J. A.

Cherry1998]. As excess loop delay increases, the in-band noise (IBN) increases and the maximum stable amplitude (MSA) decreases. The result will decrease the dynamic range [J. A. Cherry1999A].

When we design a CT  $\Delta\Sigma$  modulator, we should reduce the influence of the excess loop delay to the system. Various methods have been proposed to compensate for excess loop delay, including different DAC waveforms, feedback coefficient tuning and the inclusion of zero-order feedbacks. Choosing the right DAC pulse shape in combination with tuning of the feedback parameters (either in the design phase or automatically on-line) can greatly reduce the performance degradation brought by the excess loop delay. Note that by reducing the loop gain to compensate for the loop delay, it will deteriorate the NTF and cause the modulator to have less dynamic range and more IBN [J. A. Cherry1999]

The following methods provide ways to reduce the effect of excess loop delay.

- (1) Add one or half a period delay in the feedback loop [H. Aboushady2004]. This delay should be sufficiently large to cover comparator and digital circuitry delay. It will be shown that in  $\Delta\Sigma$  modulators it is possible to compensate for the loop-delay without additional coefficients.

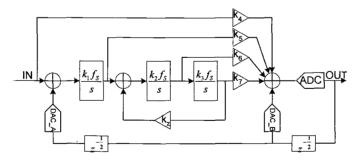

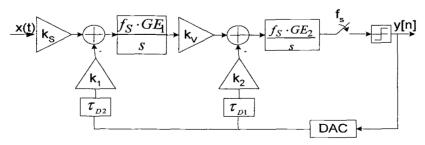

- (2) One clock delay is purposely introduced in front of DAC\_A in the main noise-shaping loop to accommodate the nonzero time delay of the internal ADC as shown in Fig 4. 5 [S. Yan2004]. To keep the output of the new loop filter unchanged at the sampling instants, a feedback path is added from the output to the input of the internal ADC, formed by a half clock cycle delay and DAC\_B. Thanks to the architectural improvements, the total time delay of the internal ADC and the feedback DAC is relaxed to nearly one clock period. Thus, the excess loop delay problem of conventional CT ΔΣ modulators is eliminated.

Fig. 4. 5 A loop filter architecture for eliminating excess loop delay

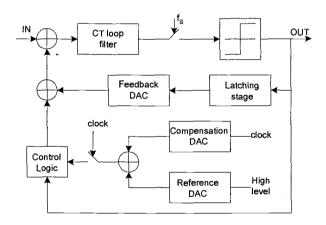

(3) Tiew [K. T. Tiew2005] provides a technique that compensates for the intersymbol interference and excess loop delay in the 1-bit feedback DAC. The three DACs matching technique is based on acquiring the error signal by using two additional DACs which are matched to the feedback DAC, as shown in Fig 4. 6.

Fig. 4.6 Continuous-time  $\Delta\Sigma$  modulator with three DACs nonidealities compensation

This technique does not require a prior knowledge of the NRZ DAC output pulse in response to the input transition. It could potentially compensate for most of the NRZ DAC non-idealities at a high sampling frequency. In the presence of DAC nonidealities, the peak SNR could be enhanced by using the three DACs nonidealities compensation scheme. It is shown that the technique works well within reasonable mismatch levels among the DACs.

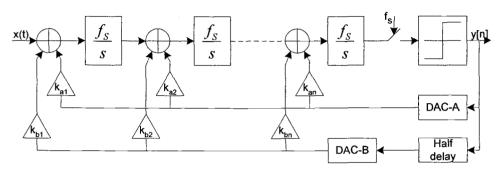

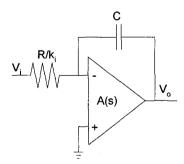

(4) Adaptive DAC pulse-shaping coefficient tuning [W. Gao1997] is based on the nonidealities estimation. Extra feedbacks are added to provide an extra degree of freedom. The pulse-shaping coefficients ( $k_{a1}, k_{b1}, k_{a2}, k_{b2},...$ ) are tuned in order to obtain a match between the desired prototype transfer function and the actual realized loop transfer function, as shown in Fig. 4.7.

Fig. 4. 7 Continuous-time  $\Delta\Sigma$  modulator with DAC pulse-shaping coefficient tuning

These parameters are tuned based on the amount of excess loop delay. The pulse-shaping tuning strategy can be generalized to correct for other nonidealities.

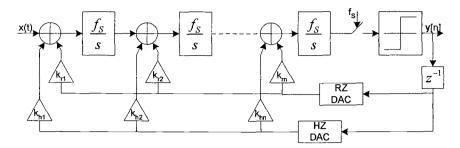

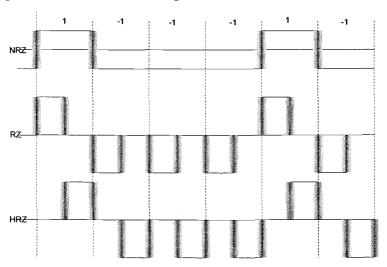

(5) Based on multi-feedback architecture, we could have used two of NRZ, RZ, and half-return-zero (HRZ), or for that matter any other two different pulses, but these three types are easiest to build in a practical circuit [J. A. Cherry1999A]. RZ DAC pulse and HRZ DAC pulse in feedback are improved [K. P. J. Thormas2005], as shown in Fig. 4. 7.

Fig. 4. 8 A continuous-time  $\Delta\Sigma$  modulator with HZ DAC and RZ DAC pulses

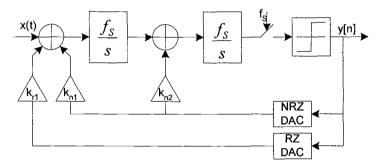

(6) Based on a CRFB CT  $\Delta\Sigma$  modulator with NRZ DAC pulse, Shamsi [H. Shamsi2005] inserts an RZ feedback DAC pulse as shown in Fig 4.8, which RZ feedback DAC pulse is instead of HRZ feedback DAC pulse in [J. A. Cherry1999].

Fig 4.9 The structure of an RZ second order continuous-time  $\Delta\Sigma$  modulator

The RZ feedback insertion method can be employed for the excess loop delay compensation.

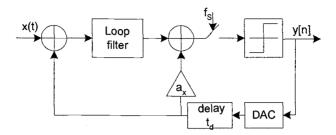

(7) Additional feedback insertion [A. Latiri2005] adds an extra feedback path before the quantizer to compensate for the excess loop-delay, as shown in Fig. 4.9. This method is valid for both the lowpass and the bandpass  $\Delta\Sigma$  modulators.

Fig. 4.10 A continuous-time  $\Delta\Sigma$  modulator with an additional feedback insertion

From the above, in order to overcome and mitigate excess loop delay, we may select the RZ DAC pulse and purposely add delay in feedback.

#### 4.2 Non-Idealities in DAC (II)---Clock Jitter

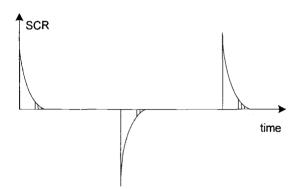

Jitter which causes a variation in the width and/or phase of the DAC pulses in a CT  $\Delta\Sigma$  modulator degrades modulator performance by whitening the in-band noise [J. A. Cherry1998].

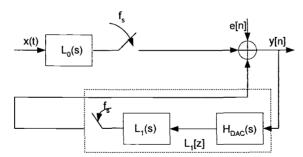

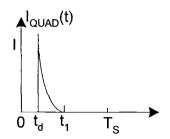

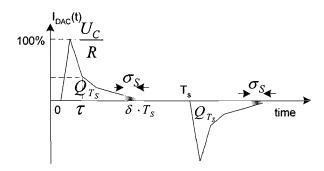

Clock jitter is caused by the random variations of the sampling frequency. It depends on the purity of the clock source. In the CT  $\Delta\Sigma$  modulator, as shown in Fig 4.11, there exist two error sources due to a clock jitter. The first one is at the quantizer and the second one is at the feedback DAC. The sampled error entering the system, which occurs at the internal quantizer in the CT case, is rejected by the high in-band loop gain. Hence, the sampled error is neglected in practice. The clock jitter has a great influence on the feedback DAC in CT  $\Delta\Sigma$  modulator, because the presence of the clock jitter in the DAC waveform changes both the duration and position of the DAC waveform and adds a random phase white noise to the feedback output signal spectrum, causing a time-variant behavior and whitening the quantization noise in the band of interest and lowering SNR. For low jitter values, the SNR is determined by the thermal noise. When jitter is raised, the performance drops.

Fig. 4.11 Jitter error sources distribution in typical CT  $\Delta\Sigma$  modulator

Due to time jitter in the clock signal, both the width and the position of the feedback pulse change. The pulse-position jitter has much less effect than the pulse-width error. Clock jitter induced by the variations of the pulse-width degrades the performance much more than any other jitter induced errors in the feedback DAC of the CT  $\Delta\Sigma$  modulator [M. Ortmanns2005]. This is because pulse-width jitter alters the amount of charge transferred within one clock cycle, while pulse delay jitter only alters the integration over time of a constant amount of charge. It turns out that the latter error is at least first order noise shaped. Pulsewidth jitter dominates over phase jitter because it directly affects the feedback charge [R. Schoofs2007]..

#### **Clock Jitter Models**

Various models for clock jitter are proposed for CT  $\Delta\Sigma$  modulators. In the first model, the clock jitter can be modeled as an additive white noise in the feedback path [H. Shamsi2006C] as shown in Fig 4.12. The model is applicable to different DAC waveforms. A discrete-time modeling technique is proposed [P. M. Chopp2007]. This technique is applicable to different DAC waveforms as well. In [Y. S. Chang2006], an auto-regressive (AR) jitter model is proposed to predict the SNR degradation due to the unwanted phase modulation on DAC output pulses caused by timing error of a clock.

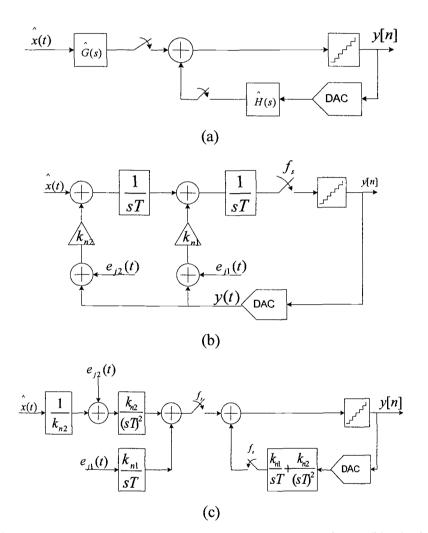

For the graph in the additive noise model proposed [H. Shamsi2006C], G(s) and  $\hat{H}(s)$  represent the feedforward and feedback gains in a CT  $\Delta\Sigma$  modulator in s-domain, respectively.

Fig. 4. 12 (a) A general block diagram of a CT  $\Delta\Sigma$  modulator. (b) The block diagram modeling the clock jitter effect. (c) The simplification of modeling the clock jitter effects

The clock jitter is modeled as two additive noises,  $e_{j1}(t)$  and  $e_{j2}(t)$ . In order to model the effects of  $e_{j1}(t)$  and  $e_{j2}(t)$  at the output of the modulator, the model is furthermore simplified, as shown in Fig. 4.12(c). For simplicity, the feedforward gains of  $e_{j1}(t)$  and  $e_{j2}(t)$  are defined as

$$\hat{G}_1(j2\pi f) = \frac{k_{n1}}{j2\pi fT} \tag{1}$$

$$\hat{G}_{2}(j2\pi f) = \frac{k_{n2}}{(j2\pi fT)^{2}}$$

(2)

By using the definition of the OSR, the feedforward gains of the additive jitter noise can be expressed as

$$\hat{G}_{1}(j2\pi f) = \frac{k_{n1} \times OSR \times 2f_{B}}{j2\pi f}$$

(3)

$$\hat{G}_{2}(j2\pi f) = \frac{k_{n2} \times (OSR \times 2f_{B})^{2}}{(j2\pi f)^{2}}$$

(4)

Since in  $\Delta\Sigma$  modulators, the OSR parameter usually varies from 8 to 128, we have

$$|\hat{G}_1(j2\pi f)| \ll |\hat{G}_2(j2\pi f)| \tag{5}$$

In a good design of the CT  $\Delta\Sigma$  modulator, the coefficients of the modulator,  $k_{n1}$  and  $k_{n2}$  are roughly near to each other, and their difference is low. Therefore, by using (5), the effects of  $e_{j1}(t)$  at the output of the modulator can be neglected in the signal band, compared with the effects of  $e_{j2}(t)$ . For additive jitter noise  $e_{j2}(t)$  is transferred to the output of the modulator as the input signal x(t).

$$P_{jitter} = \left[\frac{x(t)}{k_{n2}} + e_{j2}(t)\right] \times \frac{k_{n2}}{(sT)^2} + \left[\frac{k_{n1}}{sT} + \frac{k_{n2}}{(sT)^2}\right] \times y(t)$$

$$= x(t) \times \frac{1}{(sT)^2} + \left[\frac{k_{n1}}{sT} + \frac{k_{n2}}{(sT)^2}\right] \times y(t) + e_{j2}(t) \times \frac{k_{n2}}{(sT)^2}$$

(6)

$$P_{ieal} = \{ [x(t) + k_{n2}y(t)] \times \frac{1}{sT} + k_{n1}y(t) \} \times \frac{1}{sT}$$

$$= x(t) \times (\frac{1}{sT})^2 + [\frac{k_{n2}}{(sT)^2} + \frac{k_{n1}}{sT}] \times y(t)$$

(7)

Compared the output of the modulator with jitter (6) with the output of the ideal modulator (7), we know that the clock jitter noise increases the inband power of the modulator. Since in a  $\Delta\Sigma$  modulator, the inband frequency products of the input signal of the modulator are transferred to the output of the modulator as they are, so the clock jitter effects at the output of the modulator will be  $k_{n2} \times e_{j2}(t)$ .

#### The Suppression of Jitter Effects

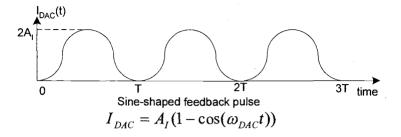

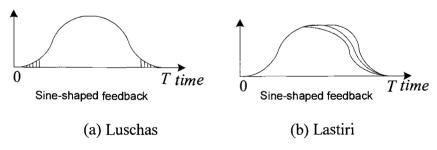

There are many methods to suppress the effect of jitter. The jitter has different influence on different DAC waveforms, which include rectangular (NRZ, RZ, HRZ, multi-bit NRZ, multi-bit RZ) pulses, peaking or shaped feedback pulse, triangular feedback waveform, sine-shaped feedback waveform, exponentially decaying feedback pulse and linearly or quadratically sloping feedback waveform[J. Fang2005], [F. Gerfers2006], [J. A. Cherry1999B] [H. Shamsi2006C] [H. Shamsi2006D] [H. Zare-Hoseini2006].

## A. Prediction and Analysis

For clock jitter analysis, the noise due to clock jitter in single-loop low pass CT  $\Delta\Sigma$  modulators was examined using NRZ DAC waveforms [K. Reddy2006] and [K. Reddy2007]. It was shown that noise transfer functions with optimized zeros result in lower jitter noise than those with all zeros at the origin. It also was shown the jitter noise and quantization noise cannot be reduced simultaneously, and there is an optimum out-of-band which minimizes the total noise. For clock prediction, by using the state-space approach, a precise method for the prediction of the spectrum of the jitter-induced noise is proposed [O. Oliaei2003]. The results are applicable to all types of analog-to-digital or digital-to-analog  $\Delta\Sigma$

modulator. Based on the use of state-space formulation, closed-form expressions were derived for the noise power and SNR [R. Tortosa2005]. It was shown that the jitter-induced noise can be separated into two main components: one depending on the modulator loop filter and the other one due to the input signal. The latter allows us to accurately predict the SNR degradation and to optimize the modulator performance in terms of jitter insensitivity. However, this state-space approach of the clock jitter is complicated since involves the analysis of a time-variant system. Besides, this analysis is limited for RZ DAC waveforms only and its solution is not applicable for NRZ DAC waveforms [H. Shamsi2006C].

#### B. Rectangular DAC Waveform

For rectangular DAC waveform, the jitter-induce noise depends on both the width and the position of the waveform. It has been shown that a variation of the width of the pulse is much worse than all other timing effects, having a larger negative effect on the performance of the modulator.

Rectangular DAC waveforms will be influenced by inter-symbol interference (ISI). If an NRZ signaling is used, a data-dependent transient exists at the DAC's output node due to its parasitic node capacitance. This data-dependent transient causes ISI, which degrades the linearity of the modulator. Even though a NRZ code will not contribute to nonlinearity, in measurements, harmonics were seen due to the NRZ code. These harmonics are the result of asymmetric switching errors in the DAC. Although we may build the DAC fully differentially, which has symmetric DAC rising and falling edges, the transported charge for a "high" or a "low" code is not the same. Mismatch in the DAC latch and mismatch in the sampling switches create different charge injection into the output noise of the DAC. Therefore, a fully differential circuit cannot remove the ISI. For lower frequencies, these effects can be neglected but cannot be ignored for high clock frequencies, such as beyond 100MHz. One approach to reduce the effects of

limited rise and fall times is to use RZ pulses. RZ feedback DACs have been used to mitigate distortion arising from different rise and fall times in NRZ DACs. By using RZ signaling, the DAC's output reset to a constant DC level before the next input comes in, removes the data-dependent transient and thus improves the linearity of the modulator. Although an RZ scheme, in other single-ended designs, ensure that unequal rise and fall times of the DAC pulses do not contribute to the distortion, in a fully differential system unequal rise and fall times appear as a common-mode signal and do not contribute distortion provided there is adequate common-mode rejection. It is well known that the RZ signaling scheme is required in the feedback DAC of a CT  $\Delta\Sigma$  modulator for low distortion. Therefore, RZ DAC pulses may overcome ISI.

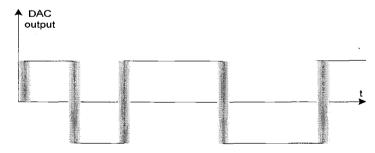

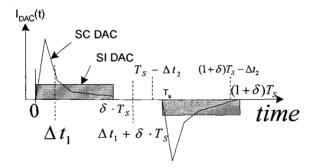

On the other hand, since the distortion in DAC depends on the preceding symbol, it is signal-dependent and will result in harmonic components and intermodulation products. The distortion in a 1-bit NRZ DAC is caused by ISI as shown in Fig. 4.13.

Fig. 4.13 Distortion due to limited rise and fall times of a DAC using NRZ pulse

Because the NRZ DAC pulse transition in practice will have a limited rise and fall time, the effective DAC feedback level will depend on whether or not there is an output transition from one level to the opposite level. In case of a transition, the effective DAC feedback level will be less than that without transition.

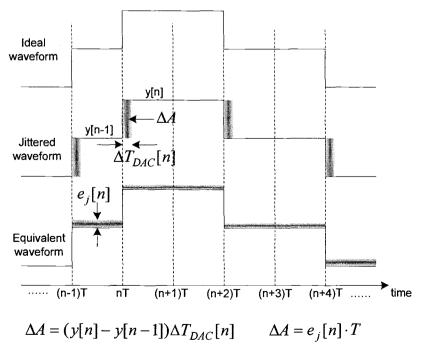

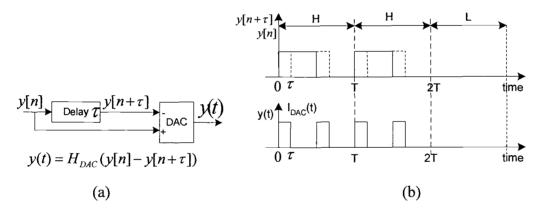

To ease the analysis of the effect of the DAC clock jitter on the CT modulator, the timing error of the DAC output signal transition edges is modeled as an equivalent error in the signal magnitude. DAC sampling uncertainties produce errors in the area of the feedback pulses for every sampling period. We can find the equivalent additive error sequence  $e_j[n]$  that produces the same area error in a feedback pulse train with ideal timing [S. Paton2004]. If the DAC sampling uncertainty between the  $(n-1)^{th}$  and the  $n^{th}$  clock period is  $\Delta T_{DAC}[n]$ , then the equivalent magnitude error  $e_j[n]$  for the  $n^{th}$  DAC pulse with an ideal timing is given by

$$e_{j}[n] = \frac{\Delta A}{T} = (y[n] - y[n-1]) \cdot \frac{\Delta T_{DAC}[n]}{T}$$

(8)

where  $\Delta A$  is the area difference between the ideal waveform and the jittered waveform during the  $n^{th}$  clock period, and y[n] is the modulator output. The jitter-induced noise for NRZ DAC is illustrated as shown in Fig 4.14 [X. Chen2007].

Fig. 4. 14 Model of the jitter-induced noise for NRZ DAC

Assuming that the output of the modulator and the clock jitter are independent, the variance of  $e_i[n]$  can be expressed as

$$\sigma_{e_j}^2 = \frac{1}{T^2} \sigma_{DAC}^2 \sigma_{dy}^2 \tag{9}$$

where dy[n] = (y[n] - y[n-1])/T,  $\sigma_{DAC}^2$  is the standard deviation of the adjacent output difference, and  $\sigma_{dy}^2$  is the standard deviation of the clock jitter.

In comparison with NRZ waveform, which involves only one transition in each clock period, RZ and HRZ waveform involve two transitions in each clock period. Thus the amplitude of the additive jitter noise of the RZ and HRZ waveforms is twice the amplitude of its NRZ counterpart.

Fig. 4.15 NRZ, RZ, HRZ including jitter

As illustration in Fig. 4.15, assuming that the duty cycle of the RZ and HRZ pulse shaping is 0.5, the amplitude of the RZ DAC and HRZ DAC have to be twice as high as that of the NRZ DAC, to keep the area of the DAC output waveform unchanged.

Furthermore, we may analyze and derive the standard variations of the rectangular feedback DAC pulses [Z. Li2007B].

$$\sigma_{e_j,NRZ}^2 = \frac{1}{T^2} \sigma_{DAC,NRZ}^2 \sigma_{dy}^2 \tag{10}$$

$$\sigma_{e_j,RZ}^2 = \frac{2}{T^2} \sigma_{DAC,RZ}^2 \sigma_{dy}^2 \tag{11}$$

$$\sigma_{e_j.HRZ}^2 = \frac{2}{T^2} \sigma_{DAC,HRZ}^2 \sigma_{dy}^2 \tag{12}$$

From (9), (10) and (11), the jitter noise power can be lowered by reducing the standard deviation of the adjacent modulator output difference. In other words, if the step size of the quantizer is reduced, the jitter noise is lowered. This means that using multi-bit DACs can reduce their sensitivity to clock jitter. For RZ and HRZ DAC, the output error due to jitter is proportional to the output value, not the difference. The coefficient "2" in the above two equations takes into account the fact that both RZ and HRZ DACs are affected by jitter twice in one cycle, at both their rising and falling edges. Multi-bit NRZ DAC should provide best jitter noise immunity than the other two in that its outputs do not need to reset to zero for every clock cycle and hence the average adjacent output difference is smaller. Note that the more levels the quantizer has, the smaller the jitter induced error will be. However, this is only true for multi-bit NRZ DAC, not for RZ and HRZ DACs [Z. Li2007B].

For a NRZ DAC pulse-shaped feedback, assuming the sinusoidal input signal amplitude is A, the oversampling ratio is OSR, the period of the sampling clock is T, the standard deviation of the clock jitter is  $\sigma_{\Delta y}^2$ , and the standard deviation of the adjacent modulator output difference is  $\sigma_{DAC,NRZ}^2$ , the signal-to-jitter ratio of a CT  $\Delta\Sigma$  modulator can be expressed as [J. A. Cherry2000] [Z. Li2007]

$$SNR_{jitter,NRZ} = \frac{P_s}{P_{jitter}} = \frac{\frac{A^2}{2}}{\sigma_{e_j,NRZ}^2 / OSR} = \frac{OSR \cdot A^2}{2\sigma_{DAC,NRZ}^2 (\frac{\sigma_{\Delta y}}{T})^2}$$

(13)

$$SNR_{jitter,RZ} = \frac{P_s}{P_{jitter}} = \frac{\frac{A^2}{2}}{\sigma_{e_j,RZ}^2 / OSR} = \frac{OSR \cdot A^2}{4 \cdot \sigma_{DAC,RZ}^2 (\frac{\sigma_{\Delta y}}{T})^2}$$

(14)

$$SNR_{jitter,HRZ} = \frac{P_s}{P_{jitter}} = \frac{\frac{A^2}{2}}{\sigma_{e_j,HRZ}^2 / OSR} = \frac{OSR \cdot A^2}{4 \cdot \sigma_{DAC,HRZ}^2 (\frac{\sigma_{\Delta y}}{T})^2}$$

(15)

From (13), (14) and (15) known, the SNR of NRZ DAC is higher than the RZ DAC or HRZ DAC in the same condition.

Traditionally, in single-bit  $\Delta\Sigma$  modulators, SNR degradation due to loop-delay may be significantly reduced by using a RZ feedback signal. RZ feedback DACs have been used in continuous-time  $\Delta\Sigma$  modulators to overcome ISI due to unequal rising and falling edges of the feedback DAC waveform. The NRZ DAC pulse suffers from ISI. A CT  $\Delta\Sigma$  modulator with the RZ DAC pulse is more sensitive to clock jitter than its NRZ counterpart [H. Shamsi2006C]. The RZ DAC may not provide sufficient feedback level, especially at high sampling frequency. The use of RZ DACs in a multi-bit modulator can lead to severe sensitivity to clock jitter when compared to CT  $\Delta\Sigma$  modulators with NRZ DACs [S. Yan2004]. So, in the multi-bit CT  $\Delta\Sigma$  modulators, an NRZ feedback signal is preference in order to take advantage of their reduced sensitivity to clock jitter [H. Aboushady2004]. A general rule of thumb is that jitter noise in a RZ DAC will have 6dB higher noise level in the signal band [K. T. Tiew2005]

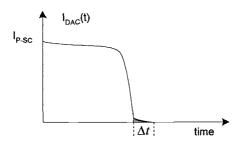

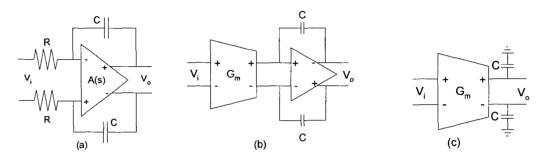

#### C. Multilevel Pulse Signals by Using FIR DAC and An Additional Delay

Finite impulse response (FIR) filters allow a single-bit modulator to achieve a jitter performance comparable with that of a multi-bit structure without causing harmonic distortion. Multi-bit NRZ DACs reduces the requirement on the clock jitter. Since the jitter-induced noise is proportional to the step height of the DAC waveform, each additional bit of the DAC means that DAC's output height is decreased corresponding to a lower sensitivity to jitter. However, the number of bits of DAC is constrained by the power consumption in quantizer. Increasing the number of DAC's bits introduces linearity problems that need additional circuits for compensations.