#### AN ABSTRACT OF THE DISSERTATION OF

<u>Drake A. Miller</u> for the degree of <u>Doctor of Philosophy</u> in Electrical and Computer Engineering presented on March 7, 2011.

Title: Random Dopants and Low-Frequency Noise Reduction in

Deep-Submicron MOSFET Technology

| Abstract approved: _ |  |  |

|----------------------|--|--|

|                      |  |  |

#### Leonard Forbes

The future of mixed-signal, memory, and microprocessor technologies are dependent on ever increasing analog and digital integration, higher cell densities, and demand for more processing power. As a result MOSFET device dimensions continue to shrink to meet these demands. A side effect of device scaling is increased variability at each technological node which affects both analog and digital circuits in terms of decreased yields, performance, and noise margins.

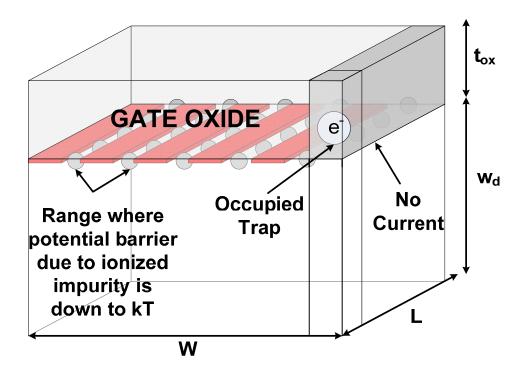

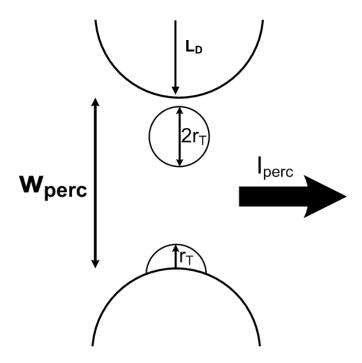

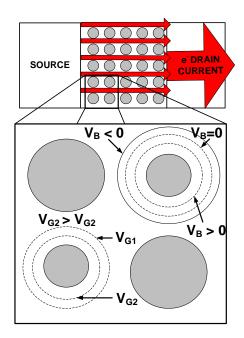

At deep sub-micron dimensions the Low-Frequency Noise (LFN) of the MOSFET is dominated by the influence of one or more active traps capturing and emitting charge to and from the oxide creating wide variations in the LFN from otherwise identical devices. Additionally, the random position of dopant atoms near the Si/SiO<sub>2</sub> interface create a potential landscape that induces regions of high and low conductivity which in turn causes a situation where the current is no longer uniform in

the device, but consist of individual current paths or percolating currents. The coupling between the random variation of the percolation current and active traps in the oxide are responsible for the large spread ( > 3 orders of magnitude) in the noise characteristics observed in deep sub-micron MOSFET devices. The compact LFN model presented here accounts for the action of traps on percolating currents in deep-sub-micron and nano-scale MOSFETs.

Two schemes for reduction of LFN are studied based on the smoothing of the surface potential. First, noise reduction is demonstrated with measurements on submicron MOSFETs with forward substrate bias. Secondly, the model is further verified through the reduction of noise by the removal of dopant atoms near the Si/SiO<sub>2</sub> interface of the device. Both schemes result in a lower noise and threshold device.

Finally, these experimental findings are applied to a 2.2µm 2 MP CMOS image sensor. From the temporal noise measurements on threshold implant process splits, the image sensor noise has been significantly reduced as a direct result of fundamentals described by this MOSFET LFN model and further proves the validity of these findings.

©Copyright by Drake A. Miller

March 7, 2011

All Rights Reserved

# Random Dopants and Low-Frequency Noise Reduction in Deep-Submicron MOSFET Technology

by

Drake A. Miller

### A DISSERTATION

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented March 7, 2011 Commencement June 2011

| <u>Doctor of Philosophy</u> dissertation of <u>Drake A. Miller</u> presented on <u>March 7, 2011</u> .                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APPROVED:                                                                                                                                                                                                 |

| Major Professor, representing Electrical and Computer Engineering                                                                                                                                         |

|                                                                                                                                                                                                           |

| Director of the School of Electrical Engineering and Computer Science                                                                                                                                     |

|                                                                                                                                                                                                           |

| Dean of the Graduate School                                                                                                                                                                               |

|                                                                                                                                                                                                           |

|                                                                                                                                                                                                           |

|                                                                                                                                                                                                           |

|                                                                                                                                                                                                           |

|                                                                                                                                                                                                           |

| I understand that my dissertation will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my dissertation to any reader upon request. |

#### **ACKNOWLEDGEMENTS**

The love and support from my wife, Jenaye, has been the fuel to continue in this most difficult of pursuits. She has so graciously put her own life goals on hold to care for and raise our three children. I am forever in her debt for the sacrifices that she has made on this long journey. I love you and will never forget what you have done for us.

My most sincere appreciation goes to Professor Leonard Forbes. His expertise and guidance have taught me a great deal. Through the years we have worked on a number of projects and I am always amazed at his reduction of complex problems to their most simplest of parts. It is this ability that I continually strive for and will take into my professional career with great gratitude. I hope that I will have the opportunity to work with Len for many years to come.

None of this would have been possible without the continued support from my parents and grandparents. They never questioned this direction I have taken and have always been a source of encouragement through the toughest of times. Finally, a special thank you, to my good friend and colleague, David Zier, who has always been there as source of reason and inspiration.

## TABLE OF CONTENTS

|                                                     | <u>Page</u> |

|-----------------------------------------------------|-------------|

| 1 Introduction                                      | 1           |

| 1.1 Organization of the Dissertation                | 5           |

| 2 Semiconductor Noise                               | 8           |

| 2.1 Johnson-Nyquist (Thermal) Noise                 | 9           |

| 2.2 Shot Noise                                      | 10          |

| 2.3 Generation-Recombination Noise                  | 11          |

| 2.4 1/ <i>f</i> Noise                               | 15          |

| 2.5 Random Telegraph Signal (RTS) Noise             | 16          |

| 2.6 Low-Frequency Noise in MOSFETs                  | 19          |

| 2.6.1 1/f Noise in MOS Devices                      | 20          |

| 2.6.2 RTS Noise in MOS Devices                      | 22          |

| 2.7 1/f and RTS in Circuits                         | 25          |

| 2.7.1 Subthreshold Leakage Due to 1/f and RTS Noise | 25          |

| 2.8 RTS Noise in MOSFET circuits                    | 33          |

| 2.8.1 RTS Noise in Sense Amplifiers                 | 33          |

| 2.8.2 1/f Noise                                     | 34          |

| 3 RTS Noise Measurement Methods                     | 44          |

| 3.1 Noise Test System                               | 45          |

| 3.2 Device Under Test                               | 48          |

| 3.3 Time Domain Noise                               | 50          |

| 3.4 Trap Histogram Analysis                         | 52          |

| 3.5 RTS Noise Spectrum Analysis                     | 54          |

| 3.6 Trap Analysis                                   | 55          |

| 4 Deep-submicron MOSFET RTS Noise Model             | 61          |

| 4.1 Random Dopants                                  | 62          |

| 4.2 MOSFET Two-State Random Fluctuation Model       | 67          |

# TABLE OF CONTENTS (Continued)

|                                                       | <u>Page</u> |

|-------------------------------------------------------|-------------|

| 4.3 Percolation Current Modulation                    | 68          |

| 4.4 Trap Time Constants                               | 76          |

| 4.5 Model Predictions                                 | 77          |

| 5 Low-Frequency Noise Reduction Techniques in MOSFETs | 80          |

| 5.1 Substrate Bias                                    | 81          |

| 5.2 Channel Engineering.                              | 87          |

| 6 Case Study: Noise Reduction in a CMOS Image Sensor  | 94          |

| 6.1 Noise in CMOS Image Sensors                       | 95          |

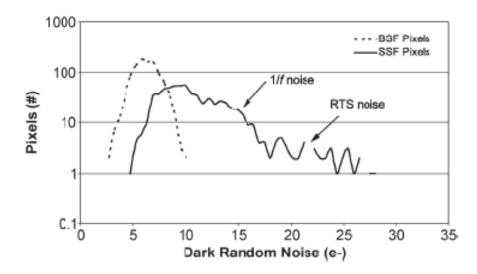

| 6.2 RTS Noise in CMOS Image Sensors                   | 98          |

| 6.3 Source Follower Transistor Measurements           | 100         |

| 6.4 Noise Reduction Process Splits                    | 105         |

| 6.5 Imager Temporal Noise Characterization            | 106         |

| 6.6 Imager RTS Noise Characterization (Time Domain)   | 117         |

| 6.7 Case Study Conclusion                             | 126         |

| 7 Conclusion                                          | 128         |

| Bibliography                                          | 131         |

| APPENDICES                                            | 139         |

| Appendix A Spectral Estimation                        | 140         |

| Appendix B Imager Sensor Noise Equations              | 144         |

# LIST OF FIGURES

| <u>Figure</u>                                                                                                                                                               | <u>Page</u> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Figure 2.1 Ideal GR Noise spectrum from a single time constant                                                                                                              | 13          |

| Figure 2.2 GR Noise Spectrum of Photoconductive Device                                                                                                                      | 14          |

| Figure 2.3 1/f noise from summation of several RTS waveforms from submicron devices                                                                                         |             |

| Figure 2.4 Idealized random telegraph signal.                                                                                                                               | 19          |

| Figure 2.5 Single Electron RTS                                                                                                                                              | 27          |

| Figure 2.6 Histogram of l/f noise from a large device                                                                                                                       | 27          |

| Figure 2.7 RTS due to traps in the channel region                                                                                                                           | 28          |

| Figure 2.8 RTS model for subthreshold leakage                                                                                                                               | 31          |

| Figure 2.9 Drain current distributions on a nanoscale 0.2um transistor                                                                                                      | 32          |

| Figure 2.10 RTS signal due to trapping and emission of multiple electrons i nanoscale n-channel CMOS transistor.                                                            |             |

| Figure 2.11 Calculated threshold voltage distributions on a 50nm transis with a 2nm gate oxide and gate width, W=2500 nm or W=2.5µm, a very w device, data taken from [29]. | ide         |

| Figure 2.12 Circuit diagram of a simplified sense amplifier.                                                                                                                | 37          |

| Figure 2.13 Error rate on a DRAM sense amplifier due to upset by mismatch for different W/L values.                                                                         |             |

| Figure 3.1 DUT bias circuit schematic                                                                                                                                       | 46          |

| Figure 3.2 Measure background noise using a $100k\Omega$ metal film resistor place of device and a $100k\Omega$ biased at $5\mu$ A.                                         |             |

| <u>Figure</u> <u>Page</u>                                                                                                                                                                                                  |      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 3.3 Implant Profile for: (a) Periphery transistor and (b) Pixel transistor                                                                                                                                          | 50   |

| Figure 3.4 Noise signal trace of a DC biased MOSFET with W, L = $0.35\mu m$ . The inset of the figure shows a zoomed-in picture of the recorded data demonstrating the discrete current fluctuations.                      |      |

| Figure 3.5 Drain current noise signal showing multiple active traps                                                                                                                                                        | . 51 |

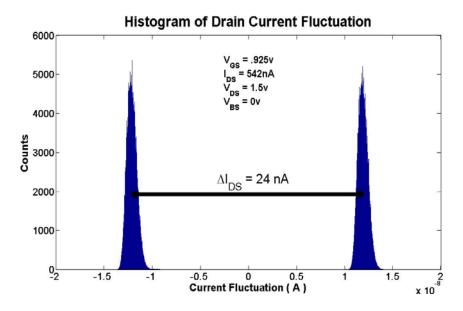

| Figure 3.6 Histogram of a single RTS trapping signal                                                                                                                                                                       | . 53 |

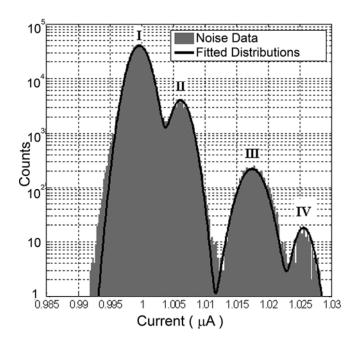

| Figure 3.7 Histogram of recorded signal of MOSFET drain noise. Two traps are readily seen as 4 peaks in the data. Peaks I and III are one trap and peaks II and IV are a second trap.                                      |      |

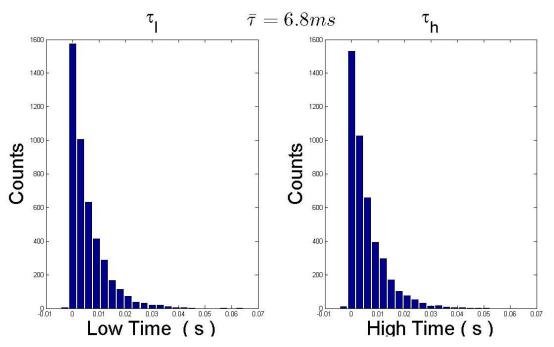

| Figure 3.8 Trapping time distribution in the high and low state from signal in Figure 3.6                                                                                                                                  |      |

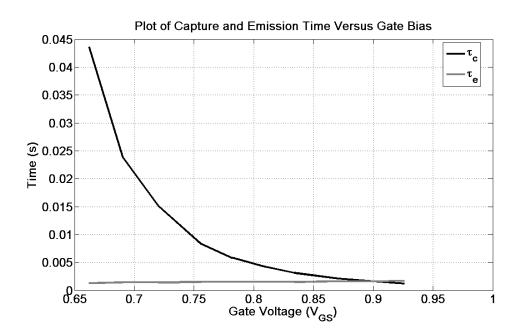

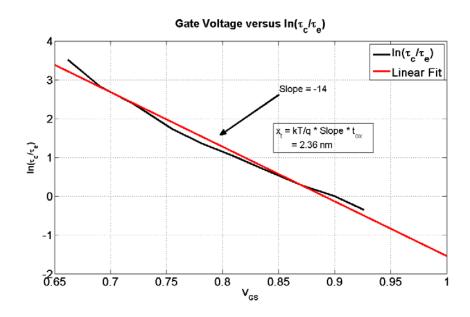

| Figure 3.9 Plot of capture and emission times versus gate voltage for a pure oxide MOSFET                                                                                                                                  |      |

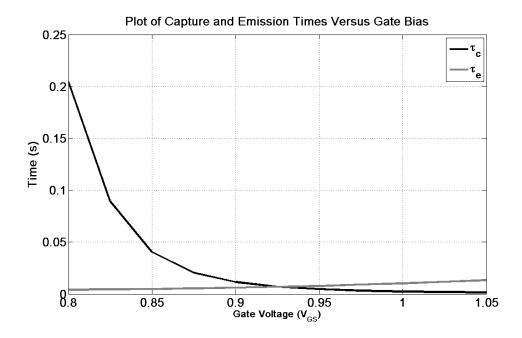

| Figure 3.10 Trap location analysis of a pure oxide gate MOSFET W/L = $0.36/0.36$ micron, $t_{ox}$ = 65 Angstroms                                                                                                           |      |

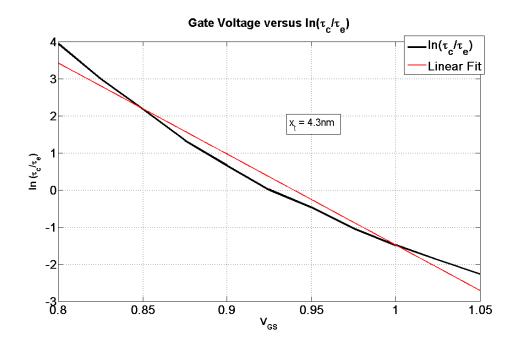

| Figure 3.11 Capture and emission times versus gate voltage for a plasma nitride gate MOSFET                                                                                                                                |      |

| Figure 3.12 Trap location analysis for plasma nitrided gate $W/L = .36/.36$ micron, $Tox = 65$ Angstroms                                                                                                                   | 59   |

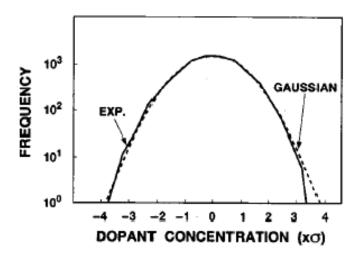

| Figure 4.1 Channel dopant distribution from 8k-MOSFET array. Shows fit to Gaussian distribution for average $N_a$ of 7.1 X $10^{16}$ cm <sup>-3</sup> at 0 and standard deviation of 1.7 X $10^{15}$ cm <sup>-3</sup> [2]. | 64   |

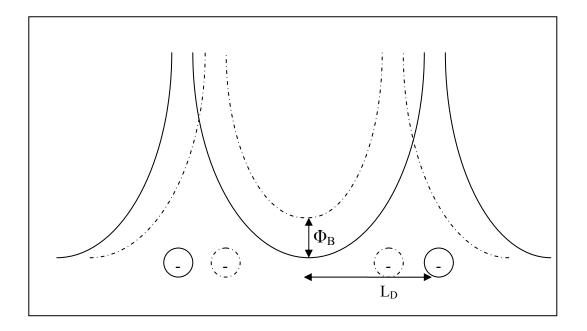

| Figure 4.2 Schematic of dopant field effects. Demonstrates that as dopants are closer together this presents an increased barrier, $\Phi B$ , to electrons.                                                                | .66  |

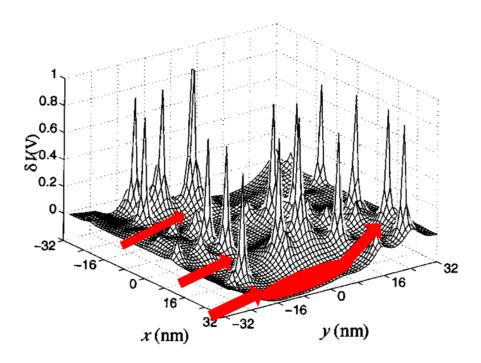

| Figure 4.3 Surface potential simulation of nano-scale MOSFET [7]                                                                                                                                                           | 69   |

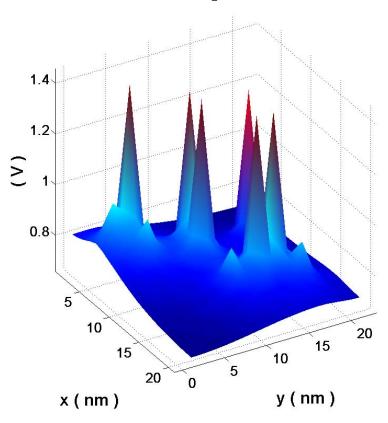

| Figure 4.4 Simple potential simulator result for 10 discrete dopant atoms at the Si/SiO2 interface                                                                                                                         | 70   |

| <u>Figure</u> Page                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------|

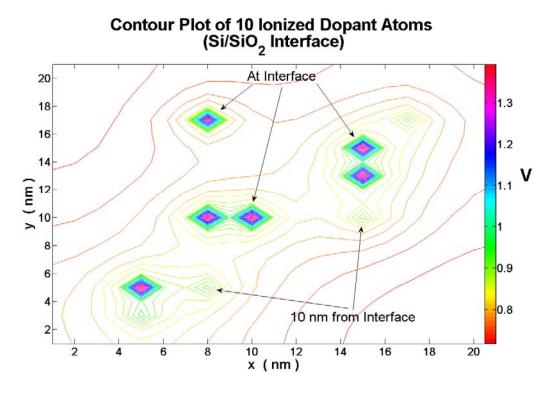

| Figure 4.5 Contour map of Figure 4.4 through a slice at the interface                                               |

| Figure 4.6 3-D pictorial view of perfect dopant arrangement and percolation currents                                |

| Figure 4.7 2-D schematic of single percolation path                                                                 |

| Figure 4.8 Bias influences on dopant field                                                                          |

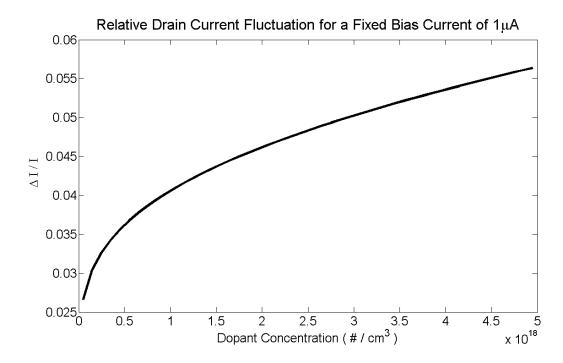

| Figure 4.9 Relative drain current fluctuation versus dopant concentration 77                                        |

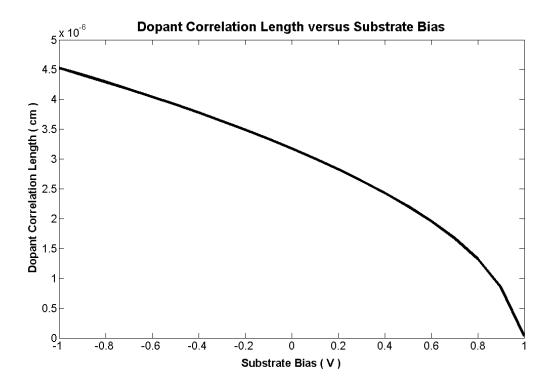

| Figure 5.1 Substrate bias versus the dopant potential correlation length for an n-channel MOSFET82                  |

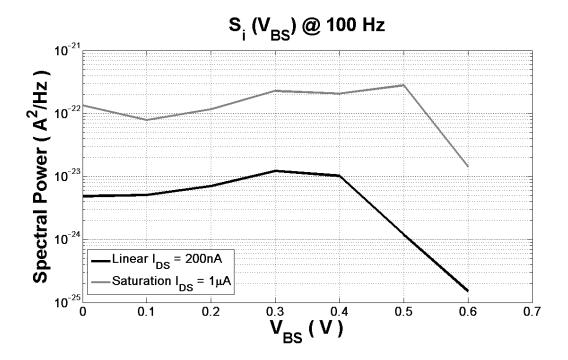

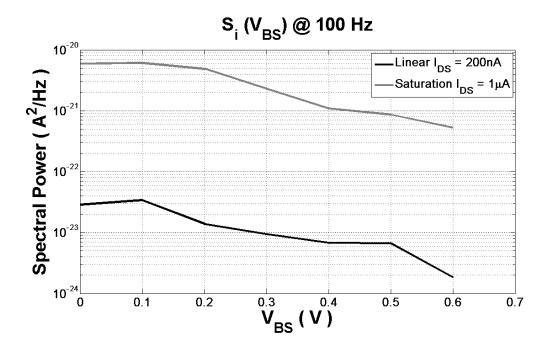

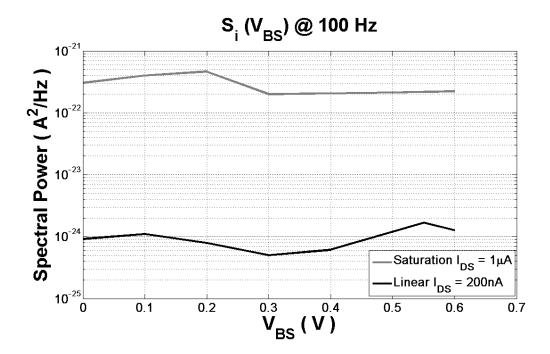

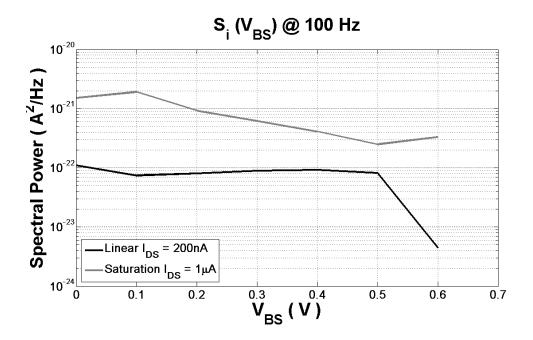

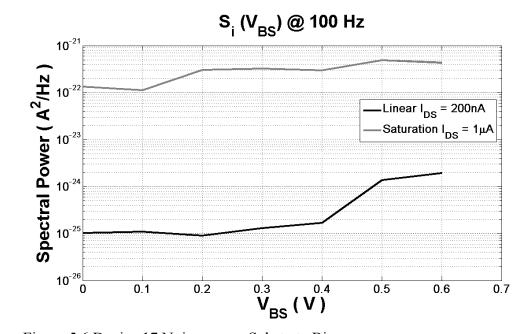

| Figure 5.2 Device 4 Noise versus Substrate Bias                                                                     |

| Figure 5.3 Device 8 Noise versus Substrate Bias                                                                     |

| Figure 5.4 Device 11 Noise versus Substrate Bias                                                                    |

| Figure 5.5 Device 14 Noise versus Substrate Bias                                                                    |

| Figure 5.6 Device 17 Noise versus Substrate Bias                                                                    |

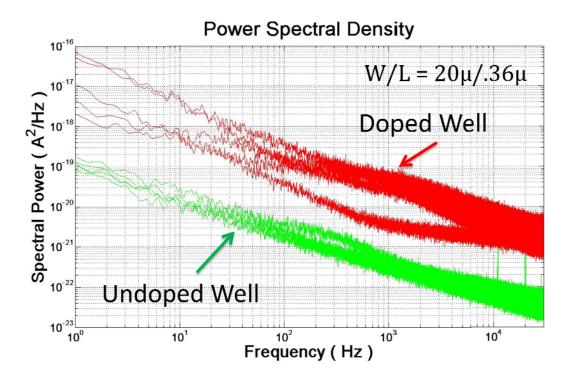

| Figure 5.7 Low-Frequency Noise in a 20µm wide MOSFET                                                                |

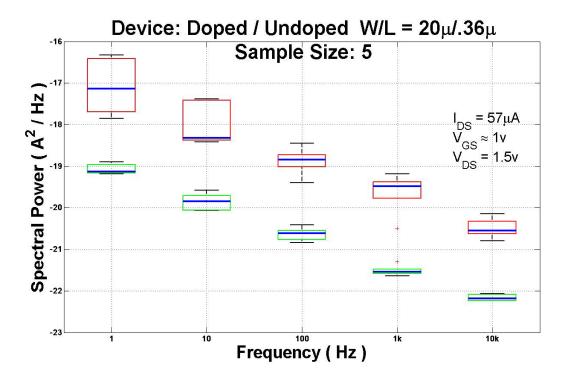

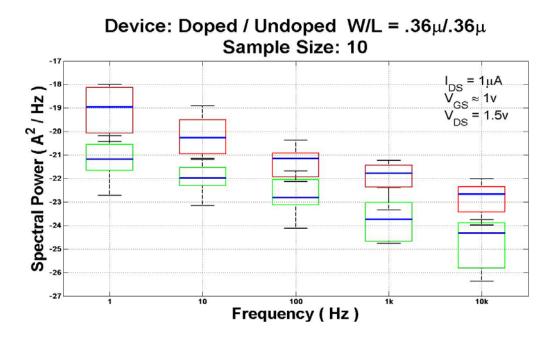

| Figure 5.8 Box plot of power spectral data                                                                          |

| Figure 5.10 Statistics of the noise of Figure 5.8 91                                                                |

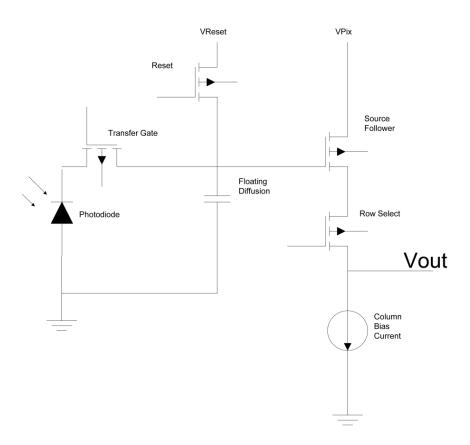

| Figure 6.1 4 transistor (4T) active pixel circuit schematic                                                         |

| Figure 6.2 Comparison of the dark read noise of a surface SF and buried channel SF [6].                             |

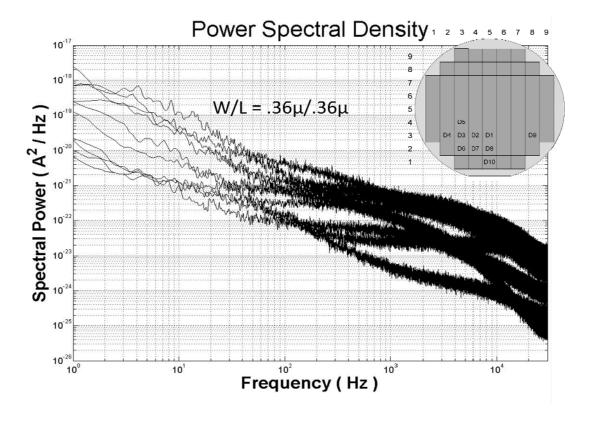

| Figure 6.3 Noise spectral power plots of 10 devices taken from 10 different locations across the wafer (see inset). |

| <u>Figure</u>                                                                                                                                   | <u>Page</u> |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

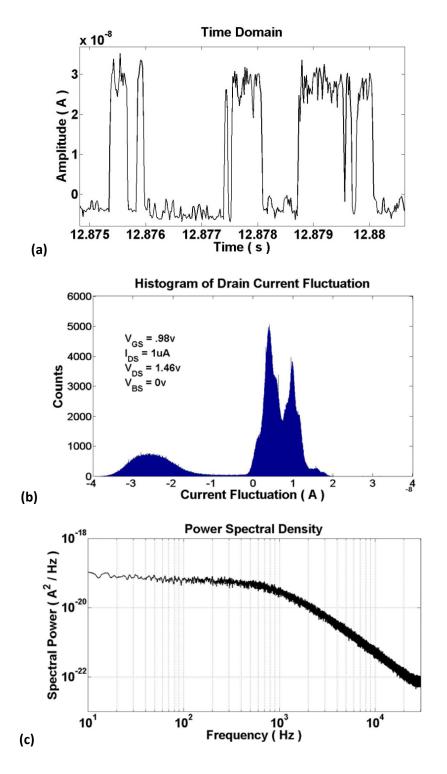

| Figure 6.4 (a) Time domain RTS waveform (b) amplitude distribut power spectral density of RTS signal                                            |             |

| Figure 6.5 Power Spectral Density of sub-micron (W, $L=0.36\mu m$ ) follower transistors                                                        |             |

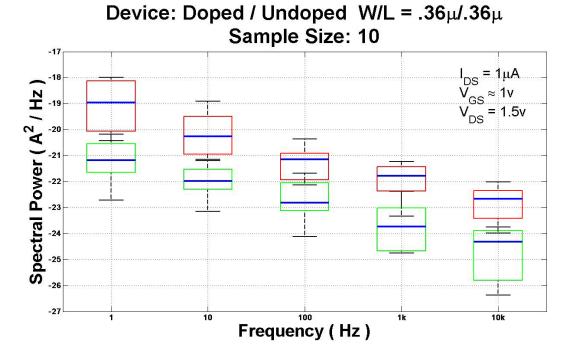

| Figure 6.6 Box plots of source follower noise power spectrum plot Figure 6.5. Red boxes are doped devices. Green boxes are undoped "transistors | native"     |

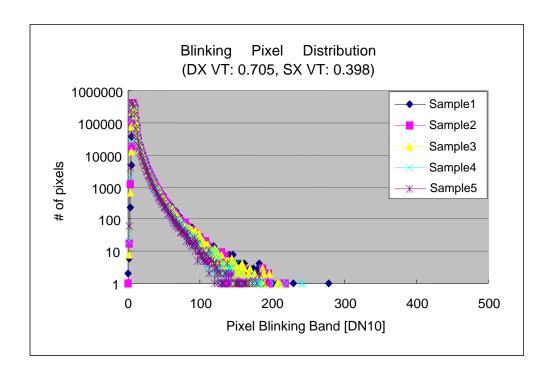

| Figure 6.7 RTS pixel distribution from baseline process conditions                                                                              | 109         |

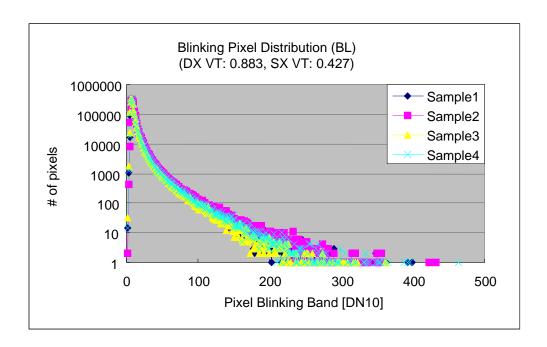

| Figure 6.8 RTS pixel distribution for split #1                                                                                                  | 109         |

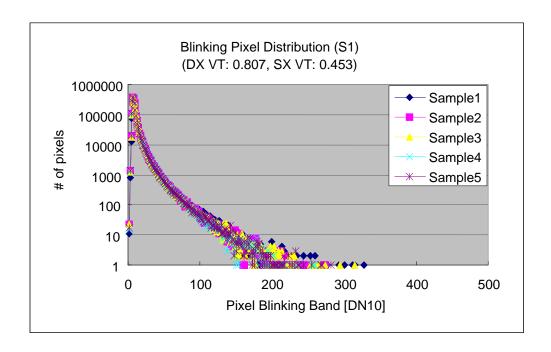

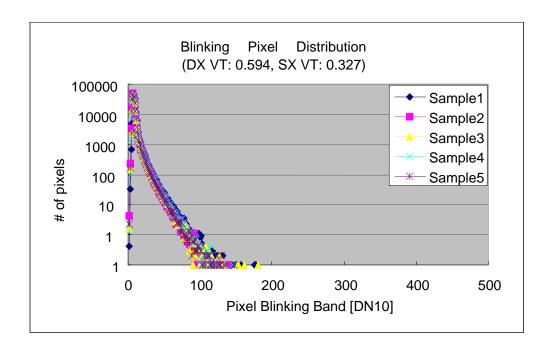

| Figure 6.9 RTS pixel distribution for split #2                                                                                                  | 110         |

| Figure 6.10 RTS pixel distribution for split #3                                                                                                 | 110         |

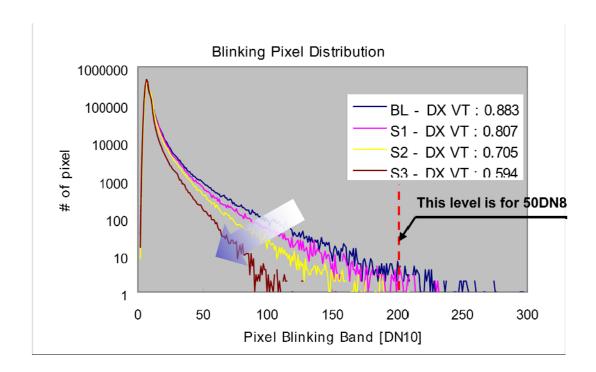

| Figure 6.11 RTS pixel distribution from mean samples taken from process split condition                                                         |             |

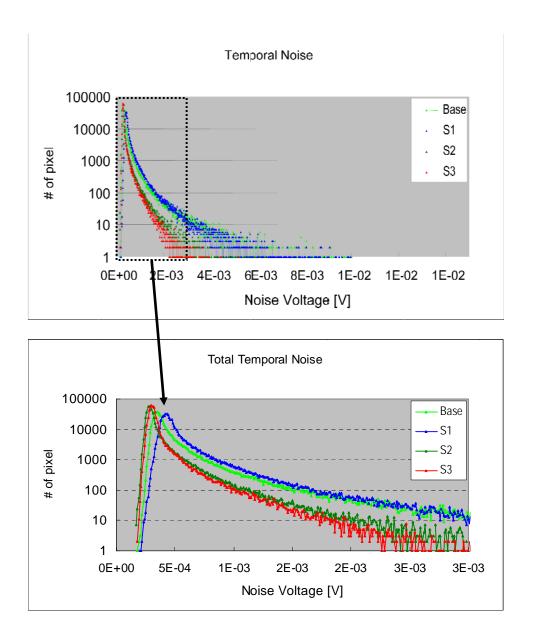

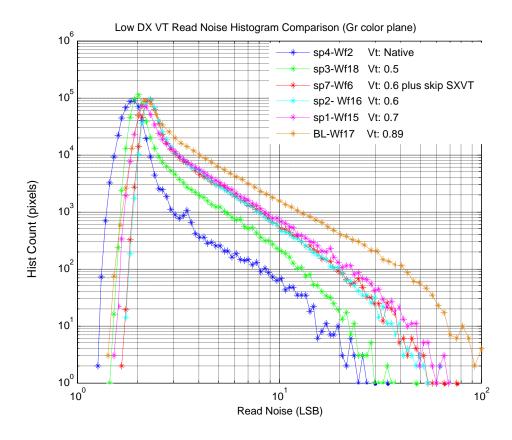

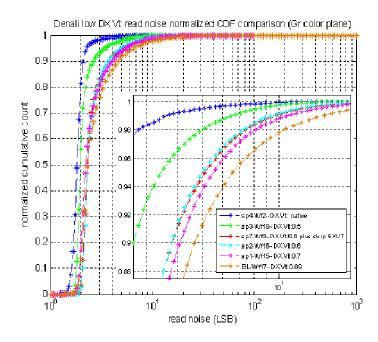

| Figure 6.12 Temporal noise distributions                                                                                                        | 112         |

| Figure 6.13 Read noise of the process splits                                                                                                    | 114         |

| Figure 6.14 Cumulative distribution function of the read noise                                                                                  | 115         |

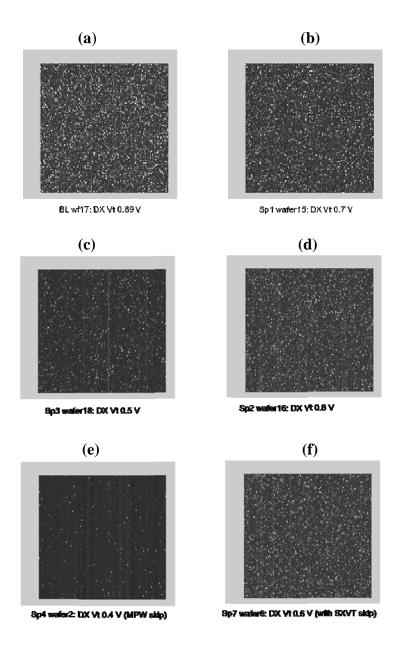

| Figure 6.15 Read noise maps for pixel splits (a) – (f) represent various splits                                                                 | -           |

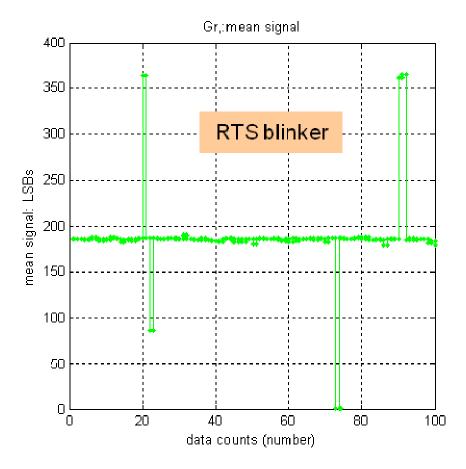

| Figure 6.16 RTS Blinker                                                                                                                         | 119         |

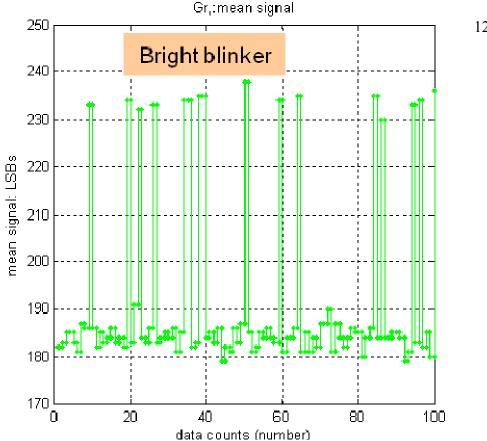

| Figure 6.17 Bright blinking pixel                                                                                                               | 120         |

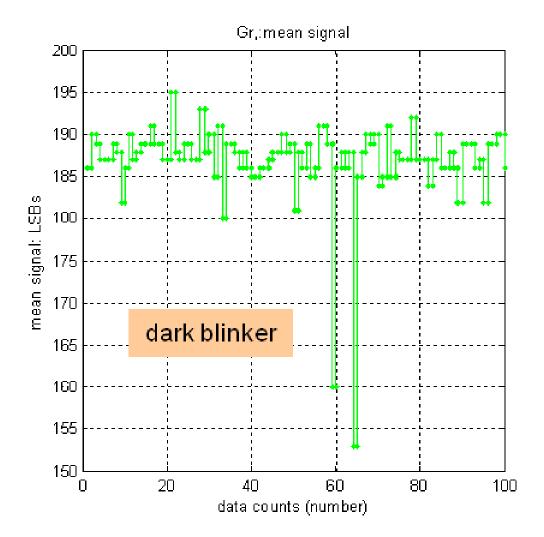

| Figure 6.18 Dark blinking pixel.                                                                                                                | 121         |

| Figure 6.19 Comparison of RTS blinking pixels.                                                                                                  | 122         |

| Figure 6.20 Normalized detection probability of RTS blinking pixels                                                                             | 123         |

| <u>Figure</u>                                    |     | Page |

|--------------------------------------------------|-----|------|

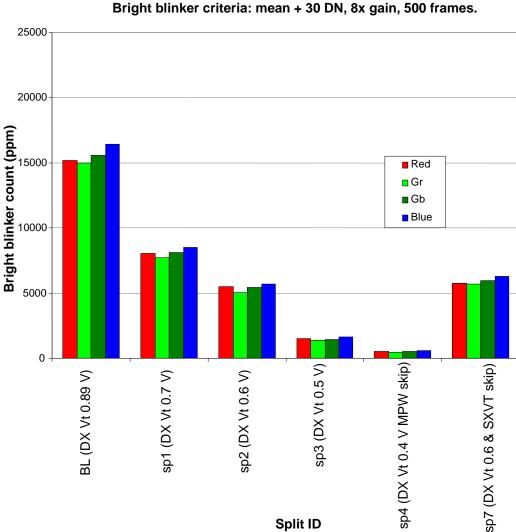

| Figure 6.21 Comparison of bright blinking pixels | 124 |      |

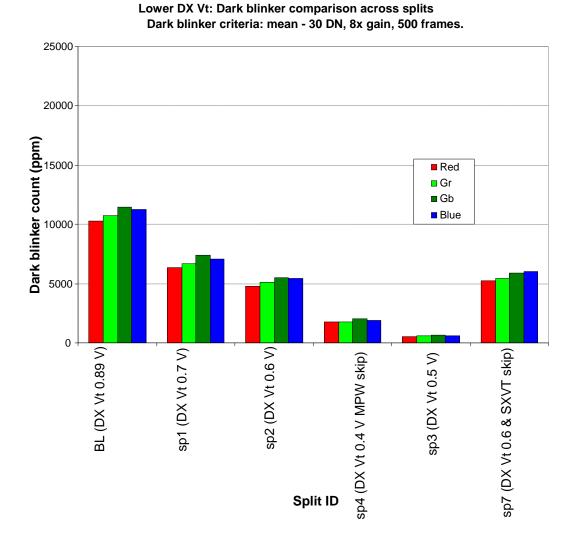

| Figure 6.22 Comparison of dark blinking pixels   |     | 125  |

## LIST OF TABLES

| <u>Table</u>                                                   | <u>Page</u> |

|----------------------------------------------------------------|-------------|

| 6.1 Split conditions for threshold voltage lowering study      | 105         |

| 6.2 Image Sensor characterization settings and conditions      | 108         |

| 6.3 Total Temporal Noise from process splits baseline, 1, 2, 3 | 113         |

| 6.4 RTS blinker type definitions                               | 118         |

For my wife

Jenaye Ryann Miller

#### 1 Introduction

Electronic noise and in particular 1/f noise has been a fundamental limit to engineers who attempt to measure and control increasingly smaller currents and voltages. A prime example of a technology where noise places severe limitations and a practical example of this research is in CMOS image sensor (CIS) technology. At a minimum a CIS device consists of an array of photodiodes, analog readout circuits, and pixel clocking circuits. Each block of the CIS chip is made up of many MOSFET devices. These devices form the circuits used to convert the optical signal to an electrical signal and for driving the pixel timing signals.

The photodiode sensor and the following analog and analog-to-digital conversion circuitry each place limits on the smallest optical signal capable of being sensed. The most fundamental of the noise limits is that of the photon shot noise, however, before a CIS can be considered as "photon shot noise limited" the readout circuitry must not add considerable noise to the signal. In the readout circuitry, the flicker noise or 1/f noise is a dominant noise source. The CIS readout path is an example where noise from a number of sources in the signal chain combines, and in most cases the noise is dominated by one of the circuit elements in the chain. In practice the readout circuitry commonly places the noise limitation on the device; however, the random telegraph signal present in deep-submicron MOSFETs used in the pixel array places an additional noise limitation especially in small pixel pitches less than 2μm and under low-light conditions.

Semiconductor materials and devices have proliferated consumer electronics and have changed the shape of information sharing and dissemination like no other technology has in human history. Solid-state technology has allowed man to explore space, create the world-wide web, and made cell phones accessible to an ever increasing portion of the world-wide population. Fundamentally all of this was made capable through the advent of one particular device, the solid-state transistor. The most desirable characteristic of a transistor is in the ability of the device to convert a small input voltage to a large current. Passing a current through a large resistor creates amplification where the small input voltage is much easier to sense and manipulate. Probably the most common use, in sheer numbers, of transistors today is for digital applications. In digital systems a transistor is simply thought of as a switch with an on or off state or high and low state. With these two states and millions of transistors logic is performed and data is added, multiplied, divided, read, and stored.

Transistors are used widely in analog systems as well. The physical world around us is innately analog. Temperature, sound, and light are examples of measureable analog quantities. Analog signals are separated from digital signal because analog signals represent continuous time quantities while digital signals are defined at discrete values for discrete time intervals. To sense an analog signal an appropriate transducer must be used to transform the physical quantity to a change in a measureable electrical quantity (i.e. current or voltage). In order to make this

transition, electronic circuits make use of transistors to provide amplification in order to measure the signal of interest.

Noise has continually been a concern in circuit and system design as noise poses a lower limit that a signal can be accurately sensed. Sources of noise come from a variety of places and each source of noise has to be investigated and handled separately as they often come from different mechanisms. In this thesis the focus in on a fundamental noise source due to physical phenomena in the transistor. Other sources of noise may be the result of the operation of the circuit and the position of components. Power supply noise is one such noise source and is generally the result from ground loops which cause spurious signals to appear on the ground or supply planes that are then coupled into the transistors that are performing the sensing operations.

With the demand for decreased power supply voltages for low-power applications and the shrinking of transistor dimensions for higher integration, noise presents a bigger challenge for analog circuit designers. In general the noise of the system becomes more difficult to mitigate as supply voltages decrease, bandwidth requirements increase, and especially when the signal of interest is small. Shrinking supply voltages poses a constraint because more and more of the available voltage is consumed by noise. High bandwidth systems will innately have noise due to the fact that in most cases the root-mean squared (RMS) of the noise is proportional to the square root of the bandwidth. When a signal is large compared to the system

noise then noise poses little problem; however, as the signal of interest becomes comparable to the noise it is increasingly difficult to distinguish between the signal and the noise and the noise in the system becomes a strict design criteria. An important metric of a circuit's small signal performance is the Signal-to-Noise Ratio (SNR). SNR is found by:

$$SNR = 20 \log \left( \frac{V_s^{RMS}}{v_n^{RMS}} \right) \tag{1.1}$$

In this case the numerator is the RMS signal voltage and the denominator is the RMS voltage of the noise. This expression calculates the margin, in decibels, between the input signal and the noise of the circuit. The larger the ratio the less the signal will be corrupted by the noise.

Today, technology allows the fabrication of MOS transistors with 32nm dimensions now in high volume manufacture. It will be shown that at these delicate sizes the noise is due to:

- 1. the effect of the random position of dopant atoms in the active region,

- 2. the few number of active traps in the oxide and,

- 3. the small number of carriers in the channel.

These properties are the primary source of the large noise levels observed in modern MOSFET technologies. Doping concentrations have increased as a necessity to maintain the threshold voltage of the transistor to an operational level;

consequentially, due to the small dimensions the total number of dopant atoms near the surface in the channel region is small. These atoms are positioned at random in the channel and create a potential landscape with peaks and valleys of high and low potential with rivers of current flowing through the valleys of the lowest barriers. Also, in and near the interface between the silicon and the gate oxide traps exist which can capture and later emit charge. This capture and emission modulates the current flowing through the channel of the device. This modulation is the low-frequency noise found in deep-submicron MOSFETs.

Low-frequency noise (LFN) is the region of noise below the corner frequency of either shot noise or thermal noise. Below the corner frequency the noise in large device dimensions is often found to increase like 1/f. This work develops a model which accounts for the physical source behind the LFN in deep submicron MOSFET devices. The central goal of the model is to provide a means to predictably reduce the noise in deep submicron and nanoscale MOSFET technology. Specifically, the noise as being effected by both random dopants and the substrate bias are taken into account. Ultimately, to keep noise levels low the dopant atoms near the surface must be minimized.

## 1.1 Organization of the Dissertation

The prime motivation behind this work is based upon the reduction of lowfrequency noise in MOSFET devices. To accomplish this, a compact model which approximates the fundamental physical nature of the low-frequency noise in MOSFETS devices is developed. The model is verified with practical applications which demonstrate a large noise reduction, not previously discovered, in both MOSFET devices and in CIS devices. The dissertation is structured as follows.

Chapter 2 provides a brief overview of noise theory in electronics. Focus will be on those noise sources that are most commonly encountered in semiconductor devices. These sources include thermal, shot, generation-recombination, 1/f, and RTS noise. Circuit implications of LFN noise in systems which employ MOS technology is discussed. These include digital systems, memories consisting of flash cells, sense amplifiers, and analog systems.

Chapter 3 discusses the methods and techniques for measuring the LFN of the MOS devices used to develop the model created in this research. Measurements of sub-micron MOSFETs will demonstrate and elucidate the reasoning behind the necessity for understanding and remediating this noise source.

Chapter 4 develops a semi-empirical compact noise model for describing those noise properties observed in Chapter 3. This noise model is presented in context of the fundamental physical mechanisms, specifically oxide traps and percolation currents, which are capable of creating the necessary fluctuations of the drain current.

Chapter 5 discusses and demonstrates two low-frequency noise reduction methods. A few methods will be briefly discussed namely switched bias. The first

noise reduction scheme that will be demonstrated is the application of substrate bias. The substrate bias is studied in a number of devices and the noise reduction of this technique is proven. Secondly, low-frequency noise reduction through decreased substrate dopant is shown in both large and small MOSFET devices.

Chapter 6 is a case study demonstrating the model resulting from this work as applied to a CMOS image sensor. This real-world application demonstrates the learning's found through the course of this research; the results of which have solved a fundamental noise issue previously not understood. With the understanding of the noise source and the application of a noise reduction technique used in Chapter 5, a scheme was adopted which significantly impacted the performance of the product resulting in a superior performing image sensor.

Chapter 7 summarizes the information provided in the dissertation and comments on those future device architectures capable of having more favorable noise performance in context of the model developed herein.

#### 2 Semiconductor Noise

Noise in electronics has been a concern for design engineers and a research interest since the conception of electrical systems. Noise in electronics is a voltage or current variation about some mean value. Thermal, shot, 1/f, and generation-recombination (GR) noise appear with a Gaussian distribution while random-telegraph noise (RTS) noise is found to be Non-Gaussian. Physical device noise is generated through processes such as the random motion, trapping, or random arrival of charge carriers. What makes understanding noise so important is that noise sets a lower limit on the capability of any particular device or circuit to reliably detect small signals.

Most often a Gaussian noise source is one that is generalized by a single parameter with no frequency dependence. Another term that can be used to qualify this type of noise is to say that it is "white" noise. White noise is characterized by the standard deviation that is in the strictest sense constant across all frequencies. The amplitude distribution of such a noise source will have a normal probability distribution.

The focus of this research is primarily on the low-frequency noise characteristics of sub-micron metal-oxide-semiconductor field effect transistors (MOSFETs). MOSFET devices serve as the work horse for most all modern

electronic devices in manufacture today. The devices are used in both digital and analog systems and it is the analog domain where noise is of utmost concern.

There are four noise sources that are important in semiconductors [1]. These noise sources are thermal, shot, GR, and 1/f noise. RTS will also be introduced as a noise source; it will be shown that it is a constituent of 1/f noise. The following sections will briefly discuss these common noise sources encountered in semiconductor devices. Emphasis is placed on the low-frequency noise in MOSFET devices.

## 2.1 Johnson-Nyquist (Thermal) Noise

Thermal noise was measured and modeled early in the infancy of electronics [2, 3]. Thermal noise is the most familiar of noise sources as it is found in all electronic devices. Thermal noise is measured as a random voltage across a resistor or in a current when passed through a resistor. It is due to the random collision of carriers with the atoms in the material. As the current moves through the resistive material, multiple collisions with the atoms of the material cause the carriers to randomly arrive at the electrodes. Thermal noise exists even in the absence of DC current. Unlike the other noise sources that will be discussed thermal noise is present at all times. The thermal noise power is expressed as:

$$i_n^2 = \frac{4kT}{R} \Delta f \tag{2.1}$$

for the current noise or for voltage noise as:

$$v_n^2 = 4kTR\Delta f \tag{2.2}$$

where k is the Boltzman constant, T the temperature in Kelvin, R the resistance of the structure or device,  $\Delta f$  is the bandwidth of the measurement.

From these equations it is seen that the noise is proportional to the resistance in the case of voltage noise and the inverse of the resistance in the case of current noise. Depending on the application the noise can be minimized by appropriate design of the resistances in the circuit.

## 2.2 Shot Noise

Walter Schottky discovered the existence of shot noise in his experiments with vacuum tubes. He discovered that electrons arrived at the cathode at different times resulting in very fast burst of current. Shot noise has been observed since the vacuum tube and is the result of discrete charge packets arriving at a point at different times.

As an example shot noise is seen in photodiodes in two forms. One, the noise due to the random arrival of photons is characterized as a shot noise process.

Two, the dark current in the device contributes shot noise since these dark current carriers are traversing the reverse bias junction and contributing to the noise fluctuation.

In bipolar junction transistors (BJT) shot noise is the dominate noise source. As in the case with the vacuum tube, a BJT has a base region where minority carriers are injected from the emitter and extracted by the collector. These minority carriers will arrive at the collector at random intervals giving rise to discrete pulses of current. At typical biases these carriers arrive in vast numbers so the time domain picture looks like the typical fuzz seen on the oscilloscope.

The equation that describes the shot noise in an electronic device is:

$$i_n^2 = 2qI \tag{2.3}$$

where q is the electron charge, 1.602e-19 and I is the DC current flowing through the device.

### 2.3 Generation-Recombination Noise

Deep levels in semiconductors are capable of causing a fluctuation in the generation, recombination, and trapping rates of charge which results in a fluctuation of the charge density [4]. This fluctuation is detected as a change in conductivity and sensed either as a current or voltage. This type of fluctuation is

called Generation-Recombination (GR) noise. This type of noise is found in the channel of JFET's, photoconductors, and semiconductor resistors [5]. For the energy level to act as a GR noise source the characteristic energy must lie relatively deep in the band gap of the semiconductor.

These deep levels can capture electrons for a time which is characteristic of the energy of the trap. During the time that the carrier remains in the trap is does not participate in conduction. A couple of events can happen while this carrier is held at the trapping site. One is that the carrier is released and in this case a current increase would result when these traps emit electrons. A second event is that the trapped carrier recombines and in effect is forever removed from conduction. At the electrodes the carriers arrive and are collected and when carriers are released there is a surge of carriers and when they are captured there is a reduction in carriers arriving at the electrodes. This generation-recombination process is described by the power spectral density:

$$S_I(f) = \frac{I_0^2}{N_0^2} S_N(f) = 4 \frac{I_0^2}{N_0^2} \overline{\Delta N^2} \frac{\tau}{1 + \omega^2 \tau^2}$$

(2.4)

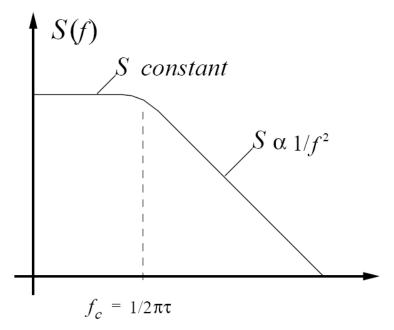

Figure 2.1 Ideal GR Noise spectrum from a single time constant

$$\tau = \frac{1}{\tau_e} + \frac{1}{\tau_c} \tag{2.5}$$

$\tau$  is the time constant of the system. The time a carrier is held in the trap is called the time-to-emission,  $\tau_e$ . The time that the carrier remains free is the time-to-capture,  $\tau_c$ . Figure 2.2 shows actual device measurements from a photoconductive sensor. The characteristics of GR noise are evident from the shape of the curve specifically the typical plateau region and the corner frequency is readily observable in the noise power spectrum.

From Figure 2.1 and 2.2, at low frequencies below the cut-off frequency,  $f_c$ , there is a plateau where the noise level is invariant with frequency. At frequencies above  $f_c$

Figure 2.2 GR Noise Spectrum of Photoconductive Device

the noise power rolls off with a  $1/f^2$  slope.  $f_c$  is dependent on the system time constant, equation 2.2, and the corner frequency is defined as:

$$f_c = \frac{1}{2\pi\tau} \tag{2.6}$$

The behavior and spectral shape of GR noise is very similar to that of an individual RTS as will be shown.

## 2.4 1/*f* Noise

1/f noise is found to exist in a number of physical processes and electronic systems. In general the power spectrum of 1/f noise is, as the name implies, proportional to the inverse of frequency [6, 7]:

$$S(f) = \frac{constant}{f} \tag{2.7}$$

Especially in semiconductors there remains controversy as to the fundamental origins of 1/*f* noise. There are two schools of thought which contributed the noise to separate mechanisms. McWhorter theorized in the middle of the 20th century that 1/*f* noise in surface dominated devices, where the current flows near the interface of an oxide-semiconductor interface, is the result of many individual trapping events that modulate the current [9]. Hooge on the other hand claims that pure or fundamental 1/*f* noise is a bulk phenomenon generated from lattice or impurity scattering causing mobility fluctuations of the charge carriers [7].

The general consensus is that 1/f is the result of conductivity fluctuations. 1/f noise in semiconductors is taken as being an instantaneous change in the conductivity of the material either through number or mobility fluctuations [1, 6].

The definition of the conductivity of a material is:

$$\sigma = q\mu n \tag{2.8}$$

where q is the elementary charge,  $\mu$  is the carrier mobility, and n is the number of free carriers. In this equation are both elements that can contribute to the measured conductivity fluctuation, number and mobility. The two schools of thought as to the absolute source of 1/f noise derive the existence of the noise from one of these two physical parameters. Whatever school of thought is adopted the generally accepted empirical formula for 1/f noise is [9]:

$$\frac{S_G}{G^2} = \frac{\alpha}{Nf} \tag{2.9}$$

Here  $\alpha$  is a fitting parameter called the Hooge parameter, N the number of charge carriers in the sample, and f the frequency. This equation serves as a basis for comparing devices of different shapes and types. All models of 1/f noise generally start from this most basic empirical equation. For instance, it will be shown that from equation 2.9 the SPICE MOSFET 1/f noise model is directly derived through substitution of the device equations.

## 2.5 Random Telegraph Signal (RTS) Noise

The source of much academic interest over the past couple decades is the random telegraph signal (RTS) seen in microstructures. RTS noise has a very similar power

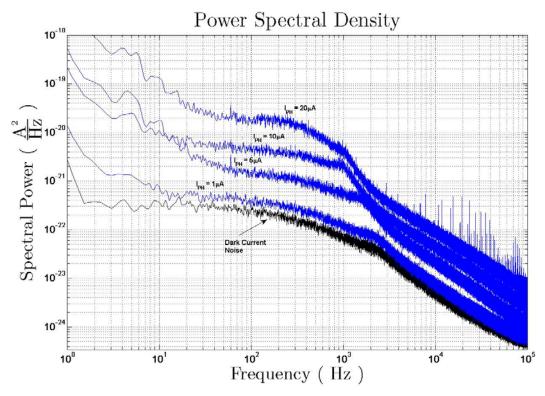

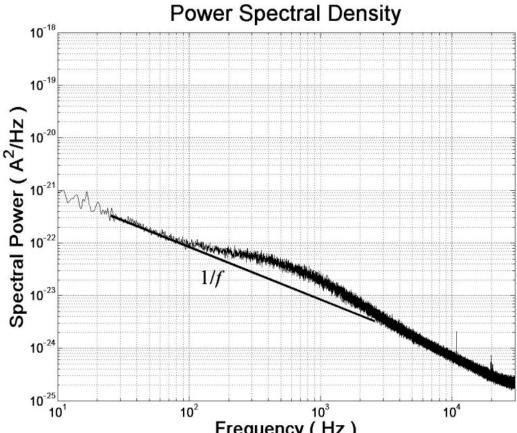

spectrum in most respects to GR noise. RTS has also been named burst or popcorn noise and fundamentally does not differ as to the origin of the noise except that RTS is considered a fundamental phenomenon while burst noise was most often associated with poor device quality. It is pretty well accepted now that the behavior of RTS is due to the capture and emission of traps near a current carrying region where the field setup by the trapped charge causes a change in the local conductivity and/or mobility. RTS has been categorized with 1/f noise due to the theoretical treatments by McWhorter and later many others that proved rather conclusively with measurement data, that a 1/f spectrum can be generated from the random capture and emission of several fluctuating traps [12-14]. Measurements performed in this research show that a 1/f spectrum is closely approximated when several RTS fluctuations are averaged together simulating what would be seen in a larger device, Figure 2.3.

Figure 2.3 1/f noise from summation of several RTS waveforms from 10 submicron devices

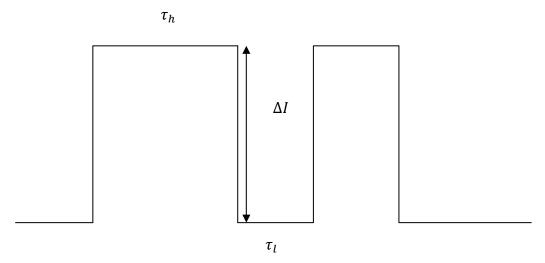

From measurement, RTS is observed as a two level fluctuation that transitions back and forth from one discrete state to another during some characteristic amount of time. The characteristic times here will be taken as the average time spent in a high or low state,  $\tau_h$  and  $\tau_l$  respectively. Figure 2.4, on the next page, shows the high and low state of this theoretical signal.

Figure 2.4 Idealized random telegraph signal

Machlup modeled the theoretical nature of a two-state fluctuation and derived that the power spectral density of this fluctuation has the form [16, 17]:

$$S(f) = \frac{4(\Delta I)^2}{(\bar{\tau}_0 + \bar{\tau}_1) \left[ \left( \frac{1}{\bar{\tau}_0} + \frac{1}{\bar{\tau}_1} \right)^2 + (2\pi f)^2 \right]}$$

2.11

This is a classical Lorentzian spectrum as also seen in GR noise, see Figure 2.1.

## 2.6 Low-Frequency Noise in MOSFETs

Low-frequency noise in metal-oxide semiconductor devices is categorized into two groups: 1/f and random telegraph noise (RTN). In the first case a measurement of the noise results in a noise power spectrum which has a 1/f slope that continues to

low frequencies. RTN on the other hand has a very different character as compared to 1/f. RTN appears with a Lorentzian shape similar to GR noise, see Figure 2.1, spectrum with a plateau and a roll off of  $1/f^{\alpha}$  with  $\alpha = 2$ . The fundamental noise mechanism behind the low-frequency noise in metal-oxide-semiconductor structures was first theorized by A.L. McWhorter [9]. McWhorter postulated that the source of the low-frequency noise was due to the interaction of surface charge with slow traps in the oxide near the interface. These interface traps had a sufficient spread in energy such that the summation of these traps spanned many decades of time constants and could account for a 1/f slope spanning many decades of frequency.

While today there remains little doubt as to the origin of 1/f noise in MOSFET devices; other theories as to the origin of 1/f noise in other semiconductor devices revolve around mobility fluctuations. These theories are primarily the result of work by F.N. Hooge [10].

## 2.6.1 1/f Noise in MOS Devices

It is well understood now that the source of 1/f noise in n-MOSFETs is due to number and mobility fluctuations [11, 15]. The number fluctuation is measured as a change in the number of carriers flowing through the device. The mobility fluctuation is taken into account in a unified model to describe the Coulombic scattering by the trapped carriers.

The SPICE NLEV=0 noise model is derived by substituting the MOSFET device equations into equation (2.9) and recognizing that  $S_G/G^2 = S_i/I^2$  in:

$$S_{i} = \frac{K_{f}\mu W \left(V_{gs} - V_{t}\right)^{2}}{2L^{3}f}$$

(2.12)

where  $K_f$  is a fitting parameter,  $\mu$  the carrier mobility, W and L the width and length of the MOSFT,  $(V_{gs} - V_t)$  the excess gate voltage above threshold. A more accurate model for the flicker noise in MOSFET's is the unified flicker noise model as developed by Hung. It is called a unified model because it brings together the correlated number and mobility fluctuations to describe the drain current modulation as [15]:

$$\frac{\Delta I_d}{I_d} = -\left(\frac{1}{\Delta N_{inv}} \frac{\delta \Delta N_{inv}}{\delta \Delta N_{it}} \pm \frac{1}{\mu_{eff}} \frac{\delta \mu_{eff}}{\delta \Delta N_{it}}\right) \delta \Delta N_{it}$$

(2.13)

The first term in 2.13 describes the number fluctuation while the second term describes the mobility fluctuations. In the linear region of operation at low drain bias the power spectral density of the drain current becomes:

$$S_{I_d} = \frac{kTI^2}{vfWL} \left(\frac{1}{N} + \alpha\mu\right)^2 N_t(E_{fn}) \tag{2.14}$$

Equation 2.14 describes the noise in the drain current of a MOSFET due to oxide traps at a particular quasi-Fermi level,  $N_t(E_{fn})$ . The theory presented in this research will taken a different approach then considering mobility degradation but instead consider the effects of the modulation of percolation currents due to the localized conductivity modulation from the field of trapped charge in the oxide.

#### 2.6.2 RTS Noise in MOS Devices

RTS noise in MOS devices has provided an interesting tool for studying the behavior of traps and poses interesting engineering challenges. It is well established now that RTS in MOS devices is the result of the capture and emission of minority charge carriers in the gate oxide of the device. There has been extensive work in modeling and understanding the mechanisms at play [13 - 24]. The action and behavior of traps is well understood, so much of the modeling has revolved around understanding the large modulation of the current that is observed in the measurements [25-28].

In general the behavior or capture and emission rates of traps are taken from considering Shockley-Reed-Hall (SRH) statistics and assuming a tunneling capture mechanism. These rates are expressed as the mean time-to-capture,  $\tau_c$ , and the mean time-to-emission,  $\tau_e$  as:

$$\tau_c = \frac{1}{n_s \sigma_n \nu_{th}} \tag{2.12}$$

where  $n_s$  is the density of carriers in the vicinity of the trap,  $\sigma_n$  is the capture cross section, and  $v_{th}$  is the thermal velocity of the carriers.

and

$$\tau_e = \frac{1}{\sigma_0 g \eta T^2} exp \left[ \frac{\Delta E_B - \Delta E_T}{kT} \right]$$

(2.13)

$\sigma_0$  is the capture cross section, g is the degeneracy fact,  $\eta$  is a device specific fitting parameter, and T the temperature in Kelvin.

These are the basic relationships that describe the trapping times and in general adequately model the behavior of the high and low time constants observed in MOSFET RTS.

Two approaches have been taken to model the RTS amplitudes. One, approach is to model the effect that a trapped charge has as imaged to the parasitic capacitances mainly those between the oxide capacitance,  $C_{ox}$ , the inversion charge capacitance,  $C_i$ , or equivalently  $q^2N_i/kT$ , and the depletion region capacitance,  $C_D$ . Assuming a number fluctuation model the drain current modulation due to the trapping of a single charge is described as:

$$\frac{\Delta I_d}{I_d} = \frac{1}{A} \frac{q\beta}{(C_{ox} + C_D + C_i)} \tag{2.14}$$

where A is the device area, and  $\beta$  is q/kT.

In the second approach a cored out area of low conductivity due to the trapped charge reduces the carrier number in the channel by an amount equal to this reduced device area. In this approach the field setup by the trapped charge creates an exclusion zone depending on the depth of the trap into the oxide and the level of inversion charge in the channel. The model for this is:

$$\frac{\Delta I_d}{I_d} = \frac{L_t}{W} \tag{2.15}$$

where  $L_t$  is the effective radius of this trapped charge field. This second approach is the foundation for model described here in Section 5. The model described in Section 5 merges both concepts to also include the non-uniform current distribution due to the effect of ionized dopant charge in the channel and bias dependence of the induced field.

## 2.7 1/f and RTS in Circuits

The following sections provide examples from published research on the impact of RTS noise in circuits. These specific examples highlight the importance of understanding this noise mechanism as it applies to MOSFET subthreshold device leakage and to bit-error rates (BER) in dynamic-random access memory (DRAM) architectures. These examples show that RTS noise plays an integral role on the performance of high density memories where noise can cause unacceptable errors if device optimizations for noise are not considered.

# 2.7.1 Subthreshold Leakage Due to 1/f and RTS Noise

Noise signals can be represented in either the frequency domain or the time domain. The modeling in the frequency domain using the SPICE model gives the mean square noise of a transistor as:

$$i_n^2 = \frac{K_f I_{ds}^{\alpha_f}}{C_{ox} L_{eff}^2 f^{e_f}}$$

(2.16)

where  $K_f$  is the 1/f noise parameter,  $L_{eff}$  the length, and W the width of the transistor channel,  $\mu$  the mobility,  $(V_{gs}-V_t)$  the excess of gate voltage above threshold, and  $e_f$ ,  $\alpha_f$  are fitting parameters. The modeling of the RTS or 1/f noise of nanoscale devices

that is easiest to understand is that done in the time domain. The capture and emission of a single electron in a nanoscale NMOS transistor of size W/L can be equated to a change in threshold voltage,  $V_T$ , as:

$$\Delta V_T = \frac{q}{C_{OX}WL} \tag{2.17}$$

where q is the electronic charge, and  $C_{\rm ox}$  is the gate capacitance. This fluctuation of the threshold voltage can modulate the surface potential causing high subthreshold leakage states.

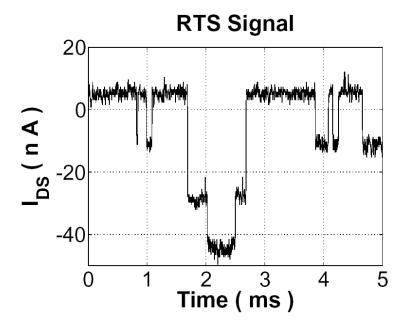

Modern devices are now small enough that we can see RTS noise signals associated with single electron trapping. RTS type traps, with single electronic charge fluctuations, are easily observable on minimum size devices which show discrete switching events in the time domain signal, Figure 2.5.

Figure 2.5 Single Electron RTS

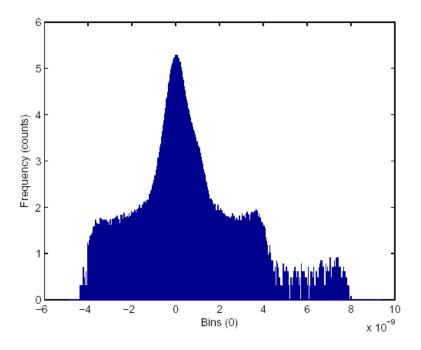

Figure 2.6 Histogram of 1/f noise from a large device

In wider devices, with dimensions greater than  $1\mu m$ , a large number of these individual RTS signals combine to give a Gaussian or Normal distribution in 1/f noise amplitudes and drain current variations, Figure 2.6. A simple estimate shows that one of these RTS traps changing charge state in the channel will modulate the subthreshold leakage as shown in Figure 2.7.

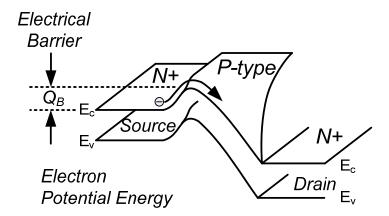

(a) Energy band diagram at the source.

(a) Charge redistribution on gate.

Figure 2.7 RTS due to traps in the channel region

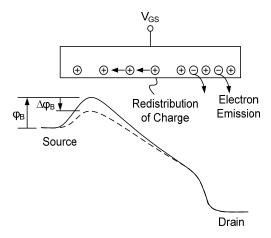

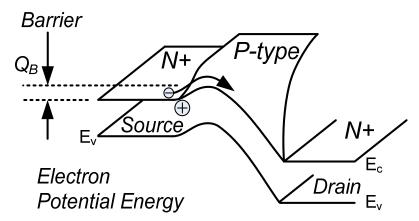

This change in oxide charge will cause a redistribution of charge on the gate and a uniform change in threshold voltage. It should be noted from [28] to quote "in Eq. 6 the subthreshold current exhibits an exponential dependence on the oxide charge. A small variation in the oxide charge can cause a significant subthreshold current transient." The subthreshold current varies as  $e^{\varphi_S}/kT$  and if there is a threshold voltage variation then as  $e^{\varphi_S}/kT$  or exponentially on the oxide charge or threshold voltage. This change in threshold voltage will result in a uniform change in the current distribution across the width of the gate and source. There can and will however be a distribution in possible magnitudes of the threshold voltage change, this is a Gaussian distribution on large devices, Figure 2.5(b). This noise current will result in a widening of the Gaussian distribution and the symmetrical wings on the bottom of the distribution as shown in Figure 2.8.

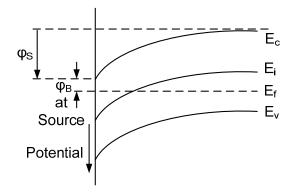

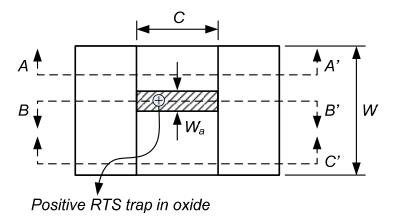

A trap near the source will be most effective in modulating the subthreshold leakage since only the surface potential near the source determines the number of carriers in the subthreshold equation. A local change in the surface potential barrier at the source could easily cause a large modulation in the localized subthreshold leakage. Figure 2.7(a) demonstrates a strip model with a positive oxide trap. The current flow through this strip can be fully or partially modulated by the capture and emission of charge at the trap site. Outside of the strip the surface potential is determined by the barrier at the source due to the doping of the channel and the charge on the gate. Figure 2.7(b) shows an increased barrier as compared to Figure

2.7(c). In Figure 2.7(c) the barrier is reduced by the positively charged trap in the gate oxide. This reduced barrier causes an exponential increase in the current under the gate until a carrier is captured which increases the local potential barrier and instantaneously reduces the current flow. The localized conduction channels are the cause of large amplitude subthreshold current changes and distort the Gaussian distribution.

## (a) Strip model of MOSFET channel region

## (b) Cross section A-A' and C-C'

(c) Cross section B-B'.

Figure 2.8 RTS model for subthreshold leakage

In the case of submicron size devices subthreshold leakage is critical in determining the retention time of DRAM's. Published results show a nominal RTS threshold voltage threshold voltage step of 10mV on a minimum size device in a 90 nm technology with 9nm gate oxides [29]. For 50 nm technology with 2 nm gate oxides and a transistor size of  $W/L = 0.5\mu/0.5\mu$  this translates into a similar threshold voltage distribution if we assume the 1/f noise varies according to the SPICE noise level 0 model. Most minimum size 50 nm x 50 nm will have on the average four traps. The probability of a RTS trap near the source is low. However, if a single electron RTS trap near the source changes charge state to a more positive charge state this in turn modulates the local surface potential barrier near the source as shown in Figure 2.8. This changes the subthreshold leakage exponentially in the local region. The resulting localized channel or percolation channel can result in a large current change and an asymmetrical distortion of the distribution, Figure 2.9.

Figure 2.9 Drain current distributions on a nanoscale 0.2um transistor

In Figure 2.9 there is a low but finite probability of 8 nA current pulses About 1/100,000 RTS noise signals will be a multiple electron event resulting in a large leakage current pulse about forty times the amplitude of the RMS variation. Even larger subthreshold current pulses will occur but at a lower probability. The magnitude in Figure 2.9 suggest a percolation channel a few Angstoms wide.

A random and variable error occurring in the transfer device due to subthreshold leakage from RTS or 1/f noise can cause errors or variable retention time in memory cells. There is a low but finite probability of large amplitude current pulses in the subthreshold leakage of nanoscale transistors which assuredly will cause errors in reading the small voltage levels in high-density memories.

## 2.8 RTS Noise in MOSFET circuits

## 2.8.1 RTS Noise in Sense Amplifiers

An analysis has previously been made of the increasing portion of the threshold voltage being occupied by thermal noise levels and the bit error rates in digital logic [30] and memory circuits [31-33]. No consideration was, however, given to the errors that might be caused by 1/f noise or random telegraph signals.

Figure 2.10 RTS signal due to trapping and emission of multiple electrons in a nanoscale n-channel CMOS transistor.

# 2.8.2 1/f Noise

1/f noise signals are typically modeled in the frequency domain. The SPICE noise level 0 model for a device in saturation, gives the mean square noise current of the read transistor as shown in (2.18) below:

$$i_n^2 = K_f \mu W (V_{gs} - V_T)^2 / (2L^3 f)$$

(2.18)

where,  $K_f$  is a 1/f noise fitting parameter mostly dependent on process, L is the length, W the device width and,  $\mu$  the mobility. The voltage read error due to the 1/f noise current in (2.18) of a sense amplifier transistor can be expressed as:

$$\Delta V = \frac{\sqrt{\int_{f_l}^{f_h} i_n^2 df \, \Delta t}}{C_{hit}} \tag{2.19}$$

and substituting equation 2.18 into 2.19 results in the read error voltage for a particular device size and process conditions.

$$\Delta V = \frac{\left(\left(\frac{K_f W \mu}{2L^3}\right) ln\left(\frac{f_h}{f_l}\right)\right)^{1/2} (V_{gs} - V_t) \Delta t}{C_{bit}}$$

(2.20)

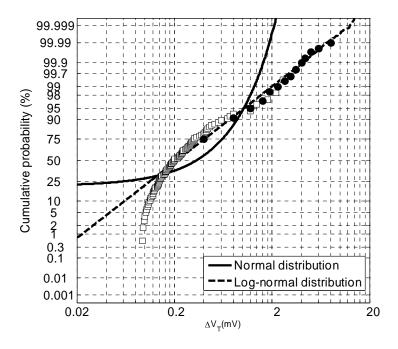

where  $f_l$  and  $f_h$  are the low and high frequency bandwidth limits,  $\Delta t$  is the access time of the signal at the sense amplifier, and  $C_{bit}$  the bit line capacitance. This average or mean error signal will be small of the order mV. This however is the mean read error voltage; there is small but finite probabilities of much larger read errors, such as tens of mV, see Figure 2.11.

The probability that there will be a coincidence of occurrence of a number of

Figure 2.11 Calculated threshold voltage distributions on a 50nm transistor with a 2nm gate oxide and gate width, W=2500 nm or W=2.5 $\mu$ m, a very wide device, data taken from [29].

electrons contributing to a large change in threshold voltage and causing an error has been found to be described by a log-normal distribution. In a log-normal distribution the probability of a large value is of the order  $e^{(-x)}$ .

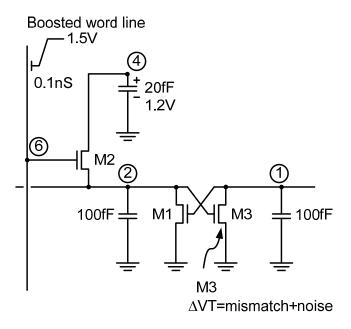

Figure 2.12 shows a simplified representation of a sense amplifier in a dynamic random access memory (DRAM). The charge stored on the storage capacitor is discharged on to the bit line when the word line is activated. This causes a signal to be applied to the cross coupled sense amplifier. This signal appears as a differential signal and causes an imbalance in the sense amplifier which is amplified.

Figure 2.12 Circuit diagram of a simplified sense amplifier.

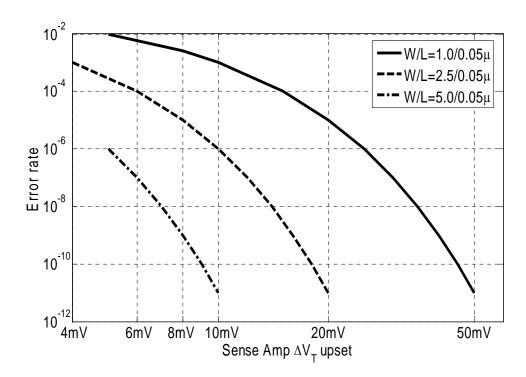

RTS noise signals also, however, appear as an offset causing an imbalance in the sense amplifier. If these two signals have opposite polarities than the noise signal can be dominant causing an upset of the sense amplifier and erroneous output. Figure 2.13 illustrates the sensitivity of the sense amplifier to noise signals and gives the change in threshold voltage caused by noise which will upset the sense amplifier causing an error [35-37].

The sensitivity of the sense amplifier is affected by the time delay over which the noise has had an opportunity to determine the output state. A representative value is that about a 20 mV threshold voltage offset is sufficient to cause an error if this delay is 100 ps.

Figure 2.11 shows there is about a 0.001% probability, or 10<sup>-5</sup> probability of an 8mV threshold shift in the transistors due to RTS noise. A 20mV threshold voltage shift causing an error will occur with a probability of about 10<sup>-11</sup>. This is still a high error rate for modern high-density memories so that a proper design would require larger device widths to reduce the error rate. Similar calculations can be made for other device sizes or width to length ratios.

If a DRAM sense amplifier is upset by a threshold voltage mismatch of  $\Delta V_T$  then Figure 2.13 shows the calculated error rate. In reality there may not be an error or variable retention time in the memory cell but rather a random and variable error occurring in the sense amplifier due to RTS or 1/f noise. This could happen as often as every time a Gbit DRAM is read without proper design and consideration of RTS noise.

Figure 2.13 Error rate on a DRAM sense amplifier due to upset by  $V_T$  mismatch for different W/L values.

#### References

- [1] F.N. Hooge, "1/f noise sources," IEEE Transactions on Electron Device, vol. 41, no. 11, pp. 1926-1935, November 1994.

- [2] J. Johnson, "Thermal Agitation of Electricity in Conductors," Physical Review, vol. 32, p. 97, 1928.

- [3] H. Nyquist, "Thermal Agitation of Electric Charge in Conductors," Physical Review, vol. 32, p.110, 1928.

- [4] K.M. Van Vliet, "Noise in Semiconductors and Photoconductors," Proceedings of the IRE, vol. 46, no. 6, pp. 1004 1018, June, 1958.

- [5] C.F. Hiatt, A. Van Der Ziel, and K.M. Van Vliet, "Generation-Recombination Noise Produced in the Channel of JFET's," IEEE Transactions on Electron Devices Correspondence, August, 1975.

- [6] Marvin S. Keshner, "1/f Noise," Proceedings of the IEEE, vol. 70, no. 3, pp. 212-218, March 1982.

- [7] P. Dutta and P.M. Horn, "Low-frequency fluctuations in solids: 1/f noise," Reviews of Modern Physics, vol. 53, no. 3, pp. 497-516, July 1981.

- [8] Albert van der Ziel, "Unified Presentation of 1/f Noise in Electron Devices: Fundamental 1/f Noise Sources," Proceedings of the IEEE, vol. 76, no. 3, March 1988.

- [9] A. L. McWhorter, "1/f noise and germanium surface properties," Semiconductor Surface Physics, University of Pennsylvania, 1957, pp. 207-228.

- [10] F.N. Hooge, "1/f noise is no surface effect," Physics Letters, vol. A-29, p.139, 1969.

- [11] L. K. J. Vandamme, Xiaosong Li, and Dominique Rigaud, "1/f Noise in MOS Devices, Mobility or Number Fluctuations?" IEEE Transaction Electron Devices, vol. 41, no.11, pp. 1936-1945, November 1994.

- [12] C.T. Rogers and R.A. Buhrman, "Composition of 1/f in Metal-Insulator-Metal Tunnel Junctions," Physical Review Letters, vol. 53, no. 13, pp. 1272 1275, 24 September 1984.

- [13] K. S. Ralls, W.J. Skocpol, L.D. Jackel, R.E. Howard, L. A. Fetter, R. W. Epworth, and D. M. Tennant, "Discrete Resistance Switching in Submicrometer Silicon Inversion Layers: Individual Interface Traps and Low-Frequency (1/f?) Noise," Physical Review Letters, vol. 52, no. 3, pp. 228-231, 16 January 1984.

- [14] M. J. Uren, D. J. Day, and M. J. Kirton, "1/f and random telegraph noise in silicon metal-oxide-semiconductor field effect transistors," Applied Physics Letters, vol. 47, no. 11, pp. 195 1197, 1 December 1985.

- [15] Kwok K. Hung, Ping K. KO, Chenming Hu, and Yiu C. Cheng, "A Unified Model for the Flicker Noise in Metal-Oxide-Semiconductor Field-Effect

- Transistors," IEEE Transactions on Electron Devices, vol. 37, no. 3, pp. 654 665, March 1990.

- [16] Stefan Machlup, "Noise in Semiconductors: Spectrum of a Two-Parameter Random Signal," Journal of Applied Physics, vol. 25, no. 3, p.341, March 1954.

- [17] Shuo-Tung Chang and N.M. Johnson, "Capture and emission of electrons by deep level in ultrathin nitride oxides on silicon," Applied Physics Letters, vol. 44, no. 3, 1 February 1984.

- [18] M. J. Kirton and M. J. Uren, "Noise in solid-state microstructures: A new perspective on individual defects, interface states, and low-frequency (1/f) noise," Advances in Physics, vol. 38, no. 4, pp. 367-468, 1989.

- [19] Eddy Simeon, Bart Dierickx, Cor L. Claeys, and Gilbert J. Declerck, "Explaining the Amplitude of RTS Noise in Submicrometer MOSFET's," IEEE Transactions on Electron Devices, vol. 39, no. 2, February 1992.

- [20] Ming-Horn Tsai, T.P. Ma, and Terence B. Hook, "Channel Length Dependence of Random Telegraph Signal in Sub-Micron MOSFET's," IEEE Electron Device Letters, vol. 15, no. 12, pp. 504-506, December 1994.

- [21] Zhongming Shi, Jean-Paul Mieville, and Michael Dutoit, "Random Telegraph Signals in Deep Submicron n-MOSFET's," IEEE Transactions on Electron Devices, vol. 41, no. 7, pp.1161-1167, July 1994.

- [22] H.H. Mueller and M. Schulz, "Conductance Modulation of Submicrometer Metal-Oxide-Semiconductor Field-Effect Transistors by Single-Electron Trapping," Journal of Applied Physics, vol. 79, no. 8, 15 April 1996.

- [23] Y. Yuzhelevski, M. Yuzhelevski, and G. Jung, "Random telegraph noise analysis in time domain," Review of Scientific Instruments, vol. 71, no. 4, p. 1681, April 2000.

- [24] Godoy, F. Gamiz, A. Palma, J.A. Jimenez-Tejada, and J.E. Carceller, "Random telegraph signal amplitude in submicron n-channel metal oxide semiconductor field effect transistors," Applied Physics Letters, vol. 70, no. 16, pp. 2153 2155, 21 April 1997.

- [25] Scott T. Martin, G.P. Li, Eugene Worley, and Joe White, "The Gate Bias and Geometry Dependence of Random Telegraph Signal Amplitudes," IEEE Electron Device Letters, vol. 18, no. 9, pp. 444-446, September 1997.

- [26] Asen Asenov, Ramesh Balasubramanian, Andrew R. Brown, and John H. Davies, "RTS Amplitudes in Decananometer MOSFETs: A 3-D Simulation Study," IEEE Transactions on Electron Devices, vol. 50, no. 3, pp. 839-845, March 2003.

- [27] Lu-Ping Chiang, N.K. Zous, Tahui Wang, T.E. Chang, and K.Y. Shen, "Field and Temperature Effects on Oxide charge Detrapping in a Metal-Oxide-Semiconductor Field Effect Transistor by Measuring a Subthreshold Current Transient," Applied Physics Letters, vol. 71, no. 8, 25 August 1997.

- [28] N. Tega, et. al, "Anomalously Large Threshold Voltage Fluctuation by Complex Random Telegraph Signal in Floating Gate Flash Memory," in IEEE International Electron Device Meeting, San Francisco, USA, December 2006, paper 18.4.

- [29] L.B. Kish, "End of Moore's Law: Thermal (noise) Death of Integration in Micro and Nano electronics," Physics Letters, vol. A, no. 305, pp.144-149, 2002.

- [30] L. Forbes, M. Mudrow and W. Wanalertlak, "Thermal Noise and Bit Error Rate Limits in Nanoscale Memories," IEE Electronics Letters, vol. 42, no. 5, pp. 279-280, March 2006.

- [31] M. Mudrow, W. Wanalertlak and L. Forbes, "Power Dissipation and Temperature Variations in Nanoscale Devices," in IEEE Workshop on Microelectronics and Electron Devices, Boise, April 2006, pp. 39-40.

- [32] L. Forbes, M. Mudrow and W. Wanalertlak, "Technique for Time and Frequency Dependent Solutions of the Diffusion Equation: Application to Temperature of Nanoscale Devices," NanoTech, Boston, USA, 7-11 May 2006, vol. 3, pp.78-81.

- [33] R. Kraus, "Analysis and Reduction of Sense-Amplifier Offset," IEEE Journal of Solid-State Circuits, vol. 24, no. 4, pp.1028 1033, Aug. 1989.

- [34] R. Sarpeshkar, J.L. Wyatt Jr., N.C. Lu, P.D. Gerber, "Mismatch Sensitivity of a Simultaneously Latched CMOS Sense Amplifier," IEEE Journal of Solid-State Circuits, vol. 26, no. 10, pp. 1413 1422, Oct. 1991.

- [35] J. Vollrath, "Signal margin analysis for DRAM sense amplifiers," in Proceedings First IEEE International Workshop on Electronic Design, Test and Applications, January 2002, pp. 123-127.

- [36] Gray, Hurst, Lewis, and Meyer, "Analysis and design of analog integrated circuits," John Wiley and Sons, Inc., 4<sup>th</sup> ed., pp. 748-758, 2001.

#### **3 RTS Noise Measurement Methods**

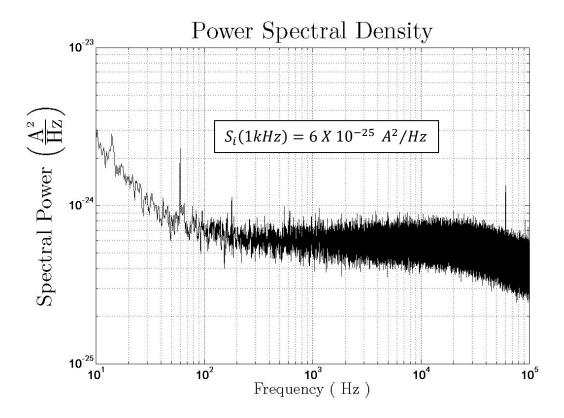

Interesting information about the traps that exists in the MOSFET system is readily obtained through RTS noise analysis. Especially with large RTS swings the ability to capture these events is not difficult. RTS noise analysis on deep-submicron devices first requires a noise measurement system with sufficient bandwidth and gain to capture the transitions of the random telegraph signal above the background noise, or noise floor, of the test system. A system bandwidth of 30 kHz is most often sufficient to accomplish this as well as a system noise floor of 1 x 10<sup>-25</sup> A<sup>2</sup>/Hz. The highest possible bandwidth and a noise floor below that of the device under test is a basic requirement for any noise measurement system.

The MOSFET devices used during the course of this study were acquired from MagnaChip Semiconductor of America. These devices are manufactured using a  $0.11\mu$  CMOS process. The process followed a standard twin-well CMOS flow. A twin well process is such that each device type is fabricated in a well of dopant which raises the doping level of the substrate higher than what is found in the bulk substrate. The well implant raises the background doping level from 1 x  $10^{15}$  #/cm<sup>3</sup> to 1 x  $10^{17}$  #/cm<sup>3</sup>. After the well has been formed there are two additional implants which serve as the anti-punch through and the threshold adjustment. The primary focus was on the devices that are used in the pixel of a CMOS image sensor (CIS) and in particular the source follower transistor. For the

noise measurements the devices were biased in a manner representative of typical operation. The typical bias currents for these devices ranged from  $1\mu A$  -  $5\mu A$ .

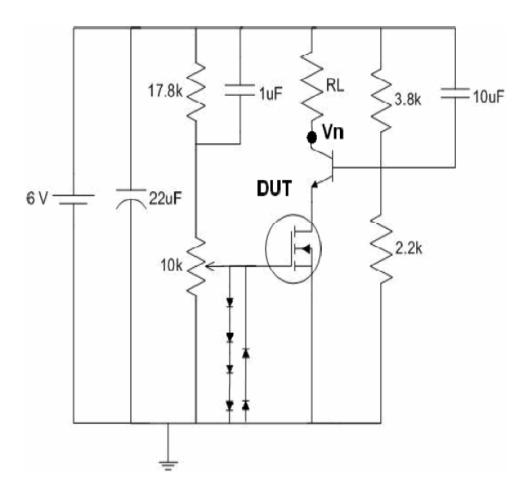

### 3.1 Noise Test System

The primary concern in the design of a noise test system is that the system be capable of measuring the low-level fluctuations which are usually buried in a dc current or voltage level and have sufficient bandwidth to characterize the noise over some span of frequencies. For the noise study carried out in this research a basic low noise system was constructed which consisted of a battery powered bias circuit, sense resistor, PAR 113 low-noise amplifier, 16-bit analog-to-digital converter, and finally a PC to capture and record the data to disk for later post-processing. In some instances a transimpedance amplifier circuit was also used to measure the noise current through the device. The bias circuit was fabricated on a custom printed circuit board (PCB). Figure 3.1 is a schematic of the circuit used for the biasing of the DUT. Fast diodes are used to protect the gate of the DUT for both positive and negative voltages as well as from electrostatic discharge. The current noise of the DUT is measured across the sense resistor, RL, at the node Vn. The noise signal is then fed into the low-noise amplifier (LNA). The LNA is capable of providing gain and bandwitdth limits to the input signal. The output of the amplifier drives a 16-bit National Instruments USB-6251 Data Acquisition System. Inside the PC the data is captured and stored for post processing to include statistical analysis and noise power spectrum generation.

Figure 3.1 DUT bias circuit schematic

At the time of measuring the noise of the device the magnitude of the device noise is unknown, so one approaches the characterization of the test system by first measuring the noise floor of the system using a known quantity or standard with confidence. A good standard is a resistor, typically a wire wound or metal film, or a

reverse biased diode that has been independently measured. The standard is then placed in the signal chain in place of the DUT. This research made use of resistor measurements to determine both the noise floor and signal bandwidth of the overall

Figure 3.2 Measure background noise using a  $100k\Omega$  metal film resistor in place of device and a  $100k\Omega$  biased at  $5\mu A$ .

test system. The background noise was measured with a  $100k\Omega$  resistor in place of the DUT as shown in Figure 3.2. Upon analysis of the noise it is found that the noise of the system is 2X higher than expected from the measurement of a  $100k\Omega$  resistor alone; however, this has shown to be more than sufficient for detection of

RTS signals. The sense resistor contributes additive noise to the measurement.

Combining the two thermal noise sources total expected noise is:

$$S_i = 2i_n^{thermal} = 2(1.66 \, X \, 10^{-25}) = 3.33 \, X \, 10^{-25} \, A^2/Hz$$

(3.1)

From the noise spectral plot of Figure 3.2, the high frequency bandwidth of the system can is deduced from the -3dB point to be 30 kHz. The bandwidth of the system was also verified through frequency sweep analysis to be 30 kHz when a  $100 \mathrm{k}\Omega$  sense resistor is used in place of the device.

The DUTs were all mounted in 24-pin Dual In-line Packages (DIP). The DIP package was seated into a 24-pin zero-insertion force (ZIF) socket for connection to the PCB bias circuitry. The ZIF socket allowed the easy removal of devices for testing of multiple packages.

#### 3.2 Device Under Test

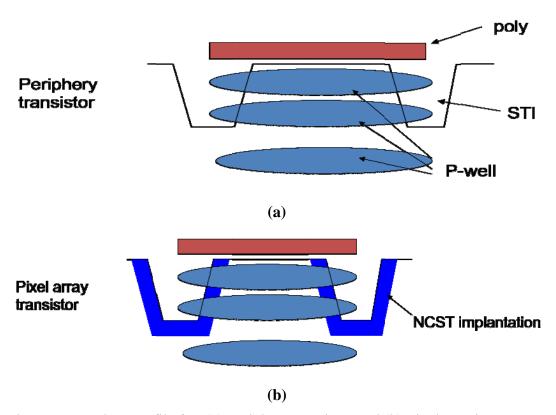

The devices that were tested during the course of this research primarily consisted of those transistors found in the array of 4T CMOS image sensor pixel architecture, specifically the source follower. The 4T architecture consists of a photodiode, transfer gate, reset, source follower amplifier, and row select transistors. The source follower is the transistor that performs the charge to voltage conversion and will be further described in section 6. A large majority of the noise testing focused around

the characterization of the source follower transistors. In a typical 4T CIS process the array and periphery use different devices. The primary difference between the pixel array transistors and those found in the periphery is an implant into the sidewall of the shallow trench isolation (STI) region; see Figure 3.3(b). This implant which is known as a channel-stop implant (CST) which effectively raises the threshold voltage for that region is for suppressing any parasitic MOSFET which might form under the trench. Another primary benefit of this implant is that the dark current, which may be generated by defects at the silicon-oxide interface, is reduced increasing the overall SNR and dark current of the pixel. One other important difference is the thickness of the gate oxide. The array transistors were manufactured with a 65 angstrom effective gate oxide while the periphery used a 32 angstrom effective gate oxide thickness. This difference in the gate oxides stems from the voltage requirements on the array which allows the use of up to 3.6V while the logic core uses a much lower supply voltages of 1.8V for the digital functionality of the device.

The test structures measured for this research contained the individual transistors which came from a number of locations across the wafer. The current baseline for the array design utilized a  $0.36\mu$  x  $0.36\mu$  sized devices. This particular transistor size was of interest, so the majority of the experimental results come from these transistors sizes. Figure 3.3, on the next page, shows the general device structure. In this process the shallow-trench isolation (STI) is formed first, followed

by the NCST implant and deep p-well implants. The STI is then filled with oxide and a sacrificial oxide is grown. Next anti-punch through and threshold implants are performed. The sacrificial oxide is then removed and the gate oxides are grown. Finally, poly is deposited and implanted to form the gate metal.

Figure 3.3 Implant Profile for: (a) Periphery transistor and (b) Pixel transistor.

### 3.3 Time Domain Noise

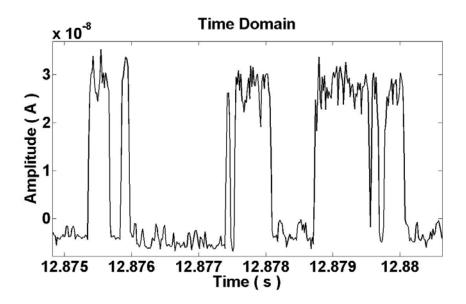

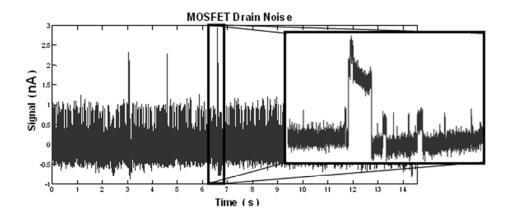

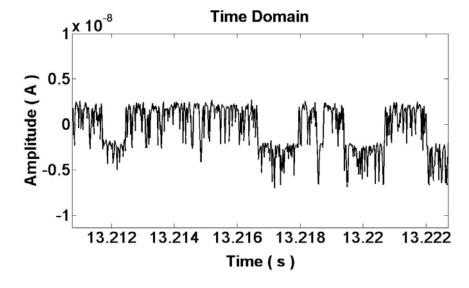

The drain current of a DC biased submicron MOSFET transistor exhibits discrete switching events as seen in Figures 3.4 and 3.5, on the next page. Each of these