### AN ABSTRACT OF THE DISSERTATION OF

Kevin A. Stewart for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and Computer</u> Engineering presented on August 22, 2017.

Title: Assessment of High Mobility Oxide Thin-Film Transistors

Abstract approved: \_\_\_\_

John F. Wager

The trend towards higher resolution, faster refresh rate active-matrix liquid-crystal displays (AMLCDs) as well as the emergence of active-matrix organic light-emitting diode (AMOLED) displays is driving the demand for amorphous oxide semiconductor thin-film transistors (AOS TFTs) with higher mobility. A physics-based model for carrier transport in an amorphous semiconductor is developed to estimate the mobility limits of an AOS TFT to be 71 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>. Only the effective mass and band tail state density need to be specified, relating to the disorder in the amorphous semiconductor. Three ways are identified to achieve a mobility higher than that of quaternary amorphous indium gallium zinc oxide (a-IGZO) with a cation ratio of 1:1:1. i) Quaternary systems with a higher indium ratio; ii) lower disorder ternary oxides (e.g., boron indium oxide); iii) dual active layer (DAL) TFTs. ITO-IGZO DAL TFT exhibits significantly improved performance with mean mobility of 31 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, threshold voltage of -3.6 V, sub-threshold swing of 175 mV/dec, minimal hysteresis, and good

bias temperature stress stability. Technology computer aided design (TCAD) simulation is used to elucidate the density of states (DOS) of various types of AOS TFTs. A mapping technique is introduced to relate experimental transfer characteristics to the sub-bandgap DOS model. <sup>©</sup>Copyright by Kevin A. Stewart August 22, 2017 All Rights Reserved

## Assessment of High Mobility Oxide Thin-Film Transistors

by

Kevin A. Stewart

### A DISSERTATION

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented August 22, 2017 Commencement June 2018  $\frac{\text{Doctor of Philosophy}}{\text{August 22, 2017.}} \text{ dissertation of } \underline{\text{Kevin A. Stewart}} \text{ presented on }$

APPROVED:

Major Professor, representing Electrical and Computer Engineering

Director of the School of Electrical Engineering and Computer Science

Dean of the Graduate School

I understand that my dissertation will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my dissertation to any reader upon request.

### ACKNOWLEDGEMENTS

I would like to thank my major advisor Dr. John Wager for giving me the opportunity to work on this project and for the continued support and guidance during my graduate education.

The work on novel AOS materials would not have been possible without my project partner Vasily Gouliouk in the Chemistry Department. I would like to thank Vasily for the fabrication of the sputter targets, training me on the x-ray diffractometer, and working together to create a presentation of the research results every month. Thanks to Dr. Douglas Keszler for being the co-advisor on the project and bringing in new, innovative ideas.

Thank you to everyone from the Wager group for their technical contributions to this work as well as making this a pleasant environment to work in. The same is true for the other folks who work in the office and labs. No mention of the lab can go without giving a special thanks to Chris Tasker and Rick Presley for bringing up new tools, keeping the existing tools running, and their great hands-on training.

Finally, I would like to thank Dr. Robert Manley of Thin Films Research, Corning Incorporated for the support of this project.

This work was funded by Corning Incorporated.

# TABLE OF CONTENTS

| 1 | IN  | TRODUCTION                                         | 1                                |

|---|-----|----------------------------------------------------|----------------------------------|

| 2 | BA  | ACKGROUND AND LITERATURE REVIEW                    | 3                                |

|   | 2.1 | Flat-Panel Displays                                | ${3 \atop {4 \atop {5}}}$        |

|   | 2.2 | Thin-Film Transistors                              | 7<br>8<br>10                     |

|   | 2.3 | Amorphous Oxide Semiconductors                     | 12<br>15<br>18                   |

|   | 2.4 | High Mobility Reports                              | 20<br>20<br>23                   |

| 3 | M   | OBILITY LIMITS CONSIDERATIONS                      | 26                               |

|   | 3.1 | Amorphous Semiconductor Mobility Limits            | 27<br>38<br>40                   |

|   | 3.2 | Single-Crystal Polar Semiconductor Mobility Limits | 41                               |

|   | 3.3 | Doping and Polycrystalline Considerations          | 46                               |

|   | 3.4 | Conclusion                                         | 49                               |

| 4 | ЕХ  | XPERIMENTAL METHODS                                | 50                               |

|   | 4.1 | Fundamentals of Vacuum Technology                  | 51<br>51<br>55                   |

|   |     | Thin Film Deposition and Analysis                  | 58<br>58<br>62<br>64<br>65<br>67 |

|   | 4.3 | Device Fabrication and Electrical Characterization | 68                               |

# TABLE OF CONTENTS (Continued)

|                                                                                                            | Page   |

|------------------------------------------------------------------------------------------------------------|--------|

| 4.3.1 Device Fabrication                                                                                   | 68     |

| 4.3.2 Transfer Curve Assessment                                                                            |        |

| 4.3.3 Output Curve Assessment                                                                              | 72     |

| 5 BORON INDIUM OXIDE THIN-FILM TRANSISTORS                                                                 | 74     |

| 5.1 Introduction                                                                                           |        |

| 5.2 Thin Film Characterization                                                                             |        |

| 5.3 Device Characterization                                                                                |        |

|                                                                                                            |        |

| 5.4 TCAD Simulation                                                                                        |        |

| 5.5 Conclusion $\ldots$   | 85     |

| 6 DUAL ACTIVE LAYER THIN-FILM TRANSISTORS                                                                  | 87     |

| 6.1 Introduction $\ldots$ | 87     |

| 6.2 Thin Film Characterization                                                                             | 90     |

| 6.3 Device Characterization                                                                                | 94     |

| 6.4 TCAD Simulation                                                                                        | 99     |

| 6.4.1 Mapping Technique                                                                                    |        |

| 6.4.2 Simulation Discussion                                                                                |        |

| 6.5 A Novel DAL TFT Concept                                                                                | 108    |

| 6.6 Conclusion $\ldots$   | 112    |

| 7 CONCLUSIONS AND RECOMMENDATIONS FOR FUTURE WOR                                                           | RK 113 |

| 7.1 Conclusions $\ldots$  | 113    |

| 7.2 Recommendations For Future Work                                                                        | 114    |

| APPENDICES                                                                                                 | 116    |

| A Additional Literature Data                                                                               |        |

| B Additional Experimental Data                                                                             |        |

| C Boron Indium Oxide TCAD Simulation Code                                                                  |        |

|                                                                                                            |        |

| D Dual Active Layer TCAD Simulation Code                                                                   | 122    |

|                                                                                                            |        |

## LIST OF FIGURES

| Figure |                                                                                                                                                                                                                                                                      | Page    |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

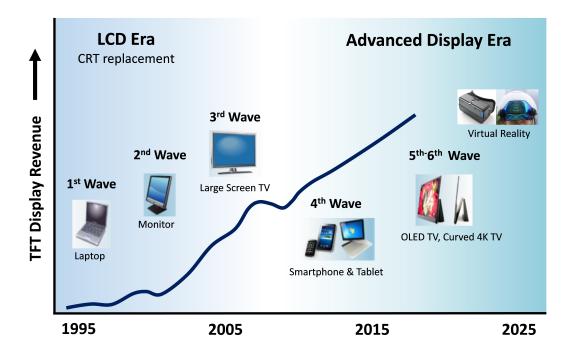

| 2.1    | Timeline of TFT-based flat-panel display technologies at point of wide-<br>spread adoption. With data from IHS DisplaySearch, Applied Materi-<br>als, and Intel.                                                                                                     | 4       |

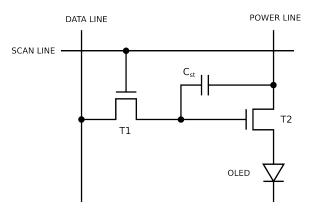

| 2.2    | A simple pixel circuit for an AMOLED display. $T1$ is a switching transistor, $T2$ is a driving transistor, and $C_{st}$ is a storage capacitor. Figure reproduced from Ref. [1]                                                                                     |         |

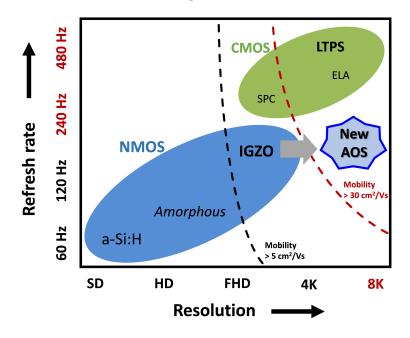

| 2.3    | Current TFT semiconductors used in mass-production are a-Si:H, LTP-S, and a-IGZO. Required mobility increases with refresh rate and resolution. Adapted from Kwon and Jeong [2].                                                                                     | 6       |

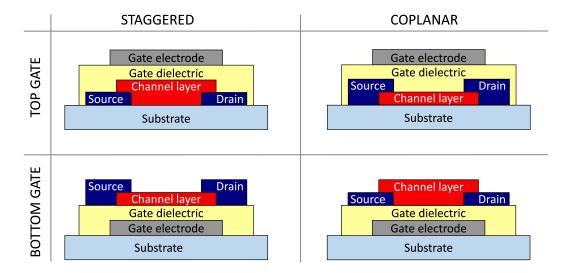

| 2.4    | Staggered top gate, coplanar top gate, staggered bottom gate, and coplanar bottom gate device structures                                                                                                                                                             | 8       |

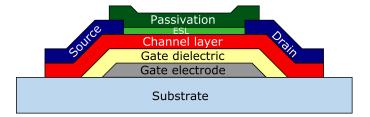

| 2.5    | Staggered bottom gate TFT structure typically used in mass-production                                                                                                                                                                                                | ı.<br>9 |

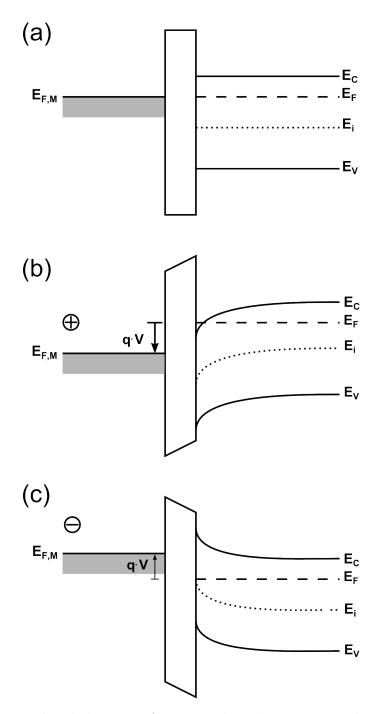

| 2.6    | Energy band diagrams for a metal-insulator-semiconductor (M-I-S) ca-<br>pacitor. The n-type semiconductor is in (a) equilibrium when no bias<br>is applied, (b) accumulation when a positive bias is applied, and (c) de-<br>pletion when a negative bias is applied | 11      |

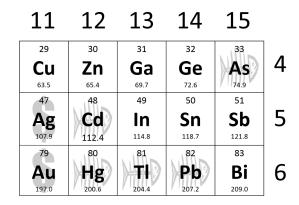

| 2.7    | The portion of the periodic table proposed for selecting AOS cations.<br>As, Cd, Hg, Tl, and Pb are usually not used due to their toxicity. Ag<br>and Au are costly. Figure adapted from Refs. [3, 4]                                                                | 12      |

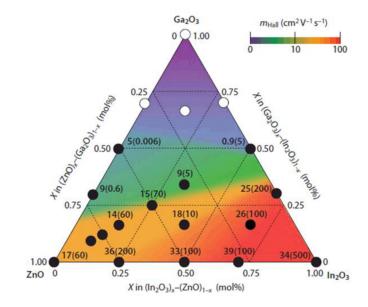

| 2.8    | Hall mobility and carrier concentration of the $In_2O_3$ -Ga <sub>2</sub> O <sub>3</sub> -ZnO system. The Hall mobility is in units of $cm^2V^{-1}s^{-1}$ and the carrier concentration (in parentheses) is in units of $10^{18}$ cm <sup>-3</sup> [5]               | 14      |

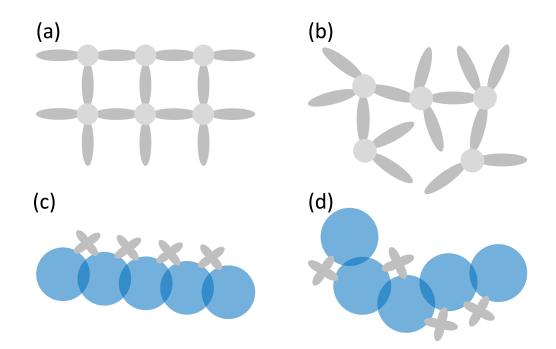

| 2.9    | Schematic illustration of orbitals for (a) crystalline covalent, (b) amorphous covalent, (c) crystalline ionic, and (d) amorphous ionic semiconductors.                                                                                                              | 14      |

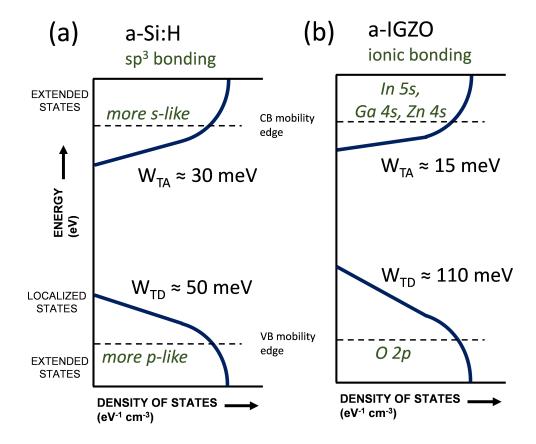

| 2.10   | (a) a-Si:H and (b) a-IGZO band-tail state Urbach energy influenced by bonding type.                                                                                                                                                                                  | 16      |

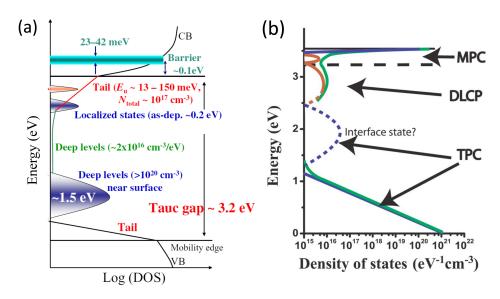

| 2.11   | Proposed AOS DOS model for (a) a-IGZO $[6,7]$ and (b) a-ZTO $[8].$ .                                                                                                                                                                                                 | 17      |

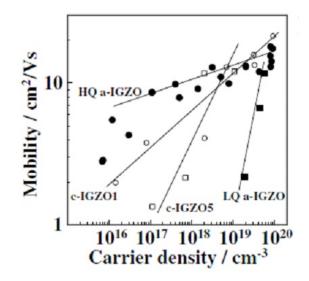

| 2.12   | Hall mobility versus carrier concentration for crystalline and amorphous IGZO with varying deposition conditions [7]                                                                                                                                                 | 19      |

| Figure |                                                                                                                                                                                                                                                                                                      | Page |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

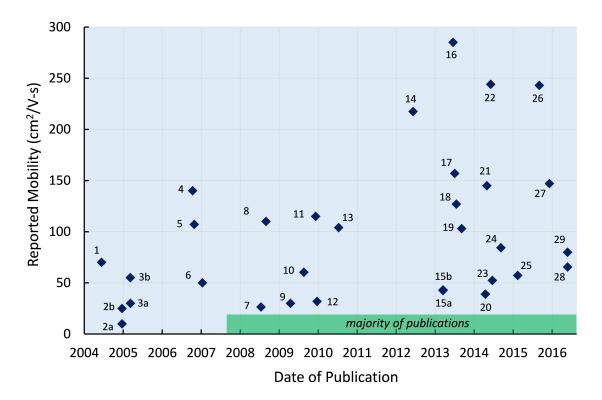

| 2.13   | High mobility reports of SAL oxide TFTs. Numbers correspond to the ID column in Table 2.1.                                                                                                                                                                                                           | 21   |

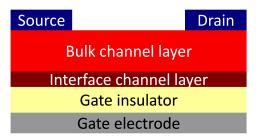

| 2.14   | Dual active layer structure                                                                                                                                                                                                                                                                          | 23   |

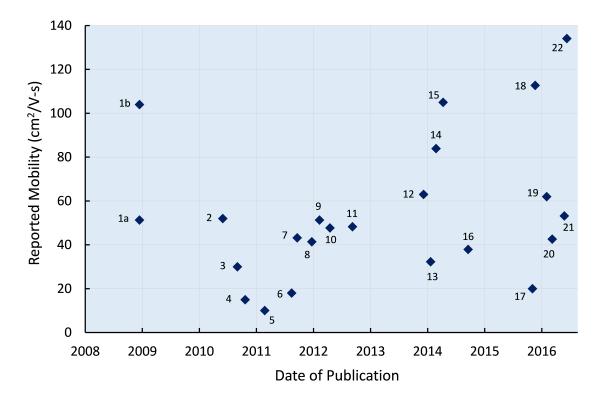

| 2.15   | Reported mobility of sputtered DAL oxide TFTs. Numbers correspond to the ID column in Table 2.2.                                                                                                                                                                                                     | 24   |

| 3.1    | Amorphous semiconductor density of states distribution and defining equations.                                                                                                                                                                                                                       | 28   |

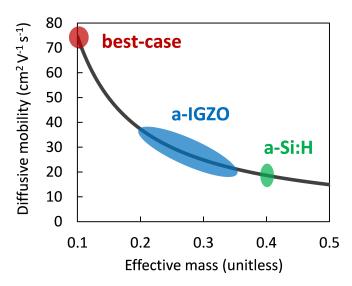

| 3.2    | Diffusive mobility, $\mu_0$ , as a function of effective mass, $m_e^*$ , at room temperature (T = 300 K).                                                                                                                                                                                            | 29   |

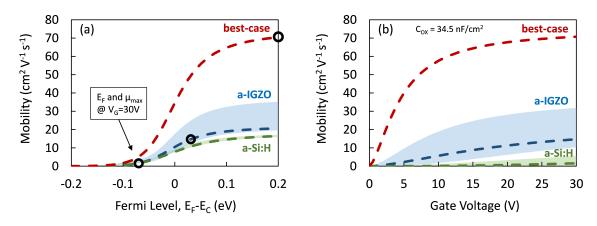

| 3.3    | Electron (n-type) mobility as a function of (a) Fermi level position and (b) gate voltage. The dashed line corresponds to the typical values specified in Table 3.2 and the shaded areas bound the low/best range values.                                                                            | 32   |

| 3.4    | Hole (p-type) mobility as a function of (a) Fermi level position and (b) gate voltage. The dashed line corresponds to the typical values specified in Table 3.2 and the shaded areas bound the low/best range values. Inset shows mobility on a log-scale (low/best range bound omitted for clarity) | 34   |

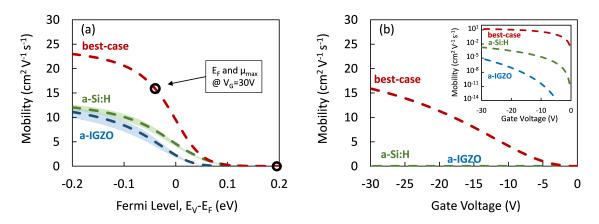

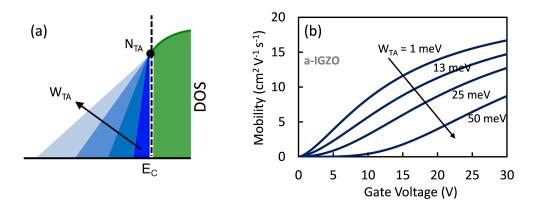

| 3.5    | (a) Increasing conduction band Urbach energy trend and (b) simulation of a-IGZO mobility while varying the Urbach energy.                                                                                                                                                                            | 39   |

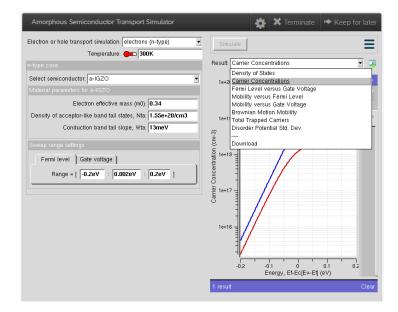

| 3.6    | Screenshot of the Amorphous Semiconductor Transport Simulator de-<br>ployed on nanoHUB [9]                                                                                                                                                                                                           | 40   |

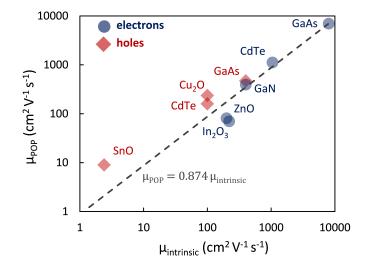

| 3.7    | POP mobility limit, $\mu_{POP}$ , versus intrinsic mobility, $\mu_{intrinsic}$                                                                                                                                                                                                                       | 43   |

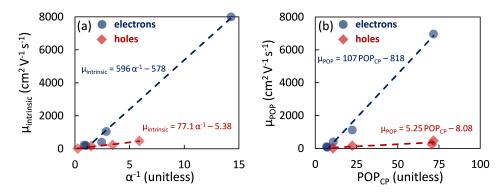

| 3.8    | (a) Intrinsic mobility as a function of the inverse Fröhlich coupling constant and (b) POP mobility as a function of the POP coupling parameter.                                                                                                                                                     | 44   |

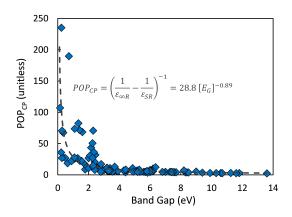

| 3.9    | POP coupling parameter versus band gap trend for 107 inorganic semi-<br>conductors and insulators                                                                                                                                                                                                    | 44   |

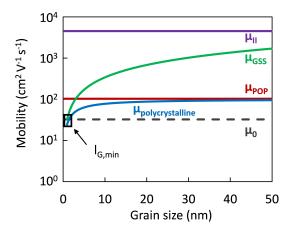

| 3.10   | Mobility as a function of grain size for the case of zinc oxide (see Table 3.4 for material parameters). Ionized impurity concentration is assumed to be $1 \times 10^{17}$ cm <sup>-3</sup> .                                                                                                       | 48   |

| Figure | Ī                                                                                                                                                                                                                                    | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

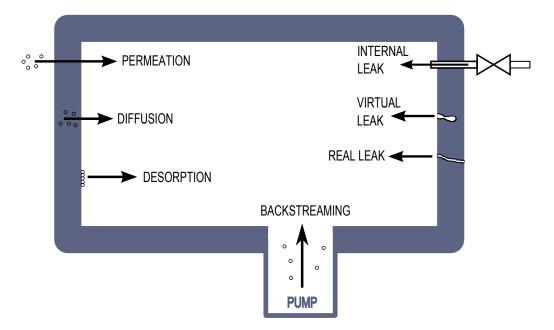

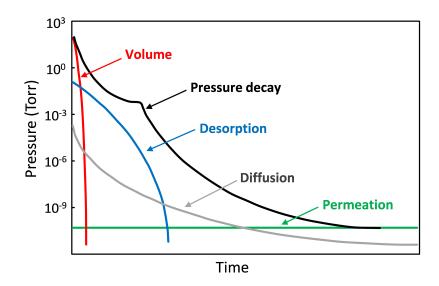

| 4.1    | Physical mechanisms that increase gas pressure in the system are per-<br>meation, diffusion, and desorption. Leaks are categorized into internal<br>leaks, virtual leaks, and real leaks. Figure created with data from<br>Ref. [10] | 52   |

| 4.2    | The various gas loads during pumpdown. Figure adapted from Ref. [10]                                                                                                                                                                 | . 53 |

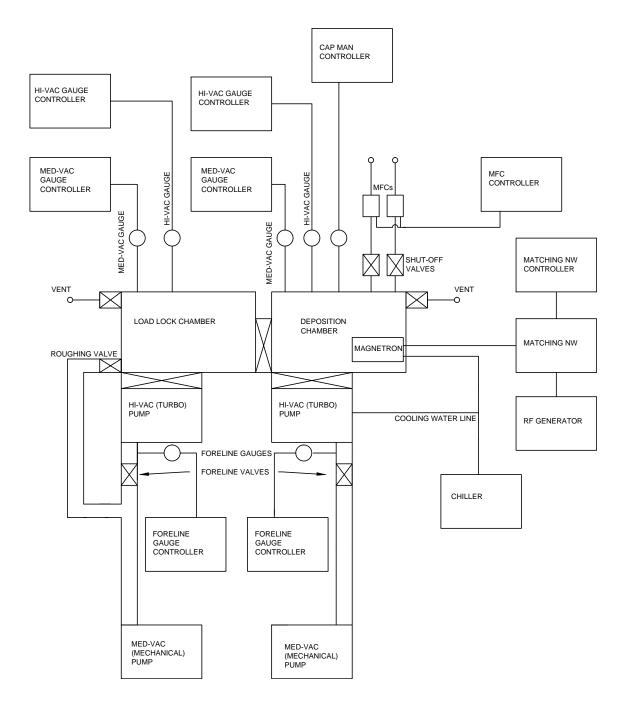

| 4.3    | Block diagram of a load-locked high vacuum system. The main cham-<br>ber is typically equipped with a single gun and corresponding RF gen-<br>erator/power supply for a sputtering system                                            | 57   |

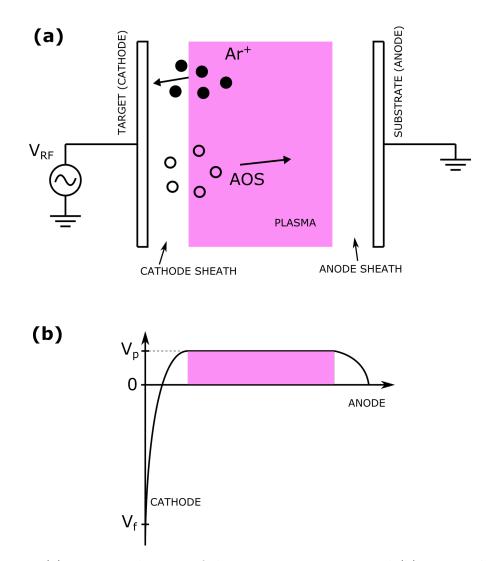

| 4.4    | (a) Basic mechanism of the sputtering process and (b) a typical voltage distribution from cathode to anode (V <sub>p</sub> is the plasma potential)                                                                                  | 59   |

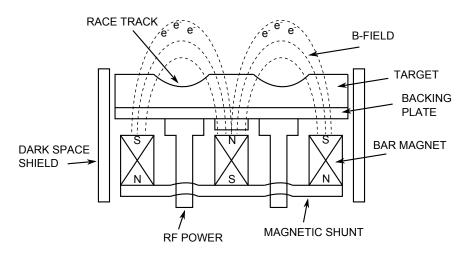

| 4.5    | Cross section of a magnetron sputter target                                                                                                                                                                                          | 61   |

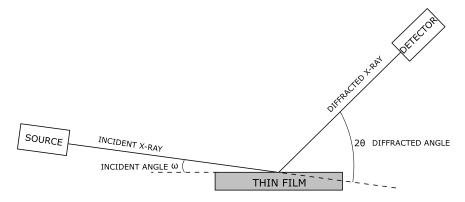

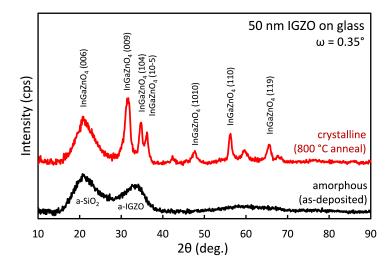

| 4.6    | Definition of angles for a GI-XRD measurement                                                                                                                                                                                        | 63   |

| 4.7    | Diffraction pattern of amorphous and crystalline IGZO thin films on fused silica.                                                                                                                                                    | 63   |

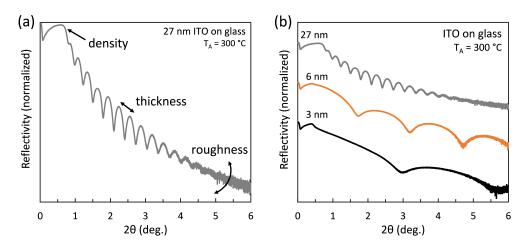

| 4.8    | (a) General trends of an XRR spectrum and (b) XRR measurement of ITO films with varying thickness.                                                                                                                                   | 64   |

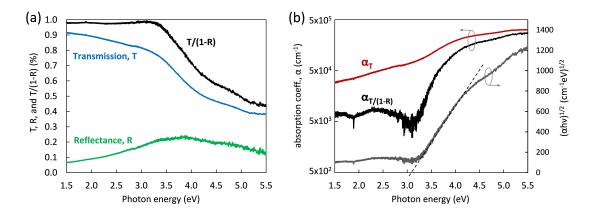

| 4.9    | Optical spectroscopy of 30 nm a-IGZO on fused silica. (a) Transmission, reflectance, and corrected transmission and (b) absorption coefficient, $\alpha$ , and Tauc plot                                                             | 66   |

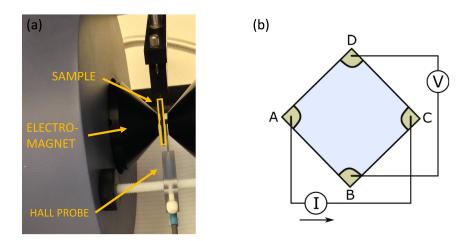

| 4.10   | (a) Picture of sample mounted between Hall pole magnets and (b) electrodes placed in the <i>Van der Pauw</i> configuration                                                                                                           | 67   |

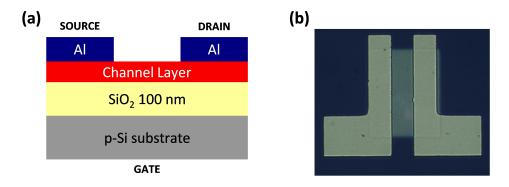

| 4.11   | (a) Schematic diagram of the TFT structure (cross-section) and (b) optical microscope image of AOS device (top view)                                                                                                                 | 69   |

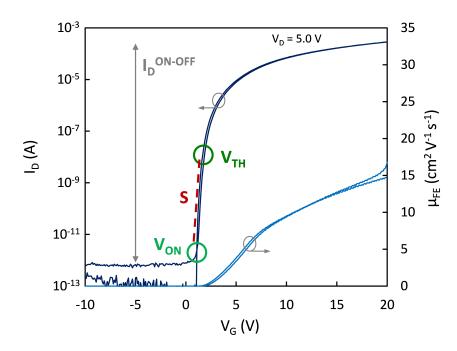

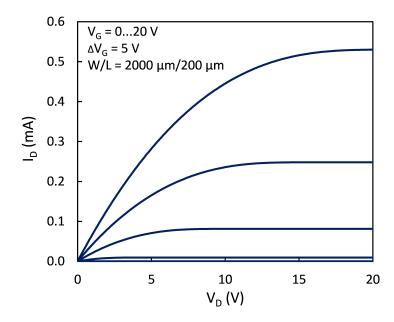

| 4.12   | Amorphous IGZO transfer curve with illustrations of $V_{ON}$ , $V_{TH}$ , $S$ , $I_D^{ON-OFF}$ , and $\mu_{FE}$ .                                                                                                                    | 70   |

| 4.13   | Output curve of an AOS TFT fabricated in this work (corresponding transfer curve shown in Fig. 4.12)                                                                                                                                 | 73   |

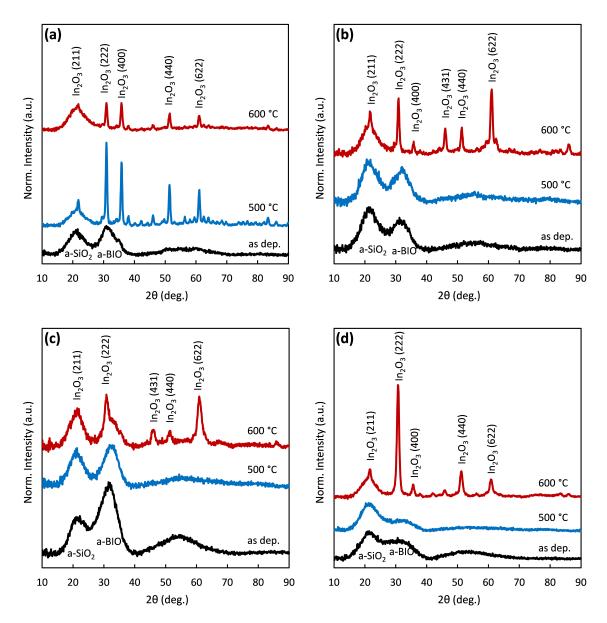

| 5.1    | GI-XRD patterns of (a) 12.5BIO, (b) 17.5BIO, (c) 25BIO, and (d) 50BIO thin films on fused silica substrates                                                                                                                          | 77   |

| Figure | Ē                                                                                                                                                                                                                                                                                                                                                                                                              | Page |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

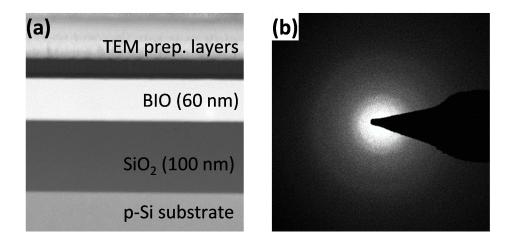

| 5.2    | (a) Cross-sectional STEM high-angle annular dark-field (HAADF) image of as-deposited 17.5BIO thin film and (b) SAED pattern of BIO layer after in-situ heating to 400 °C, showing an amorphous phase                                                                                                                                                                                                           | 78   |

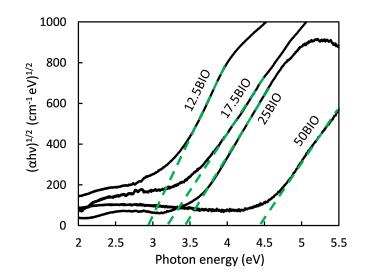

| 5.3    | Tauc plot of optical absorption of BIO thin films as-deposited                                                                                                                                                                                                                                                                                                                                                 | 79   |

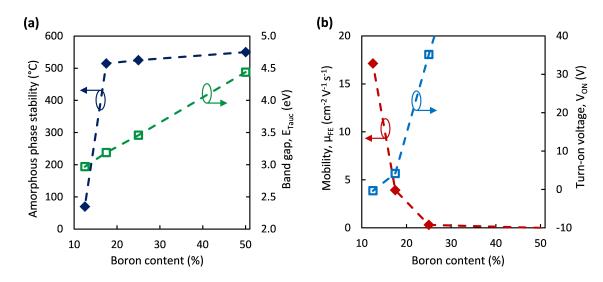

| 5.4    | Summary of trends with decreasing boron content for (a) amorphous phase stability and optical band gap of thin films; and (b) field-effect mobility and turn-on voltage of devices annealed at 400 °C                                                                                                                                                                                                          | 80   |

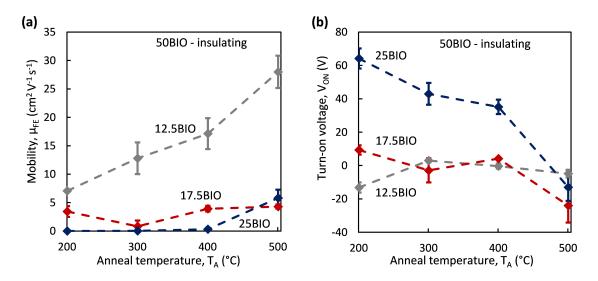

| 5.5    | (a) Field-effect mobility and (b) turn-on voltage as a function of anneal temperature for BIO TFTs.                                                                                                                                                                                                                                                                                                            | 81   |

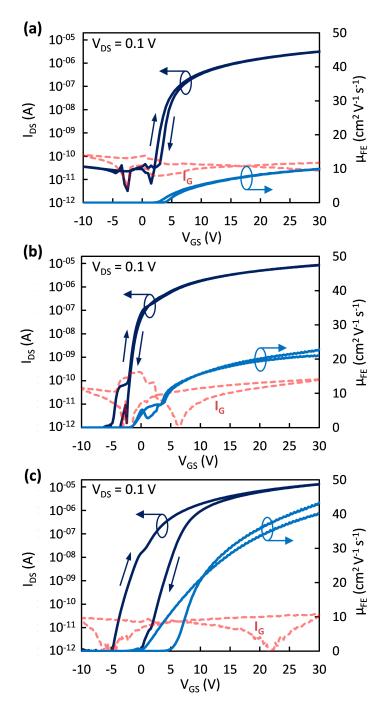

| 5.6    | Transfer characteristics with optimized process of (a) amorphous 17.5BIO device ( $t_{ch} = 50 \text{ nm}$ , $T_A = 400 \text{ °C}$ , $O_2 = 5 \text{ \%}$ ), (b) polycrystalline 12.5BIO device ( $t_{ch} = 10 \text{ nm}$ , $T_A = 200 \text{ °C}$ , $O_2 = 10 \text{ \%}$ ), and (c) ultrathin polycrystalline 12.5BIO device ( $t_{ch} = 5 \text{ nm}$ , $T_A = 500 \text{ °C}$ , $O_2 = 10 \text{ \%}$ ). | 83   |

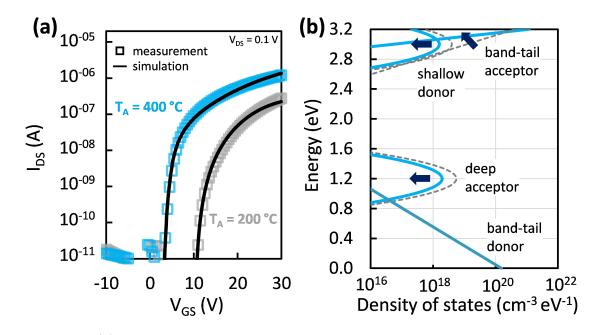

| 5.7    | (a) Experimental transfer characteristics of 200 and 400 °C annealed 17.5BIO devices and comparison with TCAD simulation. (b) BIO DOS for the 200 °C device (dashed lines) and 400 °C device (solid lines) as inferred from the TCAD simulation                                                                                                                                                                | 85   |

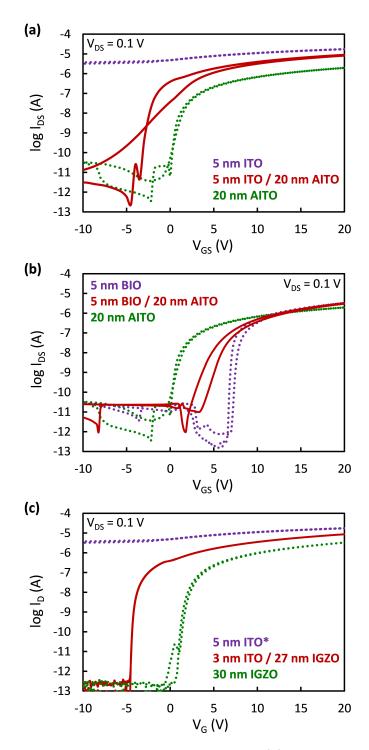

| 6.1    | Transfer curves of SAL and DAL TFTs for (a) ITO-AITO, (b) BIO-AITO, and (c) ITO-IGZO channel layers. $W/L = 1000 \ \mu m/200 \ \mu m$ for all devices.                                                                                                                                                                                                                                                         | 89   |

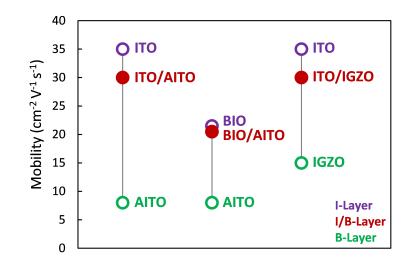

| 6.2    | Summary of field-effect mobility for SAL and DAL TFTs                                                                                                                                                                                                                                                                                                                                                          | 90   |

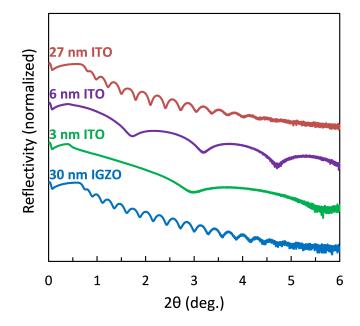

| 6.3    | XRR measurement of ITO and a-IGZO thin films on glass substrates.                                                                                                                                                                                                                                                                                                                                              | 91   |

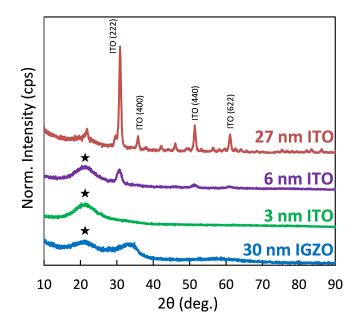

| 6.4    | GI-XRD measurement of ITO and a-IGZO thin films on glass substrates.                                                                                                                                                                                                                                                                                                                                           | 91   |

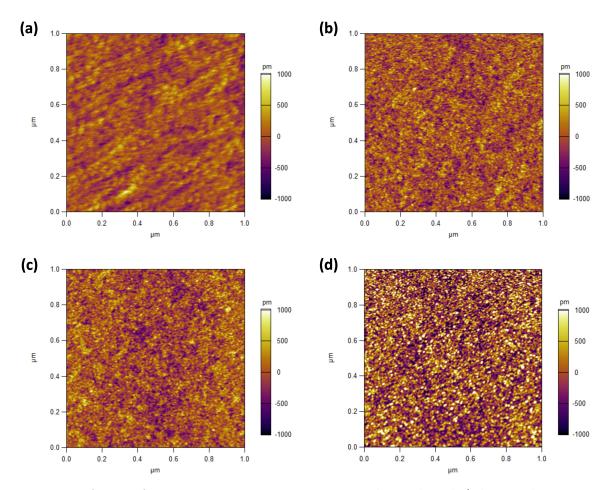

| 6.5    | Atomic force microscopy measurement on thermal oxide/silicon sub-<br>strates of (a) 30 nm a-IGZO, (b) 3 nm ITO, (c) 6 nm ITO, and (d) 27<br>nm ITO thin films.                                                                                                                                                                                                                                                 | 93   |

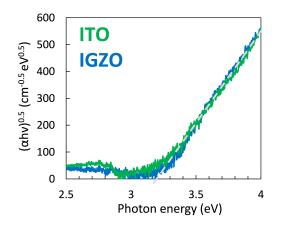

| 6.6    | Optical spectroscopy of ITO and a-IGZO thin films on glass substrates.                                                                                                                                                                                                                                                                                                                                         | 93   |

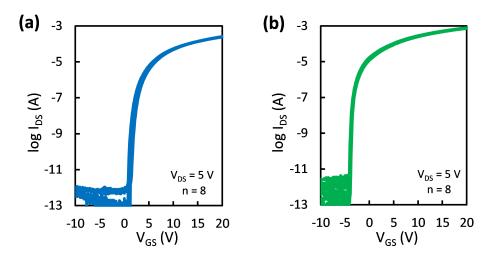

| 6.7    | Transfer characteristics (forward and reverse sweep) of (a) single active layer (SAL) and (b) dual active layer (DAL) devices                                                                                                                                                                                                                                                                                  | 94   |

| Figure |                                                                                                                                                                                                                                         | Page   |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

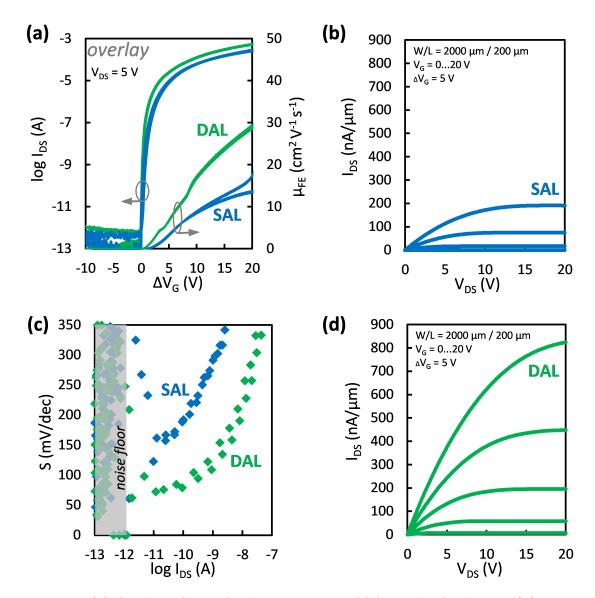

| 6.8    | (a) Overlay of transfer characteristics of SAL and DAL device, (b) output characteristics of DAL device, (c) comparison of sub-threshold swing of SAL and DAL device, and (d) output characteristics of DAL device.                     | 96     |

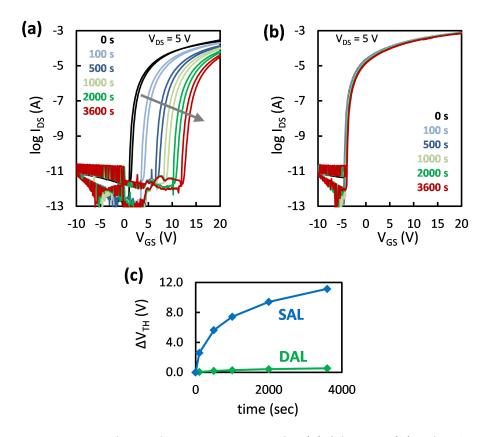

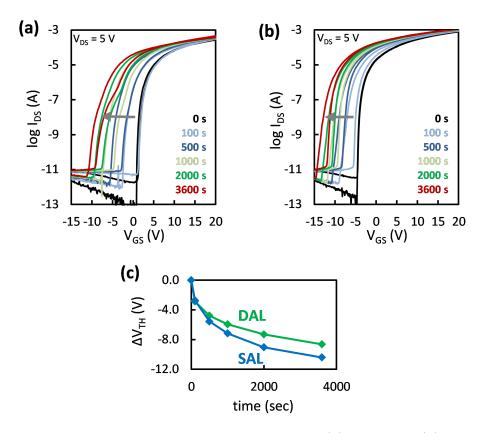

| 6.9    | Evolution of transfer characteristics for (a) SAL and (b) DAL device<br>with increasing PBTS time and (c) shift of threshold voltage with<br>increasing PBTS time                                                                       | 97     |

| 6.10   | Evolution of transfer characteristics for (a) SAL and (b) DAL device with increasing NBTIS time and (c) shift of threshold voltage with increasing NBTIS time                                                                           | 98     |

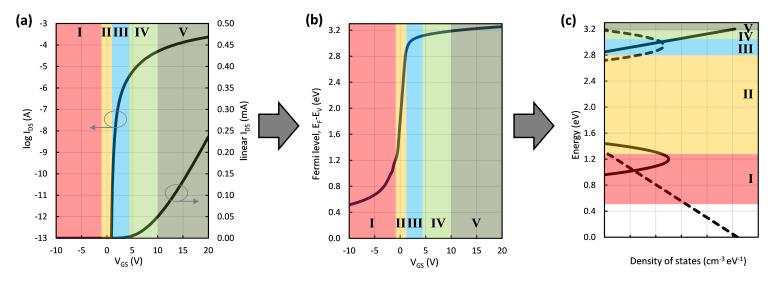

| 6.11   | Mapping electrical I-V characteristics to sub-bandgap density of states via (a) drain current as a function of gate voltage to (b) Fermi level position as a function of gate voltage to (c) energy as a function of density of states. | 101    |

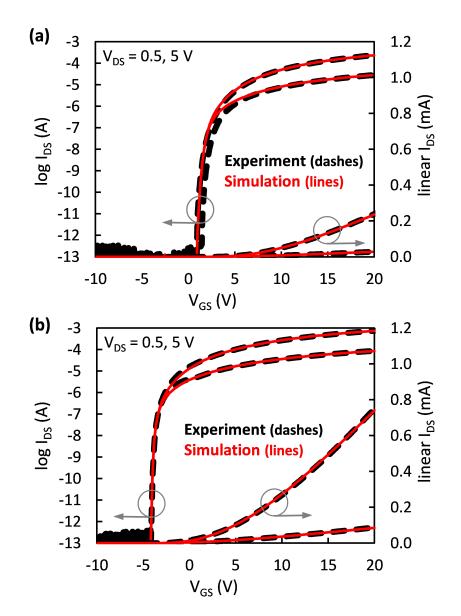

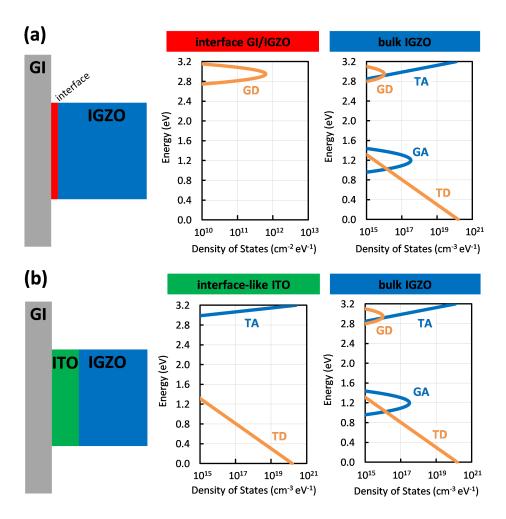

| 6.12   | Comparison of experimental and simulated transfer characteristics of (a) SAL and (b) DAL device.                                                                                                                                        | 103    |

| 6.13   | DOS of interface and channel layer for (a) SAL device and (b) DAL device                                                                                                                                                                | 105    |

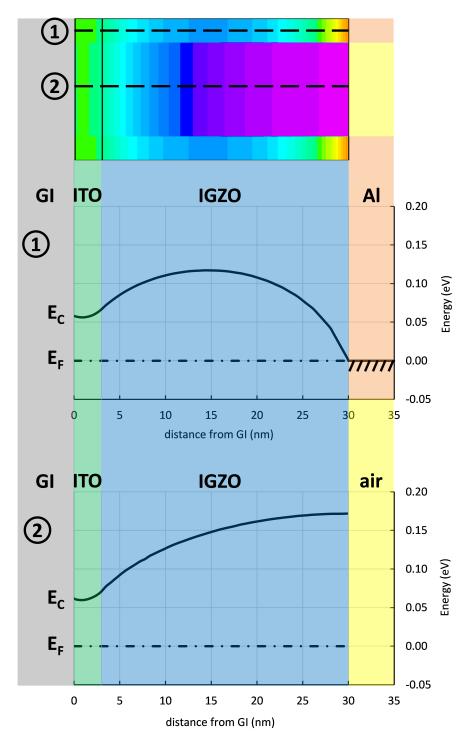

| 6.14   | Energy band diagram of ITO-IGZO channel layer in equilibrium. Cut-<br>line $\Phi$ is at the source Al metal electrode and cutline $\mathfrak{D}$ at the center<br>of the channel                                                        | 107    |

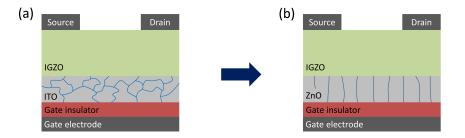

| 6.15   | (a) Conventional DAL TFT with amorphous/nanocrystalline ITO in-<br>terface layer and (b) proposed DAL TFT with (poly)crystalline ZnO<br>interface layer                                                                                 | 108    |

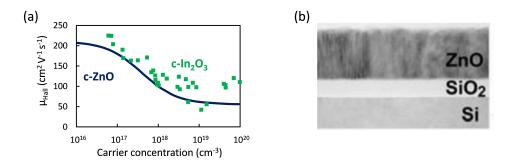

| 6.16   | (a) Hall mobility data from the literature of single-crystal ZnO [11] and single-crystal $In_2O_3$ [12] and (b) TEM image of c-axis aligned ZnO [13]                                                                                    | ]. 109 |

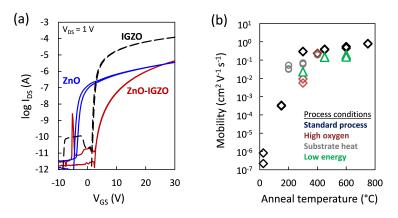

| 6.17   | (a) Summary of field-effect mobility of ZnO TFTs with varying process conditions and (b) transfer characteristics of ZnO, a-IGZO, and ZnO-IGZO TFTs                                                                                     | 109    |

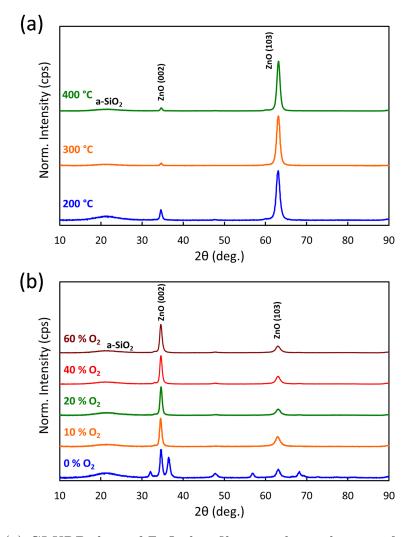

| 6.18   | (a) GI-XRD data of ZnO thin films on glass substrates for (a) varying deposition temperature (10 $\%$ O <sub>2</sub> ) and (b) varying O <sub>2</sub> flow during deposition (at room temperature)                                      | 111    |

## LIST OF TABLES

| Table |                                                                                                                                                                                                                                                                                                                                                                     | Page |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1   | High mobility reports of SAL oxide TFTs                                                                                                                                                                                                                                                                                                                             | 22   |

| 2.2   | Summary of sputtered DAL oxide TFTs reported in the literature                                                                                                                                                                                                                                                                                                      | 25   |

| 3.1   | Amorphous semiconductor mobility assessment (n-type case)                                                                                                                                                                                                                                                                                                           | 31   |

| 3.2   | Amorphous semiconductor transport parameters. $\sim$ indicates that this value is not based on a value reported in the literature; rather, it is a crude estimate.                                                                                                                                                                                                  |      |

| 3.3   | Summary of amorphous semiconductor disorder parameters and result-<br>ing mobility where $W$ and $n_{\text{total}}$ are the disorder potential standard<br>deviation and the total band-tail trap concentration, respectively. The<br>values given for N <sub>TA,D</sub> and W <sub>TA,D</sub> correspond to the <i>typical</i> range as<br>tabulated in Table 3.2. |      |

| 3.4   | Single crystal semiconductor POP model parameters, calculated POP mobility, and reported intrinsic mobility.                                                                                                                                                                                                                                                        |      |

| 4.1   | MFP, ML formation time, and corresponding vacuum level, range, and flow regime for three different pressures. The chosen values of 760, $1 \times 10^{-3}$ , and $1 \times 10^{-7}$ Torr equate to approximately atmospheric pressure, working pressure, and base pressure, respectively.                                                                           |      |

| 4.2   | Summary of incremental, average, field-effect, effective, and saturation mobility equations.                                                                                                                                                                                                                                                                        |      |

| 5.1   | Comparison of boron with commonly used cations in the design of an AOS. With data from Ref. [14].                                                                                                                                                                                                                                                                   |      |

| 5.2   | Phase separation temperature, $T_X$ , band gap, $E_G$ , and field-effect mobility, $\mu_{FE}$ , as a function of increasing boron content.                                                                                                                                                                                                                          | 86   |

| 6.1   | Device parameters for SAL and DAL TFTs                                                                                                                                                                                                                                                                                                                              | 95   |

| 6.2   | General simulation parameters.                                                                                                                                                                                                                                                                                                                                      | 99   |

| 6.3   | Simulation DOS parameters                                                                                                                                                                                                                                                                                                                                           | 104  |

## LIST OF APPENDIX FIGURES

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                              | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

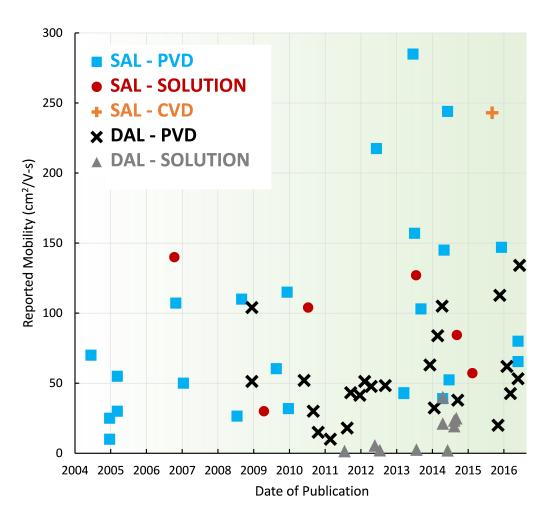

| A.1    | Mobility of selected reports for single active layer (SAL) physical vapor<br>deposited (PVD) TFTs [square], SAL solution processed TFTs [circle],<br>SAL chemical vapor deposited (CVD) TFT [cross], dual active layer<br>(DAL) PVD TFTs [multiplication sign], and DAL solution processed<br>TFTs [triangle]                                                                                                |      |

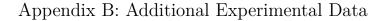

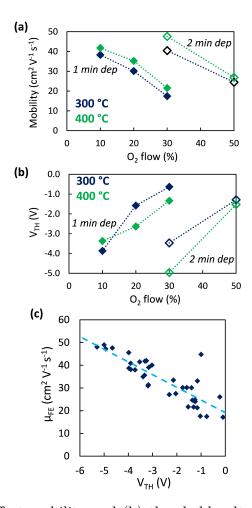

| B.1    | (a) Field-effect mobility and (b) threshold voltage as a function of oxy-<br>gen partial pressure during ITO (I-layer) deposition and ITO thick-<br>ness (one minute deposition corresponds to 3 nm ITO at 10 % $O_2$<br>flow). Amorphous IGZO (B-layer) process conditions are fixed at 10 %<br>$O_2$ flow and 30 nm thickness. (c) Mobility as a function of threshold<br>voltage for 36 ITO-IGZO DAL TFTs |      |

### CHAPTER 1: INTRODUCTION

An amorphous solid exhibits short range order but no long range order on the atomic scale. In other words, the structure beyond first or second nearest-neighbor atoms is random. People have been using and preparing amorphous solids, e.g., silicate glasses for thousands of years. However, amorphous semiconductors for (opto-)electronics applications are a much more recent discovery. The subject of amorphous semiconductors has rapidly evolved from academic curiosity [15] in the 1950s to the principal semiconductor in large-area electronics today. This is mostly due to the discovery of how to use hydrogen to passivate dangling bonds in amorphous silicon, which greatly reduces its defect density [16]. Hydrogenated amorphous silicon (a-Si:H) has been employed in solar cells and is still the dominant semiconductor in active-matrix liquid crystal displays (AMLCDs). In AMLCDs, a-Si:H is the active layer in the thinfilm transistor (TFT) that is associated with every pixel. Furthermore, amorphous semiconductors lack grain boundaries and are ultra-smooth, which makes them very suitable for deposition over large areas.

In 1996, a new class of amorphous materials was discovered [17]. These were later named amorphous oxide semiconductors (AOSs), or sometimes just 'oxides' [5]. AOSs are remarkable in that AOS electron mobility is hardly reduced compared to its crystalline counterpart. The most widely employed AOS today is amorphous indium gallium zinc oxide (a-IGZO). The electron mobility of a-IGZO is 10 to 20 times greater than that of a-Si:H. Additionally, AOSs have a wide band gap of approximately 3 eV which makes them transparent in the visible regime and AOSs can be easily deposited via sputtering at low temperatures. All of this makes oxides a prime candidate to replace a-Si:H in existing applications and to enable next-generation flat-panel displays as well as transparent, flexible, and wearable electronics. To realize these new applications, a lot of interest is directed towards finding AOSs with even higher electron mobility.

The research presented herein assesses high mobility oxide TFTs from both an experimental and modeling standpoint. Oxide TFTs are fabricated at the Materials Synthesis and Characterization laboratory at Oregon State University. Theoretical models are developed using both fundamental physics considerations as well as commercial 2-dimensional device simulation software.

This dissertation is structured as follows. Chapter 2 provides the necessary background information and a review of the current literature. Chapter 3 proposes a model to assess the upper limit of mobility in an amorphous semiconductor. Chapter 4 introduces the experimental methods used in this work. Chapter 5 presents the results of boron indium oxide TFTs. Chapter 6 investigates dual active layer TFTs as a means to further increase oxide TFT performance. Finally, Chapter 7 presents conclusions and recommendations for future work.

#### CHAPTER 2: BACKGROUND AND LITERATURE REVIEW

This chapter provides a background on TFTs and their application. The fundamental physics of AOSs are briefly summarized as it pertains to the discussion in this thesis. Lastly, the literature on high mobility oxide TFTs is reviewed.

#### 2.1 Flat-Panel Displays

#### 2.1.1 Major Display Milestones

Active-matrix, TFT-based flat-panel displays (FPDs) were first widely adopted in laptop screens around 1995. Not long after that, AMLCDs started to replace the bulky cathode ray tube (CRT) computer monitors. Nowadays, AMLCDs are ubiquitous in our everyday life. Figure 2.1 gives a brief historical overview of the most important TFT-based FPD applications. In large-screen TVs, smartphones, and tablets the display is arguably the most important component. FPDs also find new applications in infotainment systems, automotive, and household appliances. The latest displays offer a larger diameter screen, higher resolution, faster refresh rates, higher color accuracy, thinner form factor, and narrow bezel striving for the most immersive viewing experience. New material innovation is driven by head-mounted displays for virtual reality applications requiring very high pixel density (pixel per inch, ppi). AMOLED displays also require a higher performance TFT beyond that of an a-Si:H-based backplane.

Figure 2.1: Timeline of TFT-based flat-panel display technologies at point of widespread adoption. With data from IHS DisplaySearch, Applied Materials, and Intel.

#### 2.1.2 Pixel Circuit

TFTs are employed in the pixel circuit of the AMLCD backplane. Additionally, in the latest AMLCDs TFTs are sometimes used for the peripheral drive circuit using a so-called *gate driver on array* technology. In an AMLCD pixel circuit, the TFT adjusts the brightness of the RGB sub-pixel by controlling the orientation of the liquid-crystal which transmits light from the backlight. In contrast, in an AMOLED display the TFT adjusts the brightness of the sub-pixel by controlling the current passing through the OLED. Attached to each sub-pixel is a pixel circuit. One of the simplest circuits for an AMOLED pixel consisting of 2 transistors and 1 capacitor (2T1C) is shown in Fig. 2.2.

A circuit with the fewest devices and lines is almost always desired as it takes up

less area and is essential for achieving higher ppi. However, frequently more complex circuits must be used to compensate for non-uniformity and degradation of the TFT. The driving TFT in an AMOLED display is particularly sensitive to non-uniformity and degradation. A shift in the turn-on voltage can make a significant impact on the resulting drain current that is then supplied to the OLED. With a lower current the luminescence of the OLED is reduced, which results in brightness variation across the display.

In contrast, AMLCD operation involves a voltage-controlled technology so that no driving TFT is required in the pixel circuit. The requirements for uniformity and stability are not as stringent in an AMLCD as in an AMOLED display.

Figure 2.2: A simple pixel circuit for an AMOLED display. T1 is a switching transistor, T2 is a driving transistor, and  $C_{st}$  is a storage capacitor. Figure reproduced from Ref. [1].

### 2.1.3 Current TFT Semiconductors

The dominant TFT backplane material is a-Si:H. In 2012, the total TFT production capacity was approximately  $210 \times 10^6$  m<sup>2</sup> and LTPS and Oxide technologies only contributed about 5 % (or  $10 \times 10^6$  m<sup>2</sup>) [18]. In recent years, LTPS and Oxide have

increased their market share. A summary of approximate application range for a-Si:H, LTPS and Oxide (a-IGZO) is given in Fig. 2.3. Excimer laser annealed (ELA) LTPS can provide the highest mobility and the option of CMOS circuitry, however, a-IGZO exhibits a lower OFF-current and is cheaper to fabricate than LTPS. New displays require an ever higher TFT mobility which is indicated by the dashed lines in Fig. 2.3 and described in the following.

Figure 2.3: Current TFT semiconductors used in mass-production are a-Si:H, LTPS, and a-IGZO. Required mobility increases with refresh rate and resolution. Adapted from Kwon and Jeong [2].

One of the key parameters of a TFT is its carrier mobility. The general *square-law* relation describing the drain current of a FET is equal to

$$I_{DS} = \mu \frac{W}{L} C_{OX} (V_{GS} - V_{ON}) V_{DS} - \frac{V_{DS}^2}{2}, \qquad (2.1)$$

where  $\mu$  is the carrier mobility, W is the width of the channel, L is the gate length,

$C_{OX}$  is the gate oxide capacitance per unit area,  $V_{GS}$  is the gate-source voltage,  $V_{ON}$  is the turn-on voltage of the TFT, and  $V_{DS}$  is the drain-source voltage.

The on-current  $I_{ON}$  is defined as the value of  $I_{DS}$  in a fully biased/fully-on state. A higher  $I_{ON}$  is always desired. The basic parameters for increasing  $I_{ON}$  are indicated in Eq. 2.1. Namely, for a given operating voltage ( $V_{GS}$  and  $V_{DS}$ ) a higher  $I_{ON}$  can be achieved by increasing  $\mu$ , or by increasing the W/L ratio.

To motivate the need for a higher mobility two scenarios are described in the following. First, the TFT has a higher mobility with all other parameters remaining unchanged. This results in a higher  $I_{ON}$  which in turn results in faster switching (charging of capacitances) and, finally, enables faster refresh rates of the display. Second, the TFT has a high mobility, and hence,  $I_{ON}$  is sufficiently large. Therefore, W can be reduced. This allows the manufacturer to make the TFT smaller which (a) is a prerequisite step for increasing the resolution of the display, or (b) results in the TFT taking up less area in the sub-pixel (higher aperture ratio, meaning less shadowing by the black matrix) which results in a wider viewing angle and increases the brightness of the sub-pixel. If the higher brightness is not desired, one can in turn dim the backlight or reduce the supply voltage to the OLED for an AMLCD and AMOLED display, respectively, effectively reducing power consumption.

#### 2.2 Thin-Film Transistors

In the following, commonly used device structures and the general operation of a TFT are described. TFTs belong to the class of field-effect transistors (FET). They are three terminal devices. Namely, the three electrodes are gate, source, and drain. Additionally, a TFT needs a semiconducting channel layer and a substrate (typically silicon or glass) to build the device upon. A current flowing from source to drain can be controlled by biasing the gate electrode (voltage control).

#### 2.2.1 Device Structure

The four basic possible structures of a TFT are staggered top gate, coplanar top gate, staggered bottom gate, and coplanar bottom gate, shown in Fig. 2.4. The naming scheme refers to the position of the gate electrode (top/bottom) and the plane of the source and drain regions in reference to the channel (coplanar/staggered). The two bottom gate structures are sometimes referred to as inverted staggered and inverted coplanar TFT, respectively.

Figure 2.4: Staggered top gate, coplanar top gate, staggered bottom gate, and coplanar bottom gate device structures.

Each structure has its own advantages and disadvantages. The bottom gate structures need fewer mask steps and therefore, are easier and cheaper to fabricate. In a coplanar or staggered bottom gate structure the gate or the gate and source/drain electrodes, respectively, are already deposited and patterned before the potentially delicate channel layer is deposited. This avoids exposure of the channel material to any of the previous processing steps, e.g., the use of certain etchants, energetic plasmas, and/or elevated temperatures. Furthermore, the channel is not in direct contact with the glass substrate. Therefore, any negative impact the substrate might have on device characteristics, e.g., any surface roughness or out-diffusion of elements like sodium which is used during the glass substrate manufacturing, is mitigated. Typically, a nitride/oxide buffer layer is used as a barrier between the substrate and the TFT [19]. Additionally for the case of oxide TFTs, no source/drain doping is required. However, the parasitic gate-source/drain overlap capacitances are higher in the bottom gate structure.

In a top gate device the channel layer is exposed on a planar surface. This is helpful for excimer laser annealing and source/drain doping via ion-implantation which is why the coplanar top gate structure is typically used for LTPS TFTs.

Figure 2.5: Staggered bottom gate TFT structure typically used in mass-production.

For mass-manufacturing, where reproducibility and reliability are crucial, several changes need to be made to the basic TFT structure. A staggered bottom gate TFT with an etch stop layer is shown in Fig. 2.5. It has tapered sidewalls for better step coverage [20], and a passivation layer to reduce degradation of the channel due to ambient conditions (e.g., gas adsorption). The AOS channel layer can be very sensitive to etchants. The etch stop layer (ESL) aids in protecting the channel during source/drain patterning [21]. Fabrication without an ESL is called a back channel etch (BCE) type process.

#### 2.2.2 Operation

TFTs are accumulation-mode devices meaning the conducting channel is formed by majority carriers, in contrast to the ubiquitous metal-oxide-semiconductor fieldeffect transistor (MOSFET) which forms an inversion channel (minority carriers). Commonly, the desired TFT behavior for application in the display backplane is enhancement-mode (normally-off) operation. The idealized enhancement-mode operation with flat-band conditions is described in the following and the corresponding energy band diagrams are shown in Fig. 2.6.

By applying a positive bias ( $V_{GS} > 0$ ) electrons are accumulated at the insulatorsemiconductor interface and a thin, conducting accumulation region forms in the semiconductor. Is a bias applied at the drain terminal simultaneously ( $V_{DS} > 0$ ), then electrons get injected from the source contact, travel across the channel layer, and get extracted at the drain contact. As a consequence, current can flow from source to drain and the transistor is in the ON-state (Fig. 2.6(b)). In the OFF-state ( $V_{GS} \leq 0$ ) the channel is non-conducting and no current (ideally) can flow between source and drain (Fig 2.6 (a) and (c)).

For a small applied drain voltage, an increase in  $V_{DS}$  results in a linear increase in  $I_{DS}$  (pre-saturation). With a further increase in  $V_{DS}$  beyond  $V_{GS} - V_T$ , the channel is *pinched-off* at the drain and  $I_{DS}$  saturates (saturation region).

Figure 2.6: Energy band diagrams for a metal-insulator-semiconductor (M-I-S) capacitor. The n-type semiconductor is in (a) equilibrium when no bias is applied, (b) accumulation when a positive bias is applied, and (c) depletion when a negative bias is applied.

#### 2.3 Amorphous Oxide Semiconductors

The first report on AOSs was published by Hosono et al. in 1996 [17]. The amorphous oxides AgSbO<sub>3</sub>, Cd<sub>2</sub>GeO<sub>4</sub>, and Cd<sub>2</sub>PbO<sub>4</sub> were investigated. It was found that these materials exhibited a relatively large Hall mobility,  $\mu_{Hall} \approx 10 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ . TCOs are closely related to AOSs and had been reported more than a decade earlier [22]. The difference is that TCOs like In<sub>2</sub>O<sub>3</sub>:Sn (ITO) are typically polycrystalline and have too many mobile carriers to be used as a semiconducting channel layer for a TFT. A part of the periodic table of elements was suggested for selecting cations for the design of an AOS, as shown in Fig. 2.7. These are elements with an  $(n-1)d^{10}ns^0$  $(n \geq 4)$  electronic configuration.

Figure 2.7: The portion of the periodic table proposed for selecting AOS cations. As, Cd, Hg, Tl, and Pb are usually not used due to their toxicity. Ag and Au are costly. Figure adapted from Refs. [3, 4].

An amorphous phase can be achieved by selecting two ore more cations having different oxide crystal structures, thereby resulting in a frustration of the lattice. Three typically used binary oxides are indium oxide ( $In_2O_3$ ), zinc oxide (ZnO), and tin oxide ( $SnO_2$ ) which are commonly found in the crystal structures of cubic mineral bixbyite, hexagonal wurtzite, and tetragonal rutile [23]. The amorphous phase is metastable. AOSs remain amorphous until around 500 °C to 700 °C depending on the specific system. Beyond that temperature, crystallization and/or phase separation occurs.

In 2004, the first amorphous IGZO TFT was reported by the Hosono group [24]. The TFTs were fabricated on a flexible substrate (polyethylene terephthalate, PET), the IGZO channel layer was deposited by pulsed laser deposition, and a 140 nm thick  $Y_2O_3$  layer was used as a gate insulator. The devices exhibited an on-to-off ratio of  $I_D^{ON-OFF} \approx 10^3$ , a mobility of  $\mu_{FE} \approx 6 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ , and a threshold voltage of  $V_T = 1.6 \text{ V}.$

The electrical characteristics of IGZO depend on the ratio of  $In_2O_3$  to  $Ga_2O_3$  to ZnO. The most common IGZO composition is  $InGaZnO_4$ , having a molar ratio of  $In_2O_3/Ga_2O_3/ZnO$  of 1:1:2. The effect of varying the IGZO composition on the Hall mobility and carrier concentration is shown in Fig. 2.8. The mobility and carrier concentration tend to increase with higher In content. Going from the center point of the triangle of Fig. 2.8 to the bottom right corner (pure  $In_2O_3$ ) the mobility increases by a factor of  $3.8 \times$  while the carrier concentration increases by an enormous  $100 \times$ .

AOSs have larger mobilities than that historically expected from an amorphous semiconductor. This expectation stems mainly from comparison to silicon, the most prominent semiconductor. The electron mobility of silicon decreases from ~1500 to ~1 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> when going from single crystal silicon to hydrogenated amorphous silicon. Silicon forms covalent bonds. These bonds are formed with highly directional sp<sup>3</sup> orbitals. For silicon precise orbital overlap is only possible in an ordered or, more specifically, in a crystalline structure [6], as indicated in Fig. 2.9(a),(b).

Figure 2.8: Hall mobility and carrier concentration of the  $In_2O_3$ - $Ga_2O_3$ -ZnO system. The Hall mobility is in units of  $cm^2V^{-1}s^{-1}$  and the carrier concentration (in parentheses) is in units of  $10^{18}$  cm<sup>-3</sup> [5].

Figure 2.9: Schematic illustration of orbitals for (a) crystalline covalent, (b) amorphous covalent, (c) crystalline ionic, and (d) amorphous ionic semiconductors.

An AOS forms ionic bonds. Its conduction band is derived from large spherical metal s-orbitals. Directional order is not needed to have sufficient overlap between orbitals since the ionic radius of constituent cations is relatively large. Bonding in an ionic semiconductor is illustrated in Fig. 2.9(c),(d). Hence, AOSs are relatively insensitive to directional (bond angle and bond length) disorder. This gives rise to a fundamental difference in the sub-gap density of states (DOS) between a covalent and ionic amorphous semiconductor. The topic of amorphous semiconductor DOS and how it relates to the electron conduction is briefly introduced in the next section and is further discussed in Chapter 3.

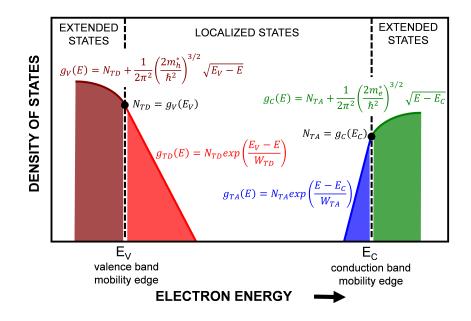

#### 2.3.1 Density of States

The type of bonding of the amorphous semiconductor directly influences the DOS. Moreover, the DOS profile determines the electrical and optical behavior of the semiconductor. The localized conduction and valance band band-tail states follow an exponential distribution and are defined according to the following equations

$$g_{TA}(E) = N_{TA} \exp\left(\frac{E - E_C}{W_{TA}}\right)$$

(2.2)

and

$$g_{TD}(E) = N_{TD} \exp\left(\frac{E_V - E}{W_{TD}}\right), \qquad (2.3)$$

where  $g_{TA}$  ( $g_{TD}$ ) is the total conduction (valence) band band-tail state density,  $N_{TA}$ ( $N_{TD}$ ) is the peak density of acceptor (donor) band-tail states, and  $W_{TA}$  ( $W_{TD}$ ) is the conduction (valence) band Urbach energy. Common Urbach values for a-Si:H and a-IGZO are summarized in Fig. 2.10.

Figure 2.10: (a) a-Si:H and (b) a-IGZO band-tail state Urbach energy influenced by bonding type.

Knowledge about the DOS is crucial for complete understanding of device behavior and for use in AOS TCAD simulations. However, the DOS is very difficult to measure experimentally and several analytical techniques need to be combined to even attempt creating a complete DOS profile. As a result, the DOS of a-IGZO is still not completely understood, particularly the existence and shape of sub-gap states besides the band-tail states are highly debated. Two attempts at a complete experimental characterization of an AOS DOS are shown in Fig. 2.11.

Figure 2.11: Proposed AOS DOS model for (a) a-IGZO [6, 7] and (b) a-ZTO [8].

The a-IGZO DOS in Fig. 2.11(a) was developed from C-V and TFT characterization, optical and hard X-ray photoemission spectroscopy, and density functional theory calculations. Three gaussian-like sub-gap features are indicated in this model. On the other hand, the amorphous zinc tin oxide (a-ZTO) DOS was determined from modulated photocurrent spectroscopy (MPC), drive level capacitance profiling (DLCP), and transient photocapitance (TPC) measurements performed on relatively thick, sputtered a-ZTO thin films. Comparing the zero-order a-IGZO DOS profile from Fig. 2.10(b) with the more complete DOS from Fig. 2.11(a), they match the band-tail states which are intrinsic to an amorphous semiconductor and relatively easy to explain, however, a multitude of other, extrinsic (gaussian) defect states are also possible as indicated in Fig. 2.11(a).

#### 2.3.2 Free Carriers and Mobility

Amorphous IGZO and all AOSs that have been discovered to date are wide band gap, unipolar n-type semiconductors. No inversion, and no hole conduction and p-type doping in general has been achieved in a-IGZO. This is not too surprising considering the large defect density near the valence band mobility edge. Rather, a-IGZO is intrinsically n-type.

Experimentally it is possible to reduce the carrier concentration by increasing the oxygen partial pressure during the deposition process (or vice versa). Furthermore, gallium-rich IGZO compositions have a lower carrier concentration than indium-rich compositions (shown in Fig. 2.8) and thus, gallium seems to act as a carrier suppressor. Gallium bonds to oxygen more strongly than indium or zinc and may aid in reducing oxygen vacancies. Because of this experimental evidence, it is commonly postulated that oxygen vacancies act as a carrier generation site (donor state). Defect creation of an oxygen vacancy can be expressed as,

$$O_{O}^{\times} \rightleftharpoons V_{O}^{\cdot \cdot} + 2e^{'} + \frac{1}{2}O_{2}(g), \qquad (2.4)$$

where  $O_O^{\times}$  is a neutrally charged oxygen on an oxygen lattice site,  $V_O^{\cdot}$  is a doubly positive charged vacancy on an oxygen site, 2e' are two mobile electrons, and  $\frac{1}{2}O_2(g)$  is a gaseous oxygen molecule stemming from the now unoccupied lattice site (vacancy). Hence, every oxygen vacancy donates two free electrons according to this model. Revisiting the DOS profile in Fig. 2.11(a), the deep levels near the valence band are often said to be the origin of oxygen vacancies, however, those levels seem too deep to act as an electron donor.

Figure 2.12: Hall mobility versus carrier concentration for crystalline and amorphous IGZO with varying deposition conditions [7].

The mobility and carrier concentration are strongly connected, as can be seen in Figs. 2.8 and 2.12. The mobility tends to increase with increasing carrier concentration. This is likely because of trap filling. For this, consider that the drift mobility in an amorphous semiconductor is often written as [16, 25, 26, 27]

$$\mu_{\rm drift} = \left(\frac{n}{n+n_T}\right)\mu_0,\tag{2.5}$$

where n is the free electron concentration,  $n_T$  is the trapped electron concentration, and  $\mu_0$  is the trap-free drift mobility. However, the carrier concentration cannot be arbitrarily chosen. Rather, the carrier concentration in an AOS channel layer needs to be tightly controlled because it strongly influences the turn-on voltage of the TFT. Trapping in band-tail states and how it affects mobility is discussed in detail in Chapter 3.

#### 2.4 High Mobility Reports

Hundreds of journal articles on the topic of AOSs have been published since 2003. An attempt was made to identify the reports claiming the highest electron mobilities from fabricated TFTs.

#### 2.4.1 Single Active Layer TFTs

Figure 2.13 gives a summary of reported mobilities for single active layer (SAL) oxide TFTs, this includes AOSs such as a-IGZO as well as polycrystalline ZnO and  $In_2O_3$ . The field-effect or saturation mobility (whichever was given), the semiconductor used for the channel layer and its deposition method, the gate insulator, a comment (if applicable), and affiliation of the main authors of those 29 publications is tabulated in Table 2.1.

The majority of channel layers were deposited via sputtering and utilize a staggered bottom gate structure. A remarkable result are the sputtered In-Zn-O TFTs with top gate structure reported by Samsung Advanced Institute of Technology in 2009 and 2013 exhibiting a mobility of 115 [28] and 157 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> [29], respectively.

Distinguishing between amorphous and polycrystalline reported experimental mobilities is difficult since adequate experimental evidence of a true amorphous phase is often not provided. Many of the reported channel layers likely lie in a grey area of nanocrystalline microstructures with grain sizes of  $\sim 2$  to 5 nm. Even the polycrystalline channel layers still have relatively small grains < 50 nm.

Note that a high mobility result can be a consequence of measurement artifacts associated with employing a leaky gate insulator (GI), not properly accounting for hysteresis, peripheral current flow in an unpatterned-channel TFT, depletion-mode operation, and/or simple incorrect calculation of the mobility [30, 31, 32, 33, 34]. A gate insulator of thermally oxidized silicon of 100 to 200 nm thickness is typically of very high quality and gate leakage current can be ruled out as a potential artifact to influence the apparent mobility. The double stack of PECVD  $Si_3N_4/SiO_2$  often used in industry is also of high quality especially since the total insulator thickness is often  $\geq 300$  nm. Low temperature deposited (low-T.) or solution-processed insulators are frequently of lower quality. Unpatterned channel layers were an issue particularly in the early days of AOS research.

Figure 2.13: High mobility reports of SAL oxide TFTs. Numbers correspond to the ID column in Table 2.1.

| ID  | $\mu_{FE,sat} \ {f cm}^2/{f Vs}$ | Channel<br>Layer | Dep.<br>Method            | Gate<br>Insulator                           | Comment         | Affiliation<br>[Ref.]     |

|-----|----------------------------------|------------------|---------------------------|---------------------------------------------|-----------------|---------------------------|

| 1   | 70                               | Zn-O             | $sputt.^1$                | therm. $SiO_2$                              | unpatterned     | U. Lisbon [35]            |

| 2a  | 10                               | Zn-Sn-O          | $\operatorname{sputt}^1$  | $220 \text{ nm ATO}^2$                      | E-mode          | OSU (ECE) [36]            |

| 2b  | 25                               | Zn-Sn-O          | $\operatorname{sputt.}^1$ | $220 \text{ nm ATO}^2$                      | D-mode          | OSU (ECE) [36]            |

| 3a  | 30                               | In-Zn-O          | $\operatorname{sputt.}^1$ | $220 \text{ nm ATO}^2$                      | E-mode          | OSU (ECE) [37]            |

| 3b  | 55                               | In-Zn-O          | $\operatorname{sputt}^1$  | $220 \text{ nm ATO}^2$                      | D-mode          | OSU (ECE) [37]            |

| 4   | 140                              | In-O             | $IAD^3$                   | organic                                     | leaky GI?       | Northwestern [38]         |

| 5   | 107                              | In-Zn-O          | $\operatorname{sputt.}^1$ | $220~\rm{nm}~\rm{ATO}^2$                    | unpatterned?    | U. Lisbon [39]            |

| 6   | 50                               | Zn-O             | $\operatorname{sputt.}^1$ | PECVD $Si_3N_4$                             | top gate        | Kochi/Casio [40]          |

| 7   | 27                               | In-Zn-O          | $\operatorname{sputt}^1$  | therm. $SiO_2$                              | -               | Tokyo Tech. [41]          |

| 8   | 110                              | Zn-O             | $\mathrm{PLD}^4$          | PECVD $SiO_2$                               | -               | $\operatorname{AFRL}[42]$ |

| 9   | 30                               | In-Zn-Sn-O       | $\mathrm{sol.}^5$         | therm. $SiO_2$                              | unpatterned     | OSU (ChE) [43]            |

| 10  | 60                               | Zn-O             | $\operatorname{sputt.}^1$ | $100 \text{ nm } \text{Ta}_2\text{O}_5$     | unpatterned     | Shanghai [44]             |

| 11  | 115                              | In-Zn-O          | ${ m sputt.}^1$           | PECVD $SiO_2$                               | top gate        | Samsung $[28]$            |

| 12  | 32                               | Al-Sn-Zn-In-O    | ${ m sputt.}^1$           | $185~\mathrm{nm}~\mathrm{Al_2O_3}$          | -               | ETRI $[45]$               |

| 13  | 104                              | In-Zn-Sn-O       | $\mathrm{sol.}^5$         | organic                                     | leaky GI        | Northwestern [46]         |

| 14  | 218                              | In-Ga-Zn-O       | $\operatorname{sputt.}^1$ | PECVD $Si_3N_4$                             | Si cap          | Chiao-T. U. [47]          |

| 15a | 43                               | Zn-O-N           | ${ m sputt.}^1$           | ${\rm Si_3N_4/SiO_2}$                       | bottom gate     | Samsung [48]              |

| 15b | 44                               | In-Zn-O          | $\operatorname{sputt}^1$  | ${\rm Si_3N_4/SiO_2}$                       | bottom gate     | Samsung [48]              |

| 16  | 285                              | Al-Zn-O          | $\operatorname{sputt}^1$  | low-T. $SiO_2$                              | unp.+GI?        | Peking U. [49]            |

| 17  | 157                              | In-Zn-O          | ${ m sputt.}^1$           | PECVD $SiO_2$                               | top gate        | Samsung [29]              |

| 18  | 127                              | In-O             | $\mathrm{sol.}^5$         | $\mathrm{sol.}^5 \mathrm{Al}_2\mathrm{O}_3$ | unp.+GI         | KAUST $[50]$              |

| 19  | 103                              | Zn-O             | ${ m sputt.}^1$           | $150~\mathrm{nm}~\mathrm{Ta_2O_5}$          | unpatterned     | Manchester [51]           |

| 20  | 39                               | In-W-O           | ${ m sputt.}^1$           | therm. $SiO_2$                              | -               | NIMS $[52]$               |

| 21  | 145                              | Al-Zn-Sn-O       | ${ m sputt.}^1$           | low-T. $SiO_2$                              | unp.?+GI?       | Peking U. [53]            |

| 22  | 244                              | Hf-Zn-O          | ${ m sputt.}^1$           | low-T. $SiO_2$                              | unp.+GI?        | Peking U. [54]            |

| 23  | 52                               | In-Zn-Sn-O       | ${ m sputt.}^1$           | PECVD $SiO_2$                               | -               | Inha/Sam. $[55]$          |

| 24  | 84                               | In-Ga-Zn-O       | $\mathrm{sol.}^5$         | $\mathrm{sol.}^5 \mathrm{Al}_2\mathrm{O}_3$ | lower $I_{GS}$  | UCLA $[56]$               |

| 25  | 57                               | In-O             | $\mathrm{sol.}^5$         | $\mathrm{sol.}^5 \mathrm{Al}_2\mathrm{O}_3$ | higher $I_{GS}$ | CUHK [57]                 |

| 26  | 243                              | In-O             | $MOCVD^6$                 | therm. $SiO_2$                              | -               | Yat-sen [58]              |

| 27  | 147                              | Sn-O             | $PVD^7$                   | $40~\mathrm{nm}~\mathrm{HfO}_2$             | -               | Chiao-T. U. [59]          |

| 28  | 66                               | $CAAC-IGZO^8$    | $\operatorname{sputt.}^1$ | unspecified                                 | top gate        | SEL/Sharp [60]            |

| 29  | 80                               | $MOx^9$          | ${ m sputt.}^1$           | PECVD $Si_3N_4$                             | -               | Cbrite [61]               |

Table 2.1: High mobility reports of SAL oxide TFTs.

<sup>1</sup>RF magnetron sputtering. <sup>2</sup>Superlattice of  $AlO_x$  and  $TiO_x$ . <sup>3</sup>Ion-assisted deposition. <sup>4</sup>Pulsed laser deposition. <sup>5</sup>Solution processing (typically spin-coating or ink-jet printing). <sup>6</sup>Metal-organic chemical vapour deposition. <sup>7</sup>Unspecified PVD method. <sup>8</sup>C-axis aligned crystalline In-Ga-Zn-O. <sup>9</sup>Unspecified oxide semiconductor.

## 2.4.2 Dual Active Layer TFTs

A dual active layer (DAL) TFT has a channel comprised of an interface layer adjacent to the gate insulator and a second (typically thicker) "bulk" layer, as illustrated in Fig. 2.14.

Figure 2.14: Dual active layer structure.

For the interface layer, a semiconductor is used which has a high mobility. The high mobility is often caused by a high carrier concentration (see Section 2.3.2). A TFT channel layer comprised of entirely this material would create a TFT that only turns-off at a very negative gate voltage or does not turn-off at all. To circumvent this issue, the high mobility material is combined with a material which has a modest mobility but has a sufficiently low carrier concentration to create an enhancement-mode TFT. The accumulation layer, where the majority of electron transport occurs, is very thin. Hence, the interface layer can be of similar thickness, typically ~5 nm, and still gain most of the benefits of the high mobility transport.

The interface and bulk layer can be comprised of different oxides, e.g., In-Sn-O and In-Ga-Zn-O for the interface and bulk layer, respectively, or of the same material. In the latter case, the carrier concentration and hence, mobility can be enhanced by, for example, adjusting the oxygen partial pressure during deposition. It is very desirable to deposit both layers without breaking vacuum to avoid any defects or contamination

Figure 2.15: Reported mobility of sputtered DAL oxide TFTs. Numbers correspond to the ID column in Table 2.2.

at the interface between both layers.

A summary of reported mobilities for sputtered DAL oxide TFTs is shown in Fig. 2.15. Note that unlike the summary of SAL devices, which only included the devices with the highest mobilities, this is a complete list of reports on DAL oxide TFTs (to my best knowledge). Overall, the median mobility reported for DAL devices is much higher than that of SAL devices across all published results. Most of the reported DAL results seem reliable. The highest reported DAL mobility is smaller than the highest claimed SAL mobility.

Indium-rich oxides such as In-Sn-O and In-Zn-O are the most common choice for the interface layer and a-IGZO is favored for the bulk layer, as tabulated in Table 2.2. Sputtering was identified early as the deposition method of choice and still produces the highest performance channel layers compared to other PVD methods as well as CVD techniques and solution processing. A chart detailing the deposition method of the channel layer for both the SAL and DAL literature is given in Appendix A.1.

| ID | $\mu_{FE,sat} \ {f cm}^2/{f Vs}$ | Channel<br>Layer I | Channel<br>Layer B              | Gate<br>Insulator      | Comment   | Affiliation<br>[Ref.] |

|----|----------------------------------|--------------------|---------------------------------|------------------------|-----------|-----------------------|

| 1a | 51                               | In-Zn-O            | In-Ga-Zn-O                      | PECVD $SiO_2$          | -         | Samsung [62]          |

| 1b | 104                              | In-Sn-O            | In-Ga-Zn-O                      | PECVD $SiO_2$          | -         | Samsung [62]          |

| 2  | 52                               | In-Sn-O            | Zn-Sn-O                         | PECVD $SiO_2$          | unpatt.   | Hitachi [63]          |

| 3  | 30                               | In-Zn-O            | In-Ga-Zn-O                      | PECVD $SiO_2$          | -         | Samsung [64]          |

| 4  | 15                               | $Hf-In-Zn-O^1$     | $\operatorname{Hf-In-Zn-O^{1}}$ | ${\rm Si_3N_4/SiO_2}$  | -         | Samsung [65]          |

| 5  | 10                               | Ga-Zn-O            | In-Ga-Zn-O                      | therm. $SiO_2$         | -         | KIST [66]             |

| 6  | 18                               | In-Zn-O            | In-Ga-Zn-O                      | PECVD $SiO_2$          | -         | ASU [67]              |

| 7  | 43                               | In-Sn-O            | Zn-Sn-O                         | PECVD $SiO_2$          | -         | Inha/LG $[68]$        |

| 8  | 41                               | In-Zn-O            | Hf-In-Zn-O                      | therm. $SiO_2$         | D-mode    | KIST [69]             |

| 9  | 51                               | In-O               | Ga-O                            | ALD $HfO_2$            | very thin | N. Taiwan [70]        |

| 10 | 48                               | In-Zn-O            | In-Ga-Zn-O                      | PECVD $SiO_2$          | -         | Yonsei U. [71]        |

| 11 | 48                               | In-Zn-O            | Hf-In-Zn-O                      | ${\rm Si_3N_4/SiO_2}$  | -         | Samsung $[72]$        |

| 12 | 63                               | In-Ga-Zn-O         | Ti-In-Ga-Zn-O                   | 56 nm $HfO_2$          | leaky GI? | Chiao-T. U. [73]      |

| 13 | 32                               | In-Zn-O            | Zn-Sn-O                         | PECVD $SiO_2$          | -         | Inha/LG $[74]$        |

| 14 | 84                               | $In-Ga-Zn-O^2$     | $In-Ga-Zn-O^2$                  | low-T. $SiO_2$         | unp.+GI?  | Peking U. [75]        |

| 15 | $105^{3}$                        | In-Sn-O            | Zn-Sn-O                         | low-T. $SiO_2$         | unp.+GI?  | Peking U. [76]        |

| 16 | 38                               | In-O               | In-Sn-O                         | $\mathrm{sol.}^5$ Zr-O | -         | Qingdao U. [77]       |

| 17 | 20                               | $CAAC-IGZO^4$      | In-Ga-Zn-O                      | therm. $SiO_2$         | -         | Cornell U. [78]       |

| 18 | 113                              | $Al-Sn-Zn-O^2$     | $Al-Sn-Zn-O^2$                  | low-T. $SiO_2$         | unp.+GI?  | Peking U. [78]        |

| 19 | 62                               | In-Zn-O            | In-Ga-Zn-O                      | unspecified            | -         | AMAT [79]             |

| 20 | 43                               | Zn-O:H             | Zn-O                            | therm. $SiO_2$         | -         | Wuhan U. [80]         |

| 21 | 53                               | In-Zn-O            | Al-In-Zn-Sn-O                   | PECVD $SiO_2$          | -         | ETRI [81]             |

| 22 | 134                              | Al-Sn-Zn-O         | Al-Sn-Zn-O                      | low-T. $SiO_2$         | leaky GI? | Peking U. [82]        |

Table 2.2: Summary of sputtered DAL oxide TFTs reported in the literature.

<sup>1</sup>Varied Hafnium content. <sup>2</sup>Varied O<sub>2</sub> partial pressure. <sup>3</sup>A  $\mu_{sat}$  of 292 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> is also reported. <sup>4</sup>C-axis aligned crystalline In-Ga-Zn-O. <sup>5</sup>Solution processing.

# CHAPTER 3: MOBILITY LIMITS CONSIDERATIONS