#### AN ABSTRACT OF THE THESIS OF

<u>Xin Meng</u> for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and Computer Engineering presented on May 22, 2015.</u>

Title: <u>Wideband Discrete-Time Delta-Sigma Analog-to-Digital Converters With Shifted Loop Delays.</u>

| Abstract approved: |      |  |

|--------------------|------|--|

|                    | <br> |  |

Gabor C. Temes

Low-distortion architecture is widely used in wideband discrete-time switched-capacitor delta-sigma ADC design. However, it suffers from the power-hungry active adder and critical timing for quantization and dynamic element matching (DEM). To solve this problem, this dissertation presents a delta-sigma modulator architecture with shifted loop delays. In this project, shifted loop delays (SLD) technique can relax the speed requirements of the quantizer and the dynamic element matching (DEM) block, and eliminate the active adder. An implemented 0.18 um CMOS prototype with the proposed architecture provided 81.6 dB SNDR, 81.8 dB dynamic range, and -95.6 dB THD in a signal bandwidth of 4 MHz. It dissipates 19.2 mW with a 1.6 V power supply. The conventional low-distortion ADC was also implemented on the same chip for comparison. The new circuit has superior performance, and dissipates 25% less power (19.2 mW vs. 24.9 mW) than the conventional one. The figure-of-merit for the ADC with SLD is among the best reported for wideband discrete-time ADCs, and is almost 40% better than that of the conventional ADC.

The second project describes two techniques to enhance the noise shaping function in the proposed low-distortion  $\Delta\Sigma$  modulator with shifted loop delays. One is self-noise coupling based on low-distortion  $\Delta\Sigma$  structure; the other is noise-coupled

time-interleaved  $\Delta\Sigma$  modulator. Both architectures use shifted loop delays to relax the critical timing constraints in the modulator feedback path, then to save power consumption of each block in the modulators. Two  $\Delta\Sigma$  ADCs were analyzed and simulated in a 0.18um CMOS technology. The simulation results highly verify the effectiveness of the proposed structure.

The third system describes the design technique for double-sampled wideband  $\Delta\Sigma$  ADCs with shifted loop delays (SLD). The added loop delay in the feedback branch relaxes the critical timing for DEM logic. Delay shifting can be combined with such useful techniques as low-distortion circuitry and noise coupling for wideband  $\Delta\Sigma$  modulators. The presented techniques relax the timing for inherent quantization delay, reduce the speed requirements for the critical circuit blocks, and achieve power efficiency by replacing the power-hungry blocks normally used in the modulators. Analysis of all architectures allows the choice of the most power-efficient topology for a wideband  $\Delta\Sigma$  modulator. The proposed second-order and third-order  $\Delta\Sigma$  modulators were designed and simulated to verify the effectiveness of the shifted loop delays techniques.

©Copyright by Xin Meng May 22, 2015 All Rights Reserved

# Wideband Discrete-Time Delta-Sigma Analog-to-Digital Converters With Shifted Loop Delays

by Xin Meng

#### A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented May 22, 2015 Commencement June 2015

| <u>Doctor of Philosophy</u> thesis of <u>Xin Meng</u> presented on <u>May 22, 2015</u>                                                                                                        |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                                                                                                                               |  |  |  |

|                                                                                                                                                                                               |  |  |  |

| APPROVED:                                                                                                                                                                                     |  |  |  |

|                                                                                                                                                                                               |  |  |  |

|                                                                                                                                                                                               |  |  |  |

| Major Professor, representing Electrical and Computer Engineering                                                                                                                             |  |  |  |

|                                                                                                                                                                                               |  |  |  |

|                                                                                                                                                                                               |  |  |  |

| Director of the School of Electrical Engineering and Computer Science                                                                                                                         |  |  |  |

|                                                                                                                                                                                               |  |  |  |

|                                                                                                                                                                                               |  |  |  |

| Dean of the Graduate School                                                                                                                                                                   |  |  |  |

|                                                                                                                                                                                               |  |  |  |

|                                                                                                                                                                                               |  |  |  |

|                                                                                                                                                                                               |  |  |  |

|                                                                                                                                                                                               |  |  |  |

|                                                                                                                                                                                               |  |  |  |

| I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request. |  |  |  |

|                                                                                                                                                                                               |  |  |  |

| Xin Meng, Author                                                                                                                                                                              |  |  |  |

#### **ACKNOWLEDGEMENTS**

First and foremost, I would like to express my sincere appreciation to my peerless advisor Professor Gabor C. Temes. I am deeply indebted to be given the golden opportunity to work under his supervision. It is my honor and privilege to benefit from his advice both on the technical and personal matters. He creates a free and comfortable environment and provides all the means and financial to let me pursue my own ideas and focus on my research.

Also I would like to thank Professor Alan Wang, Professor Karti Mayaram, Professor Raviv Raich and Professor Andreas Weisshaar for serving in my committee and giving lots of feedback on reading my thesis. Thanks are also due to Professor Roberto Albertani for serving as graduate council representative on my committee.

I appreciate Semiconductor Research Corporation (SRC), the Center for Design of Analog and Digital Integrated Circuits (CDIDIC), Texas Instruments and Asahi Kasei EMD for their funding on my research. I am grateful to Kaoru Takasuka, Koichi Hamashita, Tetsuro Sugimoto, Seiji Takeuchi, Mitsuru Aniya and Kazuki Sobue at Asahi Kasei EMD for their generous fabrication of my prototype chips. Useful technical feedback and discussions with Zhenyong Zhang at Texas Instruments and Qingdong Meng at Analog Devices are gratefully acknowledged.

I am indebted to all my colleagues in analog and mixed-signal group. Helpful discussions and useful advice on my research from Jinzhou Cao, Tao Wang, Tao Tong, Ramin Zanbaghi, Po-Yao Ke, Wenhuan Yu, Wei Li, Weilun Shen, Yan Wang, Jiaming Lin, Jeongseok Chae, Sanghyeon Lee, Youngho Jung, Pedram Payandehnia, and Chao Yang are appreciated.

I want to specially appreciate Zhengyong Zhang, Qingdong Meng, Raj Senguttuvan and Alex Alexeyev for their help when I worked as an intern.

Thanks to all my friends in Corvallis for the happy time we spent together. They are Kangmin Hu, Tao Jiang, Changhui Hu, Ruiqing Ye, Jiao Cheng, Hao Li, Rui Bai, Chao Ma, Chao Shi, Ce Cheng, Yue Hu, Yang Xu, Guanghua Shu, Wei Liu, Weiyang

Li, Liping Liu, Han Song, Fanghui Ren, Xiaojuan Zheng, Fang Yuan, Shan Xue, Ruirui Zhang, Wei Wang, Qi Gao, Fan Zhang, Qin Zhou, Gaole Jin, Lili Peng, Meng Li and Peng Jiang.

I am very grateful to my elder sister Xiaojing Meng, brother-in-law Zongjian Liu, my younger brother Huan Meng and my sister-in-law Xiuling Xu, for their love and supports throughout my life.

Finally, I want to express my deepest appreciation and love to my parents Qiaocheng Meng and Qiaozhi Zhang, for their genuine care, unselfish sacrifice and deep love throughout my whole my life.

# TABLE OF CONTENTS

|                                                                       | <u>Page</u> |

|-----------------------------------------------------------------------|-------------|

| 1. Introduction                                                       | 1           |

| 1.1. Motivation                                                       | 1           |

| 1.2. Contributions of this Research                                   | 3           |

| 1.3. Organization of the Dissertation                                 | 4           |

| 2. Low-Power Wideband Discrete-Time Delta-Sigma ADCs with Shifted Loc | р           |

| Delays                                                                | -           |

| 2.1. Introduction                                                     | 8           |

| 2.2. Architecture Considerations                                      | 9           |

| 2.3. Circuit Implementation                                           | 16          |

| 2.4. Measurement Results                                              | 22          |

| 2.5. Summary                                                          | 30          |

| 3. Noise Shaping Enhanced Delta-Sigma ADCs with Shifted Loop Delays   | 32          |

| 3.1. Introduction                                                     | 32          |

| 3.2. Self-Noise-Coupled $\Delta\Sigma$ ADC with SLD                   | 34          |

| 3.2.1 Architecture Considerations                                     | 34          |

| 3.2.2 SC Circuit Implementation                                       | 37          |

| 3.2.3 Simulation Results                                              | 39          |

| 3.3. Noise-Coupled Time-Interleaved $\Delta\Sigma$ ADC with SLD       | 42          |

| 3.3.1 Architecture Considerations                                     | 42          |

| 3.3.2 SC Circuit Implementation                                       | 46          |

| 3.3.3 Simulation Results                                              | 46          |

# TABLE OF CONTENTS (Continued)

| <u>Pa</u>                                                            | <u>ige</u> |

|----------------------------------------------------------------------|------------|

| 3.4. Summary                                                         | 50         |

| 4. Double-Sampled Wideband Delta-Sigma ADCS with Shifted Loop Delays | 53         |

| 4.1. Introduction                                                    | 53         |

| 4.2. Architecture Considerations                                     | 55         |

| 4.3. Second-order $\Delta\Sigma$ ADC with SLD                        | 59         |

| 4.3.1. Proposed Architecture                                         | 59         |

| 4.3.2 Transfer Functions                                             | 60         |

| 4.3.3 Circuit Implementation                                         | 61         |

| 4.3.4 Simulation Results                                             | 62         |

| 4.4. Third-order $\Delta\Sigma$ ADC with SLD                         | 65         |

| 4.4.1 Proposed architectures                                         | 65         |

| 4.4.2 Transfer functions                                             | 69         |

| 4.4.3 Circuit Implementation                                         | 69         |

| 4.4.4 Simulation Results                                             | 70         |

| 4.5. Summary                                                         | 72         |

| APPENDIX                                                             | 75         |

### LIST OF FIGURES

| <u>Figure</u> <u>Page</u>                                                                           |

|-----------------------------------------------------------------------------------------------------|

| Figure 1.1: Feed-forward low-distortion $\Delta\Sigma$ ADC.                                         |

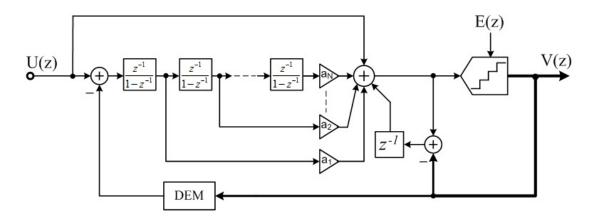

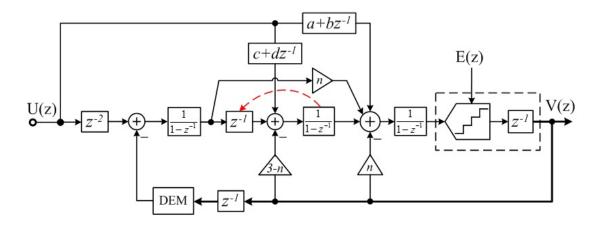

| Figure 2.1: Conventional $\Delta\Sigma$ low-distortion modulator [1]                                |

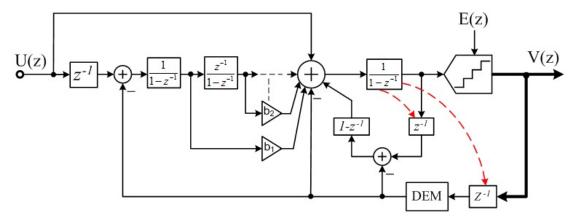

| Figure 2.2: Shifted loop delays in the CIFB-CIF topology [6]                                        |

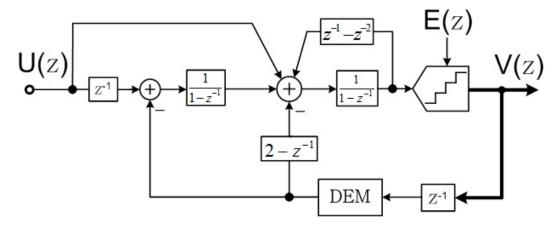

| Figure 2.3: Low-distortion $\Delta\Sigma$ ADC with Shifted loop delays [7]                          |

| Figure 2.4: Conventional third-order low-distortion $\Delta\Sigma$ modulator                        |

| Figure 2.5: Proposed third-order low-distortion $\Delta\Sigma$ modulator with SLD                   |

| Figure 2.6: Simulated spectra of the node voltage in Figure 2.5                                     |

| Figure 2.7: Single-ended SC circuit implementation of the proposed modulator with SLD of Figure 2.4 |

| Figure 2.8: Telescopic cascode opamp with SC common-mode feedback                                   |

| Figure 2.9: Bootstrapped clock generator (a) simplified diagram; (b) detailed circuit.              |

| Figure 2.10: Comparator block diagram                                                               |

| Figure 2.11: Clock generator diagram                                                                |

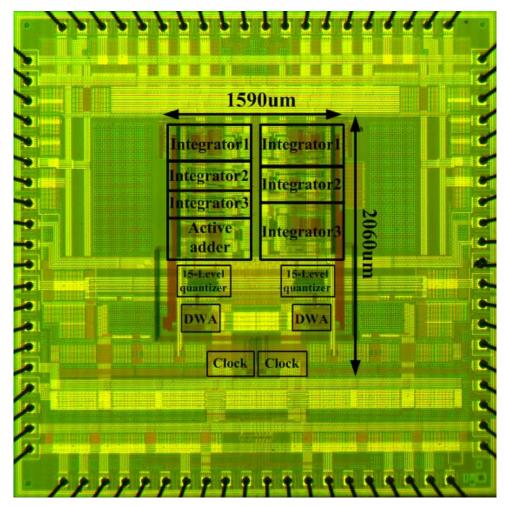

| Figure 2.12: Chip micrograph for both modulators                                                    |

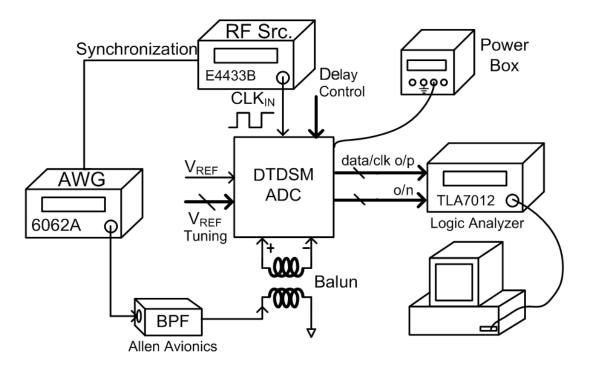

| Figure 2.13: Test bench for chip measurement                                                        |

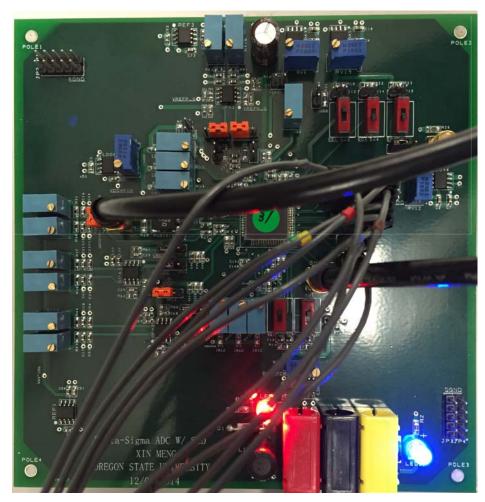

| Figure 2.14: Test board for ADC measurement                                                         |

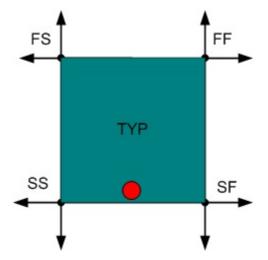

| Figure 2.15: Chip corner                                                                            |

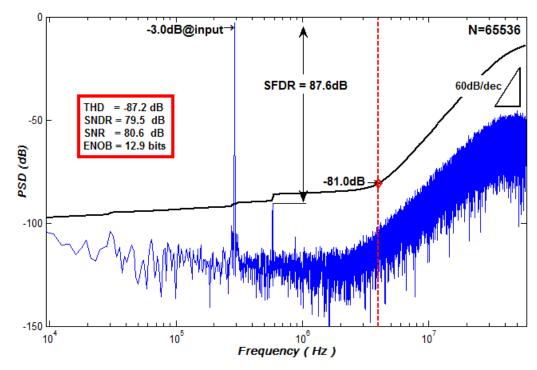

| Figure 2.16: Measured spectrum at peak SNDR for the conventional $\Delta\Sigma$ modulator.25        |

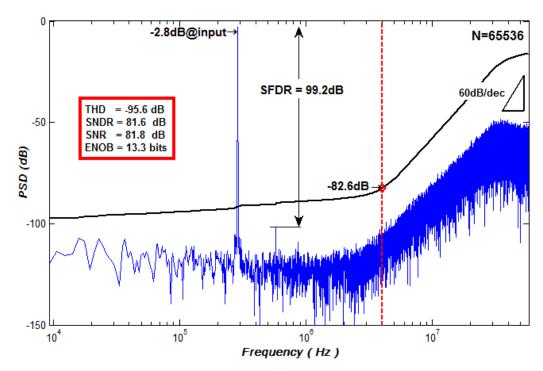

| Figure 2.17: Measured spectrum at peak SNDR for $\Delta\Sigma$ modulator with SLD 25                |

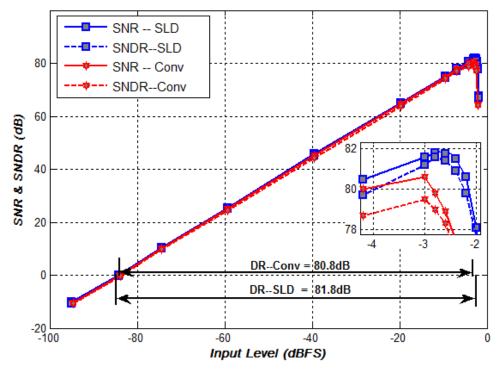

| Figure 2.18: SNR and SNDR variations with input signal power                                        |

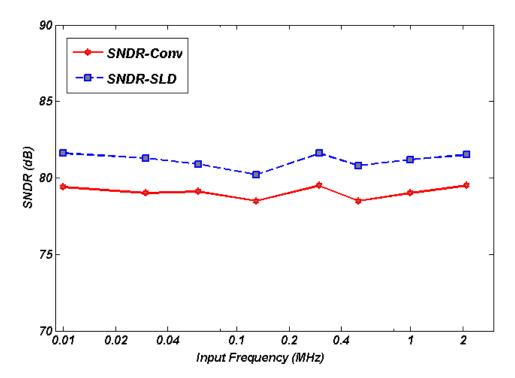

| Figure 2.19: Measured SNDR variations with input signal frequencies                                 |

| Figure 2.20: Power consumption breakdown for the proposed ADC with SLD 28                           |

# LIST OF FIGURES (Continued)

| <u>Figure</u> <u>Page</u>                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.21: Measured spectrum at peak SNDR for $\Delta\Sigma$ modulator with SLD in 5 MHz Bandwidth.                              |

| Figure 3.1: Feed-forward low-distortion $\Delta\Sigma$ ADC.                                                                        |

| Figure 3.2: Low-distortion $\Delta\Sigma$ ADC with extra loop delays [12]                                                          |

| Figure 3.3: Block diagram of the low-distortion self noise-coupled $\Delta\Sigma$ ADC 35                                           |

| Figure 3.4: Low-distortion self noise-coupled $\Delta\Sigma$ ADC with shifted loop delays 35                                       |

| Figure 3.5: Low-distortion noise-coupled $\Delta\Sigma$ ADC with shifted loop delays [13] 36                                       |

| Figure 3.6: Improved noise-coupled $\Delta\Sigma$ ADC with shifted loop delays                                                     |

| Figure 3.7: SC implementation of the first integrator in the proposed modulator 38                                                 |

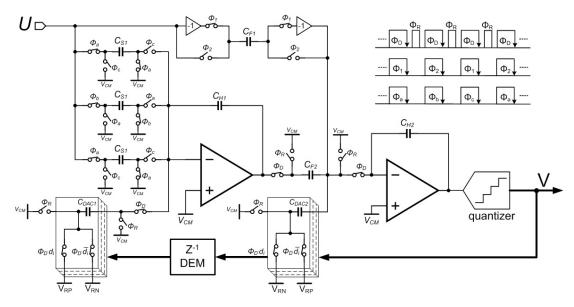

| Figure 3.8: Single-ended circuit diagram of proposed self-noise-coupled low-distortion $\Delta\Sigma$ ADC with shifted loop delays |

| Figure 3.9: Simulated spectra of the node voltages of the circuit of Figure 3.6 40                                                 |

| Figure 3.10: PSD of the output signal of the two $\Delta\Sigma$ ADCs W/ and W/O SLD 41                                             |

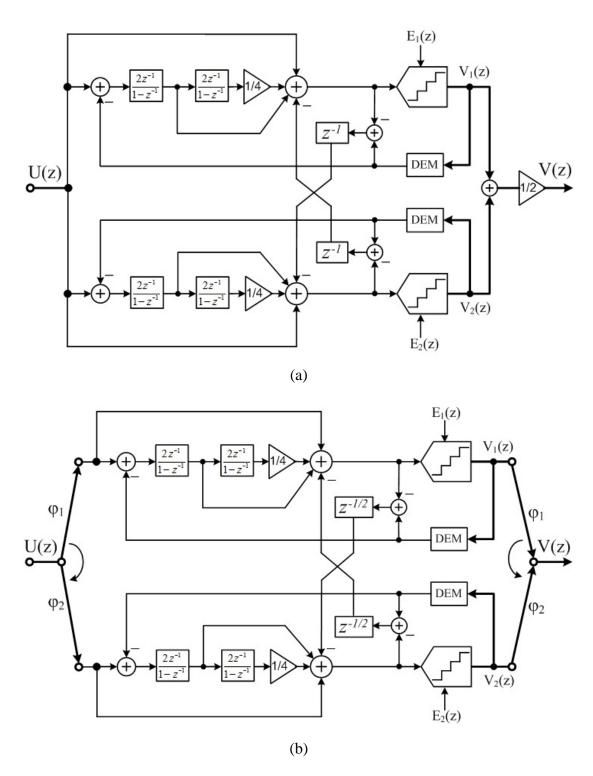

| Figure 3.11: (a) noise-coupled split modulator; (b) noise-coupled time-interleaved (NCTI) modulator                                |

| Figure 3.12: The proposed low-distortion noise-coupled time-interleaved (NCTI) $\Delta\Sigma$ ADC with shifted loop delays         |

| Figure 3.13: The single-ended circuit diagram of the proposed NCTI $\Delta\Sigma$ ADC with shifted loop delays.                    |

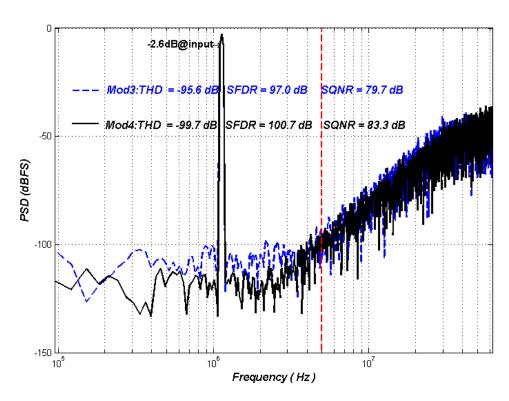

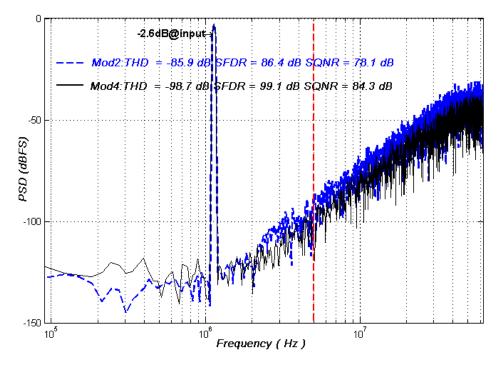

| Figure 3.14: Simulated PSDs for comparison between Mod3 and Mod4 49                                                                |

| Figure 3.15: Simulated PSDs for comparison between Mod2 and Mod4 50                                                                |

| Figure 4.1: Low-distortion $\Delta\Sigma$ ADC with embedded-adder quantizer [4] 54                                                 |

| Figure 4.2: Second-order $\Delta\Sigma$ modulator with relaxed DEM timing [10]                                                     |

| Figure 4.3: Conventional low-distortion double-sampled $\Delta\Sigma$ ADC                                                          |

| Figure 4.4: Single-ended version of a double-sampled SC integrator                                                                 |

# LIST OF FIGURES (Continued)

| <u>Page</u>                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 4.5: Proposed low-distortion double-sampled $\Delta\Sigma$ ADC with shifted loop delays.                                             |

| Figure 4.6: SC implementation for the first integrator in the proposed $\Delta\Sigma$ modulator                                             |

| Figure 4.7: Proposed double-sampled $\Delta\Sigma$ modulator with shifted loop delays 60                                                    |

| Figure 4.8: single-ended circuit diagram of proposed double-sampled low-distortion $\Delta\Sigma$ ADC.                                      |

| Figure 4.9: Simulated results of spectrums for the node voltages                                                                            |

| Figure 4.10: Simulated PSD of the single-sampled $\Delta\Sigma$ modulator                                                                   |

| Figure 4.11: Simulated PSD of the double-sampled $\Delta\Sigma$ modulator                                                                   |

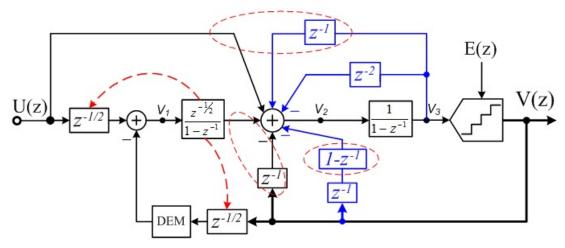

| Figure 4.12: Noise-coupled double-sampled $\Delta\Sigma$ ADC with shifted loop delays 66                                                    |

| Figure 4.13: Double-sampled third-order $\Delta\Sigma$ ADC with shifted loop delays 66                                                      |

| Figure 4.14: Double-sampled third-order $\Delta\Sigma$ ADC with improved feedback factor 66                                                 |

| Figure 4.15: Double-sampled third-order $\Delta\Sigma$ ADC with delayed integrator 67                                                       |

| Figure 4.16: Double-sampled third-order $\Delta\Sigma$ ADC with shifted loop delays in the second and the third integrators.                |

| Figure 4.17: Most power-efficient double-sampled third-order $\Delta\Sigma$ ADC with shifted loop delays.                                   |

| Figure 4.18: Single-ended circuit diagram of proposed double-sampled low-distortion third-order $\Delta\Sigma$ ADC with shifted loop delays |

| Figure 4.19: Clock phases for the circuit of Figure 4.18                                                                                    |

| Figure 4.20: Simulated PSD of the node voltages in the proposed double-sampled $\Delta\Sigma$ ADC                                           |

| Figure 4.21: Simulated PSD of the proposed double-sampled $\Delta\Sigma$ ADC output signal.                                                 |

# LIST OF TABLES

| Table                                                                           | <u>Page</u> |

|---------------------------------------------------------------------------------|-------------|

| Table 2.1: Comparison Between $\Delta\Sigma$ ADCs in Figures 2.4 and 2.5        | 15          |

| Table 2.2: Simulated performance for the first integrator opamp                 | 18          |

| Table 2.3: Performance Summary of the SLD Versus Conventional ADCs              | 27          |

| Table 2.4: Performance Summary of the SLD Versus Conventional ADCs              | 28          |

| Table 2.5: Performance Comparison With Other DT $\Delta\Sigma$ ADCs             | 29          |

| Table 3.1 Comparison Between Noise-Coupled $\Delta\Sigma$ ADCs W/ and W/O SLD   | 40          |

| Table 3.2 Comparison Between Noise-Coupled Time-Interleaved $\Delta\Sigma$ ADCs | 47          |

| Table 3.3: Comparison of Simulation Results with -2.6 dBFS Input Sigmal         | 49          |

| Table 4.1 Coefficients and feedback factors in Figure 4.16                      | 68          |

# LIST OF APPENDIX FIGURES

| <u>Figure</u>                                                 | <u>Page</u> |

|---------------------------------------------------------------|-------------|

| Figure A.1: Cascaded stages separated by a delay and a switch | 76          |

| Figure A.2: Delay-free cascaded integrators.                  | 77          |

| Figure A.3: Single-end circuit of the single-pole system.     | 78          |

| Figure A.4: Cascaded delayed integrators with three stages.   | 78          |

| Figure A.5: Cascaded delay-free integrators with three stages | 79          |

### Wideband Discrete-Time Delta-Sigma Analog-to-Digital Converters With Shifted Loop Delays

#### **CHAPTER 1. INTRODUCTION**

#### 1.1. Motivation

Hearing and seeing are real-time transmissions in the human senses. State-of-art technologies, like Hi-Fi audio system [1], high efficiency video coding and 3D video [2], are utilized to achieve high-quality audios and videos sources. When transmitting the media signal, increasing bandwidth of telecommunication channel has relieves the speed bottleneck of releasing 720p or higher-resolution videos. In the receiving terminals, smart phones, tablets and HDTV offer higher pixel density to match the audios' and videos' resolution. The whole industrial chain of transmitting media signals emphasizes an increasing market on the high-speed high-resolution analog and digital interface circuits, especially data converters.

On the other hand, portable devices are becoming more and more popular in media world because of providing one more freedom by getting rid of electric cables. However, battery-powered mobile devices restrict this unplugging to a limited time usage because of its demand on recharging. It is very common for people to expect longer battery time, which emphasizes low-power property in all electronics chips, including data converters.

Data converters are constructing a bridge between the analog world (the physical world) and digital world (the data world). With down-scaling of transistors' size, data converters, including analog-to-digital converters (ADC) and digital-to-analog converters (DAC), are become a performance bottleneck in an on-chip system. In deep submicrometer CMOS technologies, compared to other ADC counterparts, delta-sigma ( $\Delta\Sigma$ ) modulators, because of their inherent oversampling and noise shaping, are becoming popular in high-resolution bandwidth application. In this

thesis, we describe some new techniques and architectures to design a high-speed, high-resolution, low-power delta-sigma ADCs.

There are two realizations for  $\Delta\Sigma$  modulators: continuous-time (CT) modulators and discrete-time (DT) modulators. CT modulators are becoming more and more popular in wideband applications because of several advantages: 1. easy to drive from external sources; 2. higher permissible frequency; 3. inherently anti-alias filter; 4. integrator operational transconductance amplifiers (OTAs) consume less power than DT counterparts. For 10 MHz or higher signal bandwidth applications, CT modulators have often been used [3]-[10]. However, compared with DT  $\Delta\Sigma$  ADCs, the design of CT  $\Delta\Sigma$  modulators is complex and challenging. CT ADCs are very sensitive to clock jitter noise; this situation becomes worse when the feedback DAC uses return-to-zero pulses. The loop filter transfer function is suffering from the large coefficient uncertainty due to variations of resistors and capacitors referring to process, voltage and temperature (PVT). The stability of the loop filter is degrading because of the excess feedback loop delay.

So far, most commercial  $\Delta\Sigma$  ADCs use traditional DT realization, based on switched capacitor (SC) circuitry. The loop filter of DT  $\Delta\Sigma$  modulators can be easily analyzed and designed in z-domain, and the design procedure is well developed [11] [12]. Pole-zero locations of the loop filter are set by precise capacitor ratios, which are highly accurate and insensitive to process variation. DT modulators offer robust operation and are insensitive to clock jitter, as long as complete settling occurs. However, DT modulators require large switched input capacitors to lower kT/C noise, and hence are difficult to drive form external sources. Furthermore, the settling requirements of OTAs have to trade off with the power consumption of OTAs, which is limited by the sampling frequency and bandwidth of DT  $\Delta\Sigma$  ADCs. Along with the increasing signal bandwidth, the power dissipation of each integrator increases rapidly. Even so, recently published low-power DT  $\Delta\Sigma$  ADCs could achieve 10 to 25 MHz bandwidth [13]-[16]. In this thesis, we describe some new techniques and architectures to expand the bandwidth and lower the power consumption for wideband DT  $\Delta\Sigma$  ADCs.

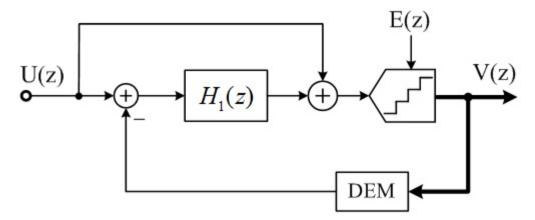

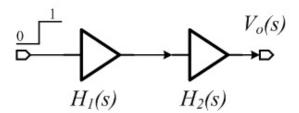

Figure 1.1: Feed-forward low-distortion  $\Delta\Sigma$  ADC.

#### 1.2. Contributions of This Research

In conventional DT  $\Delta\Sigma$  modulators, high quantizer resolution and high loop filter order helps to provides high resolution and linearity. However, finite OTA gain and nonlinear slew-rate of integrators cause harmonic components in the digital output. One effective solution to attenuate the harmonics is higher oversampling ratio (OSR). But the OSR cannot be too high, since then high-speed OTAs will be much power-hungry in wideband applications. Another effective method to greatly attenuate the harmonics is adding a direct feed-forward path from the input signal to the quantizer, making STF = 1. This structure is called the low-distortion modulator, shown in Figure 1.1. The linearity requirements of this architecture are relaxed by cancelling the signal components in the loop filter  $H_1(z)$  [17]. This situation gets even better when using multi-bit quantizer, because the quantization error is reducing further. And the DEM technique is required to improve the linearity of the feedback DAC in a multi-bit modulator. However, the processing time is restricted for the quantizer and DEM operation in the low-distortion modulator.

In this thesis, shifting loop delays technique is described to release the critical timing issue for the quantizer and DEM operation. Furthermore, the active adder is also eliminated by this technique. The major contributions of this research are summarized as follows:

- 1. A novel power-efficient  $\Delta\Sigma$  modulator with shifted loop delays is proposed. In this new architecture, the speed of quantizer and DEM logic can be greatly reduced. To verify the effectiveness, a conventional DT low-distortion  $\Delta\Sigma$  modulator are also designed and fabricated in a 0.18 um CMOS process to make the comparison.

- 2. Noise shaping enhancement techniques are demonstrated in the novel  $\Delta\Sigma$  modulators. Two discrete-time  $\Delta\Sigma$  modulator topologies combined with shifted loop delays (SLD) are proposed. One is self-noise coupling based on low-distortion  $\Delta\Sigma$  modulator; the other one is noise-coupled time-interleaved structure. Both architectures are analyzed and simulated in a 0.18um CMOS technology to verify the effectiveness.

- 3. Shifting loop delays can also used in double-sampled wideband  $\Delta\Sigma$  ADCs. Combining double sampling with shifted loop delays, the proposed modulators can relax the critical timing constraints in the modulator feedback path. In a 0.18um CMOS technology, a second-order and a third-order noise shaping  $\Delta\Sigma$  ADCs were analyzed and simulated.

### 1.3. Organization of the Dissertation

This thesis presents the design of wideband discrete-time  $\Delta\Sigma$  modulators in an advanced deep sub-micron CMOS technique. By shifting loop delays, several low-power high-performance  $\Delta\Sigma$  ADCs are designed and analyzed. Both system level and transistor level design are covered in each modulator; and simulation results and measurement results are illustrated to verify the effectiveness of the proposed architectures. The thesis is organized as follows:

Chapter 2 introduces a novel low-distortion feed-forward  $\Delta\Sigma$  modulator with shifted loop delays. This architecture relaxes the critical feedback timing issue by shifting one loop delay from the loop filter to the feedback path. The speed of quantizer and DEM logic can be greatly reduced, hence to save power consumptions of each integrator, quantizer and DEM logic. One extra feedback path is fed back into the last integrator to improve the loop stability and make the STF equal to be unity.

The transistor level circuits are also introduced; the simulation results and measurement results are illustrated.

Chapter 3 describes two techniques to enhance the noise shaping function in the proposed low-distortion  $\Delta\Sigma$  modulator with shifted loop delays. One is self-noise coupling based on low-distortion  $\Delta\Sigma$  structure; the other is noise-coupled time-interleaved  $\Delta\Sigma$  modulator. Both architectures use shifted loop delays to relax the critical timing constraints in the modulator feedback path, then to save power consumption of each block in the modulators. Two  $\Delta\Sigma$  ADCs were analyzed and simulated in a 0.18um CMOS technology. The simulation results highly verify the effectiveness of the proposed structure.

Chapter 4 presents several discrete-time double-sampled  $\Delta\Sigma$  ADCs with shifted loop delays. The proposed architectures use the shifted loop delays to compensate the inherent quantization delay. The added loop delay in the feedback branch helps to relax the critical timing for DEM logic. Delay shifting can be combined with such useful techniques as low-distortion circuitry and noise coupling for wideband double-sampled  $\Delta\Sigma$  modulators. The presented techniques reduce the speed requirements for the critical circuit blocks, and achieve power efficiency by replacing the power-hungry blocks normally used in the modulators. Analysis of all architectures allows the choice of the most power-efficient topology for a wideband  $\Delta\Sigma$  modulator. The proposed second-order and third-order  $\Delta\Sigma$  modulators were designed and simulated to verify the effectiveness of the shifted loop delays techniques.

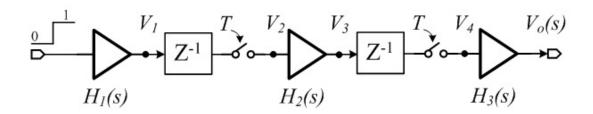

The appendix analyzes the settling operation of cascaded integrators. By comparing delayed integrators and delay-free integrators, the penalty for removing the delay from two cascaded integrators is estimated. For a 0.1% resolution, two-stage cascaded delay-free integrators consume 21% more power consumption and three-stage ones take 40% more.

#### References

- [1] F. Fernandez-Martinez, J. Ferreiros, J. M. Lucas-Cuesta, J. D. Echeverry, R. San-Segundo and R. de Cordoba, "Flexible, robust and dynamic dialogue modeling with a speech dialogue interface for controlling a hi-Fi audio system", *Database and expert systems applications*, pp. 250-254, 2010.

- [2] H. Kalva, A. Bocik, H. Chen, K. Egiazarian and Z. Wang, "Introduction to the issue on perception inspired video processing", *IEEE Journal of selected topics in signal processing*, vol. 8, no. 3, pp. 355-357, 2014.

- [3] S. Paton, A. Giandomenico, L. Hemandez, A. Wiesbauer, T. Potscher and M. Clara, "A 70-mW 300-MHz CMOS continuous-time  $\Sigma\Delta$  ADC with 15-MHz bandwidth and 11 bits of resolution," *IEEE J. Solid-State Circuits*, vol. 39, no. 7, pp. 1065-1063, 2004.

- [4] T. C. Caldwell and D. A. Johns, "A time-interleaved continuous-time  $\Delta\Sigma$  modulator with 20 MHz sigmal bandwidth," *Proceedings of the European, Solid-State Circuits Conference, ESSCIRC*, pp. 447-450, Sep. 2005.

- [5] X. Chen, Y. Wang, Y. Fujimoto, P.L. Re, Y. Kanazawa, J. Steensgaard and G. Temes, "A 18 mW CT ΔΣ Modulator with 25 MHz Bandwidth for Next Generation Wireless Applications," *IEEE Custom Integrated Circuits Conference (CICC)*, pp. 73–76, Sep. 2007.

- [6] M. Park and M. H. Perrott, "A 0.13 um CMOS 78 dB SNDR 87 mW 20 MHz BW CT ΔΣ ADC with VCO-based integrator and quantizer," *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, pp. 170–171, Feb. 2009.

- [7] V. Singh, N. Krishnapura, S. Pavan, B. Vigraham, N. Nigania, and D. Behera, "A 16MHz BW 75dB DR CT ΔΣ ADC Compensated for More Than One Cycle Excess Loop Delay," *IEEE Custom Integrated Circuits Conference* (*CICC*), pp. 1–4, Sep. 2011.

- [8] K. Reddy, S. Rao, R. Inti, B. Young, A. Elshazly, M. Talegaonkar and P. K. Hanumolu, "A 16mW 78dB-SNDR 10 MHz-BW CT- ΔΣ ADC using residue-cancelling VCO-based quantizer," *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, pp. 152–154, Feb. 2012.

- [9] H. Chae and M. P. Flynn, "A 69 dB SNDR 25 MHz BW, 800 MS/s continuous-time bandpass  $\Delta\Sigma$  ADC using DAC duty cycle control for low power and reconfigurability," *Symposium on VLSI Circuits*, pp. C62–C63, Jun. 2013.

- [10] M. Englund, K. B. Ostman, O. Viitala, M. Kaltiokallio, K. Stadius, K. Koli and J. Ryynanen, "28.1 A programmable 0.7-to-2.7 GHz direct ΔΣ receiver in 40nm CMOS," *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, pp. 470–471, Feb. 2014.

- [11] S. Norsworthy, R. Schreier and G. C. Temes, *Delta-Sigma Data Converters: Theory, Design and simulation.* New York: Wiley, 1996.

- [12] R. Schreier and G. C. Temes, *Understanding Delta-Sigma Data Converters*. New York: Wiley, 2004.

- [13] P. Balmelli and Q. Huang, "A 25MS/s 14 b 200 mW  $\Sigma\Delta$  modulator in 0.18 um CMOS," *IEEE J. Solid-State Circuits*, vol. 39, no. 12, pp. 2161-2169, 2004.

- [14] Y. Fujimoto, Y. Kanazawa. P. Lo Re and M. Miyamot, "An 80/100MS/s 76.3/70.1dB SNDR  $\Delta\Sigma$  ADC for Digital TV Receivers," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, pp. 76-77, Feb. 2006.

- [15] P. Malla, H. Lakdawala, K. Kornegay and K. Soumyanath, "A 28mW Spectrum-Sensing Reconfigurable 20MHz 72dB-SNR 70dB-SNDR DT ΔΣ ADC for 802.11n/WiMAX Receivers," *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, pp. 496-497, Feb. 2008.

- [16] J. Chae, S. Lee, M. Aniya, S. Takeuchi, K. Hamashita, P.K. Hanumolu, and G.C. Temes, "A 63 dB 16 mW 20 MHz BW Double-Sampled ΔΣ Analog-to-Digital Converter with an Embedded-Adder Quantizer," *IEEE Custom Integrated Circuits Conference (CICC)*, pp. 1–4, Sep. 2010.

- [17] J. Silva, U. Moon, J. Steensgaard and G.C. Temes, "Wideband low-distortion delta-sigma ADC topology", *Electrons Letters*, vol. 37, No.12, pp. 737-738, 2001.

# CHAPTER 2 . LOW-POWER WIDEBAND DISCRETE-TIME DELTA-SIGMA ADCs WITH SHIFTED LOOP DELAYS

Low-distortion architecture is widely used in wideband discrete-time switched-capacitor delta-sigma ADC design [1]. However, it suffers from the power-hungry active adder and critical timing for quantization and dynamic element matching (DEM). In this chapter, shifted loop delays (SLD) technique is described to solve these problem. It can relax the speed requirements of the quantizer and the DEM block, and eliminate the last stage adder. To verify the effectiveness, the proposed architecture was implemented in 0.18 um CMOS. The conventional low-distortion ADC was also implemented on the same chip for comparison. The new circuit has superior performance, and dissipates 25% less power than the conventional one.

#### 2.1. Introduction

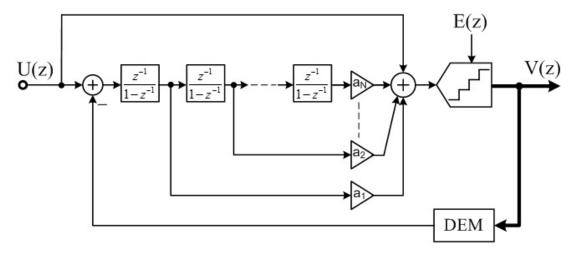

With increasing market for battery-powered portable electronics in wireless communications and high-definition media applications, high-performance low-power analog-to-digital converters (ADCs) need to meet stringent specifications. Delta-sigma ( $\Delta\Sigma$ ) modulators, because of their inherent oversampling and noise shaping, are well suited for medium-to-high resolution and MHz-bandwidth applications [2-4]. For discrete-time realization, the low-distortion  $\Delta\Sigma$  ADC with feed-forward structure in Figure 2.1 is widely used in wideband application. The input signal U passes through the feed-forward branch, the quantizer and the DEM. When U arrives at the first integrator, it cancels the input signal, leaving only the shaped quantization noise. Hence the modulator can achieve high linearity by eliminating input signal component in its loop filter [1]. The linearity requirements for all integrators are even more relaxed when using multi-bit quantizer. However, the drawback is the need for a power hungry active adder and an additional time slot required for the quantization and the DEM circuitry. These issues become even more challenging with increasing signal bandwidth.

Figure 2.1: Conventional  $\Delta\Sigma$  low-distortion modulator [1].

In this chapter, a shifted-loop-delay (SLD) architecture is proposed to solve these problems. It allows more time for quantization and DEM without degrading its loop stability, and reduces power consumption by eliminating the active adder [5]. A low-distortion  $\Delta\Sigma$  ADC with SLD and its conventional counterpart, implemented in 0.18  $\mu$ m CMOS technology are reported. The measured results verify that the ADC with SLD can achieve improved performance and dissipates less power than not only the conventional one, but also the state-of-the-art published ADCs. Section 2.2 introduces the shifted loop delays in  $\Delta\Sigma$  ADCs, providing a general design procedure for loop filters with maximally flat noise transfer function (NTF). Design details and circuit implementation for two prototypes follow in Section 2.3. The measured results that verify the effectiveness of the proposed architecture are described in section 2.4. Finally, section 2.5 draws the summary of the implementation.

#### 2.2. Architecture Considerations

A modulator with shifted loop delay was first introduced in [6], as a "cascade of integrators with distributed feedback topology with capacitive input feed-forward (CIFB-CIF)." Figure 2.2 shows a second-order CIFB-CIF  $\Delta\Sigma$  modulator using two OTAs. In this topology, one cycle delay of the last integrator is shifted to the first stage and also to the feedback path. The delay shifted to the first stage helps to avoid making the second integrator two-pole system, and makes it still delayed integrator.

Figure 2.2: Shifted loop delays in the CIFB-CIF topology [6].

Figure 2.3: Low-distortion  $\Delta\Sigma$  ADC with Shifted loop delays [7].

However, it still suffers from restricted timing; and it also needs complex feed-forward paths to retain the low-distortion property. This requires a larger capacitor area and more involved timing logic, and also consumes more power consumption due to the small feedback factor ( $\beta = 1/7$ ) of the last integrator.

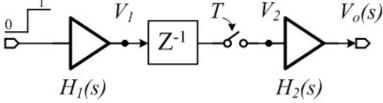

Next, we proposed shifted loop delay topologies to relax timing and power [7]. The basic idea is moving the delay of the last integrator to the feedback path, so that DEM can be performed in this delay. Also the modulator shifts the delay from the first integrator to the input signal path to keep the low-distortion property. To restore the stability affected by the shifted loop delays, an extra feedback path is also introduced to the last integrator. Figure 2.3 shows the resulting block diagram. Here,  $b_0$  is the gain of the added feedback branch;  $b_1$  and  $b_2$  are the coefficients of the feedforward paths.

The general design procedure to obtain the coefficients in Figure 2.3 is as follows. For a low-distortion DT  $\Delta\Sigma$  ADC with  $N^{\text{th}}$ -order noise shaping (Figure 2.1), the loop gain H(z) is

$$H(z) = \sum_{i=1}^{N} \frac{a_i}{(z-1)^i}$$

(2.1)

Here,  $a_N$  is usually set to 1. The noise transfer function is

$$NTF(z) = \frac{1}{1 + H(z)} \tag{2.2}$$

Matching the loop gains H(z) of the two systems shown in Figures 2.1 and 2.3 gives

$$\sum_{i=1}^{N} a_i I^i(z) = \frac{1}{1 - z^{-1}} \left[ b_0 z^{-1} + \sum_{i=1}^{N-1} b_i I^i(z) \right]$$

(2.3)

Here

$$I(z) = \frac{z^{-1}}{1 - z^{-1}} \tag{2.4}$$

Equation (2.3) can be re-arranged as

$$\sum_{i=1}^{N} a_i I^i(z) = I(z) b_0 + \sum_{i=1}^{N-1} \left[ b_i (I^i(z) + I^{i+1}(z)) \right]$$

(2.5)

For z = 0, I(0) = -1, so (2.5) gives

$$b_0 = \sum_{i=1}^{N} a_i (-1)^{i+1}$$

(2.6)

From (2.1) and (2.2),

$$b_0 = -H(0) = 1 - \frac{1}{NTF(0)} = 1$$

(2.7)

Thus,  $b_0$  is always equal to 1, regardless of the order of the modulator.

In matrix notation

$$\begin{bmatrix} a_{1} \\ a_{2} \\ a_{3} \\ M \\ a_{N-1} \\ a_{N} \end{bmatrix}^{T} \begin{bmatrix} I(z) \\ I^{2}(z) \\ I^{3}(z) \\ M \\ I^{N-1}(z) \\ I^{N}(z) \end{bmatrix} = \begin{bmatrix} b_{0} + b_{1} \\ b_{1} + b_{2} \\ b_{2} + b_{3} \\ M \\ b_{N-2} + b_{N-1} \\ b_{N-1} \end{bmatrix}^{T} \begin{bmatrix} I(z) \\ I^{2}(z) \\ I^{3}(z) \\ M \\ I^{N-1}(z) \\ I^{N}(z) \end{bmatrix}$$

(2.8)

Matching the coefficients of  $I^{i}(z)$  in (2.5) gives

$$\begin{bmatrix} a_1 \\ a_2 \\ M \\ a_{N-1} \\ a_N \end{bmatrix} = \begin{bmatrix} 1 & 1 & 0 & L & 0 \\ 0 & 1 & 1 & L & 0 \\ M & M & M & O & M \\ 0 & 0 & L & 1 & 1 \\ 0 & 0 & L & 0 & 1 \end{bmatrix} \begin{bmatrix} b_0 \\ b_1 \\ M \\ b_{N-2} \\ b_{N-1} \end{bmatrix}$$

(2.9)

By inspection,

$$b_i = a_i - b_{i-1}$$

(i = 1,2,L, N-2) (2.10)

$$b_{N-1} = a_N (2.11)$$

All  $b_i$  can be found directly from (7) and (9).

The linear model of a low-distortion  $\Delta\Sigma$  modulator with SLD is shown in Figure 2.3. The delay of the last integrator is moved to the feedback path, so that the quantization and DEM can be performed in this period. Also, the modulator shifts the delay from the loop filter to the input signal path and introduces an extra feedback path to the summing node of the last integrator, so that the stability of the loop is preserved. The proposed scheme still uses a direct feed-forward path from the input to the last integrator to keep the low-distortion property. However, it utilizes the last integrator to achieve both integration and active summation, hence eliminating the active adder. As shown in equation 2.10 and 2.11, the order of the loop filter transfer function can be one less than that in Figure 2.1.

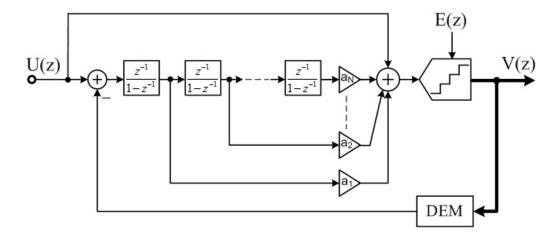

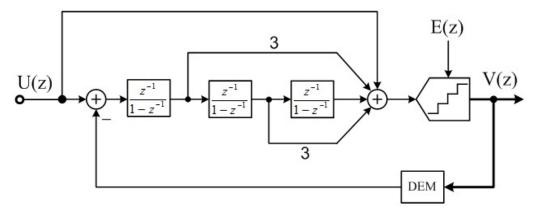

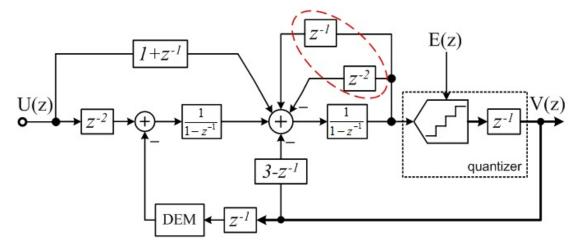

Figure 2.4: Conventional third-order low-distortion  $\Delta\Sigma$  modulator.

Figure 2.5: Proposed third-order low-distortion  $\Delta\Sigma$  modulator with SLD.

To further verify the effectiveness of the proposed SLD architecture, two third-order  $\Delta\Sigma$  modulator are analyzed. Figure 2.4 illustrates a conventional third-order low-distortion  $\Delta\Sigma$  modulator. The quantization and DEM must be performed in the non-overlapping time slot. The extra time needed by the quantization and the DEM shortens the settling time, hence requires higher speed for all blocks, including the integrators, the quantizer and the DEM logic. To alleviate this problem, in the proposed third-order modulator (Figure 2.5), one delay is moved from the last integrator to the feedback path, so that the quantizer and the DEM logic can operate in one clock period, and the non-overlapping time slot can be compressed to minimum.

In the proposed ADC, the input signal U passes through the feed-forward branch, the last integrator, the quantizer and the DEM. When U arrives at the first

integrator, it cancels the signal travelling through the other delayed path. Thus the input signal of the loop filter does not contain the input signal, and the reduced signal swing and the low-distortion property of the conventional feed-forward ADC are preserved. The multi-bit (15-level) quantizer DAC further reduces the input/output swings of the integrators in the loop filter, and improves the modulator stability.

To keep the modulator stable, an extra feedback path is connected to the input of the last integrator (Figure 2.5). A first-order noise shaping function  $(1-z^{-1})$  is applied to the input signal U(z), when combining this feedback path and the feedforward path. After passing through the delay-free integrator,  $(1-z^{-1})U(z)$  will be again equal to U(z), which makes the signal transfer function unity. The stability of the proposed modulator, its dynamic range and harmonic suppression are all improved because of the reduced signal swings at the internal nodes of the loop filter. An additional advantage is that the injected quantization noise works as a dither signal. Thus the proposed topology provides increased stability, as well as reduced idle tones and harmonic spurs [8].

Linear analysis of the modulator in Figure 2.5, given below, verifies the previous conclusions. It shows that there is only shaped quantization noise at the input of the loop filter, and that the signal swing at the input of the last integrator is also shaped:

$$V(z) = U(z) + (1 - z^{-1})^{3} E(z)$$

(2.12)

$$V_1(z) = -z^{-1}(1-z^{-1})^3 E(z)$$

(2.13)

$$V_{2}(z) = (1 - z^{-1})U(z) + (1 - z^{-1})^{4}E(z) - (1 - z^{-1})E(z)$$

(2.14)

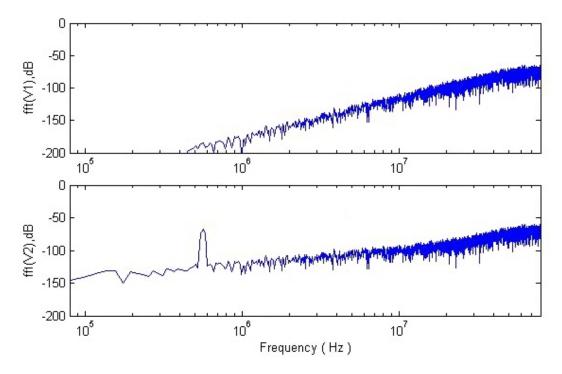

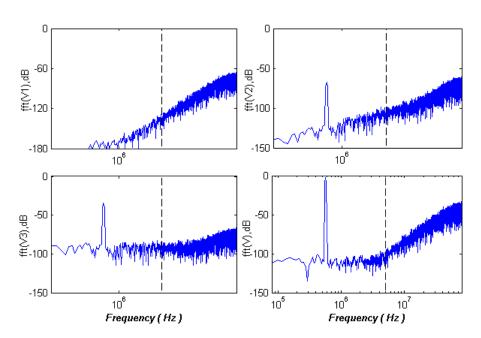

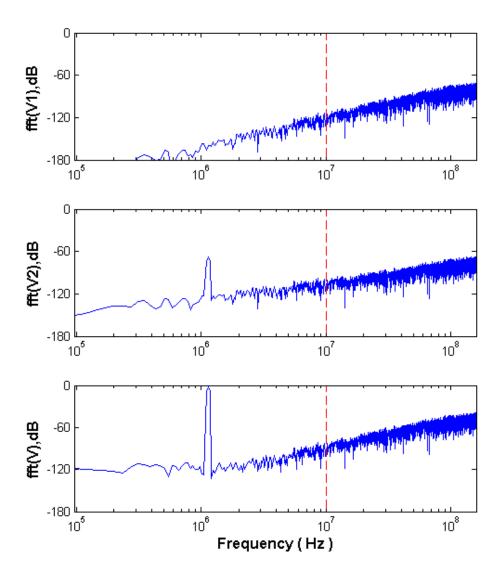

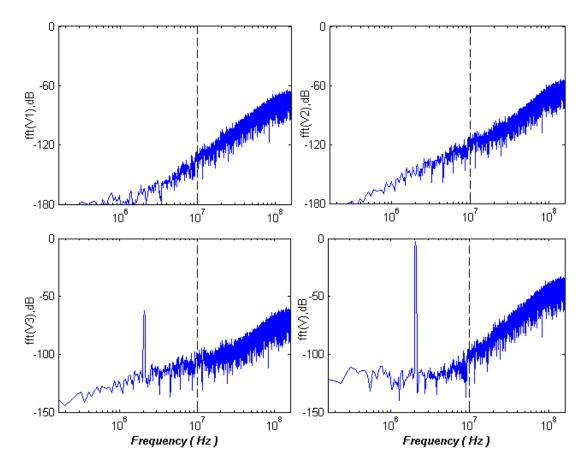

The MATLAB SIMULINK simulation results shown in Figure 2.6 also verify the analysis. They assume OSR = 15, a 15-level quantizer and 120 MHz clock for a 4 MHz bandwidth. The results in Figure 2.6 show that there is no signal component in  $V_1$ , leaving only the shaped quantization error. Thus the low-distortion characteristic has been preserved.  $V_2$  at the input of the last integrator gives the shaped input signal at -75 dBFS, which is highly suppressed compared to the input swing in the last opamp of Figure 2.4, whose is almost full-scale swing.

Figure 2.6: Simulated spectra of the node voltages  $V_1$  and  $V_2$  in Figure 2.5.

Table 2.1: Comparison Between  $\Delta\Sigma$  ADCs in Figures 2.4 and 2.5

|                                  | Specification   | Conv.      | SLD        |

|----------------------------------|-----------------|------------|------------|

| Architecture                     | No. of opamp    | 4          | 3          |

| System timing                    | Settling time   | 2.9 ns     | 3.7 ns     |

|                                  | Advanced cutoff | 360 ps     | 180 ps     |

|                                  | Non-overlapping | 790 ps     | 170 ps     |

| Specification for the last opamp | Feedback factor | 1/9        | 1/6        |

|                                  | Input swing     | -0.05 dBFS | -7.21 dBFS |

|                                  | Output swing    | -0.05 dBFS | -0.06 dBFS |

Compared with the conventional  $\Delta\Sigma$  modulator of Figure 2.4, the proposed modulator structure can use 27% more time to settle all opamps, which allows relaxation of the opamps' settling speed. The last opamp has 7.16 dB smaller input swing, which relieves also the slew rate requirement. The comparison results are shown in Table 2.1. A drawback of using shifted loop delays is that the cascaded delay-free integrators need a 20% longer settling time [7]. However, overall the required unity gain bandwidth of the last opamp in Figure 2.5 is 39% lower than for that in the circuit of Figure 2.4.

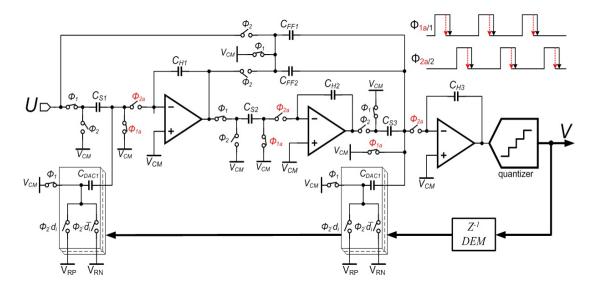

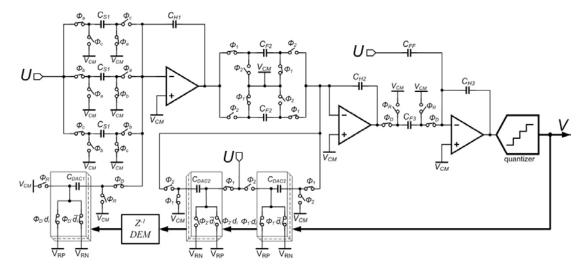

#### 2.3. Circuit Implementation

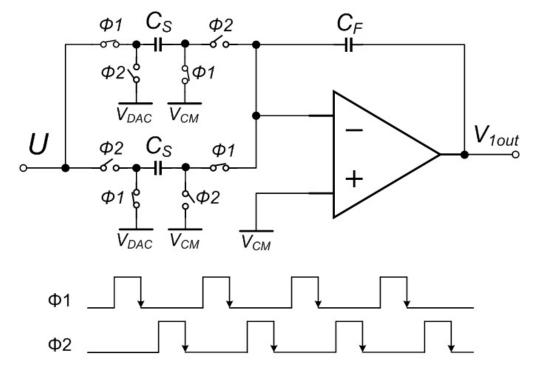

It is straightforward to implement the Figure 2.5 using switched-capacitor (SC) circuits. The most sensitive performance happens at the input of the first integrator. The shifted loop delay in the first integrator can be implemented by two-phase sampling technique [5], double sampling [2] or triple sampling [3]. However, twophase sampling suffers from large swings due to two-phase settling; double sampling and triple sampling results in linearity degradation due to path mismatch and interferers around  $F_S/2$ . In this design, the first integrator is implemented by conventional single sampling. Figure 2.7 illustrates the single-ended switchedcapacitor circuit diagram of the proposed modulator. However, here the first integrator shifts only half a clock period in the input path. The missing  $z^{-1/2}$  is not critical if the OSR is relatively large [4]. It causes a gain error of only 0.7% for OSR = 15. The input sampling and DAC capacitors of the first integrator are separated to avoid signal-dependent reference loading. The input sampling capacitors and DAC capacitors are reduced by half to preserve the same feedback factor with the shared capacitors [9], and the signal swings for input and DAC reference are doubled by cross-coupled sampling between positive and negative paths.

Bootstrapped clock signals are applied at the critical input switches to ensure signal-independent sampling. The 14 comparators use input offset sampling to minimize the offset effect. Data weighted averaging (DWA) is used to shape the mismatch errors of the 15-level DAC capacitors.

Figure 2.7: Single-ended SC circuit implementation of the proposed modulator with SLD of Figure 2.4.

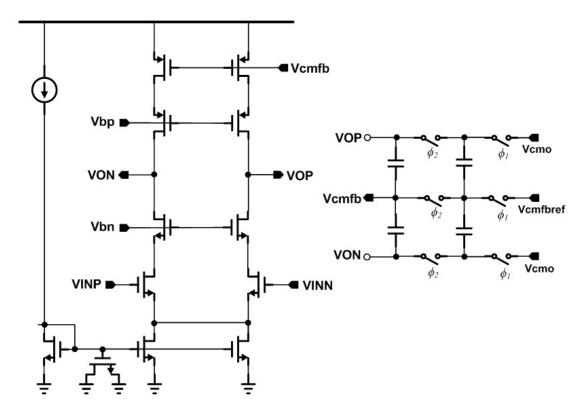

Figure 2.8: Telescopic cascode opamp with SC common-mode feedback.

Table 2.2: Simulated performance for the first integrator opamp

| DC Gain | PM  | UGBW     | I <sub>TOT</sub> | VDD   | Process |

|---------|-----|----------|------------------|-------|---------|

| 55 dB   | 65° | 1.25 GHz | 2.0 mA           | 1.6 V | 0.18 um |

The signal swings of the integrators in the loop filter are greatly reduced because of the low-distortion modulator architecture. The input swing of the last integrator is also highly reduced by the first-order noise shaping function to the input signal U(z). Thus, a telescopic cascode opamp can be used to achieve a powerefficient low-noise integrator with a 1.6 V supply. The fully-differential output signal swing of the opamp is 1.48 Vpp. Power-efficient SC circuit is used to provide common-mode feedback voltage to the two top PMOS transistors. To minimize the noise contribution from two top PMOS transistors, their transconductances are designed much smaller than those of the input differential pair. The equivalent resistor R<sub>ds</sub> of two top PMOS transistors are made larger to further suppress the noise comes from two cascode PMOS transistors. Figure 2.8 illustrates the telescopic cascode opamps in all integrators; Table 2.2 shows the simulated performance of the opamp in the first integrator. It achieves a DC gain of 55 dB to make the modulator gain error due to opamp finite gain lower than the thermal noise floor. To achieve the designed linearity, the unity gain bandwidth (UGBW) of the opamp is designed to 1.25 GHz to allow sufficient settling. It consumes 2.0 mA bais current with 1.6 V power supply. The opamps used in the second and third integrator are designed in the same structure but with scaled transistor size and current.

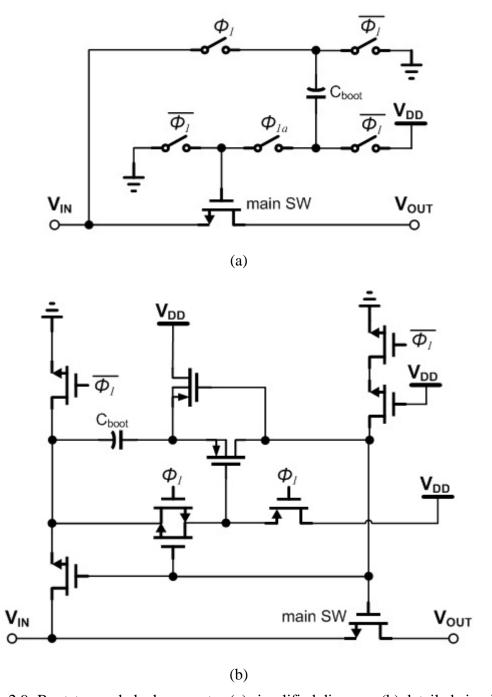

The sampling switches connected to the input signal are critical, because they limit the linearity of the modulator. To suppress the nonlinearity from charge injection and clock feedthrough, bootstrapped clock is used to ensure signal-independent sampling. Figure 2.9 shows the simplified diagram and the detailed circuit realization of the bootstrapped clock generator [10].

Figure 2.9: Bootstrapped clock generator (a) simplified diagram; (b) detailed circuit.

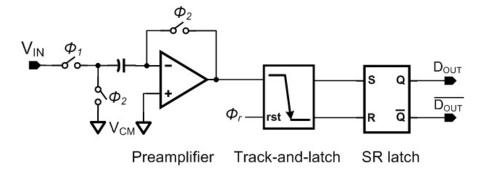

The 3.9 bits quantizer is realized by 14 comparators, based on thermometer coding. The comparator is composed of a preamplifier, a track-and-latch stage and a set-and-reset (SR) latch [11-12]. The block diagram is shown in Figure 2.10.

Figure 2.10: Comparator block diagram.

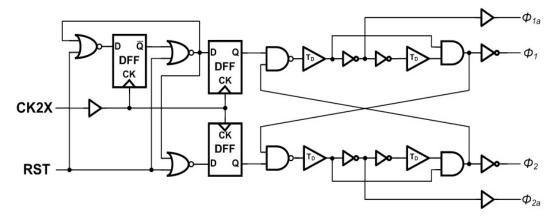

Figure 2.11: Clock generator diagram.

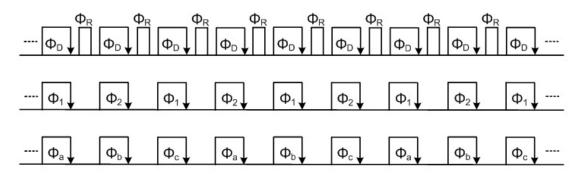

The gain of the preamplifier should not be too large; otherwise the time constants of the comparator are too large, which limits the speed, especially in track mode [13]. The preamplifier has an open loop gain of 12, and autozeroing technique is used to minimize the input-referred offset during  $\Phi_2$ , which is reduced also by 12 [14]. During the phase  $\Phi_I$ , the comparator works in the track mode and senses the output of the preamplifier. Before the end of phase  $\Phi_I$ , the reset signal  $\Phi_r$  locks the output of the track-and-latch stage and triggers the regeneration and SR latch. The speed of the quantizer is highly relaxed by the shifted loop delay, and hence the transistor sizes are easily to be optimized. The DWA logic is also working in the same time slot  $\Phi_I$ , which means its speed requirement is also relaxed. Thus the transistor sizes of switches and digital blocks in DWA are also easily to satisfy the speed. Figure 2.11 illustrates the clock generator with on-chip dived-by-two circuit. It realizes 50% duty cycle and the advanced-cutoff clock.

Figure 2.12: Chip micrograph for both modulators.

To verify the advantages of SLD structure, two  $\Delta\Sigma$  ADCs were designed and fabricated in a 0.18  $\mu$ m 2P4M CMOS process. The chip microphotograph is shown in Figure 2.12. The first modulator has a conventional low-distortion architecture, while the second one employs shifted loop delays. Both ADCs use a 1.6 V power supply for the analog circuitry, and a 1.55 V voltage for the digital circuit. The critical pins for input signals and analog bias voltages are at the top side; the power pins are at the corners at the top side; while the digital signal pins are at the bottom side. The die size is determined by the regulated pads. The core modulator area is only one fifth of the die area, while the empty area is filled with dummy metals and decoupling capacitors.

#### 2.4. Measurement Results

Figure 2.13: Test bench for chip measurement.

The test bench for chip measurement is shown in Figure 2.13. A single-tone sinewave input signal with frequencies from 10 kHz to 2 MHz is generated by AWG6062A. The single-ended signal is firstly filtered by a passive band pass filter, and then transformed to fully-differential signal by a passive balun. The sampling clock is generated by RF Src. E4433B. The bias current, input and output common voltages of all integrators are tunable on board, in order to get the best result by tweaking the opamps. The digital outputs and sampling clock of the chip are collected by Logic Analyzer TLA7012, then streamed to personal computer. The output data is analyzed by Matlab program. The power consumption is also be able to be measured on board. The test board setup is shown in Figure 2.14. In order to facilitate the setup of measurement, a corner detecting circuit is also implemented on chip. The test result in Figure 2.15 shows that all the chips in this tape-out shuttle are distributed between Slow-Fast and Slow-Slow corner.

Figure 2.14: Test board for ADC measurement.

Figure 2.15: Chip corner.

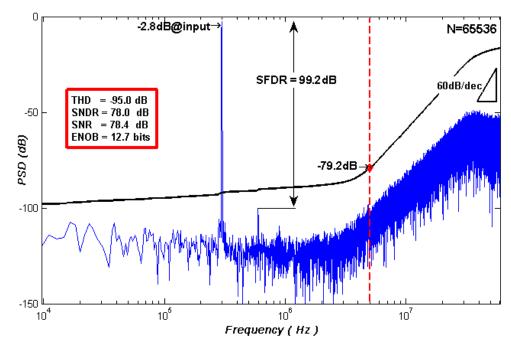

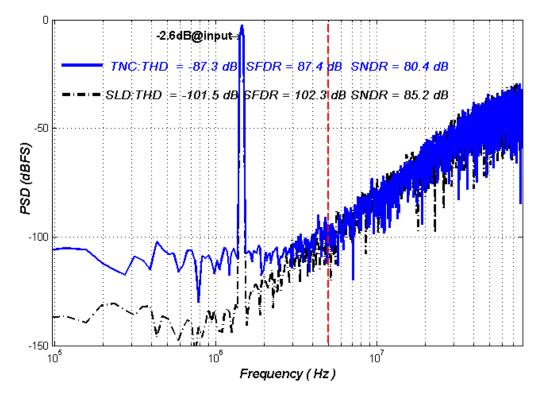

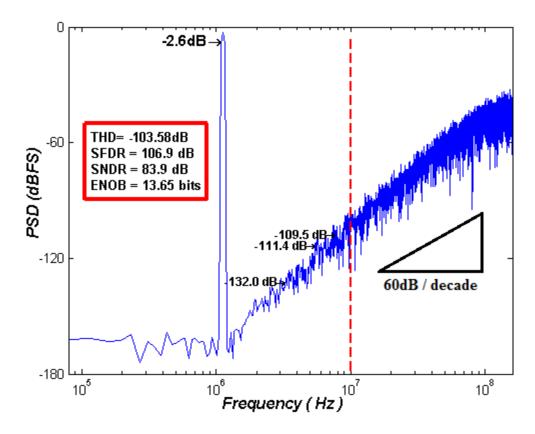

When the conventional low-distortion  $\Delta\Sigma$  modulator and the proposed  $\Delta\Sigma$ modulator with SLD run as continuously-running modulators, the spectra of the output are as shown in Figure 2.16 and 2.17. Figure 2.16 shows the power spectral density of the conventional low-distortion  $\Delta\Sigma$  modulator. The input signal is a 298.462 kHz sine wave with a -3.0 dBFS peak amplitude, and the clock frequency is 120 MHz. N=65536 points are sampled to get the power spectral density. The quantization noise with 60 dB/dec slope shows that a third-order noise shaping is achieved. After tweaking the bias currents and voltages, the peak SNDR can achieve 79.5 dB in a 4 MHz bandwidth, the THD is -87.2 dB, and the SFDR is 87.6 dB. The second harmonic (-90.6 dBFS) gives the largest distortion. The DC-offset is filtered by digital filter in Matlab code. The effective number of bits (ENOB) is 12.9 bits, calculated at ENOB = (SNDR - 1.76)/6.02. Figure 2.17 shows the measured results of the proposed  $\Delta\Sigma$  modulator with SLD. The input signal is also a 298.462 kHz sine wave but with a -2.8 dBFS peak amplitude, and the clock frequency is 120 MHz. The quantization noise shaping function is obviously also a third-order with 60 dB/dec slope. After debugging, the peak SNDR can achieve 81.6 dB, the SFDR is 99.2 dB, and the THD is -95.6 dB. The DC-offset is filtered by digital filter in Matlab code. The effective number of bits (ENOB) is 13.3bits. The second harmonic (-102 dBFS) is also the largest distortion, which is much improved than the conventional lowdistortion  $\Delta\Sigma$  modulator. The harmonics come from the signal swings and the mismatch between the differential paths in the loop filter. Thanks to the extra feedback branch, signal swings and dynamic range (DR) of the proposed modulator are improved. Hence the second harmonic achieves 11.4 dB suppression than the conventional one. Figure 2.18 illustrates the SNR and SNDR variation with input signal power for both modulators. The conventional modulator achieves 80.8 dB DR over a 4 MHz signal bandwidth; while the proposed modulator with SLD achieves 81.8 dB DR. A single-ended input signal from 10 kHz to 2 MHz is obtained from a signal generator AWG6062A and bandpass filters. The single-ended input signal is converted into a fully-differential signal pair via an on-board balan. Figure 2.19 shows the SNDR with input signal frequencies variations.

Figure 2.16: Measured spectrum at peak SNDR for the conventional  $\Delta\Sigma$  modulator. The integrated noise PSD is shown in black.

Figure 2.17: Measured spectrum at peak SNDR for  $\Delta\Sigma$  modulator with SLD. The integrated noise PSD is shown in black.

Figure 2.18: SNR and SNDR variations with input signal power.

Figure 2.19: Measured SNDR variations with input signal frequency.

**ADC** Conventional SLD Technology 0.18 um 2P4M CMOS Supply Voltage 1.6 V(A), 1.55 V(D)Clock Frequency 120 MHz 15 Oversampling Ratio Signal Bandwidth 4 MHz Input Range (diff.) 0.72 V Dynamic Range 80.8 dB81.8 dB Peak SNDR 79.5 dB 81.6 dB Peak SNR 80.6 dB 81.8 dB 87.6 dB **SFDR** 99.2 dB **THD** - 87.2 dB - 95.6 dB **Power Consumption** 24.9 mW 19.2 mW

Table 2.3: Performance Summary of the SLD Versus Conventional ADCs

In the conventional modulator, the analog power is 13.2 mW and digital power is 11.7 mW, hence the figure-of-merit (FOM) is 0.41 pJ/conversion-step, while the proposed modulator with SLD consumes 8.78 mW analog power and 10.48 mW digital power, and its FOM is 0.24 pJ/conversion-step. The FOM is calculated from

0.41 pJ/conv-step

**FOM**

$$FOM = \frac{Power}{2 \cdot BW \cdot 2^{ENOB}} \tag{2.15}$$

0.24 pJ/conv-step

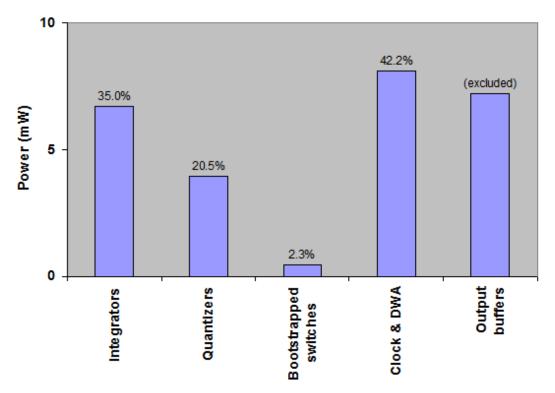

The summary of the measured performances for both prototypes is shown in Table 2.3. In spite of the large output power of output buffers, the proposed ADC with SLD achieves 0.24 pJ/convention-step for 4 MHz signal bandwidth, which is almost 40% lower than the conventional ADC FOM. More detailed power breakdown is shown in Figure 2.20 (SLD only) and Table 2.4 (both modulators).

Figure 2.20: Power consumption breakdown for the proposed ADC with SLD.

Table 2.4: Performance Summary of the Conventional Versus SLD ADCs

| ADC Power             | Conventional (mW) | SLD (mW) |

|-----------------------|-------------------|----------|

| Integrator 1          | 4.36              | 3.20     |

| Integrator 2          | 0.64              | 0.51     |

| Integrator 3          | 0.94              | 3.01     |

| Active adder          | 5.26              |          |

| Quantizer             | 3.94              | 3.94     |

| Bootstrapped switches | 0.43              | 0.43     |

| Clock & DWA           | 9.33              | 8.11     |

| Output buffers        | 7.19              | 7.19     |

Figure 2.21: Measured spectrum at peak SNDR for  $\Delta\Sigma$  modulator with SLD in 5 MHz bandwidth. The integrated noise PSD is shown in black.

| Table 2.5: Performance Comparison with Other D1 | ΔΣ ADCs |

|-------------------------------------------------|---------|

|                                                 |         |

| Ref. | BW<br>(MHz) | Power (mW) | SNDR<br>(dB) | Process (um) | FOM (pJ/conv.) |

|------|-------------|------------|--------------|--------------|----------------|

| [2]  | 4           | 33.4       | 70.1         | 0.18         | 1.64           |

| [3]  | 4           | 27.5       | 77.3         | 0.18         | 0.58           |

| [4]  | 4           | 8.0        | 59.1         | 0.09         | 1.38           |

| [8]  | 4.2         | 28         | 79           | 0.18         | 0.48           |

| [15] | 5           | 13.6       | 70.9         | 0.13         | 0.47           |

| [16] | 5           | 16         | 75.7         | 0.13         | 0.32           |

| This | 4           | 19.2       | 81.6         | 0.18         | 0.24           |

| Work | 5           | 19.2       | 78.0         | 0.18         | 0.30           |

Figure 2.21 shows the measured spectrum for the proposed ADC with SLD in 5 MHz bandwidth. Table 2.5 compares the performance of the proposed ADC with state-of-the-art DT  $\Delta\Sigma$  ADCs having bandwidths of 4-5 MHz. The proposed ADC with SLD is among the best reported for either 4 or 5 MHz discrete-time ADCs.

# 2.5. Summary

Two low-distortion third-order  $\Delta\Sigma$  modulators were implemented. Compared to a conventional  $\Delta\Sigma$  ADC, the proposed ADC with shifted loop delays can use a shifted delay to compensate the loop filter delay, hence relax the speed requirements of not only the quantizer and the block, but also the integrators in the loop filter. It eliminates the last stage adder and uses one extra feedback branch to make the STF be equal to unity. Finally, the proposed ADC with shifted loop delays could preserve the low-distortion property and optimize the stability, dynamic range and power consumption.

Compared to a conventional  $\Delta\Sigma$  ADC, the proposed ADC with shifted loop delays achieved much better performance while saving 38% of the analog power. The measurement results of the prototype demonstrated excellent performance, and verified the power efficiency of the shifted loop delay architecture.

## References

- [1] J. Silva, U. Moon, J. Steensgaard and G.C. Temes, "Wideband low-distortion delta-sigma ADC topology", *Electron. Lett.*, vol. 37, no. 12, pp. 737-738, 2001.

- [2] Y. Fujimoto, Y. Kanazawa. P. Lo Re and M. Miyamot, "An 80/100MS/s 76.3/70.1dB SNDR ΔΣ ADC for Digital TV Receivers," *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, pp. 201-210, Feb. 2006.

- [3] Y. Kanazawa, Y. Fujimoto, P. Re and M. Miyamoto, "A 100-MS/s 4-MHz Bandwidth 77.3-dB SNDR  $\Delta\Sigma$  ADC with a Triple Sampling Technique," *Custom Integrated Circuits Conference*, pp. 53-56, Sep. 2006.

- [4] A. Morgado, R. Rio, J. Rosa, L. Bos, J. Ryckaert and G. Plas, "A 100KHz-10MHz BW, 78-to-52 dB DR, 4.6-to-11mW Flexible SC ΣΔ Modulator in 1.2-V 90-nm CMOS," *Proceedings of the ESSCIRC*, pp. 418-421, Sep. 2010.

- [5] Xin Meng, Yi Zhang, Tao He and Gabor Temes, "A Noise-Coupled Low-Distortion Delta-Sigma ADC with Shifted Loop Delays," *Circuits and Systems (MWSCAS)*, 2014 IEEE 57th International Midwest Symposium on, pp 587-590, August 2014.

- [6] A. Gharbiya and D. A. Johns, "On the implementation of input-feedforward delta-sigma modulators," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 53, no. 6, pp. 453-457, June 2006.

- [7] X. Meng, Y. Zhang, T. He and G.C. Temes, "Low-Distortion Wideband Delta-Sigma ADCs with shifted Loop Delays," *IEEE Trans. Circuits Syst. I: Reg. Papers*, pp. 376 384, Jun. 2015.

- [8] K. Lee, J. Chae, M. Aniya, K. Hamashita, K. Takasuka, S. Takeuchi and G. C. Temes, "A Noise-Coupled Time-Interleaved ΔΣ ADC with 4.2MHz BW, 98dB THD and 79dB SNDR," *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, pp. 494-495, Feb. 2008.

- [9] K. Lee, M.R. Miller and G.C. Temes, "An 8.1mW, 82dB delta-sigma ADC with 1.9 MHz BW and -98dB THD", *IEEE J. Solid-State Circuits*, vol. 44, no. 8, pp. 2202-2211, Aug. 2009.

- [10] M. Dessouky and A. Kaiser, "Very low-voltage digital-audio  $\Delta\Sigma$  modulator with 88-dB dynamic range using local switch bootstrappling," *IEEE J. Solid-State Circuits*, vol. 36, no. 3, pp. 349-355, Mar, 2001.

- [11] I. Mehr and D. Dalton, "A 500-MSample/s, 6-bit Nyquist-rate ADC for disk-drive read-channel applications," *IEEE J. Solid-State Circuits*, Vol. 34, no. 7, pp. 912-920, July 1999.

- [12] I. Mehr and L. Singer, "A 55-mW, 10-bit, 40-Msample/s Nyquist-rate CMOS ADC," *IEEE J. Solid-State Circuits*, Vol. 35, no. 3, pp. 318-325, Mar. 2000.

- [13] D. A. Johns and K. Martin, *Analog Integrated Circuit Design*. New York: John Wiley & Sons, 1997.

- [14] C. C. Enz and G. C. Temes, "Circuit techniques for reducing the effects of opamp imperfections: autozeroing, correlated double sampling, and chopper stabilization," *IEEE Proceeding*, vol. 84, no. 11, pp. 1584-1614, Nov. 1996.

- [15] T. Christen and Q. Huang, "A 0.13 $\mu$ m CMOS 0.1–20MHz Bandwidth 86–70dB DR Multi-Mode DT  $\Delta\Sigma$  ADC for IMT-Advanced," *Proceedings of the ESSCIRC*, pp. 414-417, Sep. 2010.

- [16] R. Zanbaghi, S. Saxena, G.C. Temes and T.S. Fiez, "A 75-dB SNDR, 5-MHz Bandwidth Stage-Shared 2-2 MASH ΔΣ Modulator Dissipating 16 mW Power," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 59, no. 8, pp. 1614-1625, Aug. 2012.

# CHAPTER 3 . NOISE SHAPING ENHANCED DELTA-SIGMA ADCs WITH SHIFTED LOOP DELAYS

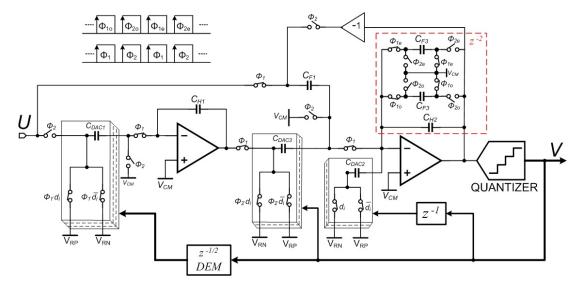

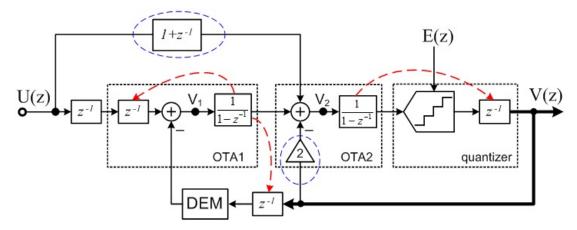

Noise coupling and time interleaving are effective methods for expanding the signal bandwidth in the low-power wideband delta-sigma ( $\Delta\Sigma$ ) ADCs. In this chapter, two discrete-time  $\Delta\Sigma$  modulator topologies combined with shifted loop delays (SLD), are proposed. One is based on a self-noise-coupled low-distortion structure; the other one is a noise-coupled time-interleaved  $\Delta\Sigma$  modulator. Both architectures use shifted loop delays to relax the critical timing constraints in the modulator loop filter. To verify the effectiveness, both  $\Delta\Sigma$  modulators were analyzed and simulated in a 0.18um CMOS technology.

## 3.1. Introduction

With increasing speed in wireless communication and portable electronics, high-resolution, low-power delta-sigma ( $\Delta\Sigma$ ) ADCs are required to achieve wider bandwidth. The feed-forward structure with low-distortion technique [1] is highly effective in wideband realization. Also, it achieves high accuracy by suppressing the input signal component and distortion in the loop filter. The dynamic requirements for all integrators are even more relaxed when the quantizer is multi-bit. The operational transconductance amplifiers (OTAs) have reduced design requirements of slewing and settling, and thus consume less power dissipation.

A drawback of the low-distortion architecture is that the adder needs to combine the signals of all feed-forward paths (Figure 3.1), either in a passive or active circuit. Although the passive summation does not need an extra OTA, the signal swing and the quantizer input steps are attenuated due to the parasitics. Also, mismatch effects and kick-back noise from the quantizer impair the performance of the modulator [2]. An active adder can achieve more accurate summation; however, it requires a fast power-hungry OTA. Thus, Nth order noise shaping modulator need N+1 OTAs.

Figure 3.1: Feed-forward low-distortion  $\Delta\Sigma$  ADC.

Noise shaping enhancement techniques such as noise coupling [2], VCO-based quantizer [3] and dual-slope quantizer [4] were used to compensate the extra OTA by increasing the order of the noise transfer function (NTF) in system level design. To further save power, charge-pump based integrators [5] and charge compensation [6] were suggested to relax the slew rate and settling requirements of the OTAs. However, the drawback of all these techniques is the critical timing required for the quantization and the dynamic element matching (DEM) circuitry [7]-[8]. The stability of the loop requires that the quantizer and the DEM operate in the non-overlapping clock intervals. This increases the power consumption in both OTAs and digital blocks. These issues become even more challenging with increased signal bandwidth.

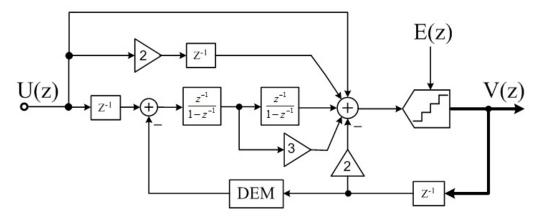

To relax the timing restrictions, extra loop delay can be introduced in the feedback path [9]-[10]. However, this additional delay has to be compensated by extra feedback and feed-forward branches (Figure 3.2) to prevent instability [11]-[12]. Also, to keep the low-distortion property, additional delay should be injected in the signal path, which makes the timing in the input of the modulator more complex. Furthermore, this architecture cannot utilize noise shaping enhancement techniques, which means thus N + 1 OTAs are still required to achieve  $N^{th}$ -order noise shaping function, the same as the conventional low-distortion architecture.

Figure 3.2: Low-distortion  $\Delta\Sigma$  ADC with extra loop delays [12].

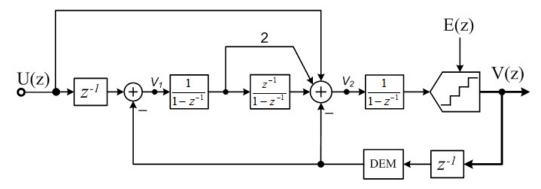

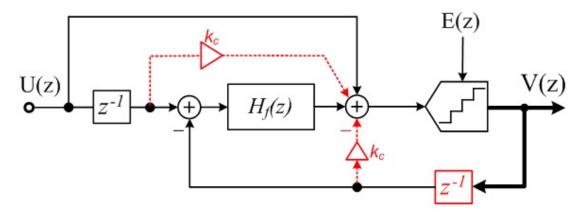

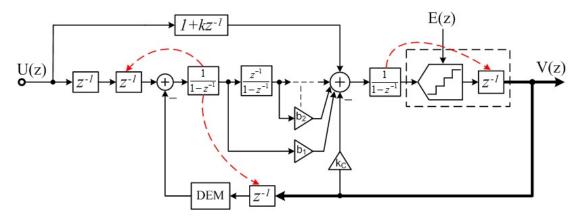

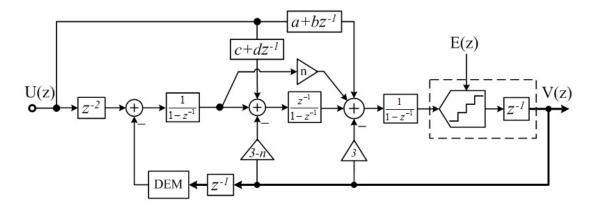

In this chapter, noise shaping enhancement techniques combined with shifted loop delays (SLD) are described. These structure shifts the loop delay from the last integrator to the feedback path, in order to relax the critical timing needed for the DEM logic. The active summation is achieved also by the last integrator, saving one OTA in the loop filter, which means that only N OTAs only required to achieve  $N^{\text{th}}$  order noise shaping function. This chapter is organized as follows. Section 3.2 describes the proposed self-noise-coupled  $\Delta\Sigma$  ADC with shifted loop delays. The proposed noise-coupled time-interleaved modulator architecture with shifted loop delays is described in section 3.3. Finally, Section 3.4 draws the summary.

# 3.2. Self-Noise-Coupled $\Delta\Sigma$ ADC with SLD

# 3.2.1 Architecture Considerations

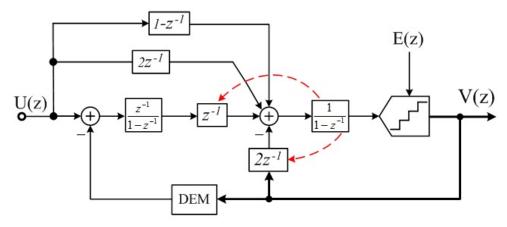

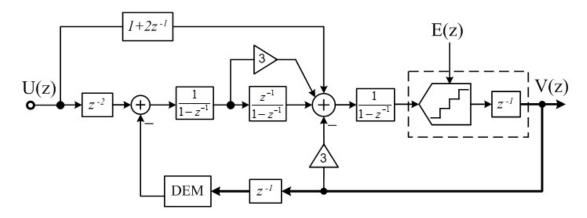

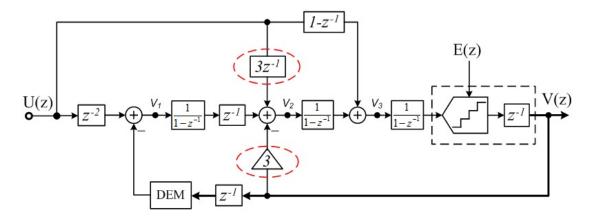

Noise coupling is a power-efficient approach in wideband  $\Delta\Sigma$  ADCs design. It boosts the noise shaping performance without requiring an extra integrator. As Figure 3.3 shows, noise coupling is achieved by delaying the quantization noise by one clock period delay, and injecting it into the summing node before the quantizer [2]. It effectively increases the modulator order of noise transfer function from N to N+1 without changing the signal transfer function. However, the extra OTA is indispensable because of the active addition and virtual ground. Additionally, the quantization noise works as a dither signal, thus it helps to reduce idle tone and harmonic spurs, and improves the modulator linearity [2].

Figure 3.3: Block diagram of the low-distortion self noise-coupled  $\Delta\Sigma$  ADC.

Figure 3.4: Low-distortion self noise-coupled  $\Delta\Sigma$  ADC with shifted loop delays.

The shifted loop delays technique, which is introduced in chapter 2, can also be utilized in  $\Delta\Sigma$  modulators combined with the self noise coupling technique. The stabilized  $\Delta\Sigma$  ADC with shifted loop delays is illustrated in Figure 3.4. The proposed architecture shifts the loop delay from the last integrator to two feedback paths. One is the noise coupling branch to generate the extra noise shaping; the other one is the feedback branch to relax the timing restricts for DEM logic. Since the feed-forward and feedback signals are added at the input of the last delay-free integrator, the delayed coupling signal should be multiplied by  $(1 - z^{-1})$ . The drawback of this architecture is also the cascaded delay-free integrators, which burn more power to achieve the same linearity.

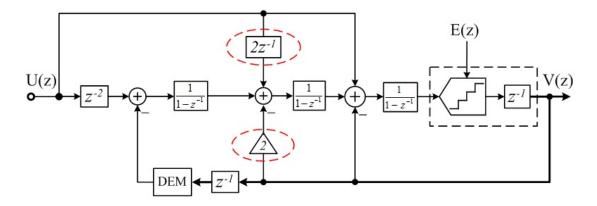

Figure 3.5: Low-distortion noise-coupled  $\Delta\Sigma$  ADC with shifted loop delays [13].

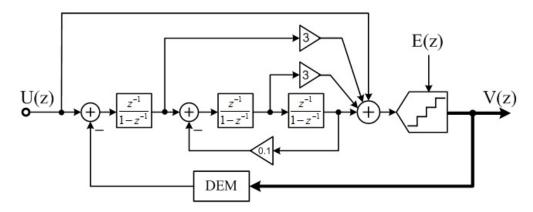

Figure 3.6: Improved noise-coupled  $\Delta\Sigma$  ADC with shifted loop delays.

As discussed, noise coupling can be used to enhance the order of the noise shaping function. A third-order noise-coupled realization is shown in Figure 3.5 [13]. To save power and area, shared capacitors (in dashed circles) are used in an improved low-distortion noise-coupled  $\Delta\Sigma$  ADC topology with shifted loop delays (Figure 3.6) [14]. This structure shifts the half clock period delay of the first integrator into the feedback and input signal paths. The half clock delay in the feedback path allows DEM logic operation. While the half clock delay in the input signal path helps to synchronize the signal components between direct input and feedback paths, and hence preserves the low-distortion property. Also, this modulator shifts one clock delay from the last integrator into the extra feedback branch to stabilize the loop. The proposed modulator also uses the last integrator to realize active summation. Three

capacitors can be shared in the last integrator. Hence, the feedback factor and the power consumption of the second OTA is further improved.

Linear analysis of the modulator in Figure 3.6 gives

$$STF = 1 \tag{3.1}$$

$$NTF = (1 - z^{-1})^3 (3.2)$$

$$V_1(z) = -z^{-1/2} (1 - z^{-1})^3 E(z)$$

(3.3)

$$V_2(z) = (1 - z^{-1})U(z) - z^{-1}(1 - z^{-1})(2 - z^{-1})E(z)$$

(3.4)

Here, E(z) is the quantization error of the internal quantizer. Equation (3.3) shows that the loop filter only needs to process the shaped quantization error, and the proposed modulator topology thus remains the low-distortion architecture.

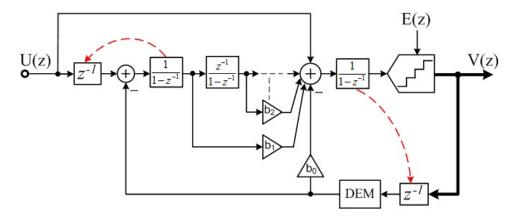

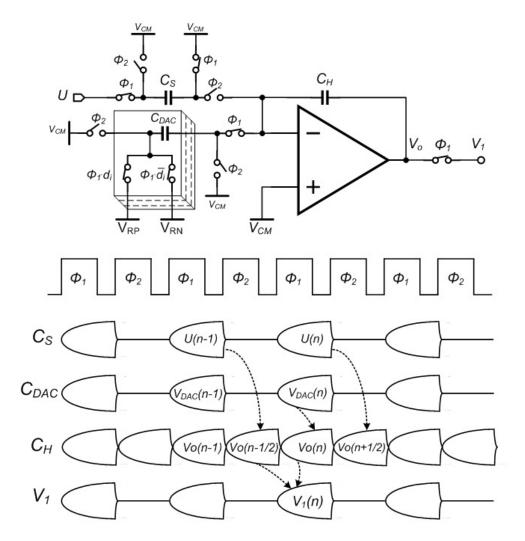

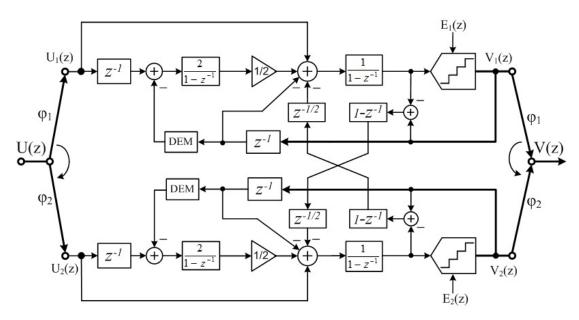

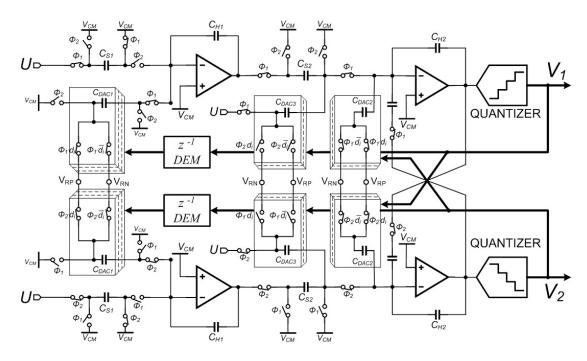

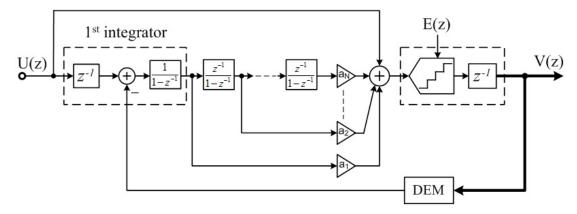

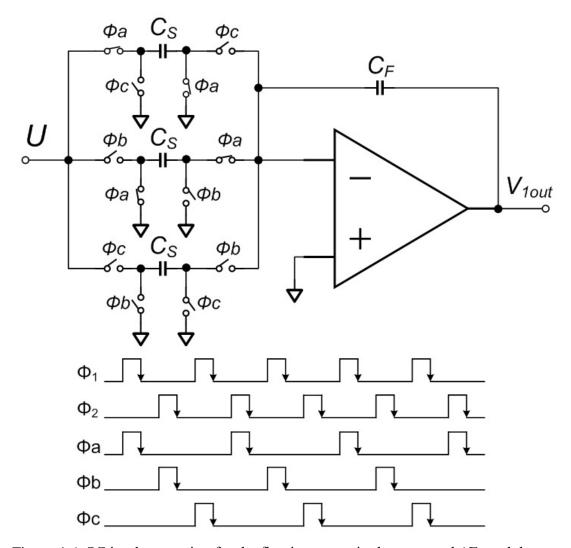

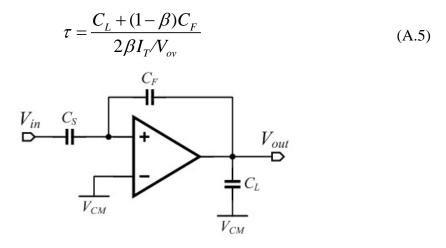

# 3.2.2 SC Circuit Implementation

Figure 3.6 is easily implemented by using switched-capacitor circuits. As discussed in chapter 2, the most sensitive operation in discrete-time modulators happens at the input of the first integrator. The SC circuit implementation of the first integrator is shown in Figure 3.7. It operates in three steps: step 1, the input signal U(n-1) is sampled at the end of clock phase  $\Phi_1$ , transferred to the hold capacitor  $C_H$  in phase  $\Phi_2$  as Vo(n-1/2); step 2, during the clock phase  $\Phi_2$ , the feedback DAC capacitors are refreshed to common-mode voltage  $V_{CM}$ , and the quantization and DEM can be operated; step 3, in the next  $\Phi_1$ , the new DAC voltage is transferred to the integrator output to generate  $V_1(n)$ . Thus the feedback DAC signal is one clock delay than the input signal.

Clock phases  $\Phi_1$  and  $\Phi_2$  are non-overlapping. In the first integrator, the signal path works in delayed mode, while the DAC branches work in delay-free operation. Compared to double sampling realization in [15], this integrator eliminates the path mismatch and avoids the interferers around  $F_S$ /2. In the SC circuits implementation, the input sampling capacitor and the feedback DAC capacitors are separated to avoid the quantization noise coupling back to the signal path and to mitigate the signal dependent DAC reference noise.

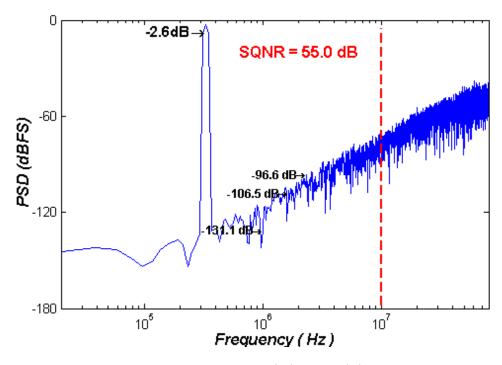

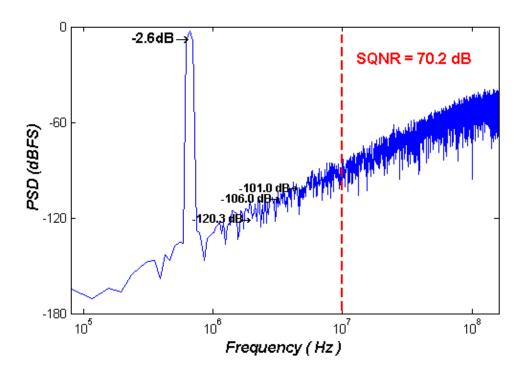

Figure 3.7: SC implementation of the first integrator in the proposed modulator.