## AN ABSTRACT OF THE DISSERTATION OF

Kyehyung Lee for the degree of Doctor of Philosophy in Electrical and Computer Engineering presented on April 2, 2008.

Title: <u>High Efficiency Delta-Sigma Modulation Data Converters.</u>

Abstract approved:

Gabor C. Temes

Enabled by continued device scaling in CMOS technology, more and more functions that were previously realized in separate chips are getting integrated on a single chip nowadays. Integration on silicon has opened the door to new portable wireless applications, and initiated a widespread use of these devices in our common everyday life. Wide signal bandwidth, high linearity and dynamic range, and low power dissipation are required of embedded data converters that are the performance-limiting key building blocks of those systems. Thus, power-efficient and highly-linear data conversion over wide range of signal bands is essential to get the full benefits from device scaling. This continued trend keeps innovation in the design of data converter continuing.

Traditionally, delta-sigma modulation data converters proved to be very effective in applications where high resolution was necessary in a relatively narrow signal band. There have been active research efforts across academia and industry on the extension of achievable signal bandwidth without compromising the performance of these data converters. In this dissertation, architectural innovations, combined with effective design techniques for delta-sigma modulation data converters, are presented to overcome the associated limitations. The effectiveness of the proposed approaches is demonstrated by test results for the following state-of-the-art prototype designs: (1) a 0.8 V, 2.6 mW, 88 dB dual-channel audio delta-sigma modulation D/A converter with headphone driver; (2) an 88 dB ring-coupled delta-sigma ADC with 1.9 MHz bandwidth and -102.4 dB THD; (3) a multi-cell noise-coupled delta-sigma ADC with 1.9 MHz bandwidth, 88 dB DR, and -98 dB THD; (4) an 8.1 mW, 82 dB self-coupled delta-sigma ADC with 1.9 MHz bandwidth, 88 dB DR, and -98 dB THD; (4) an 8.1 mW, 82 dB self-coupled delta-sigma ADC with 1.9 MHz bandwidth and -97 dB THD; (5) a noise-coupled time-interleaved delta-sigma ADC with 4.2 MHz bandwidth, -98 dB THD, and 79 dB SNDR; (6) a noise-coupled time-interleaved delta-sigma ADC with 2.5 MHz bandwidth, -104 dB THD, and 81 dB SNDR. As an extension of this research, two novel architectures for efficient double-sampling delta-sigma ADCs and improved low-distortion delta-sigma ADC are proposed, and validated by extensive simulations.

©Copyright by Kyehyung Lee April 2, 2008 All Rights Reserved

## High Efficiency Delta-Sigma Modulation Data Converters

by

Kyehyung Lee

A DISSERTATION

submitted to Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented April 2, 2008 Commencement June 2008 Doctor of Philosophy dissertation of Kyehyung Lee presented on April 2, 2008

APPROVED:

Major Professor, representing Electrical and Computer Engineering

Director of the School of Electrical Engineering and Computer Science

Dean of the Graduate School

I understand that my dissertation will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my dissertation to any reader upon request.

Kyehyung Lee, Author

### ACKNOWLEDGMENTS

I would like to express my deep gratitude to my advisor, Professor Gabor Temes. It would be impossible for me to finish this research without him. It is my great honor and pleasure to work with him. I respect his enthusiasm for research and teaching. He guided my research with boundless insights. He always gave me a lot of invaluable advice and encouragement on my research and personal life. He also allowed me lots of freedom on my research. I really enjoyed the research with him and learned from him what a superb researcher should be like.

Special thanks belong to Professor Un-Ku Moon for his generous support of my initial research at OSU. He allowed me enough time to learn analog circuit design and challenged me to improve my research to higher level.

My sincere appreciation goes to Professor Huaping Liu, Professor Pavan Kumar Hanumolu, Professor Albrecht Jander, and Professor David McIntyre for their serving on my graduate committee.

I am grateful to the Center for Design of Analog and Digital Integrated Circuits (CDADIC), Analog Devices, Broadcom, Texas Instruments, and Asahi Kasei EMD for their funding this research. I want to thank Kaoru Takasuka, Koichi Hamashita, Tetsuro Sugimoto, Seiji Takeuchi, and Mitsuru Aniya at Asahi Kasei EMD for their generous fabrication of my prototype chips. Useful technical feedback and discussions with Matt Miller and Doug Garrity at Freescale Semiconductor, and Jesper Steensgaard at Linear Technology are gratefully acknowledged.

I am indebted to many colleagues present and past in analog and mixed-signal group of OSU. When I arrived at Corvallis, Dong-Young Chang and Gil-Cho Ahn helped me to settle smoothly. Useful discussions with and help from Jose Silva, Jose Ceballos, Qingdong Meng, Zhenyong Zhang, Xuefeng Chen, Volodymyr Kratyuk, Younjae Kook, Jeongseok Chae, Peter Kurahashi, and Joshua Carnes are appreciated. Without specific order in mind, I would express my gratitude to Jipeng Li, Matthew Brown, Xuesheng Wang, Anurag Pulincherry, Ranganathan Desikachari, Kiseok Yoo, Mingyu Kim, Ting Wu, Merrick Brownlee, Charlie Myers, Kerem Ok, Anantha Nag Nemmani, Martin Vandepas, Ruopeng Wang, Sudhaka Kalakota, Madhulatha Bonu, Sanghyeon Lee, Sangho Kim, Wonseok Hwang, Sunwoo Kwon, Rob Gregoire, Naga Sasidhar Lingam, Dave Gubbins, Musah Tawfiq, Nima Maghari, Omid Rajaee, Erik Geissenhainer, Skyler Weaver, Ben Hershberg, Attila Sarhegyi, Yoshio Nishida, Yan Wang, Weilun Shen, Wenhuan Yu, Zhiqing Zhang, Xiaoran Gao, Qadeer Khan, Rishi Gupta, Christopher Hanken, Jim Le, and Igor Vytyaz.

Technical help from Robert Batten and Manfred Dittrich on testing, and technical support from Todd Shechter are appreciated.

Excellent support from Sarah O'Leary, Ferne Simendinger, Clara Knutson, Morgan Garrison, Josh Ferris, Andy Lyons, and Nancy Brown in EECS office are acknowledged.

I want to appreciate Tanay Karnik, Jaehong Han, Jianping Xu, and Fabrice Paillet at Intel for their help when I worked there as an intern.

# TABLE OF CONTENTS

|    |     |                                                                                                     | Page |

|----|-----|-----------------------------------------------------------------------------------------------------|------|

| 1. | IN  | FRODUCTION                                                                                          | 1    |

|    | 1.1 | Motivation                                                                                          | 1    |

|    | 1.2 | Contributions of This Research                                                                      | 2    |

|    | 1.3 | Organization of Dissertation                                                                        | 3    |

| 2. |     | ).8 V, 2.6 MW 88 DB DUAL-CHANNEL AUDIO DELTA-SIGMA<br>DDULATION D/A CONVERTER WITH HEADPHONE DRIVER | 5    |

|    |     |                                                                                                     |      |

|    | 2.1 | Introduction                                                                                        | 5    |

|    | 2.2 | Architecture                                                                                        | 7    |

|    | 2.3 | Digital Stages                                                                                      | 8    |

|    | 2.4 | Analog Stages                                                                                       | 20   |

|    | 2.5 | Experimental Results                                                                                | 26   |

|    | 2.6 | Summary                                                                                             | 29   |

|    |     | References                                                                                          |      |

| 3. | NO  | DISE-COUPLED MULTI-CELL DELTA-SIGMA ADCS                                                            | 33   |

|    | 3.1 | Introduction                                                                                        |      |

|    | 3.2 | Proposed Architecture                                                                               |      |

|    | 3.3 | Ring-Coupled 4-Cell $\Delta\Sigma$ ADC                                                              | 47   |

|    | 3.4 | Self-Coupled 4-Cell $\Delta\Sigma$ ADC                                                              | 54   |

|    | 3.5 | Self-Coupled Single-Cell $\Delta\Sigma$ ADC                                                         | 61   |

|    |     | References                                                                                          | 68   |

# TABLE OF CONTENTS (Continued)

## Page

| 4. | A١  | NOISE-COUPLED TIME-INTERLEAVED DELTA-SIGMA ADC WITH |     |

|----|-----|-----------------------------------------------------|-----|

|    | 4.2 | MHZ BANDWIDTH, -98 DB THD, AND 79 DB SNDR           | 70  |

|    | 4.1 | Introduction                                        | 70  |

|    | 4.2 | Architectural Considerations                        | 72  |

|    | 4.3 | SC Circuit Implementation                           | 79  |

|    | 4.4 | Experimental Results                                | 87  |

|    | 4.5 | Summary                                             | 92  |

|    |     | References                                          | 92  |

| 5. | EF  | FICIENT DOUBLE-SAMPLING DELTA-SIGMA ADC             | 96  |

|    | 5.1 | Introduction                                        | 96  |

|    | 5.2 | Conventional Double-Sampling Integrator             | 96  |

|    | 5.3 | Proposed Double-Sampling Integrator                 | 102 |

|    | 5.4 | Simulation Results                                  | 104 |

|    | 5.5 | Summary                                             | 107 |

|    |     | References                                          | 107 |

| 6. | IM  | PROVED LOW-DISTORTION DELTA-SIGMA ADC               | 109 |

|    | 6.1 | Introduction                                        | 109 |

|    | 6.2 | Prior Art                                           | 112 |

|    | 6.3 | Proposed Low-Distortion Modulator Topology          | 118 |

|    | 6.4 | Summary                                             | 125 |

|    |     | References                                          | 126 |

# TABLE OF CONTENTS (Continued)

Page

| 7. | CONCLUSIONS | 129 |

|----|-------------|-----|

|    |             |     |

## LIST OF FIGURES

| Figu | <u>re</u>                                                                                                   | <u>Page</u> |

|------|-------------------------------------------------------------------------------------------------------------|-------------|

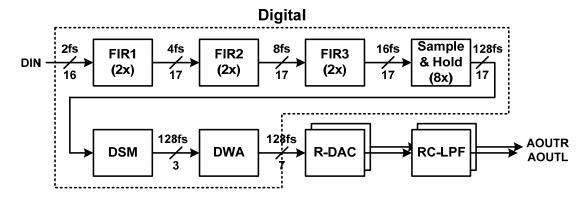

| 2.1  | DAC architecture.                                                                                           | 8           |

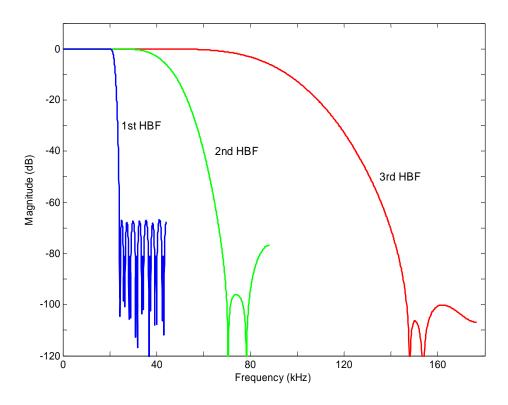

| 2.2  | Frequency responses of the HBFs in the interpolation filter.                                                | 9           |

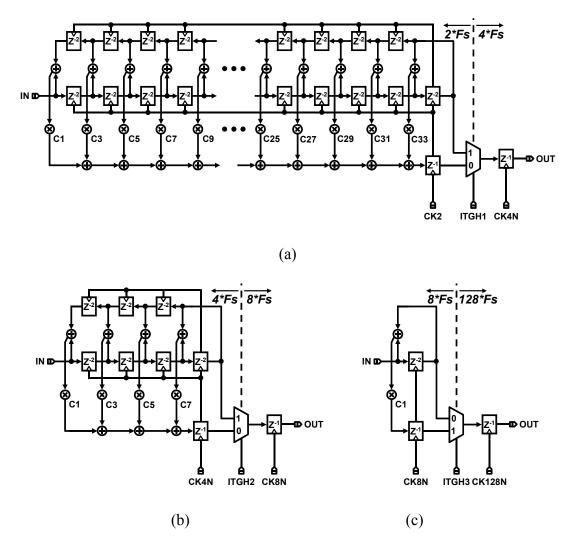

| 2.3  | Direct form realization of the HBFs and a sample-and-hold register                                          | 12          |

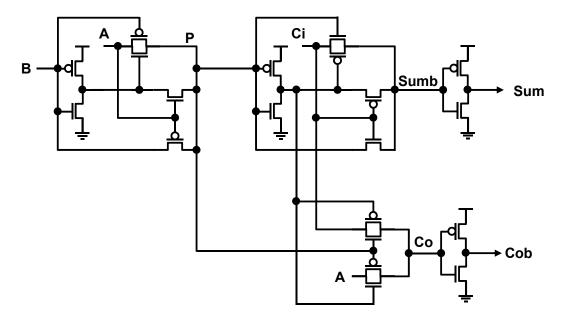

| 2.4  | One of the four basic adder cells                                                                           | 13          |

| 2.5  | Dual-channel third-order $\Delta\Sigma$ modulator with resonator                                            | 14          |

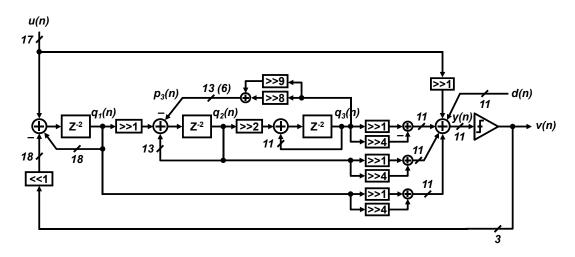

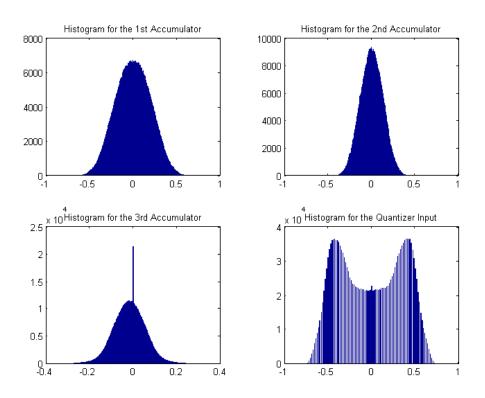

| 2.6  | Histogram of the internal nodes in the $\Delta\Sigma$ modulator                                             | 14          |

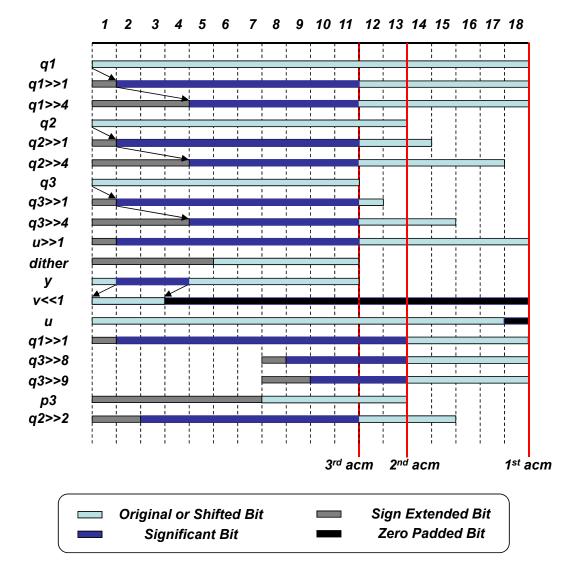

| 2.7  | Bit alignment of the $\Delta\Sigma$ modulator.                                                              | 15          |

| 2.8  | Schematic for 7-level quantizer.                                                                            | 16          |

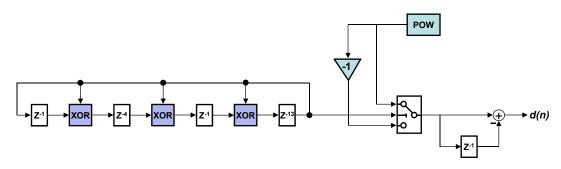

| 2.9  | Dither from the LFSR in Galois configuration.                                                               | 17          |

| 2.10 | Measured spectrum for the $\Delta\Sigma$ modulator at $V_{DD} = 0.62$ V                                     | 18          |

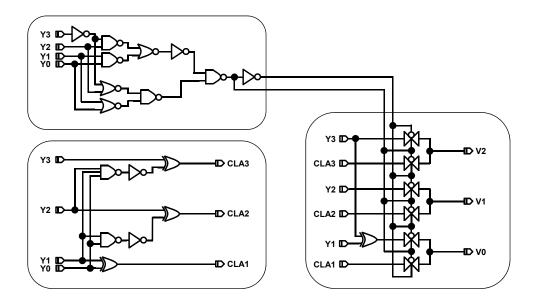

| 2.11 | Pointer generation for DWA. A 3b RCA with modulo 7 is used for the accumulator                              | 19          |

| 2.12 | Rotating barrel shifter for DWA.                                                                            | 20          |

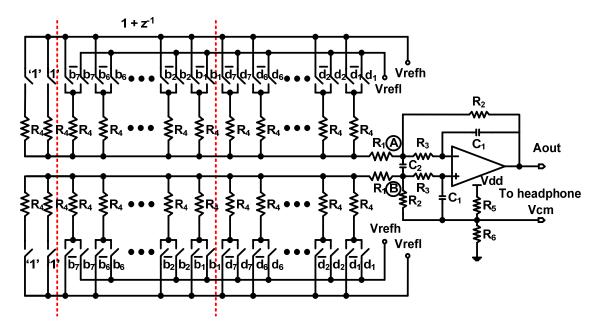

| 2.13 | R-DAC with first-order FIR filter, second-order Rauch filter, and headphone driver ( $d_i = delayed b_i$ ). | 21          |

| 2.14 | Second-order Rauch low-pass filter.                                                                         | 23          |

| 2.15 | Opamp with class-AB output stage                                                                            | 25          |

| 2.16 | Measured output spectrum with a 1.17 kHz -60 dB sine-wave input at $V_{DD} = 0.8 \text{ V}$ .               |             |

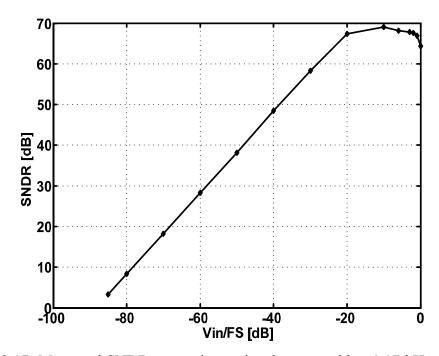

| 2.17 | Measured SNDR versus input signal power with a 1.17 kHz sine-<br>wave input at $V_{DD} = 0.8$ V.            | 27          |

| 2.18 | Measured performance with supply voltage.                                                                   | 27          |

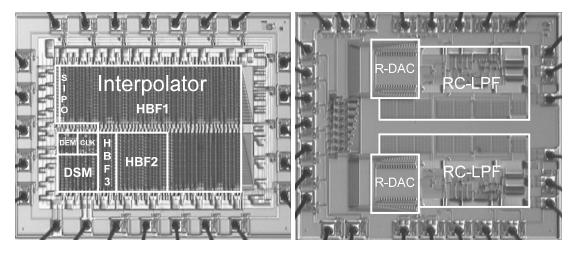

| 2.19 | Die micrographs                                                                                             | 29          |

| <u>Figu</u> | re                                                                                       | Page |

|-------------|------------------------------------------------------------------------------------------|------|

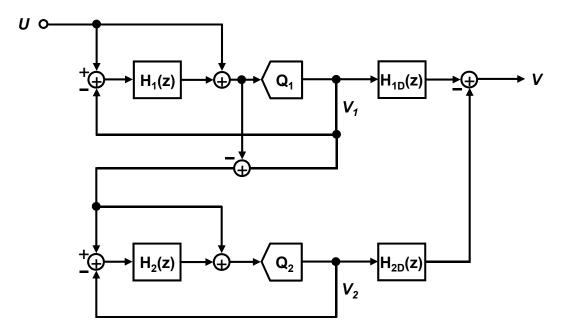

| 3.1         | Two-stage cascaded (MASH) delta-sigma ADC.                                               | 34   |

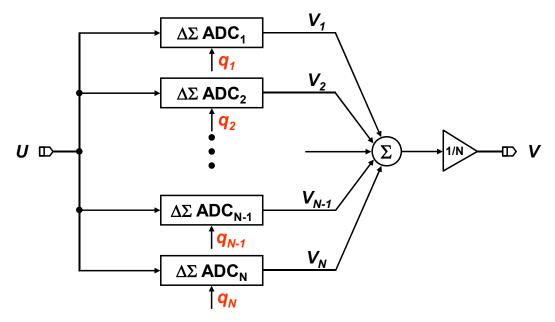

| 3.2         | Multi-cell delta-sigma ADC                                                               | 35   |

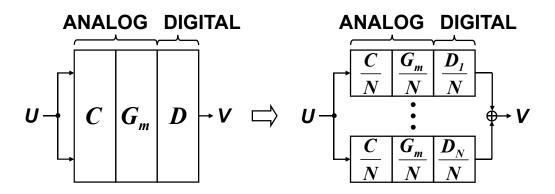

| 3.3         | Splitting is free for multi-cell delta-sigma ADC                                         | 37   |

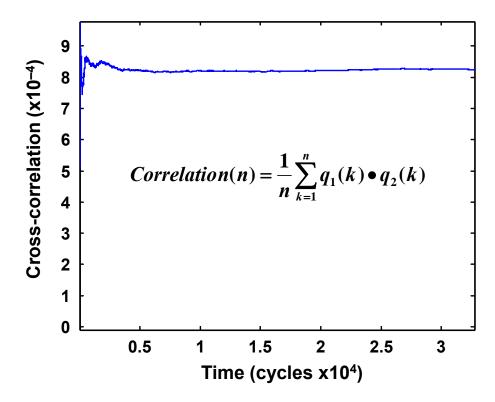

| 3.4         | Crosscorrelation of quantization noise for two ideal $\Delta\Sigma$ ADCs.                | 39   |

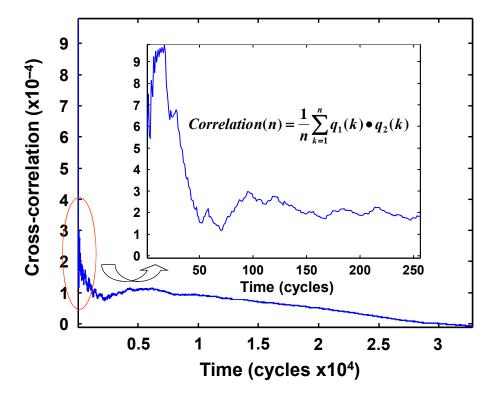

| 3.5         | Crosscorrelation of quantization noise for two nonideal $\Delta\Sigma$ ADCs              | 39   |

| 3.6         | Conventional split delta-sigma ADC.                                                      | 40   |

| 3.7         | Proposed enhanced split delta-sigma ADC                                                  | 41   |

| 3.8         | Multi-cell delta-sigma ADC with noise coupling.                                          | 43   |

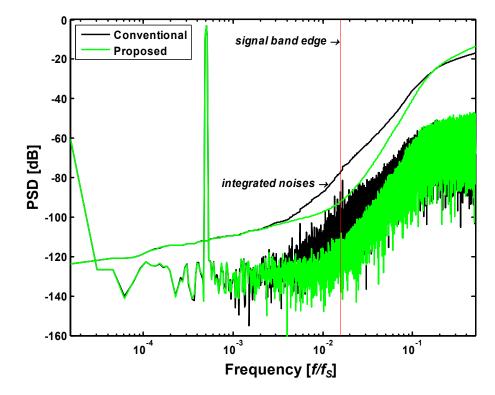

| 3.9         | PSDs for split $\Delta\Sigma$ ADC without and with 1 <sup>st</sup> -order noise coupling | 44   |

| 3.10        | PSDs for split $\Delta\Sigma$ ADC without and with 2 <sup>nd</sup> -order noise coupling | 44   |

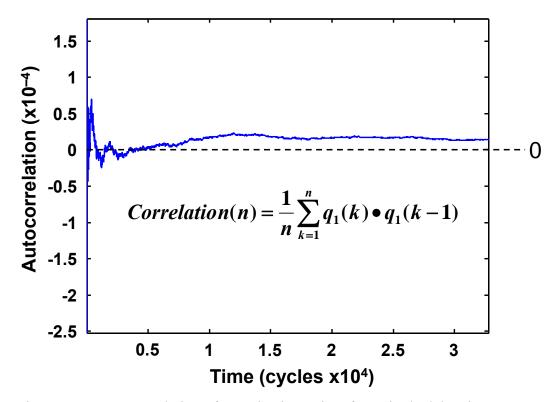

| 3.11        | Noise coupling in a single delta-sigma ADC                                               | 45   |

| 3.12        | Autocorrelation of quantization noises for a single delta-sigma ADC                      | 46   |

| 3.13        | PSDs for a single $\Delta\Sigma$ ADC without and with self noise coupling                | 46   |

| 3.14        | Block diagram of ring-coupled 4-cell $\Delta\Sigma$ ADC (RC4)                            | 48   |

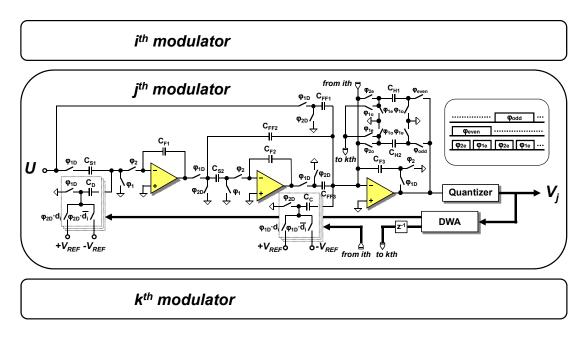

| 3.15        | SC circuit implementation of the prototype ADC (RC4)                                     | 49   |

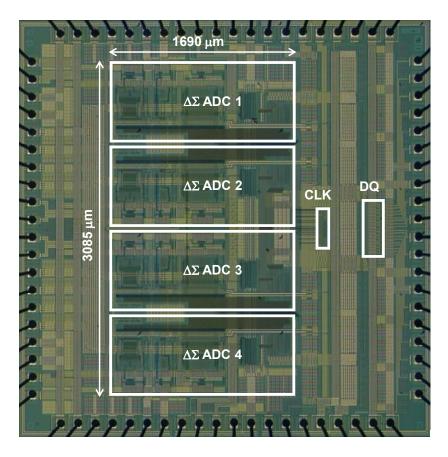

| 3.16        | Chip micrograph for the prototype ADC (RC4).                                             | 50   |

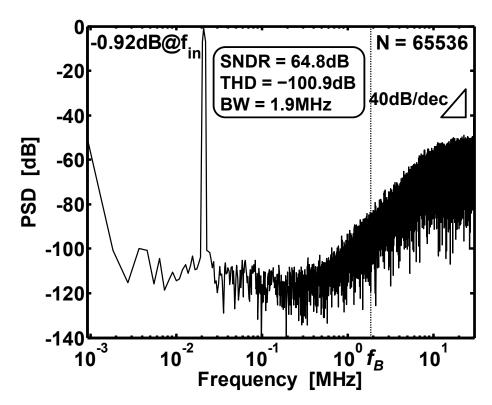

| 3.17        | Measured spectrum for the prototype ADC (a single cell only in RC4)                      | 51   |

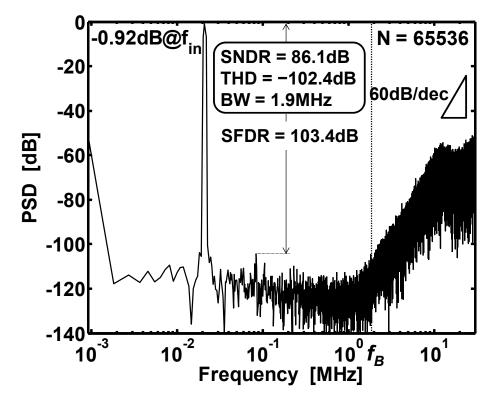

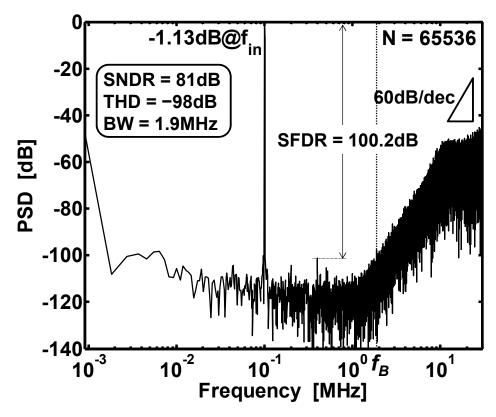

| 3.18        | Measured spectrum for the prototype ADC (RC4).                                           | 51   |

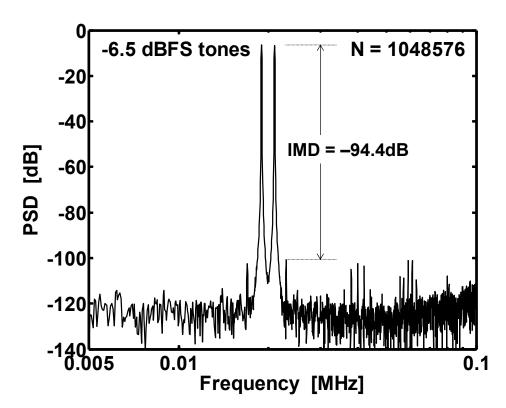

| 3.19        | Measured two-tone spectrum for the prototype ADC (RC4)                                   | 52   |

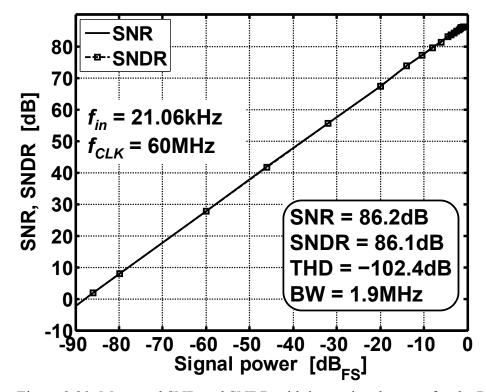

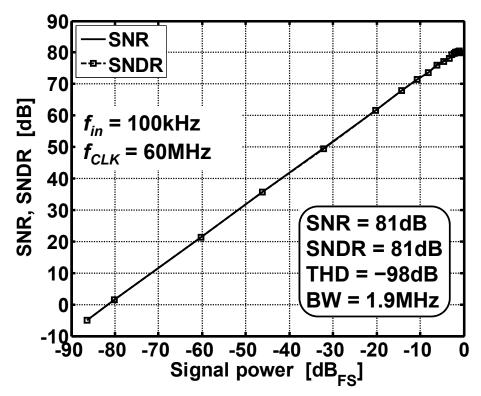

| 3.20        | Measured SNR and SNDR with input signal power for the RC4                                | 52   |

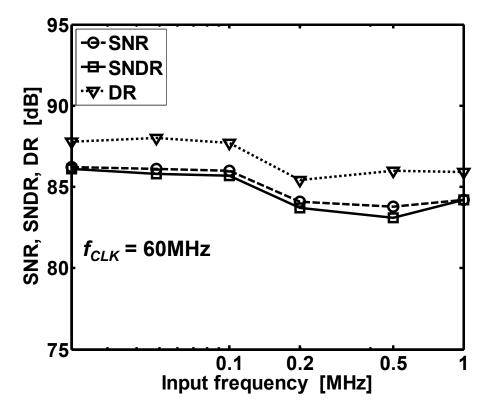

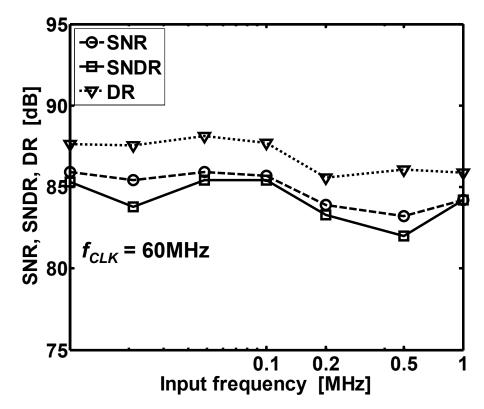

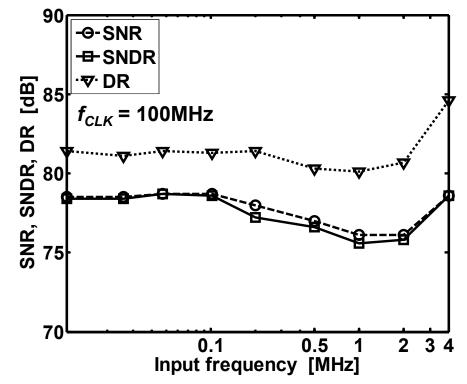

| 3.21        | Measured SNR, SNDR, and DR with input frequencies for the RC4                            | 53   |

| <u>Figu</u> | re                                                                                                                                                                        | Page |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

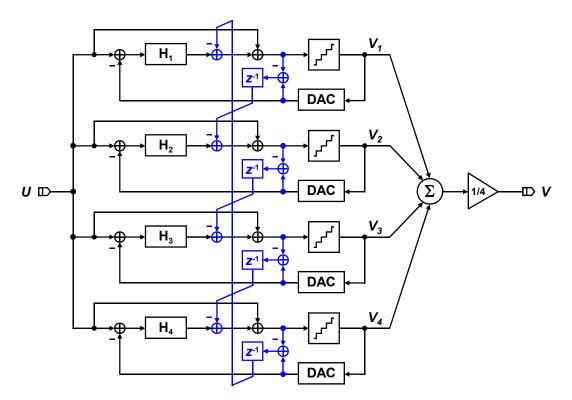

| 3.22        | Block diagram of self-coupled 4-cell $\Delta\Sigma$ ADC (SC4)                                                                                                             | 55   |

| 3.23        | SC circuit implementation of the prototype ADC (SC4)                                                                                                                      | 57   |

| 3.24        | Chip micrograph for the prototype ADC (SC4)                                                                                                                               | 58   |

| 3.25        | Measured spectrum for the prototype ADC (SC4).                                                                                                                            | 59   |

| 3.26        | Measured SNR and SNDR with input signal power for the SC4.                                                                                                                | 59   |

| 3.27        | Measured SNR, SNDR, and DR with input frequencies for the SC4                                                                                                             | 60   |

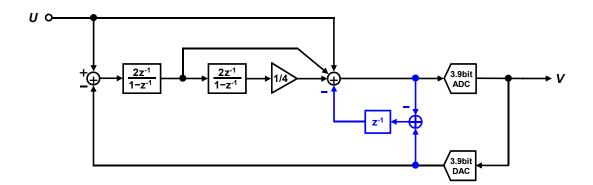

| 3.28        | Block diagram of self-coupled single-cell $\Delta\Sigma$ ADC (SC1).                                                                                                       | 62   |

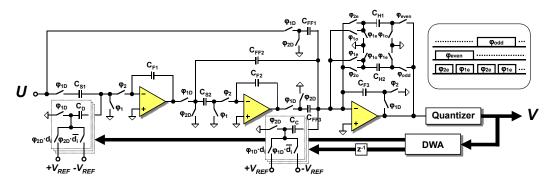

| 3.29        | SC circuit implementation of the prototype ADC (SC1)                                                                                                                      | 63   |

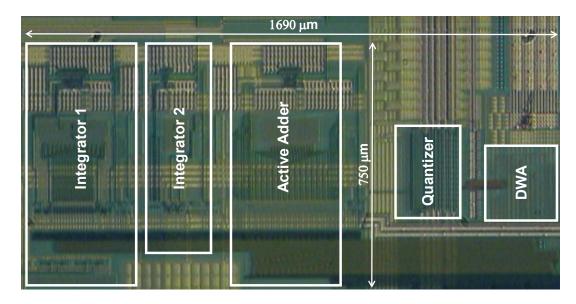

| 3.30        | Chip micrograph for the prototype ADC (SC1)                                                                                                                               | 64   |

| 3.31        | Measured spectrum for the prototype ADC (SC1).                                                                                                                            | 65   |

| 3.32        | Measured SNR and SNDR with input signal power for the SC1                                                                                                                 | 66   |

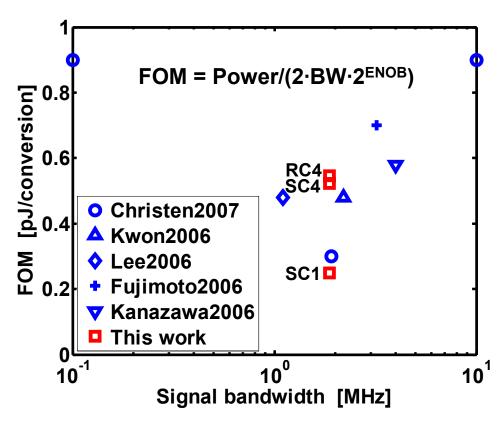

| 3.33        | Comparison with other DT modulators published recently                                                                                                                    | 67   |

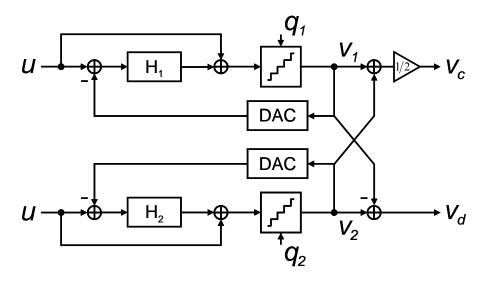

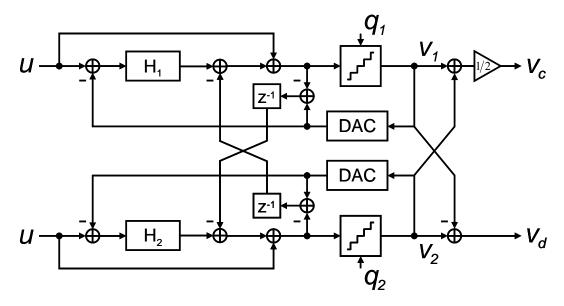

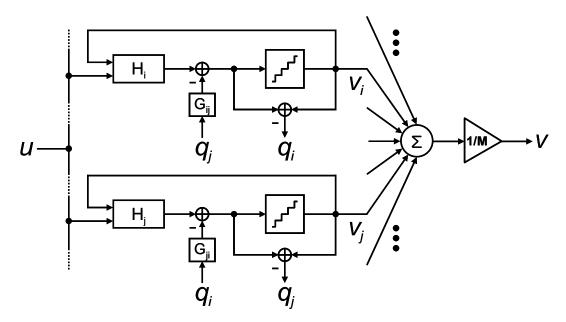

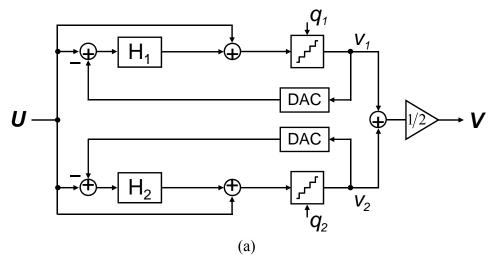

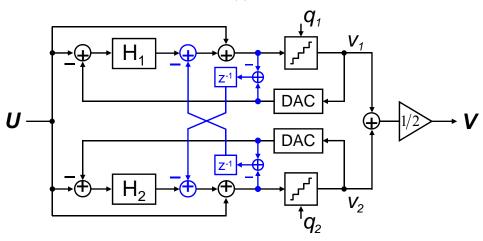

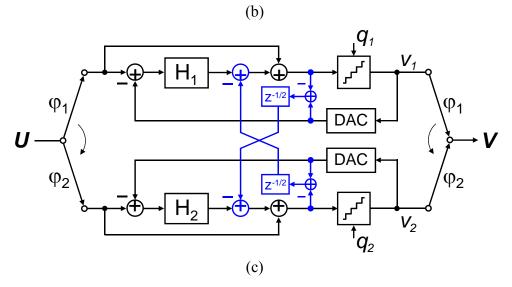

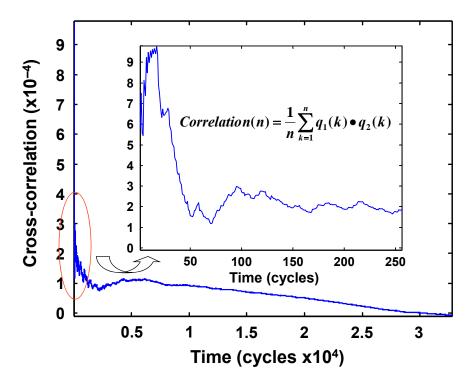

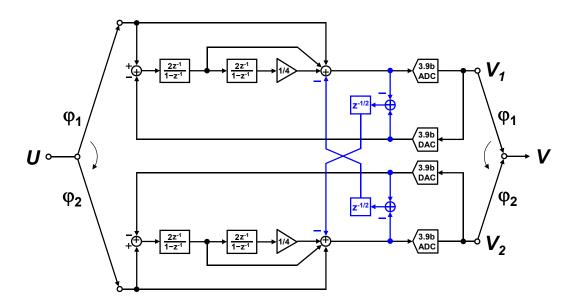

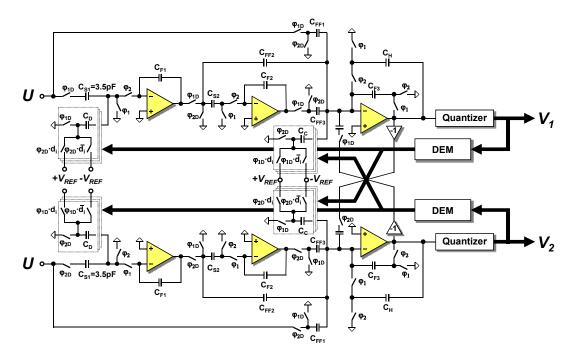

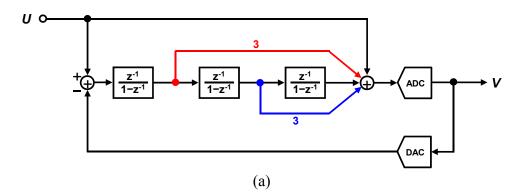

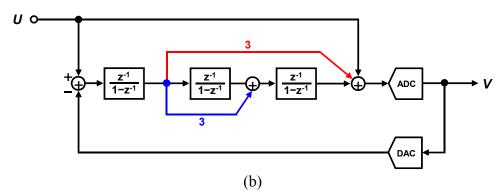

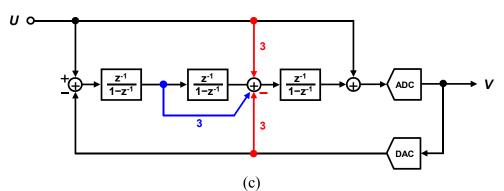

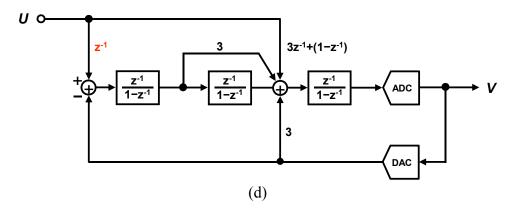

| 4.1         | Derivation of the proposed modulator architecture: (a) split modulator<br>(b) noise-coupled split (NCS) modulator (c) noise-coupled time-<br>interleaved (NCTI) modulator | 73   |

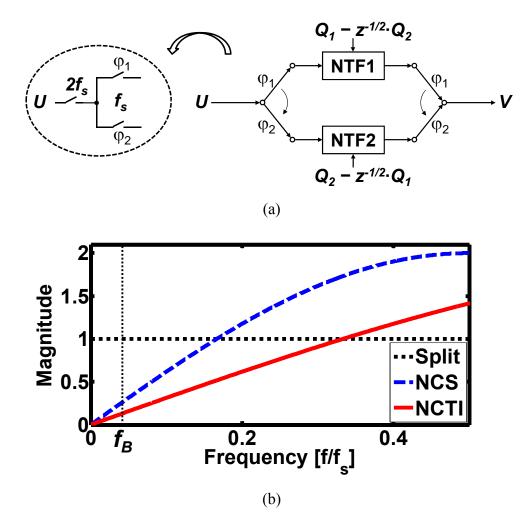

| 4.2         | The dcorrelation of quantization noises for a split delta-sigma ADC                                                                                                       | 75   |

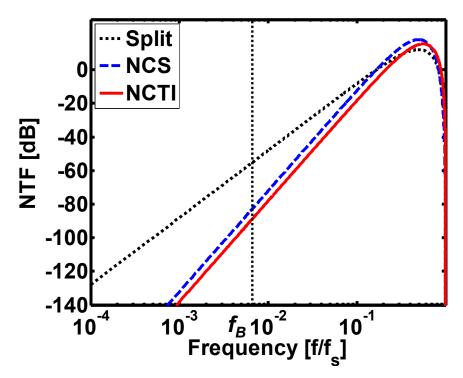

| 4.3         | (a) Block diagram of a NCTI modulator. (b) Comparison of the NTF enhancement factors for various split modulators.                                                        | 76   |

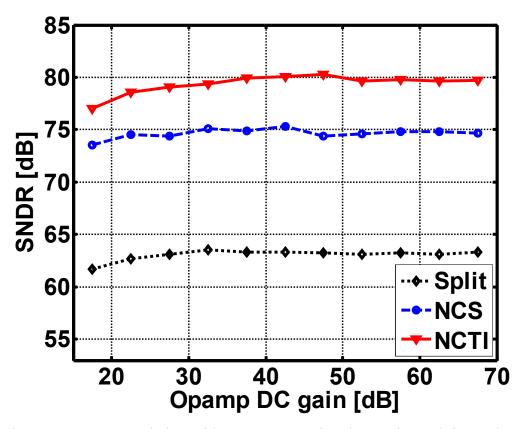

| 4.4         | Comparison of the NTFs of the three modulators shown in Fig. 4.1, with a second-order loop filter $H(z)$ .                                                                | 77   |

| 4.5         | SNDR variation with opamp DC gain whose mismatch is 5% between the two channels.                                                                                          | 78   |

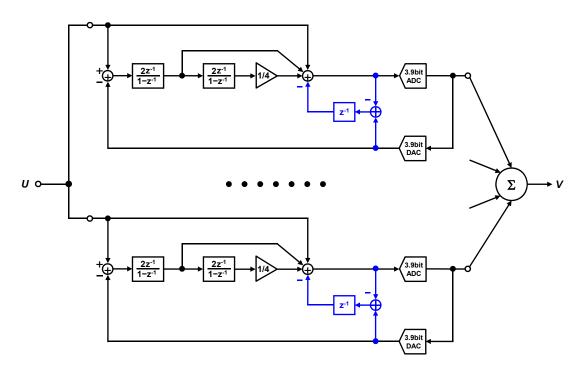

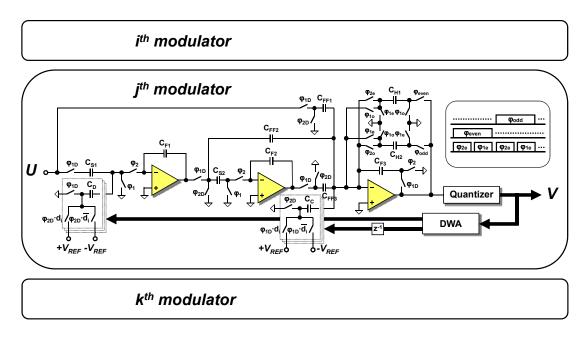

| 4.6         | Block diagram of the prototype ADC.                                                                                                                                       | 79   |

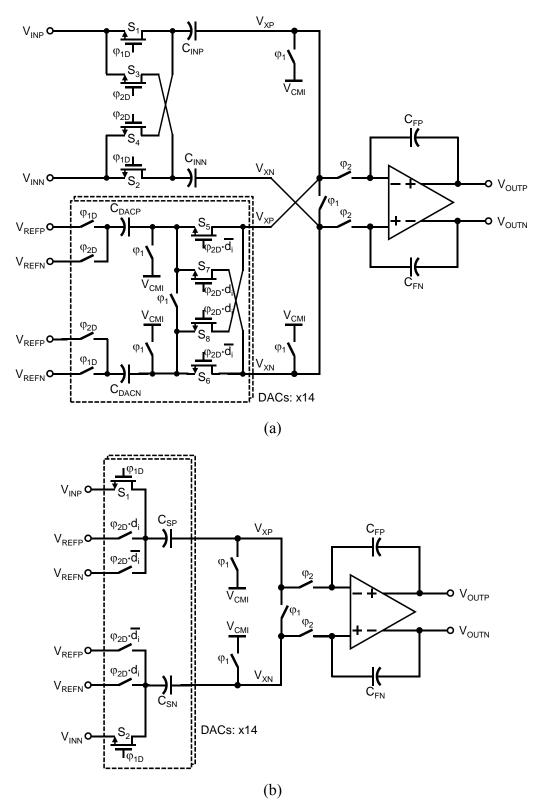

| 4.7         | SC circuit implementation of the prototype ADC                                                                                                                            | 80   |

| <u>Figu</u> | <u>re</u>                                                                                                                                            | Page |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.8         | SC circuit implementation of the 1 <sup>st</sup> integrator (a) for prototype A; (b) for prototype B.                                                | 81   |

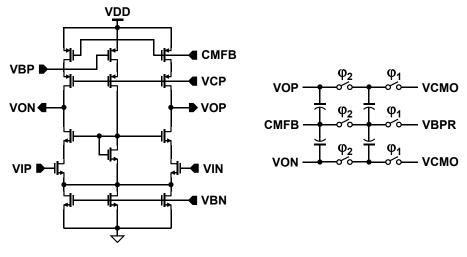

| 4.9         | Telescopic cascode opamp with SC common-mode feedback.                                                                                               | 82   |

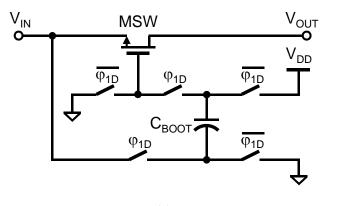

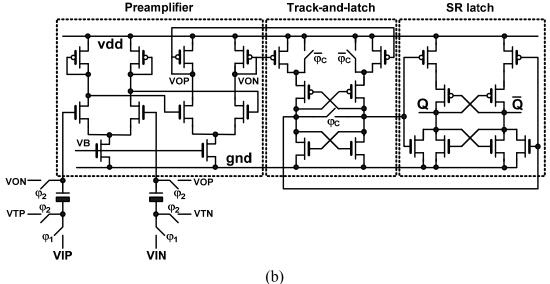

| 4.10        | The bootstrapped clock signal generator: (a) Simplified diagram; (b) Detailed circuit realization.                                                   | 83   |

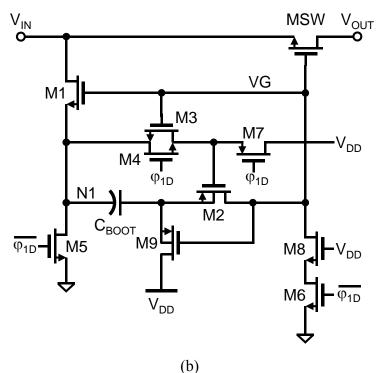

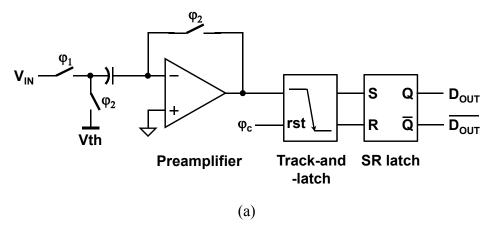

| 4.11        | Quantizer branch: (a) Block diagram (b) Circuit implementation                                                                                       | 84   |

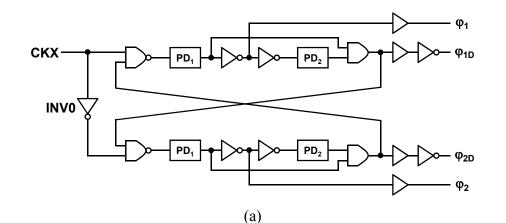

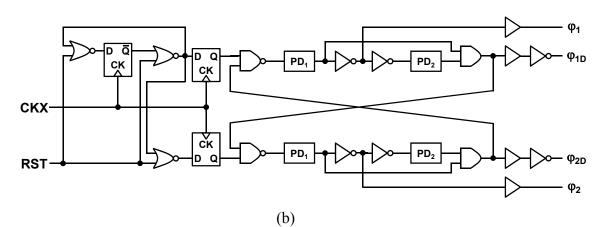

| 4.12        | Clock generator: (a) Conventional (b) Proposed.                                                                                                      | 85   |

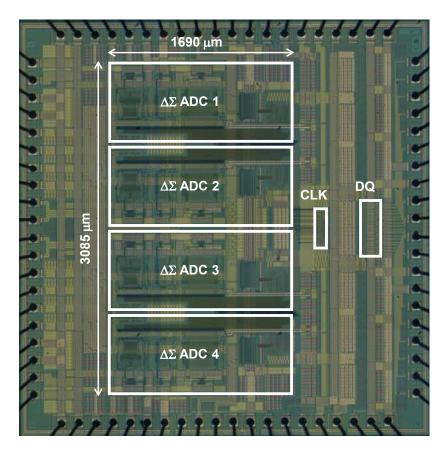

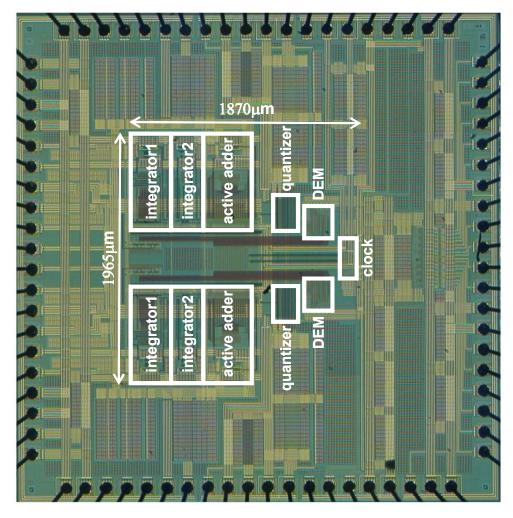

| 4.13        | Chip micrograph for prototype A                                                                                                                      | 86   |

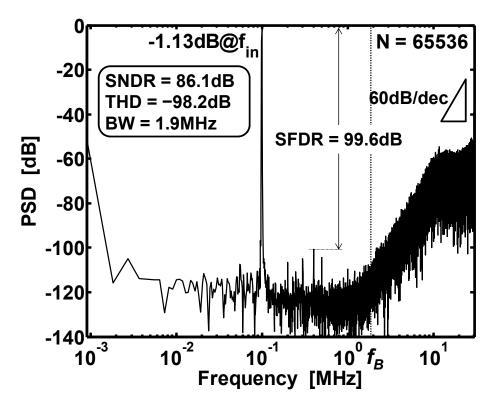

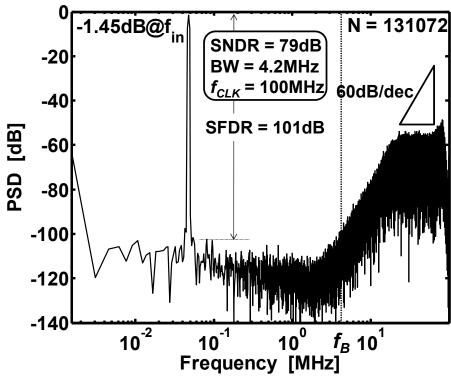

| 4.14        | Measured spectrum for prototype A.                                                                                                                   | 88   |

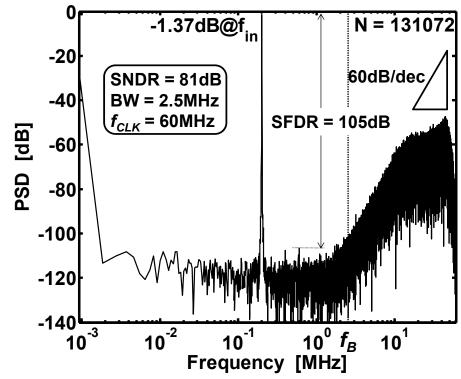

| 4.15        | Measured spectrum for prototype B                                                                                                                    | 88   |

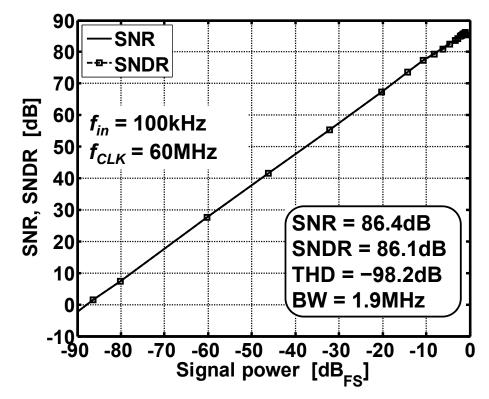

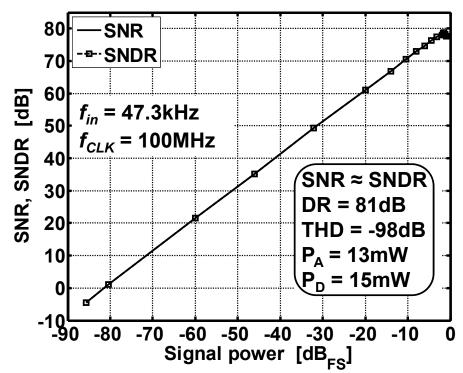

| 4.16        | Measured SNR and SNDR variation with input signal power for prototype A.                                                                             | 89   |

| 4.17        | Measured SNR, SNDR, and DR variation with input signal frequencies for prototype A.                                                                  | 89   |

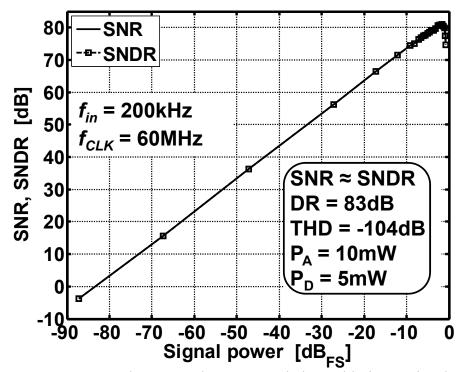

| 4.18        | Measured SNR and SNDR variation with input signal power for prototype B                                                                              | 90   |

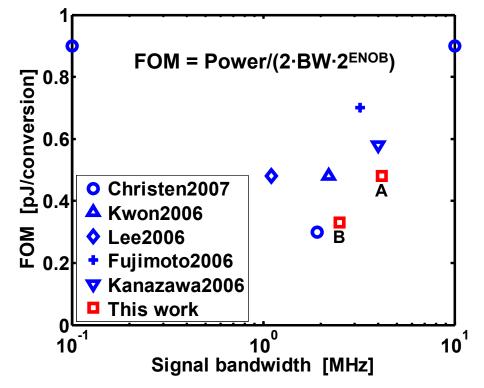

| 4.19        | Comparison with other DT modulators published recently                                                                                               | 91   |

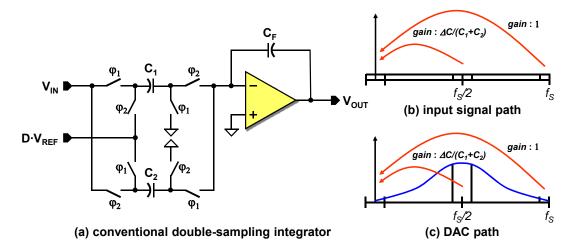

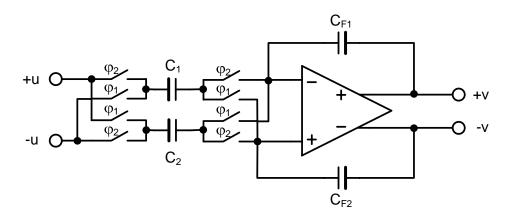

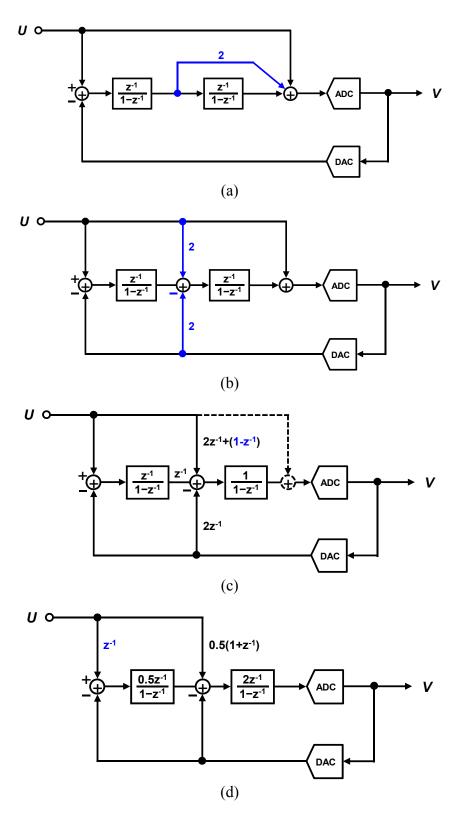

| 5.1         | Conventional double-sampling integrator and quantization noise folding by the amplitude modulation due to capacitor mismatch between $C_1$ and $C_2$ | 97   |

| 5.2         | Fully floating differential SC integrator                                                                                                            | 97   |

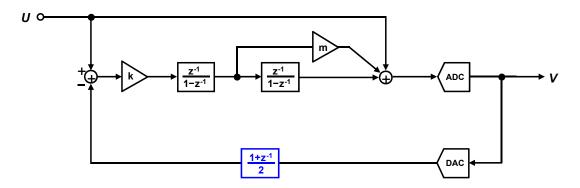

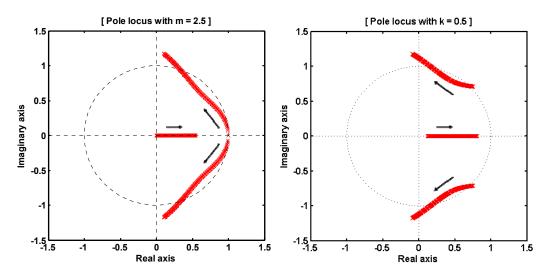

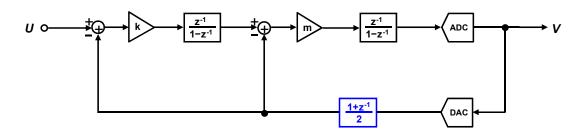

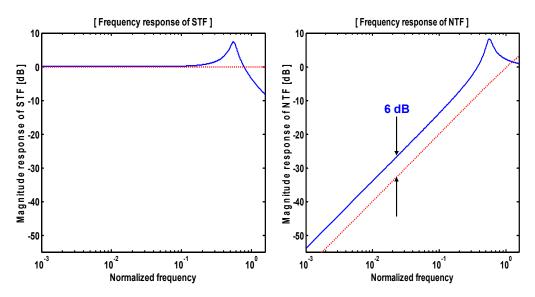

| 5.3         | Second-order low distortion modulator with extra feedback factor                                                                                     | 98   |

| 5.4         | (a) Pole locus with $k$ at $m = 2.5$ . (b) Pole locus with $m$ at $k = 0.5$ for modulator in Fig. 5.3 (arrows for increasing $k$ and $m$ )           | 99   |

| <u>Figu</u> | re                                                                                                                                                                                                                          | Page |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.5         | Frequency response of <i>STF</i> and <i>NTF</i> with $k = 0.5$ and $m = 2.5$ for modulator in Fig. 5.3. Dotted lines are for the same modulator without extra feedback factor.                                              | 99   |

| 5.6         | Second-order Boser-Wooley modulator with extra feedback factor                                                                                                                                                              | 100  |

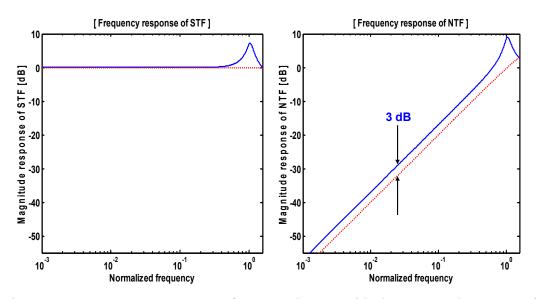

| 5.7         | (a) Pole locus with k at $m = 0.5$ . (b) Pole locus with m at $k = 0.5$ for modulator of Fig. 5.6 (arrows for increasing k and m).                                                                                          | 101  |

| 5.8         | Frequency response of <i>STF</i> and <i>NTF</i> with $k = 0.5$ and $m = 0.5$ for modulator in Fig. 5.6. Dotted lines are for the same modulator without extra feedback factor.                                              | 101  |

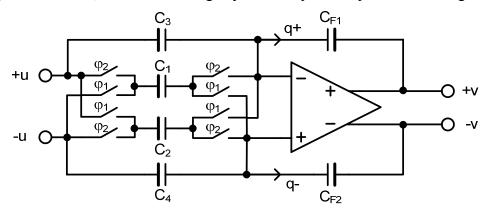

| 5.9         | Proposed floating differential SC integrator.                                                                                                                                                                               | 102  |

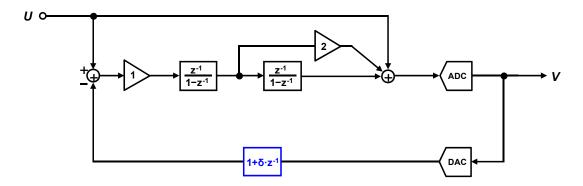

| 5.10        | Second-order low distortion modulator with the proposed fully-floating integrator                                                                                                                                           | 105  |

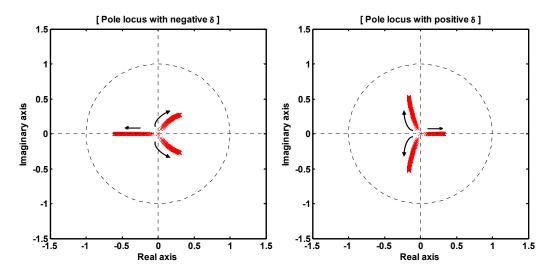

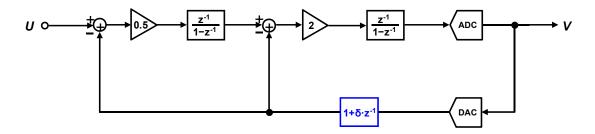

| 5.11        | (a) Pole locus with $\delta = -0.1 \sim 0$ . (b) Pole locus with $\delta = 0 \sim 0.1$ for the modulator shown in Fig. 5.10 (arrows indicate increasing $ \delta $ )                                                        | 105  |

| 5.12        | Second-order Boser-Wooley modulator with the proposed fully-floating integrator.                                                                                                                                            | 105  |

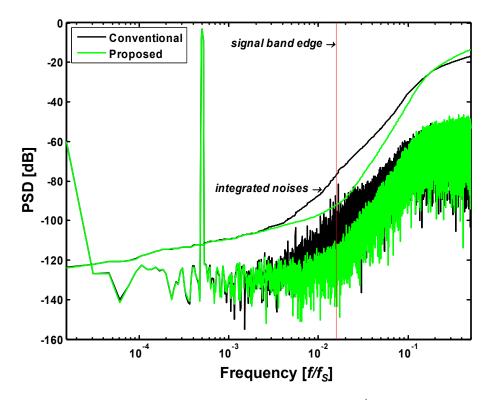

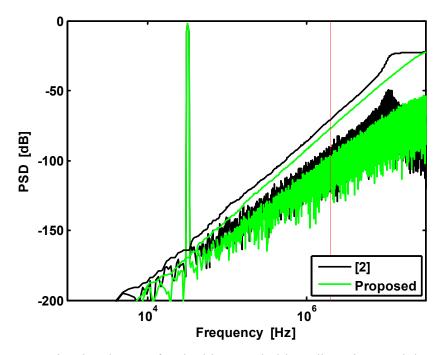

| 5.13        | Simulated PSDs for double-sampled low distortion modulator in Fig. 5.3 with the conventional Senderowicz integrator ( $SNDR = 70.7$ dB) and with the proposed fully-floating integrator ( $SNDR = 77.0$ dB)                 | 106  |

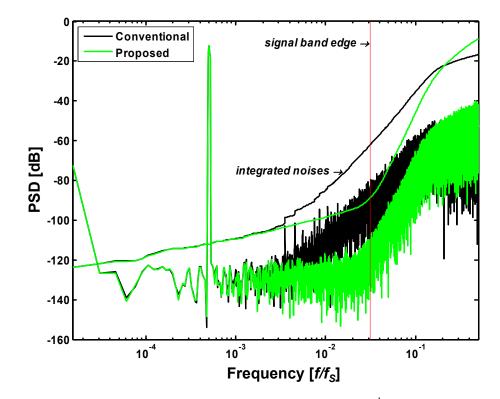

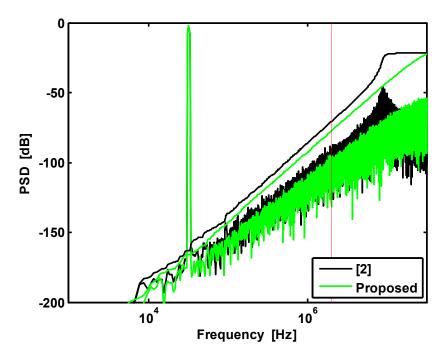

| 5.14        | Simulated PSDs for double-sampled Boser-Wooley modulator in Fig. 5.6 with the conventional Senderowicz integrator ( $SNDR = 70.6 \text{ dB}$ ) and with the proposed fully-floating integrator ( $SNDR = 77.5 \text{ dB}$ ) | 107  |

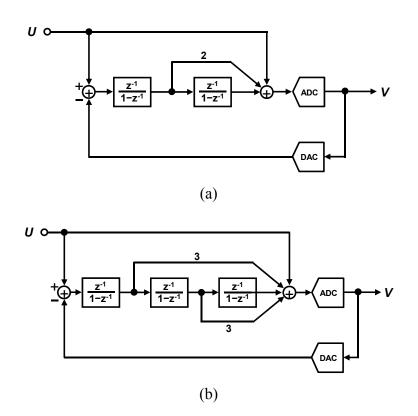

| 6.1         | Traditional single loop low-distortion modulator topologies: (a) $2^{nd}$ -order modulator (b) $3^{rd}$ -order modulator                                                                                                    | 112  |

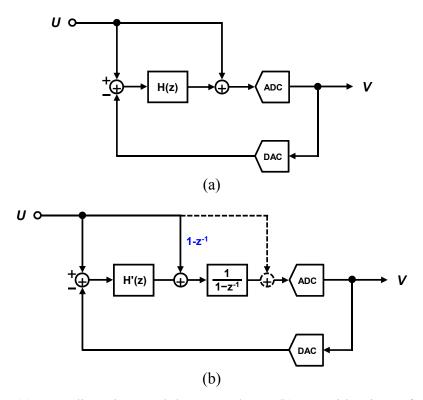

| 6.2         | (a) Low-distortion modulator topology (b) Capacitive input<br>feedforward (CIF) structure using an unswitched capacitor branch to<br>eliminate additional signal summation at the quantizer input                           | 114  |

| Figu | <u>re</u>                                                                                                                                                                                                              | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

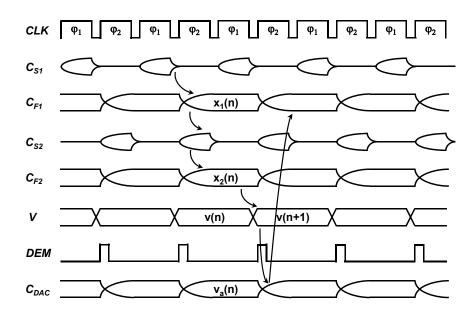

| 6.3  | Timing diagram for a second-order low-distortion modulator with CIF.<br>For proper shaping of DAC mismatch errors, the DEM switching<br>should be done within the nonoverlapping time interval of the clock<br>phases. | 114  |

| 6.4  | (a) Quantization noise self-coupling (QNSC) in a low-distortion modulator and (b) its equivalent topology.                                                                                                             | 115  |

| 6.5  | Digital feedforward (DFF) in a low-distortion modulator.                                                                                                                                                               | 116  |

| 6.6  | Delay redistribution (DRD) to relax DEM timing in a low-distortion modulator.                                                                                                                                          | 117  |

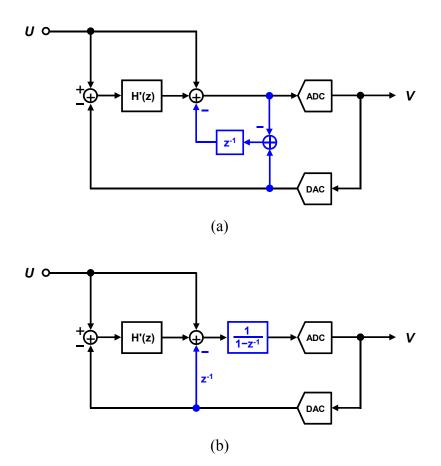

| 6.7  | One of key architectural modification techniques to achieve improved<br>low-distortion modulator topology.                                                                                                             | 119  |

| 6.8  | Steps to get the improved second-order low-distortion modulator based on equivalent transformation of its signal flow graph.                                                                                           | 120  |

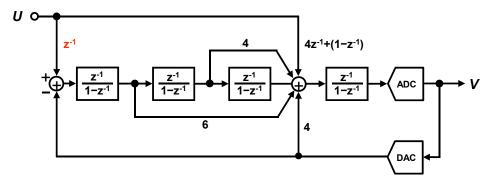

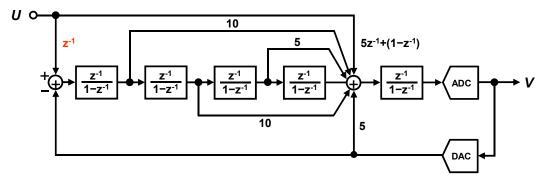

| 6.9  | Steps to get the improved third-order low-distortion modulator structure using equivalent transformations of its signal flow graph                                                                                     | 122  |

| 6.10 | Proposed improved fourth-order low-distortion modulator                                                                                                                                                                | 124  |

| 6.11 | Proposed improved fifth-order low-distortion modulator                                                                                                                                                                 | 124  |

## LIST OF TABLES

| Table |                                                     | Page |

|-------|-----------------------------------------------------|------|

| 2.1   | Filter coefficient in CSD for the first HBF.        | 11   |

| 2.2   | Thresholds of the 7-level quantizer                 | 16   |

| 2.3   | Measured power dissipation of the digital chip      | 18   |

| 2.4   | Components values for the second-order Rauch filter | 23   |

| 2.5   | Performance summary                                 | 28   |

| 2.6   | Performance comparison                              | 29   |

| 3.1   | Performance summary for the RC4                     | 53   |

| 3.2   | Performance summary for the SC4                     | 60   |

| 3.3   | Performance summary for the SC1                     | 66   |

| 4.1   | Performance summary                                 | 91   |

## DEDICATION

## Praise The Lord for his gracious guidance and being with me!

I would like to express my deepest gratitude to my family for their sacrifice and unconditional love. I would like to dedicate this dissertation to my parents, Narkhun Lee and Boonhark Goo, my parents-in-law, Donghyun Kim and Duksim Kim. My admired father, who passed away during my study, taught me the importance of learning and education and did his best during his life to provide good educational environment to his family. My beloved mother always showed me an endless love, sacrifice, and support. My adored parents-in-law gave me a deep faith and encouragement. This work was made possible with the love and patience of my beloved and treasured wife, Jungyeon Kim. I thank my dear two sons, Seyeon and Elliot Sebin, for their growing with good health and brightness. To my parents Narkhun Lee and Boonhark Goo, my parents-in-law Donghyun Kim and Duksim Kim, my wife Jungyeon Kim, my sons Seyeon and Elliot Sebin

# HIGH EFFICIENCY DELTA-SIGMA MODULATION DATA CONVERTERS

## **CHAPTER 1. INTRODUCTION**

### 1.1. MOTIVATION

The application of delta-sigma modulation data converter is getting extended rapidly to new emerging applications such as wired and wireless communications in addition to commodity consumer electronics beyond its earlier traditional narrowband applications. This popularity comes from its inherent high resolution and low power characteristics. It is also triggered by the dramatic increase of signal bandwidth from several tens kHz to several tens MHz the delta-sigma modulation data converter can deal with. It is enabled by device scaling, architectural innovations, and efficient circuit design. One of the great advantages of delta-sigma modulation data converter is that the accuracy requirements for its analog circuitry are greatly relaxed thanks to oversampling and noise shaping. This relaxation can be further expanded by introducing more effective modulator architecture such as lowdistortion topology. We need to maximize this leverage of architectural modifications to cope with design challenges and to meet more demanding design specifications.

In this dissertation, novel design techniques based on both architecture and circuit level are proposed to improve the efficiency of delta-sigma modulation data converter. The efficiency of a data converter can be quantitatively specified by the figure-of-merit (FOM) defined as dissipated power divided by bandwidth and total effective conversion steps that is calculated with 2 to the power of effective number of bits. The effectiveness of the proposed techniques is validated by experimentation with cutting-edge prototype designs.

### **1.2. CONTRIBUTIONS OF THIS RESEARCH**

The major contributions of this research can be summarized as follows.

- Low-voltage and low-power time-interleaved interpolation filter and deltasigma modulator design and its verification with CMOS for dual-channel audio DAC.

- Multi-cell architecture and first-order quantization noise coupling across modulator loops and within each loop of delta-sigma ADC.

- Generalization of quantization noise coupling to higher-order enhancement.

- Clarification of time evolution of cross-correlation and auto-correlation of quantization noises of multi-cell and noise-coupled delta-sigma ADC.

- Extension of noise coupling to time-interleaved delta-sigma ADC.

- SC circuit realization and verification with CMOS for various types of noisecoupled delta-sigma ADCs.

- Realization of state-of-the-art high-efficiency and high-linearity wideband delta-sigma ADC.

- Analysis of extra feedback factor introduced with conventional Senderowicz's double-sampling integrator onto the stability of modulator loop and the introduction of efficient double-sampling integrator.

- Development of improved low-distortion topology for delta-sigma ADC which does not require signal summation at the input of quantizer and allows

relaxed timing for dynamic element matching (DEM) to linearize multi-bit DAC in single-sampled operation.

• Development of improved low-distortion topology suitable for doublesampling delta-sigma ADC.

### **1.3. ORGANIZATION OF DISSERTATION**

Design techniques for improving the efficiency of data converter are shown in the first three chapters for a low-voltage audio delta-sigma DAC and wideband highlinearity delta-sigma ADCs. In the following two chapters, key issues with each conventional double-sampling modulator and low-distortion modulator are addressed and effective solutions are proposed, respectively.

In Chapter 2, the first sub-1V dual-channel audio DAC with on-chip headphone driver is presented. Various design techniques to enhance the hardware efficiency of interpolation filter, delta-sigma modulator, and DEM circuitry are described.

In Chapter 3, novel architectures for delta-sigma ADCs are proposed based on multi-cell structure and quantization noise coupling. Cellular approach allows robustness and flexibility. Noise coupling enhances the noise shaping of modulator loops without degrading its stability and improves the linearity of the modulator. Measured results prove the proposed concepts.

In Chapter 4, a wideband high-linearity delta-sigma ADC is introduced. The noise coupling is applied to time-interleaving modulator, which results in 19 dB SQNR improvement with little extra circuitry. Two versions of a two-channel time-interleaved noise-coupled delta-sigma ADC are described. Both prototypes show leading-edge performance.

In Chapter 5, the limitations of conventional double-sampling technique are analyzed and novel double-sampling architecture is proposed. The same modulator coefficients and design methodology available for a single-sampled modulator are applicable to a double-sampled modulator with the proposed architecture.

In Chapter 6, an improved low-distortion delta-sigma modulator topology is proposed to overcome the associated drawback of prior art. The efficiency of deltasigma ADC can be significantly improved by applying both techniques introduced in Chapter 5 and 6.

# CHAPTER 2. A 0.8 V, 2.6 MW, 88 DB DUAL-CHANNEL AUDIO DELTA-SIGMA MODULATION D/A CONVERTER WITH HEADPHONE DRIVER

#### Abstract

A 0.8 V third-order  $\Delta\Sigma$  DAC with headphone driver is described. The circuit requires only one opamp per channel, which is shared by the internal DAC, the FIR and a second-order Rauch low-pass filter, as well as by the headphone driver. Two prototype ICs (separate digital and analog chips), implemented in a 0.35µm CMOS process, achieved 88 dB dynamic range, while consuming 2.6 mW from a 0.8 V supply.

### 2.1. INTRODUCTION

Battery-powered portable audio devices require low-voltage, low-power, and medium-accuracy digital-to-analog converters (DACs). With the continuing demand for portable consumer electronics, such as digital audio/video (AV), cellular phones, and handheld global positioning systems, the downscaling of device dimensions to enable the integration of increasing numbers of transistors on a single chip is important. This trend also results in lowered power supply voltages, to reduce the power consumption and to improve the reliability of gate dielectrics. As predicted by International Technology Roadmap for Semiconductors (ITRS), for low operating power, the power supply voltage and gate length of digital CMOS devices will continue to scale down towards 0.5 V in the next decade. While the reduction of power supply voltages benefits the essential digital blocks performing data storage

and digital signal processing, it makes it hard to realize indispensable analog building blocks, such as analog-to-digital converters (ADCs), DACs, and drivers.

Delta-sigma ( $\Delta\Sigma$ ) data converters employ oversampling and noise shaping to achieve a wide dynamic range (DR) in the band of interest. They trade speed and digital complexity for the desired insensitivity to analog nonidealities, which results in high DR with low-cost and low-power digital circuitry.

In this chapter, an audio-band  $\Delta\Sigma$  DAC will be discussed. It contains a digital interpolation filter, followed by a digital  $\Delta\Sigma$  modulator, a low-resolution DAC, and an analog low-pass filter. The basic criteria for selecting the order of the  $\Delta\Sigma$  modulator and the quantizer resolution are 1) to make the pass-band quantization noise sufficiently low, so that the analog noises (thermal noise and 1/f noise) dominate the noise budget; 2) to reduce the out-of-band noise sufficiently so a low-order analog postfilter may be used; 3) to reduce clock jitter sensitivity sufficiently at the discrete-to-continuous-time interface [2].

Since thermal noise, sampled noise (kT/C), and transistor flicker noise do not scale down with the finer line-width process, smaller resistors, bigger capacitors and transistors have to be used to reduce noise, which necessitates larger drivers with more power consumption; furthermore, due to the reduced signal voltage swing, to achieve the required signal-to-noise plus distortion ratio (SNDR), extra power has to be dissipated. Switched-capacitor direct-charge-transfer DACs [2],[3] have superior noise-versus-power efficiency, but they require floating switches, which are difficult to implement with a low supply voltage. Bootstrapping [4] and switched-RC [5] circuits were proposed to realize the floating switches. In the first approach, the voltage difference between the gate and the source is kept constant at a level high enough to turn on the switch. However, this is not a truly low-voltage solution, especially for a nanometer process, since the gate voltage can then become higher

than the supply voltage, which results in potential reliability issues. In switched-RC circuits, the floating switches are replaced by resistors, and signal leakage occurs through them. This causes nonlinearity, which needs careful circuit design and optimization.

This chapter proposes a new DAC structure [6] that contains no floating switches, and requires only one opamp per channel, shared by the internal DAC, an FIR sampled-data filter, and a second-order Rauch low-pass filter [7],[8], as well as by the headphone driver. It achieves an 88 dB DR over a 20 Hz to 24 kHz passband, and consumes 2.6 mW from a 0.8 V power supply. (To our knowledge, this is the first sub-1V audio  $\Delta\Sigma$  DAC with headphone driver integrated.) Section 2.2 describes the architecture of the DAC. Section 2.3 describes the digital stages including the interpolation filter, the  $\Delta\Sigma$  modulator and the dynamic element matching (DEM) circuitry. Section 2.4 presents the low-voltage and low-power analog DAC structure. The experimental results are shown in Section 2.5. Finally, a summary is provided in Section 2.6.

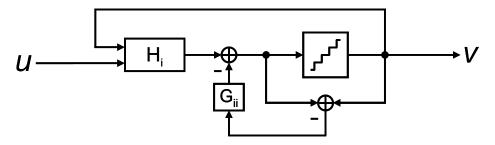

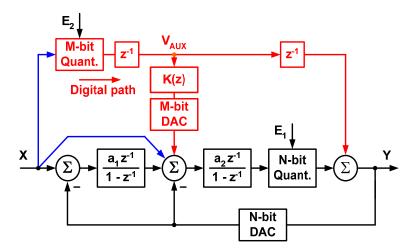

#### 2.2. ARCHITECTURE

The block diagram of the DAC is shown in Fig. 2.1. The digital part contains a four-stage finite impulse response (FIR) interpolation filter, a  $\Delta\Sigma$  modulator (DSM) and a data-weighted averaging (DWA) logic. The analog part contains the two switched-resistor DACs (R-DAC) and the RC low-pass filters (RC-LPF) that also act as the drivers for the headphones. The digital filter increases the sampling rate from  $f_s = 48$  kHz to  $64 \cdot f_s = 3.072$  MHz, and suppresses the spectral replicas to improve the DR of the DSM, and to simplify the analog filtering performed by the RC-LPF. The DSM reduces the word length of the signal from 17 bits to 3 bits, with

Figure 2.1: DAC architecture.

negligible added passband truncation noise. The DWA scrambles the bits of the thermometer-coded output of the DSM, so as to reduce the in-band power spectral density of the error due to element mismatches in the R-DAC. Finally, the RC-LPF both filters and buffers the DAC output, and is capable of driving a low-impedance  $(16 \Omega \parallel 300 \text{ pF})$  headphone.

### 2.3. DIGITAL STAGES

The digital section of the DAC includes a serial-to-parallel converter, an interpolation filter, a  $\Delta\Sigma$  modulator, and the DWA logic for the DAC.

#### 2.3.1. Serial to parallel converter

The 1b serial input data is converted into 16b parallel output data for the signal processing performed in interpolation filter.

#### 2.3.2. Interpolation filter

Figure 2.2: Frequency responses of the HBFs in the interpolation filter.

An efficient dual-channel interpolation filter was required. The strict requirements on the linear phase characteristics in audio applications mandate the use of a FIR filter, rather than an infinite impulse response (IIR) filter. An FIR interpolation filter is hardware-intensive compared to the other design blocks. So an efficient realization of the interpolation filter was important to minimize its silicon area and power consumption. To this end, it was realized with as a cascade of several stages, rather than a single stage [9]. Also, the total number of multiplication with the filter coefficient was minimized by using half-band filter (HBF) sections. The filter coefficients in a linear-phase FIR filter are symmetric with respect to the center tap, which allows the reduction by half of the required multiplication with the filter coefficients. In addition to this advantage, HBF has a zero filter coefficient at every other tap (except for the center tap). Also, each filter coefficient was quantized to the sum of a few integer powers of two, and represented by a canonic signed digit (CSD). The CSD allows encoding a binary number such that it contains the minimum possible number of non-zero bits [10]. The computation-intensive multiplication with filter coefficient is thus replaced with a few shift-and-add operations without multiplier. More aggressive quantization was applied to filter coefficients that were distant from the center tap. This results from the observation that the required accuracy for each filter coefficient is relaxed proportionately with its distance from the center tap. This reduces the total number of computation with negligible performance degradation. The computation path that takes more than half of the total active chip area was shared by both channels by introducing a time-interleaved operation between channels, at the cost of the doubled operating frequency. This enables a significant saving of silicon area without increasing the power consumption. Finally, all required filtering operations in all stages are performed using the lowest possible clock frequency to reduce the power dissipation.

The interpolation filter is composed of three cascaded FIR HBFs, followed by a sample-and-hold register. It interpolates by the oversampling ratio (OSR = 64), and achieves more than 57dB attenuation in the stopband and less than  $\pm 0.02$ dB ripple in the passband. The first 3 HBFs increase the OSR to 8, and the last sample-and-hold stage further increases the OSR by 8 times, to provide the overall OSR of 64. The first HBF is the most demanding, since it provides the sharpest cutoff. Later stages are simplified due to their much wider transition bandwidth specifications, as illustrated in Fig. 2.2. The orders of the three FIR filter stages are 66, 14, and 2. Thus, the numbers of realized distinct nonzero filter coefficients for these filters are 17, 4, and 1 thanks to their HBF properties. The filter coefficients are obtained using the method described in [11]. Table 2.1 shows the quantized filter coefficients in CSD for the first HBF. A direct-form structure, shown in Fig. 2.3, was selected for each

| Coeff | icient | Value             | CSD                                                                                    | Relative Error (%) |

|-------|--------|-------------------|----------------------------------------------------------------------------------------|--------------------|

| C(1)  | C(67)  | 0.00112899823880  | 2 <sup>-10</sup> +2 <sup>-13</sup>                                                     | -2.6895902         |

| C(3)  | C(65)  | -0.00119220557225 | -2 <sup>-10</sup> -2 <sup>-12</sup>                                                    | 2.3903221          |

| C(5)  | C(63)  | 0.00178804184892  | 2 <sup>-9</sup> -2 <sup>-13</sup>                                                      | 2.4055834          |

| C(7)  | C(61)  | -0.00257976433083 | -2 <sup>-9</sup> -2 <sup>-11</sup> -2 <sup>-13</sup>                                   | -0.6313665         |

| C(9)  | C(59)  | 0.00357827122113  | 2 <sup>-8</sup> -2 <sup>-12</sup> -2 <sup>-14</sup>                                    | 0.6372630          |

| C(11) | C(57)  | -0.00485062139929 | -2 <sup>-8</sup> -2 <sup>-10</sup>                                                     | 0.6636490          |

| C(13) | C(55)  | 0.00642693964630  | 2 <sup>-7</sup> -2 <sup>-10</sup> -2 <sup>-11</sup> +2 <sup>-14</sup>                  | -0.2839336         |

| C(15) | C(53)  | -0.00840515050728 | -2 <sup>-7</sup> -2 <sup>-11</sup> -2 <sup>-13</sup>                                   | 0.2105977          |

| C(17) | C(51)  | 0.01085841433138  | 2 <sup>-7</sup> +2 <sup>-8</sup> -2 <sup>-10</sup> +2 <sup>-13</sup>                   | 0.0538152          |

| C(19) | C(49)  | -0.01396316591895 | -2 <sup>-6</sup> +2 <sup>-9</sup> -2 <sup>-12</sup> -2 <sup>-14</sup>                  | 0.0994392          |

| C(21) | C(47)  | 0.01793207410656  | 2 <sup>-6</sup> +2 <sup>-9</sup> +2 <sup>-12</sup> +2 <sup>-13</sup>                   | 0.0683793          |

| C(23) | C(45)  | -0.02320312292368 | -2 <sup>-6</sup> -2 <sup>-7</sup> +2 <sup>-12</sup>                                    | -0.0420786         |

| C(25) | C(43)  | 0.03053302596726  | 2 <sup>-5</sup> -2 <sup>-11</sup> -2 <sup>-12</sup>                                    | -0.0505939         |

| C(27) | C(41)  | -0.04162991022557 | -2 <sup>-5</sup> -2 <sup>-7</sup> -2 <sup>-9</sup> -2 <sup>-11</sup> -2 <sup>-13</sup> | -0.0094491         |

| C(29) | C(39)  | 0.06086374667043  | 2 <sup>-4</sup> -2 <sup>-9</sup> +2 <sup>-12</sup> +2 <sup>-14</sup>                   | -0.0192165         |

| C(31) | C(37)  | -0.10440943788907 | -2 <sup>-3</sup> +2 <sup>-6</sup> +2 <sup>-8</sup> +2 <sup>-10</sup>                   | 0.0792549          |

| C(33) | C(35)  | 0.31773802216750  | 2 <sup>-2</sup> +2 <sup>-4</sup> +2 <sup>-8</sup> +2 <sup>-10</sup> +2 <sup>-12</sup>  | -0.0349562         |

TABLE 2.1: FILTER COEFFICIENT IN CSD FOR THE FIRST HBF.

FIR filter, instead of a transposed direct-form one, where extra registers are required to generate the center tap data. The relatively long critical-path delay with this structure is not an issue in this design, even without any retiming, since it takes a small fraction of the whole operation period. As mentioned earlier, each filter coefficient is quantized as a sum of a few integer powers of 2, and is realized as a series of shift-and-add operations. Since fixed filter coefficients are used in this design, the shift operation is realized in a hard-wired circuit without extra registers. A ripple-carry adder (RCA) is employed throughout the design. Four types of adder cells are used, each with the same transistor count. One of them is shown in Fig. 2.4. The two adder cells in category I are for addition, and the other two in category II for subtraction. One adder takes carry-in and outputs inverted carry-out, and the other

Figure 2.3: Direct form realization of the HBFs and a sample-and-hold register.

takes inverted carry-in and outputs carry-out in each category. The word length for each internal node of the interpolation filter is chosen carefully to avoid an overflow with a full-scale input signal. The truncation error in CSD multiplication is minimized by applying Horner's rule to all the partial product accumulations, where the scaling operation common to the partial products are delayed to improve its accuracy [10]. As illustrated in Fig. 2.3, the cascaded registers represented in  $z^{-2}$  and doubled operating frequency enable the time-interleaved operation of the two channels. Therefore, all channel data are processed in every other cycle. Care was

Figure 2.4: One of the four basic adder cells.

taken in reordering the interleaved output data stream from each stage of the interpolation filter for the proper time- interleaved dual-channel operation in the following stage. This was achieved with an additional register in the filtering path and a proper control signal to the multiplexer, as shown in Fig. 2.3.

The simulated SNR of the interpolation filter with a 16b resolution full-scale sinewave input was 96.2 dB, while the SNRs of the intermediate HBF stages were 96.9 dB, 96.2 dB, and 96.1 dB.

#### 2.3.3. Delta-sigma modulator

The main design considerations for the  $\Delta\Sigma$  modulator were: 1) negligible in-band quantization noise compared with the analog noise; 2) reduced complexity of the reconstruction filter; 3) reduced sensitivity to clock jitter for the following analog circuitry; 4) reduced idle tones; 5) minimized word length for the adders and

Figure 2.5: Dual-channel third-order  $\Delta\Sigma$  modulator with resonator.

Figure 2.6: Histogram of the internal nodes in the  $\Delta\Sigma$  modulator.

registers. Based on these criteria, a third-order modulator with a 7-level truncator, shown in Fig. 2.5, was realized. Since its in-band quantization noise is less than -95 dB, the total noise budget is dominated by the analog noise of the following stages,

Figure 2.7: Bit alignment of the  $\Delta\Sigma$  modulator.

such as 1/f and thermal noise, clock jitter noise, and mismatch noise.

The word length and power dissipation in each accumulator is reduced by using a direct feedforward path from the input to the quantizer. The word length in each accumulator was determined by requiring that its input-referred truncation noise power be -120 dB below the full-scale signal power [12]. After appending a guard bit to prevent the overload condition, the final word length was confirmed using fixed-point simulation. The histogram plots for the outputs of each accumulator and the

| Quantizer Input (Y) | Input Range         | Decision Range      | Quantizer Output | Decimal Value |

|---------------------|---------------------|---------------------|------------------|---------------|

| 0.111X              | 7 / 8 ≤ Y < 1       |                     |                  |               |

| 0.110X              | 6 / 8 ≤ Y < 7 / 8   | 5 / 8 ≤ Y < 1       | 0.11             | 3 / 4         |

| 0.101X              | 5 / 8 ≤ Y < 6 / 8   |                     |                  |               |

| 0.100X              | 4 / 8 ≤ Y < 5 / 8   |                     | 0.40             | 0/4           |

| 0.011X              | 3 / 8 ≤ Y < 4 / 8   | 3 / 8 ≤ Y < 5 / 8   | 0.10             | 2/4           |

| 0.010X              | 2 / 8 ≤ Y < 3 / 8   |                     | 0.04             |               |

| 0.001X              | 1 / 8 ≤ Y < 2 / 8   | 1 / 8 ≤ Y < 3 / 8   | 0.01             | 1/4           |

| 0.000X              | 0 ≤ Y < 1 / 8       |                     |                  |               |

| 1.111X              | −1 / 8 ≤ Y < 0      | -1 / 8 ≤ Y < 1 / 8  | 0.00             | 0             |

| 1.110X              | -2 / 8 ≤ Y < -1 / 8 |                     |                  |               |

| 1.101X              | -3 / 8 ≤ Y < -2 / 8 | -3 / 8 ≤ Y < -1 / 8 | 1.11             | -1 / 4        |

| 1.100X              | -4 / 8 ≤ Y < -3 / 8 |                     |                  | 0/4           |

| 1.011X              | -5 / 8 ≤ Y < -4 / 8 | -5 / 8 ≤ Y < -3 / 8 | 1.10             | -2 / 4        |

| 1.010X              | -6 / 8 ≤ Y < -5 / 8 |                     |                  |               |

| 1.001X              | -7 / 8 ≤ Y < -6 / 8 | −1 ≤ Y < −5 / 8     | 1.01             | - 3 / 4       |

| 1.000X              | −1 < Y < −7 / 8     |                     |                  |               |

TABLE 2.2: THRESHOLDS OF THE 7-LEVEL QUANTIZER.

Figure 2.8: Schematic for 7-level quantizer.

input of the quantizer are shown in Fig. 2.6. They confirm the stable operation of the modulator, and a reasonable signal swing with a full-scale input signal. The resonator formed by the local feedback path  $(-p_3)$  minimizes the in-band quantization

Figure 2.9: Dither from the LFSR in Galois configuration [13].

noise in the modulator loop by placing two complex-conjugate zeros close to the edge of the signal band. The optimized zeros of the noise transfer function NTF (one at DC and the other two at 20.4 kHz) in the third-order loop improves the signal-toquantization noise ratio (SQNR) by 8 dB. The word length for the local feedback path  $p_3$  is only 6, due to its small value. The bit alignment for each node in the modulator is shown in Fig. 2.7. A carry-save adder (CSA) is used at the summing node of the modulator to reduce the carry-propagation delay. The thresholds of the 7-level quantizer and its detailed schematic are shown in Table 2.2 and Fig. 2.8. Idle tones are suppressed by injecting a dither signal that is generated using a linear feedback shift register (LFSR) in Galois configuration. The generator polynomial of the LFSR is  $x^{19}+x^6+x^5+x+1$ . The pseudo-random binary sequence from the LFSR is scaled and differentiated before it is injected [13], as shown in Fig. 2.9. The scale factor is programmable down from 1/16 up to half the step size of the quantizer threshold. A single modulator is time-shared between the two channels, using the cascaded registers at doubled frequency, as in the interpolation filter.

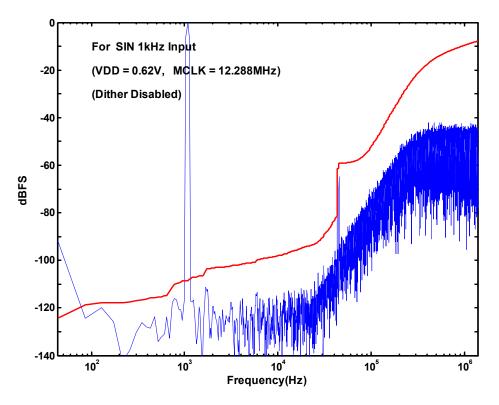

The simulated and measured SNRs of the  $\Delta\Sigma$  modulator with a 16b full-scale single-tone input were 95.9 dB and 95.6 dB, respectively. The measured spectrum at  $V_{DD} = 0.62V$  is shown in Fig. 2.10. The out-of-band tone at 44 kHz results from the limited (57 dB) stopband attenuation in the first HBF. This tone is reduced further by

Figure 2.10: Measured spectrum for the  $\Delta\Sigma$  modulator at V<sub>DD</sub> = 0.62 V.

| Supply | Power Consumption |

|--------|-------------------|

| 0.7 V  | 0.098 mW          |

| 0.8 V  | 0.128 mW          |

| 0.9 V  | 0.162 mW          |

| 1.0 V  | 0.200 mW          |

| 1.1 V  | 0.242 mW          |

| 1.2 V  | 0.288 mW          |

| 1.5 V  | 0.495 mW          |

| 1.8 V  | 0.954 mW          |

TABLE 2.3: MEASURED POWER DISSIPATION OF THE DIGITAL CHIP.

the following analog filter. Measurements showed that this performance can be obtained with supply voltages in the range of 0.62 V  $\sim$  1.8 V. The power consumption increases from 98  $\mu$ W to 954  $\mu$ W as shown in Table 2.3.

| DSM Output<br>(7 level) | 2's Complement<br>[B3 B2 B1] | Accumulator Input<br>[~B3 B2 B1] | Pointer<br>P(i+1) |

|-------------------------|------------------------------|----------------------------------|-------------------|

| -3/4                    | 101                          | 001 (1)                          | P(i)+1            |

| -2/4                    | 110                          | 010 (2)                          | P(i)+2            |

| -1/4                    | 111                          | 011 (3)                          | P(i)+3            |

| 0                       | 000                          | 100 (4)                          | P(i)+4            |

| 1/4                     | 001                          | 101 (5)                          | P(i)+5            |

| 2/4                     | 010                          | 110 (6)                          | P(i)+6            |

| 3/4                     | 011                          | 111 (7)                          | P(i)+7            |

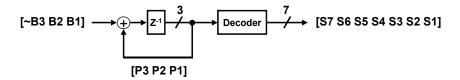

Figure 2.11: Pointer generation for DWA. A 3b RCA with modulo 7 is used for the accumulator.

### 2.3.4. DWA

The DWA stage effectively filters the mismatch noise from the following multibit R-DAC. It is common to use 6 element DAC following a  $\Delta\Sigma$  modulator with a 7-level quantizer. In this design, a seven-element DAC is created by adding one extra element to the usual six-element DAC, to shift the DAC mismatch noise and DWA-induced tones away from the signal band. An incremental DWA was applied to the N + K element DAC, where N is the original DAC element number and K is the number of added extra elements. The tones are shifted to

$$f_{tone} = \frac{r}{2(N+K)} \cdot f_s \cdot m, \qquad m = 1, 2, 3...$$

(2.1)

where *r* is the greatest common divisor (GCD) of *N* and *N* + *K* [14],[15]. Specifically, the tones are shifted to the multiples of  $f_s/14$ , which is well outside of the signal band in this design. As shown in Fig. 2.11, a 2's complement number from the

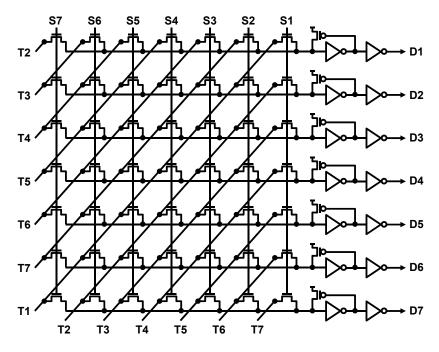

Figure 2.12: Rotating barrel shifter for DWA.

quantizer is converted to the unipolar integer number, by inverting its most significant bit (MSB) for the calculation of the pointer in DWA, where a 3b RCA with modulo 7 is used. The pointer output is decoded to control the rotating barrel shifter, as illustrated in Fig. 2.12. The DWA logic is also time-shared between both channels.

## 2.4. ANALOG STAGES

The analog stages were designed by Quingdong Meng.

# 2.4.1. Switched R-DAC

In the analog part of the system, the switched R-DAC is combined with a firstorder FIR filter, a second-order Rauch filter, and the headphone driver, as shown in

Figure 2.13: R-DAC with first-order FIR filter, second-order Rauch filter, and headphone driver  $(d_i = delayed b_i)$ .

Fig. 2.13. It needs only one opamp per channel to implement the D/A conversion, the first-order FIR and second-order IIR filtering, as well as the power amplification for the headphone. The opamp provides a low-frequency virtual short circuit at nodes A and B for the DAC output currents. An analog first-order FIR filter is also integrated into this stage, by duplicating the original DAC elements with a control signal delayed by one clock cycle. This introduces a zero at one-half the sampling frequency, and reduces the clock jitter sensitivity. The embedded second-order Rauch low-pass filter has a -3 dB cutoff frequency at 150 kHz, and its pole Q is 0.707. The values of all resistors and capacitors were optimized to achieve the minimum capacitor area for the given pole Q, cutoff frequency, and the targeted SNR.

In the switched R-DAC shown in Fig.2.13, all switches are connected either to the high reference ( $V_{DD}$ ) or to the low reference voltage (GND). This avoids the problem arising with floating switches. The value of  $R_1$  was chosen carefully to reduce the

size of the  $R_4$ , without sacrificing its matching accuracy. DWA technique is used to provide first-order noise shaping for the mismatch error among the DAC elements. Four extra resistors are added to make the output common-mode voltage equal to  $V_{DD}/2$  for maximum voltage swing.

The operation of the DAC is affected by the residual mismatch error after DWA, and by the clock jitter. Both theoretical analysis and simulations predict that these effects will be negligible in this device, due to the relatively high OSR (64), the conservative design of the DSM, and the noise shaping effect of the FIR filter. The measured results confirmed this prediction.

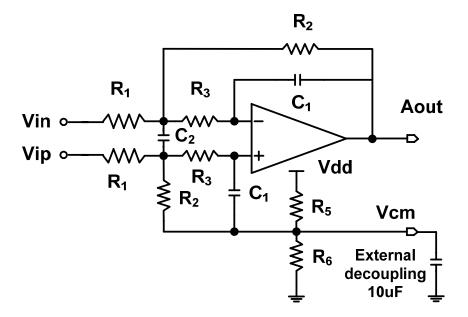

### 2.4.2. Analog low pass filter and headphone driver

As mentioned earlier, a second-order Rauch filter (Fig. 2.14) is used to suppress out-of-band noise. The transfer function of the filter (for the differential input and single-ended output) is

$$H(s) = \frac{-R_2 / R_1}{2R_2R_3C_1C_2s^2 + (R_2 + R_3 + R_2R_3 / R_1)s + 1}$$

(2.2)

The external bypass capacitor (10  $\mu$ F) at  $V_{cm}$  node provides a solid ac ground, even at very low frequencies. The DC gain of the filter is chosen as -6 dB, since the negative and positive inputs of this filter are both full-scale signals coming from the DAC output. Assuming  $R_3 = mR_2 = mR$ ,  $C_2 = nC_1 = nC$ , the -3 dB cutoff frequency and pole Q are

$$\omega_{-3dB} = \frac{1}{\sqrt{2mnRC}}$$

(2.3)

$$Q = \frac{\sqrt{2mn}}{1+1.5m} \tag{2.4}$$

Figure 2.14: Second-order Rauch low-pass filter.

TABLE 2.4: COMPONENTS VALUES FOR THE SECOND-ORDER RAUCH FILTER.

| R <sub>1</sub> | 30 kΩ |

|----------------|-------|

| $R_2$          | 15 kΩ |

| R <sub>3</sub> | 10 kΩ |

| $R_5, R_6$     | 45 kΩ |

| $C_1$          | 50 pF |

| C <sub>2</sub> | 75 pF |

Since the resistor value  $R_1$  is defined by the specifed fixed gain of the filter (0.5 in this design), it does not enter into the formulation (2.3) and (2.4) of the filter optimization. The filter -3 dB cutoff frequency is chosen to be 150 kHz, and Q is 0.707. The high cutoff frequency prevents the poorly defined -3 dB cutoff frequency from causing any gain drooping in audio band, and still provides sufficient suppression for the shaped high- frequency quantization noise. Note that the pole Q is well defined, since it only depends on the ratios  $R_2/R_1$  and  $C_2/C_1$  as indicated by (2.4). The input/output common-mode level is set by the resistor divider containing

*R5* and *R6*. Minimizing the total capacitor area is critical in reducing the whole DAC area due to the low -3 dB cutoff frequency at 150 kHz. For the circuit shown in Fig. 2.15, the total capacitor area is

$$C_{total} = (1+2n)C \tag{2.5}$$

Using (2.4),

$$C_{total} = (1+2n)C = (1 + \frac{Q^2(1+1.5m)^2}{m})C$$

(2.6)

Taking the derivative with respect to *m*, the minimum capacitor area is achieved with m = 2/3. Since Q = 0.707, n = 1.5 results. From the noise budget for the output-referred resistor noise, the resistor values can be calculated. Substituting them into (3) gives the capacitor values. Table 2.4 summarizes the nominal values for the components of the Rauch filter.

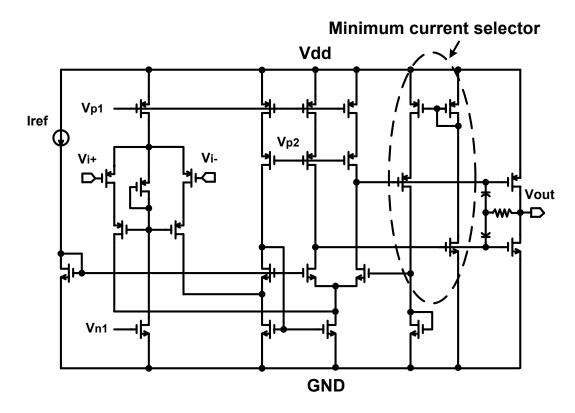

The amplifier in the filter provides the power amplification for driving the headphone as well. It must achieve a high DC gain, and also have the capability to drive a load of a 16  $\Omega$  resistor in parallel with a 300 pF capacitor, with sufficiently low thermal and flicker noises, all from a 0.8 V power supply voltage. Fig. 2.15 shows the schematic diagram of the amplifier. Since the filter has a differential input and single-ended output, it does not need a CMFB amplifier to stabilize the output common-mode level. The amplifier has two stages: a folded cascode input stage to provide a voltage gain, and a class-AB output stage to provide the headphone driving capability. For sub-1V operation, it is necessary to keep the output common-mode voltage at  $V_{DD}/2$ , to maximize the output signal swing. For the amplifier shown in Fig. 2.15, since the input and output common mode levels are the same, the minimum power supply voltage is

Figure 2.15: Opamp with class-AB output stage.

$$V_{DD MIN} = 2V_{th} + 4(V_{gs} - V_{th})$$

(2.7)

For the given process, the threshold voltage is around 300 mV, which means that the gate overdrive voltage can be as low as 50 mV. This makes a folded-cascode first stage possible, and avoids a cascaded multi-stage configuration with complicated nested Gm-C or Miller compensation needed to guarantee stability [16]. The output stage of the opamp [17] incorporates a minimum current selector in a feedback loop, which contains the split output transistors of the first stage. Since the output of the minimum current selector is equal to the bias current *Iref*, the bias current of the output transistors is determined by the current mirror ratio in the minimum current selector. The simulated voltage gain for this amplifier with a 16  $\Omega$  resistive and 300 pF capacitive load is 65 dB, and the UGBW is 7 MHz.

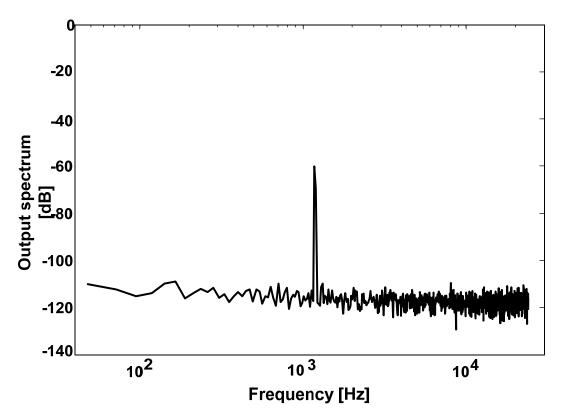

Figure 2.16: Measured output spectrum with a 1.17 kHz -60 dB sine-wave input at  $V_{DD} = 0.8$  V.

# 2.5. EXPERIMENTAL RESULTS

The DAC was fabricated in the Asahi Kasei Microsystem 2P3M  $0.35\mu m$  CMOS technology, and occupies  $1.6 \text{ mm} \times 0.9 \text{ mm}$  and  $1.6 \text{ mm} \times 1.3 \text{ mm}$  active die area for the digital and the analog chips, respectively. Both digital and analog chips are mounted on the same printed circuit board and the 7 DWA output signals from the digital chip are connected to the corresponding input ports of the analog chip. A Tektronix AWG520 (arbitrary waveform generator) was used to generate the 1b serial digital input and clock, and an Audio Precision audio analyzer was used for the measurements. Fig. 2.16 shows the measured output spectrum for a 1.17 kHz, -60 dB sine-wave input using a 0.8 V power supply. There are no idle tones present in the

Figure 2.17: Measured SNDR versus input signal power with a 1.17 kHz sine-wave input at  $V_{DD} = 0.8$  V.

Figure 2.18: Measured performance with supply voltage.

| Power supply voltage    | 0.8 V                                                                             |

|-------------------------|-----------------------------------------------------------------------------------|

| Signal bandwidth        | 24 kHz                                                                            |

| Clock frequency         | 3.072 MHz                                                                         |

| Oversampling ratio      | 64                                                                                |

| Load                    | Headphone (16 Ω II 300 pF)                                                        |

| Total power consumption | 2.6 mW                                                                            |

| Output range            | 0.45 V <sub>PP</sub> (single-ended)                                               |

| Peak SNDR               | 69 dB @ Vdd = 0.8 V<br>68 dB @ Vdd = 0.7 V                                        |

| Dynamic range           | 88 dB @ Vdd = 0.8 V<br>87 dB @ Vdd = 0.7 V                                        |

| Active die area         | Digital chip: 1.6 X 0.9 mm <sup>2</sup><br>Analog chip: 1.6 X 1.3 mm <sup>2</sup> |

| Technology              | 0.35µm CMOS                                                                       |

TABLE 2.5: PERFORMANCE SUMMARY.

quantization noise. The spurs caused by DWA rotation are also negligible (below - 109 dB). The SNDR performance versus input signal power from -85 dB to 0 dB (relative to 56% of the 0.8 V supply voltage) is shown in Fig. 2.17. The SNDR was measured over a 20 Hz to 24 kHz audio band. Without A-weighting, the prototype achieved a 69 dB peak SNDR and an 88 dB DR with a 0.8 V supply voltage. Using a 0.7 V supply, the peak SNDR and the DR were reduced to 68 dB and 87 dB, respectively. The peak SNDR is limited by the second harmonic distortion of the single-ended opamp for large input signal swings. The peak SNDR and DR both gradually improve for supply voltages increasing from 0.7 V to 1.5 V, as shown in Fig. 2.18. The chips consume 2.6 mW (0.1 mW for the digital chip, 2.5 mW for the analog chip,) with a 0.8 V supply. Table 2.5 summarizes the performance of the chip for 0.8 V supply. The die photographs are shown in Fig. 2.19. The performance of

Figure 2.19: Die micrographs.

| Refs                          | DR/SNDR<br>[dB] | Supply<br>[V] | Load   | Power<br>[mW] | Process<br>[µm CMOS] | Headphone<br>Driver |

|-------------------------------|-----------------|---------------|--------|---------------|----------------------|---------------------|

| [Adams98] <sup>[18]</sup>     | 113/100         | 5.0           | 1 kΩ   | 250           | 0.6                  | No                  |

| [Fujimori00] <sup>[2]</sup>   | 120/102         | 5.0           | 0.6 kΩ | 310           | 0.5                  | No                  |

| [Fujimori98] <sup>[3]</sup>   | 87/81           | 1.5           | 10 kΩ  | 4.1           | 0.6                  | No                  |

| [Annovazzi02] <sup>[13]</sup> | 98/86           | 3.3           | 15 kΩ  | 56            | 0.35                 | No                  |

| [Colonna05] <sup>[19]</sup>   | 97/88           | 3.3           | 40 kΩ  | 14.5          | 0.35                 | No                  |

| This work                     | 88/69           | 0.8           | 16 Ω   | 2.6           | 0.35                 | Yes                 |

TABLE 2.6: PERFORMANCE COMPARISON.

this device is compared with the other audio  $\Delta\Sigma$  DACs published earlier in Table 2.6.

# 2.6. SUMMARY

A 0.8 V third-order  $\Delta\Sigma$  DAC with headphone driver was presented. It incorporates a novel digital  $\Delta\Sigma$  modulator and interpolation filter. The analog circuitry requires only one opamp per channel, shared by the internal DAC, the FIR and the second-order Rauch low-pass filter, as well as by the headphone driver for 16  $\Omega$  resistor and 300 pF capacitor. The prototype ICs, implemented in a 0.35µm CMOS process, achieved 88 dB DR, while consuming 2.6 mW from a 0.8 V supply for the dual channels.

#### REFERENCES

- International Technology Roadmap for Semiconductors, Semiconductor Industry Association (2006). [Online]. Available: http://public.itrs.net/

- [2] I. Fujimori, A. Nogi, and T. Sugimoto, "A multibit delta-sigma audio DAC with 120 dB dynamic range," *IEEE J. Solid-State Circuits*, vol. 35, pp. 1066-1073, Aug. 2000.

- [3] I. Fujimori and T. Sugimoto, "A 1.5 V, 4.1 mW dual-channel audio deltasigma D/A converter," *IEEE J. Solid-State Circuits*, vol. 33, pp. 1879-1886, Dec. 1998.

- [4] A. Abo and P. Gray, "A 1.5-V, 10-bit, 14.3-MS/s CMOS pipeline analog-todigital converter," *IEEE J. Solid-State Circuits*, vol. 34, no. 5, pp. 599–606, May 1999.

- [5] G.-C. Ahn, D. Chang, M. Brown, N. Ozaki, H. Youra, K. Yamamura, K. Hamashita, K. Takasuka, G. C. Temes, and U. Moon, "A 0.6V 82dB delta-sigma audio ADC using switched-RC integrators," *IEEE J. Solid-State Circuits*, vol. 40, no. 12, pp. 2398-2407, Dec. 2005.

- [6] Q. Meng, K. Lee, T. Sugimoto, K. Hamashita, K. Takasuka, S. Takeuchi, U. Moon, G. C. Temes, "A 0.8V, 88dB dual-channel audio  $\Delta\Sigma$  DAC with headphone driver," *Symposium on VLSI Circuits*, pp. 53-54, Jun. 2006.

- [7] E. J. Foster, "Active low-pass filter design," *IEEE Trans. Audio*, vol. au-13, no. 5, pp. 104-111, Oct. 1965.

- [8] M. H. Nichols and L. Rauch, *Radio Telemetry*, New York: Wiley, 1956.

- [9] R. E. Crochiere and L. R. Rabiner, *Multirate Digital Signal Processing*.

Englewood Cliffs, NJ: Prentice Hall, 1983.

- [10] K. K. Parhi, VLSI Digital Signal Processing Systems: Design and Implementation. John Wiley & Sons, 1999.

- [11] P. P. Vaidyanathan and T. Q. Nguyen, "A "trick" for the design of FIR halfband filters," *IEEE Trans.Circuits Syst.*, vol. 34, No.3, pp. 297-300, Mar. 1987.

- [12] R. Schreier, G. C. Temes, Understanding Delta-Sigma Data Converters. John Wiley & Sons, 2005, ch. 9.

- [13] M. Annovazzi, V. Colonna, G. Gandolfi, F. Stefani, and A. Baschirotto, "A low-power 98-dB multibit audio DAC in a standard 3.3-V 0.35-m CMOS technology," *IEEE J. Solid-State Circuits*, vol. 37, no. 7, pp. 825–834, July 2002.

- [14] T.-H. Kuo, K.-D. Chen, and H.-R. Yeng, "A wideband CMOS sigma-delta modulator with incremental data weighted averaging," *IEEE J. Solid-State Circuits*, vol. 37, no. 1, pp. 11–17, Jan. 2002.

- [15] K.-D. Chen and T.-H. Kuo, "An improved technique for reducing baseband tones in sigma-delta modulators employing data weighted averaging algorithm without adding dither," *IEEE Trans. Circuits Syst. II*, vol. 46, no. 1, pp. 63–68, Jan. 1999.

- [16] F. You *et al.*, "Multistage amplifier topologies with nested Gm-C compensation," *IEEE J. Solid-State Circuits*, vol. 32, no. 12, pp. 2000–2011, Dec. 1997.

- [17] K. Langen and J. Huijsing, "Compact low-voltage power-efficient operational amplifier cells for VLSI," *IEEE J. Solid-State Circuits*, vol. 33, no. 10, pp. 1482-1496, Oct. 1998.

- [18] R. Adams, K. Q. Nguyen, and K. Sweetland, "A 113-dB SNR oversampling DAC with segmented noise-shaped scrambling," *IEEE J. Solid-State Circuits*, vol. 33, no. 12, pp. 1871-1878, Dec. 1998.

- [19] V. Colonna, M. Annovazzi, G. Boarin, G. Gandolfi, F. Stefani, and A. Baschirotto, "A 0.22-mm<sup>2</sup> 7.25-mW per-channel audio stereo-DAC with 97-dB DR and 39-dB SNR<sub>out</sub>," *IEEE J. Solid-State Circuits*, vol. 40, no. 7, pp. 1491-1498, July 2005.

#### Abstract

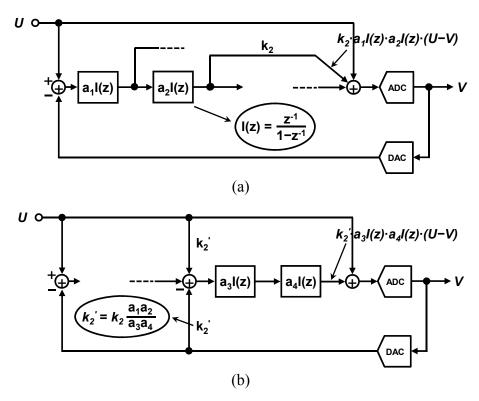

Two novel architectures are proposed for delta-sigma ADCs. The first one is the multi-cell structure, with common input and summed outputs. It allows flexible trade-off between resolution and power dissipation, and also improves the SQNR due to the uncorrelated nature of the quantization errors of the cells. The second structure couples quantization noise into the modulator loop, to enhance the noise shaping. The coupling may occur between the cells of a multi-cell structure (cross-coupling), or within a single loop (self-coupling). Noise coupling will raise the effective order of the noise transfer function, without introducing stability issues. While this feature is similar to the operation of the cascade (MASH) structure, the noise-coupled modulator does not rely on noise cancellation, and hence is less sensitive to analog circuit imperfections than MASH. Both extensive simulations and experimental results verify that the proposed schemes have significant advantages over existing ones under practical fabrication constraints.

# 3.1. INTRODUCTION

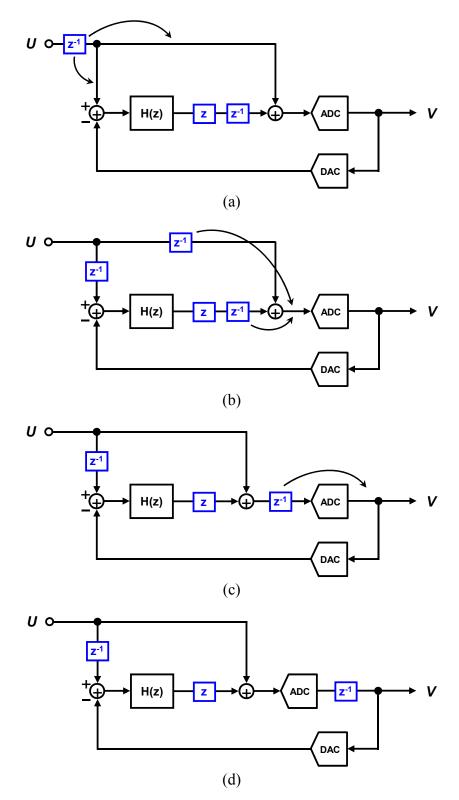

Delta-sigma ( $\Delta\Sigma$ ) analog-to-digital converters rely on oversampling and noise shaping to achieve very high accuracy even using inaccurate analog components [1]. The accuracy improves with higher oversampling ratio (OSR), but the OSR is limited by the bandwidth of the amplifiers used and by the permissible power dissipation. The performance can also be enhanced by using higher-order loop filters,

Figure 3.1: Two-stage cascaded (MASH) delta-sigma ADC.

but this may lead to instability. Finally, higher resolution may also be attained by embedding a multibit internal quantizer in the loop. However, the complexity of the quantizer and the required dynamic matching logic increases exponentially with the number of bits used in the quantizer, so this approach is also limited in effectiveness. A different structure, which combines noise shaping with noise cancellation, is used in the cascade or MASH modulator as illustrated in Fig. 3.1. Under ideal conditions, a MASH structure provides a noise transfer function (NTF) equal to the product of the NTFs of several modulator loops coupled together. Thus, for example, fourth-order noise shaping may be achieved by coupling two second-order loops. Since second-order loops are inherently stable, while fourth-order ones are not, MASH allows high-order noise filtering without stability problems.

A shortcoming of the MASH ADC is that it relies on the accurate matching of one or more analog NTFs to digital ones to achieve the cancellation of unfiltered or poorly filtered noise from the input stage(s). For high-accuracy and high-OSR ADCs

Figure 3.2: Multi-cell delta-sigma ADC.

this puts difficult constraints on the analog circuitry in these stages. While it is possible to overcome this problem using adaptive tuning of the digital filters [2], this requires additional digital logic.