# AN ABSTRACT OF THE DISSERTATION OF

José Luis Ceballos for the degree of Doctor of Philosophy in Electrical and Computer Engineering presented on October 11, 2005.

Title: Enhanced-Accuracy Oversampled Data Converters.

Abstract approved:

Gábor C. Temes

Digital-to-analog converters (DACs) suffer from static and dynamic nonlinearity problems, which degrade their accuracy and performance. Mismatch errors in the analog components restrict the maximum achievable linearity.

This thesis presents various techniques for correcting these errors. It describes a correction process for the nonlinear behavior of DACs, on three different levels: architectural design, circuit design, and layout design.

The main results achieved are listed below:

- Novel topologies using stochastic approaches to linearize multibit converters are presented.

- A new method is introduced for avoiding the use of multibit DACs in the main loop of multipath DS analog-to-digital converters (ADCs), which, combined with a novel noise leakage compensation technique, allows the use of low quality inner DACs.

- A novel correction algorithm is proposed, which is based on the acquisition of the individual DAC errors by means of correlation procedures. The extracted values are used for correction purposes. The technique is capable of background operation.

- Different circuits are proposed to improve the performance of current-steering DACs. Also, novel layout techniques are shown for reducing the spatial variations of the unit sources. Some of the presented techniques were combined in a prototype chip, designed and fabricated in a 0.35µm CMOS process. Simulation and preliminary measurement results show that they are effective.

<sup>©</sup>Copyright by José Luis Ceballos October 11, 2005 All Rights Reserved Enhanced-Accuracy Oversampled Data Converters by José Luis Ceballos

A DISSERTATION

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented October 11, 2005 Commencement June 2006 Doctor of Philosophy dissertation of José Luis Ceballos presented on October 11, 2005.

APPROVED:

Major Professor, representing Electrical and Computer Engineering

Director of the School of Electrical Engineering and Computer Science

Dean of Graduate School

I understand that my dissertation will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my dissertation to any reader upon request.

José Luis Ceballos, Author

#### ACKNOWLEDGMENTS

First of all, I would like to express my immense gratitude to my advisor, Dr. Gábor Temes, who not only provided me with the perfect environment to develop my inquietudes, but also with real friendship, help and support in almost every aspect of my technical and personal matters. I am really proud, and the reader must believe me, that it is a huge honor to me to have worked with him and to consider him as a close friend. Thank you very much *"Super"*...

I am also grateful to my close lab-friends Jose "*Potugues-de-Portugal*" Silva, Pavan "*Kumi*" Hanumolu, and Matt "*Professor M*." Brown, for giving me so many good moments during these years we have been together. In particular, I have to thank *Josecito* for his help during different stages of our (mine and my wife) life here in Corvallis, especially for being with us not only in the good times, but also during the bad ones...Obrigado. Thanks to *Pavancito* for sharing afternoons of knowledge, coffee and ideas, and Matt, What can I say about Matt and his "*thermometered barbecues*"? Thank you all!

I want to say thanks also to my friends Patrick Birrer and Husni El-Habal for the very good moments we enjoyed, and for our "culinary" meetings. My friends Pat and Ray Schmaltz occupy also a special place in this acknowledgement list. Most sincere thanks to you. Thanks to Charlie and Meredith Myers for sharing with us their delightful friendship. I'm also grateful to my dear friend Manfred Dietrich, for always helping me with his good humor, especially during "gray days".

For their important contributions to this research, I wish to thank Dr. Xuesheng Wang, and Dr. Jesper Steensgaard.

I also want to acknowledge all my lab and class mates, with whom I have shared and enjoyed these years of hard work: in no particular order, I would like to acknowledge Gilcho "Jilchito" Ahn, Ting Wu, Peter Kurahashi, Mingyu Kim, Merrick Brownlee, Qingdong Meng, Volodymyr "Vova" Kratyuk, Melinda Valencia, Kerem Ok, Anurag Pulincherry, Jipeng Li, Dong-Young Chang, Kye-Hyung "Mr." Lee, Dr. Yunjae Kook, Ranganathan "Ranga" Desikachari, Kiseok "Kisokito" Yoo, Yoshio "Nishida-San" Nishida, and Zhneyong "Gordon" Zhang.

I am also grateful to Ibi Temes for her kindness, and for many especially nice visits to the Temes' house. I felt like being at home...

This work was mainly possible thanks to the generosity of the Center for the Design of Analog and Digital Integrated Circuits (CDADIC), and Analog Devices Inc. (ADI). Special thanks to Paul Ferguson and Dennis Dempsey for their help during the design reviews and for their valuable feedback on many circuit design issues.

I would also like to thank Prof. Luca Lucchese, Prof. Mario Magaña, Prof. Un-Ku Moon, and Prof. Ron Guenther for serving in my graduate committee. Special thanks to Mario, for his honest friendship.

I wish to thank the EECS staff for their highly qualified support and help: Sarah O'Leary, Ferne Simendinger, Morgan Garrison, Clara Knutson, Brian Lindsey, Nancy Brown, Andy Lyons, and Tina Batten.

Of course and for sure I have forgotten someone (it is not unusual on my), but even though I can have a mediocre memory for names, fortunately I have a good long-term memory for friends.... Sooner or later I will see many of you, and we will have fun again.

Last but not least, I am deeply grateful to all my family (*here and there, now and then...*) for believing on me when I did not, specially my wife, Marcela, for her unconditional love, for taking care of me, and for her constant help (and also for supporting my bad mood...). Mis más especiales y sinceras gracias son para vos, *Capuchin*!

José Luis Ceballos Corvallis, Oregon, Oct. 2005

# TABLE OF CONTENTS

1

# Page

| INTRODUCT     | TION        | <br>••••• | 1 |

|---------------|-------------|-----------|---|

| 1.1 Motivatio | on          | <br>      | 1 |

| 1.2 Main Cor  | ntributions | <br>      | 2 |

| 1.3 Thesis Or | ganization  | <br>      | 2 |

| 2 | DIGITAL-TO-ANALOG CONVERTERS AND THEIR LIMITATIONS                                  | 4 |

|---|-------------------------------------------------------------------------------------|---|

|   | 2.1 Current-steering DACs                                                           | 4 |

|   | 2.2 Oversampled and Nyquist-Rate DACs                                               | 6 |

|   | 2.3 DAC Metrics and Known Solutions for the Linearization of Multibit<br>Converters | 0 |

|   |                                                                                     | 0 |

| 3 | PROPOSED SOLUTIONS                                                                                    | 9                   |

|---|-------------------------------------------------------------------------------------------------------|---------------------|

|   | 3.1 Algorithms and Architectures                                                                      | 9                   |

|   | 3.1.3 Extending the Concept                                                                           | 9<br>11<br>12<br>14 |

|   | 3.2 Stochastic Data Converters                                                                        | 14                  |

|   | 3.2.2 Sigma-Delta Modulators Using the SQ                                                             | 15<br>18<br>23      |

|   | 3.3 Digital Correction of DACs – Main Idea                                                            | 23                  |

|   | 3.3.2 Other Topologies                                                                                | 24<br>28<br>29      |

|   | 3.4 Layout Considerations                                                                             | 31                  |

|   | 3.4.1 Contour Around a Line                                                                           | 31                  |

|   | 3.4.2 Matching Considerations                                                                         | 33                  |

|   | <ul><li>3.4.2.1 Integral Non Linearity (INL) vs. Matching</li><li>3.4.2.2 Matching vs. Area</li></ul> |                     |

#### TABLE OF CONTENTS (Continued)

# 3.5 Circuit Design Point of View..... 38 3.5.1 Latches and Crossover..... 38 DIGITALLY CORRECTED DAC...... 42 4 4.6 Nonideal Effects..... 59 4.6.1 Finite Output Conductance..... 59 4.6.2 Comparator Noise..... 61 5 5.1 ANALOG SECTION..... 67 5.1.1 Comparator Design..... 67 5.1.2 Main DAC..... 70 5.1.3 Auxiliary DAC..... 72 5.2.2 Encoder and Memory..... 75 6

| TEST SETUP AND EXPERIMENTAL MEASUREMENTS | 77 |

|------------------------------------------|----|

| 6.1 Test Board Design                    | 77 |

| 6.2 Experimental Results                 | 78 |

### TABLE OF CONTENTS (Continued)

# Page

| 7 | CONCLUSIONS     | 84 |

|---|-----------------|----|

|   | 7.1 Conclusions | 84 |

|   | 7.2 Future Work | 85 |

|   |                 |    |

| 8 | BIBLIOGRAPHY    | 86 |

### LIST OF FIGURES

| Figure                                                                                                                                                            |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

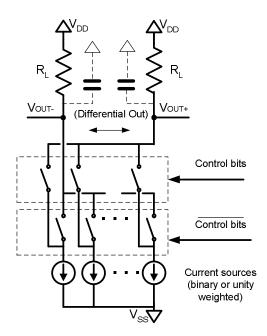

| 2.1 Schematic of a current-steering DAC                                                                                                                           | 5  |

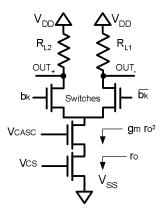

| 2.2 Schematic of the current source for current-steering DACs                                                                                                     | 6  |

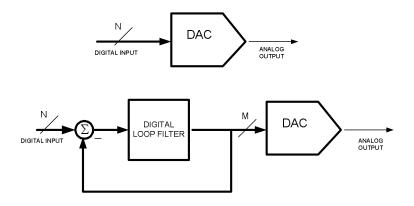

| 2.3 Nyquist and oversampled delta-sigma (D-S) DAC systems                                                                                                         | 7  |

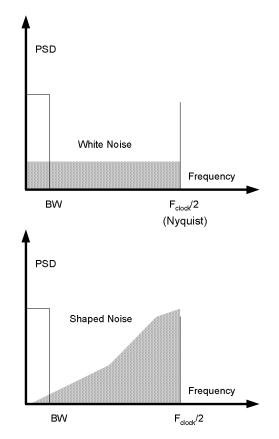

| 2.4 Power spectrum densities of the quantization noise for the Nyquist-rate<br>and for the D-S converters                                                         | 7  |

| 3.1 Schematic of a feedforward truncation cancellation                                                                                                            | 10 |

| 3.2 Requantization delta-sigma ADC; b) Linear model                                                                                                               | 11 |

| 3.3 Low distortion topology                                                                                                                                       | 13 |

| 3.4 The embedded system                                                                                                                                           | 13 |

| 3.5 Typical 32768 point FFT                                                                                                                                       | 14 |

| 3.6 Time-Spatial averaging quantizer                                                                                                                              | 16 |

| 3.7 Stochastic Quantizer embedded in a delta-sigma ADC loop                                                                                                       | 19 |

| 3.8 Delta sigma ADC using spatial averaging with embedded noise shaping                                                                                           | 20 |

| 3.9 Delta sigma DAC using spatial averaging with embedded noise shaping                                                                                           | 22 |

| 3.10 Digital to Analog system                                                                                                                                     | 24 |

| 3.11 Schematic representation of the whole system                                                                                                                 | 25 |

| 3.12 Flow Diagram that represents the functionality of the system                                                                                                 | 27 |

| 3.13 Another possible architecture, suitable for a totally analog implementation                                                                                  | 28 |

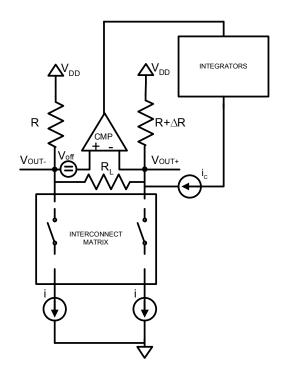

| 3.14 Mixed-mode implementation                                                                                                                                    | 30 |

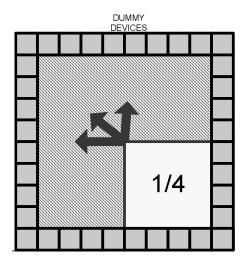

| 3.15 Possible layout that equalizes the quadratic errors in a 2-bit DAC                                                                                           | 32 |

| 3.16 Simplified layout                                                                                                                                            | 33 |

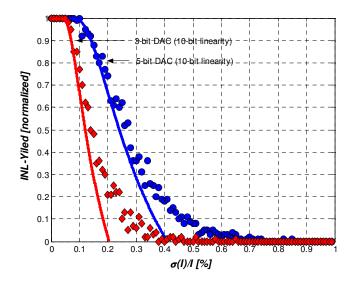

| 3.17 <i>INL-Yield</i> as a function of the normalized deviation of the unit current sources of the DAC (3-bit and 5-bit cases)                                    | 34 |

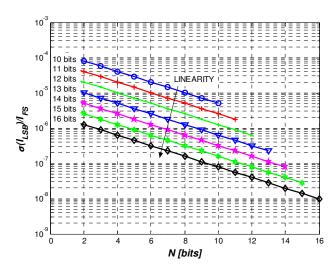

| 3.18 Unit current sources deviation normalized to the full scale current for different linearity, as function of the number of bits, for <i>INL_Yield</i> = 99.7% | 35 |

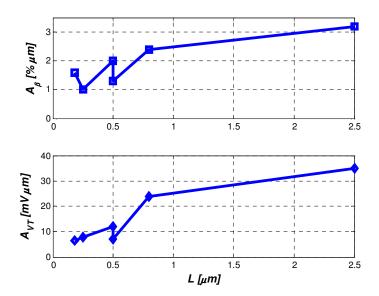

| 3.19 Matching parameters as a function of the technology length                                                                                                   | 36 |

# LIST OF FIGURES (Continued)

| Figure                                                                                                                     | <u>Page</u> |

|----------------------------------------------------------------------------------------------------------------------------|-------------|

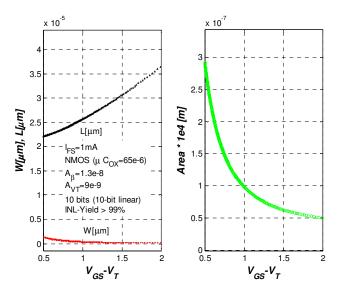

| 3.20 Length (L), Width (W) and Area (scaled by 10e4) for the typical parameters of a 0.5µ technology)                      | 36          |

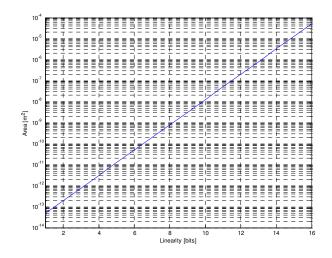

| 3.21 Area (Active) as a function of the linearity for a typical 0.5µm process                                              | 37          |

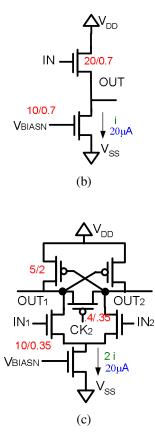

| 3.22 Schematic of the modified active cascade unit current cell                                                            | 38          |

| 3.23 Transient simulation of the unit current source                                                                       | 39          |

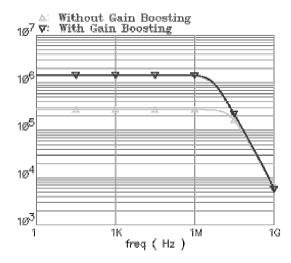

| 3.24 Increase of the output impedance using gain boosting                                                                  | 39          |

| 3.25 Unit Current sources different crossing points                                                                        | 40          |

| 3.26 Proposed Latch #1                                                                                                     | 41          |

| 4.1 Fully differential architecture. 2-bit example                                                                         | 43          |

| 4.2 Schematic of a 1-bit DAC with nonidealities                                                                            | 44          |

| 4.3 Block diagram for offset analysis                                                                                      | 45          |

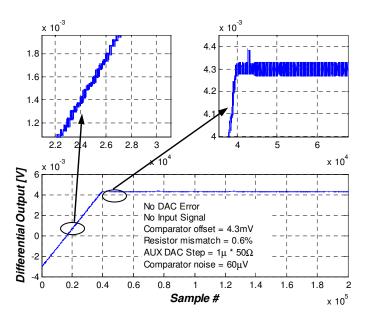

| 4.4 Simulation results. Details: Adaptation noise & steady-state noise                                                     | 47          |

| 4.5 Equivalent linear model of the correction loop for the i-th error                                                      | 48          |

| 4.6 Schematic picture for the input of the MUX                                                                             | 49          |

| 4.7 Simulated results for a 2-bit generic system                                                                           | 50          |

| 4.8 Schematic of the system under locking condition                                                                        | 50          |

| 4.9 CMP <sub>in</sub> is the input to the comparator in the middle code. 2-bit system                                      | 52          |

| 4. 10 Possibilities of connection between the different entries (TABLE 4-I-A)                                              | 54          |

| 4.11 Putting together Table 4-1 A & B                                                                                      | 54          |

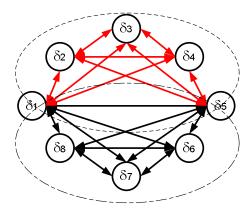

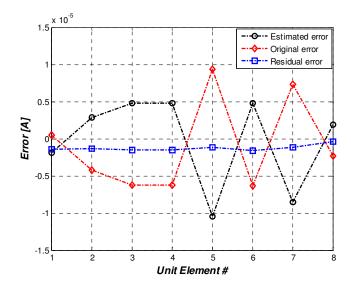

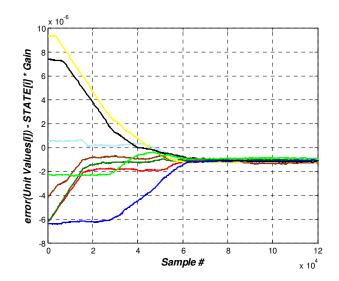

| 4.12 Errors in the 3-bit simulated system                                                                                  | 56          |

| 4.13 Convergence to steady state of the eight individual registers                                                         | 56          |

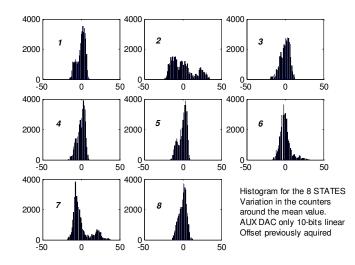

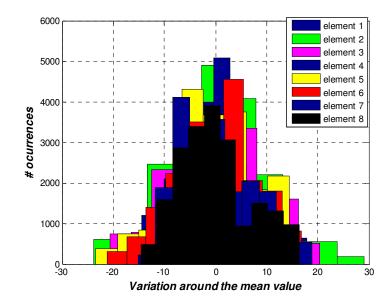

| 4.14 Histograms of counters output for the 8 unit elements around their mean value after convergence. New switching scheme | 57          |

| 4.15 Histograms of counters output for the 8 unit elements around their mean value after convergence. Fully randomization  | 57          |

### D

# LIST OF FIGURES (Continued)

| Figure                                                                         | <u>Page</u> |

|--------------------------------------------------------------------------------|-------------|

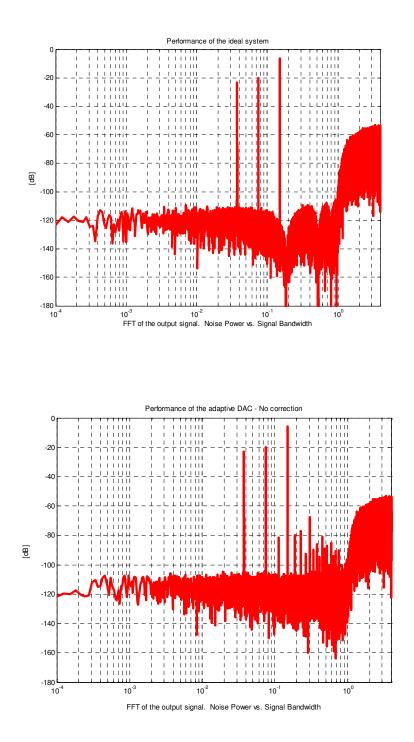

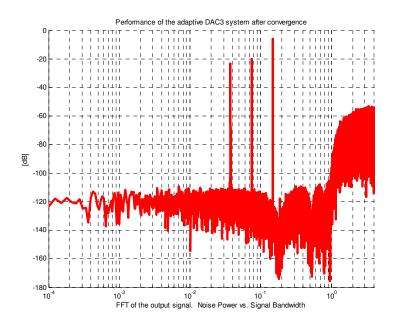

| 4.16 Simulated output spectra                                                  | 58          |

| 4.17 Simplified circuit of the DAC                                             | . 60        |

| 4.18 The comparator noise acts as a dithering signal                           | . 61        |

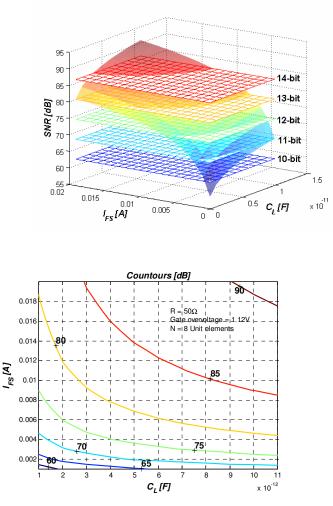

| 4.19 SNR as a function of the LSB current.                                     | . 63        |

| 4.20 SNR as a function of the BW and I <sub>FS</sub> .                         | . 63        |

| 5.1 Implemented system.                                                        | . 65        |

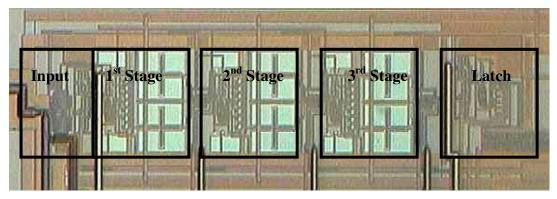

| 5.2 Schematic of the comparator                                                | . 67        |

| 5.3 a) Gain enhancement analog amplifier; b) Buffers; c) Regenerative latch    | . 68        |

| 5.4 Comparator micrograph                                                      | . 70        |

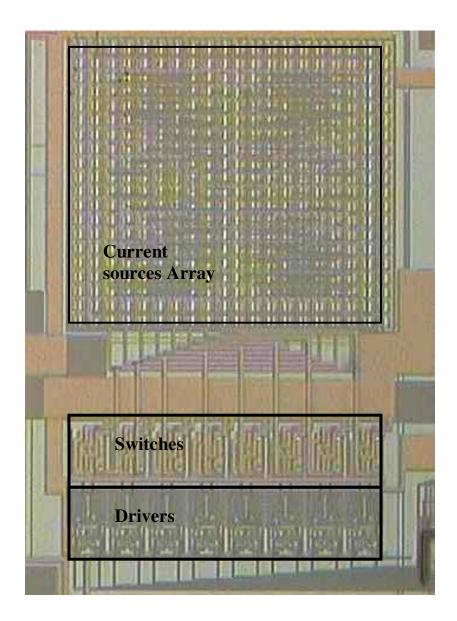

| 5.5 Main DAC micrograph                                                        | . 71        |

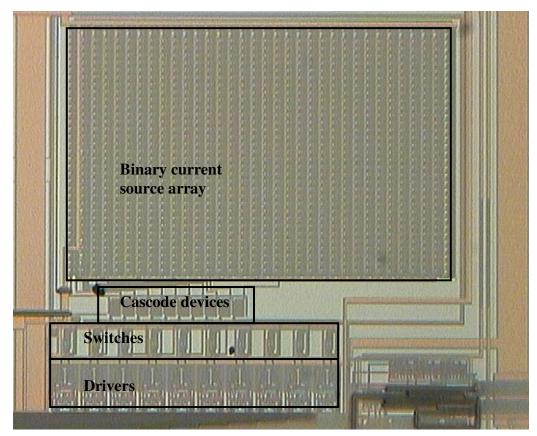

| 5.6 Aux-DAC micrograph                                                         | 73          |

| 5.7 Layout of a small (W/L) transistor                                         | . 73        |

| 5.8 Chip Micrograph                                                            | . 76        |

| 6.1 Board design                                                               | . 77        |

| 6.2 Test setup                                                                 | . 78        |

| 6.3 Low speed ramp                                                             | . 78        |

| 6.4 Analog differential output for low speed, -2dBFS sine signal               | 79          |

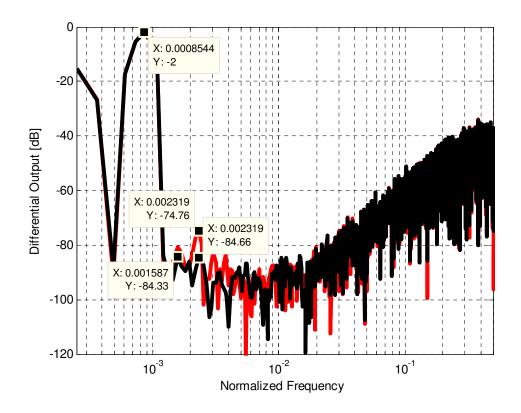

| 6.5 Output spectrum2dB <sub>FS</sub> input. OSR>500. Clock frequency = 100kHz  | . 80        |

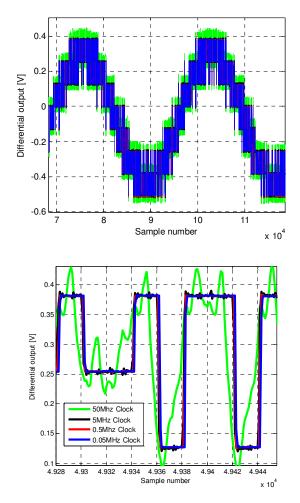

| 6.6 OSR constant. Clock frequency is: 50 kHz, 500 kHz, 5 MHz and 50 MHz        | . 81        |

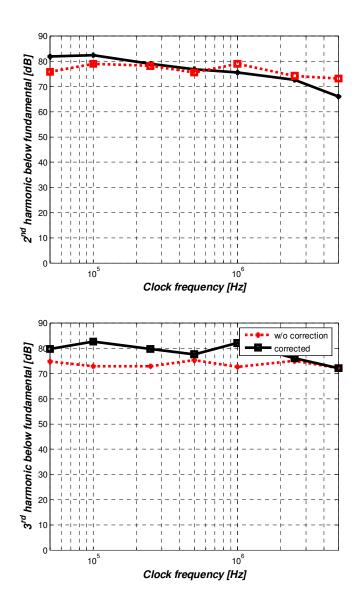

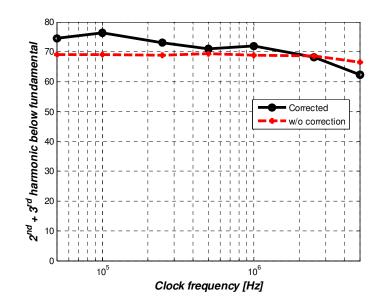

| 6.7 2 <sup>nd</sup> and 3 <sup>rd</sup> harmonic below the fundamental (in dB) | 82          |

| 6.8 THD Estimation                                                             | . 83        |

#### LIST OF TABLES

| Table                                | Page |

|--------------------------------------|------|

| 4.1 3-bit system switching sequences | . 53 |

| 5.1 Encoder                          | . 75 |

To my wife, Marcela.

# ENHANCED-ACCURACY OVERSAMPLED DATA CONVERTERS

# **CHAPTER 1. INTRODUCTION**

#### **1.1 Motivation**

Multibit delta-sigma (D-S) digital-to-analog converters (DACs) are widely used in audio, wireless and wireline communication systems. They contain a digital interpolation filter, a noise-shaping loop which reduces the word length of the digital signal, a low-resolution internal DAC, and an analog smoothing filter. Such converters are capable of very high accuracy and linearity, up to 20 bits or even higher.

A major limitation of such converters is the achievable static linearity of the embedded DAC. For D-S DACs with narrow-band signals, the effective DAC linearity can be vastly improved by using a high oversampling ratio (OSR) combined with a dynamic element matching (DEM) method [25-27, 29]. However, for DACs processing wideband signals, such as those occurring in communication applications, the OSR is restricted to low values by the limited speed capability of the analog circuitry used. In this situation, DEM does not provide enough accuracy improvement for a high (say, 15 or more ENOB) linearity for the overall converter.

There are different techniques to overcome such limitations in order to obtain high resolution/accuracy converters, even in the unavoidable presence of imperfect -and maybe low quality- analog components. Two possible paths to follow are:

- Novel multibit techniques based on the use of 1-bit DAC converters (inherently linear devices).

- 2) Correct digitally -mainly for robustness reasons- the inaccurate multibit DACs.

This thesis deals with both research directions; a possible architecture for the second set of ideas was implemented in silicon, proving its potential as a linearization technique. The other ideas are presented at the simulation level, including realistic nonideal models.

#### 1.2 Contributions

As mentioned, different paths have been followed, at the theoretical and at the practical levels. The work that emerged form this investigation was proposed and published, being shortly summarized as follows:

- 1) Requantization in multibit delta-sigma ADCs: In this research, a novel topology was introduced [2-3], having shown the potential of protection against DAC mismatches.

- 2) Stochastic data converters: Firstly presented in [3], the concept was extended in [6]. This research focuses in the redundant use (spatial and temporal averaging) of low complexity components to obtain multibit highly linear DACs and ADCs.

- 3) Digital correction of DACs: Research published in [1] and [4]. This technique is based on the adaptive correction of the DAC, after the estimation of the DAC unit element errors has been obtained by means of correlation processes. It was implemented in silicon, following a modified error extraction procedure, here also proposed and described in detail.

- 4) Novel layout techniques, current cell topologies, and drivers for current-steering DACs [5]

The research also presented modifications to previously presented analysis of matching in the area of current mode DACs.

The topologies proposed have extra potential when used in harsh environments (e.g., space and radioactive applications).

The contributions of this work can be mainly divided into two categories:

- Combination of several of the previous techniques to implement a digitally corrected DAC, with low sensitivity to unavoidable analog components imperfections.

- 2) Proposal of new solutions and directions in the field, as the stochastic approach.

#### 1.3 Thesis Organization

Following this introduction, Chapter 2 provides some insight into the DAC nonlinear problems, and defines some metrics used in the characterization of such converters.

Chapter 3 presents different proposed solutions, form the algorithmic, the geometric and from the circuital point of views. Several subsections will introduce the new ideas in each one of the previous items. Chapter 4 deals with the analysis of the digitally corrected DAC, proposing also a new switching technique for the unit element errors estimation. Nonideal component effects together with extra topologies will also be addressed here.

Chapter 5 shows different aspects of the analog and the digital implementation in detail.

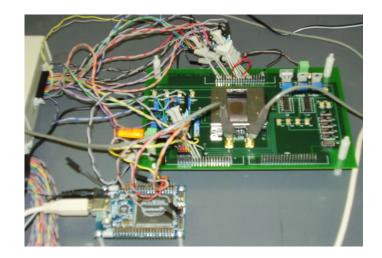

Chapter 6 describes the test setup and the laboratory experimental results of the fabricated prototype.

Finally, Chapter 7 concludes this thesis, summarizes the contributions of this work, and describes directions for future research paths to follow.

# CHAPTER 2. DIGITAL-TO-ANALOG CONVERTERS AND THEIR LIMITATIONS

Digital-to-analog converters are signal processing blocks that convert digital representations (time-discrete and amplitude-quantized) into analog quantities (time and amplitude continuous signals). To do so, different types of converters have been designed and used during many years [8], using different devices and schemes depending on the specific applications. This thesis deals with current-steering DACs, a topology that was selected as a test vehicle for a novel correction algorithm, even though the concepts that will be here presented can also be applied to other classes of converters.

#### 2.1 Current-steering DACs

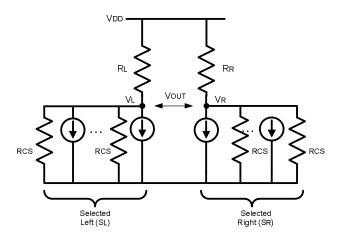

A fully differential current-steering DAC is schematically depicted in Fig. 2.1. In it, each current source can be switched either to one or to the other resistive load, in accordance with the incoming digital control bits. The differential voltage output is measured across the load resistors. A single-ended version can be easily visualized from the scheme, using only one output branch. This topology has the advantages of a high speed of operation and a relative simplicity of construction.

Depending on the weights of the current sources, the converter can be:

- 1) Binary coded: currents scaled in ascending powers of two.

- 2) Thermometer: each current source will have the same weight, making the output dependent on how many unit elements are connected (linear relationship).

- 3) Segmented: Combination of the two previous approaches. One of the unit elements of the thermometer decoded MSBs (most significant bits) array will be the parent current source of a binary weighted converter that will provide the LSBs (least significant bits).

Figure 2.1: Schematic of a current-steering DAC

Each configuration presents advantages and disadvantages regarding linearity issues and complexity [11].

In this thesis the thermometer and the binary topologies will be implemented at the circuit level. Having all the currents the same value, the thermometer encoded converter will be useful at the time of the individual error detection and estimation; the correction of these errors will be performed using a binary weighted auxiliary current-steering DAC for simplicity of design.

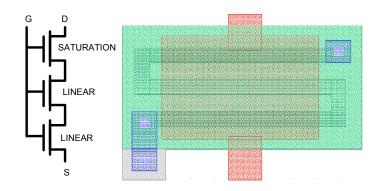

A simplified schematic of a possible unit current source is depicted in Fig. 2.2. The main current source can have a cascode device to increase its output resistance, reducing the associated nonlinear effects [22]. The switches can work as saturated devices, being only intended to convey the current to one of the loads; this condition also increases the output resistance. The control signals can have a different power supply to reduce dynamic effects. More about of the fine points of the converter and the cell will be presented throughout the following chapters of this work.

Figure 2.2: Schematic of the current source for current-steering DACs. The cascode device increases the output resistance. The switches are controlled by complementary signals with dedicated crossover point.

#### 2.2 Oversampled and Nyquist Converters.

An important categorization is based on the tradeoff between speed and accuracy. Considering that, two main classes of converters can be devised:

- 1) Nyquist rate converters: Operating at the maximum frequency (half of the clock frequency, or Nyquist frequency)

- 2) Oversampled converters: Reduced bandwidth together with moving the quantization noise towards high frequencies enhances the final achieved accuracy.

The generalized ideas are depicted schematically in Fig. 2.3. In the Nyquist multibit DAC, all N input bits are processed. It is the fastest one. In the delta-sigma modulating system, a truncation takes place from the N bits at the input to M bits at the output; hence, the number of processed bits is less, but at a higher speed. Because the truncation is inside the feedback loop and is preceded by the low pass loop filter, the net effect is moving the noise power to the high-frequency part of the spectrum. In the band of interests (at low frequency generally), the quantization noise will be greatly reduced. The tradeoff between the two converters is clear: *speed vs. accuracy.* Figure 2.4 schematically depicts the power spectrum density of the quantization (truncation) noise for both cases.

As mentioned, the number of bits processed in the delta-sigma case is less than in the Nyquist one; this can be translated as reduced complexity. Moreover, if the DAC is reduced to its minimum expression (1-bit), no nonlinear DAC errors or inaccuracies will exist (unfortunately other effects will appear, such as stability issues, idle tones, etc. [9-10]). For those reasons, a 3-bits delta-sigma structure has been selected as the test vehicle in the digitally corrected DAC prototype.

Figure 2.3: Nyquist and Oversampled delta-sigma (D-S) DAC systems.

Figure 2.4: Power spectrum densities of the quantization noise for the Nyquist rate and for the D-S converters.

# 2.3 DAC Metrics and Known Solutions for Linearization of Multibit DACs

The most commonly used parameters/errors that characterize DACs are [8]:

- 1) Offset: Shift of the output characteristic.

- 2) Gain error: The slope is different than predicted.

- 3) INL (Integral non linear error): The overall variation from the ideal linear characteristic.

- 4) *DNL (Differential non linear error):* The difference in each step from its ideal (1 LSB) value.

- 5) *Settling time:* Time required to settle in the 0.5 LSB band (the sampling rate can be roughly calculated as 1/settling time).

- 6) Aperture Jitter error: The error that appears due to sampling-time uncertainty.

A DAC is called monotonic if its analog output always grows with continuously increasing digital input codes. A converter is guaranteed to be monotonic if DNL<1 LSB and INL<0.5 LSB. In the following chapters, an analysis that relates the INL error and the production yield will be presented, a modification of the work presented in [14].

There exist different techniques to linearize the DAC characteristics, being the most important:

- 1) Correlation and calibration (digital domain) [31].

- 2) Data Weighted Averaging [28-29].

- 3) Analog calibration [24].

Extra references: [17-20].

This dissertation will present different solutions to the linearization problem.

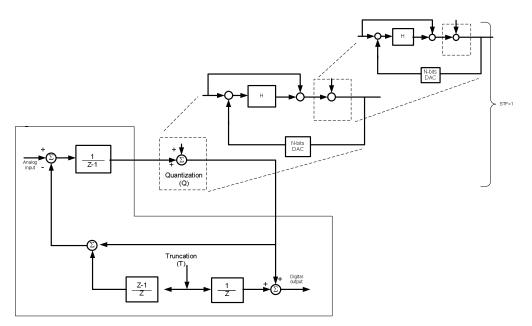

#### 3.1 Algorithms and Architectures

In this section different architectures will be presented, addressing the main problem of DACs nonlinear behavior in Nyquist and in oversampled converters. First of all, the concept of requantization in delta-sigma ADCs will be introduced, where the use of a 1-bit DAC combined with an internal multibit ADC allows high linearity and, at the same time, increases the converter's stability. Next, a novel design topology will introduce the so-called stochastic data converters. This architecture is mainly based on the fact that many similar and imprecise unit elements can be combined to perform a collective improved function. Finally, the digital correction of unit errors in nonlinear DACs will be introduced. It is based on the estimation of the individual elements errors, correcting their effect using a mixed-mode compensation circuitry. This last design procedure was studied in detail, and a silicon IC implemented; the next chapters will deal in detail with the fine points of this topology.

#### 3.1.1 Requantization in Delta-Sigma ADCs

The first question to be asked is: What is requantization? The answer is: it is the use of another delta-sigma loop (this time digital, and embedded into the main loop), trying to convert the multibit digital output of the main delta-sigma ADC into a 1-bit representation. The next question should be: Why do so? Again, the answer is relatively easy to be understood. As it was pointed out previously, a 1-bit (2 levels) DAC is an inherently linear system; if the weights of the two levels differ, the net nonideal effects are offset and gain variation, none of them being of concern in delta-sigma systems.

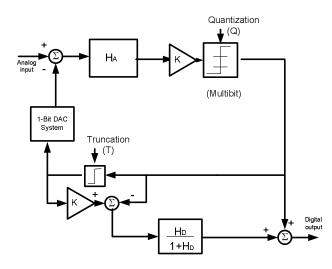

The new problem is that, in order to convert the output from a multibit representation into a 1-bit one, some truncation (T) must be introduced somewhere; it is not important which kind of error is produced (i.e. shaped or unshaped noise), the important point is where it is introduced. Unfortunately, any error associated with the feedback DACs in delta-sigma ADCs will appear at the output indistinguishable from the real modulator's input. Is there any known solution? The answer again is yes. Previously reported work [34-35] has shown that the truncation error can be compensated in the digital domain, if a modified copy of that error is combined with the output of the feedback loop trying to get a first order cancellation of the introduced error in a new (final) output. A generalized structure of this kind of systems is depicted schematically in Fig. 3.1.

Figure 3.1: Schematic of a feedforward truncation cancellation.

For a conventional first order system, the internal filters are given by:

$$H_A = \frac{1}{\left(z - 1\right)} \equiv H_D \tag{3.1}$$

$$\frac{H_D}{1+H_D} = \frac{1}{z} \tag{3.2}$$

The constant *K* symbolizes the gain variation in the analog filter. It should be pointed out that, because of the 1-bit DAC, the characteristic equation of the loop is always given by  $1+H_A$ , independently of the gain *K*.

After simple mathematical manipulations, using K=1 for the sake of simplicity without loss of generality, it can be easily shown that the output of the linearized system is given by:

$$OUT = IN \frac{H_A}{1 + H_A} + Q \frac{1}{1 + H_A} - T \frac{H_A}{1 + H_A} + T \frac{H_D}{1 + H_D}$$

(3.3)

# 3.1.2 Proposed System

The main issue with the previous architecture lies in the fact that the transfer function seen by the truncation toward the output in both worlds –analog and digital- is not the same, causing part of the truncation noise to appear at the output, an effect known as noise leakage [11]. Again, is there any solution to this problem? Yes. The solution herein proposed can be visualized if one asks the following question: Is there any way in which the difference between the analog and digital transfer functions reflects the truncation noise leakage at the output but in a noise-shaped way? The system that performs such a function is schematically represented in Fig. 3.2., together with its linearized model.

Figure 3.2: a) Requantization delta-sigma ADC; b) Linear model

At this point requantization is introduced. Now, what is appearing at the output of the DAC is a high-pass filtered (shaped) truncation error. Using a feedforward approach similar to that used before for cancellation, the noise leakage will be shaped with a first order noise transfer function (NTF) in the final output, hence minimizing the analog NTF noindealities. Under the previous assumptions, the general linear input-output relationship can be shown to be:

$$OUT = IN \frac{H_A}{(1+H_A)} + \frac{Q}{(1+H_A)} + \frac{T}{(1+H_D)} \left(\frac{H_D}{1+H_D} - \frac{H_A}{1+H_A}\right)$$

(3.4)

This in the ideal case reduces to:

$$OUT = IN\left(\frac{1}{z}\right) + Q\left(\frac{z-1}{z}\right)$$

(3.5)

From equation (3.4), the previous comments about shaping for the truncation noise (T) can be easily inferred.

It must be noted that the truncation error (T) appears at the output of the 1-bit DAC (the summing node of the main feedback loop) multiplied by a second order function, and following the 1-bit ADC *Lee's* criterion [10] this point of the circuit is the problematic one. The dithering noise (D) is used to uniformly distribute the use of the quantizer levels and to diminish idle tones. It can be previously shaped in order to move its power spectral density toward out-of-band frequencies.

#### 3.1.3 Extending the Concept

It is clear that the use of multibit quantizers improves the performance of the modulator. Considering now this block, another interesting question can emerge: Can something be done in order to improve even more the performance of the system? Yes. The quantizer can be replaced by a more elaborated block that performs the quantization, but in such a way that it has the following signal transfer function (STF) and NTF:

$$STF = 1$$

$$NTF = \left(\frac{z-1}{z}\right)^n \text{ with } n \ge 0$$

(3.6)

The previous equations can be "translated" colloquially as: the new quantizer must provide noise shaping and delay-free signal transference. A possible solution to this comes from the so-called low-distortion topology [30], schematically depicted in Fig. 3.3.

Figure 3.3: Low-distortion topology.

Under the previous assumptions, now the quantization noise can be shaped by a higher order loop. Hence the new delta-sigma can be viewed as a feedback loop that can be *added* to any stable n-th order conventional delta-sigma loop, with a delay-free NTF, as depicted in Fig. 3.4.

Figure 3.4: The embedded system

The system becomes an nth-loop modulator [41] with requantization. Moreover, because the *added* delta-sigma is in the forward path, the nonlinearities introduced by the inner DACs will

be reduced by the outer-loop gain (the requirements for the ADC and the DAC used in the innerloop delta-sigma can be considerably reduced).

#### 3.1.4 Remarks

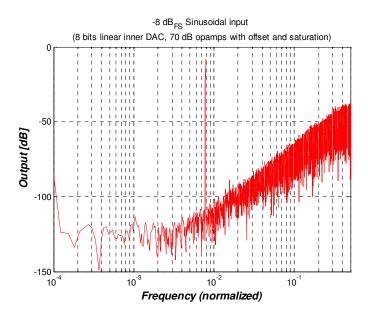

Simulation results for a second-order 5-bit ADC with only a 8-bit linear internal DAC are shown in Fig. 3.5, where nonideal effects were taken into account.

This new topology was published in [3], and its study was then discontinued. A recent publication [36] has shown the silicon implementation of a very similar – but better- approach for the requantization cancellation procedure. The concept of nested delta-sigma converters (delay free unit STF modulators) which emerged from this research was also presented in [3].

Figure 3.5 Typical 32768 point FFT. Proposed architecture having 2<sup>nd</sup> order noise shaping and a 5bit quantizer ADC. Saturation and gain blocks included. Opamp characteristics: DC-gain=70dB, offset=1mV. Inner DAC is 8-bits linear. Also considered is 1% error in integrator's gain.

# 3.2 Stochastic Data Converters

In biological systems, often a large number of low-complexity unit cells combine to perform a fairly exact function. Applying this idea to the circuits and systems domain, in this subsection it is proposed to use a set of coarse quantizers (i.e., 2- or 3-level comparators) combined

to obtain robust and highly linear multibit analog-to-digital (ADC) [2, 6], and digital-to-analog (DAC) converters [6].

The original question of linearity can be reformulated as follows: Is there any combination of unit elements (coarse elements) which can provide a multiunit (fine) linear response? The answer is yes. It was already mentioned that a 1-bit DAC is inherently linear; consequently the addition (linear operation) of many 1-bit DACs will also provide a linear output. To get a coherent result, it is common sense to ask for the same input in each one of those unit elements. But, having this request is easy to visualize that no extra information or improvement will be obtained unless some extra measures are taken (same input acting over similar signal processing blocks; in that case the obtained result is similar to having the multiplication of only one of the individual outputs by the number of combined unit elements). The proposed solution is to use a statistical approach. The general idea will be first presented, applied to delta-sigma ADCs, and then the application to the DACs will be shown.

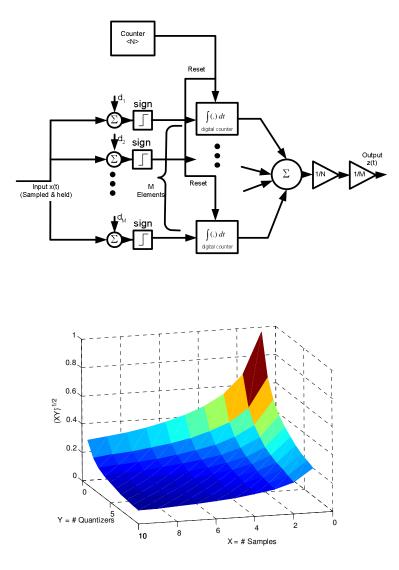

#### 3.2.1 Stochastic Quantizers (SQ)

Figure 3.6 shows the generalized stochastic quantizer. It has M branches, each one containing a one-bit quantizer, an independent identically distributed (i.i.d.) random noise source  $(d_i)$  added to the sampled and held input signal, x(t). Each digital output is followed by a digital integrator (up/down counter) controlled with a common modulo N counter. Those blocks will perform an accumulate-and-dump process (temporal averaging), while the parallel combination will provide a spatial averaging. Assuming the power of one individual quantizer to be  $q^2$ , after averaging M times spatially and N times temporally, the equivalent quantizer noise power at the output,  $q^2_{av}$ , will be:

$$q_{av}^2 \cong \frac{q^2}{NM} \tag{3.7}$$

Considering a linearized model, the output signal power will be equal to the input signal power, which means an increase in the signal to noise ratio (SNR) equal to *N*.*M*, or in other words, a reduction of the quantization noise power by the same factor The noise will decrease as the number of quantizer branches or the modulo of the counter increases, as depicted in Fig. 3.6-b). The tradeoffs depend on speed and power/area relations. It should be noted that for a given complexity, the maximum reduction of quantization noise is achieved when N = M.

Figure 3.6: a) Time-Spatial averaging quantizer. The noise sources are uncorrelated and i.i.d. The integrators are up/down counters. Scaling factors are at the output. b) Normalized RMS noise as a function of the number of samples and the number of parallel branches.

Oversampling is a well known technique to reduce in-band noise power, hence only spatial averaging (N=1) will be considered here (i.e., the counters will be disregarded in the mathematical development that follows). First, the application will be presented for an open loop configuration, but after that the emphasis will be put on delta-sigma modulators.

Based on the scheme of Fig. 3.6, and assuming no time averaging (N=1), the overall system becomes a parallel combination of M one-bit quantizer branches. It should be pointed out that the simple sign(x) quantizer could be replaced with a 3-level (1.5 bit) quantizer, obtaining

improved performance. Also, different *pdfs* (probability density functions) can be used to generate the random dithering and uncorrelating noise sources. The general case will be discussed next.

Assuming a linear operation over a continuous random variable (r.v.) d, with pdf  $f_d(d)$ :

$$y = x + a d \tag{3.8}$$

where *a* and *x* are constants<sup>1</sup>, then the pdf of the new r.v. *y* is given by [37]

$$f_{y}(y) = \frac{1}{|a|} f_{d}\left(\frac{y-x}{a}\right)$$

(3.9)

Without loss of generality, considering a=1, it is known that  $f_y(y)$  will be the convolution of  $f_d(d)$  with a Dirac's delta centered at x, i.e, the new pdf will be equal to the original one but shifted. On the other hand, the overall system output is given by

$$z = \frac{1}{M} \sum_{i=0}^{M-1} \operatorname{sign}(x+d_i) = \frac{1}{M} \sum_{i=0}^{M-1} \operatorname{sign}(y_i)$$

(3.10)

For large values of *M*, and using the law of large numbers, *z* tends to:

$$z \cong \overline{\operatorname{sign}(x+d_i)} = \overline{\operatorname{sign}(y_i)} = \overline{w}; \ w = \operatorname{sign}(y_i)$$

(3.11)

The mean value, or first moment, of a r.v. is defined as

$$\overline{w} \equiv \int_{-\infty}^{\infty} w f_{w}(w) \, dw \tag{3.12}$$

Using the sign(arg) definition (+1 if  $arg \ge 0$ , -1 otherwise), combined with the previous formulas,

<sup>&</sup>lt;sup>1</sup> *Here*, x is the sampled input value.

$$\overline{w} \equiv -\int_{-\infty}^{0} f_y(y) \, dw + \int_{0}^{\infty} f_y(y) \, dw =$$

$$-\int_{-\infty}^{0} f_d(y-x) \, dy + \int_{0}^{\infty} f_d(y-x) \, dy =$$

$$-\int_{-\infty}^{-x} f_d(\alpha) \, d\alpha + \int_{-x}^{\infty} f_d(\alpha) \, d\alpha$$

(3.13)

results.

From (3.13), it can be easily inferred that for a uniform distribution, the output is linearly related to the input. For other kind of distributions, look-up tables may be used to optimize the use of the quantizers.

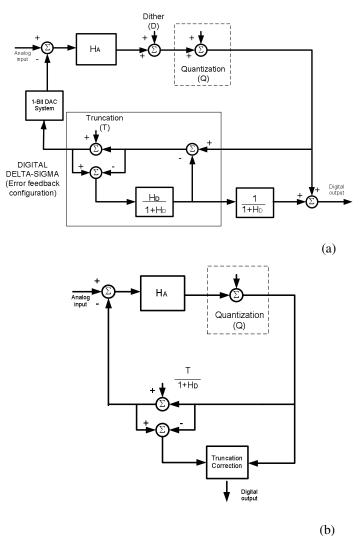

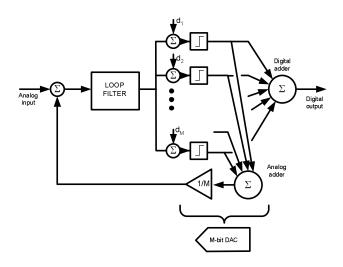

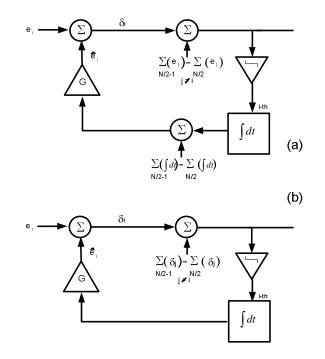

#### 3.2.2 Sigma Delta Modulators Using the Spatial Quantizer

The first design to be presented is a delta sigma ADC, schematically depicted in Fig. 3.7. In this case, to avoid excessive delays, the fast feedback toward the input addition point is made individually from each comparator. The addition in the digital domain is performed out of the loop, where delays can be tolerated. A second order system using 16 3-level comparators was simulated using ideal and nonideal components. Total correspondence with a 3-bit system was obtained. The main drawback lied in the DAC: having mismatch in the components, the main effect of the architecture is the randomization of the elements usage, reducing the harmonic content at the expense of an increased noise floor. It should be noted that the shape of the *pdf* in this case has no importance (the high loop gain tends to linearize the nonlinear quantizer characteristic). Moreover, offsets are tolerated. If the matching of the unit elements is good, this zero-order mismatch shaping (simple randomization) could provide an acceptable system.

Figure 3.7: Stochastic Quantizer embedded in a delta-sigma ADC loop.

For this example, the improvement in the signal-to-noise ratio (SNR) is evident using (3.7). The output of the system for any bandlimited input is then given by:

$$OUT = STF IN + NTF \left(\frac{Q}{\sqrt{M}}\right)$$

(3.14)

Here STF and NTF stand for the signal- and for the noise-transfer functions, respectively, and q is the quantization noise of a 3-level quantizer [9, 10].

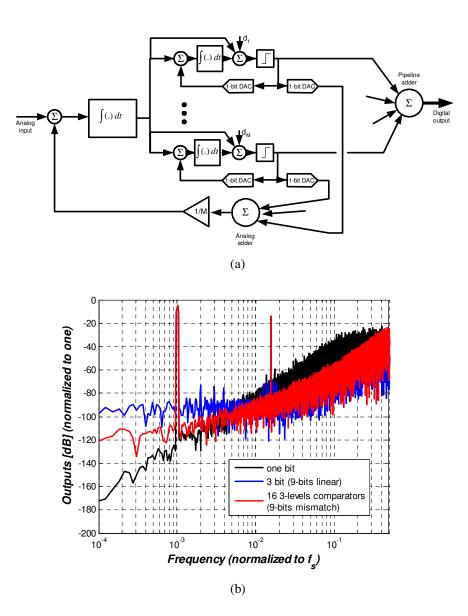

A first modification could be to use, instead of a simple 3-level quantizer, a first order delta sigma modulator for each branch. Figure 3.8-a) shows the system together with its simulation results. Nonideal effects were taken into account: The system was simulated using realistic models for the opamps (offsets in the order of +/-5mV, DC gains of 70~80dB, plus nonlinear characteristics were implemented in Simulink<sup>®</sup>), 9-bit matching for all the components, etc. It is noteworthy in this case that because each element has a 1-bit first order shaping, the overall response is highly linear (compare with the intermodulation tones in the 3-bit delta sigma modulator, with a 9-bit linear feedback DAC). For comparison purposes, the response of a 1-bit ADC is also shown. As a conclusion, an improvement in linearity is obtained without the use of data weighted averaging (DWA) or any other mismatch shaping technique in the DAC.

Figure 3.8: Delta sigma ADC using spatial averaging with embedded noise shaping. a) Simplified schematic. Two sets of 1-bit DACs are used to simulate a real system. b) Frequency response for a second order system using a 3-bit conventional quantizer, using 16 1.5-bit spatial quantizers, and using a 1-bit quantizer delta sigma. Two tones  $(-4.5dB_{FS} \text{ and } -14dB_{FS})$  used to observe nonlinear behavior. All elements are 9 bits linear.

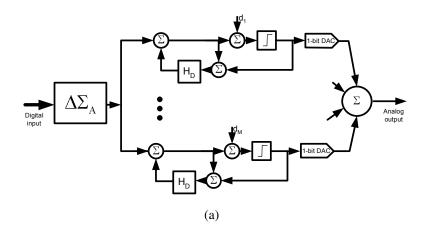

As a corollary, because of the linearity obtained, it is now possible to extend the concepts to a delta sigma DAC structure, as depicted in Fig. 3.9-a. The first step is to simplify the digital structures; hence, a first delta sigma loop ( $\Delta\Sigma_A$ ) is used to reduce the digital input word length. The dithering sources can be quantized and easily generated on-chip by means of pseudo random noise generators implemented with linear feedback shift registers (LFSR). The simulated response is shown in Fig. 3.9-b, together with a 3-bit and a 1-bit systems for comparison purposes. Also, the integrated noise powers are plotted for the three different cases.

Important points: error feedback can be used, resulting in reduced area and power consumption; no stability problems present as long as each equal individual one-bit branch is stable (possibilities of high order noise shaping); current sources can be used (obtaining consequently high speed developments).

Figure 3.9: Delta sigma DAC using spatial averaging with embedded noise shaping. a) Simplified schematic. Analog elements have 9 bits matching. Noise sources quantized to 3 levels. b) Frequency response for a second-order system using a 3-bit conventional quantizer, using 16 1.5-bit spatial quantizers, and using a one-bit quantizer delta sigma. Tone at -7dB<sub>FS</sub>. Also shown are the integrated noise powers for the three cases.

#### 3.2.3 Remarks

The idea behind this procedure can be explained as follows: under certain assumptions the quantization noise can be considered as a wide sense stationary stochastic process (generally considered uniformly distributed and with zero mean), with ergodicity in its mean and variance values (i.e., similar time and spatial statistical properties). Based on this fact, assuming zero correlation among all the individual outputs and successive samples, and using the law of the large numbers, we have concluded the previous results for a large number of comparators with large dithering sources.

Both time and space constrains were taken into account, e.g., for the spatial ADC case, a  $\log_2(M)$  bits length word is obtained as the output of the system, but with an equivalent quantization error of  $\log_2(M^{1/2})$ . The tradeoff is clear: *accuracy vs. time and/or area & power*.

On the other hand, an interesting and promising fact emerged from this research: highly linear devices can be devised using imperfect components.

As it was already mentioned, all the 1-bit inputs/outputs must be uncorrelated among themselves. The use of M noise sources at the inputs of the M comparators not only achieves this result, but also dithers the quantization noises, helping the loop filters to shape their power spectral densities (PSD). Generating the noise in the digital domain is an easy matter, something that is not so trivial in the analog domain.

As a final result, circuit robustness is obtained, which comes from the fact that there is no need of accurate voltage dividers to get the quantizer reference chain. Another extra advantage is that if one comparator (or a reduced amount of them) fails, the system will still be functional, with a little degradation on its characteristics

## 3.3 Digital Correction of DACs – Main Idea

In this section, an alternative approach is described for achieving enhanced DAC accuracy. It uses an adaptive digital correction of the internal DAC. The process is based on acquiring and refining digital estimates for the errors of all unit elements (capacitors or current sources) which form the internal DAC, and then applying the appropriate corrections to the output signal according to the known usage of these elements. Numerical simulations and practical results verified that even for large initial errors a very high conversion accuracy can be achieved using the proposed algorithm (to be discussed in Chapter 4).

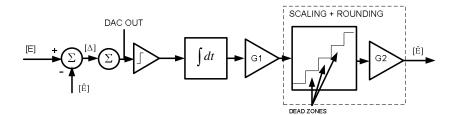

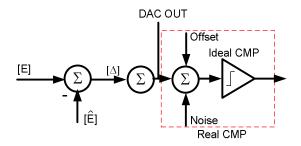

## 3.3.1 The Correction of the DAC

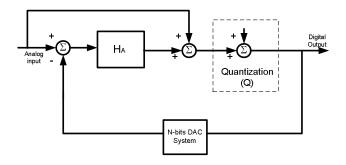

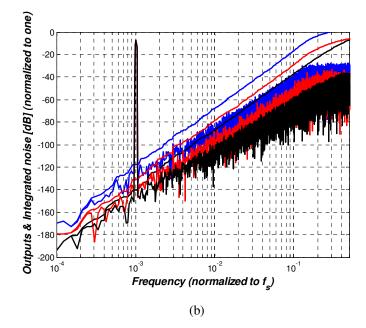

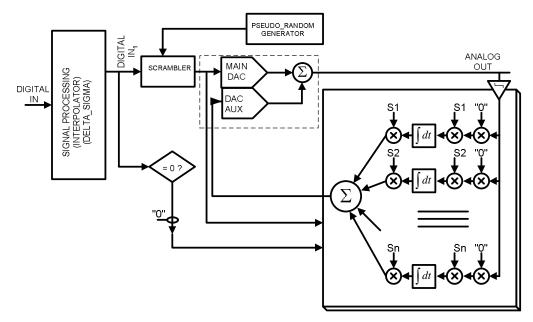

As pointed before, an oversampled DAC system can be decomposed into different subblocks, as those depicted in Fig. 3.10: The interpolation filter will increase the sampling rate and at the same time will provide replica reduction (increasing the effective number of bits, or ENOB); the delta-sigma modulator will reduce the number of processed bits, keeping the high accuracy. The part that will be described in this subsection is the one composed by the Main-DAC and its associated correction loop. The front end of the whole system is generally a smoothing filter, to suppress out of band corruptive noise and replica power.

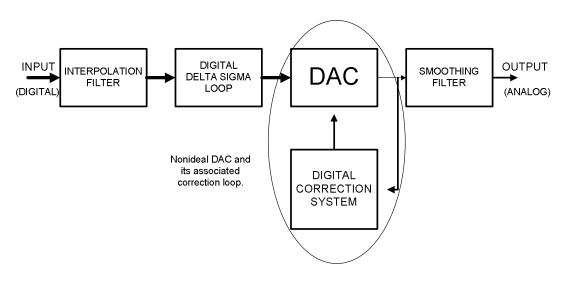

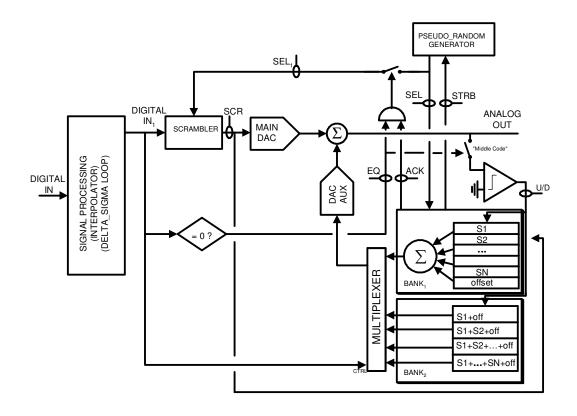

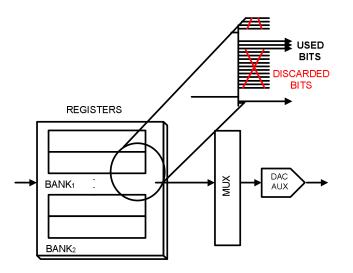

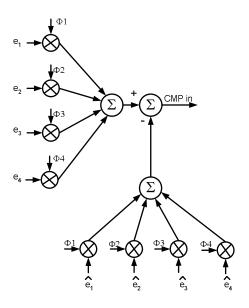

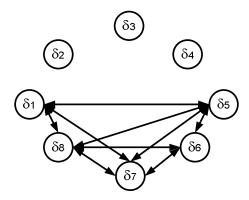

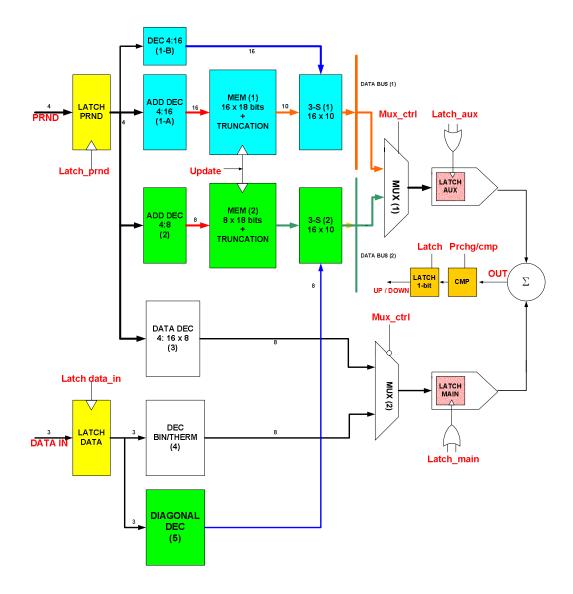

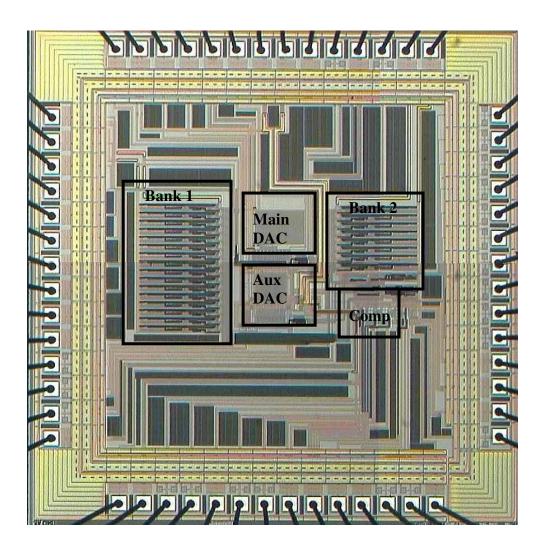

The idea of the correction loop is depicted schematically in Fig. 3.11. The main components of the system are the Main DAC (composed of  $2^n = N$  unit elements), an Auxiliary (reduced scale) DAC, 2 banks of registers (B<sub>ANK1</sub> to store the individual errors and B<sub>ANK2</sub> to store the complete errors for the different codes), a Scrambler to randomize the use of the unit elements and associated logic.

Figure 3.10: Digital to Analog system.

Figure 3.11: Schematic representation of the whole system. The Signal Processing block could contain an interpolator and a modulator to improve the ENOB (at expenses of speed)

The operation of the system can be described as follows: first, the digital input is preprocessed. Data are passed through an interpolation filter and a digital  $\Delta\Sigma$  loop.

At the same time (in a parallel process) a Pseudo-Random Code is generated for a generic "middle code". Considering a bipolar operation, the middle code is the zero code and it corresponds to the use of only half (N/2) of the total unit elements that compose the Main DAC. Also, this code will select the corresponding registers in BANK<sub>1</sub> (line SEL) to take part in the addition. This operation is realized in advance. Once the sum is completed then the system will wait until a middle code appears. At this point the digital value of the addition will be converted to an analog one (by means of the Auxiliary DAC), the Main DAC will use the corresponding elements (signal SEL will be copied to SEL<sub>1</sub> and will command the Scrambler) and a comparison will be performed.

It should be noted that the Scrambler will select the corresponding elements in the Main DAC only if  $SEL_1$  is active, and this will occur if and only if the code is the middle one (signal EQ active) and at the same time the addition in BANK<sub>1</sub> is complete (signal ACK).

After this occurs, the 1-bit comparison will tell whether the corresponding registers in  $BANK_1$  must be increased or decreased. In  $BANK_2$  the registers will be modified as follows:

referring to Fig. 3.11, it is shown that the first register of BANK<sub>2</sub> will contain the error corresponding to the first element in the Main DAC, the second register will contain the error for the  $1^{st}$  and the  $2^{nd}$  elements added together, an so on, until the last register which will contain the error of the sum of all the unit elements. When a specific unit element is used, then in accordance with the comparator output, the registers in BANK<sub>2</sub> that "contain" this element will be increased/decreased. The idea behind this procedure is that if the residual error is reduced each time a comparison is carried out, then in steady state the registers in BANK<sub>1</sub> and BANK<sub>2</sub> have been updated in the same way and at the same time, then BANK<sub>2</sub> will contain the scaled version of the errors for the  $2^n$  possible combinations (digital codes without being scrambled) for the sum of unit elements of the Main DAC. If the code is not the middle one or the system is busy, then the Auxiliary DAC will feed the corresponding output from BANK<sub>2</sub> (passing trough a Multiplexer), and the correction will be performed.

When the addition and the update of the registers in  $BANK_1$  and  $BANK_2$  is completed, then a signal (STRB) indicates that the registers are ready to perform another operation.

The total number of registers is 2N, and the delay in the Analog/Digital loop is minimized with the use of the MUX.

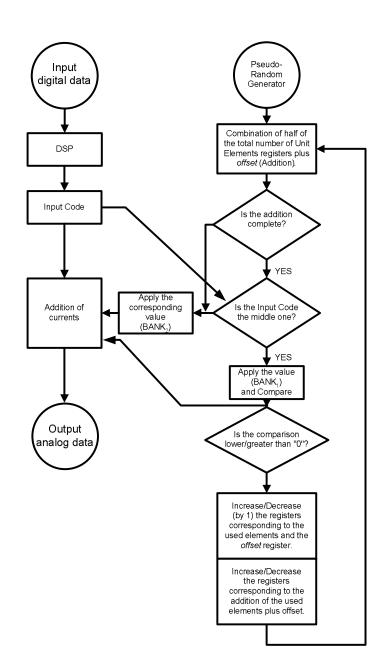

A simplified block diagram is presented in Fig. 3.12, showing the two parallel interconnected processes.

Figure 3.12: Flow graph that represents the operation of the system. 2 Processes running in parallel.

## 3.3.2 Other Topologies

#### Analog Implementation:

Another idea for the implementation is depicted schematically in Fig. 3.13. In this case, there are only N "registers" that are combined in the same way than was previously described: half of them will be considered for comparison/updating when the middle code appears (signal "0" used in conjunction with signals S<sub>i</sub> from the SCRAMBLER block). The main difference now is that these "registers" can be analog memories (capacitances), and then the Main and the Auxiliary DAC can be combined in only one device. Each analog memory could be the gate capacitance of an auxiliary current source in parallel with one of the unit-element current sources of the Main DAC. Clearly the Auxiliary DAC is absorbed in the main one. In this configuration, because it always needs an addition (no MUX involved) a delay is added in the feedback path if the processing is mixed (A/D). If the processing is only analog, the system is faster.

Another advantage is that now it is possible to use Data Weighted Averaging (DWA) techniques –for low frequencies of operation – combined with the adaptation, i.e., once the system has converged, the coefficients can be frozen and the DWA algorithm can start.

Figure 3.13: Another possible architecture, suitable for a totally analog implementation. The integrators could be implemented using switched current techniques to facilitate the additions (speed up the process).

#### Mixed-mode implementation:

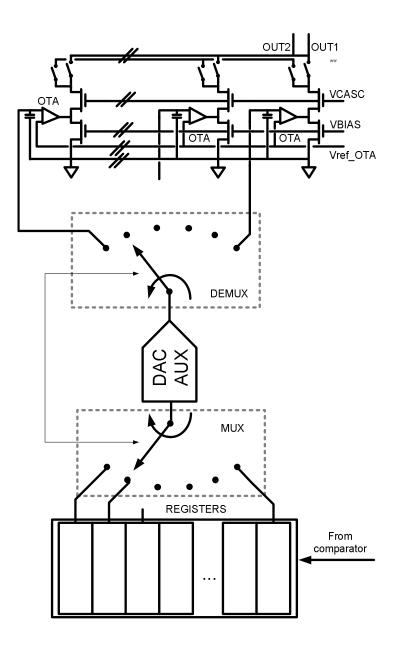

Consider the schematic of Fig. 3.14. In this case we have the digital (robust) memories acting as before. We are using a MUX and a DEMUX to feed the digital value to the AUX-DAC and to apply its result to a second set of memories, this time analog (holding capacitances). The capacitors store the analog compensation value; they do not play any role as integrators. The OTAs that are connected to these devices deliver an amount of current that will be injected in the source of the cascode transistors, not modifying the output impedance of the overall current source. The switching sequence will select which unit elements are going to be connected in each output, and hence which ones will be updated. The refresh cycle can be periodic and does not have to be clocked at the same system frequency.

### 3.3.3 Remarks

The use of Return to Zero (RZ) clocking improves the glitch immunity (reduces inter symbol interference, or ISI), and at the same time provides a periodic middle code that can be used for comparison purposes.

In the analog impelentation, the DC gain of the opamps plays an important role. Based on simulations, in order to get a linearity of 15 bits, a DC gain higher than 60dB is required (practical considerations will elevate that value to the70~80dB range).

Figure 3.14: Mixed-mode implementation.

## 3.4 Layout Considerations

This subsection will deal in detail with the current sources matching properties for currentsteering DACs. This is related with the fact that the fabricated prototype uses this type of architecture.

First of all, layout (geometrical design) techniques to overcome quadratic nonlinear effects will be addressed, proposing a new layout scheme.

After that, modified calculations to improve fabrication yield will be provided, together with their simulation results corroborating the idea. These are related with the work presented in [14]. Both developments were published in [5].

Considering unavoidable fabrication mismatches, it is known that the errors in a wafer are radial. When a small-dimension dice is obtained, this effect turns into an almost linear gradient that can be compensated with common centroid geometries [38].

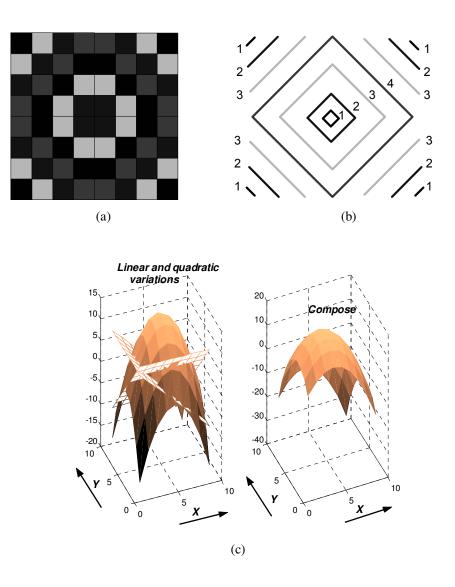

When the dice is attached to the package, stress-induced mismatches will appear following a quadratic law [12]. One way to deal with this is to decompose each unit current source and spread those sub-elements in an array, in such a way that to get again the original current source, the parallel connection of some of them will be performed starting in the "middle" and successively adding currents switching alternatively among positive and negative values in order to keep low the DNL.

#### 3.4.1 Contour Around a Line

The question here is: Is there another possibility of laying out the converter? Yes. As mentioned, there exist different ways to overcome quadratic effects [23]. By the time this research was published, almost simultaneously other authors [39] published articles with related approaches.

In order to obtain good linearity here it is proposed to follow a pattern that equalizes the errors for the current sources. The idea is based on the subdivision of the unit current sources  $(2^n)$  into  $(2^{2(n+1)})$  elements as depicted in Fig. 3.15-a) for a 2-bit example (4 elements). Of course, this is not practical for large n, but for low values (n=2, 3, 4) the linearity can be greatly improved. The idea behind the "tile shape" is to think that each current source is a point in the matrix (valid for a large matrix), and then transform the quadratic errors into only a gain error selecting accordingly unit elements around the middle contour (all the composed unit current sources will have the same error as can be inferred from Fig. 3.15-b). The linear errors are automatically compensated because the structure is a common centroid one. The use of the four quadrants minimizes random effects [11].

Fig. 3.15-c) shows the combination of linear and quadratic errors simulated. Each one of the four unit values finished with the same error, and the total error was zero.

Figure 3.15: a) Possible layout that equalizes the quadratic errors in a 2-bit DAC. All linear errors are compensated by means of a common centroid structure. b) Idea behind the proposed scheme. c) Simulated structure

Because of the symmetry, the overall layout can be subdivided in 4 quarters, as depicted in Fig. 3.16. To ensure matching, rows and files of dummy devices should be added (reducing etching effects).

Figure 3.16: Simplified layout

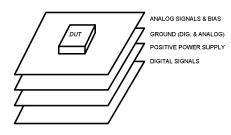

At the layout level, all the bias voltages can be routed using the lower level of metal, after that another metal layer can be used to shield the devices; a third level of metal can handle the control lines.

## 3.4.2 Matching Considerations

# 3.4.2.1 Integral Non Linearity (INL) vs. Matching

Considering the INL-Yield (defined as the fabrication yield for an acceptable INL, which is generally taken as 0.5 LSB), then a modification of the work presented in [14] for the normalized deviation of the unit current sources gives,

$$\frac{\sigma(I_{LSB})}{I_{LSB}} \cong \frac{\frac{1}{2}}{C\sqrt{2^{n}}2^{n_{1}}} = \frac{\sqrt{2^{-(n+2n_{1}+2)}}}{C}$$

(3.15)

With,

$C = inv \_normal\{0.5(1 + INL \_Yield)\}$

n = Number of bits of the converter.

$n+n_1$  = Linearity required =  $n_L$

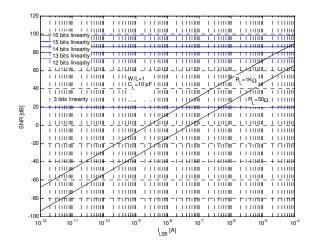

In this case, the INL-Yield will be calculated based on 0.5LSB deviation from the required (and possibly different than the original number of bits) linearity. Figure 3.17 presents the Monte Carlo simulations together with the equation result for 3-bit and 5-bit converters. Each converter having INL > 0.5 LSB of the required linearity ( $n_L$ ) was considered as a failed component. The normalized yield was taken as the ratio between good samples and the total number of samples simulated. It must be pointed out that the accuracy of the formula increases when the number of bits (n) is also increased. Fig. 3.18 plots the  $\sigma(I_{LSB})/I_{FS}$  ( $I_{FS}$ =Full scale current) for different linearity values, as a function of the number of bits (n), for *INL\_Yield*=99.7%

Figure 3.17: *INL-Yield* as a function of the normalized deviation of the unit current sources of the DAC (3-bit and 5-bit cases).

Figure 3.18: Unit current sources deviation normalized to the full scale current for different linearity, as function of the number of bits, for *INL\_Yield* = 99.7%.

For n=1 the analysis is invalid (1-bit DAC is inherently linear, hence the value of  $\sigma(I_{LSB})/I_{FS}$  is irrelevant.

Using the work presented in [15-16], the minimum area for the unit current transistors can be determined (neglecting quadratic spatial terms) from:

$$\left(\frac{\sigma(I)}{I}\right)^2 \cong \frac{A_\beta}{WL} + \frac{A_{VT}}{WL(V_{GS} - V_T)^2}$$

(3.16)

Here  $A_{\beta}$  and  $A_{VT}$  are technological parameters. Data was collected from different publications. The trend of these parameters as a function of the channel length is presented in Fig. 3.19, from which the matching properties could be extrapolated toward smaller sizes. This should be done carefully, because matching is process dependent, and then the parameters depend on metallization, etching, etc. The  $\beta$  factor is related with the transconductance, while the  $V_T$  factor relates to the threshold potential of the devices. Based on extrapolated values for a 0.35u technology, and in the previous equations, Fig. 3.20 presents the dimensions (W and L) and also the area of the devices for an INL-Yield of 99.7% (C  $\approx$  3) in a 10-bits DAC with 10 bits of linearity and a full scale current (I<sub>FS</sub>) of 1mA.

Figure 3.19: Matching parameters as a function of the technology length.

It must be pointed out that the  $\beta$  factor decreases only with the area, while the V<sub>T</sub> factor decreases with both area and gate voltage. A good tradeoff presented in [12] is to select the *equality point* (where both error contributions have the same value). For the previous example this gives big values for W and L (in the order of tens of microns). Clearly, with these values the channel length modulating effect and/or the width effects will not affect the operation of the device (it will behave like a true quadratic device).

Figure 3.20: Length (L), Width (W) and Area (scaled by 10e4) for the typical parameters of a  $0.5\mu$  technology.

## 3.4.2.2 Matching and Area

Considering the point at which both contributions (due to  $V_T$  and to  $\beta$ ) are equal (*equality\_point*), the total area depends only in the required linearity and can be approximately expressed as:

$$Area = 2^{n}WL \cong \frac{2A_{\beta}}{\left(\frac{\sigma(I_{LSB})}{I_{LSB}}\right)^{2}} 2^{n} = 3^{2}2^{3+2nL}A_{\beta}^{2}$$

(3.17)

From this it can be inferred that the active area needed will remain the same regardless of the number of bits used. The only parameter that dictates the total area (neglecting connections) is the required linearity. Fig. 3.21 presents a plot of this fact. The area grows by a factor of 4 for each linearity bit added.

Figure 3.21: Area (Active) as a function of the linearity for a typical 0.5µm process.

The advantage of the DAC correction topology is evident. In that architecture, to get 15 bits of linearity, two 10-bit DACs are required (Main and Aux). The area is roughly twice the area of a 10-bit converter. On the other hand, using the previous equation, the required area should be 32 times the 10-bit area. Of course, no logic and additional circuitry was taken into account in this calculation, but they can be made relatively small compared with the final area. Another advantage that can be expected is that increasing the accuracy using big devices reduces the maximum achievable operating speed, which does not occur in the corrected system.

#### 3.5 Circuit Design Point of View

This subsection will describe novel ideas about the implementation of the current sources and its associated drivers. The ideas behind are the improvement of the output resistance (diminishing code-dependent nonlinear effects), and the reduction of dynamic degradation due to switching glitches.

#### 3.5.1 Active Cascode in Current Sources

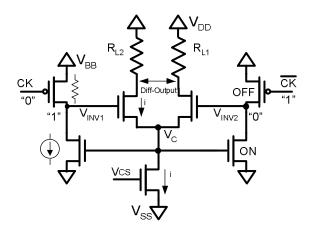

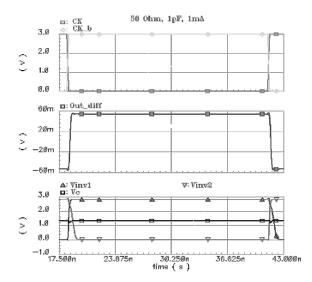

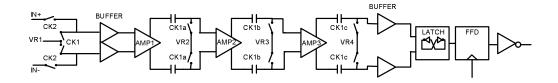

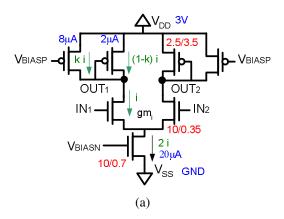

If the output resistance is of concern, the current sources can be alternatively implemented using a novel active cascode configuration [5], depicted schematically in Fig. 3.22.

Figure 3.22: Schematic of the modified active cascode unit current cell.

The extra added circuitry is shown in the figure, together with an example, in which the left side behaves as an inverter, and the right side is disconnected (switched off). It is also intrinsic to the circuitry that the cross-over point could be set high, hence minimizing the drain variation of the current source ( $V_c$  remains more constant, when compared with a conventional scheme). Fig. 3.23 shows some transient Spectre<sup>®</sup> simulations, in which these effects can be appreciated in more detail (0.35µm technology). Fig. 3.24 shows the effect of the active cascoding, with an increase of approximately six times for the output impedance (current source of 1mA, load of 50 $\Omega$  and fast switching). The operation speed is not greatly affected, since  $R_L$  sets the output dominant pole (a low-value resistor).

Figure 3.23: Transient simulation of the unit current source. The differential voltage is still fast. Important to note is the small variation in  $V_C$  (drain voltage of the current source)

Figure 3.24: Increase of the output impedance using gain boosting. Approximately six times.

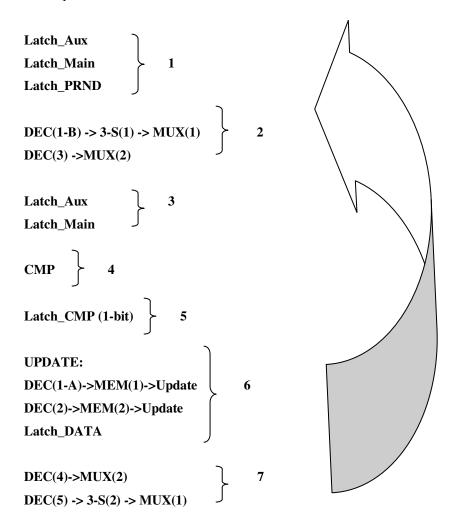

## 3.5.2 Latches and Crossover Point

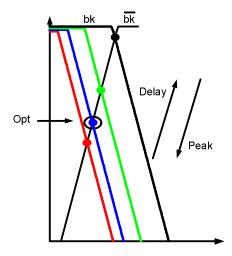

The crossover point of the input control signals is another important issue in currentsteering DACs. Depending on whether it is very high or very low, the switching characteristics are going to be influenced. As an example, Fig. 3.25 shows schematically different switching conditions (with ideal clock waveforms), which can cause glitches and degrade the dynamic linearity. If the crossing point is selected too low, then during a small amount of time both switching transistors will be OFF, and then the MOS implementing the current source will be in its linear region; when it is time to recover the normal operation, a delay and a glitch will be imposed. There exists an optimum point that minimizes delay and peak response, which was empirically found by simulation.

Figure 3.25: Unit current sources different crossing points

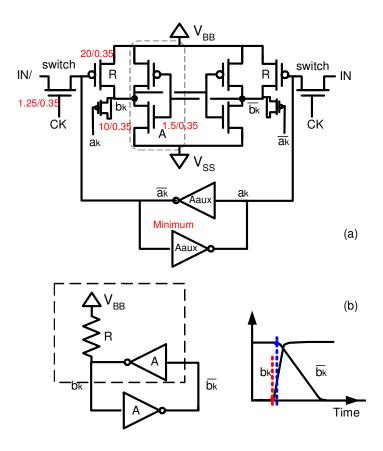

Considering the previous fact, a fast driver that controls this crossing was developed. The specially designed high-speed latch is shown in Fig. 3.26. All transistors are minimum dimension MOS except the large PMOS pull-up ones. A big pull-up will force a fast rise time, setting the crossing point high and vice versa (selecting to use large NMOS pull-down resistors the opposite situation can be gotten). A small delay after the fast rise time, the slow fall time will start (Fig. 3.26-b). The auxiliary inverters help to reduce feedthrough problems and stabilize the system at high frequencies. Two extra transistors were added to compensate feedthrough injection. These devices act as MOSCAPs neutralizers, having drain and source shortcircuited, half of the pull-up MOS

aspect ratio (W/L), and are clocked in a complementary way. Simulations and measured results have shown a large reduction of the glitch power.

Figure 3.26: Proposed Latch.

The previous latch can have all the transistors of minimum dimensions, except the pull-up. It is highly efficient in terms of area and speed.

# **CHAPTER 4. DIGITALLY CORRECTED DAC**

This section will deal with the architectural fine points of the digitally corrected currentsteering DAC.

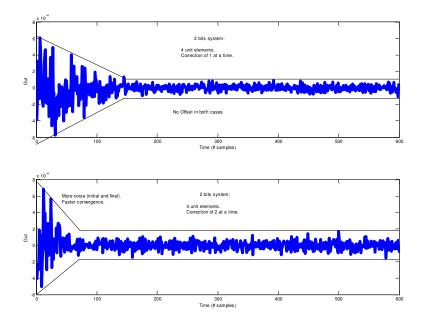

Starting with a possible implementation, errors due to resistors mismatch and to the comparator will be addressed. Analytical models and a mathematical analysis of the system will be presented. A novel switching sequence is then introduced, which is intended to speed up and to simplify the digital hardware. Finally, high level simulation results are presented, showing the feasibility of the proposed idea.

### **4.1 Possible Implementation**

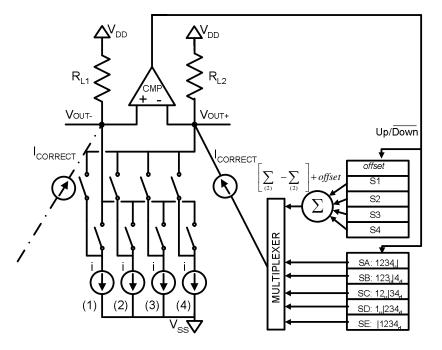

As a graphical example, Fig. 4.1 represents a possible fully differential implementation (2 bits). In this case, the unit elements are current sources of unit value (i). The comparison is carried out between the two (randomly) selected halves. As explained in previous sections there are two banks of memory: one for the storage of the individual errors, and the other for the ordered correction codes. There exist also an extra register (*offset*) whose function will be explained in detail in the next subsection; here it is only worth to mention that load mismatch and comparator offset can cause instability in a fully differential system. The manner in which the *offset* register is updated is related to the comparator output.

Because the binary 2-bit input word can only address 4 different codes, either SA or SE must be discarded (if symmetry is important, both of them can be disregarded in the final implementation). For the sake of generality in the explanation that follows, both of them will be kept.

In order to update the registers, the sum of half of the elements plus the offset is subtracted from the sum of the other half. The registers in BANK<sub>1</sub> are updated as described previously in Sec. 3.1.3. In BANK<sub>2</sub> now the registers are updated only considering the positive (or the negative) half, as depicted in the following example: if the positive half is composed of elements 1&3, that means the negative one is composed of elements 2&4. Under these assumptions, supposing the comparison dictates an increase in the positive half (signal U/D high), then S<sub>A</sub> and S<sub>B</sub> will be increased by 3, S<sub>C</sub> and S<sub>D</sub> will be increased by 1, and S<sub>E</sub> will be decreased by 1. Registers S<sub>1</sub>, S<sub>3</sub> and *offset* will be increased by 1. The output voltage value is the difference between the two halves. Each code will be corrected using  $S_A...S_E$  respectively through the Multiplexer and the Auxiliary DAC (represented in the diagram of Fig. 4.1 as the current  $I_{CORRECT}$ ).

This method has shown to be really efficient in terms of speed; its problem is complexity. Another possibility is to update only one element at a time (it can be updated the first one that was randomly selected). The price paid in speed is compensated with the simplicity of the implementation. Example1: suppose that the element  $S_2$  was the first element in the random selection, and that the comparison dictates an increase of its value. Consequently,  $S_2$  and the *offset* register will be increased by 1. In BANK<sub>2</sub>,  $S_A$ ,  $S_B$  and  $S_C$  must be increased by 2, while  $S_D$  and  $S_E$  will be left unchanged. Example 2: suppose that the same element ( $S_2$ ) was selected, but the comparison dictated a decrease. Now  $S_2$  and the *offset* register will be decreased by 1. In BANK<sub>2</sub>,  $S_A$ ,  $S_B$  and  $S_E$  will be decreased by 1. In BANK<sub>2</sub>,  $S_A$ ,  $S_B$  and  $S_C$  must be increased by 1. In BANK<sub>2</sub>,  $S_A$ ,  $S_B$  and  $S_C$  must be increased by 1. In BANK<sub>2</sub>,  $S_A$ ,  $S_B$  and  $S_C$  must be decreased by 1. In BANK<sub>2</sub>,  $S_A$ ,  $S_B$  and  $S_C$  must be decreased by 1. In BANK<sub>2</sub>,  $S_A$ ,  $S_B$  and  $S_C$  will be decreased by 2 and  $S_D$  and  $S_E$  will be left unchanged. The idea behind these examples is that the increases (decreases) in BANK<sub>1</sub> are in steps of 1, and in BANK<sub>2</sub> they are in steps of 2 (this can be done easily hard wiring a 0 to the right of the registers, expanding the digital word). Also in BANK<sub>2</sub> there exists the possibility of leaving unchanged the value of the counters, which can be again easily implemented using a Chip Enable (CE) connexion.

Figure 4.1: Fully differential architecture. 2-bit example.  $S_1...S_4$  store the individual errors and *offset* stores the offset due to mismatches in  $R_L$  and offset in the comparator.  $S_A...S_E$  store the different combination errors (letter u (d), in  $S_A...S_E$ , points the relation with  $S_1...S_4$  for *increase* (*decrease*) the corresponding register)

#### 4.2 Offset Issues and the Acquisition of Unit Element Errors

Offset compensation provides insensitivity of the system to load resistor mismatches and comparator offset. It is necessary, since as the unit-element random selection process is carried out, having a mismatch is going to impede the system to converge. Moreover, considering the offset in the comparator, this DC value could be integrated in the counters making the system unstable.

Figure 4.2: Schematic of a 1-bit DAC with nonidealities.  $R_L$  could represent the effect of a coaxial line connected across the differential output.

Consider only a 2-element current-steering DAC, as depicted in Fig. 4.2. The Interconnection Matrix only symbolizes the scrambling for the middle code. Consider the unit elements without error; hence the matrix does not have any effect in the dynamics of the system. The correction current, for the sake of simplicity, will be considered to be injected in only one side as depicted. The load resistance ( $R_L$ ) can represent the impedance of a coaxial line connected between the outputs. Offset in the comparator ( $V_{off}$ ) and resistor mismatch ( $\Delta R$ ) are considered.

Simple loop analysis gives the required correction current value  $(i_c)$ :

$$i_{c} = V_{off} \left( \frac{2R + R_{L} + \Delta R}{R_{L} (R + \Delta R)} \right) - \frac{i\Delta R}{R + \Delta R} \cong V_{off} \left( \frac{2R + R_{L}}{R_{L} R} \right) - \frac{i\Delta R}{R}$$

(4.1)

Without the load resistor, the part of the correction current that depends on the comparator offset reaches its minimum. Considering an infinite gain comparator, the differential output after the compensation has settled will present a DC offset equal to the comparator offset.

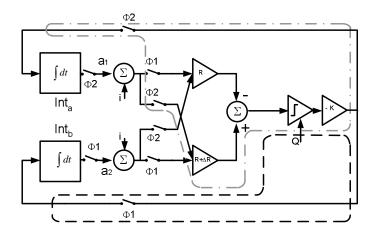

Figure 4.3: Block diagram for offset analysis

Another way to analyze the problem, now from the system point of view, is as follows. Consider no offset in the comparator, and a resistor unbalance, then an equivalent block diagram as the one depicted in Fig. 4.3 can be used. The outputs of the integrators are currents, and the gain blocks represent the resistors.

Because there are only 2 elements and a scrambling process, it can be supposed that there are 2 non-overlapping phases as depicted. Consider also that the update is made in the half that is connected to the mismatched resistor. This feedback scheme forces the error signal before the comparator to be zero, hence, in steady state, after the calibration converges, the quantizer can be thought as adding only granular noise with zero mean. Because the randomness of the process, it can be inferred that in steady state the average values of  $a_1$  and  $a_2$  are equal. If  $avg(a_1)=avg(a_2)$ , then the loop in both cases is the same. The average values can be calculated from: