#### AN ABSTRACT OF THE THESIS OF

<u>Jorge Grilo</u> for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and Computer</u> <u>Engineering</u> presented on <u>June 27, 1997</u>.

Title: <u>Improved Design Techniques For Low-Voltage Low-Power Switched-Capacitor</u> <u>Delta-Sigma Modulators</u>.

Abstract approved: \_\_\_\_\_

Gabor C. Temes

This dissertation investigates the constraints which arise when switched-capacitor (SC) delta-sigma modulators are designed for low-voltage operation, targeting also low power dissipation, and proposes methods of improving the performance and optimizing for low power dissipation. This is accomplished by identifying critical elements whose performance can lead to increased power dissipation, as well as the fundamental limitations of available analog circuit techniques. A prototype was designed and fabricated, which reflected these findings, and therefore exhibited good performance and nearly optimum power dissipation.

One of the key performance parameters is the dc gain of the amplifier in the first stage; it should be high. This is necessary for high linearity and low quantization noise leakage. In low-voltage operation, it may become impractical to use conventional topologies employing cascoding techniques (e.g., folded-cascode) which provide high gain in one single stage. Rather, cascaded structures have to be used. The disadvantage of the latter is the necessity for frequency compensation which results in increased power dissipation. Hence, another objective of this work is to exploit techniques which compensate for the open-loop gain characteristic of the amplifier (dc gain and nonlinearity), thus permitting the utilization of single-stage low-gain topologies. Predictive correlated double sampling is one of such techniques and is analyzed in detail. <sup>©</sup>Copyright by Jorge Grilo June 27, 1997 All Rights Reserved

### Improved Design Techniques For Low-Voltage Low-Power Switched-Capacitor Delta-Sigma Modulators

by

Jorge Grilo

### A THESIS

#### submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Completed June 27, 1997 Commencement June 1998 Doctor of Philosophy thesis of Jorge Grilo presented on June 27, 1997

**APPROVED:**

Major Professor, representing Electrical and Computer Engineering

Head of Department of Electrical and Computer Engineering

# Redacted for privacy

Dean of Graduate School

I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request.

Redacted for privacy

Lorge Grilo, Author

### ACKNOWLEDGEMENTS

I wish to express my deep appreciation to my research advisor Prof. Gabor C. Temes for the unique opportunity to work under his supervision. His guidance provided me with the insight, technical maturity, and incentive to pursue this work. I thank him for his refreshing sense of humor, and for his inspiring sense of responsibility and dignity.

I would like to thank the faculty in the ECE department at Oregon State University, who directly or indirectly contributed to my technical growth, in particular to Prof. Jack Kenney, Prof. Wojtek Kolodziej and Prof. Stephen Goodnick. Thanks also to my friend Rita Wells ("Red") for her support and jokes.

Thanks also to Prof. David Gobeli from the Business Administration Department for taking the time to serve in my graduate committee.

I would like to thank Prof. Epifanio da Franca for his inspiring and uncompromising commitment to excellence, for his trust, for all the opportunities he granted while in the Integrated Circuits and Systems Group in Portugal, and for encouraging me to pursue this degree.

I would like to thank Raouf Halim for the invaluable opportunity of completing this work at Rockwell Semiconductor Systems, in a highly qualified environment. Thanks to all the members in the mixed-signal group for their support, in particular to Guangming Yin and Edward MacRobbie for numerous and enlightening technical discussions, and to Mohamad Tabatabai for his support during the test of the chip.

I would like to thank Yunteng Huang for countless fruitful technical discussions, and for proofreading this text.

Thanks also to Junta Nacional de Investigação Científica e Tecnologica (JNICT) for its financial support through the CIENCIA program.

Finally, I would like to thank my parents, to whom I owe everything, for their love and understanding, and to whom this work is dedicated.

### TABLE OF CONTENTS

|    |     |        |                    |                                                                | Page |

|----|-----|--------|--------------------|----------------------------------------------------------------|------|

| 1. | INT | RODU   | CTION              |                                                                | 1    |

|    | 1.1 | Objec  | tive               |                                                                |      |

|    | 1.2 | Thesis | s organiza         | tion                                                           |      |

|    | 1.3 | Origin | nal contrit        | outions of the thesis                                          | 5    |

| 2. | GEN | NERAL  | DESIGN             | CONSIDERATIONS FOR LV/LP $\Delta\Sigma$ MODULATO               | RS 6 |

|    | 2.1 | Motiv  | ation for          | LV/LP design                                                   | 6    |

|    | 2.2 | The d  | elta-sigma         | technique                                                      | 9    |

|    | 2.3 | Perfor | mance m            | etrics                                                         | 13   |

|    | 2.4 | Gener  | al perform         | nance requirements for a $\Delta\Sigma$ modulator              | 16   |

|    | 2.5 | Funda  | mental lin         | nits to power dissipation                                      | 22   |

|    | 2.6 | Summ   | nary               |                                                                | 29   |

| 3. |     |        |                    | SIS OF VOLTAGE AND POWER CONSTRAINTS<br>A-SIGMA MODULATOR      |      |

|    | 3.1 | The 2  | nd-order s         | ingle-loop $\Delta\Sigma$ modulator                            | 30   |

|    | 3.2 | The fi | rst integra        | tor                                                            |      |

|    |     | 3.2.1  |                    | ice of the reference voltage and the sizing of the g capacitor | 36   |

|    |     | 3.2.2  | The ope            | rational amplifier                                             | 50   |

|    |     |        | 3.2.2.1<br>3.2.2.2 | Power dissipation<br>Biasing the operational amplifier         |      |

|    | 3.3 | The se | econd inte         | grator                                                         | 77   |

|    | 3.4 | The co | omparator          |                                                                | 80   |

|    | 3.5 | The D  | A conver           | ter                                                            | 81   |

|    | 3.6 | Summ   | ary                |                                                                | 86   |

### TABLE OF CONTENTS (Continued)

| Page  |

|-------|

| I uno |

| 4. |            | 8 V 94 DB DYNAMIC RANGE DELTA-SIGMA MODULATOR FOR<br>CE APPLICATIONS                               |  |  |

|----|------------|----------------------------------------------------------------------------------------------------|--|--|

|    | 4.1        | Circuit design                                                                                     |  |  |

|    | 4.2        | Layout considerations 104                                                                          |  |  |

|    | 4.3        | Experimental results                                                                               |  |  |

|    | 4.4        | Summary 110                                                                                        |  |  |

| 5. |            | ROVED DESIGN TECHNIQUES FOR RELAXED COMPONENT<br>QUIREMENTS                                        |  |  |

|    | 5.1        | The correlated double sampling technique 112                                                       |  |  |

|    | 5.2        | Analysis of gain and pole errors in SC integrators 115                                             |  |  |

|    | 5.3        | Analysis of distortion in SC integrators due to the nonlinear gain characteristic of the amplifier |  |  |

|    | 5.4        | Predictive CDS and delta-sigma modulation                                                          |  |  |

|    | 5.5        | AC analysis of a SC predictive Nagaraj integrator 131                                              |  |  |

|    | 5.6        | Analysis of the $kT/C$ noise analysis in a predictive Nagaraj integrator 140                       |  |  |

|    | 5.7        | Summary                                                                                            |  |  |

| 6. | CON        | ICLUSIONS AND FUTURE WORK 146                                                                      |  |  |

|    | 6.1        | Conclusions 146                                                                                    |  |  |

|    | 6.2        | Future work 147                                                                                    |  |  |

| BI | BLIO       | GRAPHY149                                                                                          |  |  |

| AF | APPENDICES |                                                                                                    |  |  |

### LIST OF FIGURES

| <u>Figure</u> | Page                                                                                                                                                                                                                                                                                        |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

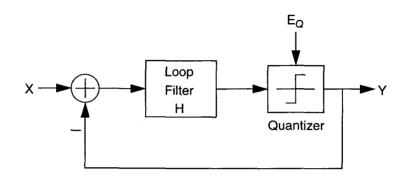

| 2.1           | Simplified block diagram of a delta-sigma modulator 11                                                                                                                                                                                                                                      |

| 2.2           | The concept of noise shaping                                                                                                                                                                                                                                                                |

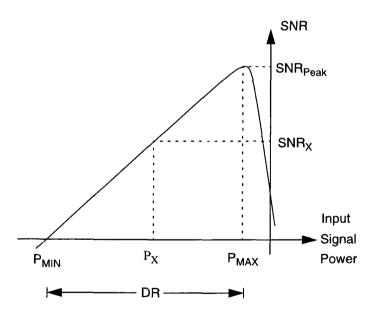

| 2.3           | Performance metrics used in connection with delta-sigma modulators 15                                                                                                                                                                                                                       |

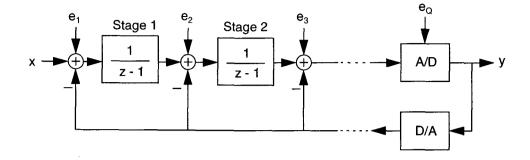

| 2.4           | Simplified diagram of an idealized $\Delta\Sigma$ modulator of arbitrary order                                                                                                                                                                                                              |

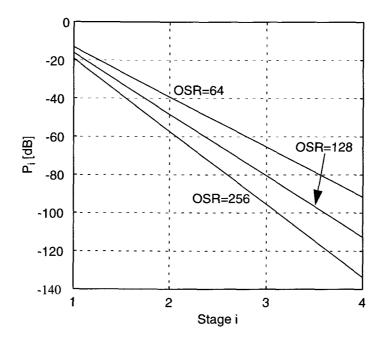

| 2.5           | Attenuation of the noise power generated at the input of stage <i>i</i>                                                                                                                                                                                                                     |

| 2.6           | Sampling the input signal                                                                                                                                                                                                                                                                   |

| 2.7           | Minimum energy consumption (power per bandwidth) as a function<br>of the dynamic range                                                                                                                                                                                                      |

| 2.8           | Trend for efficiency of utilization of energy                                                                                                                                                                                                                                               |

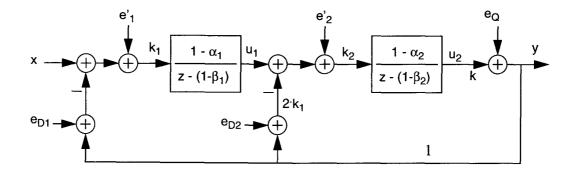

| 3.1           | Block diagram of a 2nd-order delta-sigma modulator with indication of various sources of noise                                                                                                                                                                                              |

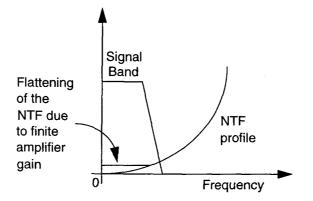

| 3.2           | Effect of the amplifier finite dc gain on the noise transfer function                                                                                                                                                                                                                       |

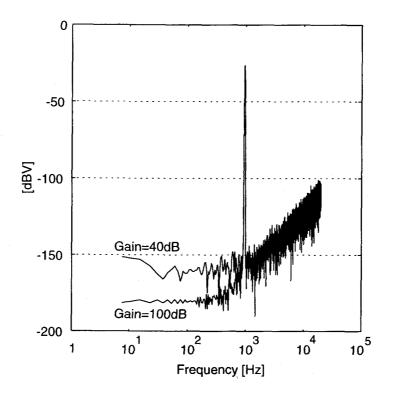

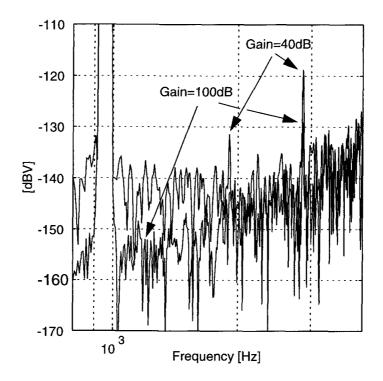

| 3.3           | Quantization noise leakage due to op-amp finite dc gain                                                                                                                                                                                                                                     |

| 3.4           | Effect of the nominal dc gain on distortion                                                                                                                                                                                                                                                 |

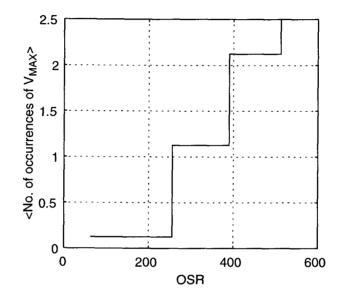

| 3.5           | Average number (simulated) of occurrences of $V_{MAX}$ , per period of the (sinusoidal) input signal, as a function of the oversampling ratio                                                                                                                                               |

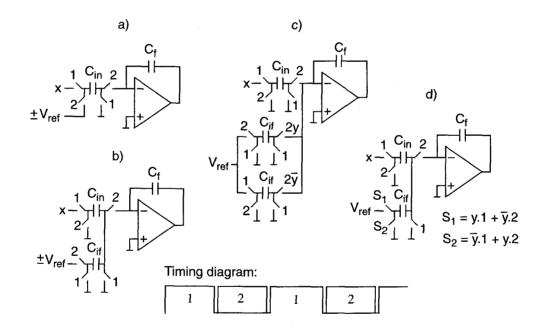

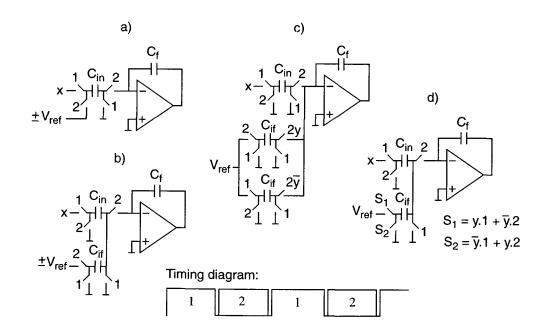

| 3.6           | Switched-capacitor, single-ended implementation of the first integrator with<br>a) double reference voltage single input branch, b) double reference<br>voltage two input branches, c) single reference voltage three input<br>branches, and d) single reference voltage two input branches |

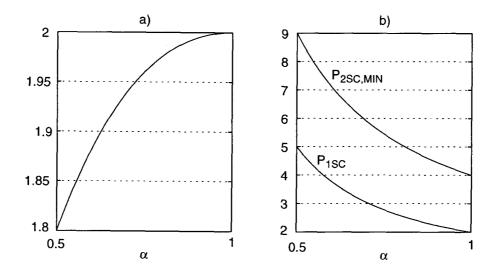

|               | a) Ratio between $P_{2SC,MIN}$ and $P_{ISC}$ .<br>b) $P_{2SC,MIN}$ and $P_{ISC}$ normalized to $2 \cdot kT \cdot DR / OSR$                                                                                                                                                                  |

|               | a) Ratio between $P_{2SC,MIN}$ and $P_{ISC}$ .<br>b) $P_{2SC,MIN}$ and $P_{ISC}$ normalized to $2 \cdot kT \cdot DR / OSR$                                                                                                                                                                  |

| Figure | Page                                                                                                                                                                                                                           |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

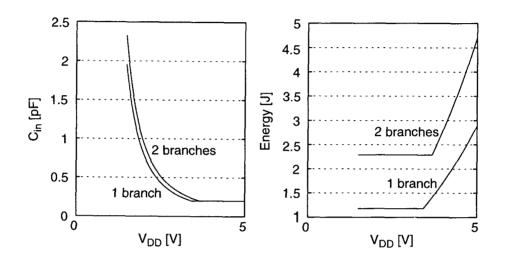

| 3.8    | a) Minimum size of the input capacitor when one and two SC branches are utilized in the input stage, as a function of $V_{DD}$ , and<br>b) Power dissipation per cycle (energy) when one and two SC branches                   |

|        | are utilized in the input stage, as a function of $V_{DD}$                                                                                                                                                                     |

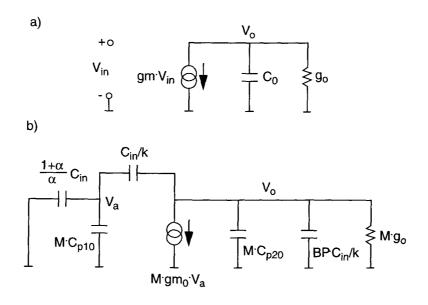

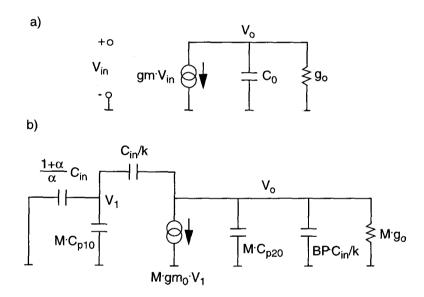

| 3.9    | Small-signal model of a single-pole amplifier<br>a) In a stand-alone configuration. b) In a feedback configuration                                                                                                             |

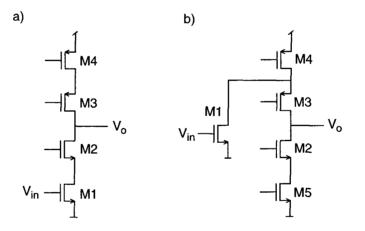

| 3.10   | Simplified single-ended implementation of<br>a) A telescopic cascode amplifier. b) A folded-cascode amplifier                                                                                                                  |

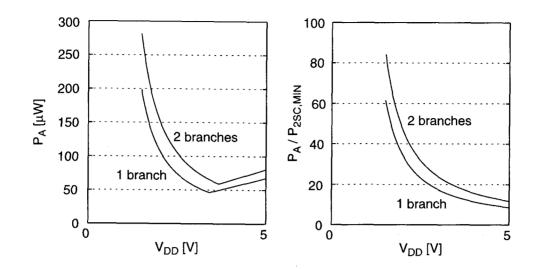

| 3.11   | <ul><li>a) Amplifier (fully-differential folded-cascode) static power dissipation.</li><li>b) Ratio between the amplifier static power dissipation and the minimum dynamic power dissipation in the sampling network</li></ul> |

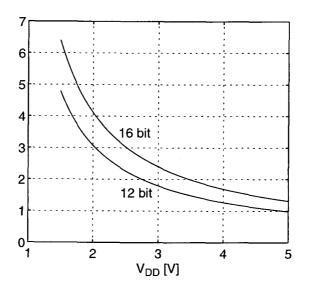

| 3.12   | Ratio between the minimum current to obtain the required closed-loop bandwidth, and the minimum current required for slewing, for $DR = 12$ bits and $DR = 16$ bits                                                            |

| 3.13   | Qualitative behavior of the minimum current required for settling $I_{BW}$<br>and of the minimum current required for slewing $I_{SR}$ ,<br>as functions of the fraction <i>m</i> of the sampling period                       |

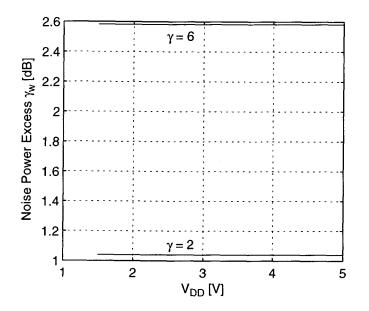

| 3.14   | Thermal noise excess factor at the input, due to amplifier noise                                                                                                                                                               |

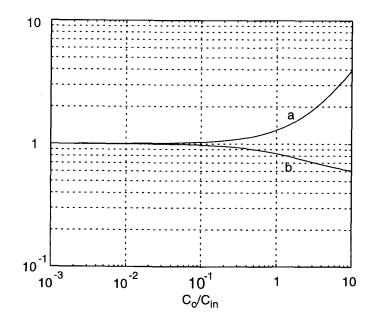

| 3.15   | Amplifier load capacitance with $C_o$ , normalized to that without $C_o$ , (a),<br>and input capacitor size with $C_o$ , normalized to that without $C_o$ , (b),<br>as a function of the ratio $C_o/C_{in}$                    |

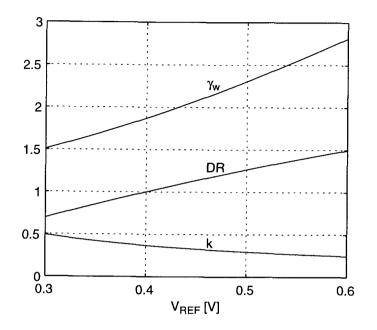

| 3.16   | Dynamic range as a function of the reference voltage,<br>normalized to the value obtained when $V_{REF} = 0.4$ V. Also shown<br>are the excess noise and gain factors                                                          |

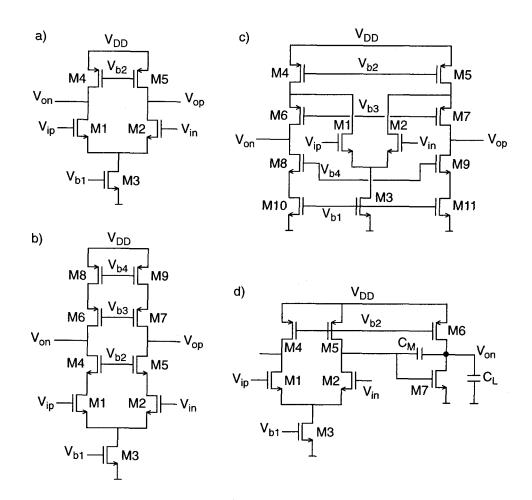

| 3.17   | Four popular amplifier topologies: a) differential pair,<br>b) telescopic cascode amplifier, c) folded-cascode amplifier, and<br>d) two-stage Miller amplifier                                                                 |

| Figure |                                                                                                                                                                                                                                                                                    | <u>Page</u> |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

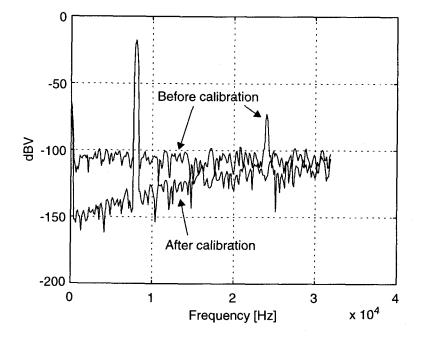

| 3.18   | Simulated spectrum of the output of a 2nd-order delta-sigma modulator employing 4-bit quantization, with and without calibration of the D/A converter                                                                                                                              | 83          |

| 3.19   | Switched-capacitor, single-ended implementation of the first integrator with a) double reference voltage single input branch. b) double reference voltage two input branches, c) single reference voltage three input branches, and d) single reference voltage two input branches | 84          |

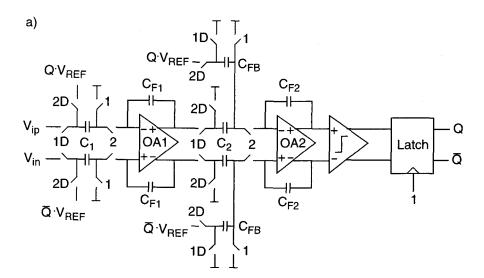

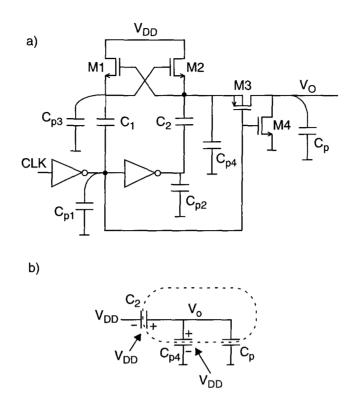

| 4.1    | a) Fully differential switched-capacitor implementation<br>of the 2nd-order delta-sigma modulator. b) Four-phase clock<br>generator and timing diagram                                                                                                                             | 88          |

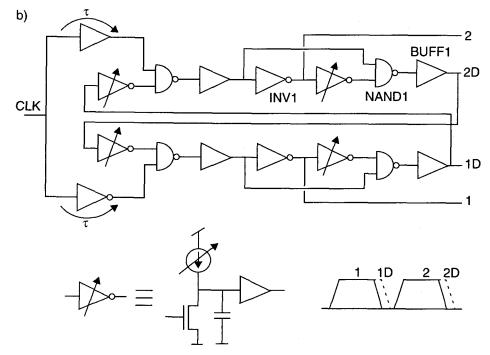

| 4.2    | Simulated SNR as a function of the input signal level power, for a 1 kHz frequency input sinewave                                                                                                                                                                                  | 91          |

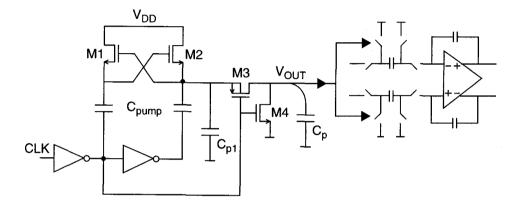

| 4.3    | Clock bootstrapping stage                                                                                                                                                                                                                                                          | 92          |

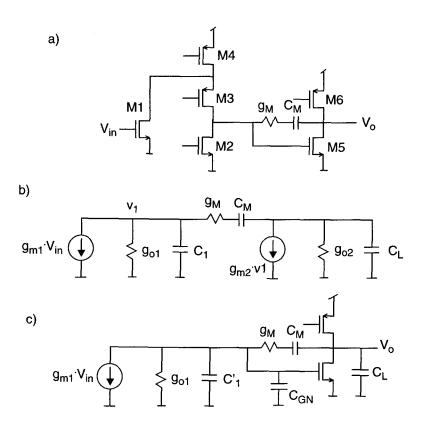

| 4.4    | <ul><li>Two-stage amplifier with Miller frequency compensation.</li><li>a) Simplified single-ended circuit. b) Simplified linear model.</li><li>c) Detail of output stage</li></ul>                                                                                                | 94          |

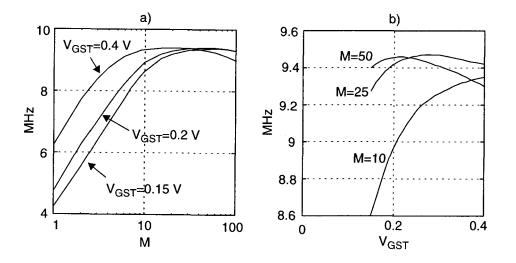

| 4.5    | Unity-gain bandwidth as a function of a) Multiplicity $M$ , parameter is gate overdrive voltage, and b) Gate overdrive voltage $V_{GST}$ , parameter is multiplicity                                                                                                               | 97          |

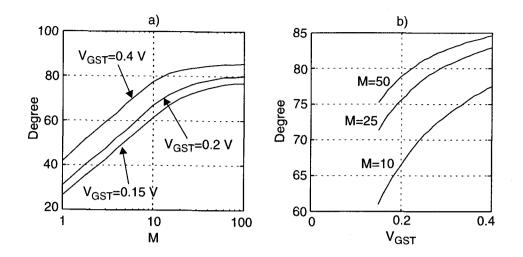

| 4.6    | Phase margin as a function of a) multiplicity $M$ , parameter is gate overdrive voltage, and b) gate overdrive voltage $V_{GST}$ , parameter is multiplicity                                                                                                                       | 98          |

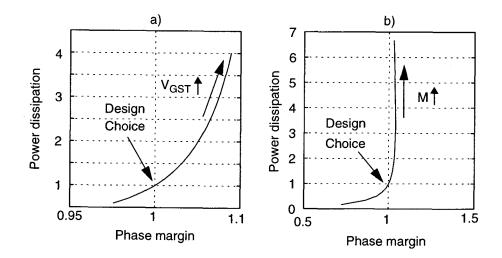

| 4.7    | Normalized power dissipation ( $V_{DD} = 1.8$ V) as a function of the normalized phase margin: a) for $V_{GST} = 0.15 \dots 0.4$ V. b) for $M = 1$ to 200                                                                                                                          |             |

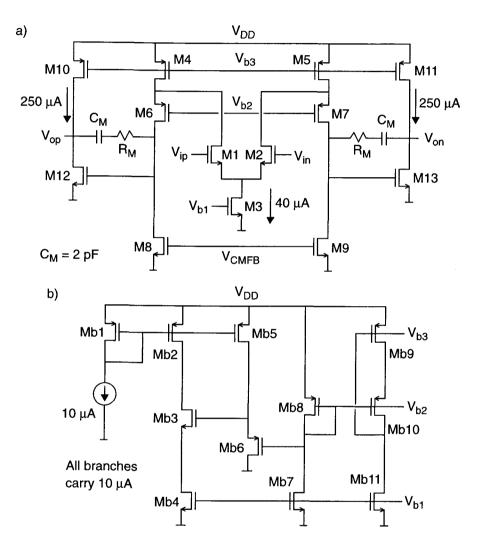

| 4.8    | a) Complete circuit diagram of the first stage amplifier. b) Bias circuit                                                                                                                                                                                                          | 100         |

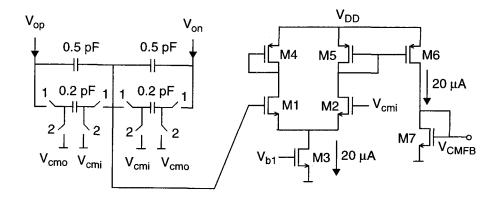

| 4.9    | Common-mode circuit                                                                                                                                                                                                                                                                | 102         |

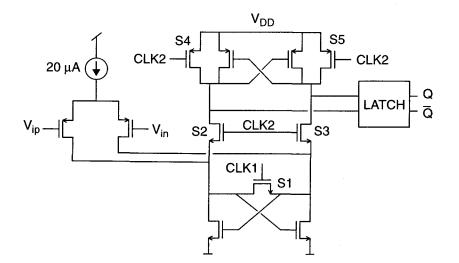

| 4.10   | Comparator circuit                                                                                                                                                                                                                                                                 | 103         |

| <u>Figure</u> | 2                                                                                                                                                                                                                                                                                                           | <u>Page</u> |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

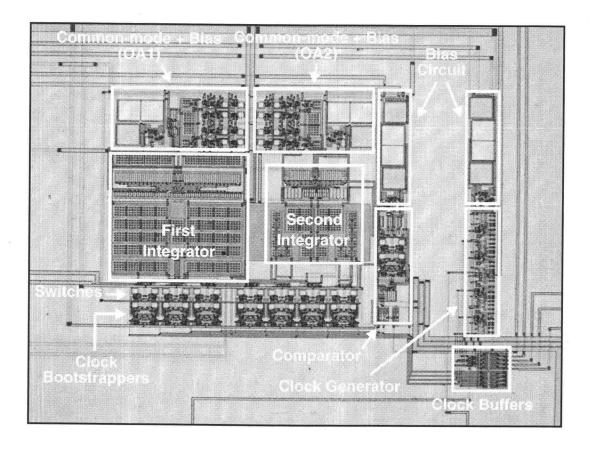

| 4.11          | Chip microphotograph                                                                                                                                                                                                                                                                                        | . 105       |

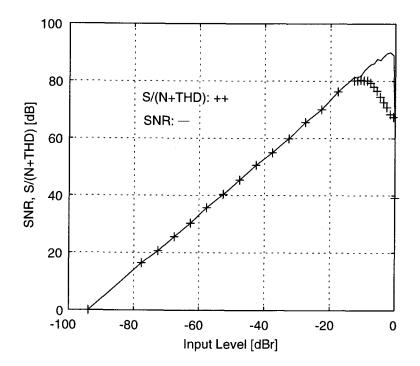

| 4.12          | Measured SNR and $S/(N + THD)$ as functions of the input signal level                                                                                                                                                                                                                                       | . 106       |

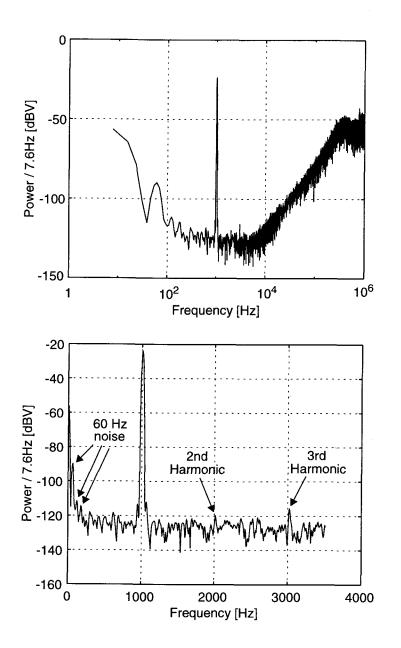

| 4.13          | Measured output spectrum for a -12.6 dBr, 1 kHz sinewave input.<br>Noise power = -99.21 dBV, Signal power = -20 dBV                                                                                                                                                                                         | . 107       |

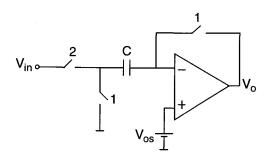

| 5.1           | SC voltage comparator employing correlated double sampling for offset compensation                                                                                                                                                                                                                          | . 113       |

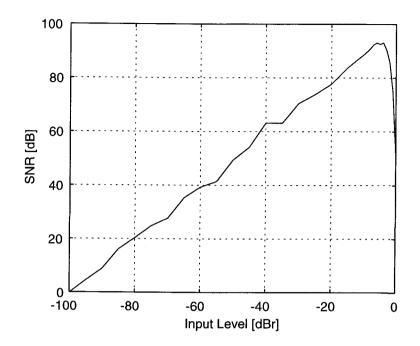

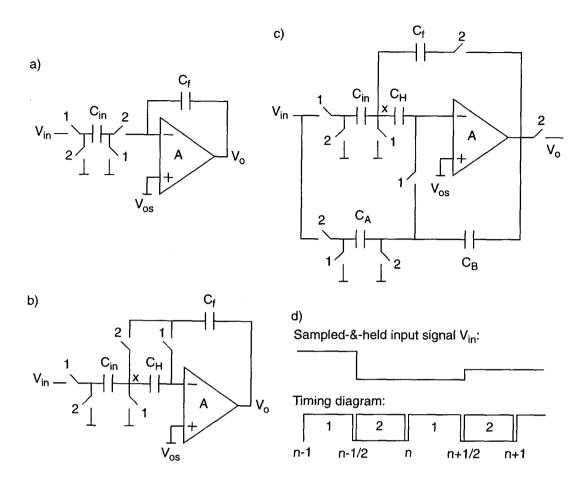

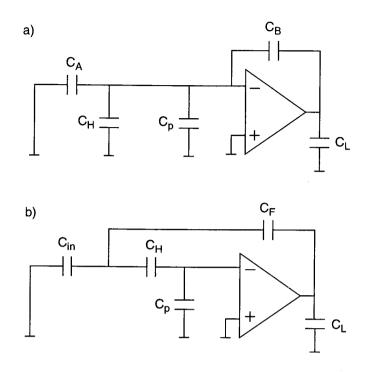

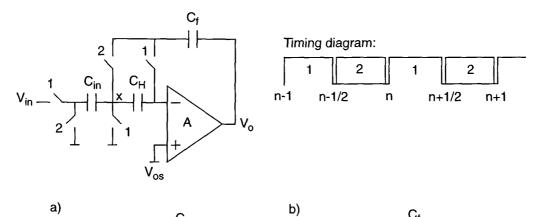

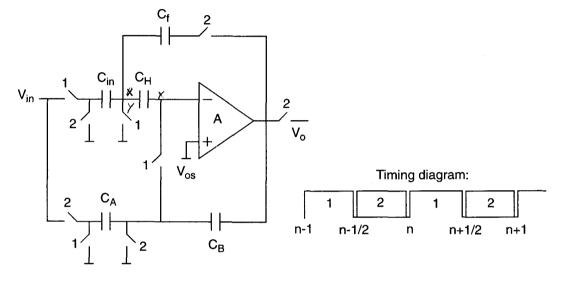

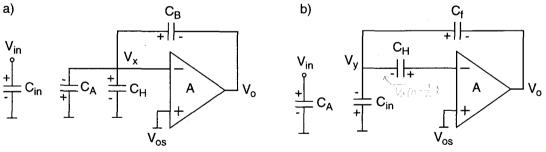

| 5.2           | <ul> <li>Three SC integrator topologies:</li> <li>a) Regular forward-Euler integrator.</li> <li>b) Offset- and gain-compensated Nagaraj integrator.</li> <li>c) Predictive Nagaraj integrator.</li> <li>d) Timing diagram and sampled-and-held input signal of the predictive Nagaraj integrator</li> </ul> | . 116       |

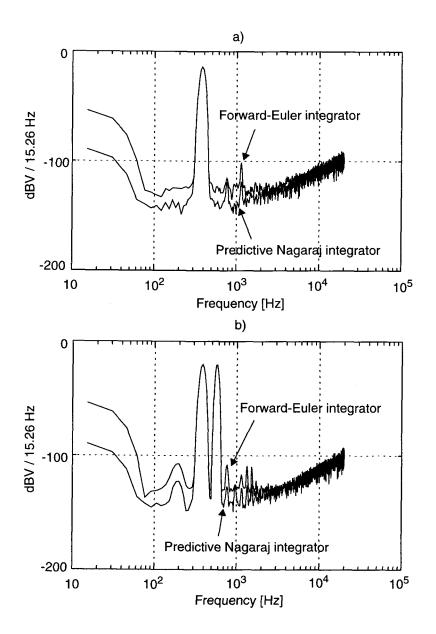

| 5.3           | Typical waveform for the output voltage of a SC integrator in a delta-sigma modulator                                                                                                                                                                                                                       | . 123       |

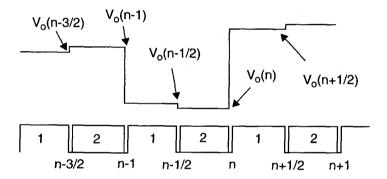

| 5.4           | Op-amp nonlinear dc gain characteristic as given by (5.17),<br>for $A_0 = 38 \text{ dB}$ , $\gamma_1 = 0.01 \text{ V}^{-1}$ and $\gamma_2 = 1.2 \text{ V}^{-2}$                                                                                                                                             | . 126       |

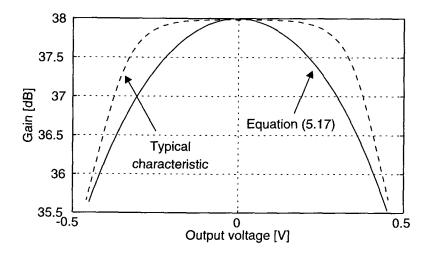

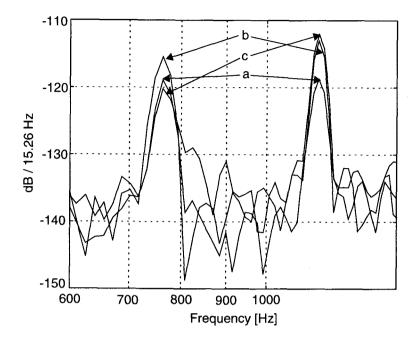

| 5.5           | Output spectra of a 2nd-order delta-sigma modulator when the input stage is a forward-Euler SC integrator and when the input stage is a predictive Nagaraj integrator                                                                                                                                       | . 127       |

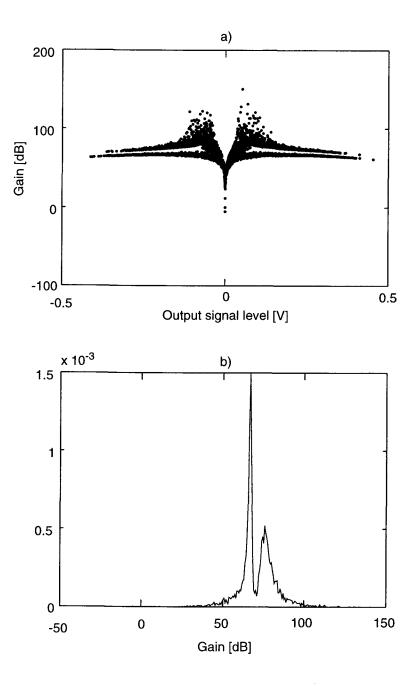

| 5.6           | Equivalent dc gain of the amplifier.<br>a) As a function of the output signal level.<br>b) Histogram of 5000 samples                                                                                                                                                                                        | . 129       |

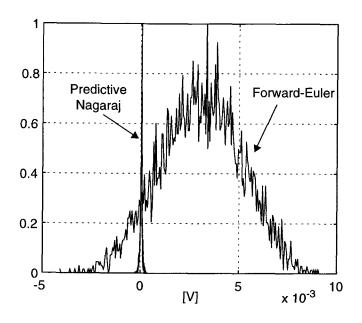

| 5.7           | Histograms of the virtual ground signal for a forward-Euler integrator<br>and a predictive Nagaraj integrator                                                                                                                                                                                               | . 131       |

| 5.8           | Magnified output spectrum of a 2nd-order delta-sigma modulator<br>(showing signal harmonics) when the input stage is a predictive Nagaraj<br>integrator                                                                                                                                                     | . 133       |

| <u>Figure</u> |                                                                                                                                                                                                         | Page |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

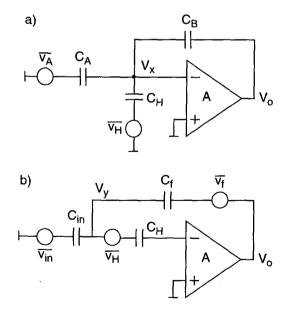

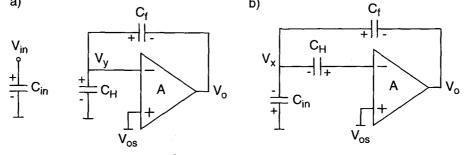

| 5.9           | Circuit configuration of a predictive Nagaraj integrator in the a) prediction phase and the b) integration phase                                                                                        | 134  |

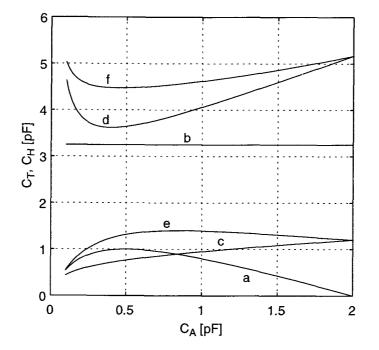

| 5.10          | Value of the holding capacitor $C_H$ required to achieve equality of the capacitive loads during prediction and integration in a predictive Nagaraj integrator, and the resulting equivalent load $C_T$ | 139  |

| 5.11          | AC model of a predictive Nagaraj integrator showing the $kT/C$ noise sources during a) prediction phase and b) integration phase                                                                        | 141  |

### LIST OF TABLES

| <u>Table</u> | Ī                                                                                                                                                   | Page |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.1          | Comparison of the performance of reported work on LV/LP delta-sigma modulators                                                                      | 28   |

| 4.1          | First stage amplifier and bias circuit device aspect ratios                                                                                         | 101  |

| 4.2          | Measured performance characteristics of the modulator                                                                                               | 109  |

| 4.3          | Structure of the current consumption in the modulator                                                                                               | 109  |

| 5.1          | Gain and pole errors for the SC integrators shown in Figure 5.2                                                                                     | 119  |

| 5.2          | Residual voltage error due to the amplifier finite dc gain for a forward-Euler integrator, a Nagaraj integrator and a predictive Nagaraj integrator | 124  |

### LIST OF APPENDICES

| <u>Appen</u> | <u>dix</u>                                            | Page |

|--------------|-------------------------------------------------------|------|

| А            | AC Analysis of a single-stage operational amplifier   | 156  |

| В            | Modeling of a fully-differential SC integrator        | 163  |

| С            | Operation and voltage efficiency of a voltage doubler | 184  |

| D            | Analysis of SC integrators employing CDS techniques   | 187  |

### LIST OF APPENDIX FIGURES

| <u>Figure</u> |                                                                                                                                                         | <u>Page</u> |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| A.1           | Small-signal model of a single-pole amplifier<br>a) in a stand-alone configuration. b) in a feedback configuration                                      | 156         |

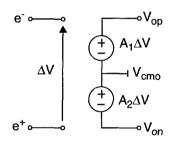

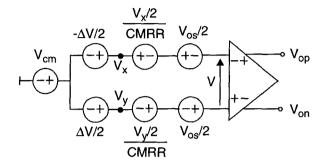

| B.1           | Basic model of a fully-differential op-amp with finite dc gain                                                                                          | 164         |

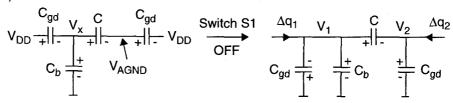

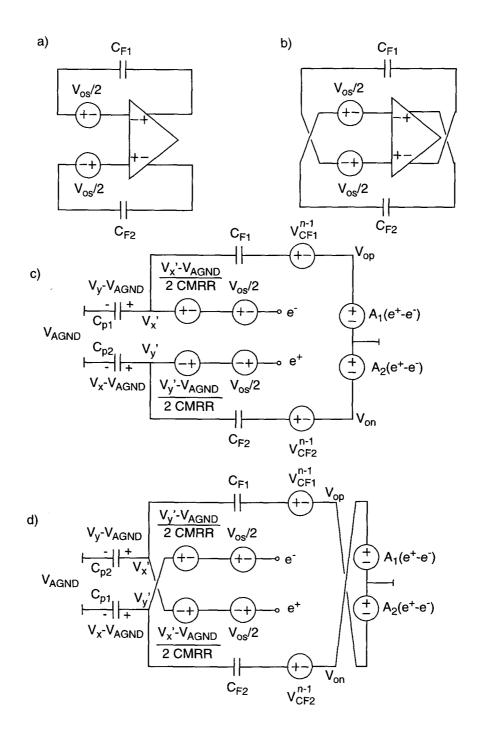

| B.2           | Modeling of the op-amp dc offset<br>and common-mode rejection ratio ( <i>CMRR</i> )                                                                     | 165         |

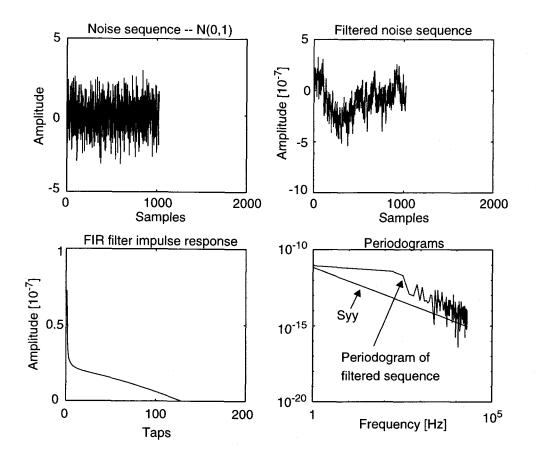

| <b>B</b> .3   | Generation of a noise time signal for simulation of flicker noise,<br>from a filtered pseudo-random white noise sequence                                | 167         |

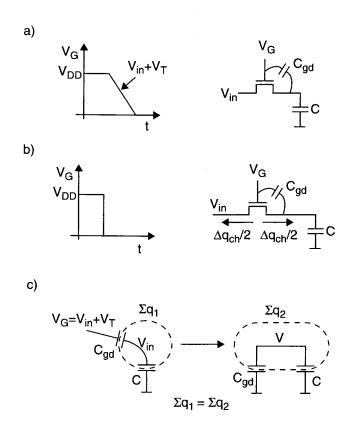

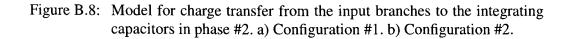

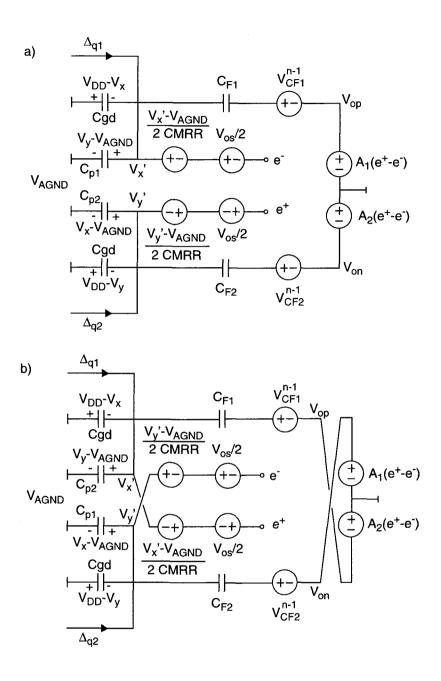

| B.4           | Modeling of the clock charge injection. a) Slow-switching mode.<br>b) Fast switching-mode. c) Charge conservation principle                             | 168         |

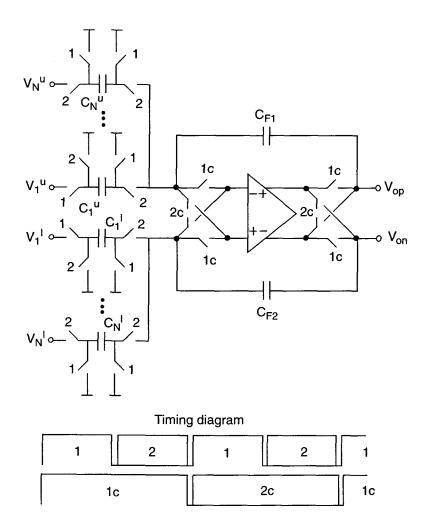

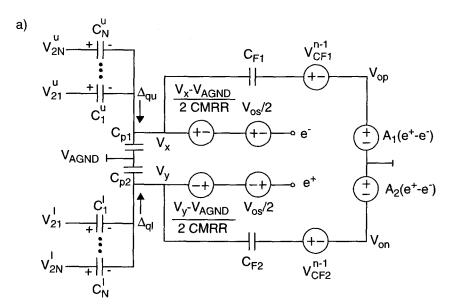

| B.5           | Circuit diagram of a generalized fully-differential switched-capacitor integrator with chopper stabilization                                            | 170         |

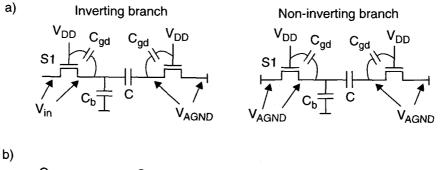

| <b>B</b> .6   | <ul><li>a) Inverting and non-inverting SC branches during phase #1.</li><li>b) Branch configuration for charge injection when switch S1 opens</li></ul> | 172         |

| B.7           | Possible configurations when chopper stabilization is used                                                                                              | 174         |

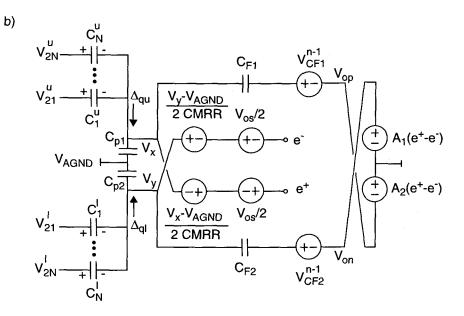

| B.8           | Model for charge transfer from the input branches to the integrating capacitors in phase #2                                                             | 177         |

| B.9           | Model for clock charge injection in the end of phase #2                                                                                                 | 179         |

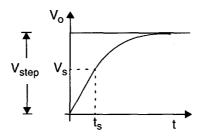

| B.10          | Transient response of an amplifier to a step voltage, showing slewing behavior $(t < t_s)$ and linear settling behavior $t > t_s$                       | 182         |

| <b>C</b> .1   | Voltage doubler                                                                                                                                         | 185         |

| D.1           | Nagaraj integrator and timing diagram                                                                                                                   | 188         |

| D.2           | Predictive Nagaraj integrator and timing diagram                                                                                                        | 192         |

To my parents.

Aos meus pais.

### Improved Design Techniques for Low-Voltage Low-Power Switched-Capacitor Delta-Sigma Modulators

### **1. INTRODUCTION**

The rapidly decreasing minimum feature device size in CMOS technologies permits the integration of a larger number of devices, and hence more signal processing functions. Due to their low sensitivity to noise and process variations, digital signal processing (DSP) techniques have become a favorite in the implementation of such functions. Moreover, digital processors have achieved a state of significant sophistication and efficiency, which strongly supports the drive towards digital solutions. However, a fully digital implementation is usually not possible, since most signals occur in analog form. This places considerable emphasis on the implementation of the interfaces between the two worlds. The devices which implement these interfaces are called analog-to-digital (A/D), and digital-to-analog (D/A) converters (ADC's and DAC's, respectively). There are many requirements on these interfaces:

- They must be compatible with high-density integrated solutions, if possible in digital technologies.

- Many digital solutions require high-performance A/D converters, and possibly high-speed operation.

- The interfaces must dissipate low power, a particularly important aspect in portable communication devices.

- The utilization of submicron technologies forces the utilization of lower power supply voltages, which complicates all aspects of the design.

Various techniques have been proposed to implement A/D and D/A interfaces [1]. The choice of one over another depends on the application and the performance requirements for that application. Dynamic range (DR), linearity and speed are perhaps the most common parameters in the design of such systems. Delta-sigma modulation is a widely adopted technique in moderate-speed, high-performance applications. It permits relaxed component performance requirements, and can provide very high dynamic range for moderate-speed applications. The purpose of this work is not to study or analyze in detail the various methods of signal conversion, or even the structures employing the delta-sigma technique (the literature on this topic is vast [2][3]). Rather, we concentrate on two important aspects of the integration of these A/D and D/A interfaces: low-voltage (LV) operation and low power (LP) dissipation, with the focus on delta-sigma modulators.

The topic of LV/LP mixed-signal design has recently received much attention, driven by technological and economical factors. Two key aspects are: 1) modern submicron CMOS processes cannot handle large power supply voltages, and 2) lower production and testing costs can be achieved when analog and digital blocks are integrated on the same die. Unfortunately, such integration raises problems associated with the performance of the analog blocks (substrate noise coupling), and also the lower power supply voltage makes the task of achieving a high dynamic range quite difficult. Since the maximum amplitude of the input signal is limited by the value of the power supply voltage, the only approach to increasing the DR is to reduce the noise floor. This solution has severe repercussions in terms of power dissipation. These topics, and others, will be further expanded in the following chapters.

#### **1.1 OBJECTIVE**

The objective of this dissertation is to investigate the constraints which arise when switched-capacitor (SC) delta-sigma modulators are designed for low-voltage operation, targeting also low power dissipation, and to propose methods of improving the performance and optimizing for low power dissipation. This is accomplished by identifying critical elements whose performance can lead to increased power dissipation, as well as the fundamental limitations of available analog circuit techniques (Chapter 3). A prototype was designed and fabricated, which reflected these findings, and therefore exhibited good performance and nearly optimum power dissipation (Chapter 4).

One of the key performance parameters is the dc gain of the amplifier in the first stage; it should be high. This is necessary for high linearity and low quantization noise leakage (Chapters 2 and 3). In low-voltage operation, it may become impractical to use conventional topologies employing cascoding techniques (folded-cascode, telescopic cascode) which provide high gain in one single stage. Rather, cascaded structures have to be used. The disadvantage of the latter is the necessity for frequency compensation which results in increased power dissipation. Hence, another objective of this work is to exploit techniques, in the context of delta-sigma modulators, which compensate for the open-loop gain characteristic of the amplifier (dc value and nonlinearity), thus permitting the utilization of single-stage low-gain topologies. Predictive correlated double sampling is one of such techniques. It will be analyzed in Chapter 5.

#### **1.2 THESIS ORGANIZATION**

This dissertation is organized in six chapters, the first of which is this introduction. In it, the objectives of this dissertation, its organization and contributions are presented.

Chapter 2 extends the background and motivation touched upon in Chapter 1. The power dissipation in digital and analog circuits is addressed, and the implications of lowering the power supply voltage are discussed. Delta-sigma modulation is introduced and its performance metrics presented. Fundamental limits to power dissipation are derived, and a figure-of-merit for delta-sigma modulators proposed. This figure-of-merit is used to compare the performance of recently proposed devices in the area of LV/LP deltasigma modulators.

Chapter 3 analyzes in detail the power and voltage constraints in a second-order delta-sigma modulator. Design criteria will be derived to minimize the power dissipation. The contribution of the amplifiers, in the context of performance requisites, towards the total power dissipation will be analyzed in detail.

Chapter 4 presents the design of a second-order switched-capacitor delta-sigma modulator intended for voice applications, based on the results of Chapter 3. This device was fabricated, and it provided low power dissipation and high performance even though operating from a low (1.8 V) power supply. Issues related to designing switched-capacitor circuits in a low-voltage environment are addressed as well.

Chapter 5 explores predictive correlated double sampling as a means of achieving good linearity and low power dissipation in low-voltage moderate-performance deltasigma modulators. The technique reduces the effect of the open-loop nonlinearity characteristic of the amplifier, thereby allowing the utilization of single-stage low-gain structures. Single-stage amplifiers require no compensation other than their load, with significant reduction in the power dissipation. Their noise performance is also analyzed. Chapter 5 presents also design criteria for delta-sigma modulators employing predictive correlated double sampling, and identifies areas of potential application. Simulations illustrate the functionality of the technique.

Chapter 6 presents the conclusions of this dissertation and proposes new directions for future work.

4

#### **1.3 ORIGINAL CONTRIBUTIONS OF THE THESIS**

The research described in this dissertation includes the following original results:

- A systematic analysis of voltage and power constraints in a switched-capacitor second-order delta-sigma modulator, and optimization criteria for the design of such structures. Based on this theory a prototype was designed and fabricated. It provided an unequaled combination of high performance and low power dissipation [31].

- A novel and useful figure-of-merit for delta-sigma modulators, which permits the evaluation of the power efficiency for a given performance.

- An analysis of predictive correlated double sampling in SC integrators, and of the design criteria and noise performance of structures employing such techniques.

# 2. GENERAL DESIGN CONSIDERATIONS FOR LV/LP $\Delta\Sigma$ MODULATORS

This chapter provides the motivation for designing integrated systems with low supply voltages and reduced power dissipation. This motivation is driven by technological factors, in particular the necessity of integrating a large number of devices and functional blocks. The delta-sigma technique is also introduced, and discussed briefly in a qualitative context, so as to provide a first insight into its characteristics. Performance metrics for delta-sigma modulators are discussed to introduce the terminology used in the remainder of the text. A more detailed and formal analysis of a generalized delta-sigma structure is presented later in order to consolidate the material introduced earlier, and provide a better understanding of the performance requirements in such structures. This section lays the foundations for a more rigorous analysis of power and voltage constraints in a delta-sigma modulator, to be given in Chapter 3. The (lower) fundamental limits to power dissipation are also derived, under the assumption of a dominant thermal noise. Based on these results, a figure-of-merit for delta-sigma modulators is proposed, which can be utilized to estimate the power efficiency of different structures. Using this figure-of-merit, a comparison of representative implementations is presented.

#### 2.1 MOTIVATION FOR LV/LP DESIGN

Why is it necessary to design for low-voltage operation, and how does this relate to power dissipation? The motivation lies in factors of technological nature, as well as application-related and market-demand factors.

As technology evolves towards submicron and deep-submicron feature sizes, the oxide thickness of the MOS devices decreases as well. To avoid punchthrough and p-n junction breakdown, the intensity of the electric field has to be reduced. For example, a standard 0.8  $\mu$ m CMOS process can withstand a maximum *sustained* power supply

voltage of about 5.5 V, but devices made using a 0.5  $\mu$ m CMOS process can only tolerate about 3.5 V. (They can, however, withstand larger voltage *transients*.) It is possible to develop a 0.5  $\mu$ m or smaller feature size process which will still withstand a 5 V supply. This can be done by increasing the doping of the substrate which results in thinner depletion regions around the drain and source diffusions, hence mitigating the risk of punchthrough. Although a higher doping concentration reduces the p-n junction breakdown voltage  $V_{BD}$ , it increases the punchthrough voltage  $V_P$  The rate at which  $V_{BD}$ decreases is, however, lower than the rate at which  $V_P$  increases, and hence some trade-off can be achieved. Eventually, as the feature size is further reduced junction breakdown becomes dominant and the power supply voltage must be reduced. This aspect clearly points towards the need to design systems capable of operating from power supply voltages lower than the typical 5 V.

In fact, this reduction of the power supply voltage is not only necessary but also desirable. In digital circuits with a high level of switching activity, the power dissipated is essentially dynamic, that is, associated with charging and discharging various capacitors. The expression for the dynamic power dissipation assumes the general form

$$P = p \cdot C \cdot V^2 \cdot f_s \tag{2.1}$$

where p is the activity factor (dependent on the statistics of the signal), and  $f_s$  is the switching frequency. In most digital circuits, the voltages representing the "high" and "low" states coincide with the power supply rails, i.e.,  $V_{DD}$  and ground, and hence V equals  $V_{DD}$ . Since the power is proportional to the square of the voltage step V, decreasing that step from, say, 5 V to 3 V, results in a reduction of the power dissipation by a factor of about 2.8. This result is important not only in terms of lower overall power dissipation but also in terms of power dissipation *density*, as submicron processes allow the integration of a larger number of functions. For reliability, the thermal density should be kept low. A side

benefit of using smaller feature sizes is that the parasitic switched capacitances contributing to C are also smaller, and hence so is the power dissipation.

It would seem that the power dissipation could be reduced to tolerable values simply by reducing the power supply voltage. In practice, various factors prevent this from happening, or at least complicate the trade-off. For instance, a lower value of the power supply voltage impacts the delay of the cells and hence reduces the speed of operation. The loss in speed can be compensated if the threshold voltages are also reduced, or if parallel or pipelined architectures are utilized [4][5]. Equation (2.1) suggests, however, that the total power can be minimized in other ways, such as by minimizing the activity and the parasitic switched capacitance. The activity can be reduced by devising algorithms which require fewer computation cycles, and by using event-driven blocks which are de-activated when not in use [6][7]. The capacitance can be reduced by making the digital processing elements (architecture, logic cells, layout) as simple and small as possible [4], and by using branch-based logic [8][9]. Nevertheless, lowering the value of the power supply voltage is still the most efficient way of reducing the power dissipation in digital circuits.

The subject of power optimization in digital circuits is beyond the scope of this work. It serves, however, to provide insight into one of the most important driving forces for designing for LV/LP conditions. The question at this point is "What about the power dissipation of analog circuits?" The answer, and this is the subject of the remainder of this work, is that lowering the power supply voltage usually does not yield a lower power dissipation. Although moving to submicron processes (small feature sizes, thin oxide) inherently provides the capability for lower power dissipation due to smaller parasitic capacitances and larger transconductances, the performance of analog circuits is often measured also in terms of dynamic range, that is, the ratio of the maximum signal power to the noise floor. Decreasing  $V_{DD}$  limits the maximum amplitude of the input signal which can be accommodated by the circuit, but it does not reduce the noise floor. To attain a lower noise floor, larger capacitances, hence larger transconductances, have to be

realized, which dramatically increase the power dissipation. We will return to this topic later in this chapter. So, why design analog circuits for low-voltage operation? The answer is cost. The present trend is to integrate analog and digital functionality on the same die, to reduce the cost of processing and packaging with single-chip solutions. However, if analog and digital circuits are to coexist on the same substrate the former has to be able to operate from the same low power supply voltage as the latter.

The proliferation of portable communication devices (laptop computers, cellular phones, etc.) constitutes another incentive for designing for LV/LP. Low voltage translates into smaller, lighter and cheaper batteries. Low power means longer battery lifetime, hence a reduced cost of operation and increased dependability. Although these are essentially market-related issues, they often constitute the major driving force for pursuing new design directions.

At this point, it should be clear why designing for low-voltage operation and for low power dissipation is a topic of great importance. The main issues are cost and dependability. This is what the industry and the consumer sees and wants. In this work we convert this simple requirement into more specific ones, involving low-power dissipation and low-voltage operation, dynamic range, reference voltage and noise floor, dynamic power and static power, power supply voltage and CMOS switches, power supply voltage and bandwidth, among others.

#### 2.2 THE DELTA-SIGMA TECHNIQUE

Delta-sigma ( $\Delta\Sigma$ ) modulation is a data conversion technique which has gained significant popularity recently in the implementation of A/D and D/A interfaces [2][3]. By trading resolution in amplitude for resolution in time, the requirements on the analog components are much relaxed. It is intuitively obvious that the fewer samples one takes from a given signal, the more accurate those samples and the processing elements have to be. If instead the signal is sampled at a very high rate, significant redundancy is introduced. Hence, even if the samples are corrupted by noise, or processed with less accuracy, it is clear that if properly averaged, the effect of those errors can be made negligible. This requires a knowledge of the statistics of the input signal and of the noise.

In delta-sigma modulation, this redundancy is exploited in two ways. One is by sampling the input signal at a rate  $f_s$  much higher than the Nyquist rate (this is called oversampling); the power of signals with spectral content extending beyond  $f_s/2$  (such as white noise) will therefore be distributed between dc and  $f_s$  [2][10]. This means that in the band of interest (input signal band), the spectral floor due to the noise will be lower. If the energy falling outside the signal band is removed by filtering, the signal-to-noise ratio (SNR) improves. (This filtering in fact implements the averaging process mentioned above.) The other way is by making use of feedback. It is known that feedback techniques can radically change properties of open-loop systems which might otherwise be of little use due to nonlinearity and other imperfections. In a delta-sigma modulator, a filter (called the loop filter) with high gain in the band of interest and a quantizer constitute the forward path of a feedback system (Figure 2.1). Due to the feedback loop, the spectral components of any signal injected or applied at nodes in the forward branch following the output of the loop filter will be attenuated by the gain of the filter at those frequencies. For the system shown in Figure 2.1, if we assume for simplicity that the quantizer linearly adds a noise component  $E_Q$  to the signal at the output of the loop filter, one can easily arrive at the following expression for the output of the system in the frequency (Laplaceor z-transform) domain:

$$Y = \frac{H}{1+H} \cdot X + \frac{1}{1+H} \cdot E_Q$$

(2.2)

If the loop filter has a very high gain  $(|H| \gg 1)$  in a range of frequencies, then the signal transfer function is approximately unity in that band, whereas the noise components in the same range are greatly attenuated, resulting in increased *SNR*. This is commonly

called in the context of delta-sigma modulation, of *noise shaping*, and is illustrated in Figure 2.2, where  $E_Q$  is assumed to have a flat power spectral density (*PSD*). Hence, the effect of the feedback loop can be significantly more beneficial than that of oversampling alone, since it effectively reduces the noise power in the band of interest. The out-of-band noise, however, is not attenuated and has to be removed by subsequent filtering.

Figure 2.1: Simplified block diagram of a delta-sigma modulator.

At this point, the potential of the delta-sigma technique should be clear. The most important feature is that the combined utilization of oversampling and feedback relaxes the requirements on blocks following the loop filter. Actual implementation of the loop filter may be by low-order sections with feedback, and possibly feedforward branches, for improved stability. In such cases, all noise appearing at any internal nodes following the *first stage* of the loop filter, when referred back to the input, will undergo some degree of filtering and becomes less important. In other words, one can tolerate noise of larger magnitude, and errors due to non-idealities of the active devices, without compromising the performance. This includes performing a coarse quantization of the signal, ultimately to one bit. Later in this chapter we will introduce performance metrics, and quantify the benefits originating from noise shaping and oversampling.

As shown in Figure 2.2, the spectral components of the noise falling inside the signal band are attenuated, compared to the original *PSD* of the noise. The same does not happen to those falling outside of the signal band. Indeed, those are amplified and need to be removed by a digital filter.

Figure 2.2: The concept of noise shaping.

The rate  $f_s$  of the output digital bit stream Y (Figure 2.1) is usually too high for complex digital post-processing, which would consequently require very complex circuitry and dissipate excessive power. Hence, the digital filter which follows the modulator implements the function of down-sampling as well. The combined filter and down-sampler is commonly (and somewhat loosely) known as *decimator* or *decimation filter*. The reduction of the sampling rate is usually accomplished in several stages, depending on the rejection characteristics of unwanted components of each block, and is accompanied by an increase in the wordlength. This is plausible since that was the original trade-off. Once the out-of-band noise has been removed, the oversampling ratio can be reduced and the wordlength has to be increased to represent the input signal accurately. The complexity of the decimator can be significant due to the large out-of-band noise energy that has to be removed. This is where one of the trade-offs takes place; the requirements for the analog blocks are relaxed, but a penalty has to be paid on the digital post-processing. Note, however, that this penalty is only in the complexity of the digital filter, which can be implemented with any desired accuracy, while the same cannot be said about analog blocks. The combination of a delta-sigma *modulator* and a *decimation filter* constitutes a delta-sigma data *converter* or ADC.

Since this technique exploits oversampling, it is not suited for very high-frequency and high-resolution applications. Some work targeting high-speed and low- to moderateresolution applications has been reported [12][13], but the delta-sigma technique finds its main niche in low- to moderate-speed, high-resolution applications, such as instrumentation [14], unconventional signal processing [15][16], and at voice [17] and audio range frequencies [18]. The latter are of particular importance in communications where high-performance, moderate-speed A/D and D/A interfaces are required. Due to its robustness, the delta-sigma technique is then typically the preferred choice.

#### 2.3 PERFORMANCE METRICS

Before we proceed, it is necessary to introduce appropriate performance metrics for delta-sigma *modulators*. Contrary to other conversion methods, the performance of a  $\Delta\Sigma$  modulator is better understood in terms of signal and noise spectra, signal-to-noise ratio and dynamic range, rather than the number of output bits. The reason lies in that the typical wordlength of the digital output of a delta-sigma modulator is *one*. (Moreover, there is not a one-to-one relation between the input and the output samples.) However, the *SNR* in the signal bandwidth can be very large, due to the noise shaping effect of the loop. For example, a flash ADC will take a sample of the input signal, quantize that sample and assign a digital code with wordlength N to the quantized value. The ADC is called an Nbit ADC. If the conversion is performed at the Nyquist rate, it can be shown that the *SNR* resulting from such quantization (for a sinusoidal input signal) can be approximated by

$$SNR_{dB} = 6.02 \cdot N + 1.76$$

(2.3)

14

Hence, a 10-bit ADC ideally displays a signal-to-noise ratio of about 62 dB, and a 16 bit ADC displays an *SNR* of about 98 dB. This concept is also used in delta-sigma modulators, where the signal-to-noise ratio is determined and "converted" to the equivalent bit accuracy or resolution. For instance, if the peak *SNR* is 98 dB, the modulator is called a 16-bit modulator, even if the output signal wordlength is unity. Note that this simply means that if the out-of-band noise would be completely eliminated, and the output rate reduced to the Nyquist rate, the maximum meaningful wordlength that could be used to represent the input signal is 16. The removal of the out-of-band noise and the reduction of the output rate constitute the function of the decimator. The wordlength of the digital output of a delta-sigma *converter* is not one, but the equivalent of the *SNR* in the signal band, or more.

We are now in a position to introduce and understand the metrics utilized in the evaluation of the performance of such systems. These metrics are illustrated graphically in Figure 2.3. Note that some of the following definitions have a scope which extends beyond delta-sigma modulation.

- Overload point,  $P_{MAX}$ , is the value of the input signal power which overloads (saturates) the modulator. At this point, the slope of the SNR curve <u>reduces</u>, and eventually becomes negative with further increase of the input signal level.

- Total dynamic range, or simply dynamic range, DR, is the ratio between the maximum input signal power  $P_{MAX}$ , and the lowest input signal power  $P_{MIN}$  that can be discriminated from the noise floor ( $P_{MIN}$  is also referred to as *resolution*).

- Instantaneous dynamic range, IDR, defined as  $IDR = SNR_X P_X$  (all quantities in decibel), where  $P_X$  is the input signal power (with appropriate reference), sufficiently small that there are no distortion or overloading effects (for instance,  $P_X = -60 \text{ dB}$ ), and  $SNR_X$  the signal-to-noise ratio for that input signal level. The following relation holds:  $IDR \ge DR$ .

- Peak signal-to-noise ratio,  $SNR_{Peak}$ , is the maximum signal-to-noise ratio that can be obtained. Strictly speaking, this maximum may occur for values of the input signal level larger than  $P_{MAX}$ . The following relation holds:  $SNR_{Peak} \leq -P_{MIN}$ .

Figure 2.3: Performance metrics used in connection with delta-sigma modulators.

Both the peak signal-to-noise ratio and the dynamic range are used to express the performance of a delta-sigma modulator, and are quantified in decibels or bits, as

discussed above. Also, it is common to normalize the curve in Figure 2.3 to the value of the reference voltage  $V_{REF}$ , in which case the scale is in dBr (0 dB corresponds to the power of a sinewave with amplitude  $V_{REF}$ ). We can now proceed with a more detailed analysis of the performance requirements of a delta-sigma modulator.

### 2.4 GENERAL PERFORMANCE REQUIREMENTS IN A $\Delta\Sigma$ MODULATOR

In section 2.2 we introduced the delta-sigma technique, and discussed how feedback techniques, in conjunction with oversampling, could be used to selectively reduce the noise power in a band of interest. In this section we quantify the benefits of such techniques, and infer the implications in terms of performance requirements. This analysis will be refined for a second-order structure in chapter 3.

Consider Figure 2.4. It illustrates an idealization of a single-loop delta-sigma modulator with arbitrary order. Note that the loop filter transfer function is expressed in terms of z-transform, because in this work we do not contemplate continuous-time implementations of such structures. Even continuous-time implementations cannot be asynchronous, hence most of the discussion that follows still applies. Another aspect that is new relative to Figure 2.1, but which was mentioned at the time, is the implementation of the loop filter. The loop filter consists of a cascade of accumulators (integrators in the continuous-time domain), with multiple feedback loops. An accumulator displays a lowpass type of transfer function, and for that reason the structure is said to be a low-pass delta-sigma modulator. Analogously, band-pass transfer functions can be implemented to process band-pass signals [19]. The feedback loops are required for stability purposes, and in most systems with order equal or larger than three, feedforward branches are required as well to realize stabilizing zeros in the transfer function. (The feedforward branches have also been used to realize a Chebyshev transfer function [11].) This is an aspect linked to the implementation of such systems, and does not greatly influence the following analysis which concentrates on the spectral properties of the signals.

Figure 2.4: Simplified block diagram of an idealized  $\Delta\Sigma$  modulator of arbitrary order.

Also new to Figure 2.1 is the presence of an A/D and a D/A converter. The A/D converter performs the function of the quantizer, and converts the result into a digital word. Typically, 1-bit quantization is utilized in delta-sigma, and the A/D converter consists of a comparator (quantizer) followed by a latch (A/D conversion). The D/A converter changes the output digital word into an analog representation of that signal. In the case of single-bit quantization, the D/A converter consists of a switch which selects  $+V_{REF}$  or  $-V_{REF}$  (or the equivalent, if only a single reference voltage is available).

Following the approach used in connection with Figure 2.1, it is assumed that the A/D converter introduces a component of quantization noise  $e_Q$  which adds to the output signal of the previous stage. Note that this is correct, as no assumption was made regarding the properties of the noise signal. For simplicity of analysis,  $e_Q$  is commonly considered to be white, uncorrelated with the input signal (linear analysis). For structures of first and second order, this is markedly untrue [20][21][22], and caution has to be exercised when estimating the noise performance. Nevertheless, the model provides a good insight on the functionality of these structures. The sources  $e_i$  denote any addition of noise or error to the signal path. They represent the input-referred noise and nonidealities of stage *i*, nonidealities in the feedback path from the D/A converter, and other sources of noise such as thermal noise, clock charge injection and substrate noise; anything that is

applied or injected at node *i*. At the output end,  $e_i$  coincides with the quantization noise  $e_Q$ . The analysis of the linearized model yields

$$Y(z) = z^{-N} \cdot X(z) + (1 - z^{-1})^{N} \cdot E_Q(z)$$

$$+ \sum_{i=1}^{N} (1 - z^{-1})^{i-1} \cdot z^{-(N+1-i)} \cdot E_i(z)$$

(2.4)

The first line in (2.4) contains the term in the input signal X and the term in the quantization noise  $E_Q$ . The second line aggregates all the remaining sources of noise  $e_i$ . The transfer function from noise source  $e_i$  to the output Y is

$$H_i(z) = \left(1 - z^{-1}\right)^{i-1}$$

(2.5)

a power of the difference between successive samples of noise. The exponent varies from 1 for the leftmost source (same as the input signal), to N-1 for the rightmost one. If the signal being sampled (noise in this case) is rapidly varying in time, the difference between two consecutive samples can yield a large value, because the samples can differ by a large amount. If the signal is slowly varying, the two consecutive samples will look alike and the difference will be small (particularly if oversampling is being used). This means that taking the difference between two consecutive samples is equivalent to performing a high-pass filtering function. Taking a power of the difference corresponds to a more elaborate filtering, with more coefficients. Notice that due to the delays in the system, it has memory, and higher-order systems make use of that memory by developing inherently more rigorous estimates of the signal, through proper averaging of noise samples. This is the essence of delta-sigma modulation.

To better understand all implications, it is useful to analyze in more detail equation (2.5). Let us assume that the oversampling ratio OSR (defined as the ratio between the sampling frequency and the Nyquist sampling rate) is very high (two orders of magnitude is a typical value). The absolute value of the transfer function in (2.5) can then be approximated according to

$$\left|H_{i}(\omega)\right| = \left|1 - \exp\left(-j \cdot \omega T_{S}\right)\right|^{i-1} \cong \left(\omega T_{S}\right)^{i-1}$$

$$(2.6)$$

where  $T_S$  is the inverse of the sampling frequency, and  $\omega$  is the variable angular frequency. The noise power in the signal band [-bw, bw] (*bw* is a normalized frequency, therefore comprised between 0 and  $\pi$ ) can be calculated by integrating the output power spectral density due to the noise sources [23]:

$$P_{i} = \frac{1}{2 \cdot \pi} \int_{bw}^{bw} \left( S_{ei}(\omega) \cdot \left| H_{i}(\omega) \right|^{2} \right) d\omega$$

(2.7)

where  $S_{ei}$  represents the *PSD* of the noise originated by source  $e_i$ . We indicated above that the sources  $e_i$  can represent any type of noise. This generality poses difficulty in evaluating the integral in (2.7). However, assuming that the  $e_i$  refer to sources of white noise, with constant power, the task of evaluating the integral is greatly simplified, and the insight gained quite significant. The auto-correlation function of white noise is a delta function [23]. Hence its *PSD* is constant with frequency, and uniformly distributed between 0 hertz and the sampling frequency (positive frequency representation). Since the power is constant, the level of the *PSD* is inversely proportional to the sampling frequency:  $S_{ei} \propto 1/f_s$ . (This result does not apply if the noise signal is *oversampled*.) In other words, if the sampling frequency doubles, the *PSD* of the noise decreases by a factor of two, or 3.01 dB. Since the band of interest is only a fraction of the whole spectrum, the noise power in that fraction is smaller by a factor of two as well. Inserting the dependency above with  $f_s$  in (2.7) one easily arrives at

$$P_i \propto \left(\frac{\pi}{OSR}\right)^{2i-1} \tag{2.8}$$

This result is of paramount importance as it combines the effects of oversampling and noise shaping. The former is accounted for through OSR and the latter through the exponent. For instance, for noise appearing at the input of the first and second stages (i=1, 2) one obtains

$$P_1 \propto \frac{\pi}{OSR} \text{ and } P_2 \propto \left(\frac{\pi}{OSR}\right)^3$$

(2.9)

This result states that noise at the input stage benefits only from oversampling, whereas noise at the input of the second stage benefits from both oversampling and from noise shaping. More generally, it can be said that the noise power (at the output) with origin in source  $e_i$  (input of i<sup>th</sup> stage) is reduced by  $3.01 \cdot (2 \cdot i - 1)$  dB for each octave of increase in *OSR*, opposed to only 3.01 dB due to oversampling. From one stage to the following, the power is reduced by a factor proportional to  $(OSR/\pi)^2$ . Figure 2.5 plots the output power as given by (2.9), for three common values of the oversampling ratio. For the values of *OSR* indicated, the in-band noise power originating at the input stage, and superimposed to the input signal, is attenuated by 13 dB to 19 dB, as a result of oversampling. The in-band noise power originating at the input of the i<sup>th</sup> stage is attenuated by 26 dB to 38 dB, relative to the *previous* stage.

This discussion assumes that all noise sources are identical. If the same noise signal appears at the output with a power which depends on the location of the source in the loop, this is an indication that we can tolerate larger levels of noise at certain nodes without seriously compromising the performance (*SNR*). Namely, it becomes clear that the input stage determines to a large extent the overall performance of the system; here, noise and errors arising from element nonideal behavior can benefit, at most, from the oversampling. They are, otherwise, regarded as part of the input signal, with unity transfer

function to the output, and have to be minimized. The following stages, however, see their performance requirements much relaxed due to the noise shaping effect, especially if that noise is *not* broadband. Offset dc signals and flicker noise are virtually cancelled (the noise transfer function has at least one zero at dc). For this reason, a large fraction of the total power (typically more than 50%) is often dissipated in the first stage, since it requires larger capacitances to reduce the noise floor, hence larger transconductances and larger biasing currents. (A different approach to implementing delta-sigma modulators was recently proposed. It utilizes a passive loop filter, thereby placing the performance requirements -- speed, gain -- on the quantizer rather than the first stage [32].)

Figure 2.5: Attenuation of the noise power generated at the input of stage *i*.

Chapter 3 addresses in detail the power and voltage constraints in a second-order delta-sigma modulator, including the power dissipation of the amplifiers. Before we investigate this subject, it is pertinent to ask "What is the minimum power that can be dissipated?" The answer to this question varies according to the specifications of the

system, and with what limits the performance. Nevertheless, the best performance that can be obtained is determined by the purity of the input signal itself and the quality of the sampling process. If the sampling process does not introduce any error, then the ubiquitous thermal noise will be the limiting factor. The next section analyzes this issue.

#### 2.5 FUNDAMENTAL LIMITS TO POWER DISSIPATION

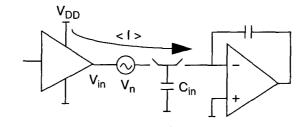

Figure 2.6 illustrates the sampling process that takes place at what could be the input stage of a delta-sigma modulator. The input signal  $V_{in}$  is sampled into a capacitor  $C_{in}$ . Due to the resistance of the switches, a noise voltage  $V_n$  is also stored in  $C_{in}$ . This noise is of thermal origin, and band-limited by the RC constant formed by the resistance of the switch and the sampling capacitor  $C_{in}$ . It can be shown [10] that the power of the resulting signal depends only on the size of the sampling capacitor, and on the absolute temperature T according to

$$N_{th} = \frac{kT}{C_{in}} \tag{2.10}$$

where k is the Boltzmann constant. Since the noise signal has a broad bandwidth (Lorentzian spectra display typical time constants in the order of  $10^{-14}$  s, the relaxation time in electron-electron scattering), it is undersampled, and only a fraction of the total power is contained in the signal band. That fraction is equal to the inverse of the oversampling ratio. Moreover, since the stored charge has to be transferred to the output through a second switch, another sample of noise is added to the stored value. Because the noise samples are uncorrelated, the powers of the corresponding signals add. Expression (2.11) gives therefore the in-band noise power:

$$N_{th, b} = \frac{2kT}{C_{in} \cdot OSR}$$

(2.11)

It is intuitive that the minimum power that is dissipated is associated with the process of sampling the input signal: the charging and discharging of the input capacitor. This transfer of charge over a fixed period of time  $(1/f_s)$  corresponds to having an average current flowing through a resistor [10], current which is drawn from the power supply. Hence the minimum dissipated power is given by

$$P_{MIN} = V_{DD} \cdot \langle I \rangle$$

$$= V_{DD} \cdot f_s \cdot \langle Q \rangle$$

$$= \alpha \cdot C_{in} \cdot V_{REF} \cdot V_{DD} \cdot f_s$$

(2.12)

where  $\alpha \cdot V_{REF}$  represents the maximum value of the input signal  $V_{in}$ , and  $\langle x \rangle$  denotes the average value of x. In this representation,  $\alpha$  is smaller than one and is an indication of a saturation mechanism. Frequently, the maximum value of the input signal which can be accommodated by a system is slightly lower than the reference voltage  $V_{REF}$ . In the case of a delta-sigma modulator, this situation is referred to as overloading, Section 2.3, and results from increased quantization noise in the signal band due to instability. Its value varies with the order and topology of the modulator.

Figure 2.6: Sampling the input signal.

Expression (2.12) gives the power which is dissipated in the process of sampling the input signal, but it does not provide any information about the purity of that sample. Except for the input capacitor  $C_{in}$ , all the variables in (2.12) are well known. As we saw earlier,  $C_{in}$  determines the noise signal which is superimposed to the input signal, and its value and the OSR define the noise floor, or the minimum input signal power which can be represented with an SNR larger than one (i.e., the resolution). Since the power is maximum when the signal reaches its maximum, we can relate the powers of both signal and noise through the parameter dynamic range (Section 2.3). For a sinusoidal signal,

$$DR = \frac{\text{Maximum Input Signal Power}}{\text{Integrated In-Band Noise Power}} = \frac{\frac{(\alpha \cdot V_{REF})^2}{2}}{\frac{2kT}{C_{in} \cdot OSR}}$$

(2.13)

This result can be used in (2.12), yielding

$$P_{MIN} = \frac{8 \cdot kT \cdot DR \cdot BW}{\alpha} \cdot \left(\frac{V_{DD}}{V_{REF}}\right)$$

(2.14)

where *BW* is the signal bandwidth, and we made use of  $F_S = 2 \cdot OSR \cdot BW$ . An optimum, or absolute minimum, is obtained when  $\alpha=1$  and  $V_{REF}=V_{DD}$  that is, when the system does not overload for signals weaker than the reference voltage, and the latter can be made as large as the power supply voltage. This absolute minimum is given by

$$P_{MIN} = 8 \cdot kT \cdot DR \cdot BW \tag{2.15}$$

A few remarks are in order:

- $P_{MIN}$  does not depend on the absolute value of the power supply voltage, but rather on how large the input signal can be made relative to that voltage.

- $P_{MIN}$  is constant for a constant dynamic range. This statement holds as long as the input capacitor size and the magnitude of the reference voltage can be exchanged to obtain the same *DR*, according to (2.13).

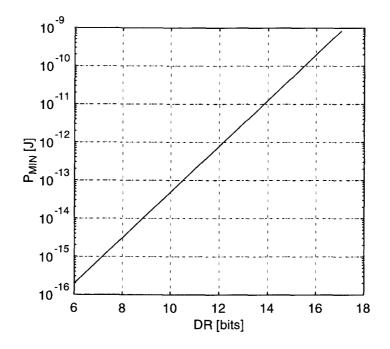

- $P_{MIN}$  increases by a factor of four for each added bit of dynamic range.

Figure 2.7 plots the minimum energy consumption as a function of the dynamic range in bits. In practice, the power dissipation is larger than the minimum given by (2.15) by three to five orders of magnitude. The reason for such large discrepancy is that expression (2.15) is representative only of the power dissipated in sampling the input signal, assuming that thermal noise is the only limitation. Other sources of noise, parasitic components and, most importantly, amplifier biasing currents, also contribute to the power dissipation. Static power dissipation from biasing currents will actually increase with decreasing power supply voltage. Assume, for instance, that a class A amplifier is used as the active element in the first stage of a delta-sigma modulator (Figure 2.6). The capacitive load of the amplifier will be in the order of magnitude of the sampling capacitor  $C_{in}$  the size of which, as we saw, is determined by the desired dynamic range. Hence, for a given gain-bandwidth product,

$$P_{STATIC} = V_{DD} \cdot I_{BIAS} \propto V_{DD} \cdot gm \propto V_{DD} \cdot C_{in}$$

(2.16)

Moreover, by (2.13), for a constant dynamic range,  $C_{in} \sim 1/V_{DD}^2$ . Introducing this result in (2.16) one concludes that  $P_{STATIC} \propto 1/V_{DD}$ . Therefore, in general, if the

performance (DR) in analog circuits is limited by thermal noise, the power dissipation *increases* with *decreasing* power supply voltage. This result is somewhat unsettling since integration of digital and analog blocks in the same fine-line IC die requires that the latter operate from lower power supply voltages. However, as we have just shown, the increase in power dissipation is inherent to the circuit techniques currently in use. There is, of course, space for numerous improvements, and in this work we will analyze a viable path in that direction.

Figure 2.7: Minimum energy consumption (power per bandwidth) as a function of the dynamic range.

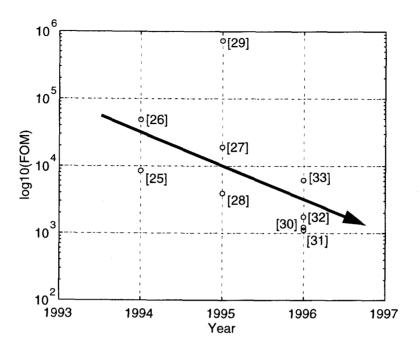

To provide insight on how far current implementations are from reaching the minimum power dissipation value expressed by (2.14) or (2.15), we propose a figure-of-merit *FOM* for delta-sigma modulators [24]. This figure-of-merit allows a coarse estimation of the performance and overall *efficiency* of a particular implementation. The

underlying assumption is that about half of the total power dissipated can be allocated to the first stage. We then define *FOM* as

$$FOM = \left(\frac{PWR}{8kT \cdot DR \cdot BW}\right) \left(\frac{V_{REF}}{V_{DD}}\right) \left(\frac{\alpha}{2}\right)$$

(2.17)

where *PWR* is the total power dissipation. Ideally, *FOM* should be close to one. Note that the parameters involved relate exclusively to performance, not to technology. Hence it provides a measure of the efficiency of utilization of the energy, to achieve such performance. The larger *FOM* is, the more <u>inefficient</u> the system.