### AN ABSTRACT OF THE THESIS OF

Shibashis Bhowmik for the degree of Doctor of Philosophy in Electrical and Computer Engineering presented on August 26, 1997.

Performance Optimization for Doubly-Fed Generation Systems Title: <sup>\*</sup>Redacted for Privacy

Abstract approved:\_\_\_\_\_\_ René Spée

A variable speed generation (VSG) system converts energy from a variable resource such as wind or water flow into variable rotational mechanical energy of a turbine or a similar device that converts translational kinetic energy into rotational mechanical energy. The mechanical energy is then converted into electrical energy by an electrical generator. Presently available and proposed generators include systems based mainly on de machines, synchronous and induction machine technology as well as reluctance machines. While extracting more energy from the resource, most proposed VSG systems suffer a cost disadvantage due to the required rating of the power electronic interface. This cost penalty may eventually render the additional energy capture meaningless. Thus, reducing the cost of the power electronic hardware is essential for VSG systems to achieve viable and competitive \$/kWh ratios when compared to fossil fuel-based generating systems.

A variable speed constant frequency (VSCF) system and controller are proposed that utilize a doubly-fed machine (DFM) as the energy conversion device. The system includes a power converter that provides the current excitation for the control winding of the DFM. Both the magnitude and frequency of the excitation is determined by an adaptive model-based controller which maximizes the power flow from the mechanical turbine to the electrical grid and reduces the generator losses by maintaining the maximum efficiency point throughout the mechanical input power range.

The proposed strategy has been experimentally verified in controlled laboratory conditions for a proof-of-concept brushless doubly-fed machine (BDFM) system of 1500 Watts power rating. Issues relating to power converter development and its incorporation in the system have been investigated. The controller and circuit design of a four quadrant, AC/AC power converter is presented and a novel sensorless current controller for the active rectifier stage is presented in detail.

While presented for a wind turbine application, the philosophy of the control algorithms are equally applicable for any variable speed application (motoring, generating, with and without gearbox, etc.) Also, the control can be augmented to not only maximize power and efficiency, but also provide for harmonic and reactive power compensation via the energy conversion system.

### **Performance Optimization**

### for Doubly-Fed Generation Systems

by

Shibashis Bhowmik

A Thesis Submitted

to

Oregon State University

In Partial Fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented August 26, 1997 Commencement June 1998 Doctor of Philosophy thesis of Shibashis Bhowmik presented on August 26, 1997

**Approved:**

Redacted for Privacy

Major professor representing Electrical and Computer Engineering

Redacted for Privacy

Chair of the Department of Electrical and Computer Engineering

Redacted for Privacy

Dean of Graduate School

I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request.

Redacted for Privacy Shibashis Bhowmik, Author

### Acknowledgements

It has been quite a few years at Oregon State University since my initiation into the M.S. program in the Department of Electrical and Computer Engineering in the fall of 1990. During this period, I was fortunate to have come across a spectrum of some of the most highly accomplished individuals as my gurus and some eagerly ambitious colleagues who, I am sure, would one day be well recognized in their vocation as well.

My special and sincere note of acknowledgement goes to Dr. René Spée, my mentor for almost all these years at Oregon State University. He has been a constant source of guidance, help and tutelage for me and has been, as in all other projects, a significant contributor towards the completion of my dissertation. Kudos is also due to Profs. G.C. Alexander and A.K. Wallace of the Energy Systems group. Despite their busy schedules, they were always willing to help whenever I needed it. My, brief but rewarding, association with Hian (Prof. H.K. Lauw), while working at Electronic Power Conditioning Inc., Corvallis, OR, had been, mostly, a didactic experience. He had me develop invaluable engineering skills and technical knowledge. I also thank Prof. W. Kolodziej for serving on my doctoral committee and for those elucidating control courses that he taught us.

Amongst my colleagues, the names that readily come to mind are those of Patrick Rochelle, Ashok (Dr. Ramchandran), Viren Javadekar, D.K. Ravi, Dongsheng (Dr. Zhou), Brian Wiley, Chris Brune, Bhanu (Dr. Gorti), Mike (Dr. Boger), Ernesto Weidenbrüg, Trey Kemp, Manfred Dittrich, Annabelle van Zyl, Alex Faveluke, Brian Koch and Bob Bellagh. I have benefited from each of them, at some time or the other, during these years. I would especially cherish the most recent memories of working with the last five, mentioned above, and the team spirit that prevailed all throughout the duration of that project. Here, I would also like to thank my very special friend Rita Wells who had been the Graduate Secretary throughout my stay at OSU. Rita has come to my rescue innumerable number of times. She always saved the day for me with a smile never letting me know that a favor was being done.

But I can never recount how much, my wife, Neeta helped me to see to the completion of this ordeal. I am indebted to her patience, her faith in me and her motivation allthroughtout. Likewise, a special note of thanks also go to my sister-in-law, Cheenu, for all the cheering and encouragement that she had provided me. Still, this work would never have been possible without the constant emotional support and understanding of my parents. I admire and respect them for their guidance and advice all throughout.

### Acknowledgements

The work described in this thesis has been supported by a consortium consisting of Electric Power Research Institute, Bonneville Power Administration and Puget Sound Power and Light. The author is appreciative of the funding which made this work possible.

### **Table of Contents**

|    |          |           |                                                                          | -        |

|----|----------|-----------|--------------------------------------------------------------------------|----------|

| 1. | Introduc | tion      |                                                                          | . 1      |

|    | 1.1.     | Basic wi  | nd turbine characteristics                                               | 3        |

|    |          | 1.1.1.    | Wind energy conversion                                                   | 3        |

|    |          | 1.1.2.    | Fixed and variable speed generation                                      | 5        |

|    |          | 1.1.3.    | Wind generation system design considerations                             | 7        |

|    | 1.2.     | Convers   | ion systems for wind power generation                                    | 9        |

|    |          | 1.2.1.    | Constant speed generators                                                | 9        |

|    |          | 1.2.2.    | Variable speed generators                                                | 11       |

|    |          | 1.2.3.    | Power converter considerations                                           | 15       |

|    |          | 1.2.4.    | Direct drive wind turbines                                               | 16       |

|    | 1.3.     | Wind tu   | rbine control systems                                                    | 17       |

|    |          | 1.3.1.    | Fixed speed generator control                                            | 17       |

|    |          | 1.3.2.    | Variable speed generator control                                         | 20       |

|    |          |           | 1.3.2.1.Singly-fed generator control1.3.2.2.Doubly-fed generator control | 21<br>23 |

|    |          | 1.3.3.    | Compensation of torque pulsations                                        | 24       |

|    | 1.4.     | Wind tu   | rbine operation                                                          | 25       |

|    | 1.5.     | Thesis c  | outline                                                                  | 28       |

| 2. | System   | and Conti | roller Design                                                            | 30       |

|    | 2.1.     | Control   | of DFM wind generator                                                    | 31       |

|    | 2.2.     | Optimiz   | ation control algorithm                                                  | 33       |

### <u>Page</u>

## Table of Contents (Continued)

3.

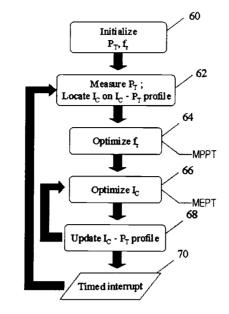

| 2.3.    | Flowcha   | rt implementation                                                                                                                                        | 5                |

|---------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|         | 2.3.1.    | Search-based controller                                                                                                                                  | 5                |

|         | 2.3.2.    | Wind speed estimation based controller                                                                                                                   | 3                |

| Convert | er Contro | ller Design45                                                                                                                                            | 5                |

| 3.1.    | Sensor-b  | pased rectifier controller46                                                                                                                             | 5                |

|         | 3.1.1.    | Sensor-based rectifier control algorithm47                                                                                                               | 7                |

|         |           | 3.1.1.1.Dc-bus voltage regulation483.1.1.2.Equivalent load conductance calculation493.1.1.3.Hysteresis current controller503.1.1.4.Switching algorithm51 | 9<br>0           |

|         | 3.1.2.    | Implementation of sensor-based controller                                                                                                                | 3                |

|         | 3.1.3.    | Experimental evaluation                                                                                                                                  | 4                |

| 3.2.    | Sensorle  | ss rectifier controller58                                                                                                                                | 8                |

|         | 3.2.1.    | Model-based predictive rectifier controller algorithm                                                                                                    | 9                |

|         |           | 3.2.1.1. Model development                                                                                                                               | 2<br>2<br>5<br>6 |

| 3.3.    | Remark    | s on the rectifier controllers7                                                                                                                          | 3                |

| 3.4.    | Inverter  | controller                                                                                                                                               | 5                |

## Table of Contents (Continued)

| 4. | System I | Implementation                                                                                                                                         | 77  |

|----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | 4.1.     | Wind turbine model development                                                                                                                         | 79  |

|    |          | 4.1.1. Wind turbine emulator                                                                                                                           | 80  |

|    |          | 4.1.2. Speed controller                                                                                                                                | 83  |

|    |          | 4.1.3. Torque controller                                                                                                                               | 83  |

|    | 4.2.     | BDFM generator                                                                                                                                         | 84  |

|    |          | 4.2.1. Features of a BDFM drive                                                                                                                        | 84  |

|    |          | 4.2.2. Generator design                                                                                                                                | 85  |

|    |          | 4.2.3. Characterization of the generator                                                                                                               | 86  |

|    | 4.3.     | Power converter implementation                                                                                                                         | 90  |

|    |          | 4.3.1. Converter components                                                                                                                            | 90  |

|    |          | 4.3.2. Converter protection                                                                                                                            | 92  |

|    |          | <ul><li>4.3.2.1. Driver level protection</li><li>4.3.2.2. Converter system level protection</li><li>4.3.2.3. Rectifier code-level protection</li></ul> | 92  |

|    | 44       | System controller implementation                                                                                                                       |     |

|    |          | Data acquisition                                                                                                                                       |     |

| 5. |          | Controller Evaluation                                                                                                                                  |     |

| 5. | 5.1.     |                                                                                                                                                        |     |

|    | 5.2.     |                                                                                                                                                        |     |

|    |          |                                                                                                                                                        |     |

|    | 5.3.     | Power distribution                                                                                                                                     | 101 |

## Table of Contents (Continued)

| 6. Conclusions and Recommendations104                          |

|----------------------------------------------------------------|

| 6.1. Salient features of thesis104                             |

| 6.2. Recommendations for future work106                        |

| Bibliography108                                                |

| Appendices113                                                  |

| Appendix A. Converter Controller Source Code114                |

| A.1Rectifier code114A.2Protection logic167                     |

| Appendix B. Performance Optimization Controller Source Code176 |

| <ul> <li>B.1 Optimization controller software</li></ul>        |

| Appendix C. Wind Turbine Emulator Source Code                  |

| Appendix D. Data Acquisition System Source Code                |

## List of Figures

| <u>Figure</u> Page                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1 Power coefficient of a 100 kW wind turbine                                                                                                                                             |

| <b>1.2</b> Variable and fixed speed power and speed characteristics of a 100 kW turbine7                                                                                                   |

| <ul><li>1.3 Energy conversion systems for variable speed generation: (a) synchronous,</li><li>(b) wound rotor induction, (c) cage rotor induction and (d) brushless doubly-fed12</li></ul> |

| <b>1.4</b> Simplified wind turbine (a) mechanical model and (b) block diagram, typically utilized for determination of mechanical system resonances and responses                          |

| <b>1.5</b> Sample annual wind speed distribution, illustrating the Rayleigh distribution of wind speeds                                                                                    |

| 1.6 Power extraction from wind using VSCF and CSCF systems                                                                                                                                 |

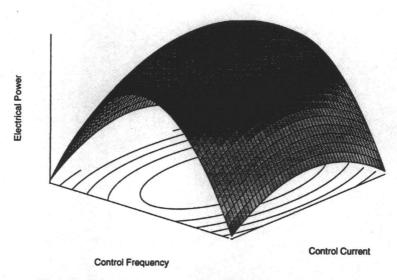

| 2.1 Conceptual representation of the VSG optimization controller as a three-<br>dimensional problem                                                                                        |

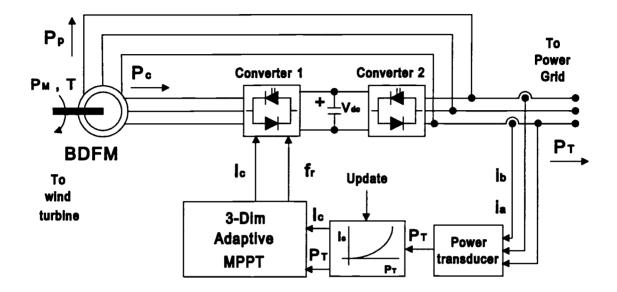

| <b>2.2</b> Block diagram representation of the controller in a wind generation application33                                                                                               |

| <b>2.3</b> Generalized flowchart representation of the proposed optimization algorithm                                                                                                     |

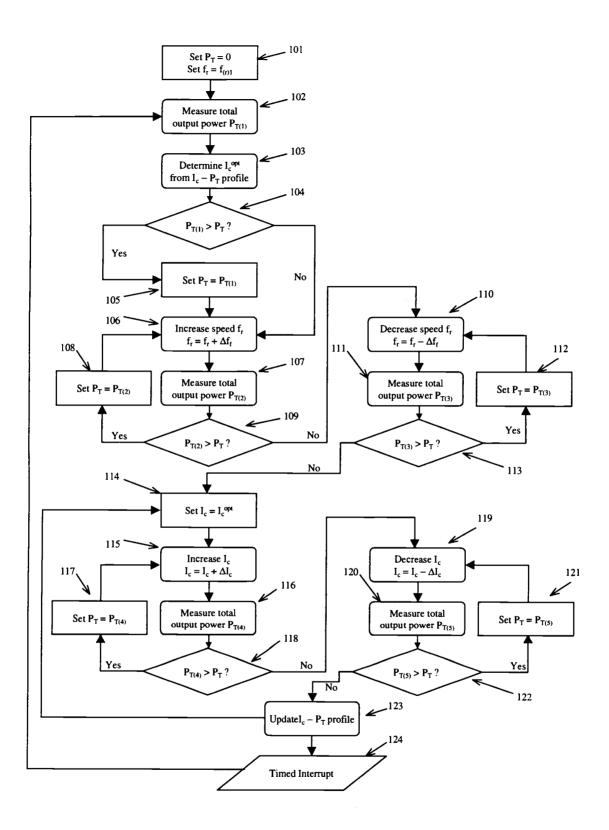

| <b>2.4</b> Perturbation based search algorithm for maximum power point tracking                                                                                                            |

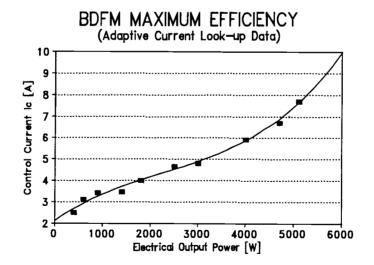

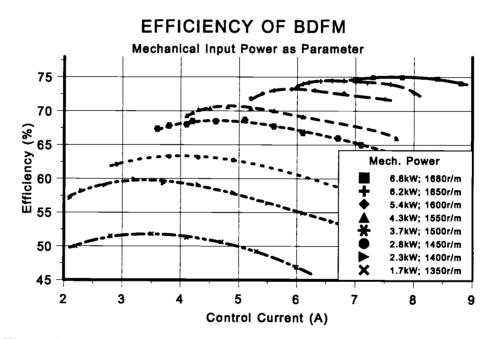

| <ul><li>2.5 Optimal control winding current requirements to ensure maximum efficiency</li><li>for a 7.5kW BDFM</li></ul>                                                                   |

| <u>Figure</u>                                                                                                                                                       | age |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <b>2.6</b> Maximum efficiency point characterization of a 230 V, 7.5 kW prototype BDFM with input mechanical power as a parameter                                   | 39  |

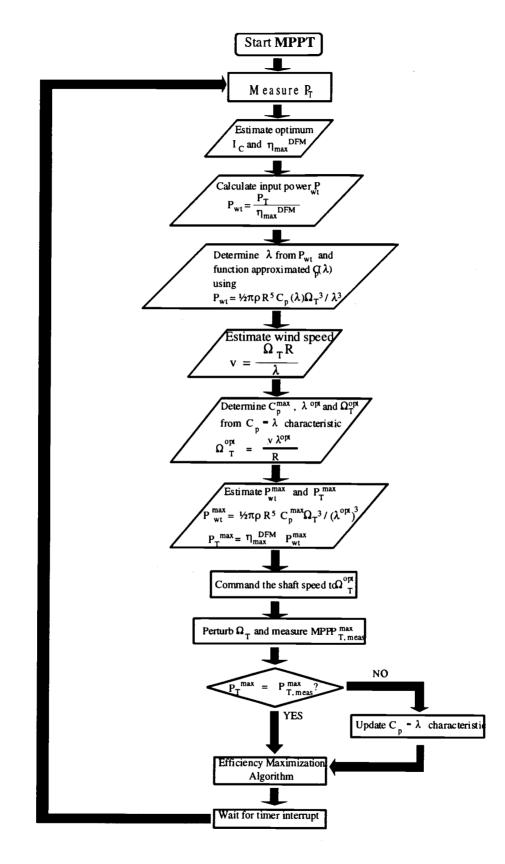

| 2.7 Maximum power point tracking based on estimated wind speed                                                                                                      | 40  |

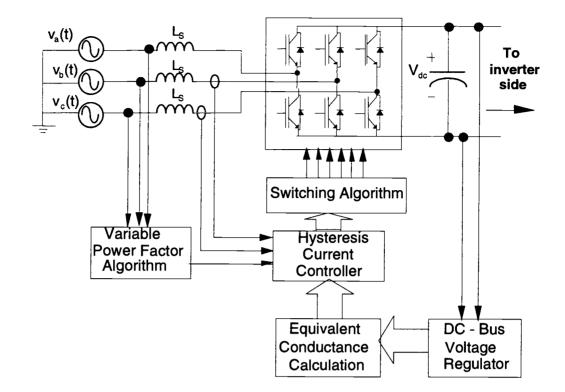

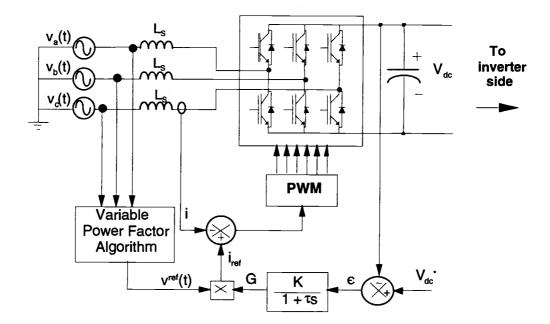

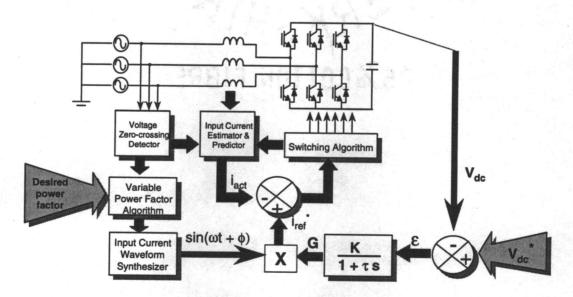

| 3.1 Block diagram representation of the sensor-based rectifier controller                                                                                           | 48  |

| 3.2 Sensor-based controller representation                                                                                                                          | 49  |

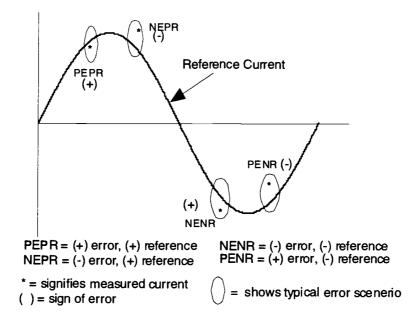

| <b>3.3</b> Possible current errors in each phase of the rectifier                                                                                                   | 52  |

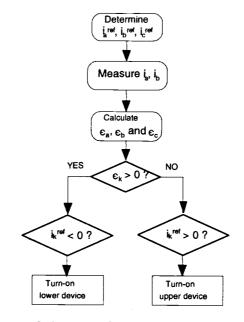

| <b>3.4</b> Switching logic of the rectifier                                                                                                                         | 53  |

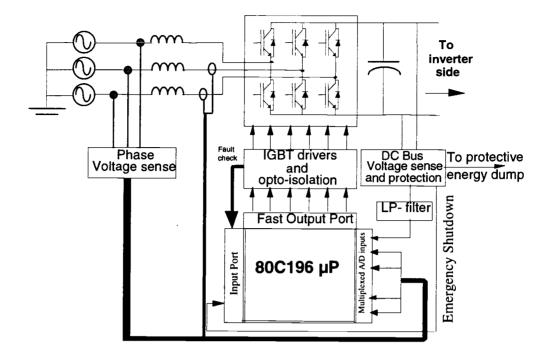

| 3.5 Sensor-based rectifier controller implementation                                                                                                                | 54  |

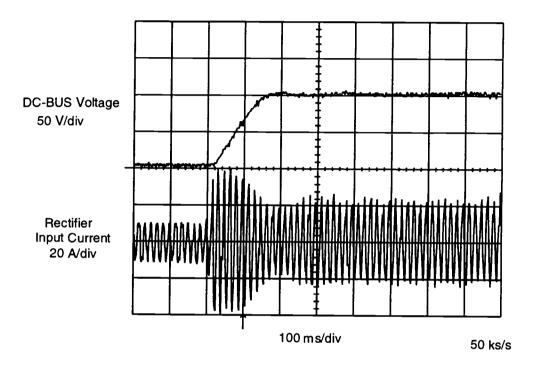

| <b>3.6</b> Rectifier controller response to a 40% (280 V- 390V) step change in commanded dc-bus voltage. DC-bus capacitance = 2400 $\mu$ F                          | 55  |

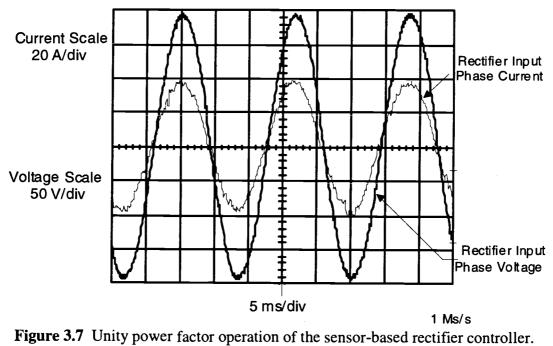

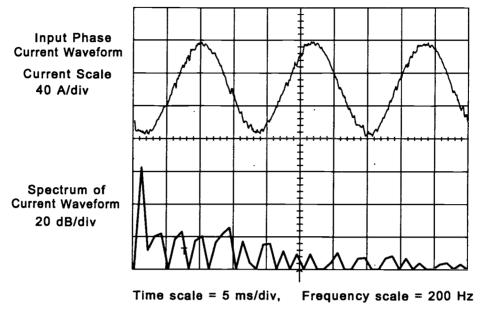

| <b>3.7</b> Unity power factor operation of the sensor-based rectifier controller.<br>$V_{dc} = 390 \text{ V}, V_{ac} = 230 \text{ V}, \text{ load} = 10 \text{ kW}$ | 56  |

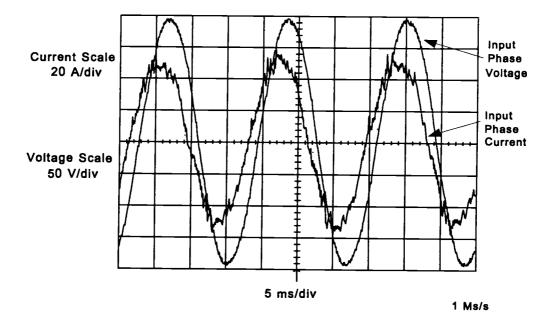

| <b>3.8</b> Leading 0.85 p.f. operation. $V_{dc} = 390 \text{ V}$ , $V_{ac} = 230 \text{ V}$ , load = 10 kW                                                          | 57  |

| <b>3.9</b> Leading 0.85 p.f. operation. $V_{dc}$ = 450 V, $V_{ac}$ = 230 V, load = 10 kW                                                                            | 57  |

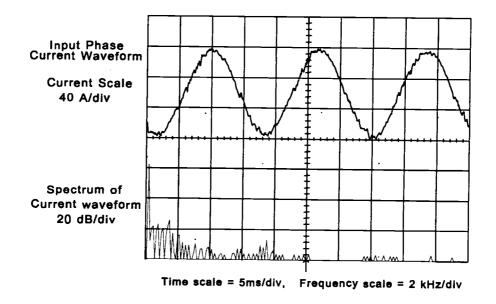

| 3.10 Expanded view of the Fourier spectrum                                                                                                                          | 58  |

| <u>Figure</u> Pag                                                                                                                                                                                | <u>ge</u> |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 3.11 Sensorless version of the rectifier controller                                                                                                                                              | 59        |

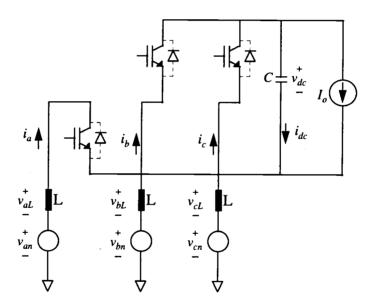

| <b>3.12</b> Lumped circuit representation of a switching state of the rectifier                                                                                                                  | 50        |

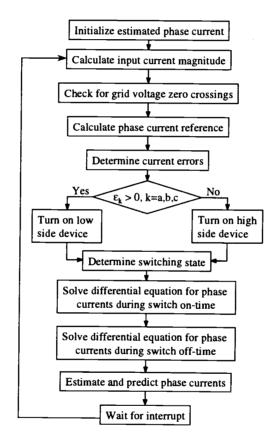

| <b>3.13</b> Simplified flowchart of the sensorless version of the rectifier controller                                                                                                           | 53        |

| <b>3.14</b> Time and frequency domain simulation result of rectifier input current with the proposed model based current controller under unity p.f. condition                                   | 55        |

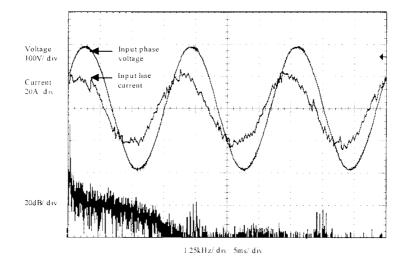

| 3.15 Experimental waveforms generated by the sensor-based controller.                                                                                                                            |           |

| $V_{ac} = 230 \text{ V}, V_{dc} = 390 \text{ V}, f_{switch} = 6.67 \text{ kHz}, \text{ load} \approx 6.5 \text{ kW}$                                                                             | 57        |

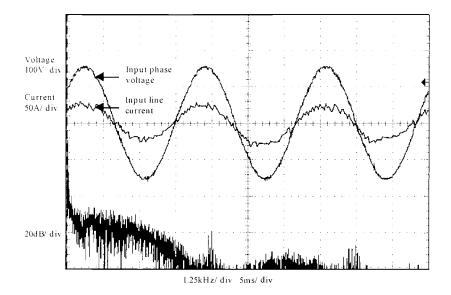

| <b>3.16</b> Unity power factor operation of the sensorless controller.<br>$V_{ac} = 230 \text{ V}, V_{dc} = 390 \text{ V}, f_{switch} = 5 \text{ kHz}, \text{ load } \approx 6 \text{ kW} \dots$ | 68        |

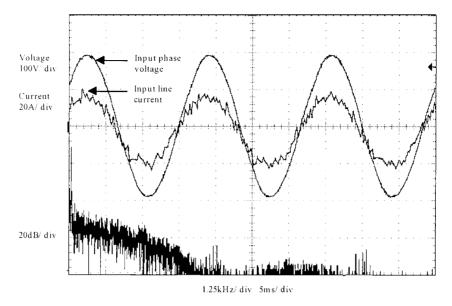

| 3.17 Leading power factor operation of the sensorless controller.                                                                                                                                |           |

| $V_{ac} = 230 \text{ V}, V_{dc} = 390 \text{ V}, f_{switch} = 5 \text{ kHz}, \text{ load } \approx 6 \text{ kW} \dots$                                                                           | 69        |

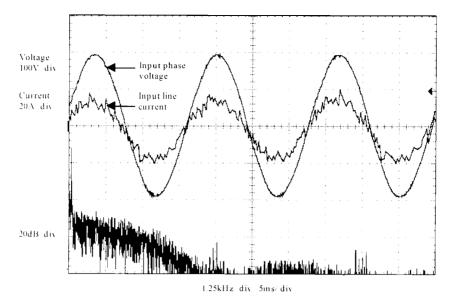

| <b>3.18</b> Rectifier operation with an (-)20% grid voltage error.<br>$V_{ac} = 184 \text{ V}, V_{dc} = 390 \text{ V}, f_{switch} = 5 \text{ kHz}, \text{ load } \approx 6 \text{ kW} \dots$     | 70        |

| 3.19 Rectifier operation with an imposed (+)17% grid voltage error.                                                                                                                              |           |

| $V_{ac} = 230 \text{ V}, V_{dc} = 390 \text{ V}, f_{switch} = 5 \text{ kHz}, \text{ load} \approx 5.5 \text{ kW}$                                                                                | 71        |

| <b>3.20</b> Rectifier operation with (-)21% line reactor inductance error.<br>$V_{ac} = 230 \text{ V}, V_{dc} = 390 \text{ V}, f_{switch} = 5 \text{ kHz}, \text{ load} \approx 6 \text{ kW}$    | 72        |

| <u>Figure</u> <u>Page</u>                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>3.21</b> Three phase current waveforms for 0.85 leading p.f. operations. Conditions similar to that of Fig. 3.17                                                                    |

|                                                                                                                                                                                        |

| <b>4.1</b> Laboratory VSG wind power generation system implementation78                                                                                                                |

| 4.2 DC machine based wind-turbine model controller                                                                                                                                     |

| <b>4.3</b> Desired mechanical power output of the laboratory wind turbine emulator                                                                                                     |

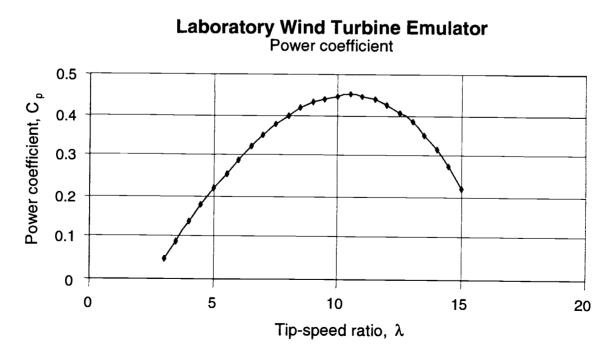

| <b>4.4</b> Power coefficient of the laboratory wind turbine emulator                                                                                                                   |

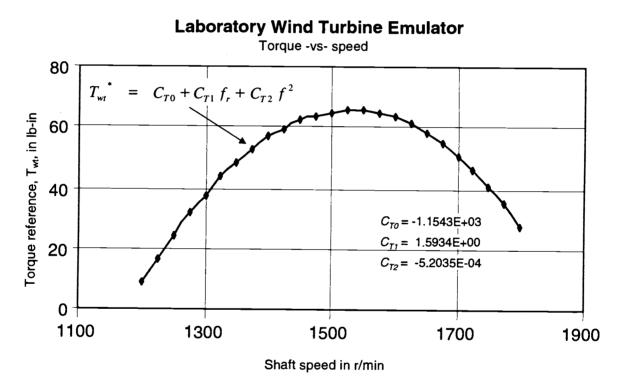

| 4.5 Desired torque-speed characteristic of the wind turbine emulator                                                                                                                   |

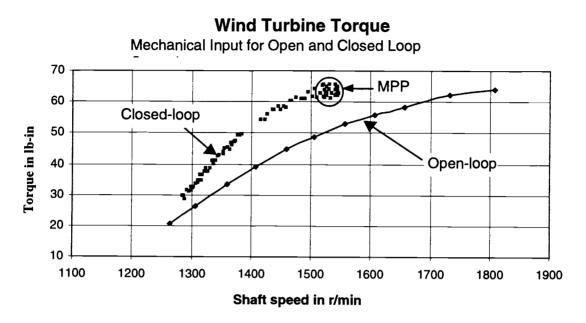

| <b>4.6</b> Measured turbine model torque. Closed-loop operation illustrates the effectiveness of the optimization controller and turbine convergence at the set MPP                    |

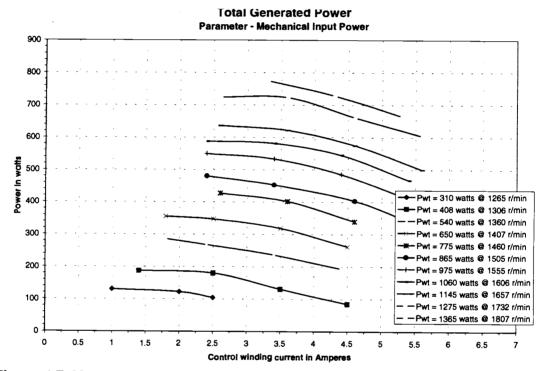

| 4.7 Variation of generated power with varying of control winding current for different input mechanical power                                                                          |

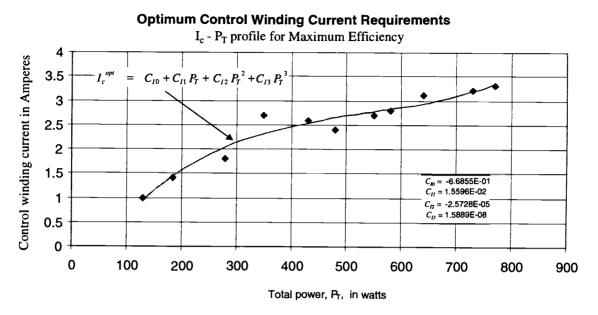

| <b>4.8</b> Optimum control winding current requirements for maximum efficiency operation of the prototype BDFM. The curve-fit polynomial, as shown, is the MEPT controller realization |

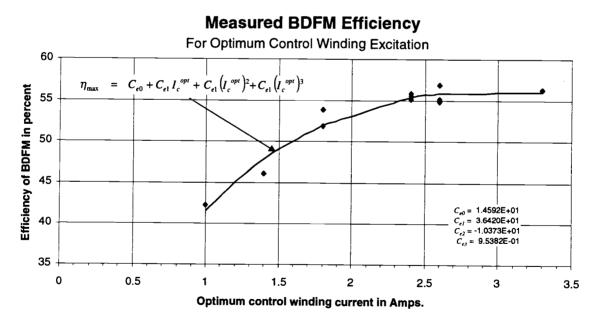

| <b>4.9</b> $\eta_{max} - I_c^{opt}$ profile of the prototype BDFM as implemented                                                                                                       |

| <b>4.10</b> Overall converter protection strategy                                                                                                                                      |

| <u>Figure</u> Pag                                                                      | <u>36</u>      |

|----------------------------------------------------------------------------------------|----------------|

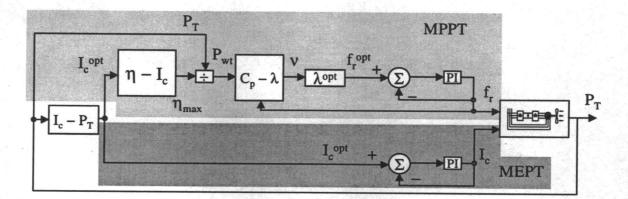

| 4.11 Block diagram of the performance optimization system controller as                |                |

| implemented in the laboratory VSG system                                               | <b>)</b> 4     |

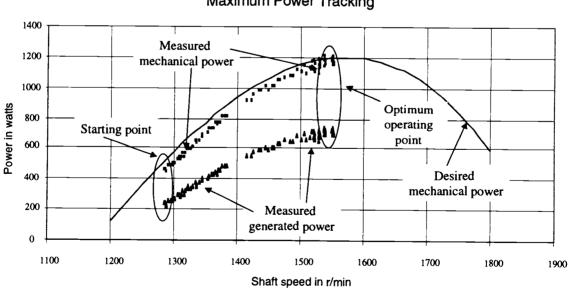

| 5.1 Closed loop operation of the performance optimization controller                   | <del>)</del> 7 |

| 5.2 Maximum efficiency point tracking by the performance optimization controller9      | 98             |

| <b>5.3</b> Turbine output power for open and closed loop operation10                   | )0             |

| 5.4 Comparison of the measured and estimated control winding current for               |                |

| maintain optimum operation. The current has been estimated by substituting             |                |

| the measured power into the polynomial of Fig. 4.810                                   | )1             |

| 5.5 Power flow through the inverter as percentage of total apparent, real and          |                |

| reactive power10                                                                       | )2             |

|                                                                                        |                |

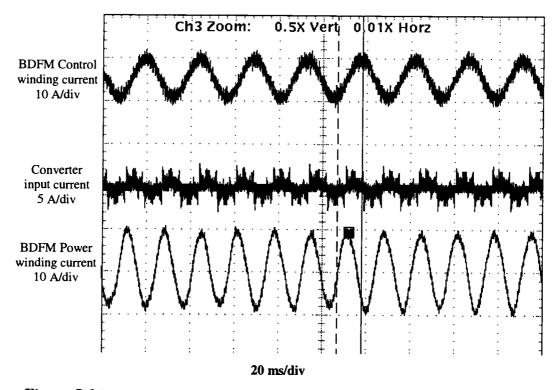

| 5.6 Representative current waveforms of the converter and the BDFM approximately       |                |

| at the maximum power point. ( $P_{wt} \approx 1150$ watts, shaft speed = 1525 r/min)10 | )3             |

### List of Tables

| T   | able                                      | <u>Page</u> |

|-----|-------------------------------------------|-------------|

| 3.1 | Typical current error scenarios           | 52          |

| 3.2 | Possible switching states                 | 64          |

| 3.3 | Comparison of spectral performance        | 73          |

| 4.1 | BDFM generator design specifications [27] | 85          |

| 4.2 | Winding specifications [27]               | 86          |

## List of Symbols

| Kinetic energy of moving air                                    |

|-----------------------------------------------------------------|

| mass of air                                                     |

| speed of moving air                                             |

| tip speed of turbine blade                                      |

| air density                                                     |

| Power in moving wind                                            |

| mechanical power in the shaft of the wind turbine               |

| power coefficient of a wind turbine; ratio of $P_{wt}$ to $P_w$ |

| mechanical torque in the shaft of the wind turbine              |

| tip-speed ratio; ratio of $v_p$ to $v$                          |

| frequency of DFM power winding excitation                       |

| frequency of DFM control winding excitation                     |

| number of pole pairs of the DFM power winding                   |

| number of pole pairs of the DFM control winding                 |

| total generated power                                           |

| estimated maximum DFM efficiency                                |

| optimum DFM control winding rms current                         |

| instantaneous dc-bus voltage                                    |

| dc-bus voltage reference                                        |

| rms grid voltage (line-to-line)                                 |

| instantaneous phase currents                                    |

| input line inductance                                           |

| capacitance of the dc-bus                                       |

| instantaneous input phase voltages                              |

|                                                                 |

### **Performance Optimization for Doubly-Fed Generation Systems**

### 1. Introduction [1]

Wind power is gradually gaining prominence as a suitable source of renewable energy. Implementations range from the propeller-type, horizontal axis wind turbine (HAWT) to vertical axis or VAWT systems. Power ratings vary from several kW for remote area, off-grid applications to several MW for systems connected to the ac power grid. As wind speeds, in practice, vary over a wide range, so does the amount of power generated by the turbine. Hence, if wind turbines are only operated at a constant rotor speed, they are not capable of optimizing power extraction over a wide range of wind speeds. This can be improved, mechanically, by providing for adjustments in the pitch of the turbine blades or by utilizing the electrical system for simple, step-wise speed control employing pole-changing techniques. However, implementing mechanical controls renders the system structure more complicated and less reliable. Also, due to the narrow control bandwidth of the mechanical controls, improvement in energy capture is only marginal. With the advent of modern power electronic converters, it is possible to refer the entire control function to the electrical side and consequently improve energy capture and system reliability substantially. Many modern, commercial wind turbines are of the variable speed design, requiring a power electronic interface between the variable frequency wind turbine and the fixed frequency electric utility grid.

Horizontal axis turbines can have blade spans of up to approximately 90 m, with the majority of commercial systems being in the range of 15 - 45 m, with a power rating of 100 to 600 kW. Rotational speeds are in the range of 30 - 100 r/min, necessitating a gearbox to increase the speed to a value suitable for low pole number electric machines, typically around 1800 r/min. Fixed speed systems utilize either conventional synchronous machines or squirrel cage induction machines. Converter-fed variable speed systems can be based on conventional generators or can be implemented utilizing doubly-

fed machines to reduce rating and cost of the power electronic converter [1,2]. In HAWT systems, the gearbox and the generator are housed in the nacelle at the top of the tower structure, while in VAWT installations, all generating equipment can be positioned on the ground at the base of the turbine. In order to increase efficiency and decrease complexity, low speed generators can be utilized to eliminate the need for a step-up gearbox and couple the electric generator to the turbine rotor in a direct-drive configuration.

Wind power is a renewable resource and freely available worldwide. However, site preparation, system installation and provision for maintenance require significant investment. Economic considerations require that the cost of wind energy has to be competitive with conventional fossil resources in order to be a viable alternative. This becomes important in variable speed systems, which, while extracting more energy from the wind, suffer an initial cost disadvantage due to either the increased mechanical complexity or the power electronic converter requirement [3]. This cost penalty may eventually negate the gains associated with additional energy capture. Thus, reducing the cost of the power generating hardware is essential for variable-speed generating systems to achieve viable and competitive \$/kWh ratios.

The power electronic utility interface necessary for converter based variable speed systems provides many additional benefits beyond enhanced energy capture. While acoustic noise produced during low power operation can be minimized, it is also possible to improve the poor displacement power factor associated with induction generators. At the same time, harmonics from other generators or non-linear loads can be compensated using appropriate converter control algorithms and utilizing passive or active harmonic filters.

While offering significant benefits in operational performance, variable-speed generators have the drawbacks of higher initial cost as well as increased complexity and potentially lower reliability. Hence, the need for a low-cost, robust variable speed generation (VSG) system is essential for enhanced energy capture with a reduced capital

investment. The brushless doubly-fed machine retains the ruggedness of an induction machine while allowing VSG operation at a significantly lower initial investment due to the reduction in rating of its power electronic energy conversion interface.

#### 1.1. Basic wind turbine characteristics

The conversion of wind energy into electricity on a large scale raises the problem of energy storage. Work is in progress on a variety of energy storage systems, including batteries, pumped storage, compressed air and flywheels. Still, the electrical supply grid remains a convenient absorber of electrical energy provided the capacity of the wind generation equipment is still small in relation to the total generating capacity coupled to the supply grid. Thus, other than in relatively low power, remote area applications, most wind turbines are coupled to the ac utility grid.

#### 1.1.1. Wind energy conversion

The energy in the wind as a result of the kinetic energy of the moving air mass is described by :

$$E_{ke} = \frac{1}{2}mv^{2}$$

with: m - air mass;

v - speed of moving

(1.1)

Air density is a function of altitude and temperature, given by:

$$\rho = 3443 \frac{P_a}{T}$$

with:  $\rho$  - air density;

$P_a$  - atmospheric pressure;

$T$  - absolute temperature.

(1.2)

The mass of air moving through a wind turbine of sweep area A per unit time is

$$m = \rho A v \tag{1.3}$$

and the total available power from the air movement through area A is expressed as

$$P_{w} = \frac{1}{2} \rho A v^{3}$$

(1.4)

Wind power is thus proportional to the cube of the wind speed, v, and the power extracted by the wind turbine in mechanical form can be described as

$$P_{wt} = C_p P_w$$

with:  $C_p$  - wind turbine power coefficient.

(1.5)

It is not possible to extract all energy from the moving air, since in this case the air movement would seize and the air would pile up behind the turbine. It was shown by Betz [4] that for maximum power extraction, the air velocity at the wind turbine is  $\frac{2}{3}$  of the upstream wind speed, further decreasing to  $\frac{1}{3}$  well downstream of the turbine. Thus, the theoretical maximum power coefficient is  $C_p = \frac{16}{27}$  or 59.3%. Practical wind turbines do not reach this Betz limit and the wind velocity at the turbine is somewhat greater than  $\frac{2}{3}v$ . The value of  $C_p$  is a function of wind and rotational speeds as well as form and pitch of the wind turbine and has a maximum at a fixed operating point, i.e. at a constant ratio of rotor speed to wind speed. Thus, the power coefficient is normally expressed in terms of the tip-speed-ratio  $\lambda$ , which is defined as:

$$\lambda = \frac{v_p}{v} = \frac{\Omega_T R}{v}$$

with:  $v_p$  - tip - speed of turbine blade;

$R$  - turbine rotor radius;

$\Omega_T$  - rotational turbine angular velocity;

$v$  - wind speed.

(1.6)

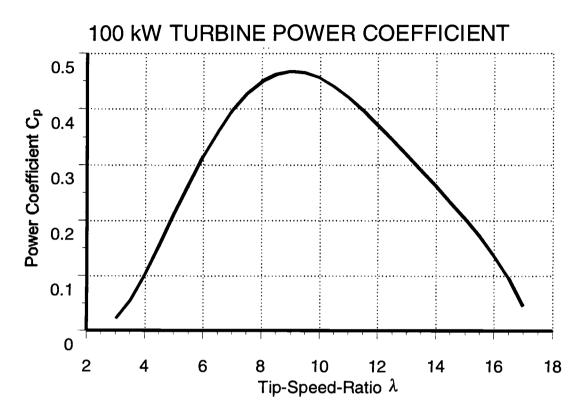

Figure 1.1 illustrates the variation of the power coefficient for a conceptual 100 kW horizontal axis wind turbine [1,2].

Figure 1.1 Power coefficient of a 100 kW wind turbine.

The torque coefficient,  $C_T$ , of the wind turbine is related to  $C_p$  as

$$C_T = \frac{Torque}{\frac{1}{2}\rho_v^2 A R} = \frac{1}{\lambda}C_p$$

(1.7)

### 1.1.2. Fixed and variable speed generation

It is evident that for optimum energy extraction, the maximum power coefficient and thus the optimum tip-speed-ratio should be maintained at all wind speeds. With a constant speed constant frequency (CSCF) wind turbine system, it may be necessary to use pitch control of the blades to limit power input to the system [5], thus introducing additional mechanical control systems. Variable-speed generation can track the changes in wind speed by adapting shaft speed and thus maintaining optimal energy generation.

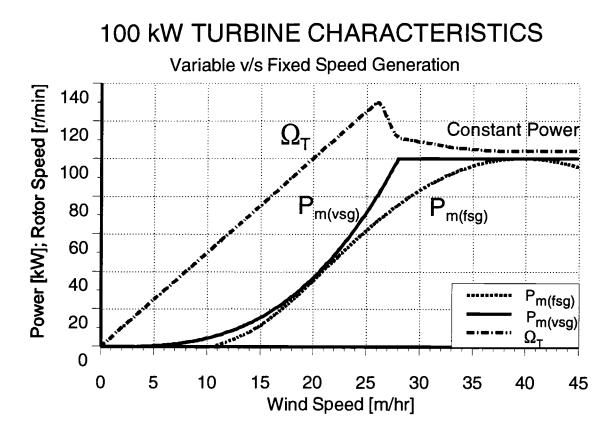

In Fig. 1.2 the rotor power for the wind turbine characteristic of Fig. 1.1 is plotted using variable speed generation (VSG) and fixed speed generation (FSG) strategies. The fixed speed system is optimized at only a single speed, generally representing maximum energy capture potential for a given site. Thus, power output at near cut-in and maximum power are significantly lower than in the case of the variable speed system. The fixed speed fixed pitch system is inherently power limited, as increasing wind speeds lower the turbine power coefficient, a phenomenon referred to as stall regulation. On the other hand, the variable speed system will attempt to track maximum power at any wind speed within the design limitations of the system. Once rated generator power or maximum rotational speed is reached, it becomes necessary to limit the turbine power by abandoning the optimum tip-speed-ratio. During variable speed operation, wind and rotor speeds are related linearly, whereas in the constant power regime, shaft speed drops off sharply and is kept essentially constant thereafter. The speed range for VSG operation is selected such that it only commences when the cut-in wind speed is reached and torque is sufficient to operate. Due to the cubic power-speed relationship, the loss of energy is minimal. The upper cut-out or furling speed is determined by the limits of the turbine and its structural strength.

The improved energy capture for VSG systems is obtained at the expense of additional system components, most often in the form of a power electronic converter. The cost of this additional hardware needs to be low enough to achieve a reasonable rate of amortization given the additional energy generated. In addition to maximizing energy extraction from the wind, the generation system efficiency needs to be as high as economically feasible in order to maximize the energy delivered from generator to the electric power grid.

Figure 1.2 Variable and fixed speed power and speed characteristics of a 100 kW turbine.

#### 1.1.3. Wind generation system design considerations

As illustrated in Fig. 1.2, wind turbines operate at a relatively low speed, in general below 100 r/min. Utilizing off-the-shelf electrical machinery with four (1800 r/min) to eight poles (900 r/min) requires a step-up gearbox with a gear ratio of at least 9 to 18, but often higher. This sometimes requires a multi-stage gearbox, with the resultant mechanical complexity and additional losses, which can be in the order of 4-8% of mechanical turbine power [6]. Eliminating the gearbox leads to significant system benefits, but requires generators of very high pole number, e.g. 160 for a turbine speed of 45 r/min. Given a minimum pole pitch, machine diameter for a high number of poles becomes very large, sometimes unacceptably so, given manufacturability and cost constraints and space restrictions in the nacelle at the top of the supporting tower in

HAWT systems. System design needs to optimize the trade-off between using an off-theshelf, relatively high speed generator in conjunction with a gearbox and utilizing a special purpose, directly coupled generator.

HAWTs produce a non-constant torque due to tower shadow [7]. As each blade passes the supporting tower, the output torque decreases. Thus, the torque produced by a two-blade wind turbine contains a harmonic at twice the rotational speed, the so-called 2P harmonic. Also contributing to torque pulsations is a wind shear effect due to the wind speed gradient along the height of the area swept by the wind. Typically, a fixed-speed system is unable to mitigate this effect in order to improve the quality of the output power. In large turbines, the power pulsations passed to the network can become unacceptable, especially when the penetration level is high. In VSG systems, though, appropriate control of the power electronic converter can minimize torque ripple and thus output power pulsations [8,9]. Here, the inertias of turbine and generator are used to store energy and mitigate torque pulsations. This not only improves the utility interface characteristics, but also damps mechanical stresses on the system, thus allowing for relaxed safety factors, lighter construction and hence, higher reliability and longer useful life.

Some large wind systems are not self-starting or self-stopping. Mechanical tower resonances at low frequencies require that the wind turbine be motored up to operating speed. Fixed-speed systems require the starting of a large induction machine with the resulting expense of soft start mechanisms; stopping a fixed-speed system usually requires a large mechanical braking system. A mechanical brake may also be required in converter fed systems, since the stopping capability needs to be available even in the absence of electrical excitation, such as during fault conditions.

While sharing many operational characteristics with HAWT systems, VAWTs in general are not self starting and require the generator to run as a motor during start up. Certain VAWT systems, such as those of the Darrieus type [8], are not susceptible to

tower shadow, but wind shear is still present and torque pulsations are produced by the continuously changing angle of attack between wind and turbine blades.

Wind generation system design needs to account for the extreme environmental conditions encountered. Depending on the site, temperatures between -30 °C to +45 °C as well as internal condensation must be allowed for. Additionally, the differential temperature of system parts will vary with time and load. The nacelle cover can only provide for some protection against environmental effects, such as rain, snow, ice, particulates and chemical pollution. Appropriate design of not only the mechanical system, but especially the electronics for control and power processing is essential. The design criteria for wind generation system design are summarized as follows:

- Reliable and low maintenance design optimized for the environmental constraints of a given site;

- Minimum number of components and cost;

- Maximum energy capture and efficiency;

- Integration of mechanical and electrical systems (start-up, shut-down, mechanical stresses);

- Utility supply interaction and contamination.

#### 1.2. Conversion systems for wind power generation

#### 1.2.1. Constant speed generators

CSCF systems use a grid-connected synchronous or induction generator, so that variations in wind speed have to be accommodated by pitch control of the wind turbine itself to limit input power at or below rating. This refers the primary power flow control function to the mechanical side of the system. Synchronous machines which can be utilized include conventional, wound-field machines as well as synchronous reluctance and permanent magnet machines. Conventional synchronous machines have the advantage of providing for reactive power control as well as voltage regulation via the rotor field winding. Many different power ratings are available off-the-shelf from established manufacturers and machine development costs are minimized.

Permanent magnet (pm) synchronous machines have the advantage of a higher efficiency due to the absence of excitation losses. However, unlike in conventional synchronous generators, output control via the excitation is lost. Consequently, magnet flux and the number of stator turns have to be chosen such that satisfactory operation over the entire load and voltage range is possible while minimizing transient currents during synchronization. Many different permanent magnet designs are feasible [6], including conventional radial field machines, axial flux machines, transverse flux geometries and hybrid claw pole designs. Present day implementations are mainly based on the radial flux concept, utilizing either a buried magnet structure or surface magnets. Interior pm machines can be implemented using high energy, rare earth (SmCo or NeFeBo) magnets or less expensive ferrites. Surface magnet machines in general require rare earth magnets to achieve the desired airgap flux density.

Synchronous reluctance machines also do not provide for excitation control, but avoid the use of magnets and the associated costs. However, rotor designs to achieve the desired reluctance ratios are difficult to manufacture, which partially negates the cost advantage. In the absence of rotor excitation, synchronous reluctance machines require excitation from the connected power grid and have relatively poor displacement power factors. Thus, power factor correction capacitors are often employed.

All synchronous machines provide for a stiff coupling between turbine and the grid. Neither pitch nor stall control can respond fast enough to the torque fluctuations due to tower shadow and wind gust effects. This transmits the torque pulsations directly to the generator and requires an increased torque capability of approximately 50% above nominal. This stiff coupling also subjects the mechanical system to considerable stresses. Subsequently, increase in compliance and damping is required in the power train to alleviate structural resonances. This discussion also applies to low-slip induction generators.

Many wind turbines utilize low cost, mass produced cage rotor induction machines. In the absence of rotor connections, these systems are also very robust. However, as with synchronous reluctance machines, excitation is required via the stator, which leads to poor power factors and requires power factor correction capacitors at the point of common coupling to the grid. The slip characteristic of induction machines is beneficial for wind turbine control, as it reduces stiffness and provides for additional compliance and damping in the electrical system as compared to synchronous generators.

#### 1.2.2. Variable speed generators

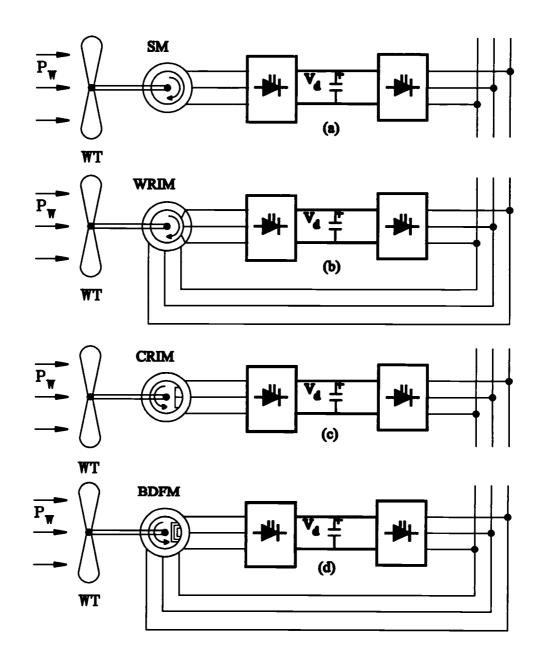

In variable speed constant frequency (VSCF) systems the wind turbine operates at variable speed. If this speed range is made large enough, it is possible to operate a fixed pitch wind turbine and refer the entire power control function to the electrical side. Figure 1.3 reviews variable speed systems based on ac machines and voltage source inverter technology [1]. These represent the desired implementation for medium power (approximately 100 kW - 500 kW) wind systems; higher power turbines may still utilize current-fed, supply commutated topologies. In most cases, a gearbox is used to interface the low speed wind turbine with the high speed generator (not shown in Fig. 1.3).

The system shown in Fig. 1.3(a) can be implemented using conventional, wound-field synchronous machines or the permanent magnet or synchronous reluctance options discussed previously. The system shown in Fig. 1.3(c) utilizes conventional, off-the-shelf, cage rotor induction machines. In both cases, all generated power is processed by a power electronic converter. In the case of reluctance and induction machines, the required reactive power is also provided by the converter, leading to large and expensive converters, typically with a continuous rating in excess of 125% of machine rating. The size of the converter also negatively influences the supply interaction, i.e. the harmonics

injected into the power grid due to converter switching. Despite these disadvantages, many commercial variable speed systems still utilize the cage rotor induction machine due to its simplicity, ruggedness and low cost.

Only limited variable speed operation is possible with a conventional induction generator, since otherwise the efficiency becomes proportional to speed. This has led to the investigation of oversynchronous operation of slip ring or doubly-fed induction generators with rotor and stator power fed back to the supply [3,8]. In this case, variable speed operation is possible while only controlling the electrical side. The system shown in Fig. 1.3(b) utilizes a wound-rotor induction machine, the stator of which is directly connected to the utility grid. Only slip power is processed by the rotor power electronic converter, reducing its required rating, size and cost. If this so-called electronic Scherbius system is rated such that maximum power operation corresponds to rated torque at twice synchronous speed, the required rating of the power electronic converter is only 50% of that necessary for the synchronous machine system [3]. This leads to an appreciable saving in capital investment and also reduces the negative impact of converter harmonics on the utility system. From a maintenance and reliability point of view, the use of slip rings is a disadvantage, especially considering that the wind turbine should be capable of working unattended, in adverse conditions, for extended periods.

Recently, doubly-fed machines without slip rings or brushes have been proposed as viable variable speed generators for wind turbines [2,10]. Figure 1.3(d) shows the Brushless Doubly-Fed Machine (BDFM) which is based on the induction principle and combines the advantages of the cage rotor systems (low machine cost, robust brushless machine construction) with the benefits of the electronic Scherbius configuration (reduced power converter rating and cost). The BDFM has two stator windings of different pole number to avoid direct transformer coupling [11]. The power and control stator windings interact through the rotor, which has a specialized cage structure with a number of identical sections corresponding to the sum of the pole pairs of the stator windings. The machine exhibits synchronous behavior where stator frequencies and shaft speed are related by [11] :

$f_{c} = f_{r}(p_{p} + p_{c}) - f_{p}$ with:  $f_{p}$  - utility grid frequency (60 Hz);  $f_{r}$  - shaft speed dictated by the variable-speed generation algorithm;  $f_{c}$  - required converter output frequency;  $p_{p}$  - pole pairs of grid connected winding; and  $p_{c}$  - pole pairs of converter controlled winding. (1.8)

In this thesis, a VSG controller is proposed which exploits the double stator winding feature to operate the machine in a maximum efficiency mode while tracking the input maximum power. In other words, the excitation of the machine is distributed in its two windings such that it operates "optimally" – in this embodiment, – the maximum efficiency mode. The optimality condition could be determined based on suitable user defined criteria such as maximum power factor mode at the grid, or a weighed product of the efficiency and the power factor at the grid. The philosophy of the controller is also applicable to any VSG or adjustable speed drive (ASD) system that utilizes a DFM as the energy conversion device from mechanical to electrical and vice versa.

In a DFM, only a fraction of the generator power is processed electronically, resulting in reduced size and cost as well as improved power quality. The die-castable rotor cage ensures robust and inexpensive machine construction. An alternative design with very similar characteristics is the doubly-fed reluctance machine [10], which uses an equivalent stator configuration, but replaces the rotor with a reluctance geometry similar to the one found in the synchronous reluctance machine. The dual power flow paths found in doubly-fed machines enables efficiency-optimized controls not possible with singly-fed machines.

The generator systems discussed so far are all based on three-phase technology with distributed stator windings. Another system which has been suggested for wind power applications is the variable reluctance machine, which differs considerably from the synchronous reluctance generator discussed previously [12]. The variable reluctance machine has a doubly salient structure, with distinct stator and rotor poles, much like a

stepper motor. Unlike in conventional ac machines, the stator windings are not distributed, but rather are concentrated on the stator poles. Combined with the simple rotor structure, this leads to ease of manufacturing and potential economic advantages. The converter topology for variable reluctance machines differs significantly from its counterpart for conventional machines. Development work is also under way to introduce magnets into variable reluctance machines in an effort to enhance generator performance [13].

Rather than follow the optimum VSG power curve (see Fig. 1.2) in a continuous fashion using the VSG systems described above, often a two-speed system is implemented to improve upon fixed speed generator performance. This can be realized with pole changing induction machines and the resulting system avoids the use of a power converter completely.

#### 1.2.3. Power converter considerations

Technological advances in gate turn-off, high power semiconductor devices have revolutionized the power electronics applications industry, especially in the medium power range. Extremely fast turn-on and turn-off characteristics are obtained for Insulated Gate Bipolar Transistor (IGBT) modules rated in excess of 2000 A. These devices allow for high switching frequency and control bandwidth with relatively simple drive requirements. Hence, for medium power (500 kW – 1 MW) wind generation applications, hard switched, pulse-width-modulation (PWM) based power interfaces are typically employed. To ameliorate the performance of the switches by reducing the switching stresses and losses and to reduce the unwanted  $\frac{dv}{dt}$  and  $\frac{di}{dt}$  effects of hard switching, topologies utilizing soft switching techniques can be incorporated in wind generation systems [14].

For wind generation systems rated at above 500 kW - 1 MW, present day technology still favors Silicon Controlled Rectifiers (SCR) and Gate Turn-Off Thyristors (GTO),

which are available in ratings of over 4000 A. However, only slow switching frequencies, typically less than 500 Hz, can be attained employing SCRs and GTOs at the high power levels. Generally, SCR-based current link converters utilizing either load or forced commutation are used for high power synchronous or induction generator based systems. Cycloconverters provide the electronic grid interface for high power, direct drive synchronous generators and limited speed range, high power doubly-fed induction machines.

### 1.2.4. Direct drive wind turbines

The gearbox used to interface slow speed wind turbines with conventional, relatively high speed electric machines is a source of additional cost and losses. Direct-drive wind turbines require generators with very high pole numbers and, given a minimum pole pitch requirement, this leads to very large generators, with approximately double the outer diameter and weight of high speed machines. Low speed generator efficiency is also lower by a few percentage points and machine cost is higher, due to both the increase in size and the higher cost for these special purpose machines, which do not enjoy the economies of scale of mass manufacturing. Nevertheless, it has been shown [5,14] that the overall direct-drive system can have significant advantages in terms of initial cost, efficiency, reliability and return on investment, when compared to the high speed, geared generators.

Due to the benefits associated with direct drive systems, numerous development programs are under way investigating suitable machine geometries. Proposed machine geometries include variable-reluctance generators [11], surface-mount [14] and buried magnet permanent magnet machines. It is expected that significant progress will be made in this area over the coming decade and that market penetration of direct-drive wind turbines will increase significantly.

#### 1.3. Wind turbine control systems

#### 1.3.1. Fixed speed generator control

The simplest wind-turbine configuration is without pitch control and a synchronous link to the grid, where the turbine speed is constant due to the generator being directly connected to the fixed-frequency grid. While it is possible to limit the power input by stall regulation with this arrangement, it is not possible to control the amount of power delivered by the turbine to the electrical generator within its operating range. It is solely dependent on the wind variations. However, since the available aerodynamic power is a function of both the wind speed, v, and the angular speed of the turbine,  $\Omega_T$ , the power delivered by the turbine could possibly be only a fraction of the maximum available power. As shown in Fig. 1.1, a fixed speed system is typically optimized at only a single speed of operation. This inherently limits the deliverable power, as increasing wind speeds lower the power coefficient. Although fixed speed wind turbine systems do not employ sophisticated speed control systems, they may still need to be equipped with electrical or mechanical control for power limiting, torque-ripple mitigation and resonance avoidance.

The tower passing effect of the turbine blades causes dynamic speed variations even for fixed speed generation systems, which could affect their performance. The use of tip vanes for dynamic rotational speed control of HAWT has been reported [16]. The tip vane is located at the tip of a turbine blade and functions as a device for power augmentation by varying the power coefficient,  $C_p$ . It can also be operated as a rotor speed braking device by varying the sweep angle between the vane orientation and the axis of rotation of the turbine blades. At zero sweep angle, the turbine power coefficient,  $C_p$ , is at its maximum. Any change in the sweep angle provides a means for turbine deceleration or acceleration. The tip vane sweep angle controller utilizes turbine speed error and its derivative to determine the absolute value of the sweep angle. In situations where large wind fluctuations occur, tip vane control in conjunction with blade pitch control can provide for effective fixed speed operation.

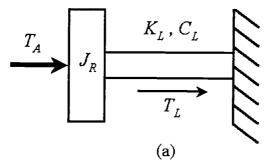

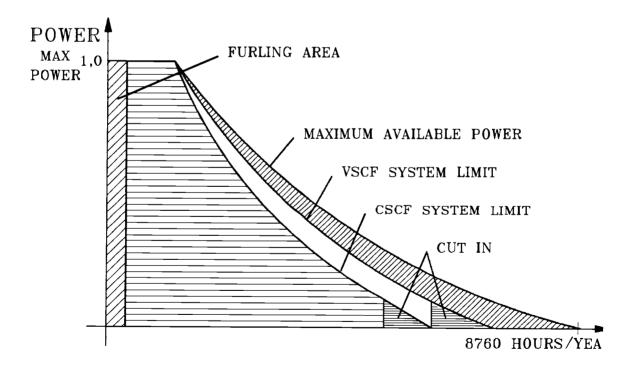

The wind turbine and the energy conversion system can be represented by a rigid rotor of inertia  $J_R$  with an applied aerodynamic torque of  $T_A$ . This torque is transmitted as  $T_L$  to a shaft of rigidity  $K_L$  and damping  $C_L$  as shown in Fig. 1.4. Upon simple analysis, the transfer function H(s) between the transmitted torque,  $T_L$  and the aerodynamic torque,  $T_A$ can be formulated as

$$H(s) = \frac{T_L}{T_A} = \frac{C_L s + K_L}{J_R s^2 + C_L s + K_L}$$

(1.9)

**Figure 1.4** Simplified wind turbine (a) mechanical model and (b) block diagram, typically utilized for determination of mechanical system resonances and responses

The natural frequency,  $\omega_N$  of the denominator of H(s) (i.e. the characteristic equation) can be determined to be

$$\omega_N = \sqrt{\frac{K_L}{J_R}}$$

(1.10)

which corresponds to the first torsional mode or the system mode [7]. Developing a more elaborate model of the wind turbine system by representing the wind turbine by two discs of equal inertia, it is observed that there exists a second resonant peak of the transfer function when plotted in the frequency domain [17]. Due to the existence of these two resonant peaks in the transfer function of the wind turbine system, usually both the 2P and the 4P (for a vertical axis turbine) harmonics are minimally attenuated, enabling them to propagate through the drive train and appear as electrical torque ripple. The ripple, if not compensated, affects the quality of electrical power generated and causes torsional fatigue of the components of the drive train.

In an effort to increase the difference between the 2P harmonic of a turbine and the natural frequency,  $\omega_N$ , various mechanical methods have been devised to reduce the rigidity of the low speed shaft. From eq. (1.10) above, it is readily seen that  $\omega_N$  decreases as  $K_L$ , the rigidity of the low speed shaft, decreases. This has led to the use of a low rigidity shaft, also known as the quill shaft, on the low speed, turbine side of the gearbox. Further separation in the 2P harmonic and the natural frequency  $\omega_N$  is possible by electrical means as discussed in section 1.2.2.

Torque pulsations and the associated power angle oscillations in slow speed direct coupled generators (small pole pitch permanent magnet synchronous generators) cannot be damped using damper windings on the rotor, as they would incur unacceptable losses as well as increase the physical size of the generator. Once the torque oscillations are passed on to the stator, they can be damped using a passive viscous damper, consisting of a spring and a mechanical damper, which connects the stator of the generator to the wind turbine housing. An adaptive mechanical damping method for wind turbine torque stabilization [17] uses a bearing-mounted stator, which oscillates about the machine axis against a torsional spring. By selecting an appropriate stiffness,  $K_S$ , and inertia,  $J_S$ , of the stator damper, the "blank" frequency,

$$f_{blank} = \frac{1}{2\pi} \sqrt{\frac{K_s}{J_s}}$$

(1.11)

can be set equal to the 2P frequency. The blank frequency is the frequency at which stator and rotor oscillate as a single mass, thus rendering the system non-responsive to any input. Hence, when the blank frequency equals the 2P frequency, all torque pulsations can be eliminated. However, this results in excessively large stator oscillations and requires slight stator damping, thus sacrificing transient response to improved tower passing response. An adaptive damping system can be based upon the fact that an optimum system allows the stator to oscillate freely at the tower passing frequency, but damps oscillations at any other frequency [17].

#### **1.3.2.** Variable speed generator control

In addition to dynamically maximizing the wind turbine efficiency, variable speed can also serve to reduce system stresses such as torque pulsations. The following advantages are beneficial with respect to system reliability and generated power quality:

- Variable speed control can lead to a substantial reduction of the torque ripple in the drive train and hence improved power quality. This is achieved by an increase in compliance, whereby a variation in the aerodynamic power results in system acceleration or deceleration rather than in output power fluctuations.

- The attenuation of torsional mode resonances in variable speed operation allows for a relaxation of design requirements.

- Dynamic loads are reduced and safety margins can be relaxed.

Some electrical systems available for variable speed generation (VSG) operation are shown in Fig. 1.3. As illustrated, both singly and doubly-fed electrical generators have been employed in variable speed wind generation configurations [1].

## 1.3.2.1. Singly-fed generator control

Speed control of a wind turbine system can be accomplished by controlling either the turbine blade angle (pitch control) or the electrical generator speed if an electronic power converter is available. The compliance of the electrical coupling between the grid and the generator varies based on the type of generator. Typically, the mechanical compliance in the drive train is higher than the electrical compliance. This leads to a lightly damped, low frequency torsional mode [18]. Speed control allows for efficient system operation and also provides for an effective way of damping the low frequency torsional mode.

From Figs. 1.1 and 1.2 it is clear that in order to obtain maximum power from the wind turbine, it is necessary to keep the tip speed ratio,  $\lambda$ , constant over a wide range of wind speeds. This is achieved by a maximum power point tracking (MPPT) system, an essential component of any VSG controller, which tracks the optimum tip speed ratio for large variations of wind speeds. Here, it should be noted that the MPPT speed range needs to avoid areas of mechanical resonance. Wind speed is a difficult quantity to measure and should not be incorporated as a control input for MPPT design. A basic search algorithm involves sweeping the generator speed command over a certain range until a maximum output power is measured [19]. Other algorithms involve the determination of the wind generator model [20,21], employ techniques of system identification [1] or utilize a model independent control method [22].

Unlike in a dc machine, in a cage rotor induction machine the magnetic flux and the electromechanical torque are coupled, i.e. the torque controller affects the flux and vice versa when scalar control methods are employed. Field oriented or vector control of induction machines utilizes real-time mathematical transformations to effectively

decouple the control of flux and torque production, thus duplicating the features inherently available in a dc machine. The availability of sophisticated low-cost microcontrollers and digital signal processors has led to wide spread implementation of field oriented control techniques for variable speed induction generators. Employing field oriented control techniques for effective torque control and fast speed response allows for both maximum power point tracking (MPPT) and the compensation of torque pulsations [9]. Reactive power control is also possible by appropriately controlling the power electronic grid interface.

Traditionally, the MPPT controller is based upon a search algorithm [3, 19] where the rotational speed of the electrical generator shaft is varied over a range determined by the design of the installation site. While the strategy is extremely simple, it is slow in responding to frequent changes in the wind speed. Hence, the VSG may not be capable of operating at the MPP all throughout the possible wind speed variations. Hence, the benefits of the VSG system may not be exploited to the maximum extent despite the increased investment incurred due to the power converter.

In this thesis, an wind speed estimation based MPPT algorithm is proposed that employs principles of the generator characterization. The optimum tip-speed ratio is maintained by determining the wind speed iteratively from the total generated power and the  $C_p - \lambda$  profile of the turbine in use. The proposed MPPT algorithm, though more complicated than the simple search based method, can still be implemented in a relatively low-end floating-point microprocessor. The ease of implementation guarantees fast control updates and ensures maximum power point operation for all wind speeds within the design limitations. While the controller has been developed based on a BDFM, the principles can be extended to other DFMs and singly-fed electrical machines.

## 1.3.2.2. Doubly-fed generator control

Utilizing a PWM converter for slip power recovery, a doubly-fed wound rotor induction machine can be operated as a variable speed generator [21]. The power converter rating and, hence, the initial cost is reduced as the converter handles only the slip power. Control of torque and thus active power can be achieved by controlling the rotor current component orthogonal to the stator flux; stator reactive power is controlled by the in-phase rotor current. The decoupling of stator active and reactive power flows, allows for an additional control function, which can be used to maintain optimal stator flux and minimize copper losses [21].

The modeling of wind turbine systems is an extremely difficult task due to the uncertainties in the modeling of the aerodynamics, such as the effects of tower shadow, wind shear, blade surface smoothness, wind turbulence and others. This suggests the use of approaches which do not rely on the physical model, as outlined in [1] for an efficiency maximization algorithm for doubly-fed generators. The doubly-fed machine provides an additional degree of control freedom, not present in singly-fed system, whereby stable operation is possible for a variety of control winding current levels at a particular operating speed [1,22]. The overall optimization problem for the mechanical (turbine) and electrical (generator) systems involves finding the maximum of power output as a function of both speed and control current, a three-dimensional optimization problem [1].

In order to keep the controller simple, mechanically robust and inexpensive, no mechanical inputs such as shaft torque should be required for the control algorithm. In addition to the power and efficiency maximizing function, the controller can also perform reactive power as well as harmonic compensation. Based on output power measurement, the controller sets converter frequency and current magnitude. Hence, no mechanical feedback signals are required. However, the compensation of torque pulsations requires an inner speed loop, which is based on field oriented control and requires rotor position feedback [24].

The proposed system optimization controller utilizes the characterization of the DFM in a certain "optimum" mode of operation, based on a user defined criterion of optimality. To create a knowledge base for the system with respect to the "optimum" operation, a set of open-loop experiments are conducted on the system to determine the output power while maintaining that "optimum" condition, such as maximum efficiency or maximum power factor operation at the grid. This information can also be constructed from initial acceptance testing of the system which is typically conducted before actual system installation. As determined in this embodiment, the control variable is the control winding current of the BDFM. Applying duality principles of electrical networks, the control winding voltage could also be employed as the control variable that ensures "optimal" operation of the system.

The optimality characterization thus obtained is then utilized for the overall system operation. If the system can be operated "optimally", the DFM characteristics obtained are employed by the wind speed estimation based MPPT algorithm discussed in section 1.3.2.1.

#### **1.3.3.** Compensation of torque pulsations

Torque pulsations are a nuisance problem even in VSG systems. They corrupt power quality as explained in the section on fixed speed generator control. The use of a power converter in variable speed generation enhances the control options for mitigation of torque oscillations. The increase in the available power due to a tower passing spike can be stored either

- in the inertia of the system by speeding up the generator utilizing field oriented control (7); or

- in the energy storage link, capacitors in voltage source inverters (VSI) or inductors in current source inverters (CSI).

The second option is impractical due to the significant increase in the required capacitance or inductance of the converter. Hence, the first option is the only practical solution and is commonly implemented in wind generation systems. The torque pulsation compensation is usually a fast inner control loop, with the MPPT algorithm implemented in a much slower and overall system control loop.

An older electrical approach for torque pulsation mitigation is to reduce the stiffness of the electric coupling with the help of a current source power electronic converter between the synchronous generator and the grid [7]. Employing a proportional-integral dc-link current regulator and operating the synchronous generator with constant air gap flux yields the following relationship between electromagnetic torque and generator speed:

$$\frac{\Delta T_E}{\Delta \omega_E} = K_P + \frac{K_I}{s}$$

(1.12)

Equation (1.12) above corresponds to the model of an electric generator with electrical stiffness,  $K_I$ , and electric damping,  $K_P$ . Hence, the PI dc-link current regulator can be adjusted for the parameters of the electromagnetic coupling to the electric grid. Also, the integral constant  $K_I$  can be tuned to fix the first torsional mode at any desired low value of frequency.

#### 1.4. Wind turbine operation

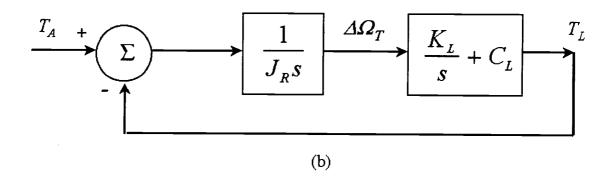

The amount of power generated by a wind turbine depends on the design characteristics of turbine and generator as well as on the properties of the wind resource. As an example, Fig. 1.5 shows the annual wind speed distribution for a wind site on the Oregon coast [1]. This variation of wind speed, v, can be represented by a Weibull or Rayleigh probability distribution [25] :

$$f(v) = \frac{k}{c} \left(\frac{v}{c}\right)^{k-1} \exp\left[-\left(\frac{v}{c}\right)^{k}\right]$$

with:  $c - \text{scale factor};$

$k - \text{shape factor};$

(1.13)

The turbine power output characteristic as shown in Fig. 1.2 can also be expressed as a function of wind speed, v:

$$P_m = P_{\max} g(v) \tag{1.14}$$

where g(v) will be different for fixed and variable speed generators. The average power output of the turbine can now be determined by

$$P_{avg} = P_{\max} \int f(v) g(v) dv$$

(1.15)

Figure 1.5 Sample annual wind speed distribution, illustrating the Rayleigh distribution of wind speeds.

The quantity inside the integral is defined as the wind turbine capacity factor and represents the ratio of average to maximum turbine outputs. Typical values are

significantly below unity, in the range of 0.3 to 0.4, reflecting the variable nature of the wind resource.

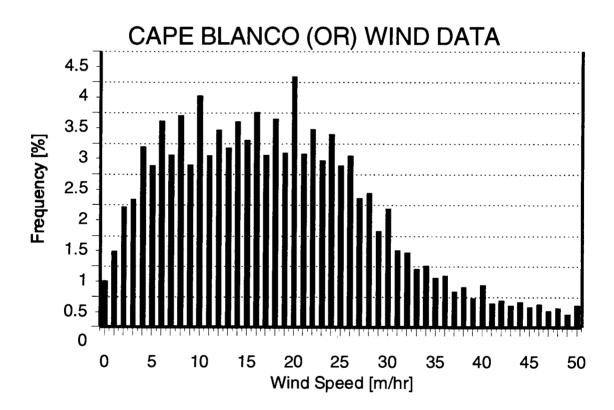

Figure 1.6 [2] shows the result of the integration in eq. (15) and illustrates the annual wind power availability and power extraction possible with CSCF and VSCF systems. The area shown in white represents the additional energy captured using VSCF generation systems and has to be weighed against the added complexity and cost of variable speed generators.

Wind power is a very competitive industry and plants are required to be competitive with fossil resources and yield a satisfactory return on investment. Issues of initial cost, generator sizing and efficiency as well as maintenance and reliability have to be carefully weighed in order to achieve satisfactory \$/kWh results from a wind power plant.

Figure 1.6 Power extraction from wind using VSCF and CSCF systems

#### 1.5. Thesis Outline

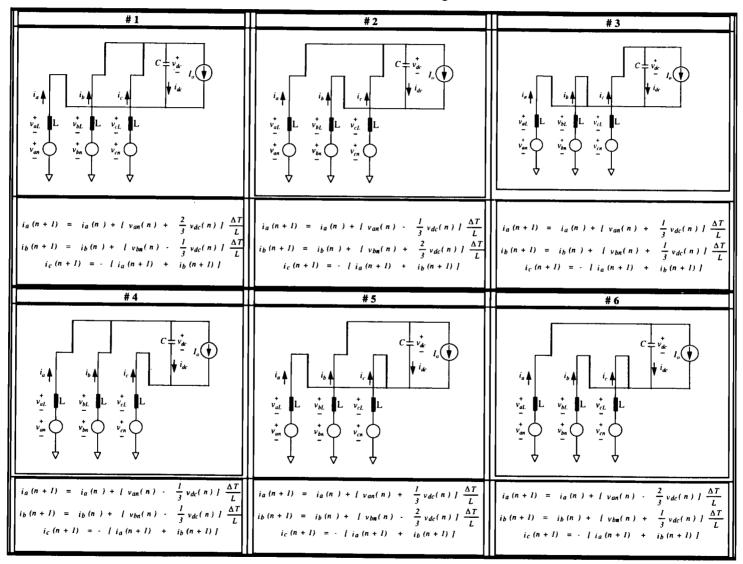

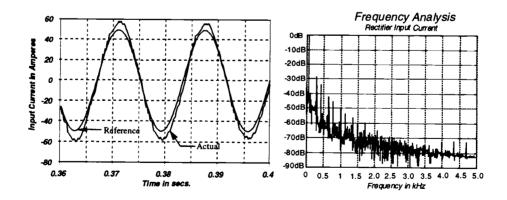

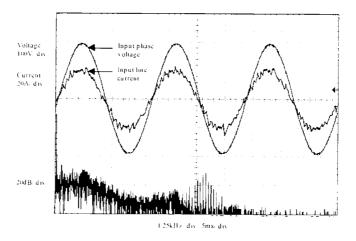

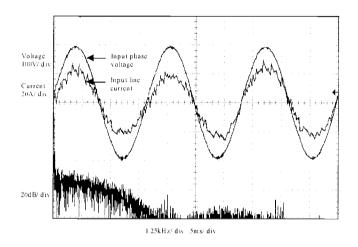

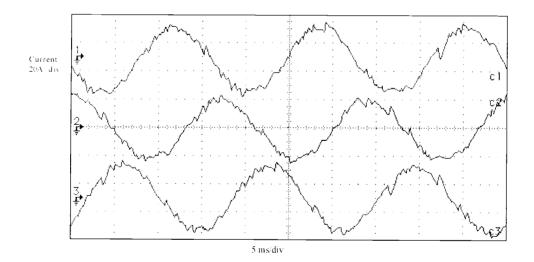

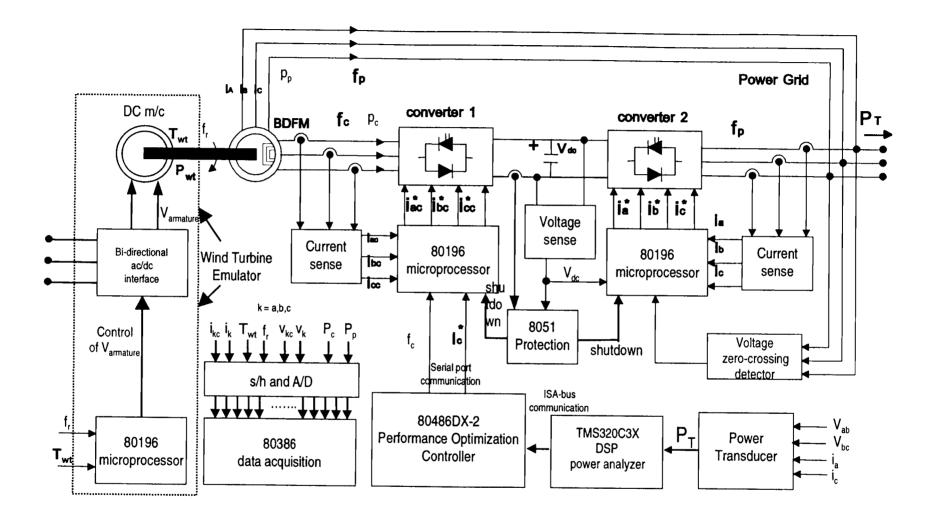

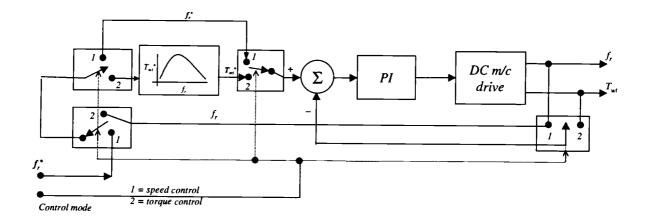

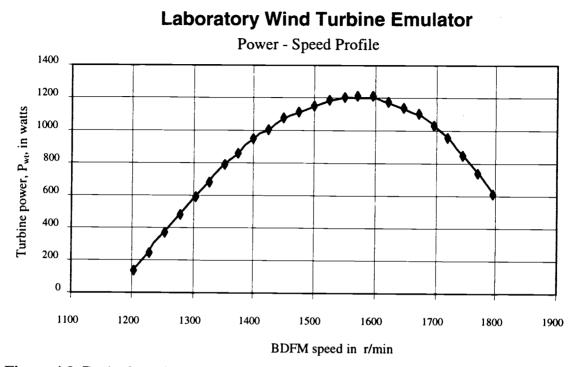

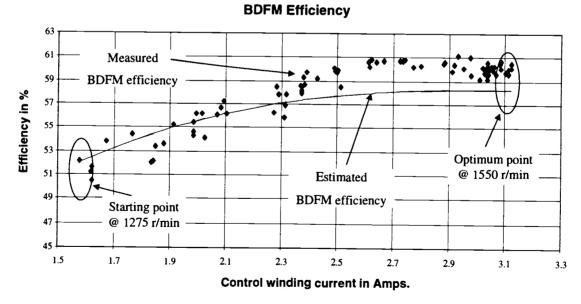

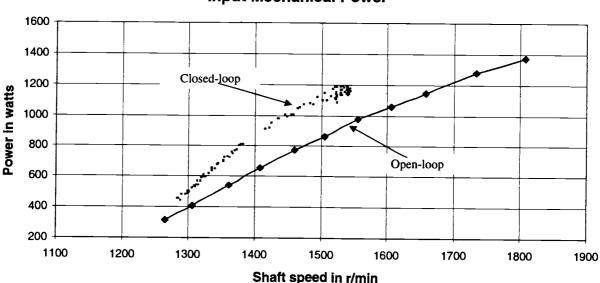

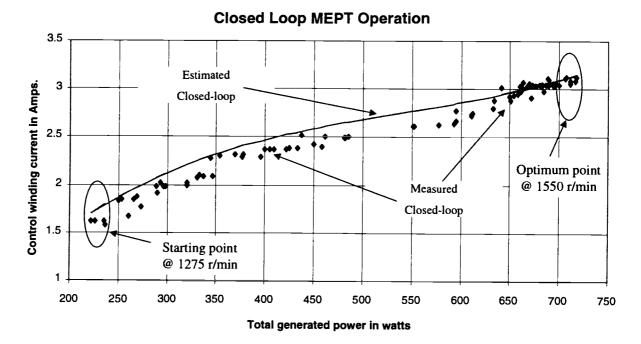

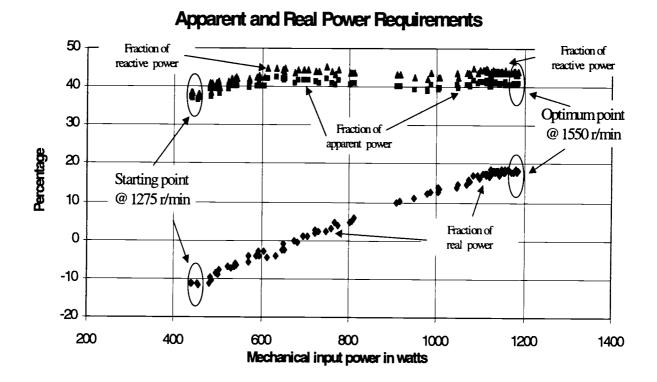

Given the advantages of variable speed wind generation as explained in section 1.2.2, it could be made economically viable by reducing the rating of the power converter. The BDFM combines the benefits of the ruggedness of a squirrel cage induction machine with the reduced rating requirements of the power converter of a wound-rotor induction machine [26]. Furthermore, the availability of the extra control variable (the control winding current) can be utilized for additional performance enhancement of the generation system.