#### AN ABSTRACT OF THE THESIS OF

Richard D. Lutz, Jr. for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and Computer Engineering</u> presented on <u>July 22, 2005</u>. Title: <u>Inductors in High-Performance Silicon Radio Frequency</u> Integrated Circuits: Analysis, Modeling, and Design Considerations

Redacted for Privacy

Abstract approved:

Andreas Weisshaar

Spiral inductors are a key component of mixed-signal and analog integrated circuits (IC's). Such circuits are often fabricated using silicon-based technology, owing to the inherent low-cost and high volume production aspects. However, semiconducting substrate materials such as silicon can have adverse effects on spiral inductor performance due to the lossy nature of the material. Since the operating requirements of many high performance IC's demand reactive components that have high Quality Factor's (Q's), and are thus low loss devices, the need for accurate modeling of such structures over lossy substrate media is key to successful circuit design.

The Q's of commonly available off-chip inductors are in the range of 50-100 for frequencies ranging up to a few gigahertz. Since off-chip inductors must be connected through package pins, solder bumps, etc., which all contribute additional loss and thus lower the apparent Q of an external device, the typical on-chip Q requirement for a given RFIC design is generally lower than that for an off-chip spiral solution. However, a spiral inductor that was designed and fabricated originally in a low loss technology such as thin-film alumina may have substantially worse performance in regard to Q if it is used in a silicon-based technology, owing to the conductive substrate. For this reason, it is imperative that semiconducting substrate effects be accurately accounted for by any modeling effort for monolithic spirals in RFICs.

This thesis presents a complete modeling solution for both single and multilevel spiral inductors over lossy silicon substrates, along with design considerations and methods for mitigation of the undesirable performance effects of semiconducting substrates. The modeling solution is based on Spectral Domain Approach (SDA) solutions for frequency dependent complex capacitive (i.e. both capacitance and conductance) parasitic elements combined with a quasi-magnetostatic field solution for calculation of the frequency dependent complex inductive (i.e. both inductance and resistance) terms. The effects of geometry and process variations are considered as well as the incorporation of Patterned Ground Shields (PGS) for the purpose of Q enhancement. Proposals for future extensions of this work are discussed in the concluding chapter. <sup>©</sup>Copyright by Richard D. Lutz, Jr.

July 22, 2005

All Rights Reserved

### Inductors in High-Performance Silicon Radio Frequency Integrated Circuits: Analysis, Modeling, and Design Considerations

by

Richard D. Lutz, Jr.

#### A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented July 22, 2005 Commencement June 2006 Doctor of Philosophy thesis of Richard D. Lutz, Jr. presented on July 22, 2005

APPROVED:

Redacted for Privacy

Major Professor, representing Electrical and Computer Engineering

Redacted for Privacy

Director of the School of Electrical Engineering and Computer Science

Rédacted for Privacy

Dean of the Graduate School

I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request.

Redacted for Privacy

Richard D. Lutz, Jr., Author

#### ACKNOWLEDGMENTS

First I wish to thank my major professors, Dr. Andreas Weisshaar and the late Dr. Vijai K. Tripathi for providing me with the opportunity to do great research work with them and for giving constant support and encouragement during my years in graduate school.

Thanks is due to Drs. Raghu Settaluri, Tom Plant, Gabor Temes, and Graduate Council Representative Dr. Keith Levien for serving on my graduate committee and reviewing the manuscript.

I also thank my colleagues, Alok Tripathi, Ed Godshalk, Garth Sundberg, Chi-Young Lim and Yeon-Chang Hahm for their encouragement, useful discussions, manuscript review, and contributions to this work.

Many thanks go to Intel Corporation, who awarded me an Intel Graduate Fellowship for the 1998-1999 academic year, and to Agilent Technologies and the Electrical and Computer Engineering Department at Oregon State University for their financial and academic support.

Thanks is due to my father-in-law and mother-in-law, Glenn and Sylvia Kaizuka, for their constant encouragement.

Finally, endless thanks to my wife, Dawn, for her support and inspiration.

## TABLE OF CONTENTS

|   |           |                | <u>I</u>                                                                                         | Page |

|---|-----------|----------------|--------------------------------------------------------------------------------------------------|------|

| 1 | INT       | rodu           | JCTION                                                                                           | 1    |

| 2 | MO<br>RAI | DELIN<br>LS    | NG TECHNIQUES FOR SINGLE AND MULTILEVEL SPI-                                                     | 9    |

|   | 2.1       |                | oduction                                                                                         |      |

|   | 2.2       | Limi           | tations of Simple Compact Models for Low-Loss Spiral Inductors                                   | 15   |

|   | 2.3       | Why            | Compact Models Fail for Some Spiral Inductors                                                    | 17   |

|   | 2.4       |                | amental Modeling Techniques for Microstrip Structures on Sil-                                    |      |

|   |           | 2.4.1          | Analysis and Modeling of Single and Coupled MIS Structures                                       | 18   |

|   |           | 2.4.2          | Complex Virtual Ground Plane Height and Expansion to<br>Multilayer Substrates                    | 23   |

|   |           | 2.4.3          | Using the Complex Virtual Ground Plane to Solve Mi-<br>crostrip Impedance Problems               | 34   |

|   |           | 2.4.4          | Proximity Effects on Resistance for Two Adjacent Lines                                           | 35   |

|   |           | 2.4.5          | Partial Inductance Calculations for Rectangular Bars                                             | 36   |

|   | 2.5       | Distri         | ibuted Spiral Inductor Models                                                                    | 40   |

|   |           | 2.5.1          | Single Level Spiral Inductor Modeling and Network Reduction                                      | 45   |

|   |           | 2.5.2          | Multilevel Spiral Inductor Modeling                                                              | 46   |

|   |           | 2.5.3          | Application of Complex Virtual Ground Plane Height to<br>Inductors and Mutual Resistance Concept | 48   |

|   | 2.6       | Simul<br>Induc | ation Results for Single and Multilevel Series-Connected Spiral tors and Discussion              | 53   |

|   |           | 2.6.1          | Single Level Spiral Inductors                                                                    | 53   |

|   |           |                |                                                                                                  | 53   |

|   | 2.7       | Parall         | el-Connected Spirals                                                                             | 56   |

| 4 | 2.8       | Conclu         | usions                                                                                           | 63   |

# TABLE OF CONTENTS (Continued)

| Ρ | $\mathbf{a}$ | g | e |

|---|--------------|---|---|

|   | w,           | 5 | ~ |

| 3 | EFI<br>ON   | FECTS OF SILICON PROCESS AND GEOMETRY VARIATIONS INDUCTOR PERFORMANCE         | 64 |

|---|-------------|-------------------------------------------------------------------------------|----|

|   | 3.1         | Introduction                                                                  |    |

|   | 3.2         | Summary of Semiconducting Substrate Effects on Si-SiO <sub>2</sub> Microstrip |    |

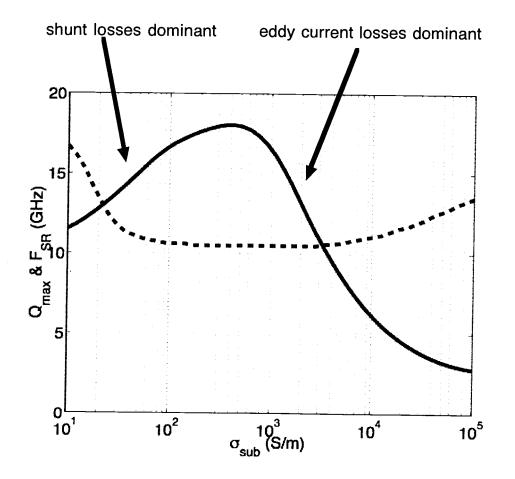

|   | 3.3         | Using Distributed Models to Predict Performance Trends                        | 65 |

|   | 3.4         | Peak Quality Factor, Self-Resonant Frequency and Other Issues                 | 67 |

|   |             | 3.4.1 Bulk Substrate Conductivity                                             | 69 |

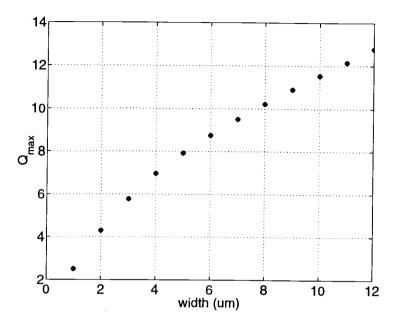

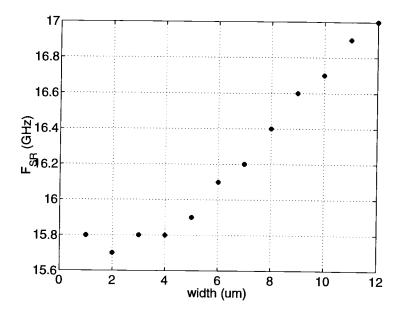

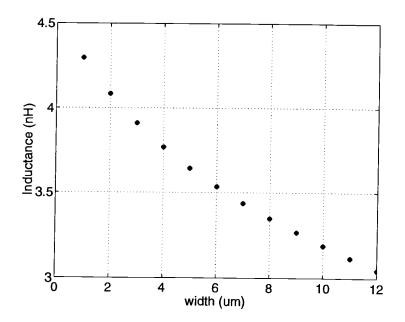

|   |             | 3.4.2 Trace Width and Shunt Capacitance & Conductance                         | 69 |

|   |             | 3.4.3 Other Considerations: Wafer Thickness and Active/Doped<br>Layers        | 80 |

|   | 3.5         | Conclusions                                                                   | 82 |

| 4 | DES<br>SPII | SIGN CONSIDERATIONS: MULTI-LEVEL VS. SINGLE-LEVEL                             | 33 |

|   | 4.1         | Introduction                                                                  | 33 |

|   | 4.2         | MLS vs. SLS: Quality Factor                                                   | 35 |

|   | 4.3         | Oxide Heights 8                                                               | 36 |

|   | 4.4         | Conductor Width and Spacing, Footprint                                        | 92 |

|   | 4.5         | Conclusions                                                                   | 15 |

| 5 |             | IGATION OF UNDESIRABLE PERFORMANCE EFFECTS OF<br>CON                          | 9  |

|   | 5.1         | Introduction                                                                  | 9  |

|   | 5.2         | Orthogonal Gridded Shields 10                                                 | 0  |

|   |             | 5.2.1 Unit-Cell Analysis 10                                                   | 4  |

۰

# TABLE OF CONTENTS (Continued)

|    |       | 5.2.2 Implementation of Orthogonal Gridded Shield 106                                                            |

|----|-------|------------------------------------------------------------------------------------------------------------------|

|    |       | 5.2.3 Equivalent Circuit Model for Effective Shunt Admittance $\dots$ 109                                        |

|    | 5.3   | Dispersion Characteristics 113                                                                                   |

|    | 5.4   | Application to Spiral Inductors 116                                                                              |

|    |       | 5.4.1 Simulation Examples 117                                                                                    |

|    |       | 5.4.2 Alternative Patterned Ground Shield Configurations 120                                                     |

|    |       | 5.4.3 Modeling the Patterned Ground Shield for Spiral Inductors . $126$                                          |

|    | 5.5   | Conclusions                                                                                                      |

| 6  | CON   | CLUSIONS AND SUGGESTIONS FOR FUTURE WORK133                                                                      |

| Bl | BLIO  | GRAPHY136                                                                                                        |

| Al | PPENI | DICES 142                                                                                                        |

|    | APPI  | ENDIX A Theory of Partial Inductance                                                                             |

|    | APPI  | ENDIX B Expressions for Quasi-Static Magnetic Vector Potential and<br>Their Application to Microstrip Structures |

|    | APPI  | ENDIX C Fundamental Explanation of PEEC Modeling                                                                 |

|    | APPI  | ENDIX D Matlab Function Script for Mutual Inductance Between<br>Rectangular Bars                                 |

|    |       |                                                                                                                  |

#### LIST OF FIGURES

| Figu | re                                                                                                                                           | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------|------|

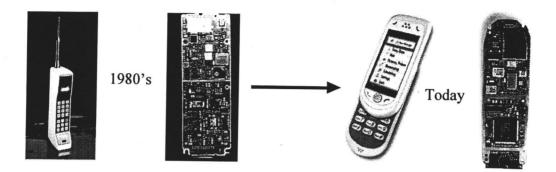

| 1.1  | Evolution of cellular telephone handsets.                                                                                                    | . 2  |

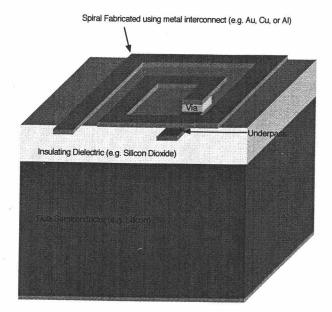

| 1.2  | Example of spiral inductor integrated onto semiconductor die                                                                                 | . 3  |

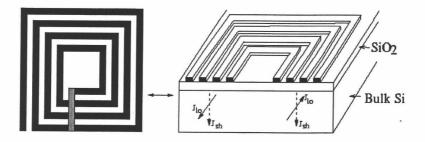

| 2.1  | Substrate currents in Si-SiO <sub>2</sub> -based spiral inductor structures. $\ldots$                                                        | . 10 |

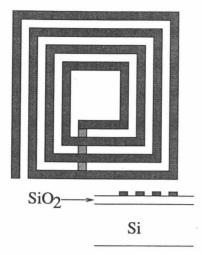

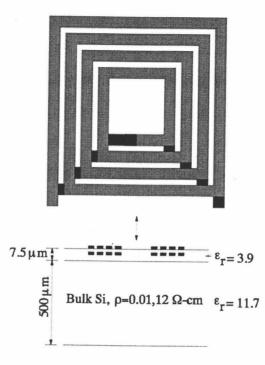

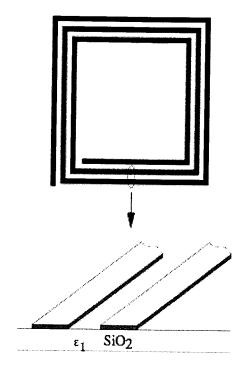

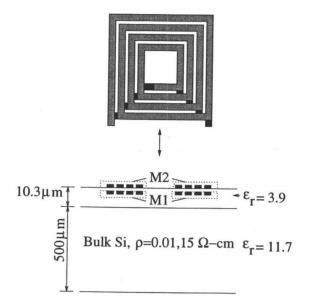

| 2.2  | Example of Si-SiO <sub>2</sub> -based single-level spiral inductor structure. $\ldots$                                                       | 12   |

| 2.3  | Example of a two level series-connected spiral inductor on lossy silicon substrate                                                           | 13   |

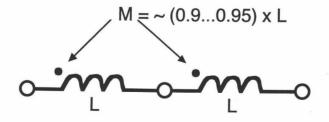

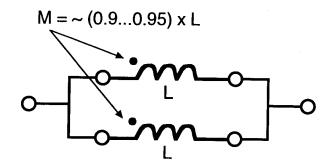

| 2.4  | Schematic representation of series-connected spiral inductor showing typical mutual inductance achievable with modern IC processes. $\ldots$ | 13   |

| 2.5  | Schematic representation of parallel-connected spiral inductor showing typical mutual inductance achievable with modern IC processes.        | 14   |

| 2.6  | General flow-chart of spiral inductor modeling technique.                                                                                    | 15   |

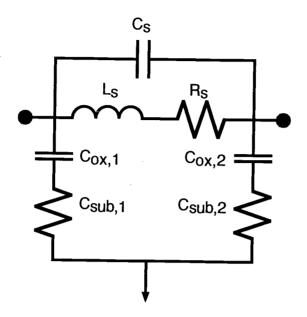

| 2.7  | Simple equivalent circuit for 'high'-resistivity Si substrates.                                                                              | 16   |

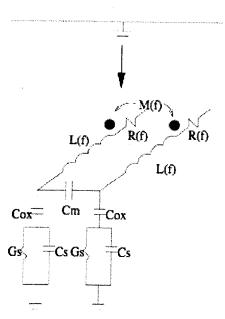

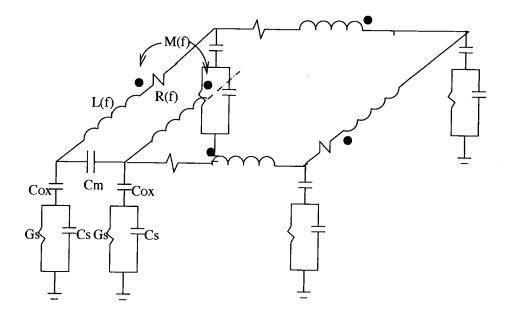

| 2.8  | Equivalent circuit for $Si-SiO_2$ microstrip coupled lines in skin effect mode                                                               | 19   |

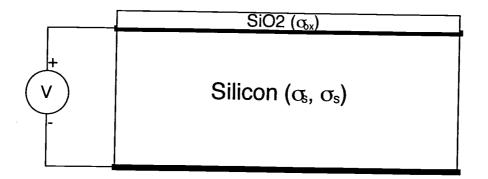

| 2.9  | Illustration of voltage applied across silicon substrate in Equa-<br>tions 2.3-2.4                                                           | 21   |

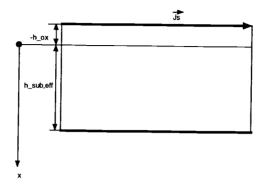

| 2.10 | Example Si-based microstrip showing definition of $h_{ox}$ and $h_{sub}$                                                                     | 23   |

| 2.11 | Normalized longitudinal substrate current density for $f= 0.001 \text{ GHz}$ (-), 0.1 GHz (-·) and 10 GHz ().                                | 24   |

| 2.12 | Longitudinal substrate current density vs. frequency and depth below oxide/Si interface.                                                     | 24   |

| 2.13 | Ideal parallel-plate waveguide, front and side views.                                                                                        | 26   |

| 2.14 | Parallel-plate waveguide with bottom plate replaced by semi-infinite semiconducting bulk substrate.                                          | 27   |

| 2.15 | Illustration of effective substrate height for two-layer Si-filled parallel-<br>plate waveguide                                              | 29   |

| 2.16 | Parallel-plate waveguide partially filled with semiconducting substrate.                                                                     |      |

| Figu |                                                                                                                                                                                                        | Page |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.17 | Parallel-plate waveguide partially filled with 2-layer semiconducting substrate.                                                                                                                       | 32   |

| 2.18 | Parallel-plate waveguide partially filled with N-layer semiconducting substrate.                                                                                                                       | 33   |

| 2.19 | Illustration of transmission line impedance analogy used for computing $h_{eff}$ for N-layer parallel-plate waveguide                                                                                  | 33   |

| 2.20 | Current distribution in two parallel lines at high frequency.                                                                                                                                          | 36   |

| 2.21 | Two parallel rectangular bars for mutual inductance calculations                                                                                                                                       | 38   |

| 2.22 | Two parallel filaments for mutual inductance calculation in Equa-<br>tion 2.45                                                                                                                         | 38   |

| 2.23 | Illustration of virtual ground plane concept for inductance calculations.                                                                                                                              | 41   |

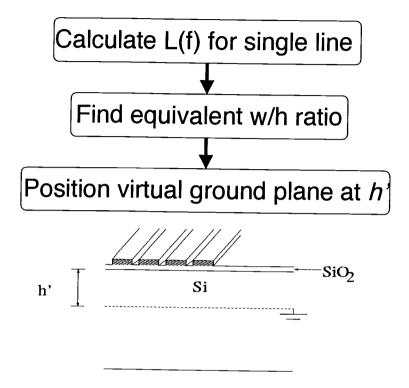

| 2.24 | Flow-chart of virtual ground plane method for inductance calculations.                                                                                                                                 | 42   |

| 2.25 | Distributed equivalent circuit model for spiral inductors.                                                                                                                                             | 43   |

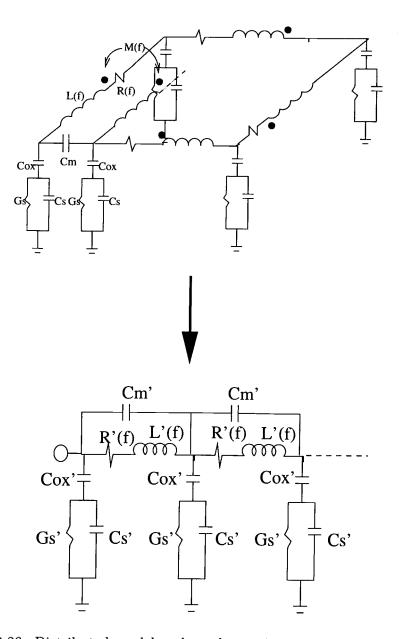

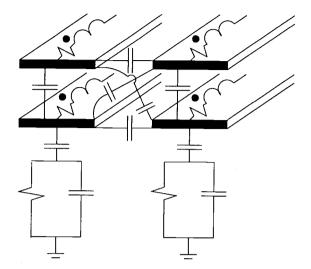

| 2.26 | Distributed model and synthesis of a corresponding ladder network for turns of a spiral inductor                                                                                                       | 47   |

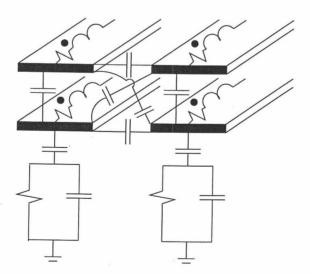

| 2.27 | Equivalent circuit modeling of multilevel structure                                                                                                                                                    | 48   |

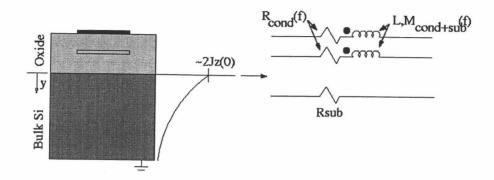

| 2.28 | Illustration of mutual resistance concept for lines above silicon                                                                                                                                      | 50   |

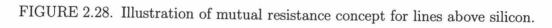

| 2.29 | Additional illustration of mutual resistance concept for coplanar lines above silicon.                                                                                                                 | 50   |

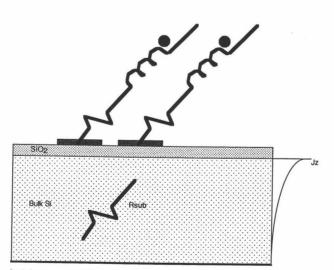

| 2.30 | Example structure for plots in Figures 2.31 and 2.32.                                                                                                                                                  | 51   |

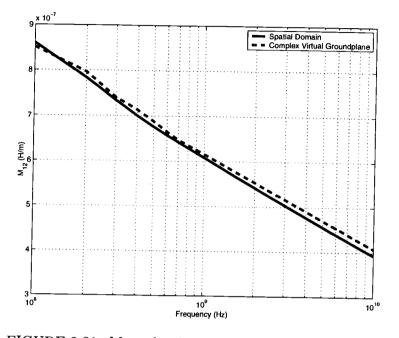

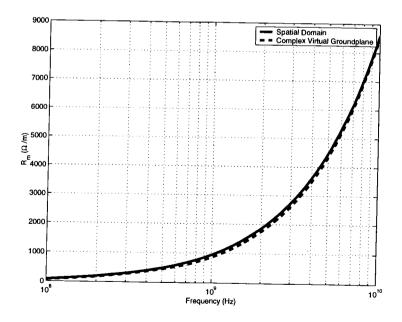

| 2.31 | Mutual inductance for lines in Figure 2.30.                                                                                                                                                            | 52   |

|      | Mutual inductance and resistance for lines in Figure 2.30.                                                                                                                                             |      |

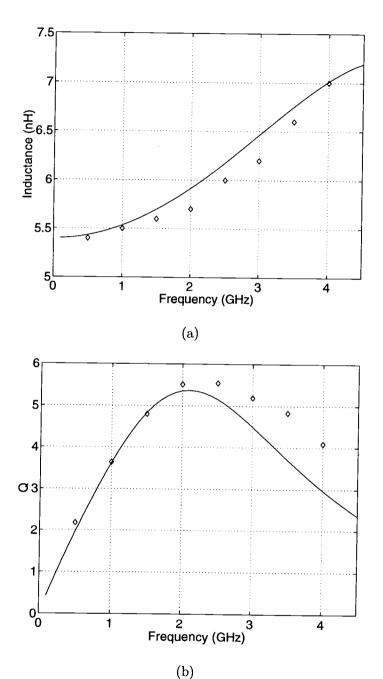

| 2.33 | Comparison of (a) inductance and (b) quality factor for simulations without Si substrate effects (-) versus measured data ( $\diamond$ ) for a 5 nH spiral inductor with $\sigma_{sub} = 10$ S/m [15]. | 54   |

| 2.34 | Comparison of (a) inductance and (b) quality factor for simulations with (- $\cdot$ distributed, $\cdot$ ladder) and without () Si substrate effects, versus measured data (-) [37]                    | 55   |

Page

| Figure | 2              |         |         |        | ,        | ,    |     |            |   |

|--------|----------------|---------|---------|--------|----------|------|-----|------------|---|

| 2.35   | (a) inductance | and (b) | quality | factor | obtained | with | tho | distribute | Ч |

Figure

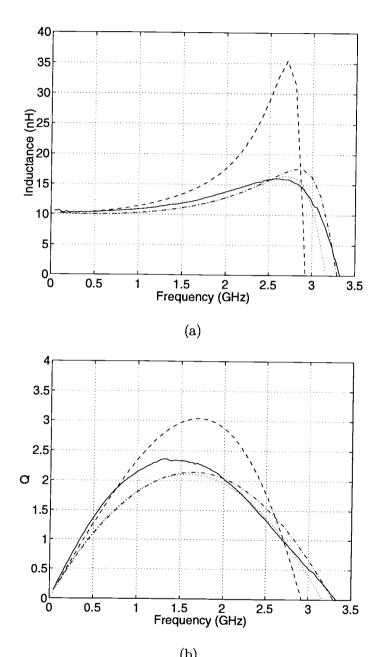

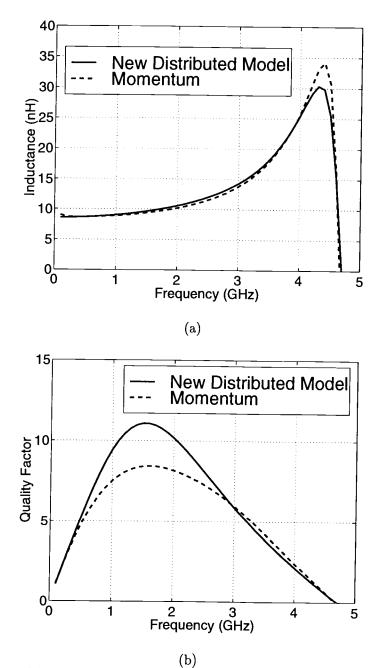

| 2.00 | model [36] and HP Momentum [37] for a multilevel spiral inductor in<br>a typical BiCMOS environment ( $\rho = 12 \ \Omega$ -cm)                                                                                                                                                                                         | 57 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

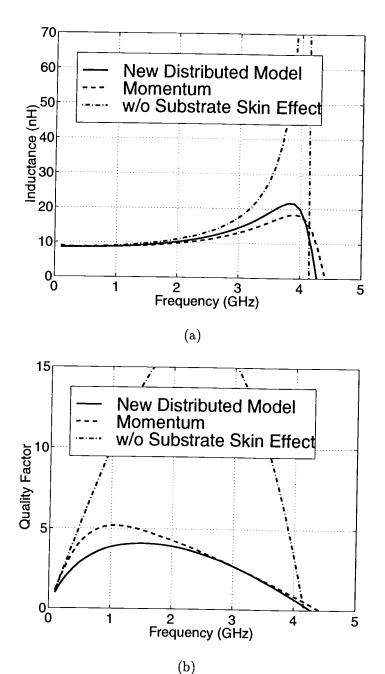

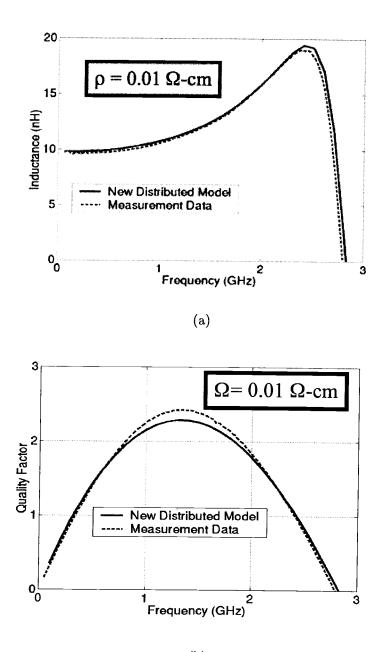

| 2.36 | 6 (a) inductance and (b) quality factor obtained with the distributed<br>model [36] and HP Momentum [37] for a multilevel spiral inductor<br>in a typical CMOS environment ( $\rho = 0.01 \ \Omega$ -cm). Results obtained<br>with a distributed model that neglects the substrate skin effect are<br>also shown        | 58 |

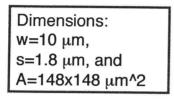

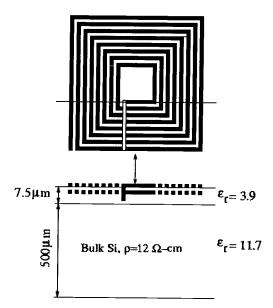

| 2.37 | Measured multilevel spiral on CMOS substrate.                                                                                                                                                                                                                                                                           | 59 |

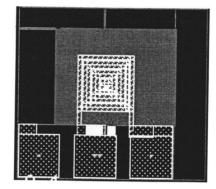

| 2.38 | (a) inductance and (b) quality factor of a multi-level spiral inductor for the distributed model versus VNA measurement data [37]. $\ldots$                                                                                                                                                                             | 60 |

| 2.39 | Parallel-connected spiral inductor used for simulation example                                                                                                                                                                                                                                                          | 61 |

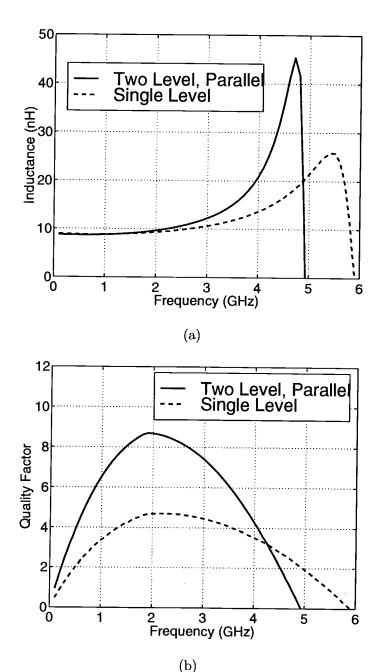

| 2.40 | Comparison of (a) inductance and (b) quality factor for a two level<br>parallel-connected spiral inductor and a single level spiral in a typical<br>CMOS environment ( $\rho = 12 \ \Omega$ -cm). All results are computed us-<br>ing distributed equivalent circuit models including the substrate skin<br>effect [36] | 62 |

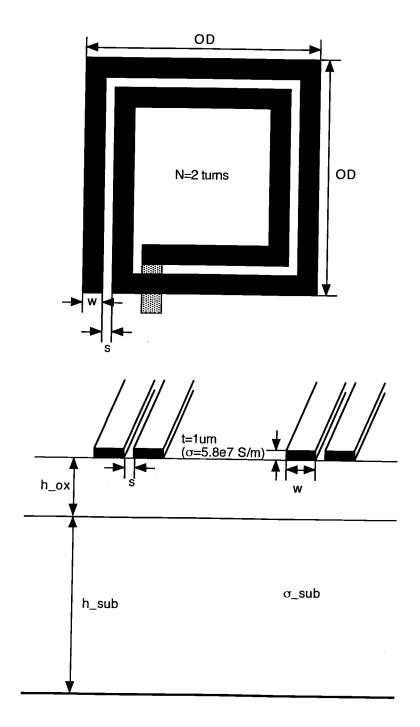

| 3.1  | Example 2-turn SLS and relevant dimensions.                                                                                                                                                                                                                                                                             | 68 |

| 3.2  | $Q_{max}$ (solid) and $f_{SR}$ (dashed) vs. $\sigma_{sub}$ for four-turn SLS inductor                                                                                                                                                                                                                                   | 70 |

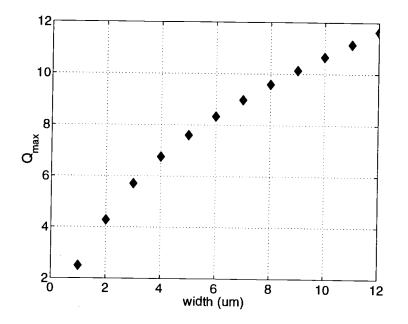

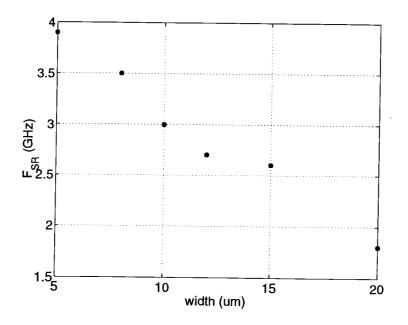

| 3.3  | $Q_{max}$ vs. trace width for OD = 200 $\mu$ m SLS inductor with constant pitch = 15 $\mu$ m                                                                                                                                                                                                                            | 71 |

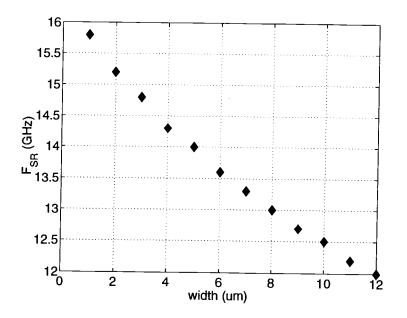

| 3.4  | $f_{SR}$ vs. trace width for OD = 200 $\mu$ m SLS inductor with constant pitch = 15 $\mu$ m                                                                                                                                                                                                                             | 72 |

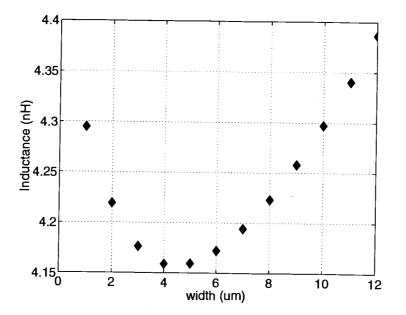

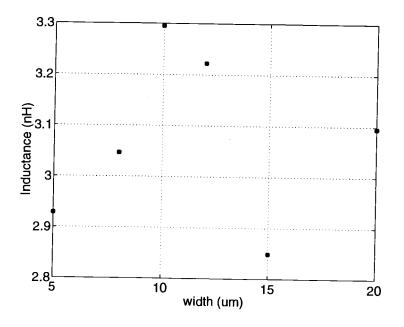

| 3.5  | Inductance vs. trace width for OD = 200 $\mu$ m SLS inductor with constant pitch = 15 $\mu$ m.                                                                                                                                                                                                                          | 72 |

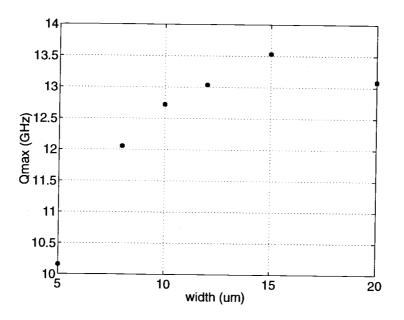

| 3.6  | $Q_{max}$ vs. trace width for approximately constant base inductance SLS inductor with constant pitch = 15 $\mu$ m                                                                                                                                                                                                      | 73 |

| 3.7  | $f_{SR}$ vs. trace width for approximately constant base inductance SLS inductor with constant pitch = 15 $\mu$ m                                                                                                                                                                                                       | 73 |

| 3.8  | Inductance vs. trace width for approximately constant base induc-<br>tance SLS inductor with constant pitch = $15 \ \mu m. \dots$                                                                                                                                                                                       | 74 |

Page

Figure

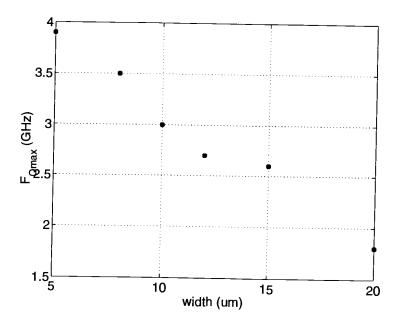

| 3.9  | $Q_{max}$ vs. trace width for OD = 200 $\mu$ m SLS inductor with s=2 $\mu$ m, variable turns and pitch.                       | 76 |

|------|-------------------------------------------------------------------------------------------------------------------------------|----|

| 3.10 | $f_{SR}$ vs. trace width for OD = 200 $\mu$ m SLS inductor with s=2 $\mu$ m, variable turns and pitch.                        | 76 |

| 3.1  | 1 Inductance vs. trace width for OD=200 $\mu$ m SLS inductor with s=2 $\mu$ m, variable turns and pitch                       | 77 |

| 3.12 | 2 $F_{Qmax}$ vs. trace width for OD = 200 $\mu$ m SLS inductor with s=2 $\mu$ m, variable turns and pitch.                    | 77 |

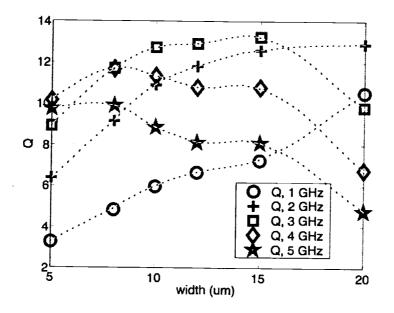

| 3.13 | <sup>3</sup> Q vs. trace width for 1-5 GHz for OD = 200 $\mu$ m SLS inductor with s=2 $\mu$ m, variable turns and pitch       | 78 |

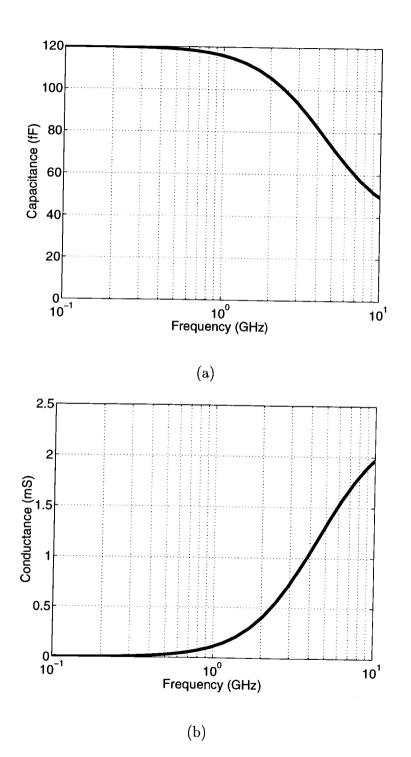

| 3.14 | a) Capacitance and b) Conductance vs. frequency for a typical spiral inductor on 10 $\Omega$ -cm bulk.                        | 79 |

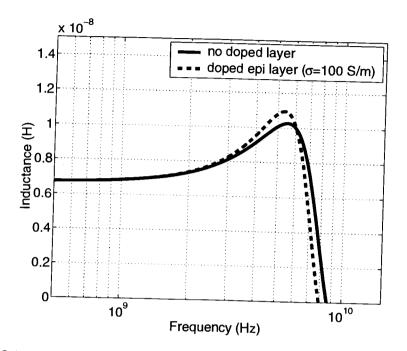

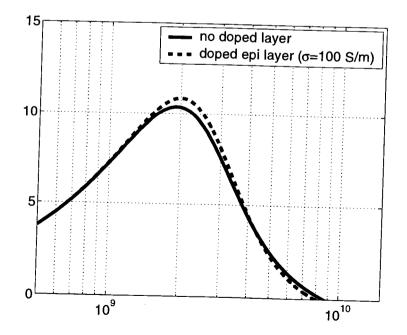

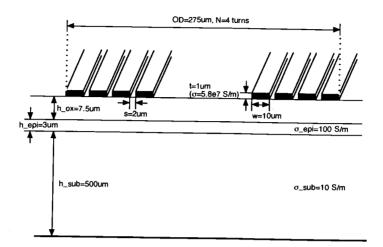

| 3.15 | Inductance for inductor with and without doped epitaxial layer                                                                | 81 |

| 3.16 | Quality factor for inductor with and without doped epitaxial layer. $\ldots$                                                  | 81 |

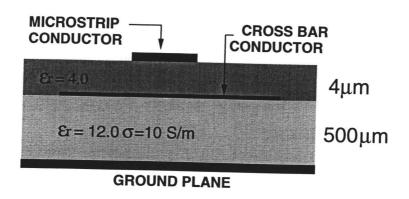

| 3.17 | Cross-section for plots in Figures 3.15 and 3.16                                                                              | 82 |

| 4.1  | Example of a two-level series-connected spiral inductor on lossy silicon substrate.                                           | 84 |

| 4.2  | Equivalent circuit modeling of multi-level structure on lossy substrate.                                                      | 84 |

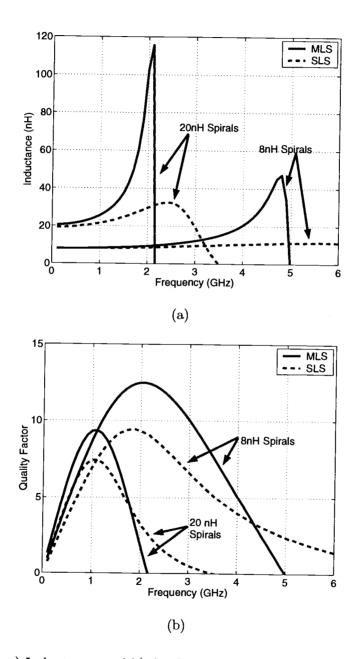

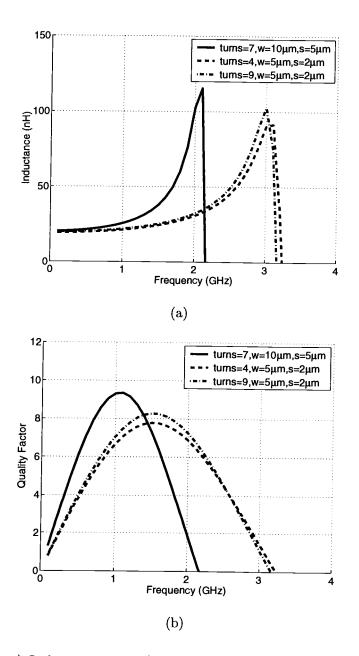

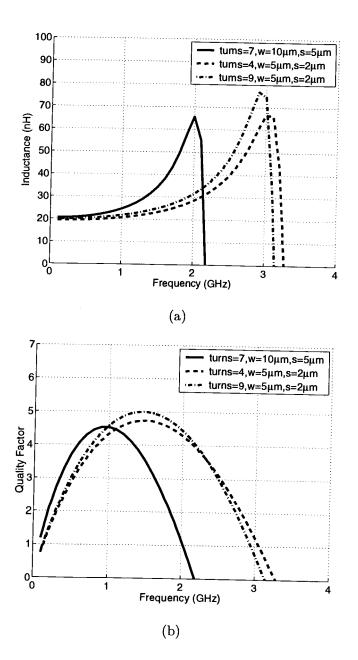

| 4.3  | a) Inductance and b) Quality Factor for 8 and 20 nH spiral inductors with $\rho_{sub} = 15\Omega - \text{cm.}$                | 87 |

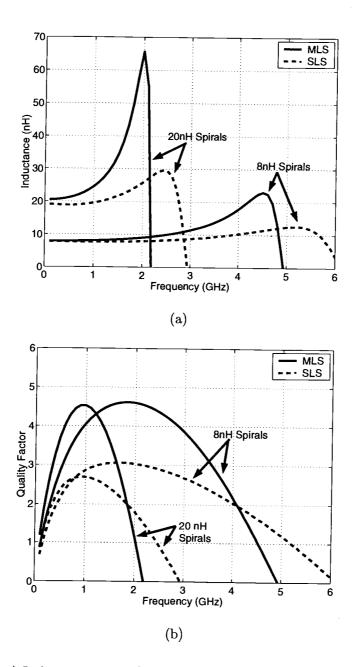

| 4.4  | a) Inductance and b) Quality Factor for 8 and 20 nH spiral inductors with $\rho_{sub} = 0.01\Omega$ -cm.                      | 88 |

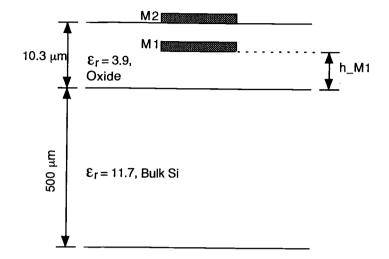

| 4.5  | Illustration of variable M1 height, $h_{M1}$ , for a multi-level spiral inductor.                                             | 89 |

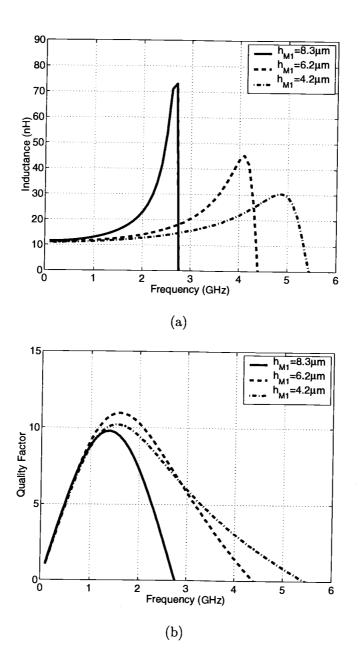

| 4.6  | a) Inductance and b) Quality Factor for 4-turn spiral inductors with variable M1 height and $\rho_{sub} = 15\Omega$ -cm.      | 90 |

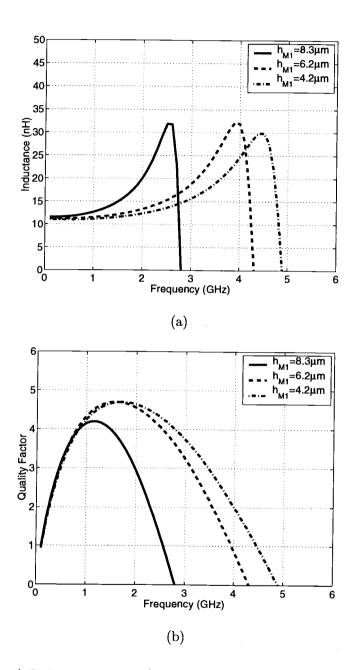

| 4.7  | a) Inductance and b) Quality Factor for 4-turn spiral inductors with variable M1 height and $\rho_{sub} = 0.01 \ \Omega$ -cm. | 91 |

| 4.8  | a) Inductance and b) Quality Factor for 20 nH spiral inductors with $\rho_{sub} = 15 \ \Omega - \text{cm}.$                   | 93 |

|      |                                                                                                                               |    |

Figure

| 4.9  | a) Inductance and b) Quality Factor for 20 nH spiral inductors with $\rho_{sub} = 0.01 \ \Omega - \text{cm}. \dots 94$                                                                     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

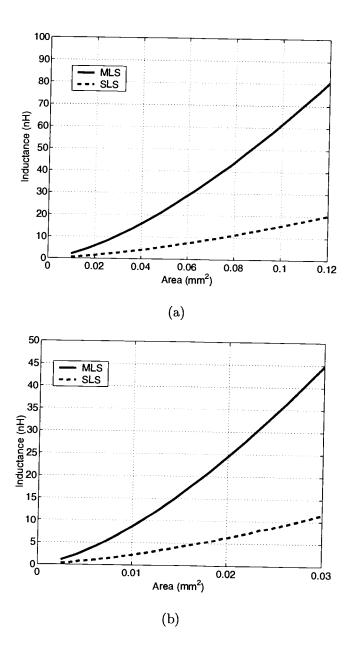

| 4.1  | 0 Inductance vs. Area for a) $w = 10 \ \mu m$ , $s = 5 \ \mu m$ , inner length $= 25 \ \mu m$ , b) $w = 5 \ \mu m$ , $s = 2 \ \mu m$ , inner length $= 20 \ \mu m$                         |

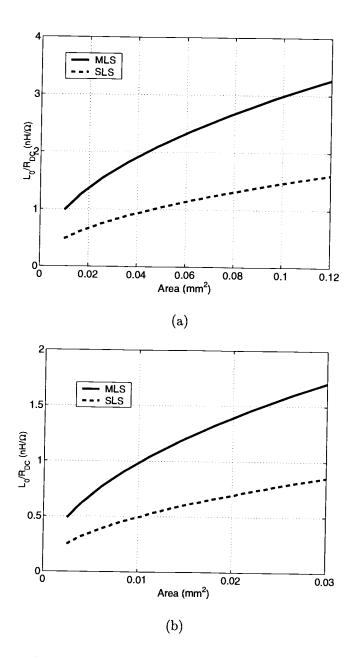

| 4.1  | 1 $L_o/R_{DC}$ vs. Area for a) w = 10 $\mu$ m, s = 5 $\mu$ m, inner length = 25 $\mu$ m,<br>b) w = 5 $\mu$ m, s = 2 $\mu$ m, inner length = 20 $\mu$ m ( $R_s = 15 \ m\Omega$ /square). 97 |

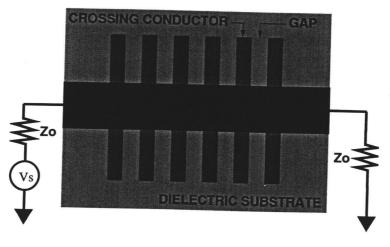

| 5.1  |                                                                                                                                                                                            |

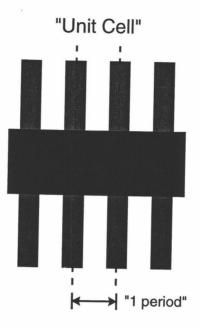

| 5.2  | Definition of unit cell and cell boundaries                                                                                                                                                |

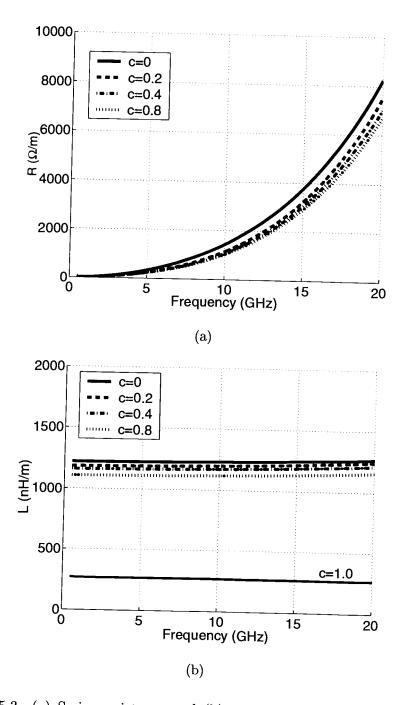

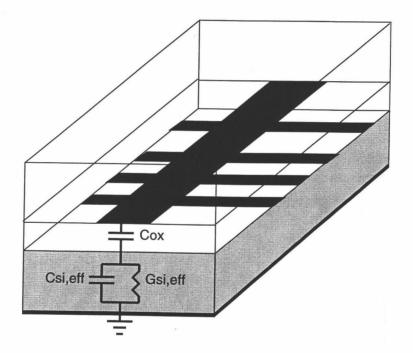

| 5.3  | (a) Series resistance and (b) inductance p.u.l. for $w = 10 \ \mu m$ inter-<br>connect with orthogonal gridded shield                                                                      |

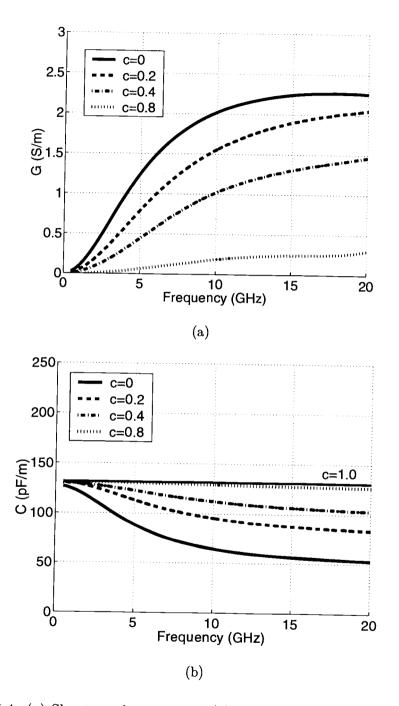

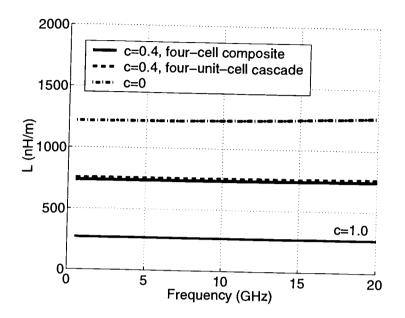

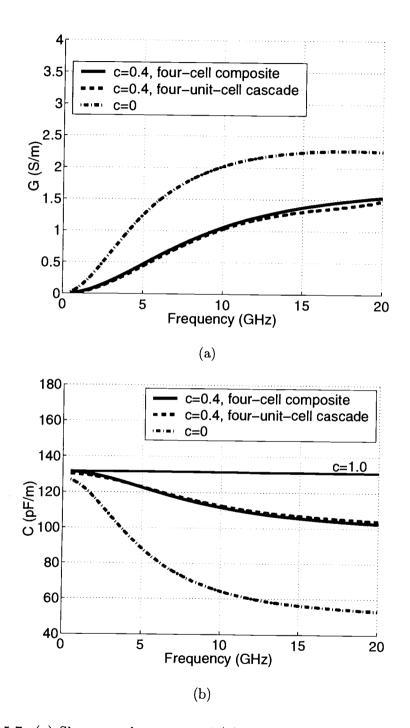

| 5.4  | (a) Shunt conductance and (b) capacitance p.u.l. for $w = 10 \ \mu m$ interconnect with orthogonal gridded shield                                                                          |

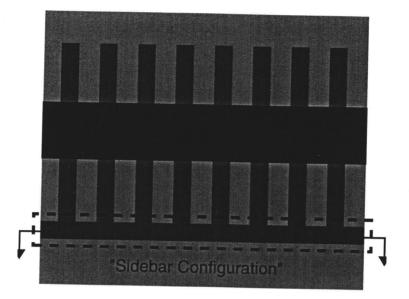

| 5.5  | Practical implementation of orthogonal gridded shield 109                                                                                                                                  |

| 5.6  | Inductance p.u.l. for $w = 10 \ \mu m$ interconnect with orthogonal gridded shield in sidebar configuration                                                                                |

| 5.7  | (a) Shunt conductance and (b) capacitance p.u.l. for $w = 10 \ \mu m$ interconnect with orthogonal gridded shield in sidebar configuration 111                                             |

| 5.8  | Equivalent circuit for effective shunt admittance of interconnect with orthogonal gridded shield                                                                                           |

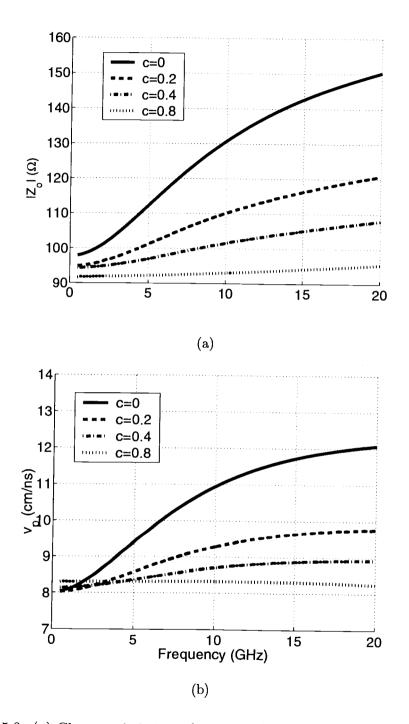

| 5.9  | (a) Characteristic impedance and (b) phase velocity for interconnects of width $w = 10 \ \mu m$ with orthogonal gridded shield                                                             |

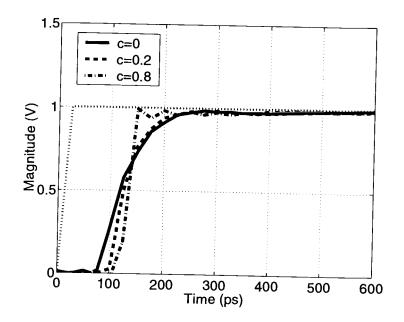

| 5.10 | Comparison of step responses for shielded and unshielded interconnects. 116                                                                                                                |

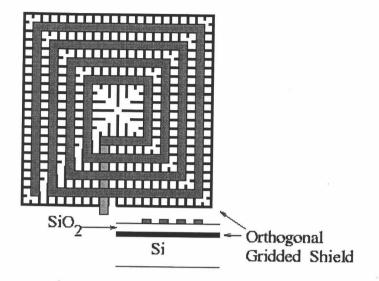

|      | Example of spiral inductor with patterned ground shield (PGS). $\dots$ 117                                                                                                                 |

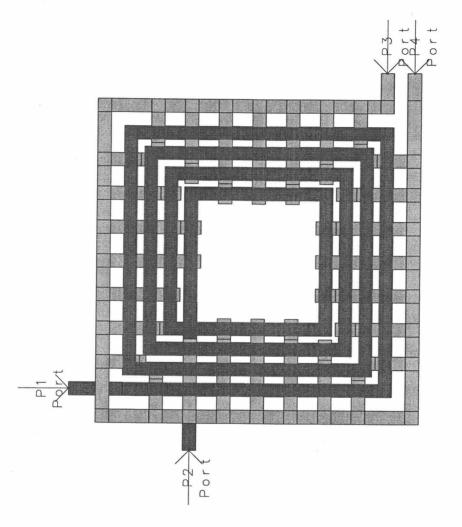

|      | Example 4-turn spiral inductor with PGS used to test various shield-<br>ing cases                                                                                                          |

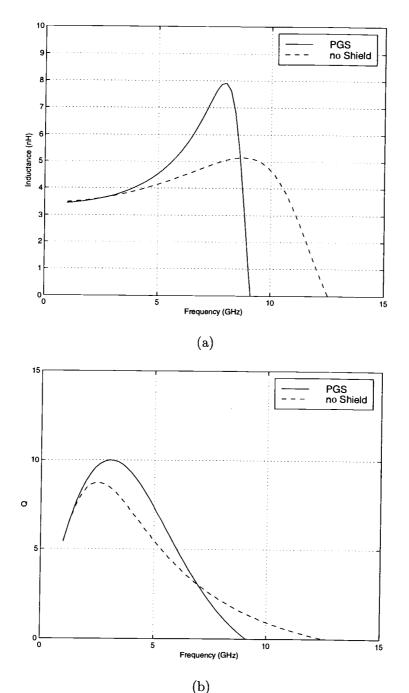

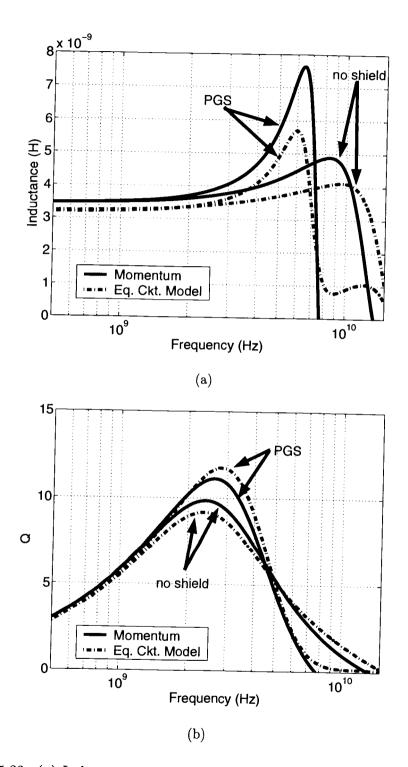

| 5.13 | (a) Inductance and (b) Q for a 4-turn spiral with and without pat-<br>terned ground shield (PGS)                                                                                           |

Figure

| Figur | Page                                                                                                                    |

|-------|-------------------------------------------------------------------------------------------------------------------------|

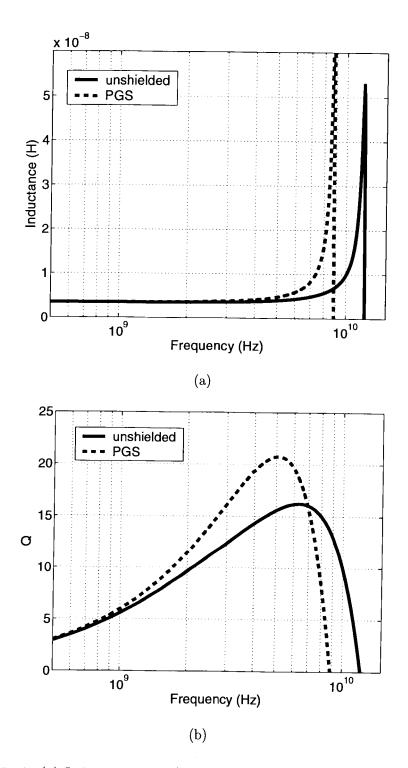

| 5.14  | (a) Inductance and (b) quality factor for 4-turn spiral inductor with and without PGS, $\rho_{sub} = 1000 \ \Omega$ -cm |

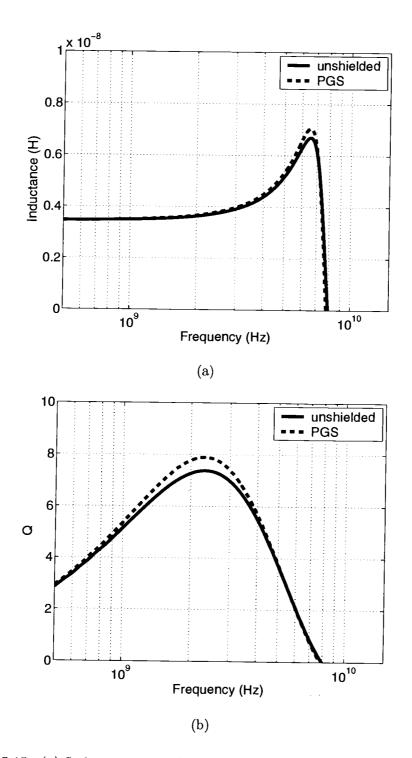

| 5.15  | (a) Inductance and (b) quality factor for 4-turn spiral inductor with and without PGS, $\rho_{sub} = 1 \ \Omega$ -cm    |

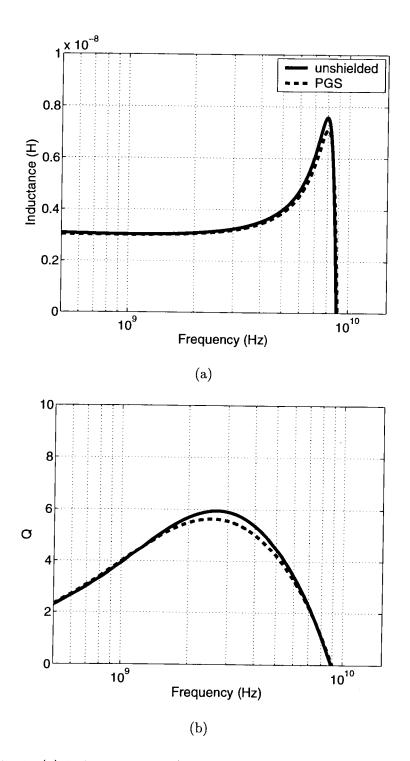

| 5.16  | (a) Inductance and (b) quality factor for 4-turn spiral inductor with and without PGS, $\rho_{sub} = 0.01 \ \Omega$ -cm |

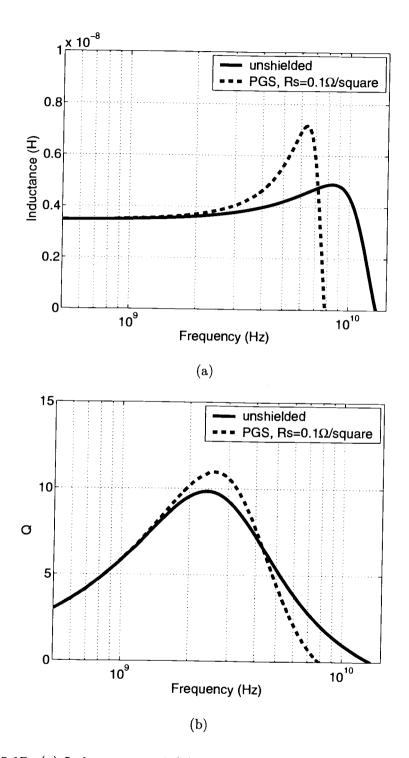

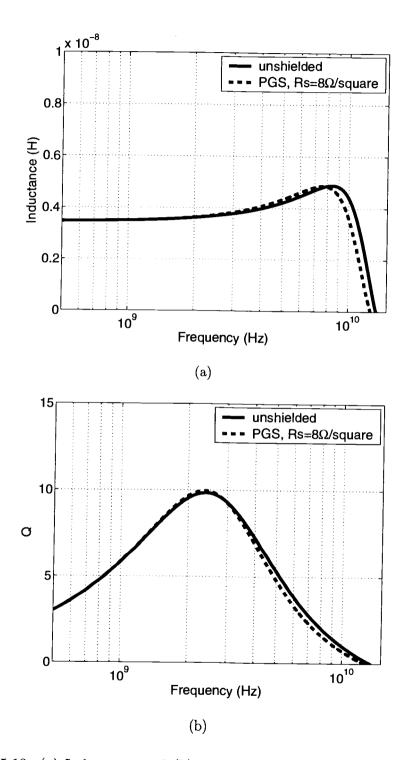

| 5.17  | (a) Inductance and (b) quality factor for 4-turn spiral inductor with and without PGS, $R_s = 0.1 \Omega$ /square       |

| 5.18  | (a) Inductance and (b) quality factor for 4-turn spiral inductor with and without PGS, $R_s = 8 \Omega/\text{square.}$  |

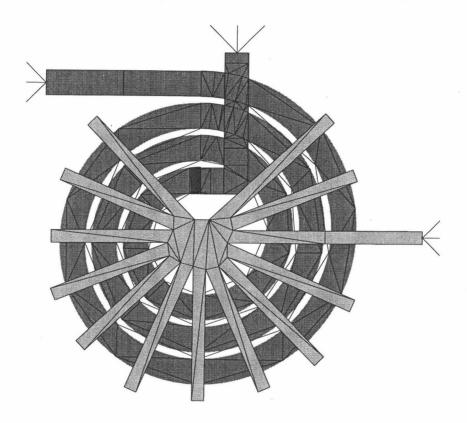

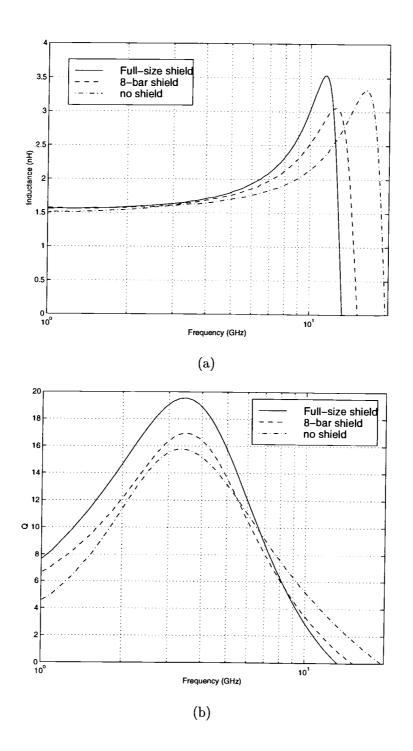

| 5.19  | Example round spiral inductor with star pattern ground shield 127                                                       |

| 5.20  | (a) Inductance and (b) Q for a round spiral inductor versus shielding coverage                                          |

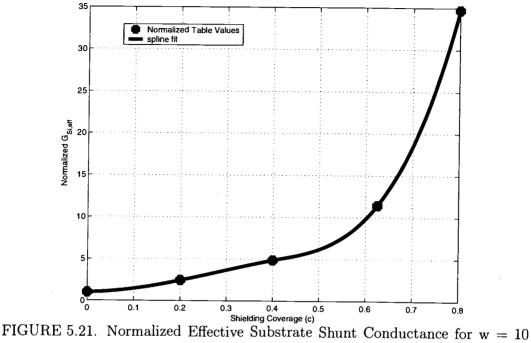

| 5.21  | Normalized Effective Substrate Shunt Conductance for $w = 10 \ \mu m 130$                                               |

| 5.22  | (a) Inductance and (b) quality factor for 4-turn spiral inductor with                                                   |

#### LIST OF TABLES

<u>Table</u>

| 3.1 | Summary of Inductor Geometry Variations.                                                      | 75  |

|-----|-----------------------------------------------------------------------------------------------|-----|

| 4.1 | Summary of Single and Multi-level Inductor Parameters.                                        | 85  |

| 5.1 | Effective Substrate Conductance versus Shielding Coverage Extracted<br>using (5.10) at 10 GHz | 114 |

#### Page

#### LIST OF APPENDIX FIGURES

Figure

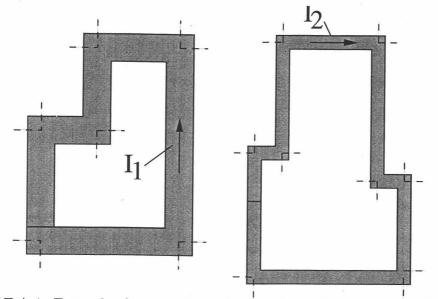

| A-1 | Example of two conductor loops to be analyzed in terms of straight line sections |

|-----|----------------------------------------------------------------------------------|

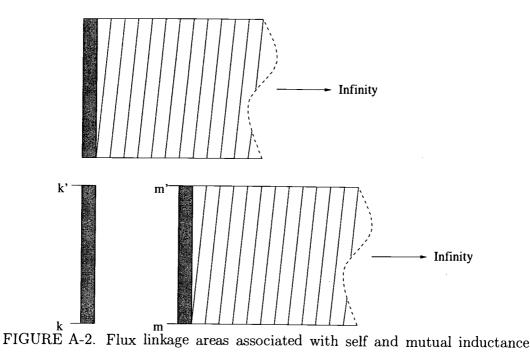

| A-2 | Flux linkage areas associated with self and mutual inductance calculations       |

| B-1 | Structure used for solution of magnetic potential                                |

| B-2 | Two-line microstrip structure used for self and mutual inductance calculations   |

| D-1 | Matlab script for calculating $M_b$ , 'mrebar.m'                                 |

#### Page

#### DEDICATION

This thesis is dedicated to the memory of my parents, Richard and Dorothy Lutz, who provided me with the guidance, love and support for me to be successful in my educational endeavors as well as life in general.

# INDUCTORS IN HIGH-PERFORMANCE SILICON RADIO FREQUENCY INTEGRATED CIRCUITS: ANALYSIS, MODELING, AND DESIGN CONSIDERATIONS

#### 1. INTRODUCTION

The advent of silicon-based Radio Frequency Integrated Circuits (RFICs) in the communications sector has led to a need for low-cost, small form factor components. To visualize this, consider the evolution of cellular telephone handsets, as shown in Figure 1.1, from the bulky, heavy and expensive phones that were used by a small percentage of the world population in the 1980's, to the small, lightweight phones of today used by millions of people worldwide. On the left side of Figure 1.1 is the Motorola<sup>©</sup> [1] DynaTAC 8000X, the world's first commercial cellular telephone, which had a retail price of approximately \$3,500 and weighed 28 ounces, while the right side shows an example of a modern cellular phone, which typically weighs 3 to 4 ounces and has a retail price in the range of \$100 - \$200. In addition to reduced-size, low-cost RFIC components, there is also demand within the communications industry for higher levels of integration that result in reduced component count for a given product. One method to lower the component count is to integrate passive devices, such as inductors and capacitors that are often implemented as off-chip components, onto the semiconductor die. This reduces the assembly time and cost for equipment manufacturers. The need to place passive components on an integrated circuit brings about different design issues than for traditional off-chip components owing to the fact that integrated circuits are fabricated on semiconducting substrates (i.e. silicon) rather than

FIGURE 1.1. Evolution of cellular telephone handsets.

low-loss materials such as alumina, duroid or semi-insulating Gallium Arsenide (GaAs). An illustration of a spiral inductor integrated onto a semiconductor die is shown in Figure 1.2.

Quality factor is traditionally defined as the ratio of angular frequency times energy stored to the power loss [2]:

$$Q = \frac{\omega U}{W} \tag{1.1}$$

where U represents the sum of electric and magnetic field energy storage and W is the energy loss per second, or power loss. For purposes of spiral inductors in integrated circuits, the industry-standard definition for Q as a figure of merit is given as

$$Q = \frac{\Im \left[ Z_{\rm in} \right]}{\Re \left[ Z_{\rm in} \right]} \tag{1.2}$$

where  $Z_{in}$  is the input impedance of the inductor at a given frequency for the desired operating condition (i.e. single-ended or differential excitation), and  $\Im$ []

FIGURE 1.2. Example of spiral inductor integrated onto semiconductor die.

and  $\Re$ [] denote the imaginary and real parts of a complex number, respectively. This expression is derived from the formula for Q of a series RLC resonant circuit at its resonant frequency,  $\omega_0$ ,

$$Q_{\text{series-RLC}} = \frac{\omega_0 L}{R}.$$

(1.3)

Since an inductor is often used as part of a resonant circuit, the ratio of its effective inductance times angular frequency to the effective resistance is indicative of its performance in such a circuit if the resonating capacitor is assumed to be ideal.

High-performance RFICs designed for use in communication devices, such as hand-held units (e.g. cellular telephones) and wireless local area network (WLAN) devices, in general require high Q passive components to enable them to adhere to the strict phase-noise and bandwidth requirements of modern telecommunications standards. Hence, the Voltage Controlled Oscillator (VCO) LC tankcircuits and matching networks used in RFICs must use high-Q inductors and capacitors. Often, the limiting factor for RFICs fabricated on silicon is the Q of the inductors, since the on-chip capacitors generally do not interact as much with the silicon substrate. Capacitors are usually of the Metal-Insulator-Metal (MIM) variety, and thus the majority of the electric field is vertical and confined to the upper-layers of dielectric material. Conversely, inductors are traditionally fabricated on-chip using a spiral pattern on the upper layers of metal for the process, resulting in a magnetic field that penetrates deep into the semiconducting substrate below as well as the space above the spiral, which is usually some sort of packaging material such as plastic. Semiconductors contain free charge, and when these charges are moved by the electric fields and electro-motive forces (EMF's) induced by the spiral inductor, the net effect on inductor performance is to lower its Q as a result of the increased power dissipation.

Often, spiral inductors in an RFIC are the most easily recognizable feature on the die, owing to their relatively large size compared to the transistors and other components on the chip. Since the goal of industry is not only to produce high performance chips, but to also offer them to customers at the lowest possible price, the overall size of a silicon chip is, of course, a key concern for semiconductor manufacturers. Methods for reducing the 'real-estate' occupied by on-chip inductors are thus a high priority for the RFIC industry. One way to accomplish such an area reduction is the use of multiple metal layers offered by modern silicon fabrication processes to create 3-D designs that have smaller footprints than typical single-level spirals with the same inductance value.

While the Q's of on-chip inductors are often inferior to off-chip components such as air-coil inductors, the cost savings and simplified circuit design aspects make on-chip integration attractive to manufacturers. Also, the manufacturing tolerances of on-chip components fabricated in a typical silicon process are generally much tighter than those of external off-chip components, furthering the argument for moving components such as inductors onto the die. Unlike an offchip inductor, an inductor fabricated on-chip does not require connection through package pins and bondwires, and thus the parasitics associated with using off-chip inductors are eliminated when an on-chip solution is used. This lack of package parasitics translates to a lower on-chip Q requirement than that of an off-chip spiral inductor, since the effective Q on the die of off-chip spirals is lowered by the package parasitic resistance and capacitance. However, the Q's to which onchip spirals must aspire are still relatively large for high performance chip designs. Hence, accurate modeling and design of on-chip spiral inductors are imperative for ensuring successful RFIC design.

The conventional modeling techniques used for monolithic spiral inductors fabricated in low-loss media are not adequate for spiral inductors in a lossy substrate environment such as silicon. Because silicon is a semiconducting material by nature, there is often significant power loss due to conduction currents in the bulk substrate when a spiral inductor is energized above it. The conduction and displacement currents in the bulk substrate may be decomposed into longitudinal and shunt components and analyzed separately, making the model formulation more straightforward and intuitive. The longitudinal current components result mainly from magnetically induced EMF's by virtue of the magnetic field produced by the spiral inductor, whereas the vertical current components are a product of the vertical electric fields produced by the finite voltage excitation driving the inductor. Thus, for conditions where the substrate dimensions are small compared to wavelength, quasi-magnetostatic and quasi-electrostatic solution techniques may be applied for the longitudinal and shunt current components respectively. In terms of potentials, the problems reduce to one of magnetic vector potential and one of electric scalar potential. The modeling methodology developed in this thesis addresses the limitations of conventional spiral inductor modeling techniques by including the impact of semiconducting substrates in terms of both longitudinal and shunt substrate current components.

Two methods for enhancing the performance of conventional planar spiral inductors in silicon technology are the implementation of multilevel structures and the use of patterned ground shields. Multilevel spirals make use of the multiple metal level systems offered by most silicon-based fabrication processes and allow a high inductance per unit area to be obtained owing to the high coupling factor between the metal levels where interlayer dielectric thicknesses are on the order of 1-2 microns. Patterned ground shields generally consist of an arrangement of conductive fingers that are orthogonal to the current flow in the inductor and can raise inductor Q by shunting much of the vertical conduction currents through a low loss path rather than through the lossy silicon substrate. The modeling methodology presented in this thesis was used to simulate various structures that utilize these two enhancement methods and evaluate their performance.

Since spiral inductors are such a key component of RFIC design, some of the recent research work has focused on optimization and improvement of inductor performance within various design constraints. The optimization technique presented in [3] relies on the use of extensive experimental data to develop fitting equations for the various spiral inductor model elements that are being optimized. Others have relied solely on experimental data and are able to determine trends in inductor performance through numerous process experiments [4]. Another recently published work includes many of the significant parasitic effects of semiconductor processes in the reported modeling tools, allowing for more accurate predictions and optimizations of performance for an array of process variables [5]. This is particularly useful when a semiconductor process is under development and the various process parameters such as doping levels and dielectric thicknesses are constantly changing, which, as a matter of course, leads to variations in inductor performance. Fabrication techniques that utilize air-suspended microstrip technology have been presented in [6] and show significant spiral performance improvement, although the high-volume manufacturability of such a process has yet to be shown. The use of patterned metallization, polysilicon and well/trench structures has also been shown to provide performance enhancements for certain process conditions, as presented in [7] and [8].

Experimental studies presented in [9] and [10] demonstrate design methods that exploit the inherent performance advantages of multilevel interconnect systems that have relatively thick metallization layers, namely constructing spiral inductors that utilize more than one layer of metal, which offers additional degrees of design freedom. The resulting structures are often referred to as dual-level or multi-level inductors. These types of inductors are a main focus of this thesis, particularly in terms of analysis, simulation and design optimization for RFICs. Such dual-level designs have also been fabricated and tested on Gallium Arsenide (GaAs) substrates in [11].

Chapter Two presents modeling techniques for both single and multilevel spiral inductors. Both single and coupled line structures are studied as fundamental components of spiral inductors. The use of a complex virtual ground plane approach is shown to be an efficient way to achieve accurate calculations of the parasitic effects of silicon on inductance and series resistance of microstrip lines and spiral inductor. The importance of inclusion of the so-called eddy-current effects on inductance and series resistance of spiral inductors over high-loss substrates is examined.

Chapter Three investigates the effects of silicon process and spiral geometry on inductor performance. Specifically, variations in the parameters related to the fabrication process such as bulk resistivity, as well as differing inductor geometries, are considered as 'knobs' in determining a spiral inductor's quality factor and inductance at microwave frequencies.

Chapter Four focuses on design considerations for multilevel spiral inductors versus single level spiral inductors over silicon. The use of multilevel spiral inductors is proposed as another degree of design freedom and is the main focus of the chapter. The relationships between various designs and geometries and performance metrics such as Quality Factor (Q) and usable frequency range are presented.

Methods for mitigation of undesirable effects of silicon on inductor and interconnect performance are presented in Chapter Five. Various configurations and material properties are examined for so-called "patterned ground shields", which electrically shield passive components from semiconducting substrate effects without substantially affecting inductance.

Chapter Six presents conclusions and suggestions for future work in the area of high-performance inductors and other passive components on silicon. The ongoing design challenges faced by the wireless and datacom industries are considered in terms of their future modeling requirements for on-chip passive components.

#### 2. MODELING TECHNIQUES FOR SINGLE AND MULTILEVEL SPIRALS

#### 2.1. Introduction

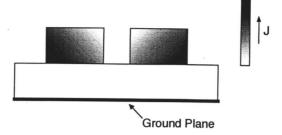

RFIC designs in lossy media incorporating passive structures, such as microstrip spiral inductors, require modeling techniques that properly address the loss mechanisms involved, particularly those losses due to semiconducting substrate effects. Spiral inductors fabricated in Si-based circuits often have poor quality factors due to high-resistivity metallization and lossy substrates. In addition, substrate currents can adversely affect the inductance of a spiral inductor for certain frequencies and substrate conductivities. Figure 2.1 illustrates these substrate currents. However, because of the low-cost aspects of silicon technology, such structures remain attractive, thus prompting the formulation of accurate modeling and design techniques.

Although an inductor's primary function is to provide magnetic energy storage and a particular reactance at a given frequency, the geometries of spiral inductors fabricated in typical silicon-based technologies, in general, have dimensions such that their so-called 'parasitic' reactances and losses have a substantial impact on the overall inductor performance. Thus, the problem of modeling a spiral inductor in silicon is not one of simply calculating an inductance value from some closed-form approximation, finding the net DC resistance of the metal, and constructing a simple series 'LR' branch to represent the spiral inductor in an equivalent circuit. While the magnetic field is the quantity of interest for a spiral inductor, its interaction with surrounding substrate materials as well as with other parts of the spiral inductor itself give rise to losses that must be properly accounted for. Additionally, because spiral inductors in silicon are typically only a few microns above a semiconducting material and are also in the presence of other dielectric media such as oxide, the parasitic capacitance terms must also be computed and included in any equivalent circuit model. This is particularly important if the predicted capacitance is expected to cause the inductor to selfresonate near its intended operating frequency. Self-resonance for a spiral inductor is defined as the condition when the inductor's input impedance is purely real, that is, there is zero reactance, neither inductive nor capacitive. The frequency at which this occurs is commonly known in the industry and research community as the self-resonant frequency,  $f_{SR}$ . The complicated nature of the electromagnetic fields and corresponding equivalent circuit representations for spiral inductors in silicon are primary reasons that full-wave 3D EM simulators are often employed by engineers and researchers for predicting and analyzing their behavior. However, the computational cost of full-wave solvers in terms of time can often be prohibitive, and thus there is a demand for less-complex, time-efficient modeling solutions for spiral inductors in a semiconducting substrate environment.

FIGURE 2.1. Substrate currents in Si-SiO<sub>2</sub>-based spiral inductor structures.

Numerous design techniques for spiral inductors attempting to improve performance have been proposed and tested, including the use of multiple metallization layers [9, 10], high resistivity substrates [12], as well as air suspended spirals [13]. One area of focus in this chapter is analysis and modeling of enhancedinductance/area-ratio multilevel spiral inductors (MLS), such as those being fabricated currently in silicon-based RFICs and GaAs MMICs [10, 14].

Even though a number of experimental results have been reported, accurate distributed models and modeling methodologies for both single and multilevel spiral inductors incorporating all of the conductor and substrate losses and reactive coupling are generally not readily available. Often, as mentioned previously, computationally intensive 3-D EM simulators are invoked to model these structures. The modeling techniques for spiral inductors fabricated on lossy substrates in [9] and [15] address the shunt currents in the silicon substrate and prove to perform quite well for relatively high resistivity substrates such as those found in BiCMOS processes. However, longitudinal substrate currents can have a dominant effect in an environment such as CMOS, where substrate resistivities are on the order of  $\rho = 0.01 \ \Omega$ -cm ( $\sigma = 10,000 \ S/m$ ), as addressed in [16]–[18]. Hence, a general analysis of the substrate effects and development of a modeling technique is necessary for both simple single-level spirals (SLS) as well as more complex multilevel spiral (MLS) structures, such as the designs described in [9], [13].

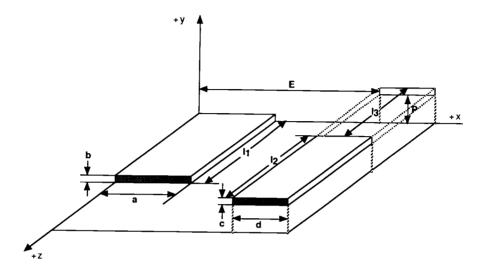

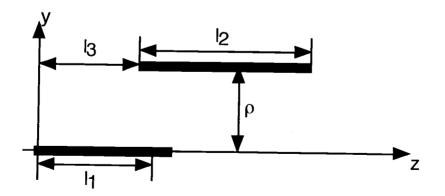

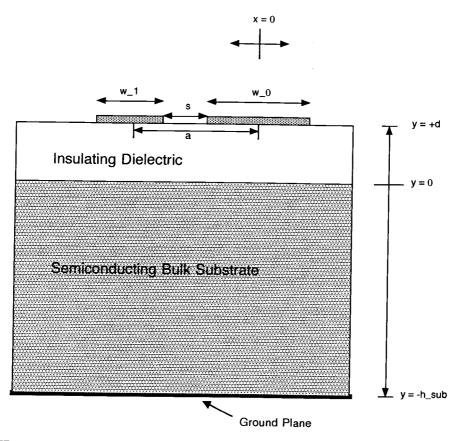

In this chapter, a complete modeling methodology for single (SLS) and multilevel spirals (MLS) on lossy substrate is presented. Two example structures, a SLS and MLS, are illustrated in Figures 2.2 and 2.3. The multilevel configuration in Figure 2.3 consists of two series-connected spirals and may be viewed as a top level coil, which spirals inward, placed directly on top of an identical coil on the lower level, which spirals outward in the same sense (e.g. clockwise). Such seriesconnected spirals are often referred to as enhanced inductance spirals, as they yield a substantial increase in base inductance value over a single level spiral of equal area due to the mutual inductance between the two coils, which is often, in

FIGURE 2.2. Example of Si-SiO<sub>2</sub>-based single-level spiral inductor structure.

modern IC processes, nearly equal (e.g. 90-95%) to the inductance, L, of one of the coils, as shown in Figure 2.4, and thus  $L_{\text{series}} = 2L + 2M = \sim (3.8...3.9) \times L$ . The two spirals may also be connected in a parallel configuration, as shown in Figure 2.5, in order to lower series resistance, which effectively makes the spiral thicker and thus have a slightly lower inductance  $(L_{\text{parallel}} = [L+M]^2/[2L+2M)] =$  $[L+M]/2 = \sim (0.95...0.975) \times L)$ . The modeling methodology presented in this chapter takes into account all significant coupling effects between the different segments of a spiral structure as well as the lossy substrate. In particular, the models consider the substrate skin effect, which leads to higher losses and reduced inductance, especially for heavily doped CMOS substrates.

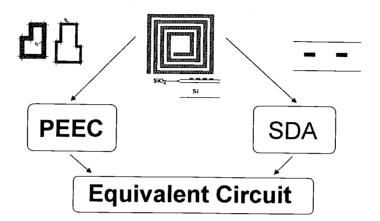

To briefly summarize the solution methods employed in the following models, a generalized flow-chart is shown in Figure 2.6. For parasitic capacitance/conductance calculations, Spectral Domain Approach (SDA) algorithms are employed that are able to handle multilayer substrates with multiple conductivities. Inductance and resistance calculations are carried out using common partial

FIGURE 2.3. Example of a two level series-connected spiral inductor on lossy silicon substrate.

FIGURE 2.4. Schematic representation of series-connected spiral inductor showing typical mutual inductance achievable with modern IC processes.

FIGURE 2.5. Schematic representation of parallel-connected spiral inductor showing typical mutual inductance achievable with modern IC processes.

inductance expressions combined with both closed-form skin effect formulae as well as spatial-domain or complex virtual ground plane height techniques [18] in order to include the semiconducting substrate effects. The complete equivalent circuit formulation can be described as a Partial Element Equivalent Circuit (PEEC) [19] ' type of distributed model, where the spiral inductor is partitioned and the corresponding self and mutual impedance and admittance terms are solved for using the methods outlined above.

The losses in a spiral inductor in silicon are primarily due to finite conductivity metallization and EM interaction with the semiconducting substrate. Because the modeling approach developed here addresses these mechanisms separately, the net effect of each loss component may be analyzed by selectively turning 'on' or 'off' the corresponding parts of the model (e.g. set conductor losses to zero in order to see the effect of longitudinal currents in the semiconductor on effective series resistance).

FIGURE 2.6. General flow-chart of spiral inductor modeling technique.

#### 2.2. Limitations of Simple Compact Models for Low-Loss Spiral Inductors

For a general spiral inductor structure above a low-loss substrate, the modeling methodologies are well known and generally consist of simple lumped element equivalent circuits [20]. Partial inductances and capacitances may be determined from closed-form equations [19], [21] and, when included with the strip resistance, form the basis of an equivalent circuit representation for a low-loss structure. Additional losses due to conductor metallization skin depth and imperfect dielectrics may also be easily incorporated.

Likewise, equivalent circuit models for spiral inductors based in Si-SiO<sub>2</sub> systems have been developed for 'high'-resistivity substrates (e.g. 10 S/m) [9], [15]. Typically, the substrate losses are addressed via inclusion of shunt conductances to represent the silicon substrate and associated transverse (shunt) currents. An example of such an equivalent model is shown in Figure 2.7. This type of model proves to be sufficient for conductivities on the order of 10 S/m or less, frequen-

FIGURE 2.7. Simple equivalent circuit for 'high'-resistivity Si substrates.

cies in the low Gigahertz range (i.e. not broadband), and typical semiconducting substrate heights (e.g. ~ 500  $\mu$ m). However, when the product of conductivity and frequency ( $\sigma\omega$ ) becomes significantly large and the skin depth,  $\delta = 1/\sqrt{\pi\mu\sigma f}$ , of the semiconducting substrate is small relative to its thickness, such equivalent circuit models for spiral inductors are not adequate. Thus, additional effects, particularly those due to longitudinal substrate currents, must also be addressed and included in an accurate model for these spiral inductors with higher conductivity substrates and frequencies of operation. These effects will be discussed in more detail later in this chapter.

#### 2.3. Why Compact Models Fail for Some Spiral Inductors

In addition to the limitations of previously published models described in the preceding section, compact spiral inductor models also suffer from limitations associated with the overall simplicity of their topology. To best illustrate the limiting factors that cause compact inductor model topologies to fail, consider an ideal transmission line that is represented by a single- $\pi$ -network. Above a certain frequency, this type of line model breaks down because it does not properly capture the distributed nature of a transmission line. The same can be said for a spiral inductor whose total line length (i.e. when it is "un-coiled") is on the order of a wavelength at its operating frequency. This supports the case for construction of more accurate distributed spiral inductor models. A 'double- $\pi$ ' type model that yields better broadband accuracy was presented in [22]. This may be viewed as a compromise in terms of accuracy versus simplicity between the distributed modeling techniques presented in this thesis and the simple single- $\pi$  inductor model.

# 2.4. Fundamental Modeling Techniques for Microstrip Structures on Silicon

Microstrip structures fabricated in conventional silicon technologies are a common component of many mixed-signal and analog integrated circuits. Spiral inductors along with simple single and coupled line structures are a class of microstrip devices. Because of the multiple conductivities and relative permittivities involved in modern silicon processes, the propagation characteristics of even a simple strip of metal are complex functions of frequency. Additionally, the lossy nature of semiconducting substrates at microwave frequencies has added to the design difficulties. However, if microstrip can be successfully analyzed and modeled for a particular process over a wide range of geometries, then successful RFIC design is possible at frequencies above 1 GHz.

#### 2.4.1. Analysis and Modeling of Single and Coupled MIS Structures

Consider the propagation characteristics of a Si-SiO<sub>2</sub> microstrip configuration as a basic element of the planar spiral inductor, as shown in Figure 2.8. The planar conductor is above a double layer substrate consisting of silicon dioxide (SiO<sub>2</sub>, commonly referred to as simply 'oxide' for a silicon based process), over bulk silicon. As described in the literature [23], three fundamental modes, namely, slow-wave, skin-effect, and dielectric quasi-TEM, can propagate in such a system, each having a certain frequency range for a given set of material parameters and geometry. Of particular interest for the case of the microstrip spirals in technologies with relatively low bulk resistivity (i.e.  $0.01 \ \Omega$ -cm) is the skin-effect mode, which is characterized by significant longitudinal, often called 'eddy', currents that serve to increase the effective series resistance and also decrease the net inductance with increasing frequency. Many production CMOS processes today utilize such low resistivity bulk materials.

The skin-effect mode [23] exists when the skin depth,  $\delta$ , of the substrate material is on the same order as or less than the semiconducting substrate height. The quantity  $\delta$  is calculated by

$$\delta = \frac{1}{\sqrt{\pi f \mu \sigma}},\tag{2.1}$$

and represents the depth at which current density in a conductor is reduced to 1/e of its value at the surface, as well as the effective thickness of a conductor

FIGURE 2.8. Equivalent circuit for  $Si-SiO_2$  microstrip coupled lines in skin effect mode.

at a particular frequency for purposes of resistance calculations. In other words, with increasing frequency, the semiconducting substrate begins to behave as a lossy conductor wall and the longitudinal currents, which lower inductance perunit-length, are closer to the substrate/oxide interface. This in turn yields an inductance and associated loss that are both frequency dependent. An equivalent circuit model for a Si-SiO<sub>2</sub> coupled microstrip line configuration is shown in Fig. 2.8. The capacitances, both shunt and nearest-neighbor line-to-line, and shunt conductances ares determined via a quasi-static Spectral Domain Analysis (SDA) [24] with complex dielectric constants to represent the semiconducting layers. The equivalent shunt elements in the common  $C_{ox} - G_s ||C_s$ , or simply C-G-C, topology may be determined by evaluating the microstrip structure using SDA at one frequency and then calculating the element values of the corresponding equivalent circuit subject to the relationship:

$$G_s = \frac{\sigma_s}{\epsilon_s} C_s. \tag{2.2}$$

The relationship in 2.2 can be derived by examining the formula for capacitance and conductance in terms of the field quantities for charge, current and electric field. Assuming that the silicon/oxide interface is an equipotential plane, a potential difference V may exist between this plane and the ground plane below, as shown in Figure 2.9. The expression for conductance may be written as

$$G_{s} = \frac{I}{V}$$

$$= \frac{\oint_{S} \mathbf{J} \cdot \mathbf{dS}}{V}$$

$$= \frac{\oint_{S} \sigma_{s} \mathbf{E} \cdot \mathbf{dS}}{V}, \qquad (2.3)$$

while for capacitance,

FIGURE 2.9. Illustration of voltage applied across silicon substrate in Equations 2.3-2.4.

$$C_{s} = \frac{Q}{V}$$

$$= \frac{\oint_{S} \mathbf{D} \cdot \mathbf{dS}}{V}$$

$$= \frac{\oint_{S} \epsilon_{s} \mathbf{E} \cdot \mathbf{dS}}{V}, \qquad (2.4)$$

and hence,

$$\frac{G_s}{C_s} = \frac{\oint_S \sigma_s \mathbf{E} \cdot \mathbf{dS}}{\oint_S \epsilon_s \mathbf{E} \cdot \mathbf{dS}} \\

= \frac{\sigma_s}{\epsilon_s}$$

(2.5)

This C-G-C configuration yields a frequency-dependent total capacitance and conductance that is in good agreement with SDA results over a broad range of frequencies. Distributed series resistances and inductances (including mutual terms) may be calculated using an SDA algorithm [25] or a spatial domain solution [26] (see Appendix B) in conjunction with a modified Partial Element Equivalent Circuit (PEEC) [19] methodology that includes frequency dependence to account for the skin effect mode. The frequency-dependent series resistances incorporate the skin effect in the finite thickness metallization [27] as well as loss in the semiconducting substrate. The formula used for the metallization skin effect for a conductor of thickness, t, is given by

$$R_{\text{cond.,skin}} = R_{DC} \cdot \Re\left\{\frac{\gamma t(1 - e^{-2\gamma t}r)}{1 - e^{-2\gamma t}}\right\},\tag{2.6}$$

where

$$\gamma = \sqrt{j\omega\mu\sigma_{\text{cond.}}} \tag{2.7}$$

$$r = \frac{\eta_0 - \sqrt{j\omega\mu/\sigma_{\text{cond.}}}}{\eta_0 + \sqrt{j\omega\mu/\sigma_{\text{cond.}}}}$$

(2.8)

$$\eta_0 = 120\pi \ (\Omega). \tag{2.9}$$

This formula for  $R_{\text{cond.,skin}}$  is valid for frequencies at which the skin depth,  $\delta$ , is less than t, that is, when

$$f \ge \frac{1}{\pi \mu \sigma_{\text{cond.}} t^2}.$$

(2.10)

The substrate losses due to longitudinal currents are computed by solving the magnetic vector potential equation in each layer i [26]

$$\nabla^2 A_{zi}(x,y) = j\omega\mu_0\sigma_i A_{zi}(x,y) \tag{2.11}$$

where z is the direction of propagation, subject to the appropriate boundary conditions (e.g.  $A_z = 0$  on the ground plane). In the semiconducting substrate region, the current density is computed as

$$J_z(x,y) = -j\omega\sigma_{sub}A_z(x,y) \tag{2.12}$$

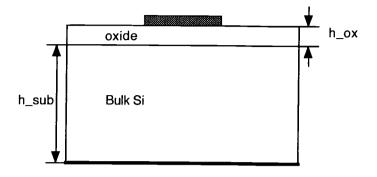

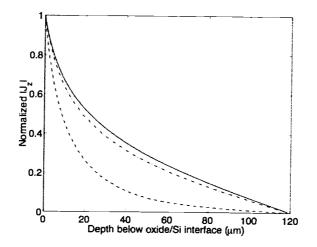

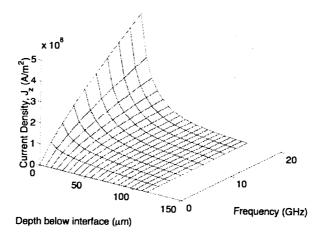

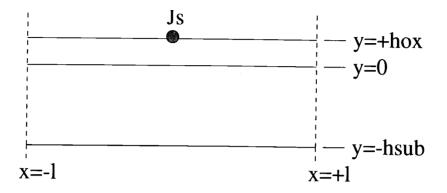

Fig. 2.11 shows the current density below the oxide as a function of frequency and depth for a typical Si-SiO<sub>2</sub> microstrip structure, as shown in Figure 2.10 with  $h_{ox} = 4 \ \mu \text{m}, \ h_{sub} = 120 \ \mu \text{m}, \ \text{and} \ \sigma_{sub} = 10^4 \ \text{S/m}.$  Similarly, Fig. 2.12 displays the normalized longitudinal current density,  $\bar{J}_z$ , in a cross section of the substrate

FIGURE 2.10. Example Si-based microstrip showing definition of  $h_{ox}$  and  $h_{sub}$ .

for various frequencies. It can be deduced that there is current crowding in the vertical dimension at the substrate/oxide interface, and also in the horizontal dimension in the area beneath the strip, as evidenced by the overall magnitude increase of the peak longitudinal substrate current density with frequency.

### 2.4.2. Complex Virtual Ground Plane Height and Expansion to Multilayer Substrates

As can be deduced from the preceding section, the effect of longitudinal substrate currents on microstrip structures fabricated in semiconducting substrate environments must be accounted for properly. One method for inclusion of the semiconducting substrate's effect on inductance is to utilize the portion of Wheeler's Incremental Inductance Rule [28] relating to inductance, which states that the effective inductance of a device over a conductor is equal to inductance calculated with the assumption that the conductor below is perfectly conducting (i.e. perfect ground plane) plus the increment of additional inductance gained if the conductor wall is receded by  $\delta/2$ , where  $\delta$  is the skin depth. Also according

FIGURE 2.11. Normalized longitudinal substrate current density for f = 0.001 GHz (-), 0.1 GHz (-·) and 10 GHz (- -).

FIGURE 2.12. Longitudinal substrate current density vs. frequency and depth below oxide/Si interface.

to Wheeler's rule, the net increase in resistance is proportional to the change in inductance by the following relationship,  $R_s = \omega \Delta L_s$ . However, Wheeler's rule is not directly applicable to the 2-D and 3-D problems associated with spiral inductors, since the stated relationship between resistance and inductance does not hold for these complex cases where . But it will be shown that the 1-D parallel-plate waveguide case examined in the proceeding paragraphs is in exact agreement with Wheeler's rule, lending validity to this alternative approach.

While the formulation for solving the frequency-dependent per-unit-length series impedance for a microstrip structure over an insulator/semiconductor (MIS) substrate is a 2-D problem, a simplified 1-D approach for parallel-plate waveguides can provide accurate results through the use of a complex height virtual ground plane [29]. Recall that the magnetic field pattern in the semiconducting substrate can be characterized in terms of a frequency- and spatially-dependent magnetic vector potential function. If the microstrip problem is replaced by an ideal parallel-plate waveguide structure that is partially filled with a semiconducting material, the problem reduces to that of a 1-D magnetic vector potential. This approach is discussed in terms of its application to interconnects in [29] and [30], and is summarized in the following paragraphs. It has also been applied to inductors in [18] and [31], building upon the 'real' virtual ground plane approach developed in [16] and [32].

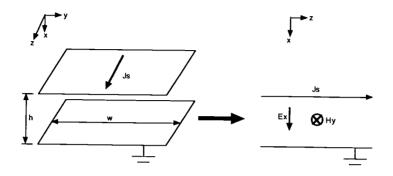

To derive the "complex height virtual ground plane" approach, first consider the inductance of an ideal air-filled parallel-plate waveguide, as shown in Figure 2.13,

$$L = \mu_0 \left[ \frac{h}{w} \right] \tag{2.13}$$

where h and w are the total height and width, respectively. Note that the electric and magnetic fields only have one component each,  $E_x$  and  $H_y$ , respectively. If the

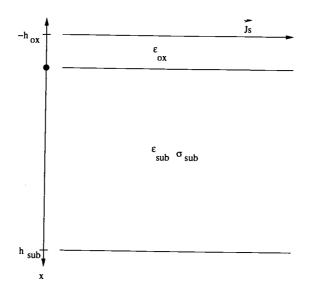

FIGURE 2.13. Ideal parallel-plate waveguide, front and side views.

bottom ground plane is replaced by a semi-infinite semiconducting bulk substrate, as illustrated in Figure 2.14, the net inductance, as well as series resistance due to the substrate's finite conductivity, will now be a function of frequency owing to the non-uniform frequency-dependent longitudinal current distribution in the semiconducting material. This problem may be solved in terms of the magnetic vector potential, in which the semiconducting substrate is replaced by a virtual perfectly conducting ground plane at a distance of  $\alpha^{-1}$  below the semiconductor interface [29]. Here  $\alpha$  is defined as

$$\alpha = \frac{(1+j)}{\delta},\tag{2.14}$$

where  $\delta$  is the skin depth for the semiconducting material, and  $j = \sqrt{-1}$ .

Upon examination of the preceding formulation, it is clear that as frequency approaches infinity, the net inductance approaches that of the case where the semiconducting substrate is perfectly conducting, since the skin depth is approaching zero. However, note that the distance  $\alpha^{-1}$  is complex, which thus implies a complex inductance, or more generally a complex series impedance. Unlike the inductance, which drops and approaches a finite value as frequency goes

FIGURE 2.14. Parallel-plate waveguide with bottom plate replaced by semi-infinite semiconducting bulk substrate.

to infinity, the net resistance continues to increase as the square-root of frequency and is hence unbounded, as will be shown in the following derivation.

The solution for  $A_z$  in the semi-infinite semiconducting substrate is

$$A_z(x)|_{x\ge 0} = \frac{\mu_0 J_s}{\alpha} e^{-\alpha x}$$

(2.15)

where  $J_s$  is the assumed surface current density on the top plate of the waveguide. The series inductance per-unit-length for a parallel-plate waveguide filled with oxide of height,  $h_{ox}$ , may be computed as

$$\frac{L}{l} = \frac{A_z(-h_{ox}) - A_z(0)}{J_s w}$$

(2.16)

where

$$A_z(x)|_{x \le 0} = -\mu_0 J_s x + A_{z0} \tag{2.17}$$

$$A_{z0} = A_z(0). (2.18)$$

The solution for the case of oxide and semi-infinite semiconducting bulk is

$$\frac{L}{l} = \frac{A_z(-h_{ox}) - A_z(\infty)}{J_s w}$$

(2.19)

where

$$A_{z}(x)|_{x \le 0} = -\mu_{0}J_{s}x + \frac{\mu_{0}J_{s}}{\alpha}$$

(2.20)

$$A_z(\infty) = 0. \tag{2.21}$$

This reduces to

$$\frac{L}{l} = \frac{\mu_0 J_s (h_{ox} + \frac{1}{\alpha})}{J_s w}$$

$$= \mu_0 \frac{h_{ox}}{w} + \mu_0 \frac{1}{\alpha w}$$

$$= \mu_0 \frac{h_{ox}}{w} + (1 - j) \mu_0 \frac{\delta/2}{w}.$$

(2.22)

Clearly the solution for the complex series inductance consists of the ideal parallelplate inductance for a waveguide of height,  $h_{ox}$ , plus a term that represents the complex inductance of the semi-infinite bulk semiconducting substrate,

$$\frac{L}{l} = \frac{L_{ox}}{l} + \frac{L_{sub}}{l}.$$

(2.23)

Upon examination of the secondary term,

$$\frac{L_{sub}}{l} = (1-j)\mu_0 \frac{\delta/2}{w}$$

(2.24)

the complex series inductance term for the semi-infinite substrate is observed to be that of a parallel-plate waveguide of height

$$h_{sub,eff} = (1-j)(\delta/2)$$

(2.25)

as shown in Figure 2.15, which is a complex value. Thus, the complex inductance for the entire waveguide may be represented as the solution for two plates

FIGURE 2.15. Illustration of effective substrate height for two-layer Si-filled parallel-plate waveguide.

separated by a complex distance  $h_{eff}$ ,

$$L_{\text{complex}} = \frac{L}{l} = \mu_0 \frac{h_{eff}}{w}$$

(2.26)

where

$$h_{eff} = h_{ox} + h_{sub,eff}$$

=  $h_{ox} + (1 - j)(\delta/2).$  (2.27)

The resulting net complex series inductance for the entire waveguide may also be written in terms of a complex impedance per-unit-length,

$$Z_s = j\omega L_{\rm complex} \tag{2.28}$$

$$= j\omega \left[\mu_0 \frac{h_{eff}}{w}\right]. \tag{2.29}$$

When divided into real and imaginary components, the net real inductance and resistance per unit length are computed as

$$L_{s} = \frac{\Im\{Z_{s}\}}{\omega}$$

$$= \frac{\Im\{j\omega L_{\text{complex}}\}}{\omega}$$

$$= \Re\{L_{\text{complex}}\}$$

$$= \mu_{0} \left[\frac{d + (\delta/2)}{w}\right]$$

$$R_{s} = \Re\{Z_{s}\}$$

$$= \Re\{J\omega L_{\text{complex}}\}$$

$$= -\omega \Im\{L_{\text{complex}}\}$$

$$= \mu_{0} \omega \frac{\delta/2}{w}$$

(2.31)

As discussed previously, Wheeler's Incremental Inductance Rule states that the contribution to net resistance from a finite conductivity ground plane is computed as

$$R_s = \omega \Delta L_s \tag{2.32}$$

where  $\Delta L_s$  is the net increase in inductance due to magnetic field penetration into the conducting plane over the inductance of the same structure with a perfectly conducting ground plane. This incremental change in inductance, according to Wheeler's Rule, is equal to the increase resulting from a recession of the perfectly conducting plane by a distance equal to  $\delta/2$ . For the case of a parallel plate waveguide of height  $h_{ox}$  with a semi-infinite semiconducting substrate as the bottom conductor, the inductance will be, according to Wheeler,

$$L_s = \mu_0 \frac{h_{ox}}{w} + \Delta L_s$$

$$= \mu_0 \frac{h_{ox} + (\delta/2)}{w}.$$

(2.33)

This is the same result already derived in Eq. 2.30. The net resistance should be, according to Wheeler's rule,

FIGURE 2.16. Parallel-plate waveguide partially filled with semiconducting substrate.

$$R_s = \omega \Delta L_s$$

=  $\omega \mu_0 \frac{(\delta/2)}{w}$ , (2.34)

which is equivalent to Eq. 2.31. Thus, the formulation presented here for a parallelplate waveguide with a semi-infinite semiconducting substrate as the bottom conductor is consistent with Wheeler's Incremental Inductance Rule.

A more practical case of the parallel-plate waveguide is that of an oxide layer over a finite thickness semiconducting substrate with ground plane on the backside, as illustrated in Figure 2.16. The effective height for this case is [30]

$$h_{eff,\text{groundplane}} = \frac{\delta}{2}(1-j)\tanh\left((1+j)\left(\frac{h_{sub}}{\delta}\right)\right)$$

$$= \frac{1}{\alpha}\tanh\left(\alpha h_{sub}\right)$$

(2.35)

FIGURE 2.17. Parallel-plate waveguide partially filled with 2-layer semiconducting substrate.

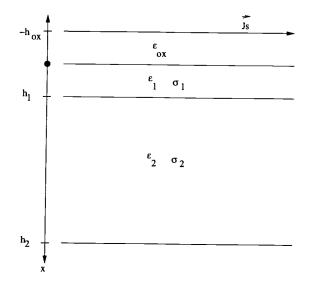

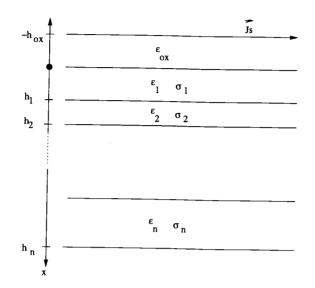

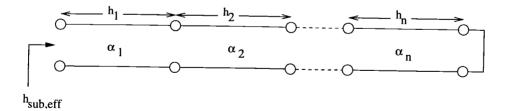

Similarly, for the case of two different semiconductor layers, shown in Figure 2.17, the effective height is given by [30]

$$h_{eff,2lyr-semi,groundplane} = \frac{1}{\alpha_1} \left( \frac{\frac{1}{\alpha_2} \tanh(\alpha_2 h_2) + \frac{1}{\alpha_1} \tanh(\alpha_1 h_1)}{\frac{1}{\alpha_1} + \frac{1}{\alpha_2} \tanh(\alpha_2 h_2) \tanh(\alpha_1 h_1)} \right)$$

(2.36)

An examination of the two-layer semiconductor solution in Eq. 2.36 reveals that the equation is of the same form as that of the generalized input impedance of a series of cascaded transmission lines with arbitrary lengths and impedances with the end termination impedance equivalent to a short circuit [30]. As will be shown in the following section, this method can greatly simplify the problem of solving for the series impedance of interconnects over multilayer substrates as is typical in silicon process environments.

FIGURE 2.18. Parallel-plate waveguide partially filled with N-layer semiconducting substrate.

FIGURE 2.19. Illustration of transmission line impedance analogy used for computing  $h_{eff}$  for N-layer parallel-plate waveguide.

33

## 2.4.3. Using the Complex Virtual Ground Plane to Solve Microstrip Impedance Problems

In general, a microstrip-type structure requires some sort of 2D field solution or a closed-form expression in order to determine its propagation characteristics and line impedance. The technique presented in the previous section employs a ground plane spaced at a complex distance to represent a mutilayer substrate. Many closed-form expressions already exist for single microstrip and even finite length strips above a ground plane [33]. One of the most common formulations for microstrip is presented in [34] and is given as

$$Z_{0} = \frac{60}{\sqrt{\epsilon_{e}}} \ln\left(\frac{8h}{w} + \frac{w}{4h}\right) \quad \text{for} \quad w/h \le 1$$

=  $\frac{120\pi}{\sqrt{\epsilon_{e}} \left[w/h + 1.393 + 0.667 \ln\left(w/h + 1.444\right)\right]} \quad \text{for} \quad w/h \ge 1$  (2.37)

$\epsilon_{r} + 1 \quad \epsilon_{r} - 1 \qquad 1$

$$\epsilon_e = \frac{\epsilon_r + 1}{2} + \frac{\epsilon_r - 1}{2} \frac{1}{\sqrt{1 + 12h/w}}$$

(2.38)

If these expressions are evaluated for the case of an air dielectric ( $\epsilon_r = 1$ ), then the inductance per-unit-length is given by

$$L_{\rm p.u.l.} = \frac{Z_0}{c_0} \quad ({\rm H/m})$$

(2.39)

where  $c_0$  is the speed of light in a vacuum. As in the case of the parallel-plate waveguide, the resulting inductance per-unit-length will be complex when the value for h is complex. This is true when there are semiconducting substrate layers present, implying a net series resistance per-unit-length,  $R_{p.u.l.}$ . The method for obtaining the frequency-dependent complex inductance for a single microstrip using this closed-form expression for impedance is as follows [29]: