## DREGON STATE

#### DEPARTMENT OF COMPUTER SCIENCE

DEPARTMENT OF ONEUTER SCIENCE

> DEPARTMENT OF COMPUTER SCIENCE

78-01-01

# COMPVTER SCIENCE

UNIVERSITY

### DEPARTMENT

### Hardware, Firmware, Software Technology in Microcomputer Systems

T. G. Lewis Computer Science Dept.

H. Jafari Electrical Engineering Dept.

Oregon State University

COMPUTER SCIENCE

#### HARDWARE, FIRMWARE, SOFTWARE TECHNOLOGY IN MICROCOMPUTER SYSTEMS

#### T. G. LEWIS

#### COMPUTER SCIENCE DEPARTMENT OREGON STATE UNIVERSITY CORVALLIS, OREGON

For "Advances in Information Systems Science," Julius Tou ed., Plenum Publishing Company, 227 West 17th Street New York, New York 10011

> Editor: Julius Tou University of Florida Gainesville, Florida 32611

#### 1. Hardware Organization

#### 1.1 Introduction

Computer systems advance by revolutions rather than evolutions. The jump from vacuum tube machines to solid state transistor machines was revolutionary. Never before had computers been reduced in size, cost, and computation time until this revolution.

Computer revolutions are enumerated by a generation number. First generation computers were based on vacuum tube technology, second generation was based on transistors. We can say that the current generation is based on large-scale-integration LSI.

The LSI age of computing is no longer denoted by a single generation number because LSI is causing many upheavals in computing. The upheavals are too numerous and spread over too short a time for numbering systems to keep up. Even the terminology needed to describe the changes is hard pressed to keep pace.

It is important to realize the significance of terminology. One measure of the rate of technological change is the rate of semantic shifts occurring in the language. For example, a <u>microprocessor</u> is a cpu in a single LSI transistor wafer. A few years earlier, however, a microprocessor was any microprogrammable cpu. To avoid confusion, the following definitions will be used throughout this chapter.

A <u>microcomputer</u> is a cpu memory, interfaces and boards needed to package a microporcessor to make it appear as a computer to the user. A microcomputer may be microprogrammable if it has a control memory and sequencing unit that allows <u>firmware</u> programming. For the purpose of this chapter, a firmware program will be any program residing in a read-only memory, ROM. This definition sidesteps the problem posed by microcomputers that emulate their instructions as compared with microcomputers that take instructions from either ROM or random-access-memory, RAM. In either case, a microcomputer is said to be <u>microprogrammed</u> if programs reside in ROM, regardless of the processor's architecture\*.

A microcomputer that incorporates ROM and a microprocessor in a single unit is called a <u>grand-scale-</u> <u>integration</u> GSI microcomputer. An example of a GSI microcomputer is the common pocket calculator. Each calculator has a processor and a ROM containing the instructions for executing each button stroke. Since programming in the stored program tradition is not possible by the user, the calculator is considered a single unit of GSI equipment.

\*Emulation can be roughly defined as simulation of one computer on another computer. Typically, the simulator resides in ROM as part of the control unit of the host cpu.

Microprocessors are packaged in dual-in-line packages called <u>DIP chips</u>. A DIP chip is typically a 40-pin ceramic package about one to two inches long, 'one-fourth to one inch wide, and less than 1/2 inch thick. Access to the resident circuitry is through the 40 pins. Because of their size and packaging, microprocessors are often called chip computers.

It is the decreased size, cost, and power consumption that is responsible for the chip computer revolution. This revolution permeates the application, design, programming, and manufacture of computers, their peripherals, and the people who use them. Such pervasion into science, technology, and society will have far reaching effects for the future.

The purpose of this chapter is to narrow the discussion of this revolution to a specific technical area. The discussion will focus on fundamental technological concepts underlying the revolution. For this purpose we examine three architectures, three software systems, and conclude with an analysis of resource sharing and the impact of microcomputing on sharing.

1.2 A Simple Microprossor

Perhaps the simplest microprocessor would be an LSI circuit for adding, subtracting, and performing I/O on a two-bit word of memory. Such a small processor holds little interest because of the elaborate

encoding of data and extensive programming effort required to make the hypothetical processor useful. What then, is the lower limit of "size" acceptable for a practical microprocessor?

The first requirement for a practical microcomputer is that decimal numbers be easily represented in the microprocessor storage unit. This means a minimum word length of 4 bits, since digits 0-9 can be encoded in BCD with 4 bits. A four bit computer can perform most functions of a decimal calculator with relative ease.

Greater parallelism leads to speed and the potential for extensive programming. A four-bit word can address only 16 locations in memory while an 8-bit word can hold 256 addresses. Furthermore, an 8-bit instruction word has greater capability for an improved instruction set.

Obviously, the same arguments for 16-bit processors can be applied to 8-bit processors. The improvements of a 16-bit computer certainly make their development inevitable.

Before any technological device is made available on a widespread basis, there must be a <u>dollar-</u> <u>volume force</u> behind the technological device. <u>Dollar-volume force</u> is defined as the product of unitprice times market-volume.

\$\_VOL\_FORCE = (Unit-price) (Market-volume)

A microcomputer valued at \$10 and sold 10,000 times is

a technological device with a \$100,000 dollar-volume

force behind it.

This leads to the concept of <u>technology</u> <u>availability</u>, which in turn partially determines the design of a simple <u>microprocessor</u>. <u>An invention becomes available</u> <u>only when the dollar-volume force is significantly in-</u> <u>creased by the proposed invention\*</u>.

A two-bit microcomputer, while feasible for many years before microcomputers were generally available, lacked potential for increasing the dollar-volume force. A four-bit computer, because of its usefulness in pocket calculators and BCD processing machines successfully increased the dollar-volume force thereby making the first microprocessor available. Hence the simplest microprocessor that was both technologically possible and economically feasible was the 4-bit processor.

An 8-bit microprocessor offers many technological advantages over 4-bit processors. The advantages in themselves are not sufficient to bring about a true

\*It could be argued that television arose without an initial dollar-volume force behind prior developments. However, it is also possible to view TV as an outgrowth of radio, in which case the dollar-volume force is increased. In general, consumer electronics are marketed only when new markets expand the dollar-volume.

8-bit microcomputer. Instead, the dollar-volume force had to increase before 8-bit microcomputers were possible.

The 8-bit microcomputer increased the dollarvolume force sufficiently to drive 8-bit microprocessors into general availability. The reason is that ASCII and EBCDIC encoding are 8-bit codes, floating point arithmetic is facilitated, and addressability is improved. These primitive improvements manifest themselves in more sophisticated software packages that in turn expand the usefulness of 8-bit computers beyond the pocket calculator market. Therefore, the 8-bit microcomputer owes its driving dollar-volume force to applications that transcend pocket calculators.

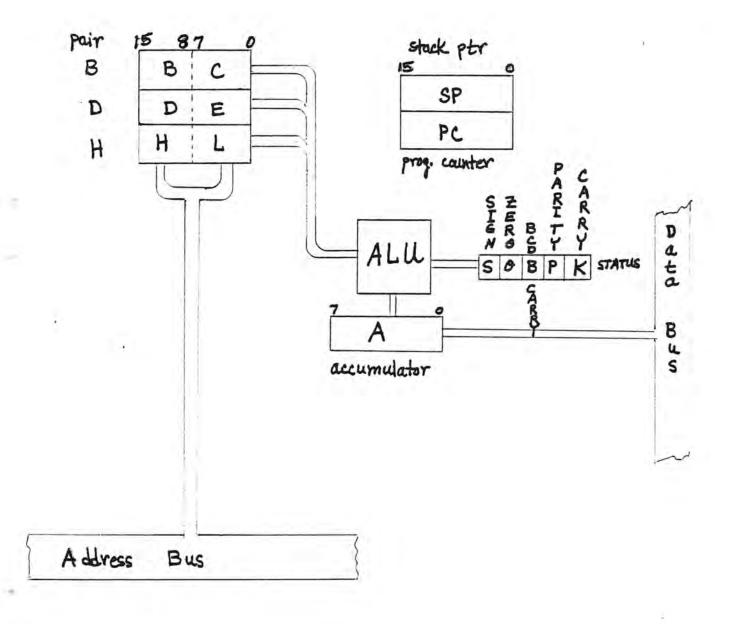

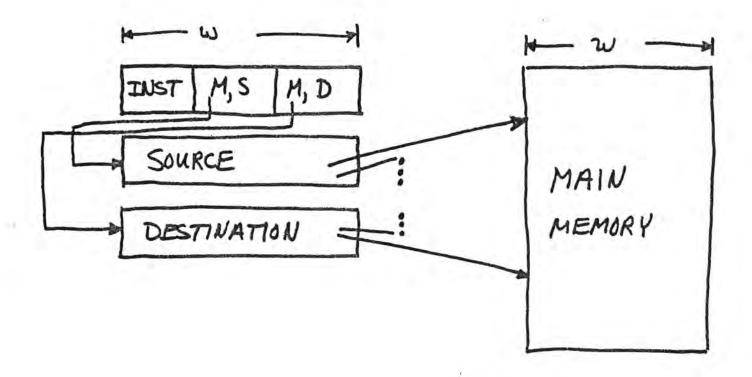

The 8-bit microcomputer architecture of Figure 1 shows a simple microprocessor organization that typifies the early generation of microprocessors. The machine of Figure 1 is a register-transfer machine. This means that all operands are either stored in the working registers or they are accessed by pointers stored in the working registers.

One of the dollar-volume driving forces behind the eventual availabilty of 8-bit microprocessors was the advantages of multiple precision calculators. This advantage is noted in the double register feature of Figure 1. Registers B, D, and H are treated as 16-bit operands in certain operations. Also, 4-bit The architecture of Figure 1 is an Intel '8080, see reference 7.

Figure 1. A Simple 8-Bit Microprocessor

precision is preserved by the "BCD CARRY" bit B in the status register. We will study the behavior of bit B in a later programming example.

Each instruction of the microprocessor of Figure 1 is one, two, or three bytes long. The niladic operators\* such as "SET CARRY", "COMPLEMENT", and "DECIMAL ADJUST" require only one byte of memory. The monadic operators such as "ADD", "AND", and "COMPARE" require two bytes because of extended addressing. The dyadic operators such as "MOVE" and "LOAD INDEX" require three bytes. In most cases operands are working register or memory register, either one accessed through the pointer loaded into register pair H-L.

The A, B, C, D, and E registers are used to accumulate results from the ALU. The H and L registers combine to form a 16-bit memory address. The address in H-L is used to load or store single bytes from or to memory. The memory may be ROM, in which case store operations via H-L are meaningless.

\*Niladic operators have zero explicit operands, monadic operators have one explicit operand, and diadic operators have two explicit operands. For example, in the DAA operation, the accumulator is implied.

The memory of this 8-bit microprocessor is hierarchial: Register A is immediately available while registers B, C, D, E, H, and L are available as operands in the instruction set. Main memory is at a third level of access because bytes come from main memory by way of the pointer in H and L.

The program counter, PC and stack pointer, SP operate as expected. The PC register holds the 16-bit address of the next instruction to be executed. The SP register holds the address of the top element of a push down stack. A "PUSH" operation causes 16 bits to be placed on the stack after SP has been decremented by two.

(SP) 🔶 (SP) 🗕 2

After a "POP" operation, the SP register is incremented. Therefore, the stack grows toward the low end of memory. This feature guarantees that 16-bit register pairs are loaded and unloaded in the order needed during multiple precision calculations.

The stack facility provides recursive subroutining. During a "CAL" to subroutine, the "old PC" is saved on the push down stack. During a return from subroutine the "new PC" is popped from the stack.

Input and output is performed through the A register under program control. The "IN" instruction fetches an 8-bit byte from a specified device and "OUT" copies the contents of register A onto the data bus.

Interrupts are allowed with the "EI" instruction and disabled with the "DI" instruction. There is no automatic vectoring\* of traps. This weakness must be overcome through considerable programming by the user.

Figure 2 demonstrates a short segment of machine level code for the microprocessor of Figure 1. The program computes the sum of two 3-byte numbers stored at symbolic locations, FIRST and SECND. The answer is stored back into FIRST.

|   | 32AF8A <sub>16</sub> |   | SECND_ |          |

|---|----------------------|---|--------|----------|

| + | 84BA90 <sub>16</sub> | + | FIRST  |          |

|   | B76A1A               |   | FIRST  | (answer) |

The program demonstrates how multiple precision calculations are performed and how the lack of indexing is overcome by programming. The "ADD:" segment of code initializes two pointers to the operands. The B-C

\*Automatic I/O or vectored I/O is a feature on many minicomputers. An I/O vector is a memory cell containing status information and a pointer to a service routine. Upon interruption, the service routine is called. register pair point to FIRST after the load-indeximmediate LXI instruction. The H-L pair points to SECND after execution of the LXI instruction.

The "LOOP:" segment performs addition on three bytes, from right (least significant byte) to left (most significant byte). This is done by accessing the byte pointed to by B-C, accessing the byte pointed to by H-L, and performing the ADC instruction. The ADC adds with CARRY included so that multiple precision carry-outs are saved in bit K=CARRY. The STAX instruction uses B-C as a pointer to FIRST. The DCR decrement instruction subtracts one from register C because this segment of code also uses register C as a loop counter. This dual use of B-C (as pointer and counter) may lead to errors in the program unless the data is stored on a 256-byte page boundary. The next instruction tests for completion.

The operand pointer B-C also is used as a loop counter in the previous example. This is necessary in the limited architecture of a simple microprocessor.

The result, however, is greater software overhead, possible errors as pointed out above, and added effort.

Most microprocessors are oriented toward decimal BCD calculations. The "DAA" decimal adjust instruction is provided to translate partial binary results back into BCD results after an arithmetic operation. The following example will demonstrate this.

| <sup>25</sup> BCD | = | 0010 | 01012 |

|-------------------|---|------|-------|

| 7 <sub>BCD</sub>  | + | 0000 | 01112 |

| <sup>32</sup> BCD |   | 0010 | 11002 |

The BCD numbers 25 and 7 are stored as binary nunbers, internally. When the microprocessor adds them together, it produces the <u>binary sum</u> 0010 1100 as shown to the right. This sum must now be converted to a BCD numeral instead of a binary number. The DAA instruction tests the BCD CARRY bit in the status register. Depending upon the value of the BCD CARRY, the upper and lower byte of the result, and the condition of the CARRY bit, the DAA instruction will either add  $+00_{16}$ ,  $+06_{16}$ ,  $+60_{16}$ , or  $+66_{16}$  to the result.

In the case of the sample calculation, above, the result is "corrected" by addition of  $+06_{16}$ .

| 2 | 0010 | 1100 |                     |

|---|------|------|---------------------|

| + | 0000 | 0110 |                     |

|   | 0011 | 0010 | = 32 <sub>BCD</sub> |

The DAA operation produces a BCD result that would have been obtained had the micropressor been capable of direct decimal addition. Thus, 25+7 = 32 as desired.

We could modify the sample program of Figure 2 to produce BCD results by giving the data in BCD format and using a DAA instruction after each addition. This would mean inserting a DAA instruction between the ADC and STAX instruction in the LOOP segment of code.

The simple microcomputer described here has an extensive instruction set and a 16-bit addressing capability. It has found applications in a variety of first-time computer uses. Indeed, its simplicity is a virtue in many new applications.

There are both obvious and subtle deficiencies in the simple microprocessor design we have just examined. Basically the deficiencies stem from the microprocessors weak indexing and addressing capability and underdeveloped interrupt handling facilities. The next microprocessor studied partially overcomes these deficiencies and represents a typical second generation microcomputer processor.

Figure 2. A Sample Program For the Microprocessor of Figure 1.

90H FIRST: DB Hexadecimal data bytes... DB BAH stored in reverse order. 84H DB 84H Hexadecimal data bytes... SECND: DB DB AFH stored in reverse order. 32H DB

\* (A) sum of multiple precision add

(B-C) index to FIRST operand.

\* (C) length of operands, in bytes.

\* (H-L) index to SECND operand

\* FIRST operand and answer (sum).

\* SECND operand

\*

| ADD : | LXI B,FIRST  | S set (B-C) pointer to FIRST.  |

|-------|--------------|--------------------------------|

|       | LXI H, SECNI | ) set (H-L) pointer to SECND   |

|       | XRA A        | clear CARRY bit, set A=0.      |

| LOOP: | LDAX B       | get a byte of FIRST            |

|       | ADC M        | (A) $-(A) + (H-L) + (CARRY)$ . |

|       | STAX B       | put a byte into FIRST          |

|       | DCR C        | done                           |

|       | JZ DONE      | otherwise, continue.           |

| INX | В    | increment to next byte of FIRST |  |

|-----|------|---------------------------------|--|

| INX | н    | increment to next byte of SECND |  |

| JMP | LOOP | add next byte.                  |  |

|     |      | continue                        |  |

14

DONE :

0

14.0

110

END

1.3 An Improved Microprocessor

Once a dollar-volume force is set into motion by a technological breakthrough, many minor stepwise improvements follow. The improvements act as minor pertubations in the revolution. Nonetheless, it is by way of these smaller steps that we build-up to a subsequent breakthrough.

The advantages of 8-bit microcomputers soon become obvious to many who would use them for purposes not forseen by the designers. These new applications were implemented by custom made software resident in the microprocessor memories. It became evident to many software engineers that the simple 8-bit microprocessor studied in section12 could be improved to alleviate some of the problems associated with more general applications.

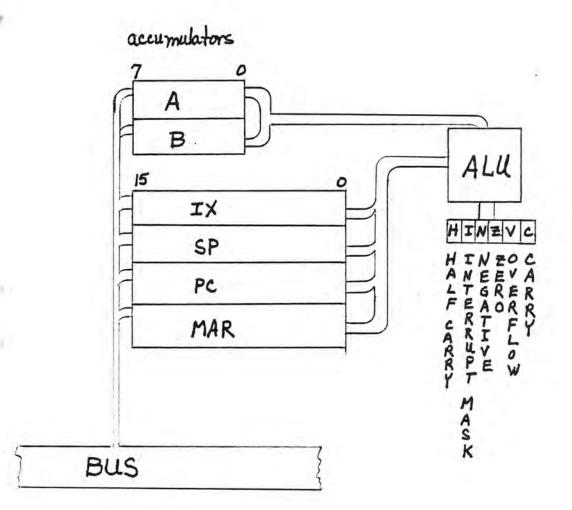

The improved microprocessor of Figure 3 gives the false impression that the microprocessor is actually less capable than the one just studied.<sup>\*</sup> Actually, the simpler organization belies a more powerful microprocessor instruction set. The reason for its improved organization centers on the index register, IX and 72 unique instructions.

The architecture of Figure 3 is a Motorola 6800 MPU, see reference (8).

All operations are performed between registers A, B and memory, or between registers A and B themselves. For example, the "ADDA" and "ADDB" instructions sum the contents of a memory byte at the location specified by register MAR. They also can sum the contents of A or B and store the result back into A or B.

Instruction operands are fetched from either A or B and via MAR from memory as stated before. The index register, however, may enter into addressing via MAR. The contents of IX are added to the address in MAR to compute an effective address. This added capability greatly simplifies programming and requires smaller programs as illustrated in Figure 4.

The SP and PC registers operate as before with the stack in main memory. The stack is used for recursive subroutine calls but may also contain intermediate results or parameters to a subroutine.

The condition codes include HALF CARRY, and CARRY as in the simple microprocessor. This enables the improved microprocessor to perform both BCD arithmetic on single bytes and multiple precision arithmetic on strings of bytes. The INTERRUPT MASK bit provides control over interrupt enables. For example, I is set (=0) with the "SEI" instruction. Interrupt service routines are entered recursively.

Figure 3. An Improved 8-bit Microprocessor

Input/output is generalized through the use of a central bus. The bus handles addressing of memory, peripherals, and other microprocessors through generalized interface chips. Each interface chip is dedicated to either cycle - stealing direct memory access, or to jamming data into the A or B accumulator. Therefore, to output a byte from register A, it is necessary to perform a store instruction, STAA IOBUF. This store accumulator A instruction addresses the interface chip IOBUF as if it were a location in memory. Whatever device is attached to IOBUF receives the byte of data.

Examination of the multiple precision addition of FIRST and SECND byte strings of Figure 4 reveals a much simpler, shorter, and understandable program when compared with Figure 2.

In Figure 4 the microprocessor is programmed to add together any two byte strings of length N and store the result back in the FIRST string. This is done by using the index register as a pointer into the strings. The addition is done right-to-left with the CARRY bit linking together partial results.

The DAA decimal adjust instruction can be inserted where shown if BCD arithmetic is desired. The DEX decrement instruction sets the zero Z indicator when X has been reduced to zero. This signifies termination of the loop.

Figure 4. A Sample Program For the Microprocessor of Figure 3.

\$84 Hexadecimal data bytes... FIRST FCB FCB \$BA stored in forward order. FCB \$90 SECND FCB \$32 Form Constant Byte for ... FCB \$AF second operand. FCB \$84 N EQU 3 length of operands. clear CARRY. AD2N CLC LDX #N load length of operands... into index register. LDAA LOOP FIRST,X get least significant byte ADCA SECND, X add with CARRY (DAA) (could go here for BCD add-see text) STAA FIRST, X put result back into FIRST. DEX decrement index pointer. LOOP BNE Done?

DONE

10

The realization of greater capability in an 8-bit processor suggests that other improvements may be possible. In the next demonstration microprocessor we examine several areas of improvement representing the third generation of microprocessor organization.

#### 1.4 A Sophisticated Microprocessor

While the 4 and 8-bit microprocessors discussed earlier represent sophisticated programmable logic, the truly sophisticated microprocessor has the replacement of mini and midi computers as its dollarvolume driving force. For any microcomputer to move into applications traditionally held by minicomputers greater software development potential must be possible through improved architecture. Therefore, it is the software development capability that differentiates the sophisticated microprocessor from earlier generations of microprocessors.

The dollar-volume force is increased by a microprocessor with ease of programming, sophisticated memory addressing, and expansion capability built into the chip. Such a microprocessor competes with minicomputers for acceptance. For this reason, the improved microcomputer must also be an improvement over many contemporary minicomputer architectures. For example, it must overcome limitations placed on main memory size in favor of a large memory address space.

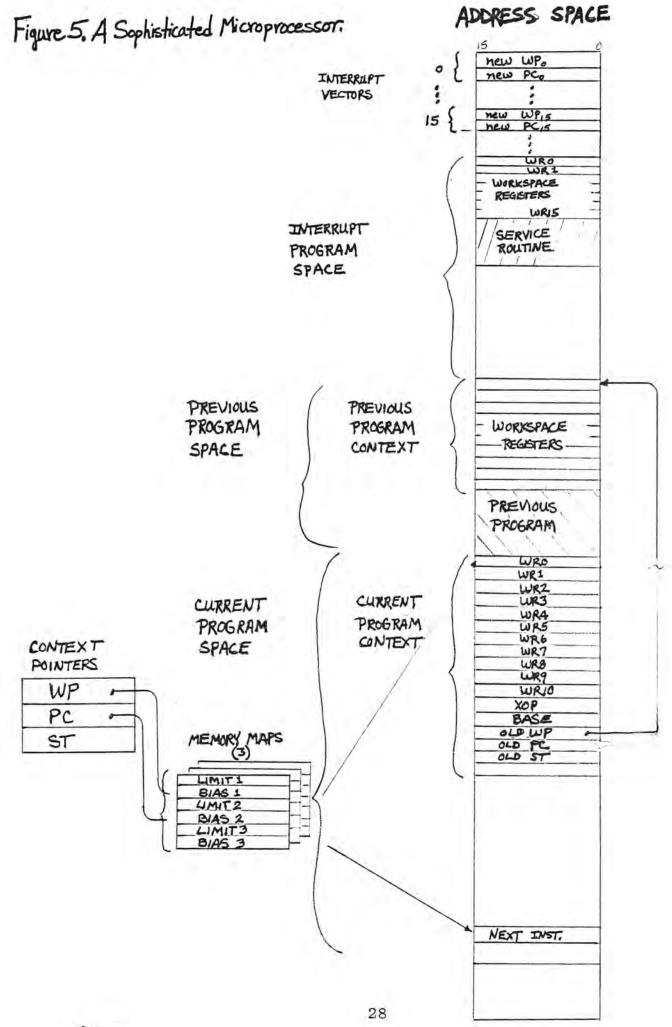

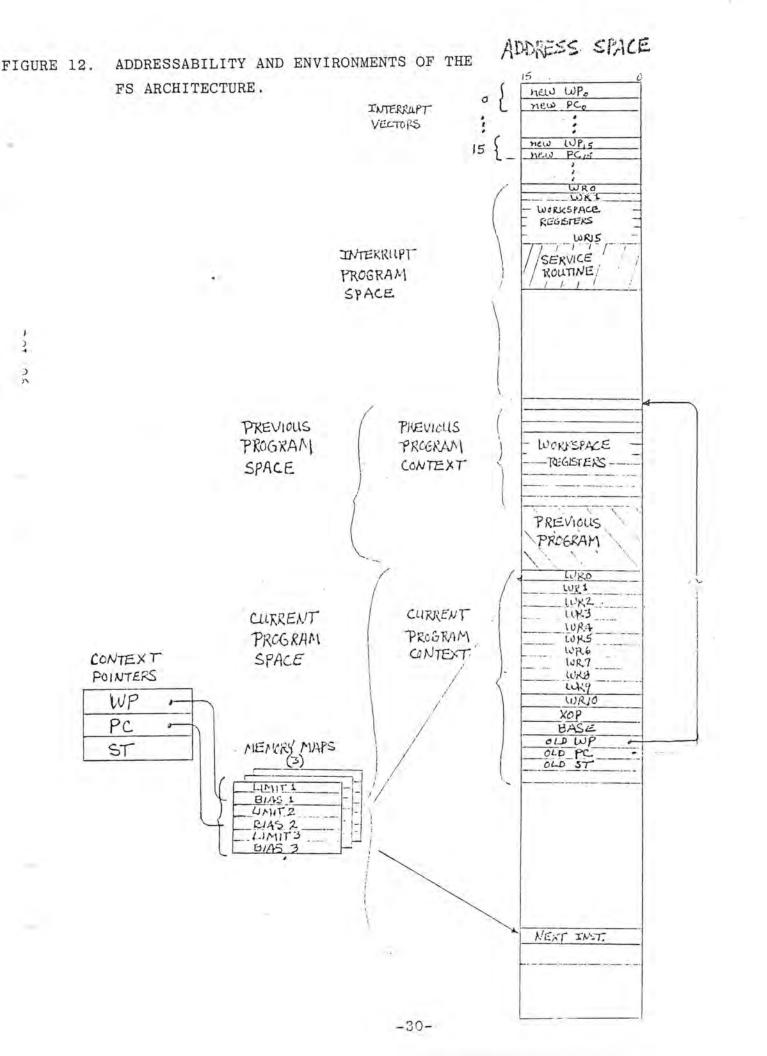

The sophisticated microprocessor is a 16-bit parallel, word, byte, and bit addressable machine with versatile memory addressing facilities, strong interrupt handling features, automatic memory mapping, and context

switching\* ability. How can all of these requirements be met in a single microprocessor?

The first architectural innovation needed to satisfy the stated requirements is the elimination of working registers. Architectures based on working registers as a separate resource invite inefficiencies in at least two fundamental ways. First, they invite unnecessary software overhead because the registers must be loaded and stored, frequently. The loads and stores do not produce results; they only prepare operands for operations that produce results. It would be more efficient to directly perform the operations on the operands regardless of their location in memory.

Secondly, the registers of a traditional architecture are shared by every process in the system. Whenever processing <u>switches contexts</u>, the registers must be saved and then restored. Context switching may occur whenever a subprocedure is invoked either through an interrupt or else by normal program execution. Clearly, the need to share working registers has caused many problems in the design of operating sytems.

Register allocation and management problems are avoided in machines organized around a pushdown stack architecture. The stack is stored in memory and every

\*Context switching is defined here as a state change requiring a new environment. The context of this machine changes whenever a subroutine, interrupt, or process change occurs.

operation in the instruction set operates on the top elements of the stack. Context switching is simple and fast because the stack has the natural ability to nest environments or mark the top of the stack in order to return later to a previous state. Unfortunately, stack machines restrict access to other portions of memory and require wasteful loads (push) and stores (pop) to prepare operands for processing.

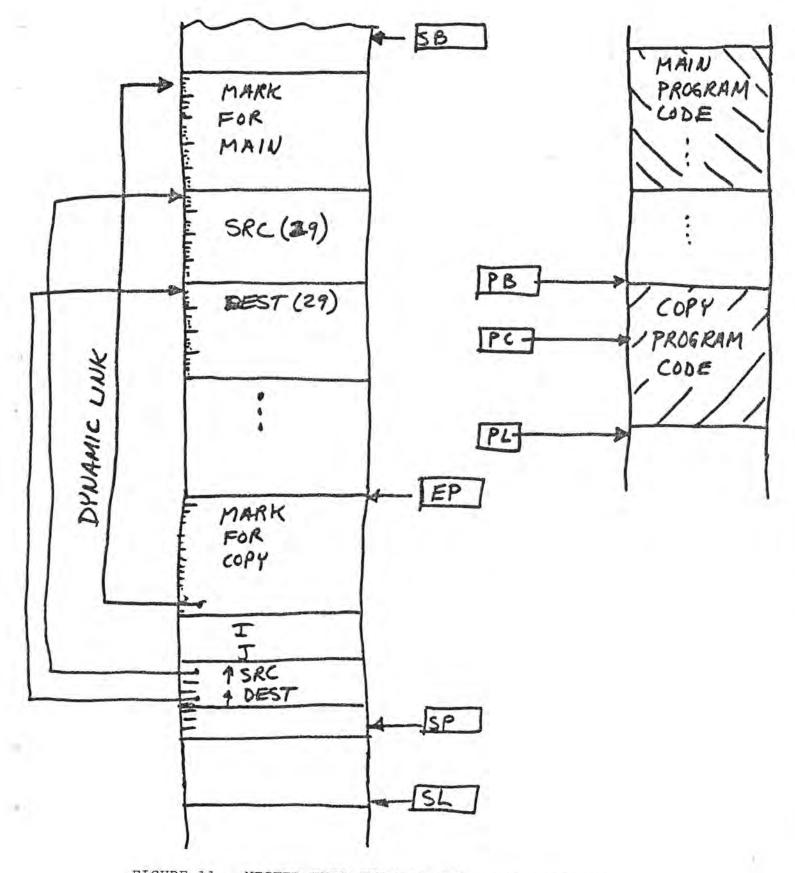

An example that illustrates an inherent weakness of stack architectures is the process of dynamic storage allocation. Dynamic storage allocation is performed by programs written in block-structured languages such as ALGOL and PL/1. Upon entry into a nested block, the local variables are allocated space by creating a segment of storage on the top of the pushdown stack. As processing continues, the stack continues to grow, and indeed when a second nested block is encountered, it is possible to require a second block of local storage to be allocated on the top of the stack. At this point, the stack

architecture must be able to also access the data stored in the outer block. This non-local data is not on the top of the stack, but instead it is many stack frames into the stack. Thus, the top-of-stack operations no longer are able to access the outer data without additional modes of addressing.

The stack machine can be stressed further with the problem of global dynamic allocation posed by PL/I derivatives. The ALLOCATE construct of PL/I makes it possible for a programmer to create a variable (and its space) at any time in the execution of a program. Conversely the FREE construct allows a programmer to destroy the variable (and its space) at any point in the program. These operations fragment pushdown stack storage disciplines and the resultant overhead becomes prohibitive. Typically, this problem is handled by bypassing the stack and resorting the traditional addressing modes and traditional load/store overhead operations. In otherwords, pushdown stack mechanisms have only limited advantages over traditional organizations.

A sophisticated microprocessor must be able to switch contexts as easily as a pushdown stack machine and yet access data as randomly as a register machine.

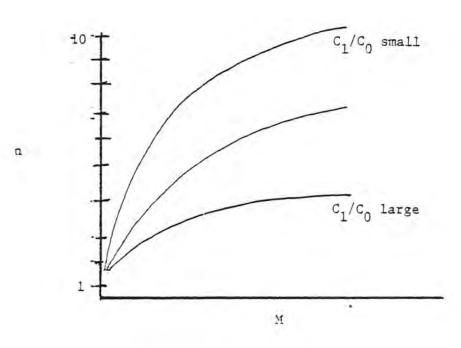

In addition, it would be highly desirable to either maintain a very large number of working registers or else eliminate them entirely in favor of direct access to memory words. The microprocessor and RAM (random access memory) of Figure 5 is a step in this direction.

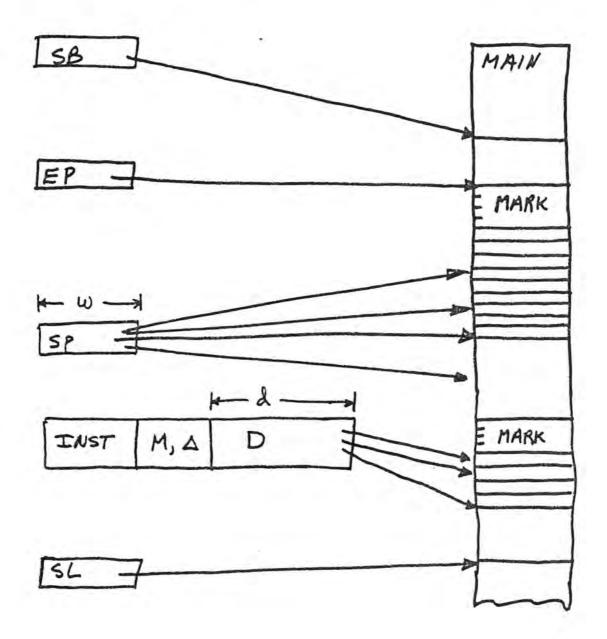

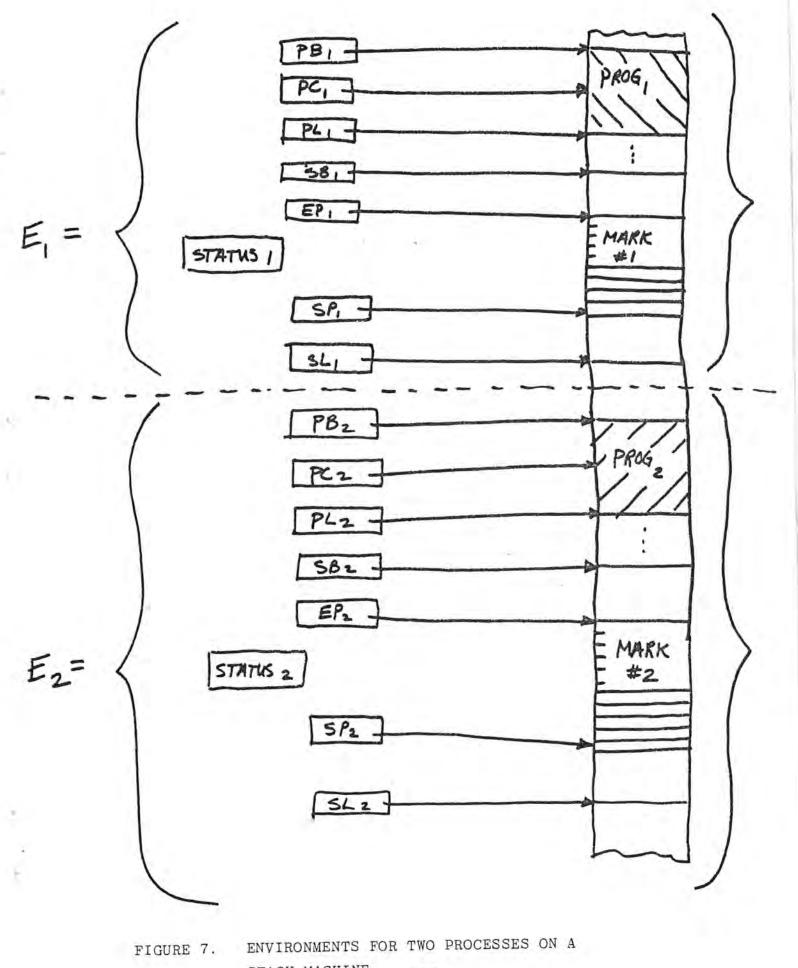

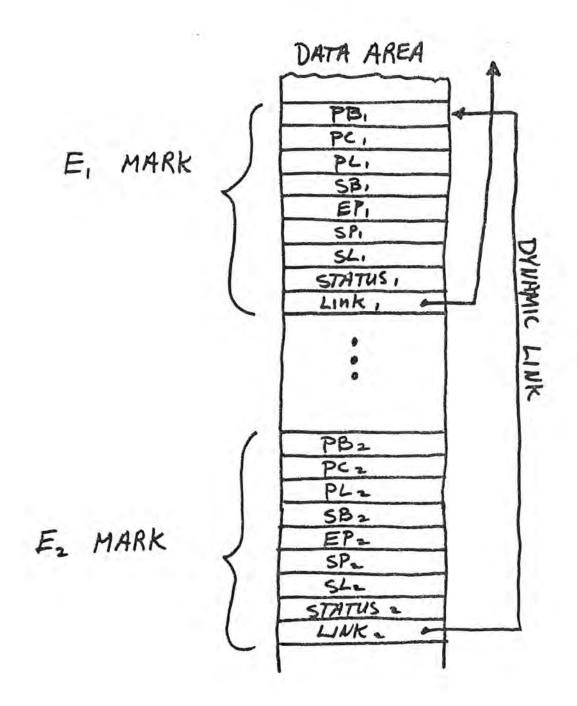

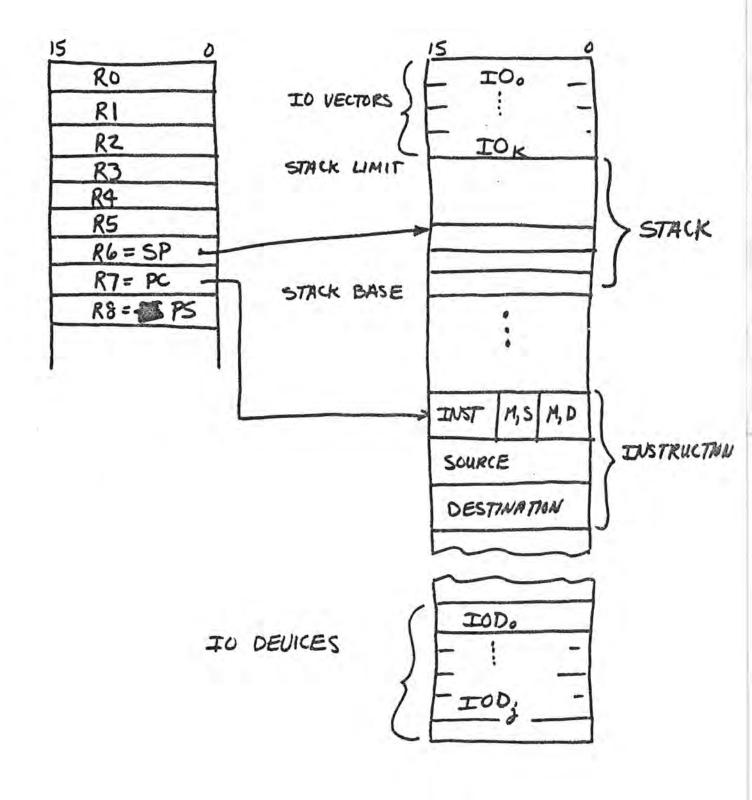

The microprocessor of Figure 5 contains three internal registers called CONTEXT POINTERS and three files of 6 registers each called the MEMORY MAPS. All other registers are part of main memory and are accessed through the CONTEXT POINTERS working in harmony with a MEMORY MAP.

The CONTEXT POINTER WP (working pointer) is a 16-bit address that is modified by BIAS i, where i is determined by the value of WP and the LIMIT registers. If LIMIT 2  $\lt$  WP  $\lt$  LIMIT 1 then a 20-bit effective address is formed by adding (BIAS 1) \*2<sup>5</sup> to WP. The BIAS register is shifted left 5 bits before addition to effect the multiplication by 32. If LIMIT 2  $\lt$  WP  $\lt$  LIMIT 3, then BIAS 2 is used to compute a 20-bit effective address. Finally, when WP > LIMIT 3 the BIAS 3 offset is used.

Clearly, the memory mechanism adds to the power of this microprocessor. Programs and data are all referenced through the MAP. This means that large memory spaces can be addressed and segments containing data or programs need not be contiguous.

\* This is the Texas Instruments 990 series processor, see reference (5).

Notice in the description thus far, that the microprocessor manipulates pointers to data as opposed to manipulating data directly in internal registers. This level of indirection is the source of much of the microprocessor's power and sophistication. Indirection supplies the ability to do context switching with the ease of a pushdown stack machine.

The WP pointer (with modification by the MAP) references a segment of memory called the CURRENT PROGRAM CONTEXT. The first 16 words of this context serve as "workspace registers". WRO through WR15 appear to a programmer as working registers. Each context has its own bank of workspace registers WRO through WR15. Observe that WR11 through WR15 are special purpose registers as well as being general registers. In particular, WR14 is used to hold the OLD WP of the previous context. Thus the advantages of a pushdown stack are realized while at the same time the advantages of random access remain. Furthermore, local register space is protected from non-local contexts that endanger the integrity of data stored in the registers.

The example of Figure 5 also demonstrates how interrupts are vectored to the appropriate service routine. The INTERRUPT VECTORS contain "new WP"

lais

and "new PC" addresses that point to the service routine and its workspace. Since the old WP and old PC are automatically saved in the service routine workspace, returns from interrupts are simplified. Interrupts may be nested inside of interrupts.

The XOP (extended operations) register in WR11 of the workspace provides a means for extending the hardware or software of the sophisticated microprocessor. There are 16 instructions not implemented in the processor. When one of the unimplemented opcodes is encountered, a trap occurs and the microprocessor tests the effective address generated by the "illegal" opcode to determine if the address points to hardware or software. This pointer is stored in WR11 (XOP) of the new context. If the instruction is simulated by software, the routine at XOP is executed. If the instruction is interpreted by hardware, the execution at XOP is performed and the results returned to the workspace. The reader is advised to keep this feature in mind for a later discussion concerning LSI software, see section 2.2.

The driving force behind the sophisticated microprocessor is the dollar-volume expansion that results from replacing minicomputers with microcomputers.

Figure 6. A Sample Program For The Microprocessor of Figure 5.

|       | TITL        | 'MULTIPLE BYT  | E ADD ROUTINE'           |

|-------|-------------|----------------|--------------------------|

|       | IDT         | 'ADDITION'     |                          |

| *     |             |                |                          |

| *     | Set-up      | WP, PC, ST and | Workspace Registers      |

| *     |             |                |                          |

| os    | DATA        | WS, PC, >F     | initialize WP,PC and ST. |

| WS    | DATA        | FIRST          | WRO points to FIRST      |

|       | DATA        | SECND          | WR1 points to SECND.     |

|       | DATA        | > 3            | WR2 indexes operands.    |

|       | BSS         | 26             | WR3-WR15 not used.       |

| FIRST | DATA        | > 0084, > BA90 | right justified operand. |

| SECND | DATA        | >0032, >AF84   | right justified operand. |

| *     |             |                |                          |

| *     | COMPUTE SUM |                |                          |

| *     |             |                |                          |

|       | CLC         |                | clear carry bit in ST    |

| LOOP  | ABC @SECND( | 2),@FIRST(2)   | add low-to-high bytes.   |

|       | DEC 2       |                | decrement WR2 index      |

|       | JNE LOOP    |                | done?                    |

This technological jump is reflected in greater programming "power" when compared with the previous microprocessors. Figure 6 illustrates how the 3-byte addition routine of Figure 2 and Figure 4 appears if programmed in the assembly language of the sophisticated microprocessor.

Notice the actual executable segment of Figure 6 is only 4 words long. This is a 50% reduction in program length and corresponding execution time over the improved microprocessor routine in Figure 4. The improvement is possible because memory-to-memory operands are allowed and WR2 is used as an indexcounter. This mode of addressing is possible without sacrificing the advantages of rapid context switching.

Also, a fair comparison of microprocessors must account for the overhead required to set up the workspace and data. This overhead was sizeable in the sample of Figure 6, but of minor consequence in realistically sized programs. Once the context environment is set up for each context, the advantages of rapid switching offset the set-up inconvenience.

The OS statement illustrates how three words are used to initialize WP, PC, and ST in the CONTEXT POINTER registers. The >F bit pattern supplies initial condition codes for the active ST register.

The WS statement initializes the workspace for this context. A pointer to FIRST and SECND are set up in WRO and WR1, and the length of operands is set up in WR2. The BSS pseudoop simply reserves space for the other workspace registers.

The FIRST and SECND operands are stored in two 16-bit words. They are hexadecimal constants designated by the assembler " > " notation.

The summation is performed by clearing the CARRY bit in ST, performing an "add with carry" ABC, and looping until all three bytes have been summed.

The @ notation indicates that the data is at FIRST plus index register 2, and at SECND plus index register 2, respectively. The first operand is added to the second operand. The sum is stored in FIRST.

Finally, the index register is decremented and the loop is repeated as long as WR2 is not equal to zero (NE). Execution of these four instructions takes ten machine cycles to sum all three bytes.

The idea behind this microprocessor is to gain sophistication through elegant simplicity. The elegance of stack processing and direct memory-to-memory random access processing are retained without loss of simplicity.

The goals of this microprocessor are futile if we cannot find ways to tap the simple elegance of this architecture. This requires programming in a form

consistent with the cost of a microcomputer. How can we cope with programming a microcomputer?

2. Firmware

#### 2.1 Definitions

Firmware is programmed hardware. It is software merged into hardward because it combines programming with non-alterable hardware. How can this be?

A <u>microprogram</u> was defined earlier as a program residing in ROM (read-only-memory). Because it is unalterable, the microprogram is called firmware.

Software for a microcomputer is turned into firmware by storing\* it in ROM. This means that constants may be taken from the program space but that results can never be returned to the program space. Thus program and data must be separated. The side effects of alterable program spaces are eliminated.

Traditionally, (and more precisely) the concept of microprogramming applies to the firmware resident in the control unit of a computer. Since the control unit directs a computer during hardware interpretation of machine language instructions, microprogramming

\*The ROM is initially "burned" by passing a high voltage through the memory. This high voltage distructively alters the ROM leaving a bit pattern which can be output during emulation.

is meant to determine the nature of machine language. In a sense, the control unit is another computer inside of the machine language level computer.

The invention of microprocessors and microcomputers blurred the precise meaning of microprogramming. The trend is to accept the definition used here. We will see why this definition may persist when the concept of LSI software is expanded.

#### 2.2 Software LSI

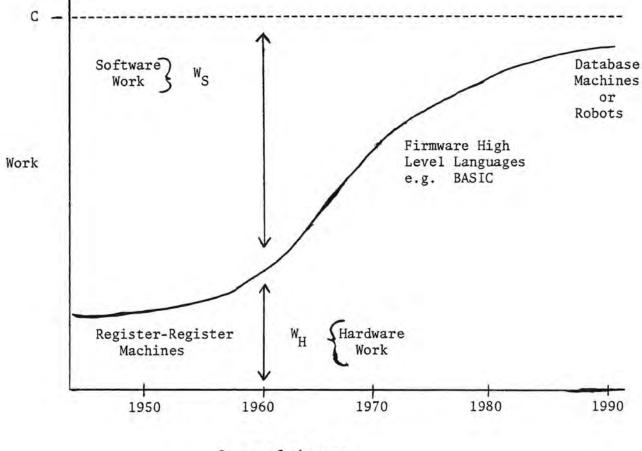

LSI (large scale integration) is responsible for the microcomputer revolution. LSI hardware technology reduced the cost of entire cpus, memory, and peripherals to the point where hardware is "free".

Unfortunately, software costs have continued to climb due to increased complexity in systems and the fact that software production is essentially a custom manufacturing process. Daily, software programmers implement their customized versions of mathematical routines, payroll routines, etc. Most of

these software packages have been written hundreds of times with little knowledge of their duplication.

Manufacturing of software must turn to "software" LSI techniques analogous with hardware LSI techniques before advances can be made in reducing software costs.

An obvious step toward reducing the cost of software is to share identical programs with many different microcomputers. Pocket calculators, for example, share the same SIN (x), %, and 1/x routines with thousands of microcomputers. This is done by encapsulating software in a ROM which is mass produced as an LSI software module.

An <u>LSI software module</u> is a microcomputer and companion ROM memory containing firmware dedicated to a specific function or functions. The scientific subroutine package of a large computer can be economically replaced by an LSI software module similar to the pocket calculator. Once this module is "plugged in" it is never "reinvented" by a software programmer. Instead, it is forever encapsulated in firmware.

A software module must be used frequently and be thoroughly tested before it is committed to LSI encapsulation. Wide acceptance of the module is based upon frequent use, and recognizing that the module is a "primitive". Obviously, since it is shared by thousands of microcomputers, it must work properly.

A language interpreter such as BASIC or APL is easily encapsulated as an LSI software module. These languages have an ad hoc standard that assures relative stability. Thus, the standard APL and BASIC are recognized as primitives. Mass production of APL or BASIC interpreters is accomplished by mass production of ROMs containing bit patterns for controlling a microcomputer. The result is low cost "software".

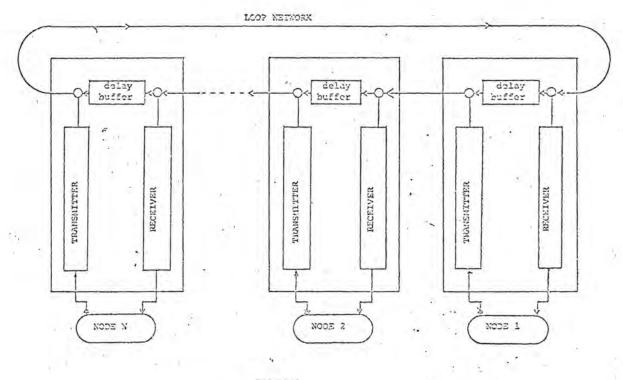

The concept of pluggable LSI software leads to the concept of distributed microcomputer processors. Such processors are constructed from LSI software modules. Each module is a ROM and microprocessor dedicated to a specific function.

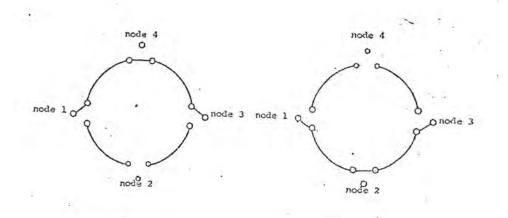

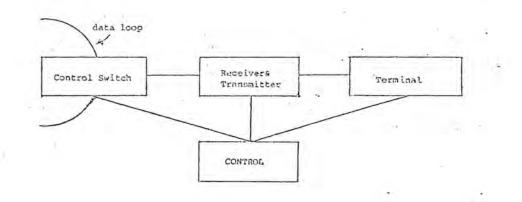

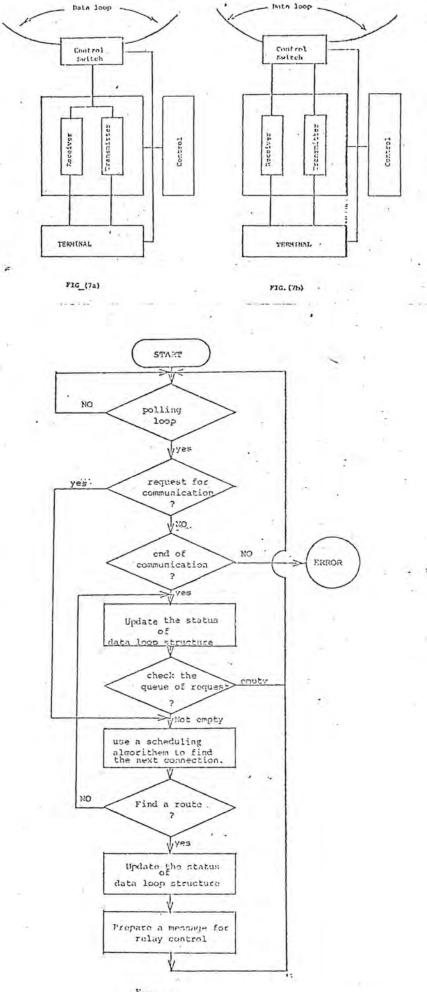

Distributed microcomputers must be managed in a simple, yet elegant way or else the same complexities that plague larger computers and networks will also plague distributed LSI software microcomputers. The <u>microcomputer</u> ring, Figure 7, is one such approach.

In Figure 7, two LSI software rings have been formed from LSI software modules. The PROCESSOR ring is formed by plugging APL, BASIC, a CALCULATOR, an OPERATING SYSTEM, and two MEMORY units into a circular shift register. In addition, an INTERCOMM module is plugged into both rings to handle communication between the PROCESSOR ring and the I/O ring. Each ring consists of a large circulating shift register memory. Information is introduced into the

Figure 7. The Microcomputer Ring Concept MEMORY NEWORY CALCULATE BASIC PROCESSOR RING  $\leq$ APL OPER SYS. DATER terminal I/O RING A Commal terminal 37

shift register by any LSI software module interfaced to the ring. Each module has an address corresponding to the address of the shift register word or words connected to its LSI software module interface.

Information is circulated in the ring forever or until removed by one of the LSI software modules. Thus, the counter clockwise circulating shift register provides input on one side and output on the other side of each interface.

The I/O ring consists of a circulating shift register with LSI software modules for terminals plugged into it, and a connection to the PROCESSOR ring. The terminal LSI software modules consist of CRT/KEYBOARD and local memory/microprocessor for controlling terminal activities. The ring interface allows information to flow to other terminals of the ring or to the PROCESSOR ring via the INTERCOMM LSI software module.

The microcomputer ring concept eliminates system software. System programs are LSI software programs encapsulated in ROM. The firmware eliminates the need for protection and increases reliability.

As an example, suppose a terminal user decides to execute an APL statement.

A ← +/A ÷ ρ A

The user logs onto the I/O ring by typing a password into his terminal. This password is copied into the circulating

I/O ring where it continues to circulate until the INTERCOMM module takes it from the I/O ring and enters it into the PROCESSOR ring.

Clearly the messages entered into a ring are accompanied by a source and destination address. Hence, at each interface these addresses are compared to determine which LSI software module should respond. When the addresses match, the LSI module may be busy, thus the message is circulated one full cycle before reaching the destination again. This process is repeated until the message is absorbed by the destination LSI module.

The password is circulated in the PROCESSOR ring until picked off by the OPERATING SYSTEM module. The OPERATING SYSTEM module reverses source and destination addresses and formats a return message. This process also initiates the necessary control tables for this user. These tables are kept in the OPERATING SYSTEM module's local memory or in one of the MEMORY modules.

The terminal user types in a command, next:

## APL

This command travels around to the OPERATING SYSTEM again and when the APL statement is entered, the following steps take place. The OPERATING SYSTEM intercepts the statement. Since the user is in APL mode, the OPERATING SYSTEM forwards the statement to the APL LSI software module. The APL

module parses the statement and sends out a series of CALCULATOR messages to perform the +/,  $\rho$ , and  $\div$  operations. These operations are eventually performed and the results returned to the APL module. The APL module returns a message to the OPERATING SYSTEM. Finally, the user receives a message from the OPERATING SYSTEM and the dialog continues.

The ring structured microcomputer is simple and elegant. Network complexity is not allowed to get out of control because a ring is the simplest kind of network.

System software is manageable in a ring microcomputer because it is modular and encapsulated as firmware primitives. Even when testing a new module, the interaction between the untried module and the other modules is localized. This eases system integration problems in the same way that top-down structured programming does.

The ring network of microcomputers is untested. For example, when the ring shift register becomes full, a contention will arise. In this sense, the ring is a buffer. Further investigation into the properties of rings is needed before conclusions can be drawn.

LSI software is an outgrowth of good programming technique. Programming in single statements is analogous to building a computer from flip-flops. Programming in

subroutines or structured control structures with single entry/single exit flow of control can be compared with building a computer from medium scale integrated circuits. Programming with firmware modules can be compared to building microcomputers from LSI microprocessor chips.

2.3 Grand Scale Integration

<u>Grand scale integration</u>, GSI is the concept of combining LSI memory and microprocessor units into a single chip. The memory is "charged" with a firmware program at the factory. The firmware charge customizes the GSI chip into a tailored device. A firmware charge may turn one GSI chip into a memory management processor and another chip into a language processor.

GSI chips may be used to build ring microcomputers, or they may be used in applications previously untouched by microcomputers. Since GSI expands the dollar-volume force, we should expect to see GSI in widespread use in the future. The author conjectures that GSI is the next step following the LSI age.

In the next section we examine alternatives to the problem of developing end-user applications through programming LSI and GSI computers.

## 3. Software

## 3.1 Problems

The dollar-volume force driving a technological advance ultimately owes its power to applications. In microcomputer technology, applications are realized only after considerable programming effort. Historically, programming effort has grown to the point where software cost is the economic determining factor.

In the previous section, we studied LSI software approaches to reducing software costs. In both cases, the cost is reduced after the software is produced. In this section, we study methods of reducing the implementation costs of first-time systems.

The problems associated with microcomputer programming stem from 1) the limitations of the architecture, 2) the transient period of bootstrapping from one machine to another machine, and 3) the problems that have always plagued programming.

The previous study of three typical microprocessors revealed features that facilitate assembly language programming. The use of index registers and a pushdown stack were noted as improvements over simple register transfer architectures. The sophisticated microprocessor example demonstrated how context switching and direct memory access to operands can ease the burden of system implementation.

Thus, the architecture of a microcomputer is fundamentally important to software development.

Once an architecture manifests itself in the form of a microcomputer, there is a time delay between hardware design and software design. The contemporary generation of microcomputers suffer from a lack of software. This shortage will continue until the transient period passes. Several temporary solutions are employed to overcome the software development transient.

A <u>cross-translator</u> is a program running on one machine that produces object code for another machine. The cross-translator runs on a parent computer and generates code to be executed on a child computer. The parent computer typically executes an assembler or high level language compiler written in a common language like FORTRAN. The output from the parent computer is loadable object code for the child.

A <u>portable software package</u> is a software package written in a language that is "easily" moved from machine to machine. The mobility of a portable software package may be due to its self-compiler feature or due to a collection of primitives that can be easily transported onto another machine.

In the case of self-compile portability, a crosscompiler is employed on the parent computer. The crosscompiler produces code for the child computer regardless

of source input. Suppose the source input is the crosscompiler itself. Then the object code that results from self-compile is used to transport the cross-compiler onto the child computer. Once moved to the child, the cross-compiler becomes a stand-alone compiler and may be used in the same way that it was used on the parent computer.

A portability software package may also be written in a primitive portable language. The primitive portable language may actually consist of a set of macros whose expansion is determined by the child computer's architecture. A different prototype model is needed for each new child computer.

The primitive portable language may manifest itself as a hypothetical child machine. The hypothetical child instruction set is used to implement all portable software. When the software needs to be moved, a <u>transportation program</u> is written that maps each hypothetical child instruction into an equivalent actual child instruction (s).

Both approaches to portability are being used in contemporary microcomputer systems. The central problem hindering both approaches is code efficiency. Further work is needed to improve the object code resulting from transportation of software.

Ultimately, the problems that microcomputer programming faces are the general problems of software production.

The need for more "powerful" and expressive languages, for example. There are some indications that programming is about to make a grand departure from traditional procedural language techniques to other forms of man-machine communication. In the following sections, we examine alternate approaches to programming. In particular, we concentrate on forms of man-machine communication that fit well into the microcomputer dollar-volume force.

3.2 A System Implementation Language

The obvious approach to implementing software on a microcomputer is to use a high level language. The high level language should have several features of an assembler language, however, because the language is used to implement control programs, compilers, etc and requires the ability to access machine level resources. Such languages are called SIL's (system implementation languages).

Typically a SIL for a microcomputer executes as a cross-compiler. Although, this may be a transient mode of operation, the limited memory of many microcomputer systems prevent implementation of sophisticated SIL's. Often the resulting object code being produced is on the order of 16KB while the SIL translation may require 128KB of memory.

Figure 8. Example Of A Systems Implementation Language

MATCH: PROCEDURE (PTR1, PTR2) BYTE ; DELCARE (PTR1, PTR2) BYTE ; DECLARE (STR1, BASED PTR1 , STR2 BASED PTR2) ADDRESS ; DECLARE I ADDRESS ; DECLARE (J1, J2) BYTE ; J1, J2, I = 0 ;

IF J1 = OFFH THEN RETURN (0) ; J1 = STR1 (I) ; J2 = STR2 (I) ; I = I = 1 ; END LOOP:

LOOP: DO WHILE J1 = J2;

RETURN (-1); Return (-1) when no match, 0 when match. END MATCH ; Figure 8 illustrates a SIL<sup>\*</sup>for implementing software on the microcomputer of Figure 1. This program computes a zero if the two strings at location PTR1 and PTR2, respectively are equal. An 8-bit (-1) is returned as a hexadecimal OFF, otherwise.

Upon entry into PROCEDURE MATCH, the first string STR1 is located by pointer PTR1 and the second string STR2 is located by PTR2. This is indicated by the ADDRESS attribute that declares STR1, STR2, and I as symbolic labels for addresses in memory.

The BYTE sized pointers PTR1 and PTR2 contain the address of STR1 and STR2. Since they are passed by value, the MATCH routine is useful for comparing any two strings at location specified by PTR1 and PTR2.

In the sample program, each character of the two strings is moved to J1 and J2, respectively. J1 and J2 are compared and as long as they are equal, the next byte pair is compared. The code OFFH is used to indicate that the end of the string STR1 has been reached. In this case, the strings are equal and a zero is assigned to location MATCH.

The LOOP segment of the demonstration program repeats as long as the character in Jl matches the character in J2. When the value of Jl = OFF hexadecimal, the last character of the string has been reached.

\* The SIL in this example is a version of PL/M for the Intell 8080 system.

Each byte of STR1 is copied into J1 and each byte of STR2 is copied into J2. This is done by indexing STR1 and STR2 by I. The index value stored at location I is incremented and the loop executed again unless J1 does not match J2.

This program is compiled into machine language for the microprocessor of Figure 1. Since the microcomputer is an 8-bit architecture and we know that considerable effort is required to overcome its limitations, this language greatly improves the prospects for programming the machine. The language "covers-up" the limited architecture and yet allows a programmer access to data bytes and addresses. Perhaps the greatest improvement is that the SIL provides indexing and addressing capability lacking in the machine itself.

The SIL approach is an outgrowth of language development on large machines. Since microcomputers are revolutionizing the way we think about computing, perhaps it is also time to question the SIL approach. Are there better ways to program extremely low-cost hardware without paying dearly for software?

3.3. Pushbutton Programming

One of the startling revelations of the LSI hardware era was the significance of pocket calculators. Pocket

calculators are partially successful because of their simple man-machine interface. Their interface eliminates the traditional operating system, language processor, utilities, and computer terminology and replaces them with the finger. A pocket calculator is programmed by pushbutton.

Pushbutton programming can be elegant and sophisticated in spite of its simplicity. Elegance is usually achieved in one of two ways, 1) identifying primitive "button" operations for a given application, or 2) building primitive "button" operations on top of other primitives in a hierarchy of modules.

Primitive button operations are implemented in LSI software modules or as software programs. The LSI software module approach is based on firmware encapsulation of accepted standards. We discussed the encapsulation process for a ring structured microcomputer, earlier.

The software program approach typically represents an experimental or intermediate step in developing a truly pushbutton microcomputer system. Once the function represented by each "button" is known to be primitive to the application, the software program for the function should be encapsulated as an LSI software module. This has been done, for example, with BASIC interpreters and I/O controllers.

Figure 9. Sample Pushbutton Program For Business Primitives

| ACCOUNT | FILE                                   |

|---------|----------------------------------------|

| NUM     | FORM 8                                 |

| NO      | FORM 8                                 |

| INDEX   | FORM 8                                 |

| NAME    | DIM 40                                 |

| BALANCE | FORM 5.2                               |

| LENGTH  | FORM "3997"                            |

|         | OPEN ACCOUNT, "LOOK UP"                |

| START   | DISPLAY "ENTER ACCOUNT NUMBER"         |

|         | KEYIN *N, "ACCOUNT?", NUM              |

|         | MOVE NUM TO INDEX                      |

| MOD     | SUBTRACT LENGTH FROM INDEX             |

|         | COMPARE LENGTH TO INDEX                |

|         | GOTO MOD IF LESS                       |

| LOOK    | READ ACCOUNT, INDEX; NO, NAME, BALANCE |

|         | GOTO ERROR IF OVER                     |

|         | COMPARE NO TO NUM                      |

|         | GOTO LOOK IF NOT EQUAL                 |

|         | DISPLAY NAME, "HAS BALANCE=", BALANCE  |

|         | GOTO START                             |

| ERROR   | DISPLAY "NO SUCH ACCOUNT IN FILE"      |

|         | GOTO START                             |

|         | STOP                                   |

Figure 9 demonstrates a pushbutton program for a pushbutton microcomputer. The microcomputer is assumed to consist of a CRT/Keyboard, microprocessor and memory, and a diskette mass storage device for file storage.

The program of Figure 9 assumes a file containing names and balances. Upon entry of a name, a balance is retrieved and output to the CRT console.

The FILE button establishes a file named ACCOUNT. The FORM buttons declare (NUM, NO, INDEX) as numbers requiring 8-digit accuracy. The DIM button reserves space for a 40-character string. The BALANCE number is a dollar and cents figure with up to 5 digits for the dollar amount and 2 digits for the cents amount.

The ACCOUNT file is OPENed for "look-up". The DISPLAY and KEYIN buttons perform I/O via the CRT/Keyboard. The account number NUM is moved into variable INDEX where it is reduced modulo LENGTH (notice that LENGTH is 3997). The remainder produced by the MOD segment of code is used to index into the ACCOUNT file.

The LOOK segment searches the ACCOUNT file by directly indexing into the ACCOUNT file. If NO, NAME, and BALANCE are not the desired matching record, then the file is searched sequentially until the matching records are found. If no matching records are found, then the search terminates with a DISPLAY message at ERROR.

The language is DATABUS which is used on Datapoint computers, see reference (4).

Each time a READ is executed, the value of INDEX is incremented to the next record in the file. Thus, each time through the LOOK loop another record is retrieved from the diskette file.

The pushbutton microcomputer illustrates how programming is simplified for business data processing applications. The primitives are data processing primitives as opposed to mathematical, word processing, or graphical primitives.

The disadvantage of the type of microcomputer system shown in figure 9 is that the system is limited. The primitives are fixed, and although sufficient for the intended novice user, they cannot be combined into subprocedures, "superbuttons", or extended by adding other functions. The next section illustrates a more sophisticated button pushing language that overcomes these limitations.

## 3.4 Improved Pushbutton Programming

It is desirable to have a powerful pushbutton language that is simple and easy to use. Simplicity and power do not always go hand-in-hand, however. How can we reach a compromise between the two within the limits of microcomputer based systems?

Suppose a primitive set of "buttons" are used to build more sophisticated structures through modular con-

struction of "superbuttons". A superbutton is a procedure that invokes many lower level buttons. It is the concept of a subprocedure as applied to pushbutton programming.

Extension through superbutton programming requires a table mechanism to manage the names of the buttons. A <u>dictionary</u> and <u>interpreter</u> are needed to process the superbutton primitives.

The dictionary contains the name of each button and a pointer to a code segment. The code segment is a chain of other pushbuttons (all of which are contained in the dictionary) or a segment of microcomputer executable machine code.

Since each button could possibly have one or more parameters passed to it or generated for it by another button, a parameter passing mechanism is needed. Thus, a pushdown stack processor is used to execute the superbuttons and process their parameters.

The interpreter performs dictionary look-up and manages the pushdown stack. Obviously, since the interpreter is nothing more than a program, it too can be written in the pushbutton language. In fact, the interpreter is an example of a superbutton, see below.

: INTERPRET

BEGIN

WORD FIND IF EXECUTE ELSE NUMBER THEN QUERY

END ;

The : denotes that this is a superbutton named INTERPRET. The chain of buttons to follow define what it means to push INTERPRET. Since the interpreter runs forever, the BEGIN-END pair brackets a never-ending loop.

WORD extracts the name of a button from the input device (we assume a microcomputer like the one in the previous section). FIND searches the dictionary and returns TRUE if the name previously input matches an entry in the dictionary.

The pushdown stack maintained by the superbutton processor contains either a TRUE or FALSE after FIND is performed. The IF is performed if the stack contains a TRUE. The ELSE clause is executed if a FALSE appears on the stack. Suppose the TRUE condition results, then the EXECUTE button performs the function indicated by the button found in the dictionary.

If the FALSE condition results, then NUMBER is executed. This button attempts to convert the input name to a binary number. Failure aborts the execution of a user's button stream. The interpreter expects either valid names for buttons or valid numbers as input.

THEN marks the end of the IF-ELSE clauses. Control returns to QUERY in either TRUE or FALSE cases. The QUERY button puts the interpreter in idle mode until more input is available.

The dictionary and interpreter combine to give a user powerful, yet simple access to increasingly complex structures. Extensibility results from building superbuttons on top of relatively low level primitives.

A simple pocket calculator example shows how the INTERPRET button processes an expression.

12 50 \* 10 / .

The 12 and 50 are pushed onto the stack as they are input. This happens because the FIND button returned a FALSE condition (12 and 50 do not occur in the dictionary). The FIND button does locate on \* in the dictionary, though, and the result is that EXECUTE performs a multiply. The result (600) is placed back on the stack and QUERY waits for another input. The 10 is pushed onto the stack, and the / is EXECUTED, leaving a 60 on the stack. The period causes the 60 to be printed out. The interpreter idles.

As a final example, suppose we want a superbutton to compute absolute value. Assuming that ABS is not a primitive button already, we could add it to the dictionary merely by defining it with an : control character.

: ABS

DUP O **<** IF MINUS THEN ;

This code strings together a chain of buttons to perform sign reversal when desired. DUP produces a duplicate on the stack. This duplicate is absorbed by the 0  $\checkmark$  test button that sets a TRUE or FALSE condition on the stack. If a TRUE condition exists, then MINUS performs a sign reversal, and replaces the number on the stack, otherwise nothing is done to the number originally on the stack.

Since the superbuttons are constructed from primitives, the problem of portability is partially solved. Each button is defined in terms of a particular microcomputer machine language. A package of superbuttons for a special application can be moved from one microcomputer to another by rewriting only the basic primitives. These primitives occur in the dictionary, so the actual re-coding is done by changing the code segment referenced by each dictionary entry.

In summary, we can say that SIL's and pushbutton languages both strive to cover-up the limited architectures underlying microcomputer design. The user sees only a symbolic manifestation of the microcomputer.

In the transient period between the large machine era and the LSI era, we should expect a re-examination of the problems and solutions of the past. Pushbutton programming has no precedent in earlier systems because of the easy access by novice users. In the next section,

This is the approach taken by FORTH, Inc, see reference (3).

we study some of the trends brought on by LSI hardware and software.

4. What Computing Has Come To.

4.1 How Large Should a Computer Be?

The microcomputer invasion is bringing an end to the Renaissance Computer\* Age. The reasons for this are both technological and economical.

Hardware costs have, because of LSI technology, diminished below the cost of complexity making general purpose k-way shared systems uneconomical for large values of k. On the otherhand, software development costs remain high due to complexity. Therefore, software complexity is forcing duplication of integrated hard/soft systems in place of hardware systems running a variety of programs.

The hardware shift, as it is called, is also responsible for a shift in the type and number of computer applications. Shifts in applications lead eventually to greater hardware shifts. Viewed from an economic point-of-view, the hardware shift is an "acceleration force" whose rate of change determines the size of future computers.

The first 3 computer generations were charaterized

\* A Renaissance Computer is a general purpose, large, central computer. Its purpose is to do all things. Its size and cost are justified by its multipurpose, multiprogrammed, and often timeshared operation.

by cost and physical size. A typical computer installation consisted of millions of dollars worth of hardware and required massive support in terms of air conditioning, tape libraries, programmers and administrative personnel.

These large, costly computers quickly became Renaissance Computers or what IBM popularized as General Purpose computers. A Renaissance Computer is capable of doing a variety of things: business data processing, scientific calculations, telecommunications, word processing, information storage and retrieval, etc. Actually, however, it was only the very expensive processing problems that were attacked by Renaissance Computers. That is, space age calculations, business for large corporations, and information storage and retrieval for large private universities that could afford to experiment. Small scale computing was a very expensive hobby carried out mostly by aerospace engineers who bootlegged time on the company's Renaissance Computer to simulate Las Vegas games of chance, or academic people who experimented under the name of artificial intelligence or CAI.

There were valid reasons for the Renaissance Computer. Any computer was expensive to fabricate and maintain and so <u>had to be multipurpose</u>. The Renaissance Computer, because of its cost, was an affordable machine only for those with a variety of uses in mind.

The emergence of minicomputers heralded the end of the Renaissance Computer Age. LSI technology has greatly accelerated the coming of the end by decreasing hardware costs to the point where cpu costs were negligible. Indeed, the only obstacles remaining for "computing for the millions" is the cost of peripherals and the amount of effort required in developing software.

The mini/microcomputer provides a hardware basis for the emergence of the Common Computer Age. This age is characterized by inexpensive hardware, novel I/O devices, inexperienced users/programmers, and expanding market and applications, and reorientation of the economics of computing. As in the Renaissance Computer Age, the new age will be governed by economic forces more than technical forces (even though LSI technology brought about the revolution).

The logic of the economic force behind the Common Computer Age goes as follows: The cost of computing is controlled by the number and kind of applications. The number and kind of applications are determined by the cost of computing. Thus, a feedback loop is completed. The delay in this loop is speculated to be 3-5 years, but decreasing with each computer generation.

The topics of 1) novel I/O devices, 2) inexperienced users/programmers, and 3) applications are not central to the issues addressed here, but suffice it to note that TV/keyboard devices are on the increase, BASIC as a pro-

gramming language is rampant, and computer games are in tremendous demand. The reader can easily make predictions based upon these trends.

4.2 The Cost of Complexity

A general system is a collection of interacting parts, each part having well defined features. An understanding of these features does <u>not</u> guarantee an equal understanding of the general system. Indeed, a system often behaves in unexpected ways even after careful study of its parts. Unexpected behavior is frequently observed in computer systems, much to the chagrin of programmers, hardware designers, and users.

A simple model of complexity may be applied to computer systems to determine optimal degree of sharing of hardware, optimal degree of sharing in software design, and to make conjectures about the best size for a "computer".

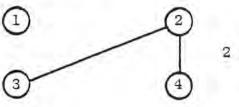

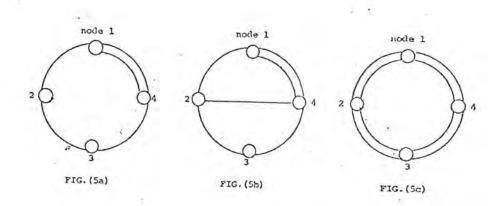

Suppose a system is made of 4 parts as shown below.

3 connections

The first part is allowed to interact in some way with the other 3 parts, also shown above. "Interaction" is a generalized concept. It may refer to communication, a

physical connection, an effect, or some other tangible or intangible connection.

Let us define <u>complexity</u> and its corresponding "cost" as follows:

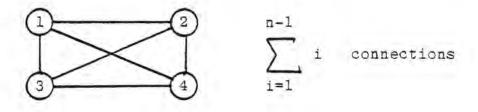

$C_n = C_0$  (the potential maximum number of interactions possible in system of n parts) We can compute the potential maximum number of interactions possible in a system of 4 parts by completing all of the connections in the 4-part system, above.

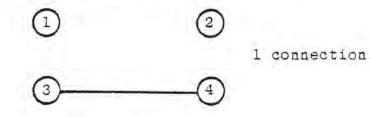

2 connections

The remaining number of connections between the second part and all other parts is 2. The remaining number of connections from part 3 is shown below.

The composite of all of the above shows that in a system of n parts, there are  $(n-1) + (n-2) + \dots 1$  connections.

Thus, the cost of complexity in an n-part general system is proportional to the sum of the first (n-1) integers.

$$C_n = C_0 \frac{n(n-1)}{2}$$

4.3 Large-Scale Versus Micro Hardware

The Renaissance Computer was, and is, made affordable by time-multiplexing the hardware. This is done in a variety of ways, all falling under the misnomer of "timesharing" or "multiprogramming". Actually, what goes on inside of a multiplexed Renaissance Computer is a division of cpu power into k parts by a k-way multiplexing scheme, The purpose of the k-way division is to keep the expensive cpu busy in order to spread its cost k ways.

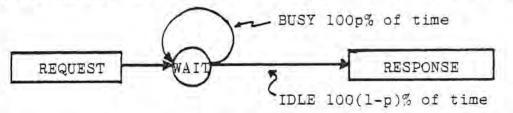

Extensive sharing is a modern day fallacy for two reasons: 1) the cpu is no longer the most expensive part of a system, and 2) the ability of the cpu to render service increases as the cpu becomes <u>idle</u>. This is demonstrated by the simple Markov model of a request for service, below.

The request enters a WAIT state that may or may not hold the request for W units of time, say, and then when the cpu

is idle, the response is given in R units of time. The average delay is given by the simple formula, below.

Avg. Response Time =  $R + \frac{P}{(1-P)} W$ Examination of a plot of Avg. Response Time versus busy time p shows that the smaller p (more idle time) the better is the expected response.

In light of the Common Computer Age, the rule of multiuser cpu design should be to keep the cpu idle as much as possible. This can be done by increasing the cpu speed so that every request takes zero time (R = 0), thus freeing the cpu. Alternatively, we can decrease R by increasing the number of cpu's. Hence, R is decreased, and so is p, by incorporating multiple copies of cpu's.

Let us look now, at the cost of a k-way shared computer. The cost is conjectured to be the sum of the singleunit (k=1) system plus the cost of k-way complexity.

$$H_k = h_0 + h_1 - \frac{k(k-1)}{2}$$

where h<sub>0</sub> = cost of a single system and h<sub>1</sub> = cost of each additional unit needed to provide shared service

The value of h<sub>1</sub> includes the cost of the added complexity in hardware and software (reflected in main memory size) needed to share the basic hardware. This includes protection and addressing mechanisms, communications equipment, large central stores, scheduling algorithms, etc.

This model may seem pessimistic at first, but when compared to other "laws of complexity" is actually rather generous\*. This cost is even more generous when distributed over all k of the parts.

$H_k/k = h_0/k + h_1 (k-1)/2$

The corresponding cost function for non-shared hardware/software systems is obtained when k=1.

$$H_1 = h_0$$

A collection of k non-shared "mini" systems would cost  $kH_1$ . When is it cheaper to use  $kH_1$  systems in place of one  $H_k$  system?

Set  $H_1 = H_k/k$  and solve for k. This produces the quadratic formula:

$k^{2} - (1 + \frac{2h_{0}}{h_{1}})k + \frac{2h_{0}}{h_{1}} = 0$  [A]

with solution:

$$k = \frac{2h_0}{h_1}$$

\*Grosh's Law states that doubling the cost of a system can only be justified if its performance is quadrupled. Why? Minsky's conjecture claims  $\log_2 k$  utility in a k-way parallel system. Thus, we are encouraged to speculate that k-way redundancy will cost somewhere between  $(h_1 k^2)$  and  $(h_1 2^k)$ .

When  $h_0$  and  $h_1$  are known, formula A gives the optimal k-way sharing strategy for a Renaissance Computer. In the case  $h_0 \gg h_1$  (expensive hardware) the result is that  $k \gg 2$ . Hence, multiplexing the hardware is indeed a valid strategy.

In the case  $h_0 \ll h_1$  (cheap cpu hardware) the optimal strategy is to limit sharing, k  $\leq \leq 2$ . If more than 2 users are to share the same cpu, we are advised to duplicate the basic system instead of multiplexing it.

A <u>balanced system</u> is one in which k = 2. Thus, when  $h_0 = h_1$ , we see that there are advantages to foregroundbackground processing. It is only fair to note, however, that the cost of sharing,  $h_1$ , is also declining as memory, communications, and programming techniques decline in cost. In summary, it appears to be wiser to expect shared systems for small values of k in the future. The age of larger scale k-way Renaissance systems has passed\*.

\*Large-scale special purpose systems <u>are</u> expected, as long as a narrow objective is kept in mind. The airlines reservation systems, credit check systems, etc. are examples. These systems minimize complexity by trading-off vast objectives, and do not represent Renaissance Computer systems.

4.4 Large-Scale Versus Micro Software

Large-scale hardware systems imply large scale software efforts. The exception, of course, is when the band of applications is narrow or the system is designed for a special purpose. The software effort expended on Renaissance Computers is documented elsewhere and need not be repeated here. Instead we seek to determine possible boundaries on software effort regardless of hardware limits.

Brooks [1] reports that the effort needed to develop M instructions of software is proportional to  $M^{1.5}$ . If we divide the M instructions into n optimal-sized modules, we can prove that

$S_n = C_0 (M/\sqrt{n})$

This is sketched for the reader as follows: Given,  $S_n = C_0 M^{1.5}$ Let  $S_i = C_0 M_i^{1.5}$ , and  $S_n = \sum_{i=1}^n S_i$  $M = \sum_{i=1}^n M_i$

The object function F is minimized:

$$F = C_0 \sum_{i=1}^{n} M_i^{1.5} - \lambda \left[ M - \sum_{i=1}^{n} M_i \right]$$

$$\frac{dF}{dM_j} = 0; \text{ yields } M_j = M/n$$

and substitution produces  $S_n$ .

A software project that is large enough to be brokenup into n parts also suffers from a loss proportional to the complexity of an n-part system. The cost function for  $S_n$  must be amended to show this.

$$S_n = C_0 \frac{M}{\sqrt{n}} + C_1 \frac{n(n-1)}{2}$$

[B]

$C_0 = man-months$  effort per instruction

$C_1 = man-months$  effort per interaction

The parameters of formula B depend upon vague quantities like "human communication" and "type" of application. Brooks [1] indicates that  $C_0 \doteq 0.001$  for operating systems programming, while  $C_0 \doteq 0.01$  for applications programming. In general, very little is known about the behavior of  $C_0$ or  $C_1$ .

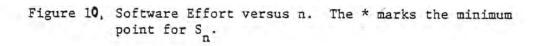

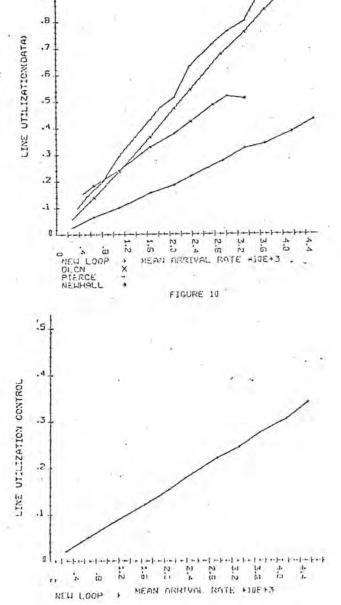

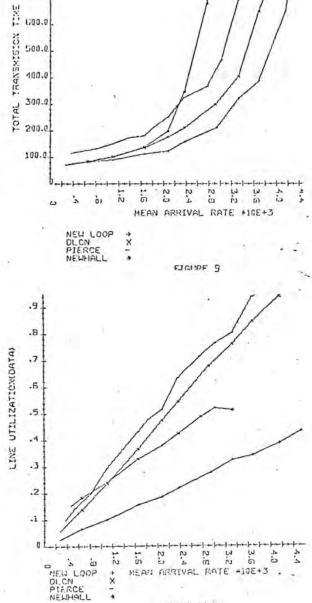

A plot of S<sub>n</sub> versus n reveals an optimal value of n, see Figure 10. This point gives the smallest investment needed to successfully complete the software.

Minimization of  $S_n$  gives the formula for software size as a function of the number of software parts.

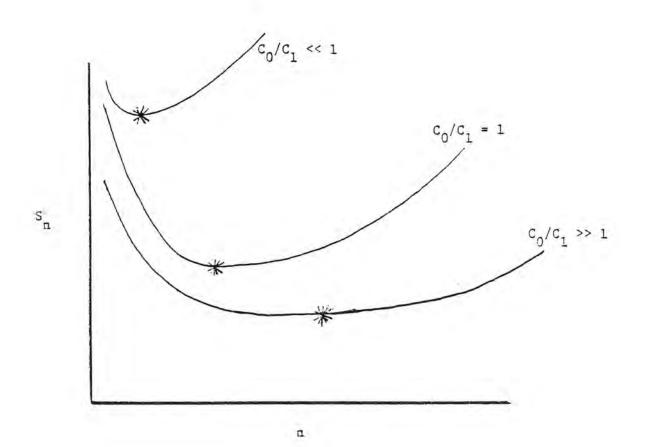

$$M = \frac{C_1}{C_0} \qquad n^{3/2} (2n-1)$$

The inverse of this function is plotted in Figure 11. It shows that even for small software projects, the number of parts should be relatively large (8 to 12), unless  $C_1/C_0$  is extremely large. In short, programming is costly even though the software project is relatively small. There is an "economy of scale" possible, however, because large scale software projects diminish in cost as their size grows, <u>if subdivided into the proper number of parts and  $C_1/C_0$  is</u> <u>large enough</u>.

4.5 Summary

It is clear that a shift in hardware costs is causing revolution in computing. In the past, a single piece of hardware employed a variety of software to solve a (limited) variety of problems. In the future, a (limited) variety of hardware pieces will employ a single piece of software to solve a variety of problems. The most dramatic contemporary example of this Common Computer Age fact is the pocket calculator. The pocket calculator market is built from the notion that a variety of hardware pieces can be applied to a single software piece.

A subtle example of the effects of the hardware shift is found in the many "turnkey" minicomputer systems designed for business data processing. Duplicate hardware systems are married to a single copy of software. The software is

69

....

Figure 11 n versus M for software development

packaged for "vertical" lines of applications, e.g., payroll, accounts receivable/payable, etc. These packages are called vertical because they cut across many industries with small changes in parameters. These systems also demonstrate the principle of limited k-way sharing, because they are restricted to k  $\checkmark$  16 in most cases.

Application of the hardware shift to larger systems leads us to believe that either 1) distributed network of microcomputers, or 2) integrated network of microcomputers are advisable. The distributed network consists of isolated cpu's each with access to a common mass storage unit (s). This provides a way of limiting the local complexity by spreading it over several levels of the network hierarchy.

The integrated network approach consists of a central dispatching unit, cdu, and access to/from special purpose "organs". The organ computers are actually special purpose computers akin to the controllers of current Renaissance computers. The integrated network system copes with complexity by compartmentalizing it inside each specialpurpose organ. Before the total system can be made to operate efficiently, however, some means of intercommunication must be devised so that large-scale breakdowns can be avoided. This problem has not been solved, but the ring structured microcomputer represents an approach to coping with network complexity.

71

In answer to the question posed by the title of this section, we must say that a computer should be large enough to support a limited application and a small number of users. Additional applications and number of users justifies additional systems rather than additional complexity of a single system. The trend should be toward dedicated microcomputer systems with large memories and about 2 users. The number of users may be increased, but the application must then be narrowed to compensate for the added complexity.