#### AN ABSTRACT OF THE DISSERTATION OF

Manideep Gande for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and Computer Engineering</u> presented on <u>June 5, 2013</u>. Title: Design Techniques for Time Based Data Converters.

Abstract approved: \_

Un-Ku Moon

Modern day CMOS processes are characterized by voltage scaling and geometry scaling. Geometry scaling helps reduce gate delays, thereby aiding in the design of data converters which use time based processing. Another artifact of geometry scaling is the increase in complexity of digital circuitry available on traditional analog ICs, as digital signal processing could be used to compensate for analog inaccuracies. Calibration assisted analog-to-digital converters(ADCs), software defined radio, digital phase locked loops, etc... have all gained from improvements in the digital processing available on chip. This thesis focusses on data converters which utilize the above features of modern day CMOS processes.

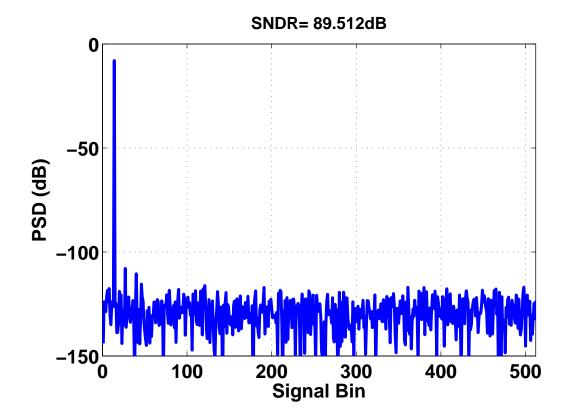

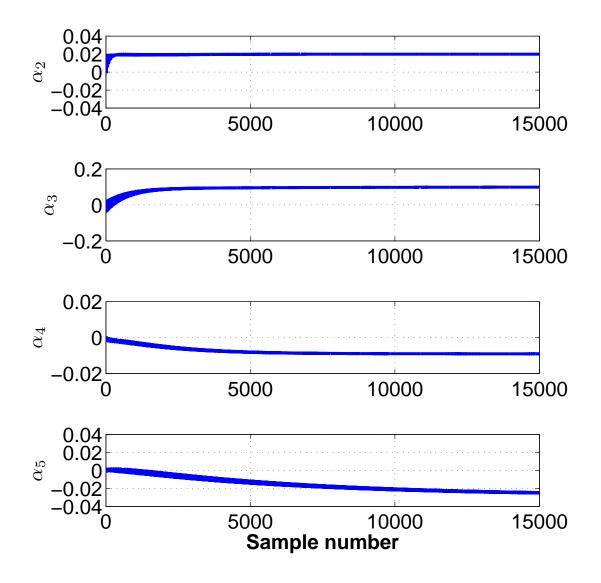

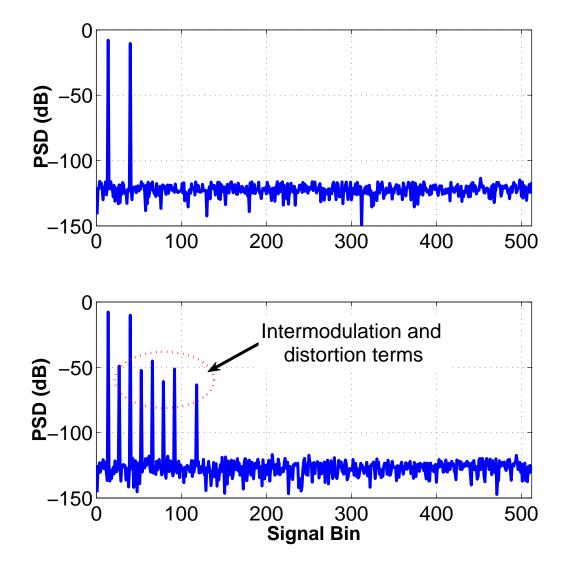

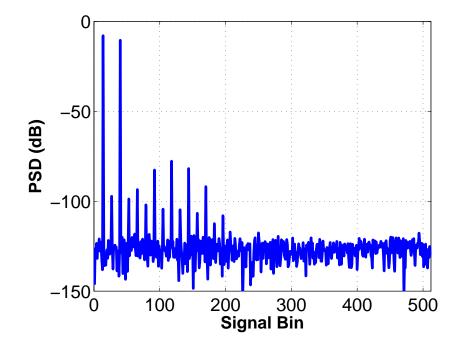

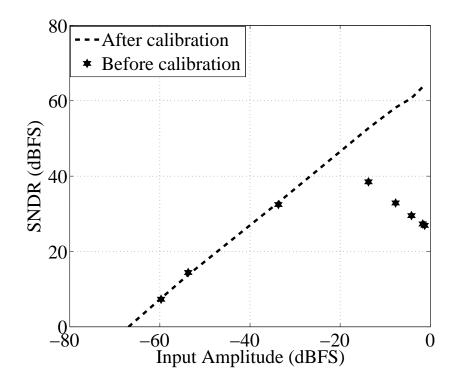

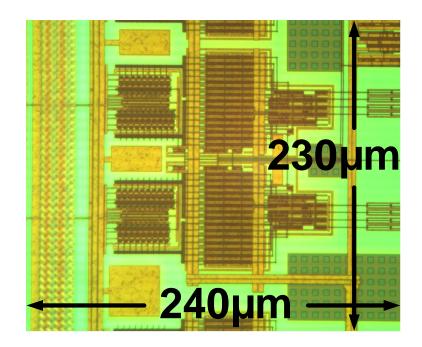

The thesis is primarily divided into two parts. The first part focuses on a technique to convert the time information into a digital word. A high resolution time-to-digital converter (TDC) architecture is proposed which combines the principles of noise-shaping integrating quantizer and charge-pump to build a thirdorder delta-sigma TDC using a dedicated feedback DAC. Fabricated in a  $0.13\mu$ m CMOS process, the prototype TDC achieves better than 71dB DR for a 2.8MHz signal bandwidth. The second part of the thesis proposes a blind digital calibration technique to remove non-linearity in any traditional ADC architectures. The proposed technique uses the concept of downsampling and orthogonality of sinusoidal waves to estimate the harmonic distortion in ADCs and can be used to calibrate multiple harmonics simultaneously. As a proof of concept, the algorithm is demonstrated on a first-order ring oscillator based delta-sigma ADC, whose performance is harmonic distortion limited. Built in  $0.13\mu$ m CMOS process, the algorithm improves the SNDR of the ADC by 39dB while improving SFDR by 45 dB. <sup>©</sup>Copyright by Manideep Gande June 5, 2013 All Rights Reserved Design Techniques for Time Based Data Converters

by

Manideep Gande

#### A DISSERTATION

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented June 5, 2013 Commencement June 2014  $\label{eq:constraint} \frac{\text{Doctor of Philosophy}}{\text{June 5, 2013}} \text{ dissertation of } \underline{\text{Manideep Gande}} \text{ presented on}$

APPROVED:

Major Professor, representing Electrical and Computer Engineering

Director of the School of Electrical Engineering and Computer Science

Dean of the Graduate School

I understand that my dissertation will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my dissertation to any reader upon request.

Manideep Gande, Author

#### ACKNOWLEDGMENTS

It all began on the 25th of December, 2007 when I first received an opportunity to do a PhD from Dr. Moon. Honestly, I wasn't sure of what to do back then, as I just received a job offer earlier that day. After taking numerous suggestions from everyone I knew, a month later I accepted Dr. Moon's offer. And since then I never looked back. Dr. Moon always was always available to guide me in right direction. He was also present to give the valuable feedback on both professional and personal fronts. His insight into circuit design is unique and quite amazing, and it is something which I hope to achieve in the future. I think my PhD would not have been as much fun had it not been for Dr. Moon.

I would like to thank my committee members Prof. Karti Mayaram, Prof. Gabor C. Temes, and Prof. Pavan Kumar Hanumolufor for serving on my technical committee for all the exams, taking time of their busy schedules. I would also like to thank my GCR Prof. Adam Schultz for serving on my program committee.

I would like to thank all Dr. Moon's group members: Taehwan Oh, Ho-young Lee, Jon Guerber, Hariprasath Venkatram, Benjamin Hershberg, Skyler Weaver, Tawfiq Musah, Nima Maghari, Omid Rajaee, Dave Gubbins, Naga Sasidhar, Yue Hu (Simon), Allen Waters, Peter Kurahashi and Sunwoo Kwon. I had a real great time interacting with you guys. I learnt a lot aspects of circuit design from you guys and I am really grateful for all your help. I would like to thank Hari in particular for all the discussions we had over the past 10 years.

I had the benefit of interacting with some amazing set of people during the course of my PhD. Sachin Rao Bandigadi, Mrunmay Talegaonkar, Amr Elshazly, Saurabh Saxena, Romesh Nandanwana, Ankur Guha Roy, Reddy Karthikeyan, Praveen Prabha, Rajesh Inti, Sameer, Tesjasvi Anand, Tao Wang, Brian Young, Wei Li, Sai Praneeth are some of the people who made my stay in Corvallis a memorable one. I wish all the very the best for all of you guys.

I was fortunate enough to have great roommates throughout my entire stay in Corvallis. Thanks Hari, Sachin, Sudarshan, Saurabh and Romesh for making my stay in Corvallis a memorable one. I also have some very fond memories of time spent in Brew Station with Sachin, Hari, Mrinmay and Amr.

I wish the young blood of Dr. Moon's group: Brandi Coker, Farshad Farahbakhshian, Jason Muhlestein, Jerry Leung and Spencer Leuenberger all the very best for their future research work.

I would like to thank my parents, my sisters and all my other family members for always being supportive of my work. It would have been very difficult without your support! Also, I would like to thank my wife, Deepthi, who is my current roommate :). Your support was crucial and helped me concentrate on finishing my work on time.

Finally, I do agree that PhD is was one BIG bumpy ride. But during the entire course of my PhD I learned a lot of things both professionally and personally which I would have missed out on otherwise. I am glad the way things turned out, and given a time machine to take me back to the 25th of December2007, I would sign the offer and sent it back on the 26th.

Thanks Dr. Moon for giving me the opportunity to work with you. It was my pleasure.

#### TABLE OF CONTENTS

Page

| 1 | INTI | RODUCTION                                                                                                                       | 1               |

|---|------|---------------------------------------------------------------------------------------------------------------------------------|-----------------|

|   | 1.1  | Introduction                                                                                                                    | 1               |

|   | 1.2  | Motivation                                                                                                                      | 2               |

|   | 1.3  | Thesis Organization                                                                                                             | 4               |

| 2 | BAC  | KGROUND ON TIME TO DIGITAL CONVERTERS                                                                                           | 5               |

|   | 2.1  | Introduction                                                                                                                    | 5               |

|   | 2.2  | Nyquist Rate TDCs                                                                                                               | 8               |

|   |      | <ul> <li>2.2.1 Gate delay TDC</li> <li>2.2.2 Vernier TDC</li> <li>2.2.3 Pipeline TDC</li> </ul>                                 | 8<br>10<br>13   |

|   | 2.3  | Oversampling TDC                                                                                                                | 14              |

|   |      | <ul><li>2.3.1 Gated Ring Oscillator based TDC</li><li>2.3.2 Switched Ring Oscillator based TDC</li><li>2.3.3 MASH TDC</li></ul> | 14<br>17<br>18  |

|   | 2.4  | Summary                                                                                                                         | 18              |

| 3 | CHA  | RGE PUMP BASED $\Delta\Sigma$ TDC                                                                                               | 20              |

|   | 3.1  | Noise-shaping Integrating Quantizer                                                                                             | 21              |

|   |      | 3.1.1 Noise-shaping Integrating Quantizer                                                                                       | 22              |

|   | 3.2  | A $2^{nd}$ Order Charge-pump Based $\Delta \Sigma$ TDC                                                                          | 27              |

|   |      | 3.2.1Charge-pump as a Phase Difference Integrator3.2.2Charge-pump based $\Delta\Sigma$ TDC                                      | 27<br>29        |

|   | 3.3  | A $3^{rd}$ Order Charge-pump Based $\Delta\Sigma$ TDC                                                                           | 34              |

|   |      | 3.3.1Signal Feed-forward Path3.3.2A $3^{rd}$ Order Charge-pump Based $\Delta\Sigma$ TDC                                         | $\frac{35}{37}$ |

# TABLE OF CONTENTS (Continued)

|   | 3.4 | Circuit Implementation                                                                                                                                                        | 40                         |

|---|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|   |     | <ul> <li>3.4.1 Charge-pump</li> <li>3.4.2 Transconductors</li> <li>3.4.3 Zero Crossing Detector</li> <li>3.4.4 Fast Clock</li> <li>3.4.5 Time to Digital Converter</li> </ul> | 40<br>41<br>41<br>43<br>44 |

|   | 3.5 | Non-idealities                                                                                                                                                                | 47                         |

|   |     | <ul><li>3.5.1 Zero Crossing Detector</li></ul>                                                                                                                                | 47<br>50<br>53             |

|   | 3.6 | Measured Results                                                                                                                                                              | 54                         |

|   |     | <ul> <li>3.6.1 Test Setup</li> <li>3.6.2 Measured Results</li> <li>3.6.3 Explanation for Observed Harmonic Distortion</li> </ul>                                              | 54<br>54<br>59             |

|   | 3.7 | Summary                                                                                                                                                                       | 62                         |

| 4 |     | KGROUND ON DIGITAL CALIBRATION ALGORITHMS FOR<br>LINEARITY CORRECTION IN ADCS                                                                                                 | 64                         |

|   | 4.1 | Introduction                                                                                                                                                                  | 64                         |

|   | 4.2 | DAC based Calibration Technique                                                                                                                                               | 67                         |

|   | 4.3 | Split ADC based Calibration Technique                                                                                                                                         | 69                         |

|   | 4.4 | Straight line based Calibration Technique                                                                                                                                     | 70                         |

|   | 4.5 | Multiple Pseudo-random Number Based Calibration Technique                                                                                                                     | 72                         |

|   | 4.6 | Blind Calibration Based Calibration Technique                                                                                                                                 | 73                         |

|   |     |                                                                                                                                                                               |                            |

# 5 BLIND CALIBRATION ALGORITHM FOR NONLINEARITY IN ADCS 74

# TABLE OF CONTENTS (Continued)

|    | 5.1  | Introduction                          | 74             |

|----|------|---------------------------------------|----------------|

|    | 5.2  | Proposed Algorithm in Foreground Mode | 75             |

|    |      | 5.2.2 Orthogonality                   | 76<br>78<br>79 |

|    | 5.3  | Background Calibration                | 81             |

|    | 5.4  | Calibration for Multiple Harmonics    | 84             |

|    | 5.5  | Final System Architecture 8           | 35             |

|    |      | 5.5.1 Example Nyquist Converter 8     | 87             |

|    | 5.6  | VCO Based $\Delta\Sigma$ ADC          | 92             |

|    | 5.7  | Circuit Implementation                | 96             |

|    |      | 5.7.2 Phase Quantizer                 | 96<br>98<br>99 |

|    | 5.8  | Measured Results                      | )0             |

|    | 5.9  | Summary 10                            | )2             |

| 6  | CON  | CLUSION 10                            | )5             |

| BI | BLIO | GRAPHY 10                             | )7             |

# Page

# LIST OF FIGURES

| Figu | <u>are</u>                                                                                                                                | Pag | ge |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|----|

| 1.1  | Role of data converters in everyday life                                                                                                  |     | 1  |

| 1.2  | Application of data converters.                                                                                                           | ••• | 2  |

| 1.3  | Trends in CMOS scaling                                                                                                                    |     | 3  |

| 2.1  | Concept of time to digital converter                                                                                                      | • • | 5  |

| 2.2  | Basic TDC operation                                                                                                                       | ••• | 6  |

| 2.3  | Gate delay based TDC.                                                                                                                     | ••• | 8  |

| 2.4  | Timing for gate delay based TDC                                                                                                           | ••  | 9  |

| 2.5  | Vernier TDC                                                                                                                               | • • | 11 |

| 2.6  | Timing diagram for vernier TDC                                                                                                            | • • | 12 |

| 2.7  | Pipeline TDC                                                                                                                              | • • | 13 |

| 2.8  | GRO based TDC                                                                                                                             | • • | 15 |

| 2.9  | Conceptual diagram of GRO based TDC                                                                                                       | • • | 16 |

| 2.10 | Phase leakage in GRO-TDC                                                                                                                  | • • | 17 |

| 2.11 | SRO based TDC.                                                                                                                            | • • | 17 |

| 2.12 | 1-1-1 MASH $\Delta\Sigma$ TDC                                                                                                             | • • | 19 |

| 3.1  | Oversampling ADC architecture extended to operate as a TDC.                                                                               |     | 20 |

| 3.2  | Noise-shaping integrating quantizer system                                                                                                |     | 22 |

| 3.3  | Sampling phase of NSIQ                                                                                                                    | • • | 23 |

| 3.4  | Discharge phase of noise-shaping integrating quantizer showing<br>the quantization error being stored at the end of quantization<br>phase | 1   | 25 |

| 3.5  | Timing diagram showing the operation of NSIQ over two cycles of operation                                                                 |     | 26 |

| 3.6  | Equivalent model of noise-shaping integrating quantizer                                                                                   |     | 27 |

# LIST OF FIGURES (Continued)

| Figu | ure <u>H</u>                                                                                        | Page  |

|------|-----------------------------------------------------------------------------------------------------|-------|

| 3.7  | Charge-pump as a phase subtractor and integrator                                                    | 28    |

| 3.8  | $2^{nd}$ order $\Delta\Sigma$ TDC                                                                   | 29    |

| 3.9  | $2^{nd}$ order $\Delta\Sigma$ TDC built using charge-pump and NSIQ                                  | 30    |

| 3.10 | Input sampling phase of $\Delta\Sigma$ TDC                                                          | 31    |

| 3.11 | Discharge phase of $\Delta\Sigma$ TDC                                                               | 33    |

| 3.12 | Extending the $2^{nd}$ order $\Delta \Sigma$ TDC to operate as a $3^{rd}$ order $\Delta \Sigma$ TDC | C. 35 |

| 3.13 | Transconductor and feed-forward path using transconductors                                          | 35    |

| 3.14 | Voltage domain low distortion architecture                                                          | 36    |

| 3.15 | Time domain low distortion architecture                                                             | 36    |

| 3.16 | Implementation of feed-forward path in TDC.                                                         | 37    |

| 3.17 | A $3^{rd}$ order charge-pump based $\Delta \Sigma$ TDC                                              | 38    |

| 3.18 | Current switched charge-pump                                                                        | 41    |

| 3.19 | Transconductance                                                                                    | 42    |

| 3.20 | Zero crossing detector                                                                              | 42    |

| 3.21 | Delay line                                                                                          | 43    |

| 3.22 | Basic time-to-digital converter                                                                     | 44    |

| 3.23 | Signal dependent delay of DFF                                                                       | 45    |

| 3.24 | (a)Time-to-digital converter. (b) Timing diagram                                                    | 46    |

| 3.25 | Effect of comparator noise on TDC decisions                                                         | 48    |

| 3.26 | Effect of comparator delay on TDC                                                                   | 49    |

| 3.27 | Effect of mismatch in discharge time steps                                                          | 51    |

| 3.28 | Effect of mismatch in DAC feedback path                                                             | 52    |

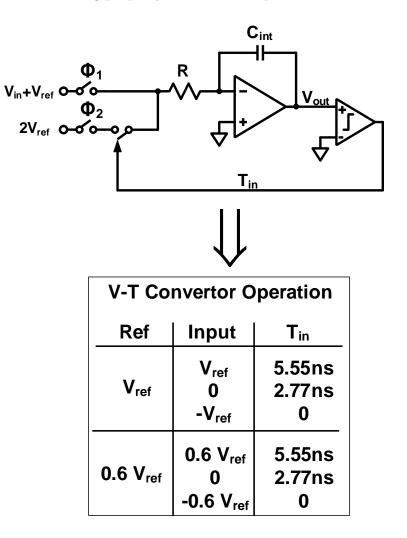

| 3.29 | Dual slope ADC reconfigured to give time input to the TDC                                           | 55    |

# LIST OF FIGURES (Continued)

| Figu | ure                                                                                          | Page |

|------|----------------------------------------------------------------------------------------------|------|

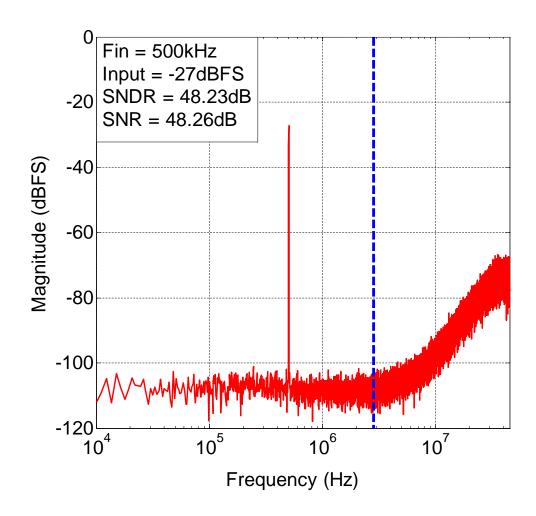

| 3.30 | Measured spectrum for large input                                                            | 56   |

| 3.31 | Measured spectrum for small input.                                                           | 57   |

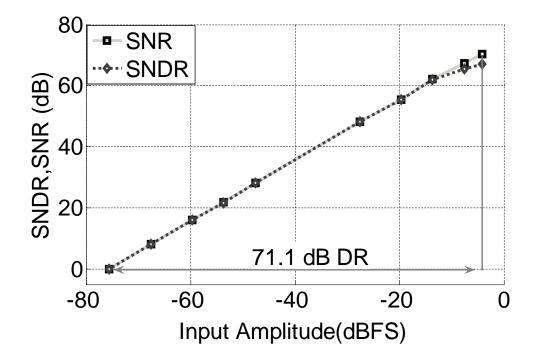

| 3.32 | SNDR vs. input amplitude.                                                                    | 58   |

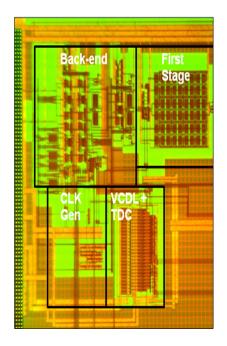

| 3.33 | Die Photo                                                                                    | 58   |

| 3.34 | Effect of scaling reference for a dual-slope ADC                                             | 59   |

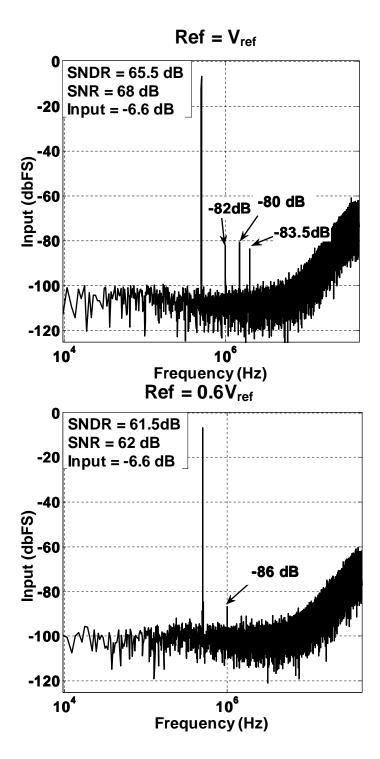

| 3.35 | Effect on output spectrum by scaling the reference and input in dual-slope ADC               |      |

| 4.1  | Need for calibration.                                                                        | 65   |

| 4.2  | DAC based calibration technique.                                                             | 67   |

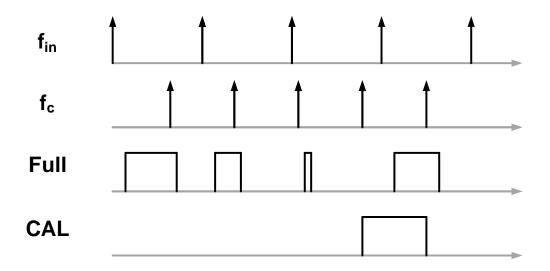

| 4.3  | Timing diagram for DAC based calibration technique                                           | 68   |

| 4.4  | Split ADC based calibration technique                                                        | 69   |

| 4.5  | Straight line fit based calibration technique                                                | 70   |

| 4.6  | Varying $V_{DC}$ over the entire range of ADC to estimate the mean value of the error        |      |

| 4.7  | Pseudo random number based calibration technique                                             | 72   |

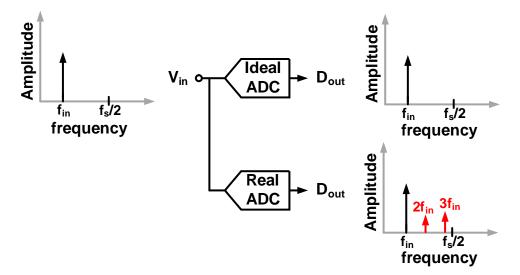

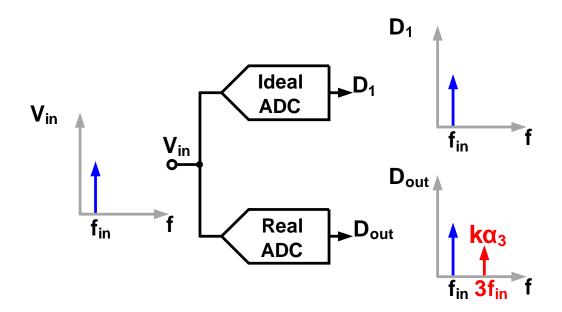

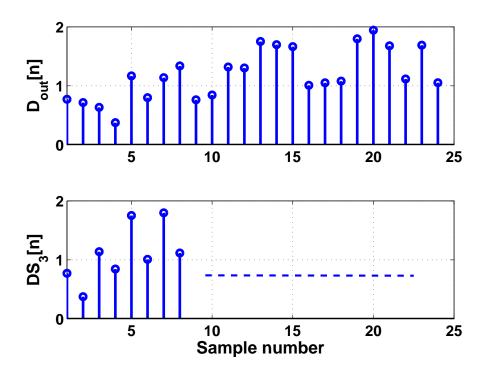

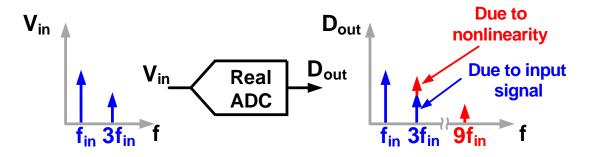

| 5.1  | Single tone frequency response of ideal and non-ideal ADC                                    | 75   |

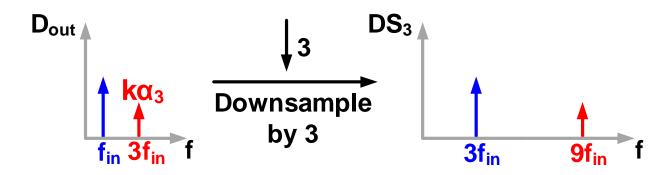

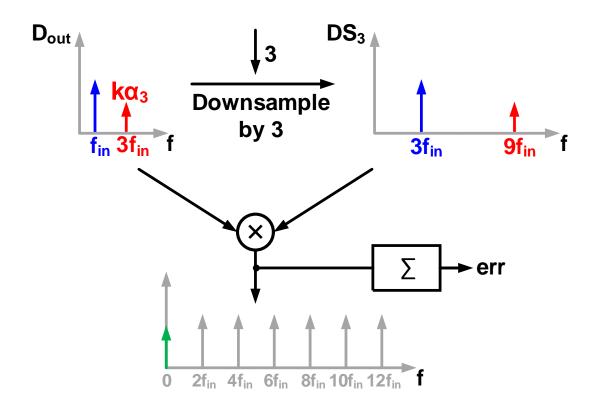

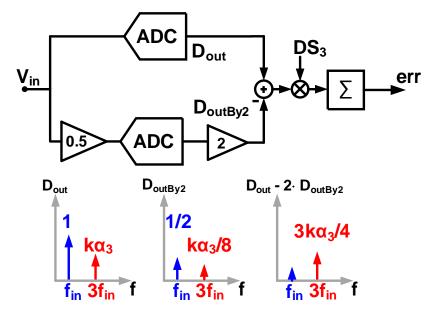

| 5.2  | Relationship between $DS_3[n]$ and $D_{out}[n]$ in time domain                               | 77   |

| 5.3  | Effect of downsampling in frequency domain                                                   | 78   |

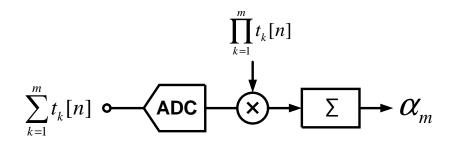

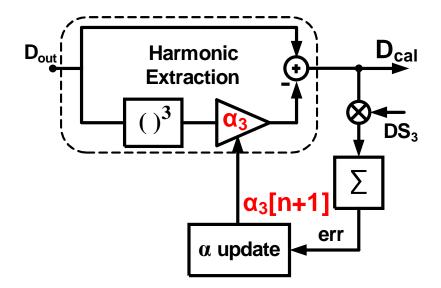

| 5.4  | LMS engine                                                                                   | 80   |

| 5.5  | Update engine used to perform the LMS operation to estimate<br>the nonlinearity coefficient. |      |

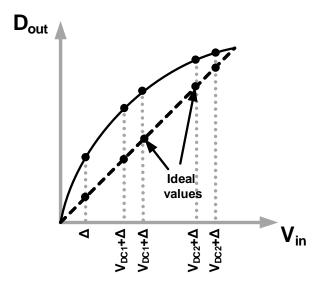

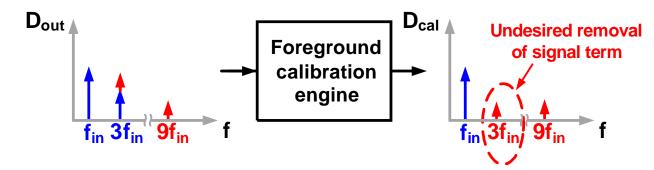

| 5.6  | Limitations of foreground calibration technique                                              | 81   |

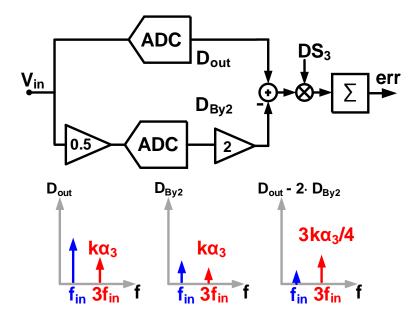

| 5.7  | Illustration of limitation of foreground calibration technique                               | 82   |

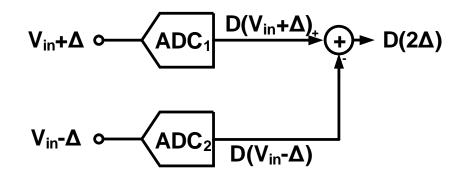

| 5.8  | Removal of signal term from the input signal by using two ADCs with scaled inputs            |      |

# LIST OF FIGURES (Continued)

# Figure

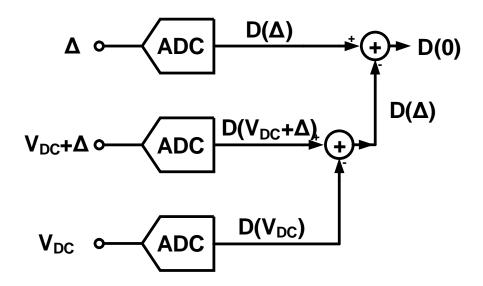

| 5.9  | System update equations in background calibration mode                                                                   | 84   |

|------|--------------------------------------------------------------------------------------------------------------------------|------|

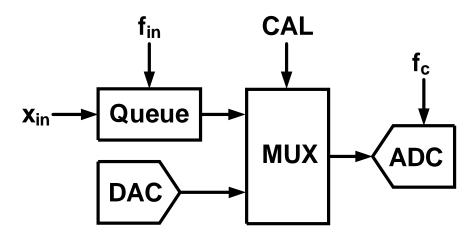

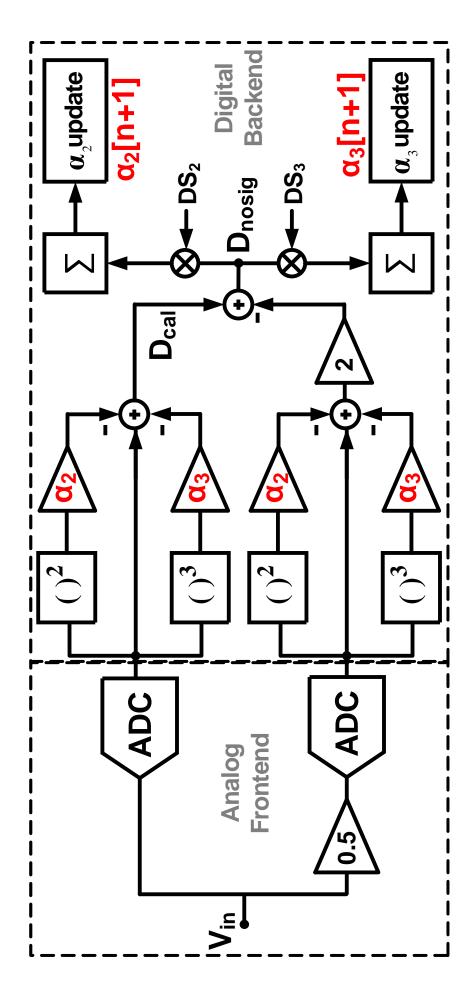

| 5.10 | Background calibration architecture implemented                                                                          | 86   |

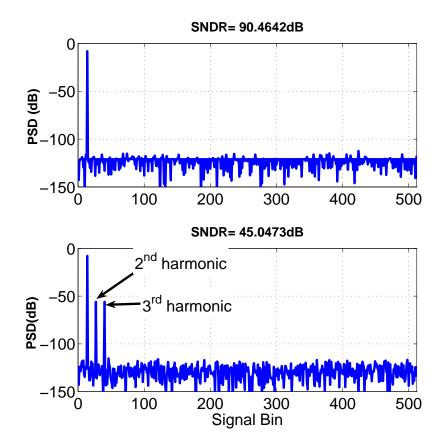

| 5.11 | Uncalibrated spectrum of ADC suffering from $2^{nd}$ and $3^{rd}$ order nonlinearity.                                    | 87   |

| 5.12 | Spectrum of ADC after calibrating for $2^{nd}$ and $3^{rd}$ order nonlinearity.                                          | . 88 |

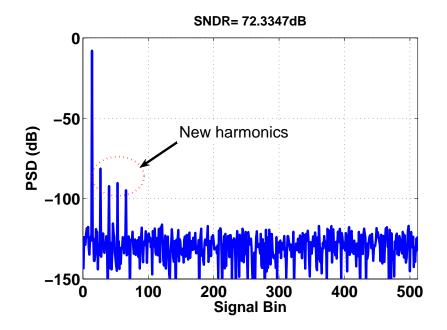

| 5.13 | Spectrum of ADC after calibrating for $2^{nd}$ , $3^{rd}$ , $4^{th}$ and $5^{th}$ order nonlinearity.                    | 89   |

| 5.14 | Settling of $2^{nd}$ , $3^{rd}$ , $4^{th}$ and $5^{th}$ order coefficients                                               | 90   |

| 5.15 | Input and un-calibrated output spectrum for multi-tone input,<br>with second tone being a harmonic bin of the first tone | 91   |

| 5.16 | Calibrated spectrum for multi-tone input                                                                                 | 92   |

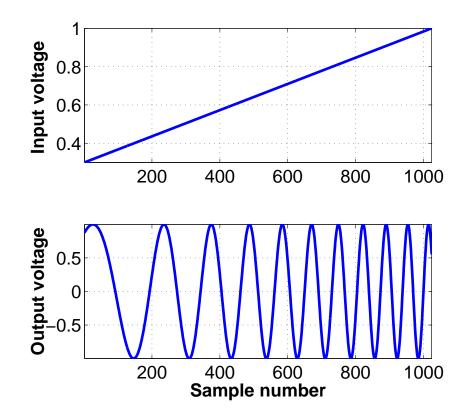

| 5.17 | Oscillator whose output frequency is a function of input voltage                                                         | 93   |

| 5.18 | Model diagram of VCO.                                                                                                    | 95   |

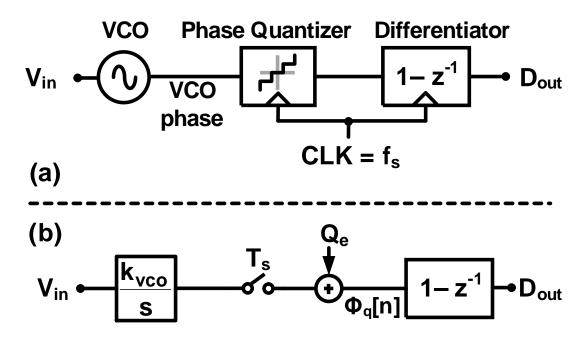

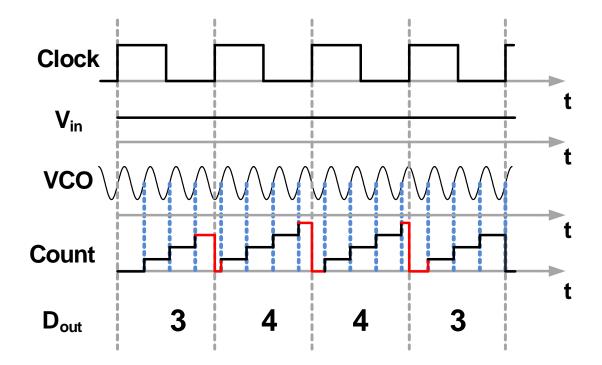

| 5.19 | Illustration of first order noise shaping in VCO.                                                                        | 96   |

| 5.20 | Voltage controlled ring oscillator                                                                                       | 97   |

| 5.21 | Sense amplifier flip-flop                                                                                                | 98   |

| 5.22 | Ex-or phase differentiator.                                                                                              | 99   |

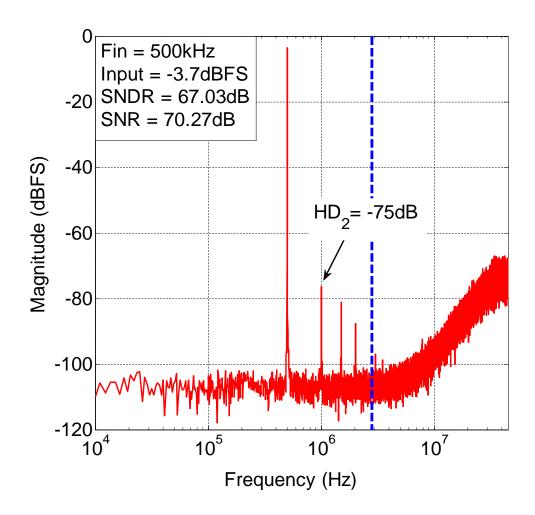

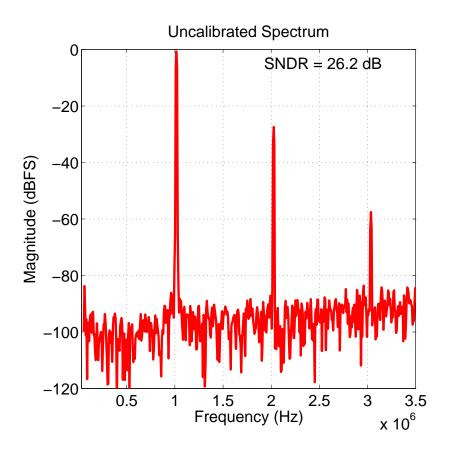

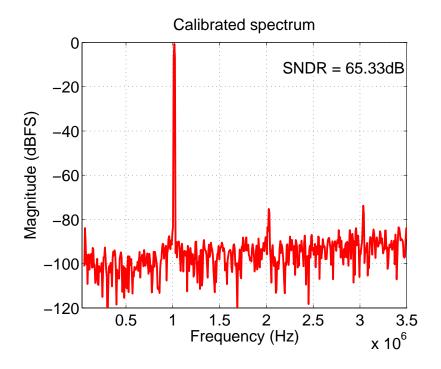

| 5.23 | Measured spectrum before calibration.                                                                                    | 101  |

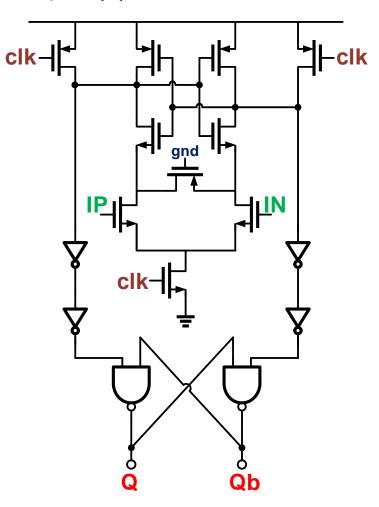

| 5.24 | Measured spectrum after calibration.                                                                                     | 102  |

| 5.25 | SNDR vs. input amplitude.                                                                                                | 104  |

| 5.26 | Chip micrograph                                                                                                          | 104  |

#### LIST OF TABLES

| Tab | ble                                                                    | Page  |  |

|-----|------------------------------------------------------------------------|-------|--|

| 3.1 | Summary of performance and comparison with existing architec-<br>tures |       |  |

| 5.1 | Summary of performance                                                 | . 103 |  |

# DESIGN TECHNIQUES FOR TIME BASED DATA CONVERTERS

### CHAPTER 1. INTRODUCTION

#### 1.1 Introduction

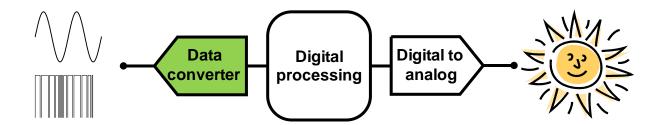

Figure 1.1: Role of data converters in everyday life.

In this digital era, communication, health, instrumentation and space electronics enhance our accessibility and information exchange. However, this information exchange happens through the interface between analog world and digital world. Data Converters are imperative for the exchange of information and help in interfacing our communication with the digital world. Analog-to-digital converters and Time-to-digital converters are the two major data converter architectures which steer forward this digital evolution.

Portable, efficient and high performance systems are the nature of today's digital evolution. To this end, some of the latest technology trends are shown in

Fig. 1.2. WiGig, 400 Gbps optical links, highly sensitive physics experiments have created an increasing appetite for data converters that are capable of operating on a wider bandwidth range, while being able to provide high resolution and high linearity, while consuming low power.

Figure 1.2: Application of data converters.

### 1.2 Motivation

If it can be done in CMOS, it will be done in CMOS.

-Arun Natarajan

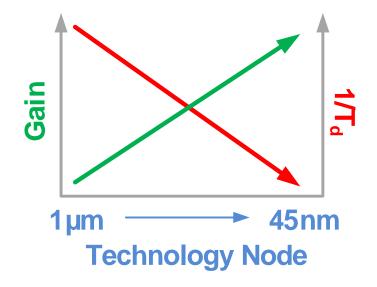

The CMOS backend process is the most commonly used digital electronics platform. The reason being near zero incremental device cost/ easy digital-RF integration and the very fact that millions of transistors are available, thereby making digital calibration a viable option. Also, scaling is an integral part of CMOS technology as it helps pack in more transistors, while reducing digital power consumption. However, scaling in deep sub-micron nodes exhibit the general trend of reduced intrinsic gain and smaller gate delays. This trend is shown in Fig. 1.3. Although the trend is a sign of trouble for conventional voltage based signal processing, it works in favor of data converters that use time based information or are more digital in nature.

Figure 1.3: Trends in CMOS scaling.

Deep sub-micron CMOS technology provides the user with benefits of reduced gate delay and faster processes, at the cost of reduced voltage headroom and reduced intrinsic gain. Therefore, it is imperative that one looks into alternative design methodologies which take the advantages of the modern processes and make data converters which use time domain signal processing or build data converters which are more digital in nature. This thesis presents two new data converter architectures which utilize the advantages of reduced gate delay available with modern CMOS process. The proposed architectures are also more digital in nature, thereby taking advantage of scaling in CMOS processes.

#### 1.3 Thesis Organization

Chapter 2 introduces some of the basics of Time-to-Digital converters(TDCs), while also giving a peek at attempts made by in the past into improving this field. The merits and demerits of some of the existing architectures are discussed in this chapter.

In Chapter 3, a novel TDC architecture is proposed by combining the properties of noise-shaping quantizer and charge-pump. This proposed architecture makes use of a dedicated feedback path in a TDC, thereby enabling the possibility of building higher order  $\Delta\Sigma$  TDCs. The design aspects of the  $\Delta\Sigma$  TDC are discussed along with a few important design considerations. This chapter concludes by presenting the measured results of the proposed  $\Delta\Sigma$  TDC which is built in 0.13  $\mu$ m CMOS technology.

In Chapter 4, the effects of nonlinearity on an ADC are studied. One of the many possible ways of combating nonlinearity in ADCs is to use "Digital Calibration". In this chapter, some of the existing nonlinearity calibration algorithms for ADCs are studied, and their shortcomings are discussed.

In Chapter 5, a novel digital calibration algorithm to reduce nonlinearity in ADCs is proposed. The calibration algorithm makes use of downsampling and orthogonality of sinusoid waves to calibrate for nonlinearity in ADCs. This chapter also proves the effectiveness of the proposed algorithm by showing the performance improvement of a VCO based  $\Delta\Sigma$  ADC, which are known to be notoriously non-linear. The VCO based  $\Delta\Sigma$  ADC is also built in 0.13  $\mu$ m CMOS technology.

Chapter 6 summarizes the work presented in this thesis.

# CHAPTER 2. BACKGROUND ON TIME TO DIGITAL CONVERTERS

#### 2.1 Introduction

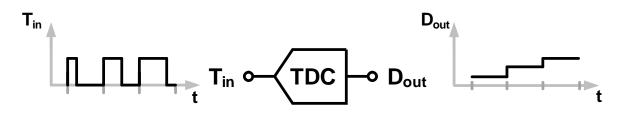

Historically, the basic motivation to synchronize our activities has been one of the main motivations to measure time. Today, measurements of mean lifetime of nuclear particles, particle identification, time-of-flight, timing jitter calculations, instrumentation and communication circuitry etc... require time measurement that are much more precise [1, 2, 3, 4, 5]. Time-to-digital converters (TDCs), as the name suggests, are used to quantize the time interval between two events. Figure 2.1 shows the basic operation of a TDC [6].

Figure 2.1: Concept of time to digital converter

The input to a TDC is the time interval between two events, and this time interval is quantized and the digital representation of it is given as the output. As shown in Fig. 2.1, the width of the pulse, which is the time input  $(T_{in})$ , varies with time; thereby its digital output  $(D_{out})$  also varies proportionally with time. Although Fig. 2.1 represents that the time pulse is synchronized with the sampling clock edge, this need not be the case in general. An important characteristic of TDC is the minimum time interval which can be measured. This is defined as the resolution of the TDC. Therefore as the resolution of TDC improves, the smaller the time pulse that can be measured by the TDC. Figure 2.2 illustrates some of the terms discussed thus far.

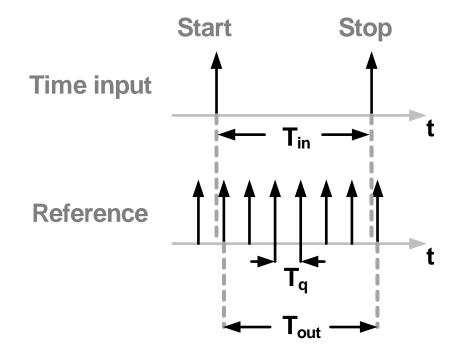

Figure 2.2: Basic TDC operation

The time interval between the two events start  $(T_{in})$  and stop  $(T_{stop})$ , which is an analog quantity, is a quantity that needs to measured. One possible way to do this is to divide the time scale into finer references and measure the number of finer reference pulses between the two events. As shown in Fig. 2.2,  $T_q$  represents the finer reference pulse width, thereby representing the minimum time width that can be determined by the system, i.e. the resolution of the TDC. The output  $T_{out}$ is a integer multiple of  $T_q$ , i.e.  $T_{out}[n] = k \times T_q$ , where k is a digital word, an integer, equalling the number of reference pulse widths in the time event. Therefore, we can express the input as

$$T_{in}[n] = T_{out}[n] + Q(e)$$

(2.1)

where Q(e) is equal to the quantization error. Therefore the digital representation of  $T_{in}$  can be written as

$$T_{out} = k \times T_q = T_{in} - Q(e) \tag{2.2}$$

The digital representation of  $T_{in}$ , which is k, is obtained from eq. 2.3

$$k = \frac{T_{in} - Q(e)}{T_q} \tag{2.3}$$

In the above example, the TDC resolution is limited by  $T_q$ , i.e. a time interval smaller than  $T_q$  cannot be measured by the above TDC. With decreasing gate delays in modern day CMOS technology, the resolution achievable by the above kind of TDC improves (i.e.  $T_q$  decreases), but this technique has limited uses as it depends on the minimum possible reference width that be accurately obtained.

Many modern applications like energy efficient analog-to-digital converters, wherein the analog voltage is converted to time information that is processed by a TDC to give a digital word [7], and jitter measurement applications [4] where a TDC is used to measure the phase difference between the input reference clock and VCO clock, require sub-pico second TDC resolutions. Therefore, over the years, a great deal of effort has been made in to improve the time resolutions that can be measured.

The remainder of the chapter discusses a few design techniques that help improve the resolution achievable by TDCs.

# 2.2 Nyquist Rate TDCs

#### 2.2.1 Gate delay TDC

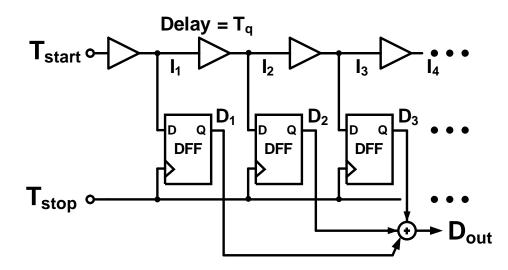

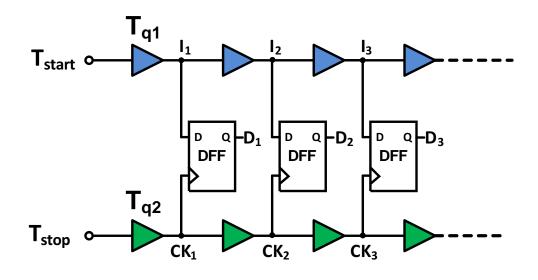

One of the most basic TDC architectures comprises of a chain of delay elements as shown in Fig. 2.3 [8]. This TDC works by counting the number of sequential delays that occur between two rising signal edges (start and stop). One attractive feature of this TDC architecture is that it can be constructed entirely from standard digital gates, thereby enabling the possibility of synthesizing the TDC.

Figure 2.3: Gate delay based TDC.

To explain its operation, the rising edge of the input,  $T_{start}$ , which represents the start event, is successively delayed by a series of delay elements, each with delay  $T_q$ . Therefore, as shown in the timing diagram Fig. 2.4, the output of the of  $x^{th}$  delay cell,  $I_x$ , goes high  $T_q$  time after  $I_{x-1}$  goes high, where  $T_q$  is the time delay of the delay element. Therefore in a gate-delay based TDC, the minimum time step that can be measured is equal to  $T_q$ ,

$T_{lsb} = T_{q1} - T_{q2} \tag{2.4}$

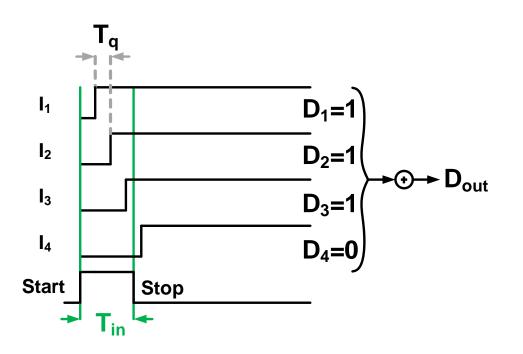

Figure 2.4: Timing for gate delay based TDC.

The delayed outputs of the delay elements act as inputs to D-flip flops(DFFs), which are clocked synchronously with the rising edge of the stop signal,  $T_{stop}$ , representing the second event. The thermometer code generated at the register output corresponds to the number of delay elements the input has transitioned during the time interval  $T_{stop} - T_{start}$ . The TDC digital output  $D_{out}[n]$  is then simply equal to the thermometer code i.e.

$$D_{out}[n] = \sum_{i=1}^{N} D_i \tag{2.5}$$

where N is the total number of delay elements in the TDC. The above delay-chain architecture is very digital in nature and offers moderate performance, with the resolution of TDC  $(T_q)$  being limited by the minimum delay achievable. With decreasing gate delays, the above architecture is shown to achieve resolution in the order of tens of pico-seconds.

Another important limitation of the above architecture is the high cost for increase in dynamic range. Increasing the dynamic range of the delay-chain TDC requires a linear increase in the number of delay elements, which inadvertently decreases the sampling rate of the TDC. Although technology scaling will improve the intrinsic delay, the mismatch of delay elements is expected to get worse. This inherently means larger device sizes and larger area and larger power. One alternative solution to the above problem is to use the delay-chain in a wrapped around fashion [9].

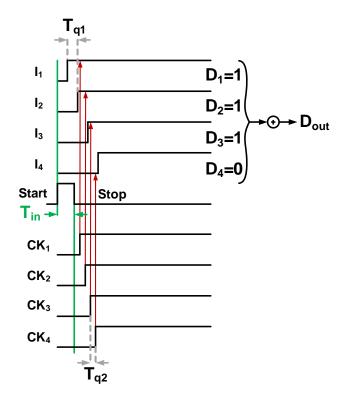

#### 2.2.2 Vernier TDC

The Vernier delay technique is one of the very basic time digitization architectures and has been widely used [10, 11, 12, 13]. As shown in Figure 2.5, the vernier TDC works by effectively stretching the input time interval  $T_{in}$  by delaying both the start and stop signals with two different delay-chains, whose delay values are nominally different  $(T_{q1} \text{ and } T_{q2})$ .

The start signal is made to pass through a delay chain of delay  $T_{q1}$ , the outputs of which are sent to a DFF. The clocks of these DFF's are themselves obtained from a delay chain, whose input is the stop signal. Therefore, the resolution in this case is equal to the relative rate of transitions. As a result, the effective resolution of the Vernier TDC is found to be the difference of the two delays, or more specifically,

$$T_{lsb} = T_{q1} - T_{q2} \tag{2.6}$$

Figure 2.5: Vernier TDC.

Figure 2.6 shows the timing diagram for the vernier TDC. As seen, the vernier technique appears to be able to substantially increase the TDC resolution (as it is the difference between two delays, as opposed to absolute delay like in the gate-delay TDC). However, there are a number of issues that practically limit the resolution. Mismatch between the delay chains provides a bigger problem in a vernier TDC, as the matching now has to be done over two delay lines as opposed to one. Also increasing the dynamic range of a vernier TDC is a bigger problem than a gate-delay based TDC. This can be seen from the following example.

Consider a TDC which can measure a time input of pulse width  $T_{max}$ . In a gate-delay based TDC, the resolution with  $T_{lsb} = T_{delay}$ , the length of the delay chain is given by

$$(\text{Delay chain length})_{gate-delay} = \frac{T_{max}}{T_{delay}}$$

(2.7)

For a vernier TDC with  $T_{lsb} = T_{delay1} - T_{delay2}$ , the number of delay elements

Figure 2.6: Timing diagram for vernier TDC.

required is

$$(\text{Delay chain length})_{vernier} = \frac{T_{max}}{T_{delay1} - T_{delay2}}$$

(2.8)

therefore, the length of the delay chain increases with improving resolution of the TDC. Another artifact of the above is the reduction in frequency of operation of the vernier TDC. To mitigate some of these problems, alternative approaches using a ring-based architecture have been proposed [11].

Thus far gate-delay based TDCs and vernier TDCs that are single-step TDC architectures have been described. In the next subsection, multi-step TDC architecture is studied.

#### 2.2.3 Pipeline TDC

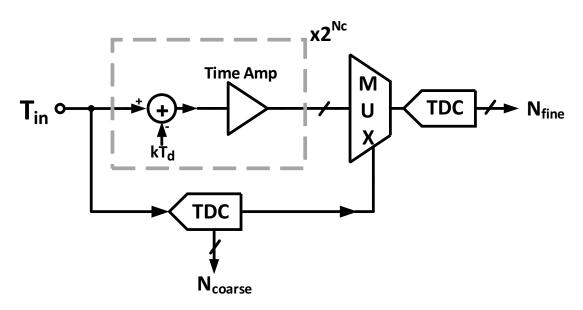

Gate-delay based TDCs and vernier TDCs incur a huge penalty when trying to increase the dynamic range of the TDC. An alternative architecture involves using a multi-stage architecture, where the first stage coarsely resolves the time input. The residue is found out using a time subtractor, which is then amplified and sent to the next stage, which repeats the operation, analogous to a pipeline ADC. Figure 2.7 shows a pipeline TDC architecture [14].

Figure 2.7: Pipeline TDC.

The time input  $(T_{in})$  is sent to a coarse TDC which gives the coarse bits  $N_c$ . The coarse value of the time output is now subtracted from the time input and the residue is amplified before being passed onto the next stage. However, unlike voltage, time cannot be stored unless it is converted to other storable quantities such as voltage or current. Therefore every possible time residue is created and amplified using a separate time amplifier. The coarse bits act as a select signal for a MUX, and the appropriate amplified time residue is passed to the next stage(fine TDC).

The final resolution of the TDC is equal to  $T_{fs}/2^N$ , where N is the total number of bits resolved in the TDC. The performance of this architecture is limited by the time-amplifier, as it is difficult to build high resolution time amplifiers. Another drawback of this architecture is that the number of time amplifiers required increases exponentially with the number of coarse bits resolved. This therefore increases the power consumption, while also increasing the errors due to mismatch.

#### 2.3 Oversampling TDC

For each of the Nyquist TDC architectures described so far, we have seen that significant effort is required to reduce the TDC resolution below that of a gatedelay, and in each case the cost for doing so is increased complexity. Calibration does generally improve resolution performance in the presence of mismatch, but it comes at an increased cost of power. Therefore, an alternative set of architectures that use the properties of oversampling have been developed to achieve a sub-ps resolution TDCs.

#### 2.3.1 Gated Ring Oscillator based TDC

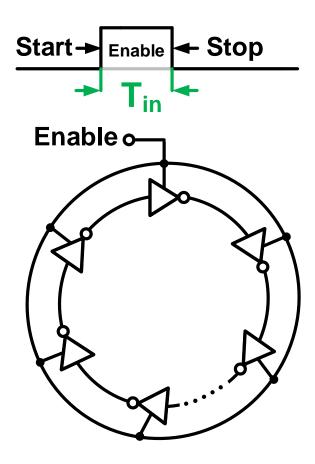

A gated ring oscillator (GRO) based TDC is similar to that of a ring-based gate-delay TDC, except that in GRO TDC the oscillator ring is switched in accordance with the time input [15, 16].

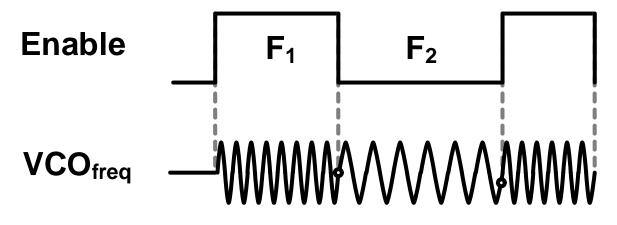

Figure 2.8 shows a GRO-TDC, in which the Enable pulse switches the ring oscillator ON/OFF, where the Enable pulse represents the time input. In other

Figure 2.8: GRO based TDC.

words, the amount of time for which the ring oscillator oscillates is equal to the time input  $(T_{in})$ . Therefore the output of the GRO TDC is the change in the phase of the ring oscillator, i.e.

$$D_{out} = \phi[n+1] - \phi[n] \tag{2.9}$$

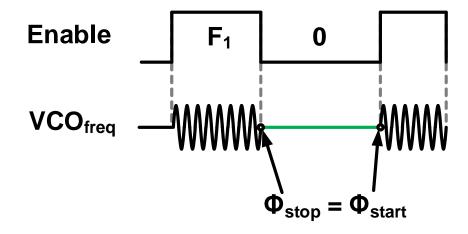

where  $\phi[n]$  is the phase of ring oscillator. Since the GRO-TDC is never reset, it preserves the phase at which it stops oscillating for the next cycle as shown in Fig. 2.9. As shown in the figure, the ring-oscillator oscillates at frequency  $F_1$  when Enable is high, and is stagnant when Enable is low. Therefore, ideally the starting phase of the next clock phase is exactly equal to stopping phase of the previous cycle.

Figure 2.9: Conceptual diagram of GRO based TDC.

By noting that  $\phi[n] = \int T_{in} + Q(e)$ , and updating eq. 2.9, we get the digital output of the GRO TDC as

$$D_{out} = T_{in} + (1 - z^{-1})Q(e)$$

(2.10)

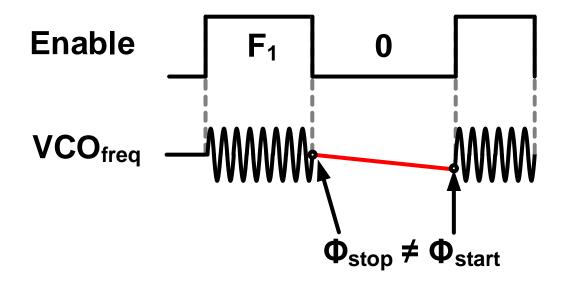

Therefore, the output of the GRO-TDC is input + shaped quantization noise, hence giving us first order noise-shaping. However, this approach is plagued with phase leakage problems as shown in Fig. 2.10.

Ideally, during the off-state of the ring oscillator the phase is preserved. However, in practical situations the phase is not preserved and leakage is observed thereby making it a leaky first order  $\Delta\Sigma$  TDC. This problem is addressed in a switched ring oscillator (SRO) TDC, as discussed in the next subsection.

Figure 2.10: Phase leakage in GRO-TDC.

#### 2.3.2 Switched Ring Oscillator based TDC

A switched ring oscillator (SRO) TDC is identical to a GRO-TDC in many aspects, with the main difference being that instead of turning off the VCO during the off state, it is made to oscillate at a lower frequency [17]. Figure 2.11 shows the conceptual diagram of a SRO-TDC.

Figure 2.11: SRO based TDC.

The advantage of continuing the oscillation is that the phase leakage problems are reduced. The digital output of the SRO-TDC is also first order noise-shaped [17, 18].

Thus far, only first order noise shaped TDC's are discussed. The next subsection looks at a higher order  $\Delta\Sigma$  TDC.

#### 2.3.3 MASH TDC

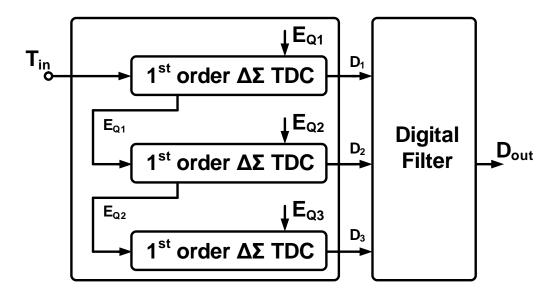

In ADCs, multi-stage noise shaping (MASH) architecture is one in which the quantization error from one  $\Delta\Sigma$  loop is extracted and sent for processing into another loop, typically another  $\Delta\Sigma$  loop. The digital outputs of both the loops are later combined to give a higher order noise shaping (sum of the orders of the two individual loops) [19]. The advantages of the MASH  $\Delta\Sigma$  modulator is that higher order noise shaping is achieved with the stability enjoyed by that of a lower order  $\Delta\Sigma$  architecture. The concept of MASH ADC can be readily extended to a TDC as implemented by [20] and as shown in Fig. 2.12.

In this TDC architecture, a  $3^{rd}$  order  $\Delta \Sigma$  TDC is built using 1-1-1 MASH architecture. The performance of the TDC is, however, limited by noise leakage.

#### 2.4 Summary

One common trait of the  $\Delta\Sigma$  TDC architectures is that they lack a dedicated feedback DAC. One reason for the lack of a dedicated feedback DAC is that, unlike voltage, time cannot be stored unless it is converted to other measurable quantities such as voltage or current (which itself adds noise and other nonlinearities in the

Figure 2.12: 1-1-1 MASH  $\Delta\Sigma$  TDC

process of conversion). In the next chapter, we propose a  $3^{rd}$  order  $\Delta \Sigma$  TDC which makes use of dedicated feedback DAC and show the measured chip results [21].

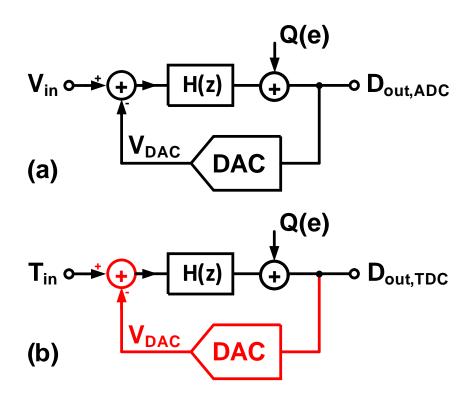

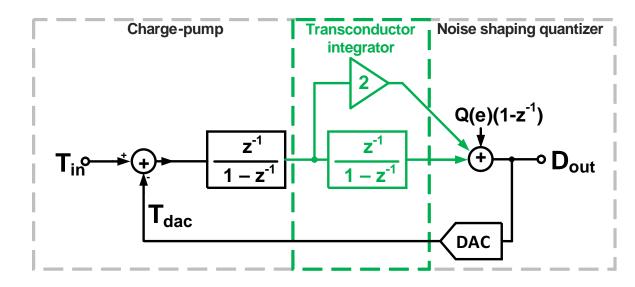

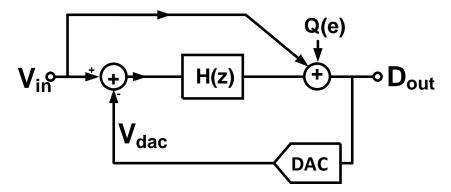

Time to digital converters with sub-ps resolution have found various applications such as high resolution ADC's, phase jitter measurements etc. Oversampling TDCs have emerged as an attractive option and have achieved sub-ps resolution [15, 20, 22]. However, the range of architectures used for oversampling converters are limited since it is difficult to subtract input time from a voltage quantity. Figure 3.1 highlights some of these problems.

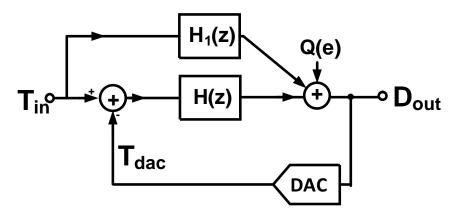

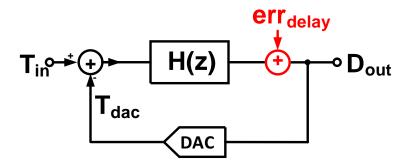

Figure 3.1: Oversampling ADC architecture extended to operate as a TDC.

Figure 3.1 (a) shows a typical oversampling ADC, where H(z) is the loop filter, and Q(e) is the quantization error, and  $D_{out,ADC}$  is the digital output of the ADC [19]. The DAC converts the digital output to an analog voltage  $V_{DAC}$ .  $V_{DAC}$  is subtracted from the input voltage  $V_{in}$ , and the error signal is processed by the loop.

In a oversampling TDC, the analog voltage is replaced by  $T_{in}$  as shown in Fig. 3.1 (b). Traditionally, it is difficult to subtract an analog voltage from time input thereby seriously limiting the range of architectures available for oversampling TDCs. Also, with current technology, it is still impossible to directly preserve the quantization error. Instead, the time information has to be converted into another intermediate physical quantity such as voltage or charge. This resulted in developing architectures that do not use a dedicated feedback path like GRO-TDC, SRO-TDC, 1-1-1 MASH [15, 17, 20].

In this half of the project, a novel TDC architecture is proposed that overcomes the problem of subtraction by using a modified dual-slope ADC (noise shaping integrating quantizer) for DAC and a charge-pump as a phase detector, or in other words as a subtractor. The following section starts by discussing the noise shaping integrating quantizer.

# 3.1 Noise-shaping Integrating Quantizer

A noise shaping integrating quantizer [23, 24] works on a principle similar to that of a dual-slope ADC [25], which in itself can be considered equivalent to a first-order incremental ADC [26]. It acts as quantizer in the  $\Delta\Sigma$  loop, while also giving a extra order of noise shaping and above all providing the feedback DAC information in time domain. The operation is discussed in detail in the remainder of this section.

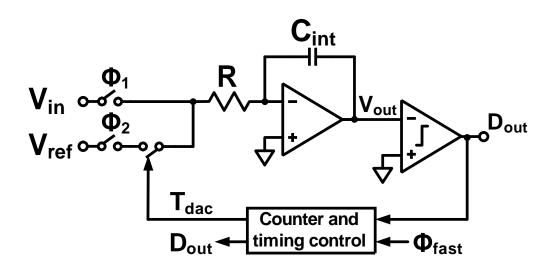

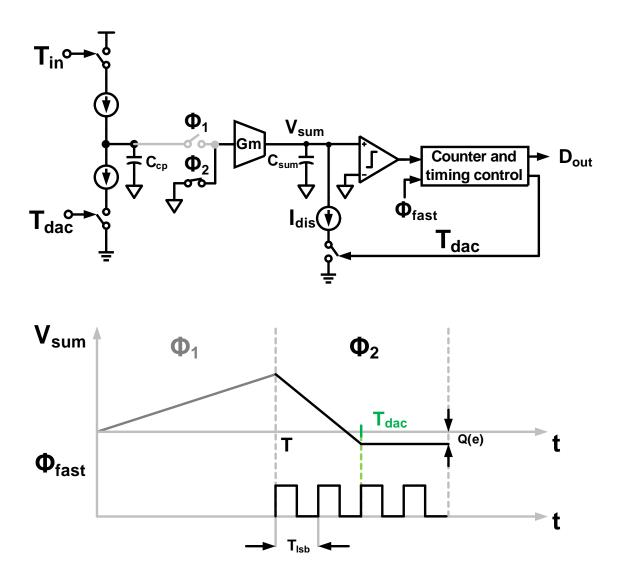

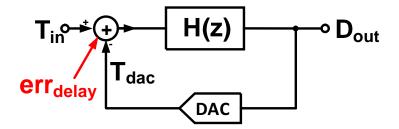

## 3.1.1 Noise-shaping Integrating Quantizer

The operation of a noise-shaping integrating quantizer (NSIQ) is similar to that of a conventional dual-slope ADC with two key differences: the integrating capacitor is never reset, and the discharging current must disconnect on the next fast-clock edge after the comparator has detected a zero crossing [23]. Figure 3.2 shows the system of NSIQ. The key difference when compared to a dual-slope ADC is the timing control in the feedback path. The operation of NSIQ can be broadly classified into two categories (1) Sampling phase and (2) Discharge phase.

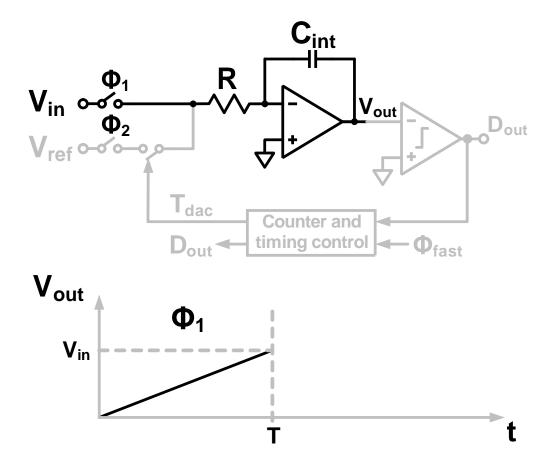

Figure 3.2: Noise-shaping integrating quantizer system.

#### **Input Sampling Phase**

Figure 3.3 shows the input sampling phase of the noise-shaping single slope quantizer. The input sampling phase of NSIQ differs from the input sampling phase of a dual-slope ADC in that the integrating capacitor is not reset before the beginning of the sampling cycle ( $\phi_1$ ). During this phase, the input is integrated onto the capacitor ' $C_{int}$ ' for a fixed duration of time through a resistor of value

Figure 3.3: Sampling phase of NSIQ.

'R'. Assuming that the time period of integration is T, the voltage at the end of the sampling cycle  $\phi_1$  is given by

$$V_{out,\phi_1} = \int_0^T \frac{V_{in}}{RC} dt + c \tag{3.1}$$

Note that c is a constant of integration, and is dependent on the initial voltage stored on the capacitor. For a constant input, the above equation is simplified and is given as

$$V_{out} = \frac{V_{in} \times T}{RC} + c \tag{3.2}$$

By scaling  $\frac{T}{RC}$  to be equal to one, the voltage at the end of charging phase is given  $V_{out} = V_{in}$  as shown in Fig. 3.3. Since the integrating capacitor is not reset, the final output voltage at the end of the sampling phase is dependent on c. In Figure 3.3, the initial value for the first cycle is assumed to be equal to zero.

#### **Discharge Phase**

During the discharge phase, the input voltage is disconnected and the capacitor is discharged using a constant reference voltage  $-V_{ref}$  via the resistor 'R' until the next fast-clock edge after the comparator has detected a zero crossing.

Figure 3.4 shows the operation of the dual-slope ADC during the discharge phase. The slope of discharge in this case is calculated to be equal to  $V_{ref}/RC$ . As shown in Fig. 3.4, the discharging is continued after the zero crossing is detected, until the next fast clock edge. In alternate words, after the zero crossing is detected, the zero crossing edge is synchronized with one of the fast clock edges. This synchronized edge is used to turn off the discharging. By doing this, the negative of quantization error is stored on the integrating capacitor. Therefore, the output voltage at the end of the discharge phase is given by

$$V_{out,\phi_2} = -Q(e) \tag{3.3}$$

As opposed to a dual-slope ADC, the integrating capacitor is not reset, and the value is carried forward to the next phase.

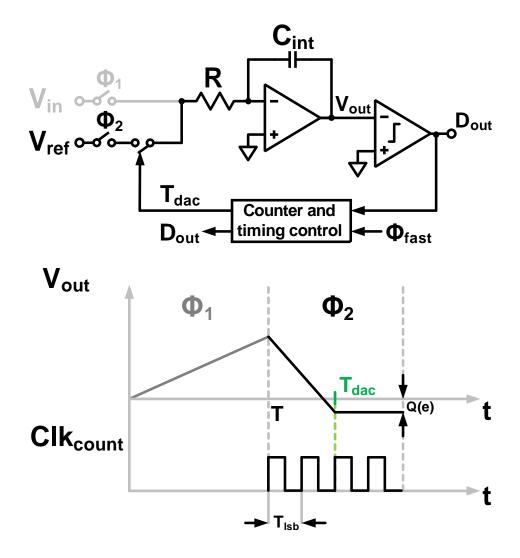

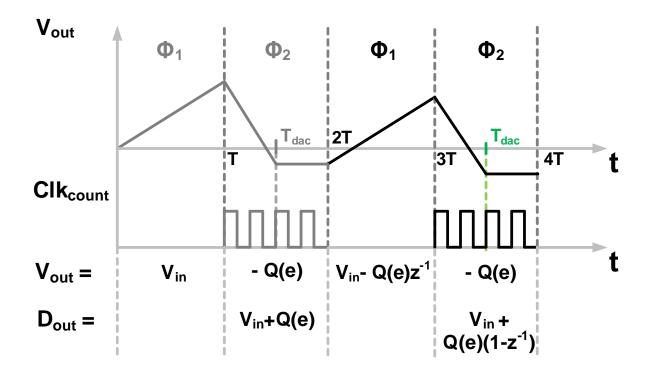

#### Noise-shaping Integrating Quantizer

Figure 3.5 shows the timing diagram over two cycles for the NSIQ. Assuming that the initial voltage on the integrating capacitor is equal to zero, the voltages during the first cycle are given by eq. 3.4

Figure 3.4: Discharge phase of noise-shaping integrating quantizer showing the quantization error being stored at the end of quantization phase.

$$V_{out,\phi_1}[1] = V_{in} \tag{3.4a}$$

$$V_{out,\phi_2}[1] = -Q(e)$$

(3.4b)

$$D_{out}[1] = V_{in} + Q(e) \tag{3.4c}$$

Note for the beginning of the second cycle, the voltage on the integrating capacitor is equal to  $-Q_e$ . Therefore, voltages during the second cycle are given

Figure 3.5: Timing diagram showing the operation of NSIQ over two cycles of operation.

by eq. 3.5

$$V_{out,\phi_1}[2] = V_{in} - z^{-1}Q(e)$$

(3.5a)

$$V_{out,\phi_2}[2] = -Q(e)$$

(3.5b)

$$D_{out}[2] = [V_{in} - z^{-1}Q(e)] + Q(e)$$

(3.5c)

$$= V_{in} + (1 - z^{-1})Q(e)$$

(3.5d)

From eq. 3.5, it is evident that final digital output shapes the quantization error, and hence we get  $1^{st}$  order noise shaping from the NSIQ.

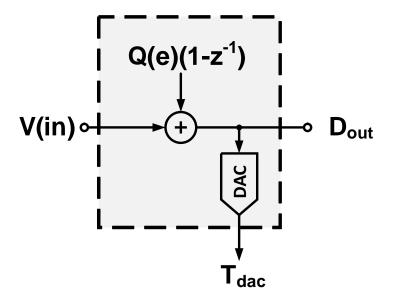

One more key property of NSIQ is that  $T_{dac}$  represents the DAC value in time domain. Therefore, as discussed in next section, a charge-pump is used to find the phase difference between time input,  $T_{in}$ , and  $T_{dac}$ . Figure 3.6 shows the equivalent model of the noise-shaping integrating quantizer. The input to the system is an analog voltage  $V_{in}$ , and the digital output  $(D_{out})$  is the input + shaped quantization error. Along with the digital output,  $T_{dac}$  is also available, which is a time pulse whose width is proportional to  $D_{out}$ .

Figure 3.6: Equivalent model of noise-shaping integrating quantizer.

# **3.2** A $2^{nd}$ Order Charge-pump Based $\Delta \Sigma$ TDC

# 3.2.1 Charge-pump as a Phase Difference Integrator

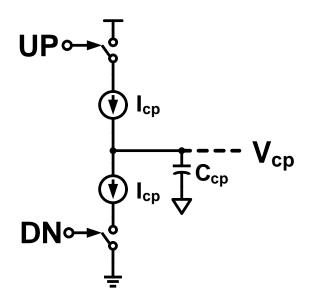

A charge-pump is typically used in a phased locked loop (PLL) to find the phase difference between the reference signal and the output signal - typically designated as UP and DN [27]. As shown in Fig. 3.7, the two signals UP and DN are used to control two switches, which help steer identical currents  $I_{cp}$  into or out of a capacitor, thereby integrating the phase difference between the two signals UP and DN onto the charge-pump capacitance  $C_{cp}$ .

Figure 3.7: Charge-pump as a phase subtractor and integrator.

In each cycle, the time during which the switch is turned on is proportional to the phase difference, hence the charge integrated onto the capacitor is dependent on the phase difference between UP and DN signals. The voltage change on the capacitor during each cycle is given by

$$\Delta V_{cp} = \frac{I_{cp} \times \Delta T}{C_{cp}} \tag{3.6}$$

where  $\Delta V_{cp}$  is the the change in the charge pump voltage,  $\Delta T$  is the phase difference between the UP and DN phases,  $I_{cp}$  is the charge-pump current and  $C_{cp}$  is the integrating capacitor. Capacitor  $C_{cp}$  is not reset, thereby acting as an integrator. Therefore, the voltage across the capacitor at the end of any cycle is given by the following equation

$$V_{cp}[n+1] = \Delta V_{int} + V_{cp}[n] \tag{3.7}$$

where  $V_{cp}[n+1]$  is the sum of the previous voltage and the change in voltage during the present cycle.

From the above discussion, it is clear that one could use the charge-pump to integrate the phase difference between two time signals. We use this property to build a second-order  $\Delta\Sigma$  TDC, as discussed in the following section.

# 3.2.2 Charge-pump based $\Delta\Sigma$ TDC

Figure 3.8:  $2^{nd}$  order  $\Delta \Sigma$  TDC.

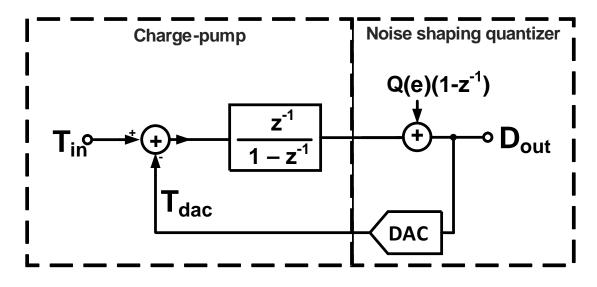

Figure 3.8 shows one possible structure for a second order  $\Delta\Sigma$  TDC. It consists of a delayed integrator, giving one order of noise-shaping, and a noise-shaped quantizer which makes it a second order  $\Delta\Sigma$  TDC. The input to the TDC is a time input  $T_{in}$  and the digital output of the system is  $D_{out}$ .

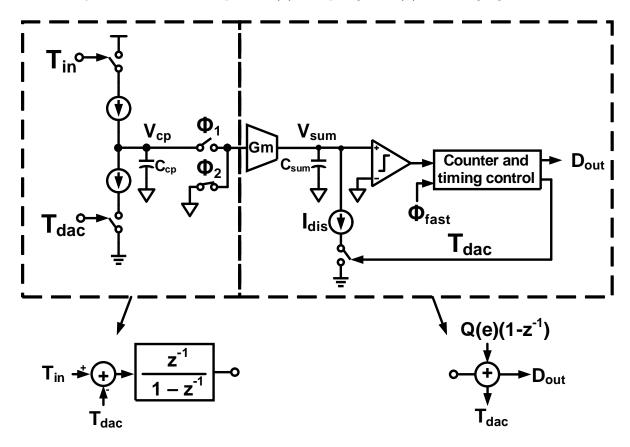

The charge-pump is used to integrate the phase difference between the timeinput  $T_{in}$  and  $T_{dac}$ . A NSIQ is used as a quantizer as it gives one extra order of noise-shaping, while also giving the quantizer DAC value in time domain  $T_{dac}$ . The resulting structure of the second order  $\Delta\Sigma$  TDC is shown in Fig. 3.9. The TDC structure is a cascade of a charge-pump and noise-shaping integrating quantizer. The operation of this TDC is very similar to that of a NSIQ and its operation can be broadly classified into two phases (1) Sampling and (2) Discharging.

Figure 3.9:  $2^{nd}$  order  $\Delta\Sigma$  TDC built using charge-pump and NSIQ.

#### **Sampling Phase**

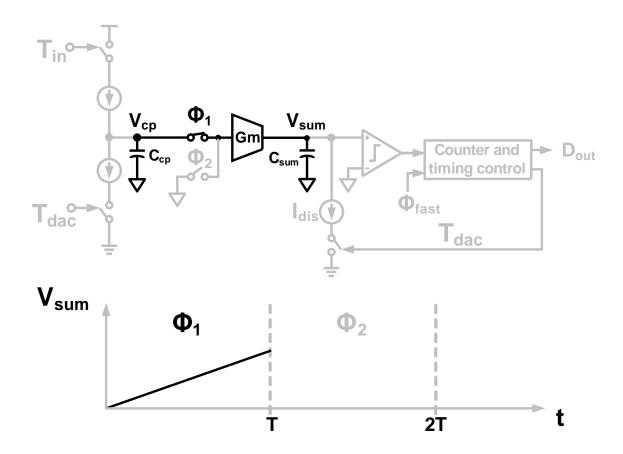

The sampling phase of the TDC is similar to that of the input sampling phase dual-slope ADC, wherein the input of the first integrator is summed on the summing capacitor  $C_{sum}$  using a transconductance Gm. This operation happens during phase  $\phi_1$  as shown in Fig. 3.10.

The summing capacitor is equivalent to the integrating capacitor of the dual

Figure 3.10: Input sampling phase of  $\Delta\Sigma$  TDC

slope ADC, and is never reset. The total charge summed onto the summing capacitor during this phase is equal to  $I\Delta T$ , where I is the current and is equal to  $Gm \times V_{cp}$ . Therefore, the change in the output voltage is given as

$$\Delta V_{sum} = \frac{Gm\Delta T}{C_{sum}} \times V_{cp} \tag{3.8}$$

where Gm is the transconductance of the stage,  $\Delta T$  is the time interval for which the summing happens, which in this case is T (sampling time period/2). If  $\frac{Gm\Delta T}{C_{sum}}$ is normalized to one,  $\Delta V_{sum} = V_{cp}$ . In this case, the output voltage  $V_{sum}$  at the end of the sampling phase is given as

$$V_{sum}[n] = -z^{-1}Q(e) + V_{cp}[n]$$

(3.9)

where  $-z^{-1}Q(e)$  represents the quantization error of the previous cycle. Figure 3.10 also shows  $V_{sum}$  voltage as a function of time.

### **Discharging Phase**

The discharge phase of the TDC is similar to that of NSIQ and is shown in Fig. 3.11. The capacitor  $C_{sum}$  is discharged, using a constant current source  $I_{dis}$  which is disconnected on the next fast-clock edge after the comparator has detected a zero crossing.

The summing capacitor is not reset, thereby storing the quantization error of the stage. The number of fast clock edges for which the discharge happened represents the DAC code,  $D_{out}[n]$ . Therefore, the voltages at the end of the discharge phase can be summarized as below

$$I_{dis} \times D_{out}[n] = (V_{sum}[n] + Q(e)) \times C_{sum}$$

$$(3.10)$$

When  $I_{dis}C_{sum}$  is scaled to be equal to 1, we get

$$D_{out}[n] = V_{sum} + Q(e) \tag{3.11a}$$

$$= V_{cp}[n] + (1 - z^{-1}) \times Q(e)$$

(3.11b)

Note that  $T_{dac}$  represents the DAC value in time domain.

# A $2^{nd}$ Order Charge-pump Based $\Delta \Sigma$ TDC

The starting edge of the time input to the TDC is synchronized with rising edge of  $\phi_1$ , while the stop edge of the input occurs asynchronously during  $\phi_1$ . Therefore, during the discharge phase the difference between the DAC value in time

Figure 3.11: Discharge phase of  $\Delta\Sigma$  TDC

domain  $(T_{dac})$  and the input  $(T_{in})$  is integrated onto the charge-pump capacitance  $C_{cp}$  using the input charge-pump as shown in Fig. 3.11. Therefore,  $V_{cp}[n]$  is given by the following equations:

$$V_{cp}[n] = \frac{I_{cp} \times (T_{in}[n-1] - T_{dac}[n-1])}{C_{cp}} + V_{cp}[n-1]$$

(3.12a)

When  $I_{cp}/C_{cp}$  is normalized to 1, we get

$$V_{cp}[n] = (T_{in}[n-1] - T_{dac}[n-1]) + V_{cp}[n-1]$$

(3.13a)

$$\Rightarrow V_{cp} \times (1 - z^{-1}) = T_{in}[n - 1] - T_{dac}[n - 1]$$

(3.13b)

$$\Rightarrow V_{cp} = \frac{(T_{in} - T_{dac})z^{-1}}{1 - z^{-1}}$$

(3.13c)

Therefore, by rearranging the terms of the above equation and using eq. 3.11 while also realizing that  $T_{dac} = D_{out}$ , we get

$$D_{out}[n] = T_{in}[n]z^{-1} + (1 - z^{-1})^2 \times Q(e)$$

(3.14)

Therefore, using a charge-pump and a NSIQ a second-order  $\Delta\Sigma$  TDC can be built. The above concept can be extended to build a  $3^{rd}$  order  $\Delta\Sigma$  TDC as discussed in the next section.

# **3.3** A $3^{rd}$ Order Charge-pump Based $\Delta \Sigma$ TDC

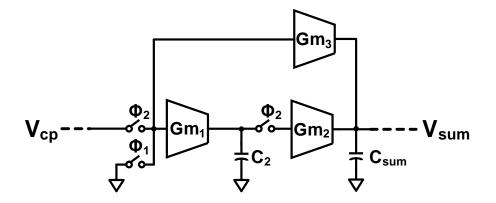

The  $2^{nd}$  order  $\Delta\Sigma$  TDC structure discussed above could be extended to operate as a  $3^{rd}$  order  $\Delta\Sigma$  TDC by using an extra integrator and a feed-forward path in the loop as shown in Fig. 3.12.

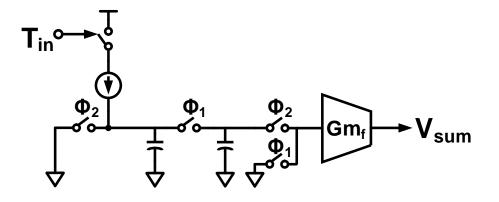

The additional integrator and the feed-forward path shown in Fig. 3.12 are implemented using Gm-C filter as shown in Fig. 3.13

During phase  $\phi_2$ , transconductor  $Gm_1$  integrates the voltage  $V_{cp}$  onto capacitor  $C_2$ , thereby acting as an integrator. During the same phase, the voltage on  $C_2$ is sensed by transconductor  $Gm_2$  which adds a voltage proportional to the previous value of the onto the summing node  $V_{sum}$  along with some portion of the current input value. This therefore reduces the gain required by the direct feed-forward path  $(Gm_3 - C_{sum})$ .

Figure 3.12: Extending the  $2^{nd}$  order  $\Delta \Sigma$  TDC to operate as a  $3^{rd}$  order  $\Delta \Sigma$  TDC.

Figure 3.13: Transconductor and feed-forward path using transconductors.

## 3.3.1 Signal Feed-forward Path

To reduce the amount of signal processed by the loop, and also reduce the amount of distortion caused by the loop components, a input signal feed-forward path is used [28]. In voltage domain, the signal feed-forward path is implemented as shown in Fig. 3.14. The loop filter H(z) processes only the shaped quantization noise, thereby making the architecture immune to distortion by the loop. It has to

be noted that the feedback path has to be delay free for the implementation to be effective. Therefore, a delay is included in the input voltage path, which is later compensated for in the loop.

Figure 3.14: Voltage domain low distortion architecture.

However, a direct one-to-one mapping to a TDC is not so straight forward. Using the current technology, it is impossible to delay/store time information accurately. Therefore, an alternative feed-forward path is used in the TDC architecture as shown in Fig. 3.15.

Figure 3.15: Time domain low distortion architecture.

In the feed-forward path shown in Fig. 3.15, the time input is converted to voltage domain using a charge-pump. This voltage is then passed through a low pass filter and added appropriately to the summing capacitor. The timing diagram

and the implementation of the feed-forward path filter is shown in Fig. 3.16. The feed-forward path implements the following transfer function:

$$y[n] = \frac{y[n-1] + x[n]}{2}$$

(3.15a)

$$\Rightarrow H_1(z) = \frac{1}{2 - z^{-1}}$$

(3.15b)

Figure 3.16: Implementation of feed-forward path in TDC.

Since the oversampling ratio of the  $\Delta\Sigma$  ADC is 16, the value of  $H_1(z)$  was approximated to 1, and  $Gm_f$  was designed such that  $Gm_f \times T/C_{sum} = 1$ .

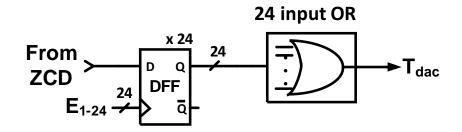

# 3.3.2 A 3<sup>rd</sup> Order Charge-pump Based $\Delta\Sigma$ TDC

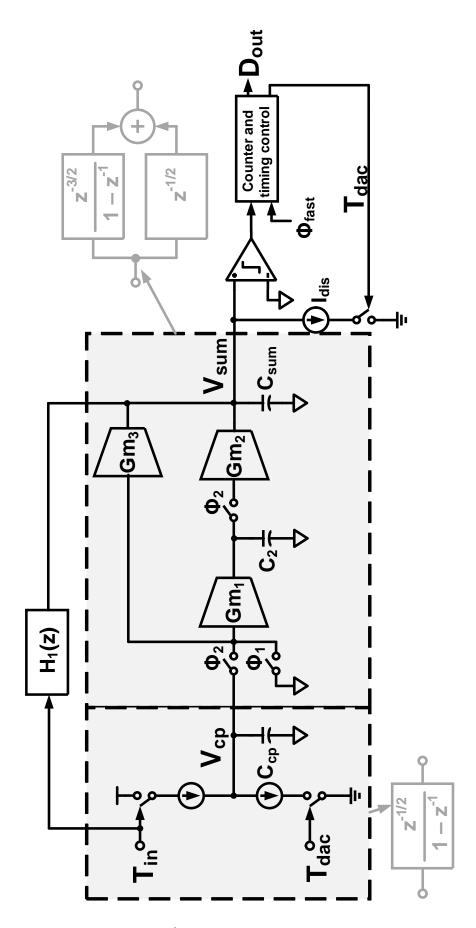

By incorporating the extra integrator and the feed-forward path, a  $3^{rd}$  order charge-pump based  $\Delta\Sigma$  TDC is built. The final structure of the third-order  $\Delta\Sigma$  TDC, which was implemented is shown in Fig. 3.17.

For increasing the stability of the loop, the loop transconductors were designed such that the out of band gain of the modulator was equal to 4 [19]. The quantizer was designed such that the 24 fast clock edges occur during the discharge phase of the TDC, thereby making it a 24-level quantizer.

Figure 3.17: A  $3^{rd}$  order charge-pump based  $\Delta\Sigma$  TDC.

The next section talks about the circuit level implementation of some of the important blocks in the  $\Delta\Sigma$  TDC.

# 3.4 Circuit Implementation

This section discusses the circuit level implementation of the individual blocks used to build the third order  $\Delta\Sigma$  TDC.

# 3.4.1 Charge-pump

The input charge-pump acts as a time subtractor as well as an integrator. Due to the feed-forward architecture used for the TDC, the main  $\Delta\Sigma$  loop only processes quantization error, thereby relaxing the requirements on the loop components considerably. Also, any errors at the output of the charge-pump are first order noise shaped, thereby relaxing the design requirements of the charge-pump.

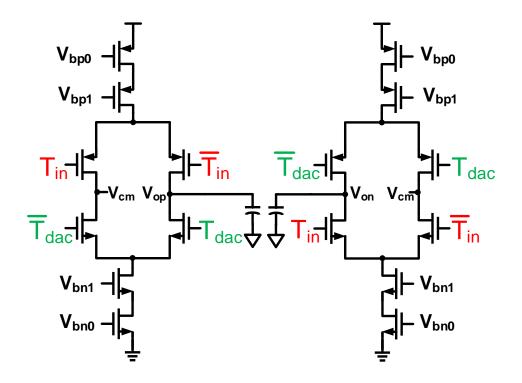

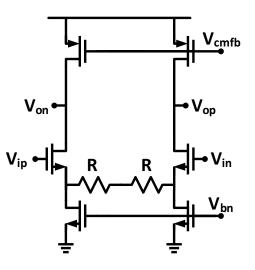

A current switched architecture for the charge-pump was chosen, with the current of the charge-pump either being pumped into the output nodes  $(V_{op}, V_{on})$ , or being directed into the common mode of the system [29]. The inputs to the charge-pump being  $T_{in}$  and  $T_{dac}$ . A single-ended charge-pump architecture would suffer from NMOS-PMOS mismatch, thereby seriously limiting the achievable SNDR. Therefore, a pseudo differential architecture was used to reduce nonlinearity from the charge-pump, as shown in Fig. 3.18.

Large device sizes were used to reduce the effects of mismatch and also reduce non-linearity due to small channel effects. Noise from the charge-pump is directly proportional to the on-time of the charge-pump and the analysis is done assuming that the charge-pump current sources were "ON" for half the duration of  $\phi_1$ .

A scaled version of the pseudo-differential charge-pump was also used for the discharging current source  $(I_{dis})$ , which is used to discharge the summing capacitor.

Figure 3.18: Current switched charge-pump.

# 3.4.2 Transconductors

Since the output of all the transconductors are at least second noise shaped, resistor degenerated transconductors, with wide bandwidth were used in the design [30]. The basic structure of the transconductor is shown in Fig. 3.19

Note that the transconductances of each stage were scaled appropriately based on their respective requirements.

# 3.4.3 Zero Crossing Detector

In this implementation of the TDC, the direction of discharge is always in the same direction. Therefore, the voltage at which the zero crossing happens is the

Figure 3.19: Transconductance.

same for all voltage inputs (i.e. a zero detection always happens at a differential input of zero), the zero crossing detector (ZCD) produces a constant time delay. In practice, however, finite ZCD gain and bandwidth result in a signal dependent delay for the ZCD for small inputs [31]. Therefore, in order to minimize these artifacts, a high gain wide bandwidth ZCD was used in the TDC. This ZCD was built by cascading low gain wide bandwidth amplifiers as shown in Fig. 3.20.

Figure 3.20: Zero crossing detector

Also, note that any signal dependent errors from the ZCD are second order

noise shaped by the loop filter as it occurs only in the later part of the loop. This further relaxes the design requirements on the ZCD.

## 3.4.4 Fast Clock

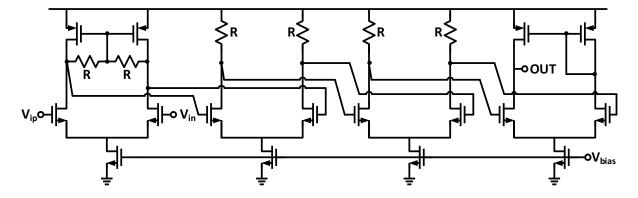

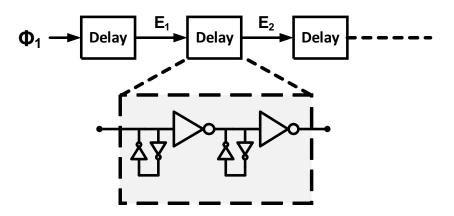

The number of fast clock edges in the time interval  $\phi_1$  directly determines the number of quantization levels of the TDC. Therefore, it is advantageous to increase the frequency of the fast clock as it reduces the signal content which is processed by the loop, thereby stabilizing the loop, while also improving the SQNR. However, it is not practical to inject a high frequency clock onto the chip as it would be difficult to synchronize the beginning of discharge cycle with the beginning of  $\phi_1$ . Therefore, the fast clock is implemented using an on-chip voltage controlled delay line as shown in Fig. 3.21

Figure 3.21: Delay line.

The delay line consists of a cascade of delay elements. Each delay element consists of two inverters, whose supply is controlled off-chip, thereby enabling the control on the delay value. The intermediate nodes of the delay element are restored to near full voltage levels using smaller back-to-back connected inverters as shown in Fig. 3.21. The input to the delay line is the rising edge of  $\phi_1$ , thereby synchronizing the beginning of discharge cycle with beginning of  $\phi_1$ .

In this design, a delay chain of 24-elements was used, thereby making the number of quantization levels equal to 24.

# 3.4.5 Time to Digital Converter

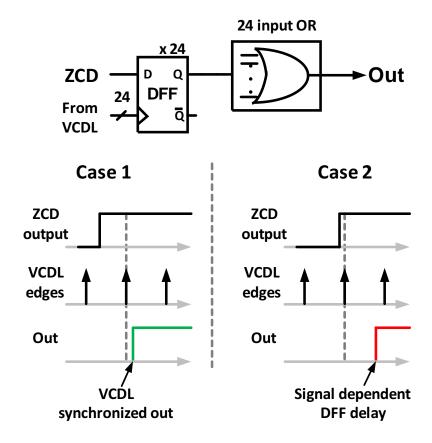

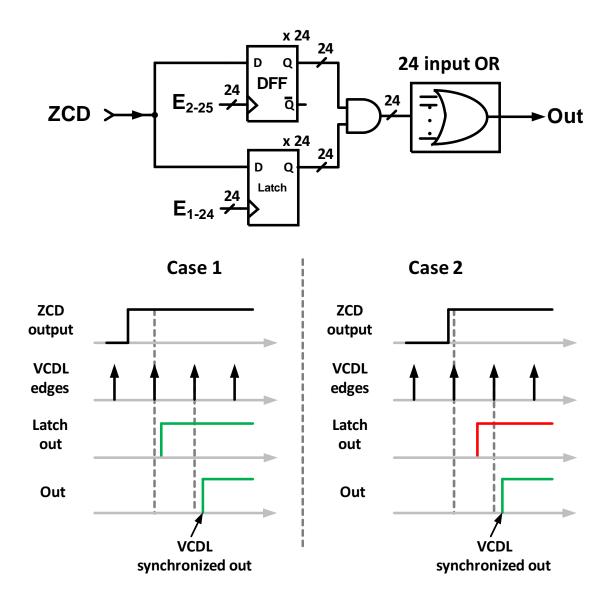

The main operation of the TDC is to synchronize the zero crossing edge with one of the 24 fast clock edges. The simplest approach to perform this operation is shown in Fig. 3.22 [?].

Figure 3.22: Basic time-to-digital converter.

As discussed in the earlier subsection, the fast-clock is implemented using a voltage controlled delay line (VCDL). The 24 edges of the VCDL ( $E_{1-24}$ ) act as clocks to 24 DFFs. The input to these DFFs is the same, and is got from the ZCD. Once the zero crossing edge occurs, the output of one of the DFFs triggers high synchronously with one of the VCDL edges. The outputs of these 24-DFFs are "OR'ed" using a 24-input OR gate. Thus the output of the OR gate synchronizes the zero-crossing detector edge with one of the VCDL edges.

Unfortunately, the above architecture suffers greatly due to the signal dependent delay of the DFF. This problem is articulated in Fig. 3.23

Figure 3.23: Signal dependent delay of DFF.

When the input to the DFF occurs well before a VCDL edge, i.e. well before the setup time of DFF, the delay of the DFF is fixed thereby synchronizing the input with the VCDL edge. This is shown in Case 1 of Fig. 3.23. However, more often than not, the input edge occurs very close to a VCDL edge, thereby making the delay of the DFF signal dependent. Therefore, the output of DFF is no longer synchronous with a VCDL edge, thereby defeating the purpose of the TDC. This phenomenon is shown in Case 2 of Fig. 3.23. Fortunately, an alternative architecture exists which can mitigate the problem of signal dependent DFF delay and this is shown in Fig. 3.24.

The solution makes use of a two level time-staggered DFF and latch [32].

Figure 3.24: (a)Time-to-digital converter. (b) Timing diagram.

The input to the DFF and latch is recieved from the ZCD, while their clocks are time staggered as shown in Fig. 3.24. In case 1, the zero crossing edge is far from the VCDL edge. Therefore, the output of the latch and that of the OR gate are synchronous with a VCDL edge. In case 2, when the zero crossing edge is close to the VCDL edge, the output of the latch suffers from signal dependent delay. However, the output of OR is still synchronous with a VCDL edge due to time staggering i.e. the DFF triggers only on the next VCDL edge thereby making the output of the AND gate and hence the OR gate synchronous with a VCDL edge. Also, the latches are designed such that the setup time is reduced. Note that the problem of input dependent delay is greatly reduced, but not completely removed [33, 34].

Note that the penalty of using the above time staggering approach is that the architecture introduces one extra delay in synchronizing the zero crossing edge with VCDL edge.

# 3.5 Non-idealities

The  $\Delta\Sigma$  TDC, due to its noise-shaping properties, is immune to some circuit non-idealities and not so immune to others. This section discusses some of the important non-idealities which need to be carefully considered in building the noise-shaping  $\Delta\Sigma$  TDC.

### 3.5.1 Zero Crossing Detector

The zero crossing detector(ZCD) compares the voltage of  $V_{sum}$  with zero, and triggers once a zero crossing has been detected. There are two aspects of the zero crossing detector which need to be considered. (1) Comparator noise and (2) Comparator delay.

#### **Comparator Noise**

The analysis of the comparator noise is similar to the comparator-based circuits [35], with the main difference being that the reference voltage at which the zero crossing happens and the discharging slope are fixed for all cycles. If the zero crossing happens towards the middle of the fast clock, the noise will have no effect on the performance of the TDC because the discharging will stop only at the next fast-clock edge (shown in green in Fig. 3.25). In the case where the zero crossing edge happens close to the fast-clock edge, the comparator noise could change when the zero crossing happens, and hence the discharge can take place for one extra cycle/ one less cycle. This is shown in red in Fig. 3.25. Note that this phenomenon is equivalent to that of comparator noise in a flash ADC.

Figure 3.25: Effect of comparator noise on TDC decisions.

In a flash ADC, this would mandate the comparator be designed such that the noise of the comparator be less than LSB/2. Luckily, this is not a big problem in the TDC architecture as the noise in the comparator is added towards the end-of the  $\Delta\Sigma$  loop, and hence it is noise shaped. For the above third order system, the comparator noise is second order noise-shaped. In other words, the comparator noise sees a high pass transfer function, thereby relaxing the design requirements on the comparator and reducing the power consumption. A simple example as shown in Fig. 3.25 illustrates that the error in the dual-slope is high pass filtered i.e. on average the error is removed.

#### **Comparator Delay**

The other important aspect, in designing the comparator, is the comparator delay  $(t_{delay})$ . The delay acts like a fixed offset since the reference voltage at which the zero crossing happens and the discharging slope are fixed for all cycles. This effect is shown in Fig. 3.26. The signal path in black shows the charging and discharging phases when the comparator is ideal and has zero delay. The curve in red shows the case where the comparator delay is non-zero.

Figure 3.26: Effect of comparator delay on TDC.

However, one interesting effect of comparator delay is observed in Fig. 3.26. Given that the feedback element in the  $\Delta\Sigma$  modulator is time information, the  $\Delta\Sigma$  loop ensures that the average value which is feeded back is equal to the average value of the input. Therefore, the value of the comparator delay is absorbed into the loop, and the overall value of  $D_{out}$  (in other words  $T_{dac}$ ) will follow the input  $T_{in}$  on the average sense. This interesting property is observed in Fig. 3.26 wherein the value the value of  $D_{out}$  is the same after the first cycle onwards. This is because the loop absorbs the delay of the comparator.

## 3.5.2 Delay Element Mismatch

Delay element forms one of the key blocks in  $\Delta\Sigma$  TDC. Since the delay elements are used to build the fast-clock, which are used for counting as well as providing feedback DAC information, any mismatch in them would directly affect the overall performance of the  $\Delta\Sigma$  TDC. Mismatch in the delay elements directly translates to mismatch in the time steps. The mismatch in time steps has impact in two different places (1) Mismatch in discharge time steps (2) Mismatch in DAC feedback value.

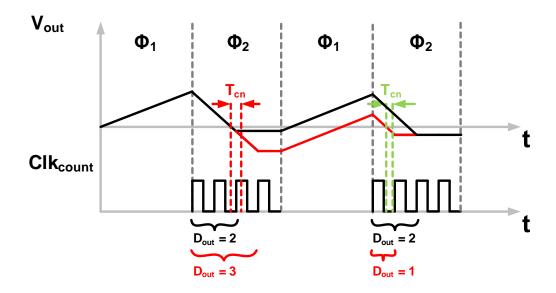

#### Mismatch in Discharge Time Steps

Mismatch in discharge time steps is equivalent to mismatch in the flash quantizer typically used in  $\Delta\Sigma$  ADCs and is very similar to the effect of comparator noise on  $\Delta\Sigma$  TDC. In the case of noise-shaping quantizer, it effectively means the amount of discharge time is not directly proportional to the  $D_{out}$ , but instead suffers from mismatch. For example, assume  $D_{out} = 2$  corresponds to a time step of width 20ns, then ideally  $D_{out} = 3$  would correspond to a time step of width 30ns. But due to mismatches in the delay elements, it could so happen that  $D_{out} = 3$ would correspond to a time step of width 31ns. This would mean that the voltage on the summing node has an error, whose value is proportional to the mismatch in the delay line. Fortunately, as in a conventional  $\Delta\Sigma$  ADC, the mismatches in comparator time steps are noise shaped by the loop filter, and therefore have little/no effect on the performance on the overall TDC as shown in Fig. 3.27.

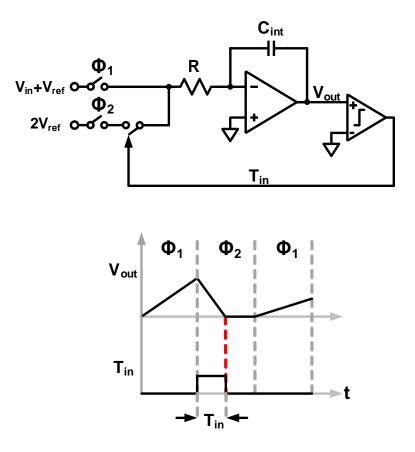

Figure 3.27: Effect of mismatch in discharge time steps

H(z) represents the loop filter in Fig. 3.27 and  $err_{delay}$  represents the error due to mismatch in the delay line. H(z) is a low pass filter, therefore the transfer function of  $err_{delay}$  due to mismatch in time steps is given by eq. 3.16

$$TF_{err_{delay,time-step}} = \frac{1}{1 - H(z)}$$

(3.16)

where  $TF_{err_{mismtach}}$  is a high pass filtered, thereby reducing the impact of mismatch in discharge time steps on the overall performance of the TDC.

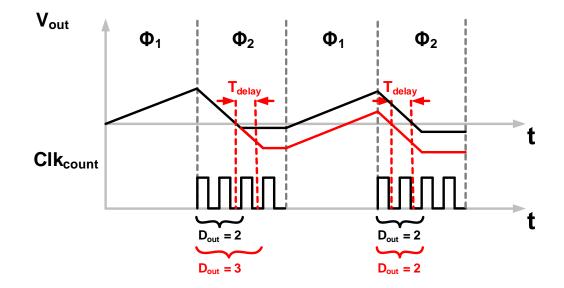

## Mismatch in DAC Feedback Value

Mismatch in delay elements also implies mismatch in the DAC feedback value as the feedback pulse is directly equal to the amount of discharge time. This has a profound impact on the performance of the TDC, as any errors in the DAC feedback value would be directly represented at the output, as it sees a low pass transfer function, thereby massively impacting the overall performance of the TDC. Figure 3.28 illustrates this point.

Figure 3.28: Effect of mismatch in DAC feedback path

The transfer function of  $err_{delay}$  due to mismatch in the DAC feedback value is give by eq. 3.17

$$TF_{err_{delay,dac}} = \frac{-H(z)}{1 - H(z)} \tag{3.17}$$

where  $TF_{err_{delay,dac}}$  is a low pass transfer function, and therefore has a huge impact on the performance of the ADC. Note that the overall transfer function of the mismatch in delay line is obtained by combining equations 3.16 and 3.17.

$$TF_{err_{delay}} = \frac{1}{1 - H(z)} + \frac{-H(z)}{1 - H(z)}$$

(3.18a)

$$= 1$$

(3.18b)

The above equation suggests that delay line design is one of the most critical designs for the overall performance of the TDC. Therefore, for this test chip, care has been taken to reduce the mismatch in the delay line to acceptable value. This was done by using larger device sizes (as mismatch  $\alpha$  1/Area) and also making the layout of the delay line as symmetric as possible, thereby reducing the possibility of any deterministic mismatches. Extensive monte-carlo simulations were run to ensure that the overall performance of the TDC is not limited due to the mismatch in delay line. Also, to reduce the effect of dynamic mismatches, huge decoupling

capacitors were used on the delay line supplies.

## 3.5.3 Clock Jitter

Systems which rely upon continuous time input sampling/continuous time discharging and are synchronized with an external clock are always prone to effects of clock jitter [36]. Continuous time  $\Delta\Sigma$  ADCs (CTDSM) are the best examples of systems in which clock jitter has a massive impact on the performance of the ADC [37]. In CTDSM ADCs, the feedback DAC is a pulse whose duty cycle depends on the clock pulse width, thereby any noise in the clock i.e. any jitter present in the clock will directly effect the overall performance of the ADC.