### AN ABSTRACT OF THE DISSERTATION OF

Sachin B Rao for the degree of Doctor of Philosophy in <u>Electrical and Computer Engineering</u> presented on <u>May 13, 2013</u>. Title: <u>Linearizing Techniques for Voltage Controlled Oscillator Based</u> Analog to Digital Converters.

Abstract approved: \_

### Pavan Kumar Hanumolu

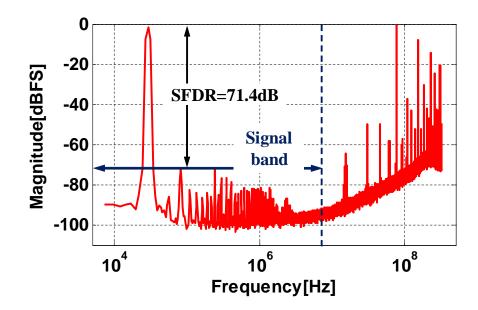

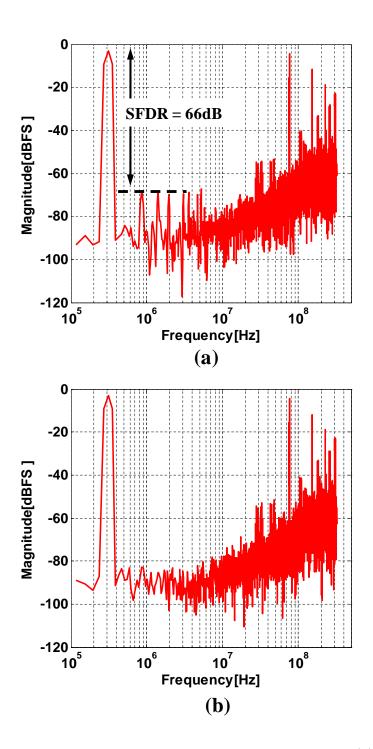

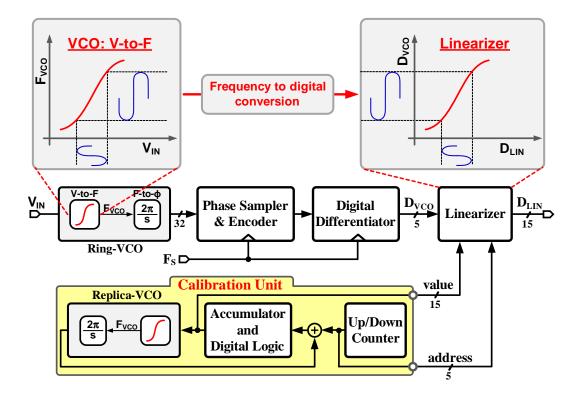

Voltage controlled oscillator (VCO) based ADC is an important class of timedomain ADC that has gained widespread acceptance due to their several desirable properties. VCO-based ADCs behave like an open-loop continuous time  $\Delta\Sigma$  modulator and achieve excellent resolution by first order noise shaping the quantization error. However, the SNDR of an open-loop VCO-based ADC is severely distortion limited by the voltage-to-frequency tuning characteristics of the VCO. This work examines various techniques that have already been proposed to overcome the VCO tuning non-linearity problem. Two new VCO-based ADC architectures, that overcome the limitations of the conventional approaches, are proposed. In the first approach, the ADC is linearized by forcing the VCO to operate at only two operating points using a front-end two level modulator. With this technique, the linearity is improved without using either a multi-bit feedback DAC or calibration. Fabricated in a 90 nm CMOS process, the prototype ADC achieves better than 71 dB SFDR and 59.1 dB SNDR in 8 MHz signal bandwidth while consuming 4.3 mW power. The ADC achieves a figure of merit of 366 fJ/conv-step, which is comparable with other state of the art time based ADCs. In the second approach, the need for a front-end two level modulator is obviated using linearizers, which introduce an inverse of VCO's voltage to frequency characteristics in the signal path. A deterministic digital calibration unit runs continuously in the background and builds the inverse voltage to frequency transfer function. Implemented in a 90nm CMOS process, this on-chip calibration improves SFDR of the prototype ADC from 46 dB to more than 83 dB. The ADC consumes 4.1 mW power and achieves 73.9 dB SNDR in 5 MHz signal bandwidth resulting in an excellent figure of merit of 101 fJ/conv-step.

<sup>©</sup>Copyright by Sachin B Rao May 13, 2013 All Rights Reserved

### Linearizing Techniques for Voltage Controlled Oscillator Based Analog to Digital Converters

by

Sachin B Rao

### A DISSERTATION

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented May 13, 2013 Commencement June 2013  $\frac{\text{Doctor of Philosophy}}{\text{May 13, 2013.}} \text{ dissertation of } \frac{\text{Sachin B Rao}}{\text{May 13, 2013.}} \text{ presented on }$

APPROVED:

Major Professor, representing Electrical and Computer Engineering

Director of the School of Electrical Engineering and Computer Science

Dean of the Graduate School

I understand that my dissertation will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my dissertation to any reader upon request.

Sachin B Rao, Author

#### ACKNOWLEDGMENTS

My experience as a graduate student at Oregon State University has been very rewarding and enriching. In addition to the research and the course work, I have had the opportunity to know and work with some of the brightest people in the area of analog and mixed signal circuit design. Many of them have directly or indirectly contributed towards the successful completion of my graduate studies. Therefore, in a way, this work belongs to every one of them.

First and foremost, I am indebted to my adviser, Dr. Pavan Kumar Hanumolu, for giving me the opportunity to be a part of his research group. Without his guidance and unswerving trust, this work would not have been anywhere close to it's current form. In-spite of his very busy schedule, he somehow always made himself available to discuss research related or personal issues and provided his honest opinion. I do not know of any other person who works so hard and has so many things going on in parallel, but yet is so unassuming and laid back. I would always strive to inculcate such qualities.

I am also grateful to Dr. Un-Ku Moon for agreeing to serve in my committee in-spite of his busy schedule. He has always been approachable and provided valuable feedback. Thanks to Dr. Gabor Temes, Dr. Raviv Raich, and Dr. Leonard Coop for agreeing to be on the committee. Dr. Karti Mayaram has helped me whenever I approached him. I would like to thank him for all the discussions and also for pointing out typos and errors in my Master's thesis.

I would also like to thank William McIntyre, Arun Rao, Damian Swank, and Bijoy from Texas Instruments Inc., for all the discussions and supporting a part of my graduate research work.

All the staff members in the Department of EECS have been very friendly

and helpful. Thanks to Ferne Simendinger and Nicole Thompson for all the help with scheduling my exams. Thanks to Renee for helping me so many times by making payments for conference registrations, test boards, air-tickets etc.

The last few years would not have been so delightful without the company of so many friends and lab mates. I would like to thank all the MMIC group members for the technical help and discussions. Thanks to Brian Young, Karthikeyan Reddy, Amr Elshazly, Rajesh Inti, Sasidhar, Qadeer Khan for helping during tapeout and during testing. Thanks to Manideep for being such a wonderful roommate. Thanks to Hariprasath, Mrinmay, Praveen, Abjhijith, Saurabh, Romesh, Mahmoud, Ahmed, Simon, Woo-Seok, Kim, Saeed, Brian Drost, Bangda, Jon, Ho-Young Lee, Taehwan Oh, Yue Hu, Tawfik, Omid, Wenjing, Seok-Min, Derek, Sudarshanram and anyone else that I might have missed for such a great time.

Finally, my deepest gratitude goes to my wife, parents and brother. Without their unconditional love and support nothing would have been possible. I owe everything to them.

## TABLE OF CONTENTS

| Р | a  | g | е      |

|---|----|---|--------|

| • | c, | b | $\sim$ |

| 1 | INT | RODUCTION                                                                  | 1                    |

|---|-----|----------------------------------------------------------------------------|----------------------|

|   | 1.1 | Effect of Technology Scaling                                               | 2                    |

|   | 1.2 | Scope of this work                                                         | 3                    |

|   | 1.3 | Thesis Organization                                                        | 4                    |

| 2 |     | E DOMAIN ANALOG TO DIGITAL CONVERTER ARCHITEC-<br>RES                      | 5                    |

|   | 2.1 | Integrating ADC                                                            | 6                    |

|   |     |                                                                            | 8<br>10<br>12        |

|   | 2.2 | Delay-line based ADC                                                       | 13                   |

|   |     | 1                                                                          | 15<br>16             |

|   | 2.3 | Voltage-to-Frequency Conversion Based ADC                                  | 18                   |

| 3 | OVE | CRVIEW OF VCO-BASED ADCS                                                   | 20                   |

|   |     | 3.0.2 Anti-aliasing property                                               | 21<br>23<br>23       |

|   | 3.1 | Effect of VCO tuning non-linearity                                         | 24                   |

|   | 3.2 | Prior-art VCO-based ADC architectures                                      | 25                   |

|   |     | 3.2.2 VCO-based ADC with phase output3.2.3 Residue canceling VCO-based ADC | 26<br>28<br>29<br>30 |

## TABLE OF CONTENTS (Continued)

| 4 | LINE | AR VCO-BASED ADC USING TWO LEVEL OPERATION 3                         | 33                   |

|---|------|----------------------------------------------------------------------|----------------------|

|   | 4.1  | Proposed Architecture                                                | 33                   |

|   | 4.2  | Fwo level modulator design considerations    3                       | 35                   |

|   |      | 4.2.2 Natural sampling PWM34.2.3 Two level modulator implementation3 | 36<br>37<br>39<br>12 |

|   | 4.3  | VCO quantizer design considerations 4                                | 14                   |

|   |      |                                                                      | 14<br>17             |

|   | 4.4  | Circuit Design Details 4                                             | 19                   |

|   |      | 1.4.2 VCO phase sampler                                              | 49<br>51<br>52       |

|   | 4.5  | Measured Results                                                     | 55                   |

| 5 | BAC  | GROUND CALIBRATION OF VCO-BASED ADC 6                                | 60                   |

|   | 5.1  | Proposed Architecture                                                | 60                   |

|   |      | 1                                                                    | 52<br>56             |

|   | 5.2  | Circuit Design Details                                               | 67                   |

|   |      | 5.2.2 Calibration Unit                                               | 67<br>71<br>75       |

|   | 5.3  | Design Considerations and Non Ideal Effects                          | 76                   |

|   |      | 5.3.2 Effect of Dynamic Non-Linearity                                | 76<br>79<br>81       |

## TABLE OF CONTENTS (Continued)

|    |      |                  | Pag | ge |

|----|------|------------------|-----|----|

|    | 5.4  | Measured Results |     | 82 |

| 6  | CON  | ICLUSION         |     | 90 |

| BI | BLIO | GRAPHY           |     | 93 |

### LIST OF FIGURES

#### Figure Page 1.1 Simplified architecture of the RF receiver employing ADC. (a) Down converting receiver. (b) Direct sampling receiver..... 1 2.1Simplified block diagram of first patented time-domain ADC. .... 52.2Single slope ADC. (a) Simplified block diagram. (b) Time domain waveforms. 7 Multi slope ADC. (a) Simplified block diagram. (b) Time domain 2.39 waveforms. 2.4Subranging time domain ADC. (a) Simplified block diagram. (b) Time domain waveforms..... 11 2.5Noise shaping integrating ADC. (a) Simplified block diagram. (b) Waveforms depicting noise-shaping integrating ADC operation. . . 12Delay line based TDC. (a) Block diagram. (b) Time domain 2.6waveforms. 14Two-step TDC based ADC. (a) Simplified block diagram. (b) 2.7Timing diagram. 162.8High resolution TDC-ADC using a $\Delta\Sigma$ loop. 172.9Voltage to frequency conversion based ADC. 183.1VCO-based quantizer. (a) Simplified block diagram. (b) Representative waveforms. 203.2Modeling of VCO-based ADC. (a) Simplified functional block diagram of VCO-based ADC. (b) VCO-based ADC model with antialiasing filter and $\Delta\Sigma$ modulator. 22Simplified model of VCO-based quantizer..... 3.3 24Output spectrum of open loop VCO-based ADC. 3.425Schematic of VCO-based ADC in a delta sigma loop. ..... 263.5Loop filter gain vs. frequency..... 273.63.7 Basic structure of VCO-based ADC with phase output..... 28

## LIST OF FIGURES (Continued)

| <b>T</b> · |      |

|------------|------|

| F1         | gure |

| 3.8  | Simplified block diagram of residue canceling VCO-based ADC. $$ .                                                                                                                            | 29 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.9  | VCO-based ADC with off-chip foreground calibration.                                                                                                                                          | 30 |

| 3.10 | Block diagram showing background calibration of VCO-based ADC.                                                                                                                               | 31 |

| 4.1  | Illustration of the basic idea of the proposed architecture                                                                                                                                  | 33 |

| 4.2  | Proposed VCO-based ADC architecture                                                                                                                                                          | 34 |

| 4.3  | Uniform sampling pulse width modulation. (a) Basic block dia-<br>gram and principle of operation. (b) Output spectrum with sinu-<br>soidal input.                                            | 36 |

| 4.4  | Natural sampling pulse width modulation. (a) Basic block dia-<br>gram and principle of operation. (b) Output spectrum with sinu-<br>soidal input                                             | 38 |

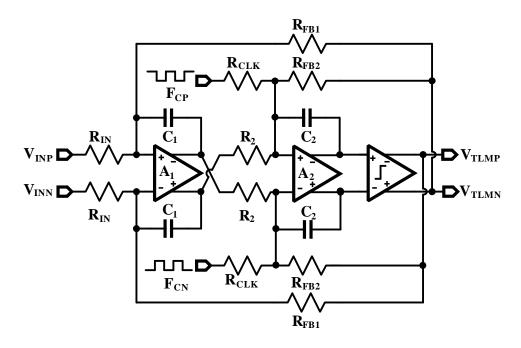

| 4.5  | Block diagram of a fully differential two level modulator                                                                                                                                    | 40 |

| 4.6  | Simulated two level modulator output spectrum                                                                                                                                                | 41 |

| 4.7  | Aliasing of inter-modulation tones. (a) Carrier frequency is har-<br>monically related to sampling frequency. (b) Carrier frequency is<br>harmonically not not related to sampling frequency | 43 |

| 4.8  | Current starved VCO. (a) Block diagram. (b) Equivalent model                                                                                                                                 | 44 |

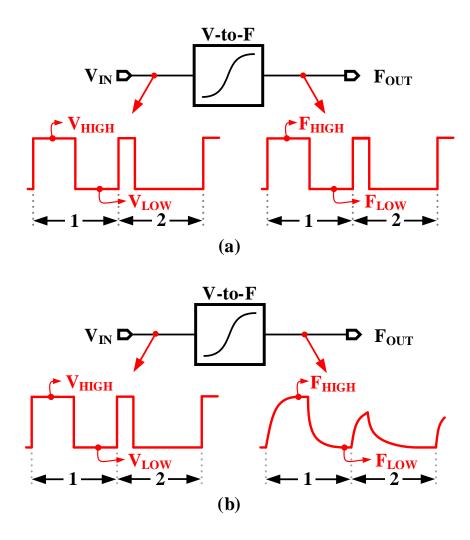

| 4.9  | VCO response to a two level input. (a) Ideal VCO response. (b)<br>Practical VCO response                                                                                                     | 46 |

| 4.10 | Simulated SFDR vs. $\omega_{\rm P} T_{\rm MIN}$                                                                                                                                              | 47 |

| 4.11 | Schematic and waveforms for a single ended wide bandwidth VCO.                                                                                                                               | 47 |

| 4.12 | Schematic and waveforms for a pseudo-differential wide band-<br>width VCO.                                                                                                                   | 48 |

| 4.13 | Opamp architecture used in NSPWM                                                                                                                                                             | 49 |

| 4.14 | Comparator architecture used in NSPWM                                                                                                                                                        | 50 |

| 4.15 | Conventional phase sampler. (a) Simplified block diagram. (b)<br>Phase waveforms depicting non-uniform quantaization steps                                                                   | 52 |

## LIST OF FIGURES (Continued)

| Figu | ure                                                                                                                                      | Page |

|------|------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.16 | Proposed pseudo-differential phase sampler. (a) Simplified block<br>diagram. (b) Phase waveforms depicting uniform quantization<br>steps | 1    |

| 4.17 | Complete VCO quantizer architecture                                                                                                      | 54   |

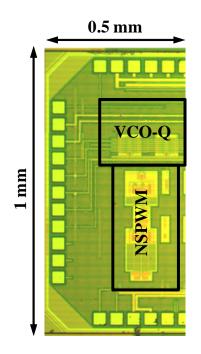

| 4.18 | Die micrograph.                                                                                                                          | 55   |

| 4.19 | Measured output spectrum                                                                                                                 | 56   |

| 4.20 | Simulated output spectrum with supply parasitics. (a) 2.5nH bond-wire inductance. (b) 0.5nH bond-wire inductance                         |      |

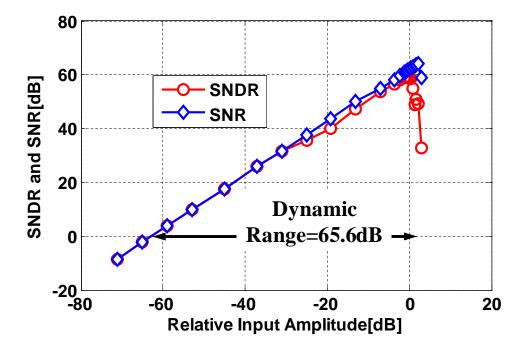

| 4.21 | Measured SNDR and SNR vs. input amplitude                                                                                                | 58   |

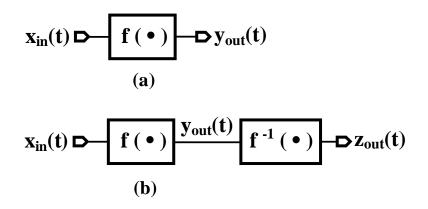

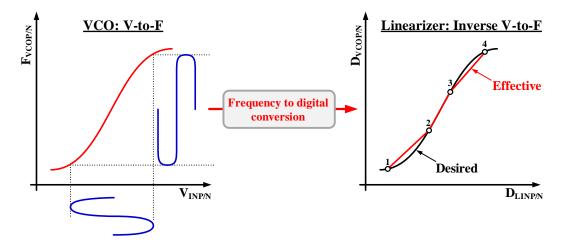

| 5.1  | Figure depicting the basic idea. (a) A general non-linear system<br>(b) Linear system realized with cascaded inverse systems             |      |

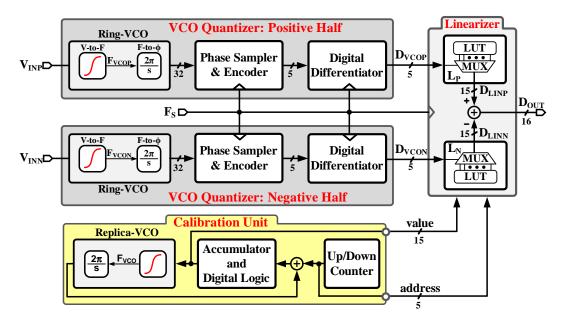

| 5.2  | Simplified block diagram of the proposed architecture                                                                                    | 62   |

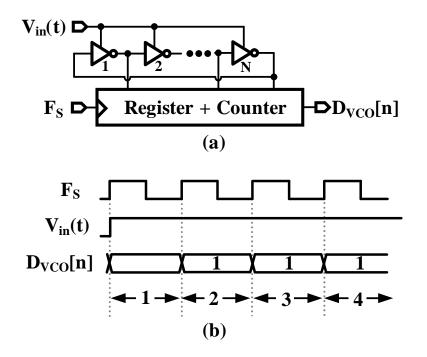

| 5.3  | N-delay stage ring VCO. (a) Simplified block diagram. (b) Wave forms depicting $D_{OUT}[n] = 1$ .                                        |      |

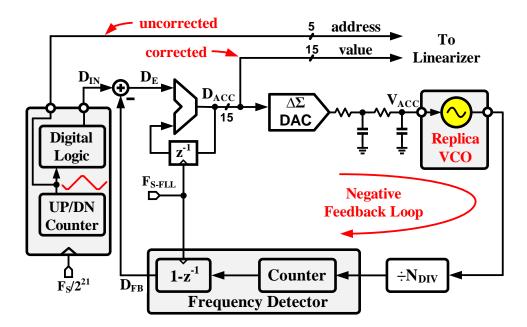

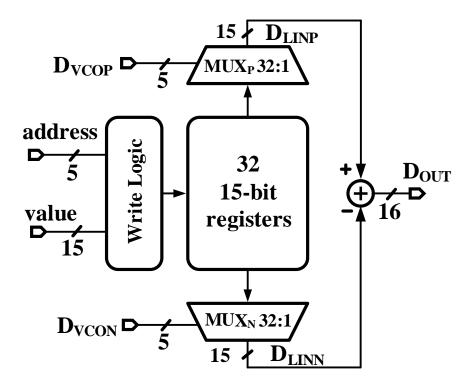

| 5.4  | Simplified block diagram of the proposed calibration unit                                                                                | 64   |

| 5.5  | Simplified block diagram of the pseudo differential VCO-based quantizer.                                                                 |      |

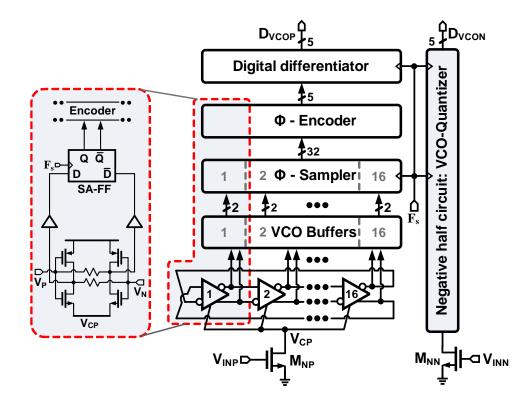

| 5.6  | VCO-based quantizer architecture                                                                                                         | 68   |

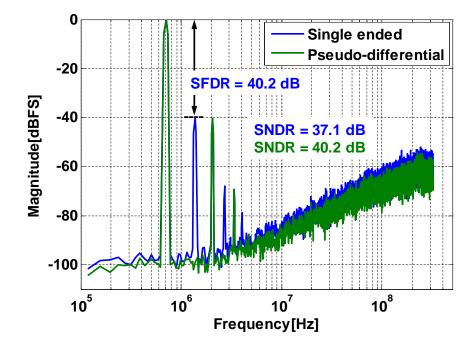

| 5.7  | Simulated output power spectral density of the VCO-based quan-<br>tizer.                                                                 |      |

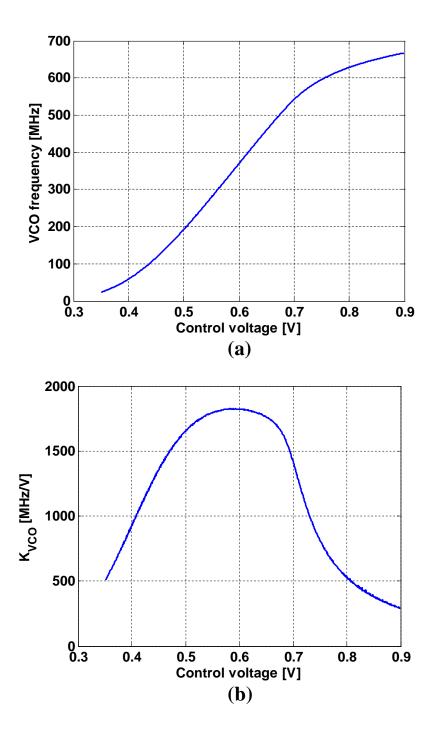

| 5.8  | Simulated VCO characteristics. (a) Voltage to frequency tuning characteristics. (b) VCO gain ( $K_{VCO}$ ) vs. control voltage           |      |

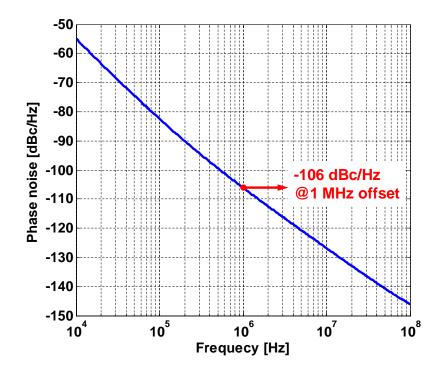

| 5.9  | Simulated VCO phase noise.                                                                                                               | 72   |

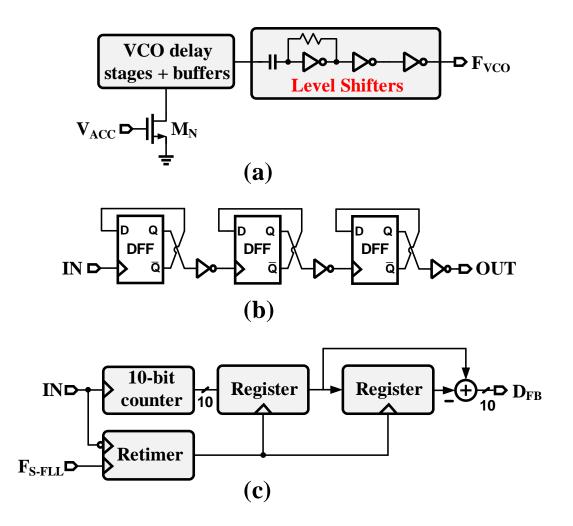

| 5.10 | Blocks in calibration unit feedback path. (a) AC coupled leve<br>shifters. (b) Frequency divider. (c) Frequency detector                 |      |

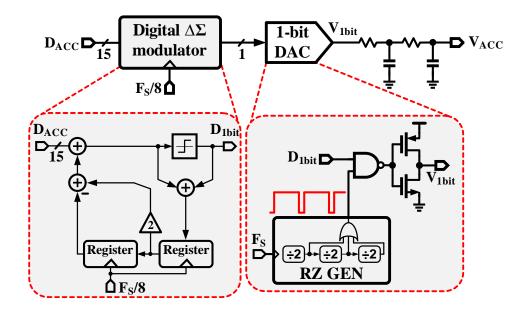

| 5.11 | Schematic of 1-bit $\Delta\Sigma$ DAC                                                                                                    | 74   |

| 5.12 | Implementation of the linearizer.                                                                                                        | 75   |

## LIST OF FIGURES (Continued)

Figure

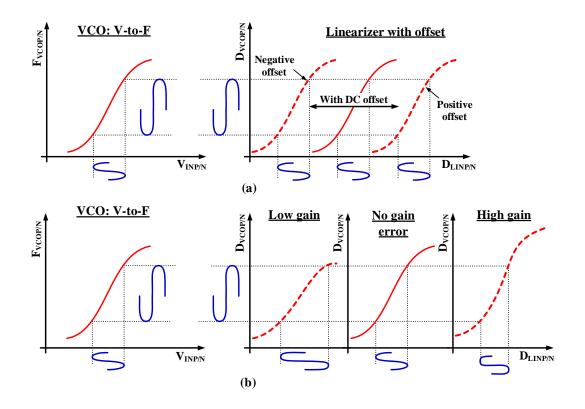

| 5.13 | Effect of mismatch between the VCOs. (a) Manifestation of offset mismatch. (b) Manifestation of gain mismatch.                | 77 |

|------|-------------------------------------------------------------------------------------------------------------------------------|----|

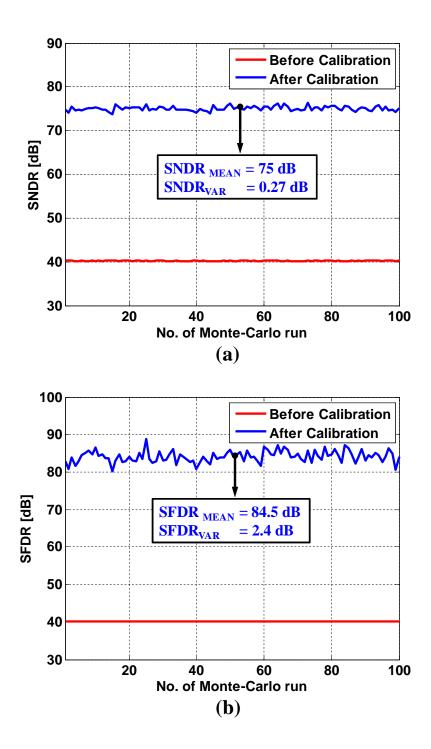

| 5.14 | Monte-Carlo simulation results. (a) SNDR in 5 MHz bandwidth.<br>(b) SFDR in 5 MHz bandwidth.                                  | 78 |

| 5.15 | Dynamic behavior VCO. (a) Schematic of current starved VCO.<br>(b) Approximate small signal model.                            | 79 |

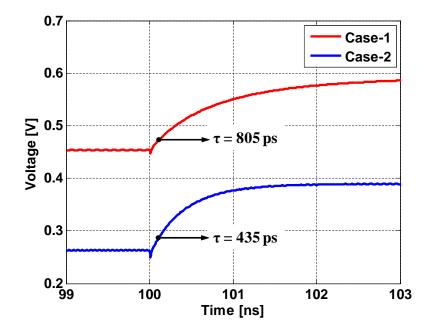

| 5.16 | Voltage settling at the drain node for a step input at 100 ns. $\dots$                                                        | 80 |

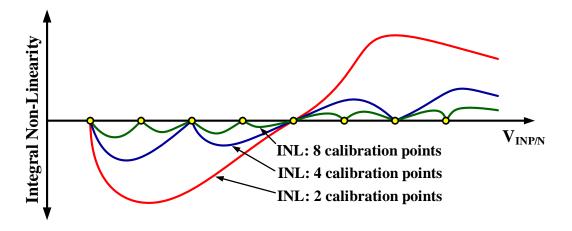

| 5.17 | Effect of finite point calibration on distortion correction                                                                   | 81 |

| 5.18 | Representative integral-non-linearity for different calibration points.<br>82                                                 |    |

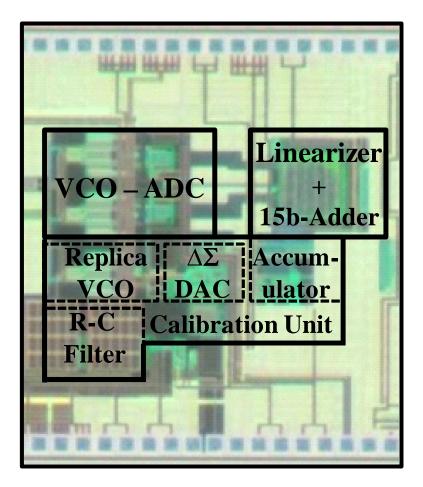

| 5.19 | Die photograph of the proposed ADC                                                                                            | 83 |

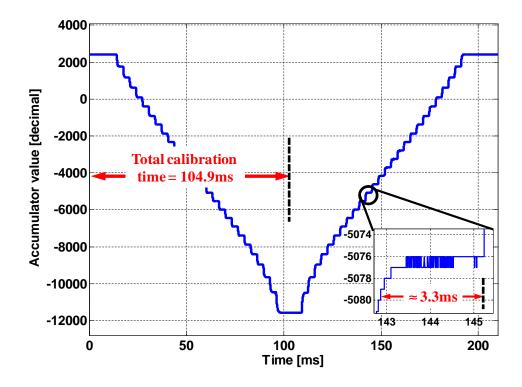

| 5.20 | Measured accumulator output as replica-VCO locks to different frequencies                                                     | 84 |

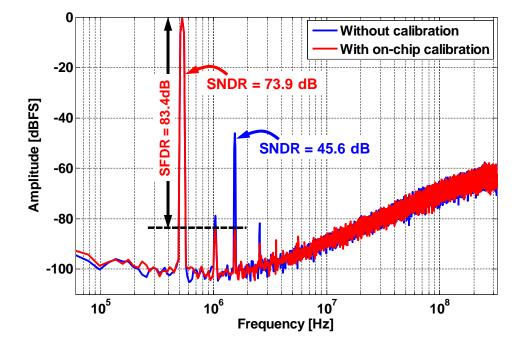

| 5.21 | Measured ADC output power spectral density with and without background calibration.                                           | 85 |

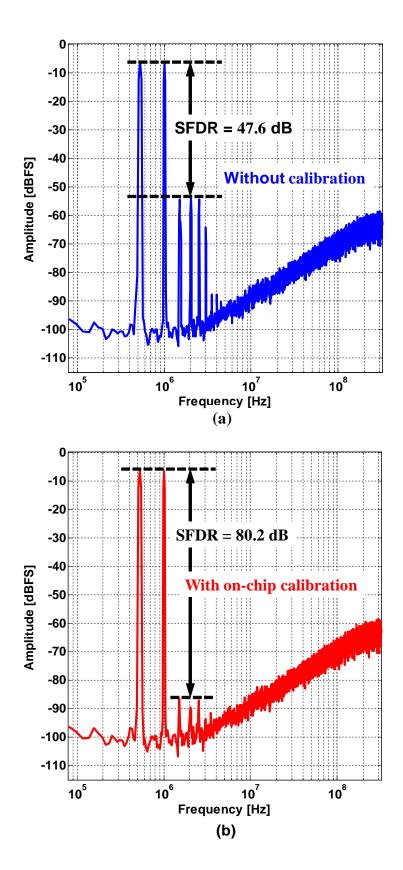

| 5.22 | Measured ADC output power spectral density with two tone in-<br>put. (a) Without calibration. (b) With background calibration | 88 |

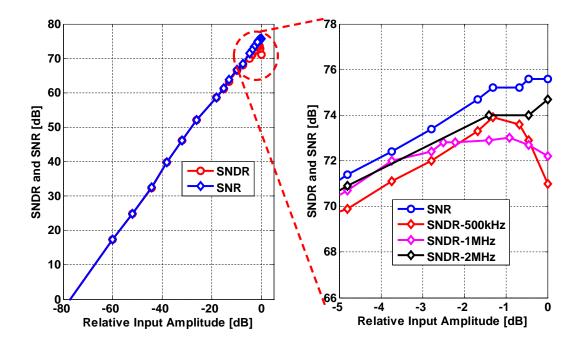

| 5.23 | Measured ADC SNR and SNDR vs. input amplitude                                                                                 | 89 |

## Page

### LIST OF TABLES

| Tab | ble                                              | Pa    | age |

|-----|--------------------------------------------------|-------|-----|

| 4.1 | Performance summary of the operational amplifier | • • • | 50  |

| 4.2 | Performance summary and comparison               | •••   | 59  |

| 5.1 | Performance summary and comparison               |       | 87  |

# LINEARIZING TECHNIQUES FOR VOLTAGE CONTROLLED OSCILLATOR BASED ANALOG TO DIGITAL CONVERTERS

### **CHAPTER 1. INTRODUCTION**

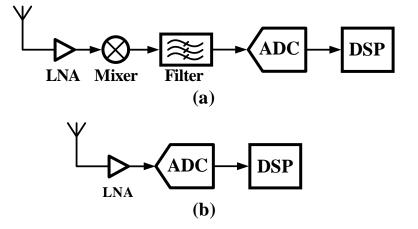

CMOS technology scaling has enabled the integration of very large scale systems on a single chip, where bulk of the signal processing is performed efficiently in the digital domain. However, since the real world signals are analog in nature they need to be converted to the digital domain. This conversion is done using analog to digital converters (ADCs). ADCs thus form the indispensable bridge between the 'real world' and the 'digital world' which exist in almost every electronic system. Figure 1.1(a) shows an example ADC application in a typical radio-frequency (RF) receiver system. The low noise amplifier (LNA), mixer and filter form the RF

Figure 1.1: Simplified architecture of the RF receiver employing ADC. (a) Down converting receiver. (b) Direct sampling receiver.

section of the system which down-convert the received signal to base-band. The ADC then converts the base-band signal to digital domain. Most of the remaining signal processing including decoding, compression, storage etc., is performed in digital-domain using the digital-signal-processor (DSP). Recently in more advanced systems, the RF section is simplified by directly digitizing the received RF signal using a high performance ADC as shown in Fig. 1.1(b). In such systems, entire signal processing including the RF demodulation is performed in the digital domain by a high-speed DSP. To reduce system cost in such applications, it is highly desirable to integrate both the ADC and DSP on a single chip. To reduce system power and improve performance, the DSPs are implemented in the most advanced technology nodes, thereby forcing even the ADCs to be designed in such technology nodes.

### 1.1 Effect of Technology Scaling

As CMOS technology continues to scale, faster and smaller transistors have been realized, which significantly reduce power consumption in digital circuits. However, the transistor's intrinsic gain, headroom and leakage currents have progressively degraded. These factors negatively impact analog circuits such as ADCs, and their power consumption does not scale accordingly. In fact, for a given signal to noise ratio, in a thermal noise limited scenario, the power consumption of analog ciruits is higher in an advanced technology node. This is mainly because of the reduced supply voltage and reduced signal swing [1]. In addition to this, conventional high-performance voltage-domain ADCs, such as pipelined-ADC,  $\Delta\Sigma$ -ADC etc., require high-gain and high-bandwidth operational amplifiers (op-amps) [2]. Due to reduced intrinsic gain and headroom, realizing such high-performance opamps is becoming increasingly difficult. These factors have forced designers to invent new ADC architectures and circuit design techniques that take advantage of technology scaling and reduce power consumption.

Time-domain analog to digital conversion is one such technique that benefits from miniaturization and improved transistor speed. Contrary to conventional voltage domain ADCs which perform voltage quantization, time-domain ADCs perform quantization in time. Therefore, these ADCs take advantage of faster clock and improved time resolution in advanced technology nodes. It can be shown that a time-domain flash ADC consumes relatively much less power when compared with a voltage-domain flash-ADC, especially at higher resolution [3]. Because of these advantages, time-domain ADCs have recently become popular and various such ADC architectures have been invented.

### 1.2 Scope of this work

Among different time-based ADC architectures, voltage controlled oscillator (VCO) based ADCs are very attractive and possess several desirable properties. While retaining all the benefits of other time-based ADCs, VCO-based ADCs achieve high resolution without employing analog building blocks such as op-amps, comparators, precision references etc., which suffer from technology scaling. However, the performance of open-loop VCO-based ADCs are severely distortion limited by the VCO tuning non-linearity. This work focuses mainly on developing new techniques to improve the linearity of VCO-based ADCs. After a brief review of various time-based ADC architectures, advantages and limitations of existing VCO-based ADC architectures are discussed. Two new VCO-based ADC architectures, that overcome the limitations of conventional approaches are presented. Measurement and simulation results are provided to validate both the proposed architectures.

### 1.3 Thesis Organization

The thesis is organized as follows. Chapter 2 discusses various time-domain ADC architectures. Chapter 3 introduces VCO-based ADC and discusses the advantages and limitations of prior-art VCO-based ADC architectures. In Chapter 4, a technique to linearize the VCO-based ADC by operating it at only two points on the tuning curve is presented. A new background calibration scheme is presented in Chapter 5. Finally, Chapter 6 provides a brief summary and concludes this research work.

# CHAPTER 2. TIME DOMAIN ANALOG TO DIGITAL CONVERTER ARCHITECTURES

Time-domain analog to digital converters (ADCs) differ from voltage-domain ADC in that they quantize the input signal using time as the reference quantity. Since quantization is performed in time domain, these ADCs take advantage of improved time resolution in finer technology nodes. Therefore, they have emerged as an attractive alternative to conventional voltage-domain ADCs, especially in the the last few years. Various types of time-domain ADC architectures have been developed over the years. This chapter briefly discusses different time-domain ADC architectures, their advantages, disadvantages and performance limiting factors.

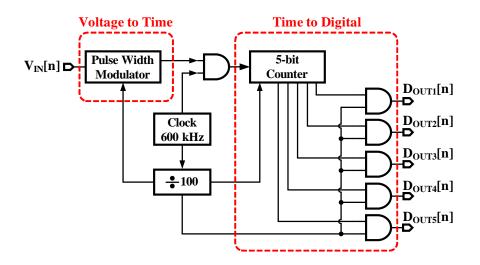

Figure 2.1 shows a simplified version of one of the earliest time-domain ADCs [4, 5]. A pulse width modulator (PWM) produces an output pulse whose width is

Figure 2.1: Simplified block diagram of first patented time-domain ADC.

proportional to the sampled input signal,  $V_{IN}[n]$ . The PWM therefore acts as a

voltage-to-time converter (VTC). The 5-bit counter measures the width of the VTC output pulse by counting total number of clock edges of the 600 kHz clock when the PWM output is 'high' and gives a digital output,  $D_{OUT}[n]$ . The counter thus acts as a time-to-digital converter (TDC). In the above example, since the quantization step corresponds to one time period of the 600 kHz clock, the resolution this ADC is limited by the 600 kHz clock. Due to technology scaling, multi giga-hertz clock frequencies can be realized at relatively low power. The resulting improved time resolution leads to improved ADC resolution.

All time-domain ADCs have the general structure shown in Fig. 2.1 and contain a VTC and a TDC. The VTC converts the input voltage signal to a time signal and the TDC quantizes the time signal to give a digital output. These ADCs differ by employing different VTC and TDC architectures. The rest of the chapter discusses different time-domain ADC architectures. Section 2.1 discusses recent developments in integrating ADCs. Time-domain ADCs that use high-resolution and high-sampling rate TDCs are discussed in Sec. 2.2 followed by a discussion of voltage-to-frequency conversion based ADCs in Sec. 2.3.

### 2.1 Integrating ADC

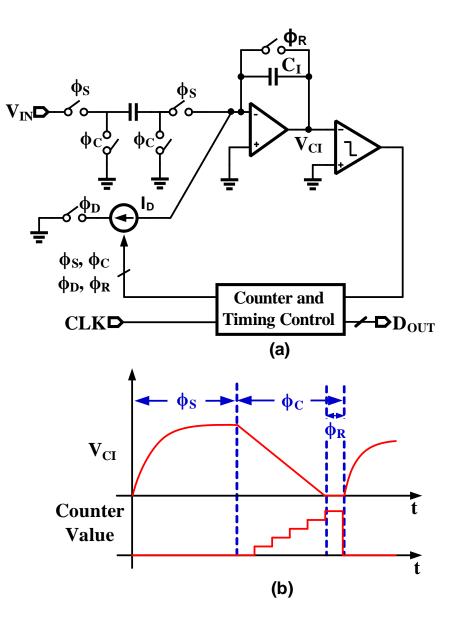

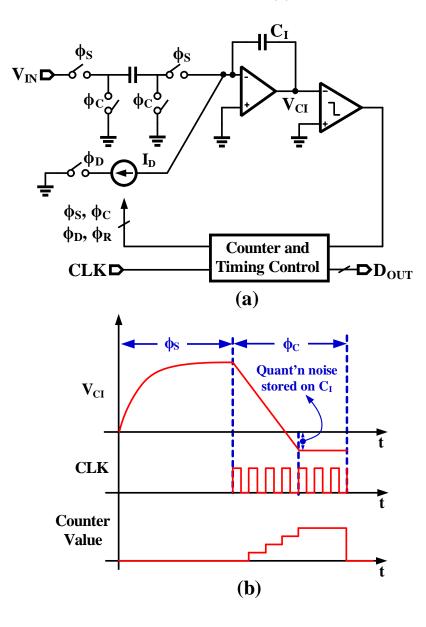

A simple block diagram of a single-slope integrating ADC is shown in Fig. 2.2(a). It's operation is explained with the waveforms shown in Fig. 2.2(b). During the sampling phase,  $\Phi_S$ , the input is sampled on to the integrating capacitor C<sub>1</sub>. In the counting phase,  $\Phi_C$ , the integrating capacitor is discharged with a constant current source, I<sub>D</sub>. The counter is enabled at the beginning of  $\Phi_C$  and it counts till the integrating capacitor is fully discharged. A reset phase is applied to remove any residual charge on the capacitor before the start of next sampling phase. With

Figure 2.2: Single slope ADC. (a) Simplified block diagram. (b) Time domain waveforms.

this operation, the counter value at the end of each count phase is given by,

$$D_{OUT}[n] \frac{T_S I_D}{C_I} = V_{IN}[n] + E_Q[n]$$

$$(2.1)$$

where  $D_{OUT}[n]$  represents the ADC output and  $T_S$  represents period of the counter reference clock, CLK.  $0 \le E_Q[n] < \frac{T_S I_D}{C_I}$  represents the quantization noise.

Though this ADC has a relatively simple implementation it requires a large conversion time. Assuming equal durations for  $\Phi_{\rm S}$  and  $\Phi_{\rm D}$ , the time taken by this ADC to resolve N-bits is given by,

$$T = 2^{(N+1)}T_S$$

(2.2)

which indicates that the conversion time varies exponentially with the desired ADC resolution. Nevertheless, this architecture can be used in low speed applications where monotonic or high-resolution output is desired.

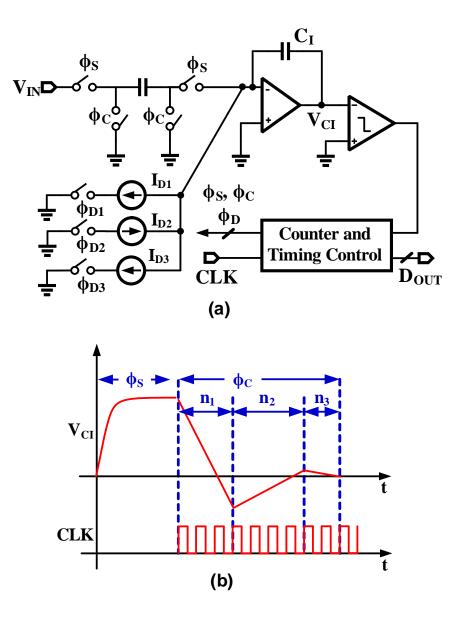

### 2.1.1 Multi-slope Integrating ADC

To improve the conversion time of the single slope ADC, various architectural changes have been employed. Figure 2.3(a) shows the simplified block diagram of a multi-slope ADC [6]. As opposed to the architecture shown in Fig. 2.2, multiple current sources  $I_{D1}$ ,  $I_{D2}$  and  $I_{D3}$ , have been employed in this implementation. The operation can be explained using the waveforms shown in Fig. 2.3(b). During  $\Phi_S$ , the operation is similar to single slope ADC and the input is sampled on to the integrating capacitor  $C_I$ . The count phase,  $\Phi_C$ , begins by enabling current source  $I_{D1}$  which discharges  $C_I$ . Once completely discharged,  $I_{D1}$  is disabled at the next rising edge of the reference clock, CLK. During this time the counter determines the total number of clock edges to give a digital output,  $n_1$ . Since  $I_{D1}$  is disabled only at the rising edge of the reference clock, the quantization noise from this measurement is stored in  $C_I$  as shown in Fig. 2.3(b). Next, in a similar way,  $n_2$ is obtained by measuring the stored quantization noise by enabling  $I_{D2}$ . Since  $I_{D2}$  has smaller magnitude and opposite polarity to that of  $I_{D1}$ , finer resolution is obtained in this step. The above procedure is repeated till all the current sources

Figure 2.3: Multi slope ADC. (a) Simplified block diagram. (b) Time domain waveforms.

are successively enabled and disabled. The resolution of this ADC is  $N = N_1 + N_2 + N_3$ , where  $N_1$ ,  $N_2$  and  $N_3$  are total number of bits resolved by  $I_{D1}$ ,  $I_{D2}$  and  $I_{D3}$ , respectively. The worst case convergence time of this ADC is given by,

$$T = (2^{N_1} + 2^{N_2} + 2^{N_3})T_S$$

(2.3)

which is much smaller than a single-slope ADC. Though multi-slope ADC results in much faster conversion time, the requirement of multiple current sources is an important drawback. Mismatch between these current sources results in nonlinearity and non-monotonic behavior and limits the ADC performance.

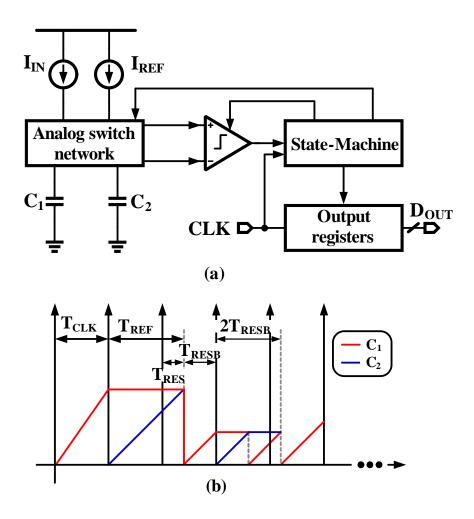

### 2.1.2 Sub-ranging Integrating ADC

Another architecture that improves the conversion time employs sub-ranging techniques [7]. Figure 2.4(a) shows the simplified block diagram of a sub-ranging time-domain ADC. The sub-ranging algorithm is demonstrated with the timedomain waveforms shown in Fig. 2.4(b). An input current, I<sub>IN</sub>, charges the capacitor  $C_1$  for one reference clock period,  $T_{CLK}$ . The counter determines the number of clock cycles taken by a reference current,  $I_{REF}$ , to charge another capacitor  $C_2$  (=  $C_1$ ) to the same voltage as that on  $C_1$ . Once the voltage on  $C_2$  equals to that on  $C_1$ , the counter value, which represents the MSBs, is read and both the capacitors and the counter are reset. Next, by charging  $C_1$  till the end of the next clock edge, the complement of residue,  $T_{RESB}$ , can be stored on  $C_1$ . Each sub-ranging phase involves charging  $C_2$  till its voltage equals that of  $C_1$ , resetting  $C_1$  and charging it again till voltage across it equals that of  $C_2$ . This process amplifies the residue by 2, in time, as shown in Fig. 2.4(b). The number of rising edges of CLK in each sub-ranging phase represents the amplified residue from the previous sub-ranging phase. In the actual implementation of this technique, the time taken to resolve N bits is given by,

$$\mathbf{T} = (5\mathbf{N})\mathbf{T}_{\mathbf{S}} \tag{2.4}$$

Figure 2.4: Subranging time domain ADC. (a) Simplified block diagram. (b) Time domain waveforms.

where the multiplication by 5 comes from a special algorithm used to avoid very small time residues in each sub-ranging phase. Though the above technique greatly reduces the conversion time, it requires a highly linear voltage to current converter to convert input voltage to current,  $I_{IN}$ . Furthermore, the performance is affected by the comparator delay, and charge injection from the switch network.

### 2.1.3 Noise shaping Integrating ADC

With simple modifications to the single-slope ADC shown in Fig. 2.2 quantization noise shaping can be achieved. Figure 2.5(a) shows the modified ADC [8].

Figure 2.5: Noise shaping integrating ADC. (a) Simplified block diagram. (b) Waveforms depicting noise-shaping integrating ADC operation.

Here, instead of disabling the current source immediately after  $V_{CI}$  is completely

discharged, it is disabled at the next rising edge of the reference clock as shown in Fig. 2.5(b). Consequently, the quantization noise is stored in the capacitor  $C_I$ . By avoiding the reset phase for the integrating capacitor, the stored quantization noise can be used in the next clock period to obtain first order noise-shaping [8]. Though good resolution is obtained at a relatively higher speed, compared with other types of time-domain ADCs, these techniques are not suited for very high speed applications.

### 2.2 Delay-line based ADC

The integrating ADCs discussed in the previous section are suitable for high resolution, low speed applications. In applications where high speed, but medium resolution (6 - 10bits) is desired, delay-line based analog to digital converters are used. Architecturally, these ADCs are similar the one shown in Fig. 2.1, but instead of counters, they employ CMOS delay-line based time-to-digital converters (TDC). Such TDCs are also employed in digital phase locked loops (PLLs) to replace the phase frequency detectors. Improvements in the process technology and scaling have led to the development of high-speed, high-resolution and low-power TDCs.

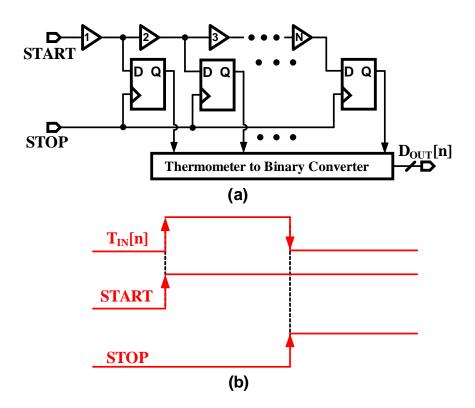

Figure 2.6(a) shows a simple delay-line based TDC that digitizes the time difference,  $T_{IN}[n]$ , between the rising edges of START and STOP signals [9]. The START pulse edge is applied to the delay line and the state of the delay elements is captured at the rising edge of STOP. Since it takes a time,  $\tau_d$ , for the START pulse edge to propagate through one delay element, the captured value in the flip-flops represent a thermometer encoded representation of the input pulse width  $T_{IN}[n]$ .

Figure 2.6: Delay line based TDC. (a) Block diagram. (b) Time domain waveforms.

The TDC output,  $D_{OUT}[n]$ , can be expressed as,

$$T_{\rm IN}[n] = D_{\rm OUT}[n]\tau_{\rm d} + T_{\rm Q}[n]$$

(2.5)

where  $0 \leq T_Q[n] < \tau_d$  represents the quantization noise in time. Since this TDC consists of only inverters and flip-flops and does not require any precision references it is easy to design. Furthermore, since the buffer delay,  $\tau_d$ , reduces with process scaling, the resolution of this TDC improves with technology scaling. When used in an ADC, the START and STOP pulses are generated from a voltage to time converter. A pulse width modulator or an asynchronous  $\Delta\Sigma$  modulator may be used as a voltage to time converter [10].

Though the TDC-ADC discussed above is easy to implement and is scaling friendly, it suffers from two main drawbacks. First, its dynamic range is limited by the number of stages (delay cells) in the delay line. A large dynamic range would require a large number of stages, thereby complicating the design. For example, a 10-bit dynamic range would require as many as 1024 delay elements. Second, ensuring good matching between all these delay elements across PVT corners is a very difficult design task.

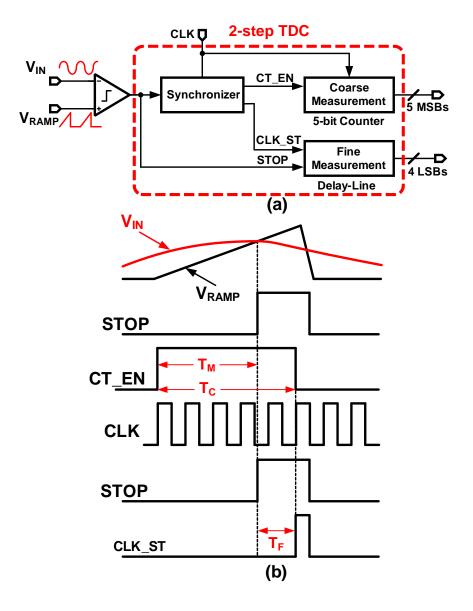

### 2.2.1 Two-step TDC based ADC

The low dynamic-range problem associated with basic TDC discussed in the previous section can be overcome by employing a two-step TDC as shown in Fig. 2.7(a) [11]. The associated time domain waveforms are shown in Fig. 2.7(b). The voltage-to-time conversion is performed by a continuous time comparator by comparing the input to a ramp signal. A 5-bit counter acts as a coarse quantizer and quantizes the time,  $T_C$ , into 5 MSBs. A 32-stage delay line quantizes the time,  $T_F$ , into 4-bit LSBs. The final output is obtained by subtracting the MSBs from the LSBs to get  $T_M = T_C - T_F$ . In order avoid very small  $T_F$ , one additional reference clock (CLK) period is added to both  $T_C$  and  $T_F$ . Since the two times are subtracted after digitization, the added reference clock period cancels and does not have any impact on the final output. By operating the TDC at 400mV supply, the power consumption is limited to only 7  $\mu$ W while operating at 1MHz sampling rate. The power consumption of the entire ADC (including the ramp generator) is 14  $\mu$ W resulting in a figure-of-merit (FOM) of 97 fJ/conv-step.

Figure 2.7: Two-step TDC based ADC. (a) Simplified block diagram. (b) Timing diagram.

## 2.2.2 Oversampling TDC based ADC

Using the two-step TDC architecture, improving the SNDR further would be difficult as the linearity of the voltage-to-time converter and matching between delay-cells would start to limit the performance. In another design approach, the performance of the TDC-ADC has been improved using a  $\Delta\Sigma$  loop as shown in Fig. 2.8 [12]. Since the loop filter high-pass shapes any error introduced in the

Figure 2.8: High resolution TDC-ADC using a  $\Delta\Sigma$  loop.

TDC-ADC, the linearity requirement of the voltage-to-time converter is greatly reduced. For example, since a 3<sup>rd</sup> order loop filter is used in [12], a voltage-totime converter with only 35 dB SNDR is sufficient to achieve an overall SNDR better than 70 dB. Furthermore, since quantization is performed in time-domain, as many as 50 quantization steps can be obtained in the 65nm CMOS process, thereby reducing the quantization noise. The large number of quantization steps would have complicated the feedback DAC design in a conventional  $\Delta\Sigma$  modulator. This problem is circumvented in this design by generating a 1-bit PWM feedback pulse from the TDC. Though the PWM feedback DAC is highly linear due to the absence of multiple elements in the DAC, it imposes a stringent matching requirement (800 fs-rms) on the delay-stages in the TDC that are used to generate the feedback pulse. However, it should be noted that this matching requirement is a result of PWM feedback and not due to the application of TDC-ADC as a quantizer in a  $\Delta\Sigma$  loop.

### 2.3 Voltage-to-Frequency Conversion Based ADC

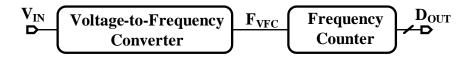

The earliest voltage-to-frequency conversion based ADC (VFC-ADC) was described in a US patent [13]. Figure 2.9 shows a simplified block diagram of one such VFC-ADC [5].

Figure 2.9: Voltage to frequency conversion based ADC.

Voltage to frequency converter is used to convert the analog input to an output frequency,  $F_{VFC}$ . This frequency is converted to digital representation using a frequency counter, which periodically determines the total number of rising edges (pulses) in the VFC output [14]. The digital output,  $D_{OUT}[n]$ , is therefore given by,

$$D_{OUT} \propto F_{VFC} \propto k V_{IN}$$

(2.6)

which indicates that the digital output is proportional to input,  $V_{IN}$ , if the VFC output frequency is proportional to  $V_{IN}$ . Since these ADCs consume very less power and are monotonic, they have been used in telemetry applications where the VFC and frequency counter need not be located physically close to one another.

Traditionally, current steering multi-vibrator based VFCs or charge-balance VFCs have been used to achieve high linearity. Consequently such ADCs had been used in application requiring 12 - 14 bit linearity. However, more recently CMOS based ring-oscillators have been employed to improve resolution and achieve wide bandwidth [15]. Such VFC-ADCs are also known as voltage-controlled-oscillator based ADC (VCO-based ADC). VCO-based ADCs offer a number of advantages over other types of time-domain, and voltage-domain ADCs and therefore are highly desirable. In addition to being scaling friendly, these ADCs obviate the need for a front-end VTC. Furthermore, they achieve excellent resolution by first order noise shaping the quantization noise. In the next chapter, implementation details of a VCO-based ADC, their properties, advantages and limitations are discussed.

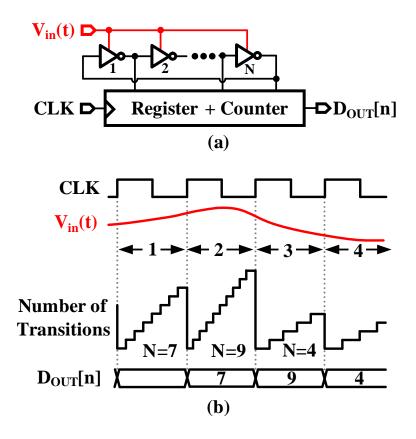

A simplified block diagram of high sampling rate ring VCO-based ADC is shown in Fig. 3.1(a) [15]. The analog input,  $V_{in}(t)$ , controls the delay of each inverter and sets the oscillation frequency of the N-stage ring-oscillator.

Figure 3.1: VCO-based quantizer. (a) Simplified block diagram. (b) Representative waveforms.

The digital output,  $D_{OUT}$ , is obtained from the register and counter by determining the total number of inverters that undergo a transition in each period of the reference clock, CLK. The operation of this ADC can be understood with the waveforms shown in Fig. 3.1(b). During the reference clock period 1, V<sub>in</sub> sets the delay such that seven inverters in the ring-oscillator undergo a transition resulting in  $D_{OUT} = 7$ . During the clock period 2,  $V_{in}$  has increased which reduces inverter delay resulting in nine transitions and therefore  $D_{OUT} = 9$ . Similarly, in the subsequent clock period 3,  $D_{OUT} = 4$ . The digital output during each reference clock period can be expressed as,

$$D_{OUT} = \frac{T_S}{t_d (V_{in})}$$

(3.1)

where  $T_S$  is the reference clock period, and  $t_d (V_{in})$  is the input voltage dependent delay of each inverter. For a simple N-stage ring-VCO shown in Fig. 3.1(a), the oscillation frequency is related to  $t_d (V_{in})$  as,

$$f_{VCO}(V_{in}) = \frac{1}{2Nt_d(V_{in})}$$

(3.2)

Therefore,

$$D_{OUT} = \frac{T_S}{t_d (V_{in})} = 2NT_S f_{VCO} (V_{in})$$

(3.3)

From the above equations,

$$D_{OUT} \propto V_{in} \text{ if, } f_{VCO} (V_{in}) \propto V_{in}$$

(3.4)

which confirms that the digital output indeed represents the analog input. Rigorous analyses of VCO-based ADCs have already been performed by others [15, 16, 17, 18, 19]. In the following sections some important properties will be briefly discussed

## 3.0.1 Quantization noise shaping

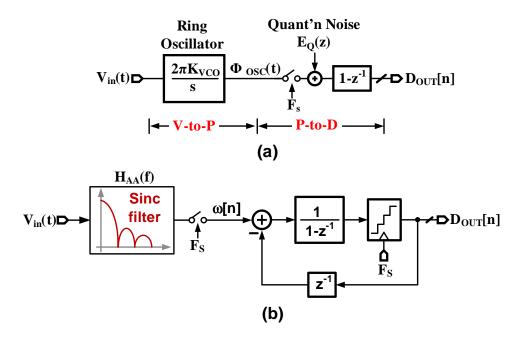

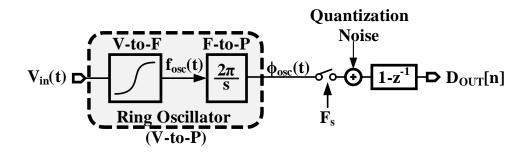

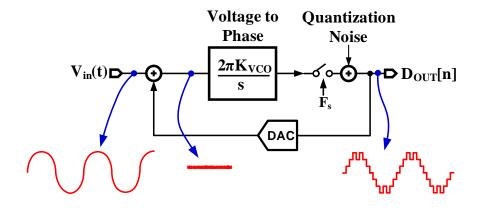

VCO-based ADC provide first-order noise shaping to the quantization error. Consider the simplified functional block diagram shown in Fig. 3.2(a) [16, 17]. Here, the ring oscillator acts as a voltage-to-phase (V-to-P) converter which inte-

Figure 3.2: Modeling of VCO-based ADC. (a) Simplified functional block diagram of VCO-based ADC. (b) VCO-based ADC model with anti-aliasing filter and  $\Delta\Sigma$  modulator.

grates the input voltage to produce an output phase,  $\Phi_{OSC}(t)$ , with a VCO gain  $K_{VCO}$ . The quantizer and digital differentiator model the process of determining the total number of inverters that undergo transition in every period of the reference clock. Since the input voltage sees a continuous time integration and a digital differentiation, there is no net integration or differentiation and the input appears at the output in digital form. However, since the quantization noise,  $E_Q(z)$ , sees only a differentiator, it is first order noise shaped at the ADC output. Consequently, this ADC benefits from oversampling and achieves an excellent resolution.

#### 3.0.2 Anti-aliasing property

It can be shown that the models in Fig. 3.2(a) and Fig. 3.2(b) are mathematically equivalent [19]. Therefore a VCO-based ADC is equivalent to a  $\Delta\Sigma$ modulator with a front-end anti-aliasing filter. The transfer function of this filter is given by,

$$H_{AA}(f) = K_{VCO} e^{-j2\pi T_S f} \frac{\sin(\pi T_S f)}{\pi f}$$

(3.5)

which indicates that the ADC provides first order anti-aliasing to the input signal. Intuitively, in the small signal model shown in Fig. 3.2(a), since sampling is performed after a continuous time integration of the input, aliasing high frequency contents are suppressed relative to the low frequency input signal. Therefore, the ADC provides first order anti-aliasing to the input signal.

#### 3.0.3 Effect of sampler metastability and offset

Compared with a voltage-domain ADCs such as a Flash-ADC, VCO-based ADCs exhibit improved sampler metastability behavior. In a flash-ADC, as the resolution of ADC is increased the voltage swing at the samplers reduce, thereby increasing the probability of metastable behavior. However, in a VCO-based ADC, the voltage swing at the input of the samplers is independent of the ADC resolution. Therefore, the probability of metastable behavior is significantly lower. It can be shown that, a N-bit VCO-based ADC is  $2^{N}$  times less likely to encounter a metastable event [20].

Sampler offsets in a flash ADC changes the reference voltage and results in non-linearity. It can also lead to missing codes in higher resolution ADCs. A VCO-based ADC is robust to such offset errors. Since these errors are introduced in the samplers, the digital differentiator first order noise shapes such errors and improves the ADC performance [18].

#### 3.1 Effect of VCO tuning non-linearity

Though VCO-based ADCs have several desirable properties, their signal to noise and distortion ratio (SNDR) is severely limited by VCO tuning non-linearity. This can be understood with the simplified functional block diagram shown in Fig. 3.3. This model is similar to the one shown in Fig. 3.2(a), but here the V-to-

Figure 3.3: Simplified model of VCO-based quantizer.

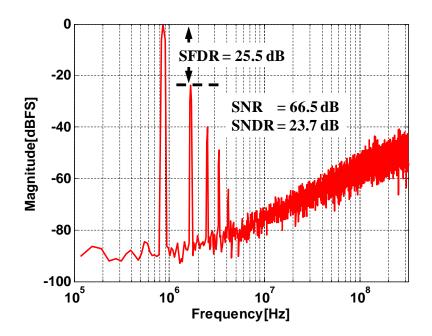

P conversion within the ring-oscillator is divided into two separate steps, voltage to frequency (V-to-F) and frequency to phase (F-to-P) conversions. Since V-to-F transfer characteristic of a ring oscillator is highly non-linear, significant distortion is introduced in the V-to-F conversion. The simulated output spectrum of an open loop VCO-based quantizer with 16 ring-elements is shown in Fig. 3.4. The resulting SNDR and SNR are 23.7 dB and 66.5 dB, respectively, for an over-sampling-ratio (OSR) of 40. Since other error sources such as quantization noise, sampler offset errors etc., are suppressed by the digital differentiator, the V-to-F non-linearity forms the biggest bottleneck in achieving good SNDR from an open VCO-based

Figure 3.4: Output spectrum of open loop VCO-based ADC.

ADC.

# 3.2 Prior-art VCO-based ADC architectures

Various design techniques have already been proposed to overcome the VCO tuning non-linearity and improve the ADC performance. This section briefly discusses such prior-art VCO-based ADC architectures and appreciate their advantages and disadvantages.

## 3.2.1 Linear VCO-based ADC using $\Delta\Sigma$ loop

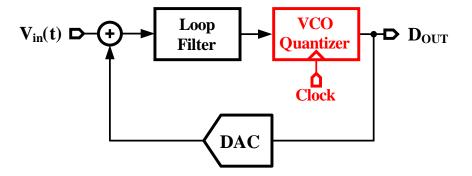

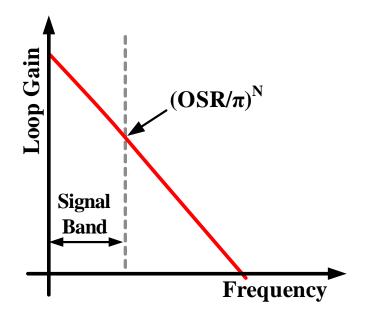

In [17, 21], the VCO quantizer is linearized by placing it inside a continuoustime  $\Delta\Sigma$  loop as shown in Fig. 3.5. The negative feedback loop suppresses the

Figure 3.5: Schematic of VCO-based ADC in a delta sigma loop.

VCO non-linearity approximately by the gain of the loop filter. The improved spurious-free-dynamic-range (SFDR) given by,

$$SFDR_{OUT,CL} \approx \frac{SFDR_{VCO,OL}}{|1 + L(s)|}$$

(3.6)

where  $SFDR_{OUT,CL}$  and  $SFDR_{VCO,OL}$  represent the SFDR with and without the negative feedback loop, respectively, and L(s) is loop filter gain. Though this technique improves the ADC performance, a high order loop filter is required to sufficiently suppress VCO non-linearity. To understand this, consider the typical loop filter gain as a function of frequency as shown in Fig. 3.6. The loop filter gain decreases at higher frequencies and the gain at the band edge, for a loop filter with non optimized zeros, can be approximated as [22],

$$|L(s)| \approx \left(\frac{OSR}{\pi}\right)^{N}$$

(3.7)

which indicates that the problem is especially severe at low OSR. For example, from Eq. 3.6, to improve the SFDR from 25 dB to more than 75 dB the loop

Figure 3.6: Loop filter gain vs. frequency.

filter must provide more than 50 dB gain within the signal-band. A  $3^{rd}$ -order filter would be sufficient to achieve this with an OSR of 40, however with an OSR of 40 a  $4^{th}$  order loop filter would be required [20]. Stabilizing a higher order feedback system poses many challenges and typically incurs a power penalty. Furthermore, even with a high order loop filter, the ADC performance continues to be limited by the VCO tuning non-linearity rather than the quantization noise. For example, the  $2^{nd}$ -order loop filter used in [17] results in a  $3^{rd}$  order noise shaping for the quantization noise. As a result, the peak SNDR is distortion limited to 65 dB even though the peak SQNR is more than 100 dB.

## 3.2.2 VCO-based ADC with phase output

By using VCO phase instead of its frequency as the output quantity, the loop filter requirements are greatly relaxed [23]. Figure 3.7 shows a simple im-

Figure 3.7: Basic structure of VCO-based ADC with phase output.

plementation of one such VCO-based ADC. Here, instead of differentiating the quantized VCO phase, it is directly used as the output quantity and is fed back to the input using a feedback DAC. Therefore, the VCO quantizer behaves like an integrator with large gain within the signal band, thereby minimizing the signal swing at the VCO input. With small signal swing at the VCO input, only a small section of the non-linear tuning is exercised which automatically improves the linearity. Using the basic structure shown in Fig. 3.7, a 4<sup>th</sup>-order continuous time  $\Delta\Sigma$  modulator was realized in [23]. The performance is no longer limited by the VCO tuning non-linearity and the ADC achieved an SNDR of 78 dB in a 20 MHz signal bandwidth.

#### 3.2.3 Residue canceling VCO-based ADC

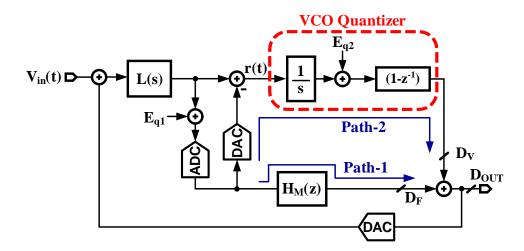

While the architecture in Fig. 3.7 uses feedback, a feed-forward architecture can also be used to minimize the signal swing at the input of the VCO quantizer as shown in Fig. 3.8 [24]. Here, a two-step quantizer is employed such that the

Figure 3.8: Simplified block diagram of residue canceling VCO-based ADC.

VCO-based quantizer process only the residue from the first stage. Consequently, it's input signal swing is minimized leading to a highly linear behavior. Filter,  $H_M(z)$ , ensures that the first stage residue has the same transfer function through the two the paths, thereby canceling it at the final ADC output. Gain mismatch between the two paths is first order noise shaped by the loop filter. Therefore, the final ADC output contains only the shaped quantization noise of the VCO-based quantizer. Using a first order loop filter, second order quantization noise shaping is obtained.

Two-step ADCs with VCO-based ADC at the second stage, similar to the quantizer in [24] have also been proposed in [25, 26]. In [25] a 5-bit flash ADC is used in the first stage followed by a second stage VCO-based ADC. In [26] a 1-1 MASH is realized with a 1<sup>st</sup>-order discrete-time  $\Delta\Sigma$  in the first stage, followed by the VCO based second stage. Furthermore, multi-rate sampling is employed to maximize the benefits of the VCO-based ADC. Though both these techniques mitigate the VCO non-linearity problem by minimizing the voltage swing at the VCO, they are sensitive to variations in the VCO gain across PVT corners [24].

#### 3.2.4 VCO-based ADC with calibration

All the VCO-based ADC architectures discussed so far require a multi-bit feedback digital-to-analog converter (DAC). Since the DAC is in the feedback path, its linearity directly determines the linearity of the entire ADC. Realizing a highly linear, multi-bit DAC is a very challenging design task and increases system complexity and typically incurs a power penalty [27]. Various calibration techniques have been successfully employed for VCO-based ADCs [28, 19, 29]. These techniques perform analog to digital conversion in an open loop manner and obviate the need for a multi-bit DAC.

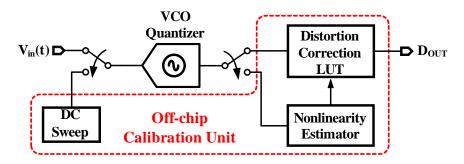

In [28], foreground calibration is employed to correct VCO tuning nonlinearity as shown in Fig. 3.9. When in calibration mode, the ADC is disconnected

Figure 3.9: VCO-based ADC with off-chip foreground calibration.

from the signal path and different DC voltages are applied to its input. Based on

the resulting output the the non-linearity is determined and it is used to correct the output when the ADC is connected back to the signal path. While this technique improves linearity, the calibration is performed off-chip and it requires an accurate external voltage source to perform DC sweep. Furthermore, since calibration is performed in the foreground, this technique is sensitive to PVT variations.

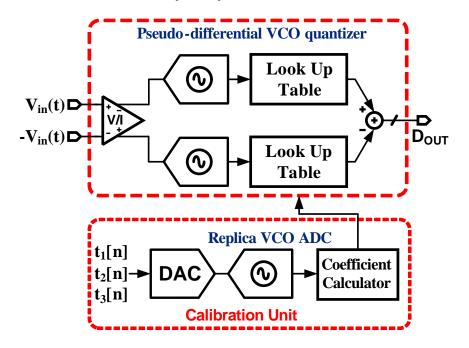

The sensitivity to PVT variations is minimized using statistical background calibration as shown in Fig. 3.10 [19, 29]. Here, a third order polynomial is assumed

Figure 3.10: Block diagram showing background calibration of VCO-based ADC.

to represent the VCO's V-to-F transfer characteristics. Three psuedo-random sequences  $t_1[n]$ ,  $t_2[n]$  and  $t_3[n]$  are applied to a replica VCO, and a calibration unit consisting of multipliers and correlators determine the coefficients of the V-to-F polynomial. The estimated coefficients are used to correct the output of the main VCO quantizer. The first version of this ADC required a high-performance, linear front-end voltage to current (V-to-I) converter which consumed significant power [19]. However, this requirement was overcome in the second version by calibrating even the V-to-I non-linearity [29]. Though this technique effectively improves the ADC performance, the calibration unit corrects only the second and third order harmonic terms. Furthermore, the calibration unit employs a multi-bit DAC which needs to be highly linear.

In the following chapters, two new VCO-based ADC architectures are presented that simplifies the design of linear VCO-based ADCs. In the first approach, the ADC is linearized by operating it at only two points on the non-linear VCO tuning characteristics. The second approach employs a new background calibration technique to linearize the ADC. Both techniques avoid the stability issues associated with a continuous-time  $\Delta\Sigma$  loop and obviate the need for a multi-bit feedback DAC. The implementation details of the first technique are discussed in the next chapter.

# CHAPTER 4. LINEAR VCO-BASED ADC USING TWO LEVEL OPERATION

# 4.1 Proposed Architecture

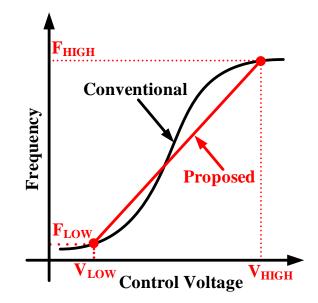

The genesis of the proposed architecture can be explained using the VCO's V-to-F transfer characteristics shown in Fig. 4.1. In a conventional VCO-based

Figure 4.1: Illustration of the basic idea of the proposed architecture.

ADC, the analog voltage input spans the entire non-linear tuning curve which causes frequency output to be severely distorted. We propose to improve the linearity by exercising only two points corresponding to frequencies  $F_{\rm HIGH}$  and  $F_{\rm LOW}$  on the non-linear tuning curve. This two level operation results in a V-to-F

gain given by,

$$K_{\rm VCO,2-level} = \frac{(F_{\rm HIGH} - F_{\rm LOW})}{(V_{\rm HIGH} - V_{\rm LOW})}$$

(4.1)

which is linear. Consequently, the detrimental impact of VCO non-linearity on the ADC performance is eliminated.

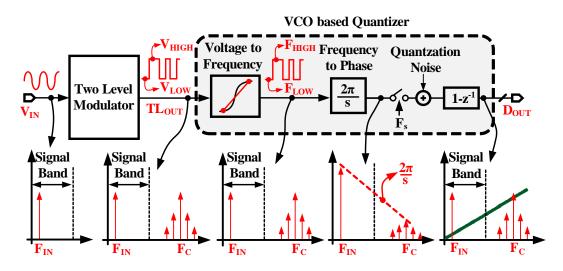

The block diagram of the proposed VCO-based ADC that takes advantage of the two-level operation discussed above is shown in Fig. 4.2 [30]. It consists

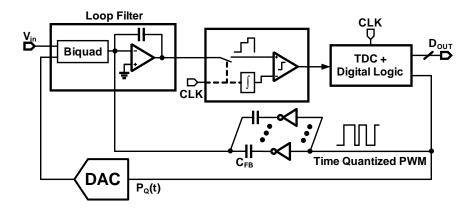

Figure 4.2: Proposed VCO-based ADC architecture.

of a two-level-modulator (TLM) that converts the analog input signal,  $V_{IN}$ , to a two level signal, TL<sub>OUT</sub>. The TLM output drives the tuning port of VCO and forces it to operate at only two frequencies thus, ideally, eliminating the impact of its non-linearity. The phase sampler and the digital differentiator within the VCO quantizer form a frequency-to-digital converter that digitizes the VCO output frequency and generates the ADC output,  $D_{OUT}$ .

The representative spectra in Fig. 4.2 highlight the linear behavior and quantization noise shaping property of the proposed architecture. By an appropriate choice of TLM architecture (see Sec. 4.2), it is ensured that the two-level output contains only the input signal with no other modulation tones in the signal band. Because VCO acts only as a V-to-F converter by mapping  $V_{\text{HIGH}}$  and  $V_{\text{LOW}}$  voltages to  $F_{\text{HIGH}}$  and  $F_{\text{LOW}}$  frequencies, respectively, it does not alter the spectrum of the TLM output. In other words, the spectrum of the VCO output frequency is only a scaled version of the TLM output. Since VCO phase (rather than its frequency) is sampled in a VCO quantizer, the spectrum of the VCO output frequency is integrated. This integration suppresses the high frequency tones relative to the signal and provides anti-aliasing. Quantization of the sampled phase introduces quantization noise. The spectrum at the final ADC output shows that the quantization noise is 1<sup>st</sup>-order shaped due to the digital differentiator. Thus, by operating the VCO at only two levels, a linear VCO-based ADC is realized while retaining its noise shaping properties. The trade-offs and considerations involved with the design of two level modulator and the VCO quantizer are discussed in the following sections.

## 4.2 Two level modulator design considerations

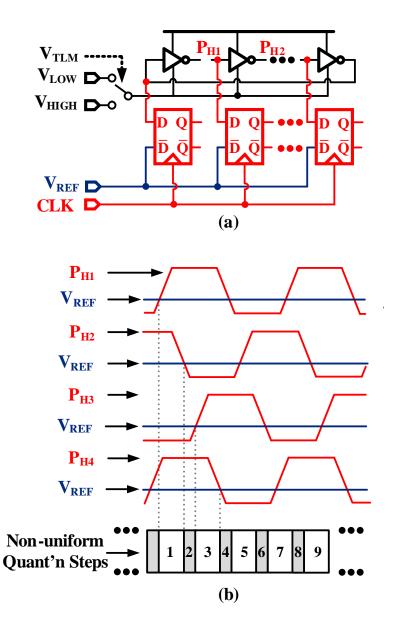

Since the two level modulator is at the front-end of the proposed ADC, it needs to satisfy the linearity requirement of the entire ADC. Pulse width modulation (PWM) is used to realize the two level modulator. While PWM can effectively convert the analog input to a two level signal, the linearity of the pulse width modulated output differs widely depending on whether the input is uniformly sampled or naturally sampled. Next, we will briefly review the distortion performance of the two well known PWM schemes.

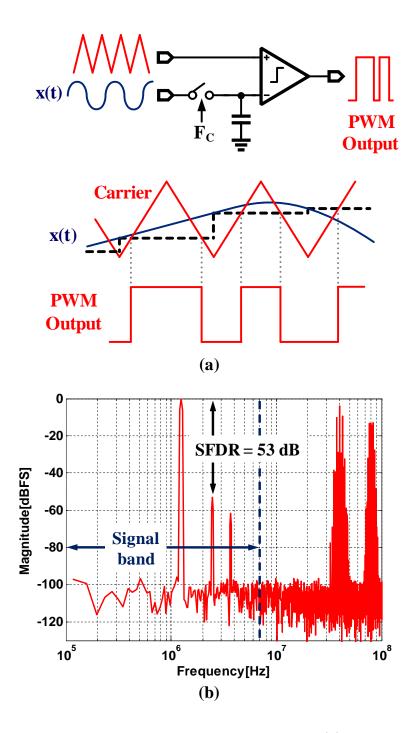

Figure 4.3: Uniform sampling pulse width modulation. (a) Basic block diagram and principle of operation. (b) Output spectrum with sinusoidal input.

Figure 4.3(a) shows a simple pulse width modulator implementation where the input, x(t), is sampled at a rate  $F_C$  and compared with a triangular wave (also called carrier) to produce a two level output [31]. The pulse width of the two level output within each carrier period is proportional to the sampled input,  $x(nT_C)$  i.e.

$$T_{\rm PWM}(n) = \frac{T_{\rm C}}{2} \left(1 - \frac{x_{\rm in}(nT_{\rm C})}{A_{\rm C}}\right)$$

where  $T_{PWM}(n)$  represents the pulse width during n<sup>th</sup> carrier period and  $T_C$  and  $A_C$  represent the carrier period and amplitude, respectively. Since the output pulse width depends on uniformly sampled input, this PWM scheme is called uniform sampling pulse width modulation. While uniform sampling is a linear process, the resulting pulse width modulated output suffers from distortion. Figure 4.3(b) shows the output spectrum for a 1.2 MHz sinusoidal input. Within the signal band, it contains harmonic tones of the input and outside the signal band it contains higher order inter-modulation tones around the carrier frequency and its harmonics. The high frequency inter-modulation tones can be filtered out by a low-pass filter. However, harmonic tones in the signal band degrade SFDR to 53 dB. It is important to note that these harmonic tones are inherent to uniform sampling pulse width modulation and they are not a result of non-ideal circuit behavior [32].

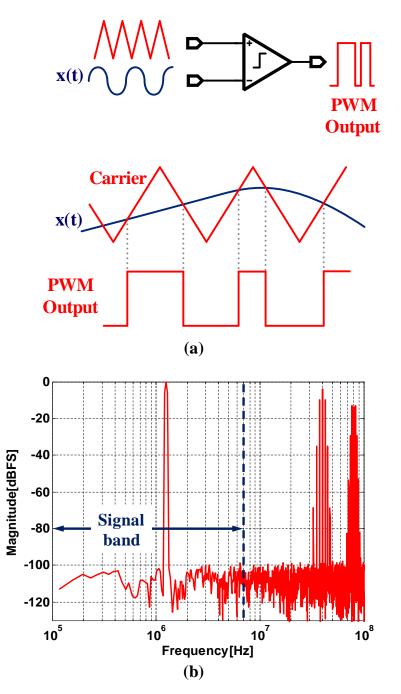

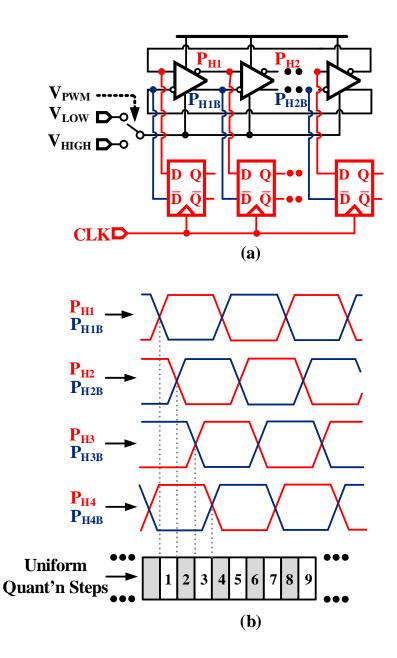

#### 4.2.2 Natural sampling PWM

The inherent non-linearity associated with the above architecture is eliminated by naturally sampling the input signal. Figure 4.4(a) shows a simplified block diagram of a natural sampling pulse width modulator wherein, instead of uniformly sampling the input signal, it is directly compared with the triangular carrier. Since an explicit input sampler is absent, the output pulse width during

Figure 4.4: Natural sampling pulse width modulation. (a) Basic block diagram and principle of operation. (b) Output spectrum with sinusoidal input.

each carrier period depends on instantaneous values of the input when the com-

parator output undergoes a transition, as depicted by the waveforms in Fig. 4.4(a). For a sinusoidal input, the naturally sampled PWM output can be decomposed as (using the general expression derived in [32]),

$$PWM_{OUT,NS}(t) = Msin(2\pi f_{in}t) - \sum_{k=odd} \left(\frac{4}{k\pi} \sum_{n=even} J_n(\frac{k\pi M}{2})cos(2\pi (kF_C + nf_{in}))\right) + \sum_{k=even} \left(\frac{4}{k\pi} \sum_{n=odd} J_n(\frac{k\pi M}{2})sin(2\pi (kF_C + nf_{in}))\right)$$

$$(4.2)$$

where M represents the modulation index equal to the ratio of input signal amplitude to carrier amplitude and  $J_n(x)$  represents the n<sup>th</sup> order Bessel function of 1<sup>st</sup> kind. Equation 4.2 clearly shows that the input harmonic tones are absent in natural sampling PWM output. However, like the uniform sampling PWM, it contains inter-modulation tones at even or odd multiples of  $f_{in}$ , around  $F_C$  and its harmonic frequencies. Though theoretically there are an infinite number of such inter-modulation tones, their magnitude decays rapidly with increasing 'k' and 'n' as governed by the values of the bessel function. Therefore, if  $F_C$  is set high enough, the inter-modulation tones that extend into the signal band correspond to large values of 'n' and have negligible impact on the targeted linearity. The simulated output spectrum for a 1.2 MHz sinusoidal input shown in Fig. 4.4(b) confirms the absence of harmonic tones. Because natural sampling PWM is inherently linear and exhibits better distortion performance, it is employed in this work.

#### 4.2.3 Two level modulator implementation

The natural sampling PWM shown in Fig. 4.4(a) has simple implementation and is inherently linear, however, non-ideal circuit behavior introduces distortion. For example, in the single ended implementation shown in Fig. 4.4(a), the comparator input common mode varies with the amplitude of input signal and the triangular carrier. Consequently, its transition delays become signal dependent re-

Figure 4.5: Block diagram of a fully differential two level modulator.

sulting in distortion. Simulations indicated that the linearity of this single-ended implementation is limited to about 40 dB. Furthermore, the triangular carrier needs to be generated on-chip since providing it from an off-chip source would render this architecture not very useful.

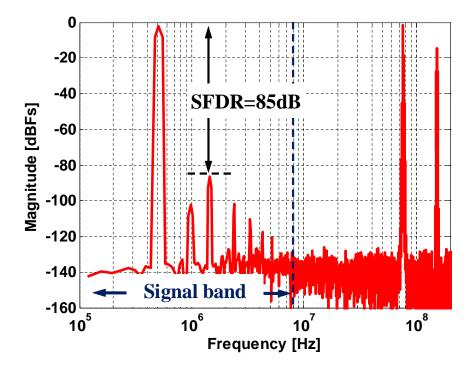

Figure 4.5 shows the complete block diagram of the two level modulator used in the proposed ADC. It consists of a second order loop filter realized with two active-RC integrators, and a comparator. The second integrator along with the comparator realize natural sampling pulse width modulator. Triangular carrier is generated by integrating the square wave carrier clock at the second integrator [33]. Because the implementation is fully differential, the input common mode of the comparator is independent of the input signal. Consequently, atleast to a first order, the comparator transition delays are independent of input signal and the carrier thereby improving the overall linearity. Any residual distortion either due to the comparator or due to non-ideal carrier is suppressed by the loop filter. The simulated transistor level output spectrum, shown in Fig. 4.6, indicates that the linearity of this stage is about 85 dB. The circuit implementation details of the operational amplifiers and comparator are discussed in Section 5.1.

Figure 4.6: Simulated two level modulator output spectrum.

At this point it is important to identify difference between the architecture in Fig. 4.5 and a 2<sup>nd</sup>-order 1-bit continuous time  $\Delta\Sigma$  modulator. The difference lies in the behavior of the last stage in each modulator. The last stage in a  $\Delta\Sigma$  modulator consists of a 1-bit quantizer which would introduce quantization noise. Therefore a large oversampling ratio would be required to push the quantization noise out of the signal band and achieve good signal to noise ratio (SNR). On the contrary, since natural sampling PWM is used in Fig. 4.5, there is no source of quantization noise. Therefore good SNR can be achieved with reasonably low oversampling ratios. For example, while the two level modulator achieves better than 78 dB SNR with an oversampling ratio of 8, the SNR of a 2<sup>nd</sup>-order 1-bit  $\Delta\Sigma$  modulator is limited to only around 40 dB [22]. Obviously, the  $\Delta\Sigma$ - modulator would directly give out digital output, but the two level modulator output needs to be processed by a VCO quantizer to get the digital bits.

#### 4.2.4 Choice of carrier frequency

The choice of carrier frequency,  $F_{\rm C}$ , in Fig. 4.5 is governed both by the characteristics of the two level modulator and the VCO quantizer. For the simple natural sampling PWM (see Fig. 4.4(a)), as discussed  $F_{\rm C}$  should be set high enough such that the magnitude of the inter-modulation tones is negligible within the signal band. In the presence of negative feedback loop around the pulse width modulator as shown in Fig. 4.5, additional distortion terms are introduced [34]. For a given loop filter order, the magnitude of these additional distortion depends on the relative values of signal bandwidth and  $F_{\rm C}$ , such that higher  $F_{\rm C}$  results in lower distortion. These factors set a lower bound on  $F_{\rm C}$ . Simulations indicted that  $F_{\rm C} \geq 75$  MHz is sufficient to achieve better than 75 dB distortion. While the two level modulator sets the lower bound, the upper bound on  $F_{\rm C}$  comes from the characteristics of the VCO-quantizer as discussed in Sec. 4.3.1.

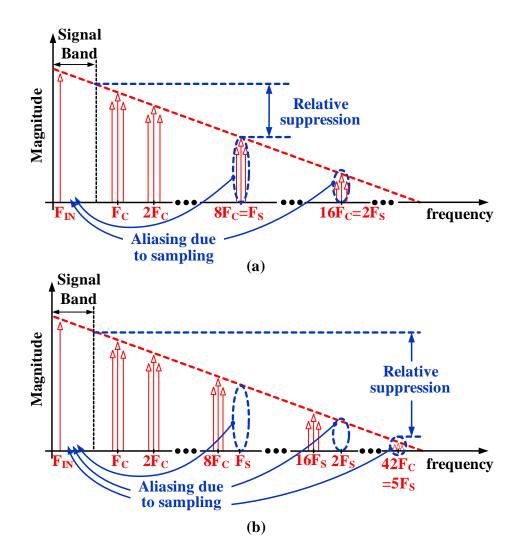

When the two level modulator output is sampled by the VCO quantizer, the inter-modulation tones present around the sampling frequency,  $F_S$ , and its harmonics alias into to the signal band. However, as discussed in Sec. 4.1, since the VCO quantizer samples the VCO phase, high frequency inter-modulation tones are suppressed relative to the signal before being sampled, thereby minimizing the

Figure 4.7: Aliasing of inter-modulation tones. (a) Carrier frequency is harmonically related to sampling frequency. (b) Carrier frequency is harmonically not not related to sampling frequency.

ill-effects of aliasing. Tones at higher frequencies are suppressed to a greater extent as shown in Fig. 4.7(a). If  $F_C$  and  $F_S$  are not harmonically related, the tones that alias into the signal band correspond to very high frequencies and are therefore greatly attenuated. For example, if  $F_C = 80$  MHz and  $F_S = 640$  MHz, intermodulation tones around the 8<sup>th</sup> harmonic of  $F_C$  (= 640 MHz) alias into the signal band as shown in Fig. 4.7(a). However, if  $F_S$  is not an integer multiple of  $F_C$  ( $F_C = 76.2$  MHz,  $F_S = 640$  MHz), the inter-modulation tones that alias into the signal band correspond to 3.2 GHz, which is much higher than the sampling frequency of 640 MHz. Consequently, these tones are attenuated to a greater extent as depicted in Fig. 4.7(b). Thus with the right choice of  $F_C$  and  $F_S$ , benefits due to the anti-aliasing property of VCO-based quantizer can be maximized.

# 4.3 VCO quantizer design considerations

# 4.3.1 VCO quantizer response time

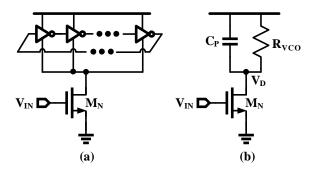

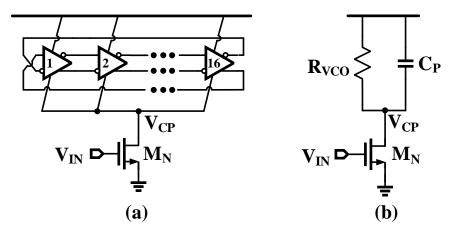

The upper bound on  $F_C$  is set by the speed with which VCO quantizer responds to a two level input. Until now the V-to-F conversion within the VCO is assumed to be instantaneous. However, in practice this conversion takes a finite time due to the limited bandwidth of the VCO. To gain more insight, consider a simple current starved VCO architecture shown in Fig. 4.8(a). The input volt-

Figure 4.8: Current starved VCO. (a) Block diagram. (b) Equivalent model.

age controls the current through transistor,  $M_N$ , which in turn changes oscillation frequency. Figure 4.8(b) shows an equivalent model of the current starved VCO, where  $C_P$  represents the parasitic capacitance at the drain node and  $R_{VCO}$  represents the equivalent resistance looking into the inverter ring. Capacitance  $C_P$  and  $R_{VCO}$  introduce a parasitic pole,  $\omega_p$ , and modify the VCO transfer function to,

$$H_{\rm VCO}(s) = \frac{K_{\rm VCO}}{1 + \frac{s}{\omega_{\rm p}}}$$

(4.3)

and

$$\omega_{\rm P} = \frac{1}{C_{\rm P} R_{\rm VCO}} \tag{4.4}$$

where  $K_{VCO}$  represents the ideal V-to-F transfer characteristic. Pole at  $\omega_p$  sets the VCO bandwidth and modifies its response to the two level input signal as shown in Fig. 4.9. The response of an ideal VCO is depicted in Fig. 4.9(a). The output frequency transitions are instantaneous and the VCO operates only at  $F_{HIGH}$  and  $F_{LOW}$  resulting in the desired linear behavior. Figure 4.9(b) depicts the response of a practical VCO. Due to finite VCO bandwidth, the frequency transitions are not instantaneous and it takes a finite time for the output frequency to transition from  $F_{HIGH}$  to  $F_{LOW}$  and vice-versa. During time period 1, the input pulse width is wide enough for the VCO to complete the transition. However, during time period 2, due to the narrow input pulse, the VCO fails to reach  $F_{HIGH}$  and the final operating point depends on the input pulse width. Thus, depending on the input pulse width, different points on the  $K_{VCO}$  curve are excited leading to non-linear behavior. The linearity improvement of the proposed ADC therefore depends on the relative magnitudes of VCO bandwidth,  $\omega_{\rm p}$ , and the minimum input pulse width,  $T_{MIN}$ . For the proposed two level modulator with sinusoidal input,  $T_{MIN}$  is given by

$$T_{\rm MIN} = \frac{T_{\rm C}}{2} \left( 1 - \frac{A_{\rm IN}}{A_{\rm C}} \right) \tag{4.5}$$

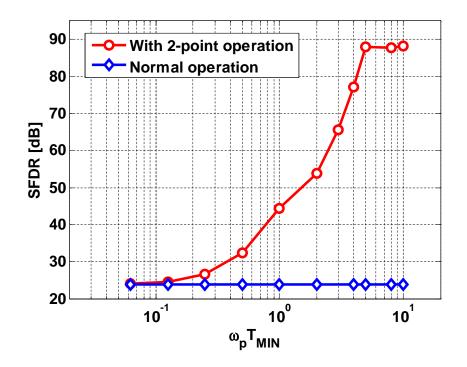

where  $A_{IN}$  and  $A_C$  represent the amplitudes of the input and the carrier, respectively and  $T_C$  represents the carrier period. The simulated SFDR as a function of the product  $\omega_P T_{MIN}$  is shown in Fig. 4.10. For very small  $\omega_P T_{MIN}$ , since the VCO output frequency fails to reach the desired final value in every carrier period,

Figure 4.9: VCO response to a two level input. (a) Ideal VCO response. (b) Practical VCO response.

the linearity degrades to that of a conventional open loop VCO quantizer. The linearity improves as  $\omega_{\rm P}$  is increased with respect to  $T_{\rm MIN}$  and to achieve an SFDR better than 75 dB,  $\omega_{\rm P} > (4/T_{\rm MIN})$  is required. From Eq. 4.5, for  $F_{\rm C} = 80$  MHz and -1.5 dB input, the required VCO bandwidth is about 650 MHz. If  $F_{\rm C}$  is increased, the required VCO bandwidth also increases, thus setting the upper bound on  $F_{\rm C}$ .

Figure 4.10: Simulated SFDR vs.  $\omega_{\rm P} T_{\rm MIN}$ .

# 4.3.2 VCO quantizer architecture

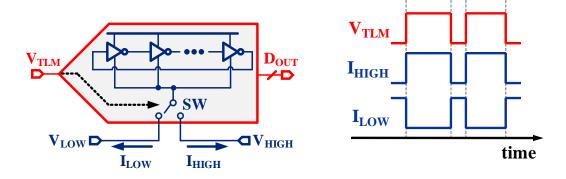

Wide bandwidth VCO can be realized by directly switching the supply voltage of the inverter ring as shown in the Fig. 4.11. When the input is high,  $V_{HIGH}$

Figure 4.11: Schematic and waveforms for a single ended wide bandwidth VCO.

is connected to the ring oscillator and when it is low,  $V_{LOW}$  is connected to the oscillator. The signal path pole,  $\omega_p$ , for this VCO is given by,

$$\omega_{\rm P} = \frac{1}{C_{\rm P}(R_{\rm VCO}||R_{\rm SW})} \tag{4.6}$$

where  $R_{SW}$  represents the switch resistance. By reducing the switch resistance,  $R_{SW}$ , the bandwidth can be maximized. The representative waveforms, for currents  $I_{HIGH}$  and  $I_{LOW}$  drawn from  $V_{HIGH}$  and  $V_{LOW}$ , respectively, are also shown in Fig. 4.11, indicating that the currents have the same profile as the input two level voltage signal. The sharp  $I_{HIGH}$  and  $I_{LOW}$  current pulses impose stringent speed and slewing requirements on the buffers that drive  $V_{HIGH}$  and  $V_{LOW}$ .

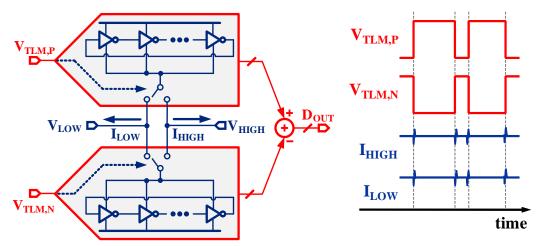

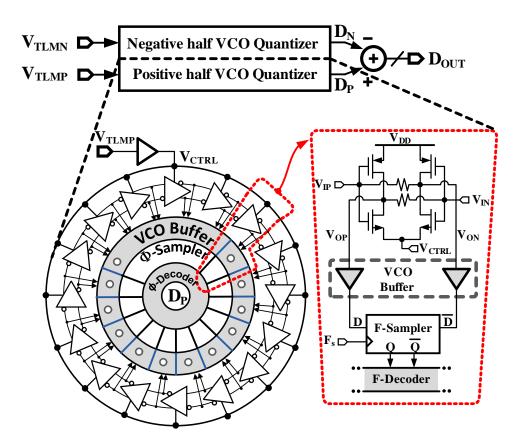

The high speed and slewing requirements are relaxed using a pseudo-differential quantizer architecture as shown in Fig. 4.12. The positive and negative half cir-

Figure 4.12: Schematic and waveforms for a pseudo-differential wide bandwidth VCO.

cuits process the complimentary two level signals denoted by  $V_{TLM,P}$  and  $V_{TLM,N}$ , respectively. The digital outputs from the positive and negative half circuits are subtracted to get the final output,  $D_{OUT}$ . Since the two level input signals are complimentary,  $V_{HIGH}$  and  $V_{LOW}$  are always connected to one of the two half circuits. Therefore, to an extent that the two half-circuits match, currents  $I_{HIGH}$  and  $I_{LOW}$  remain constant thereby relaxing the speed and slewing requirements on the  $V_{HIGH}$  and  $V_{LOW}$  buffers. Other benefits of pseudo-differential architecture include improved SNR and linearity. Since the signal in each half circuit is correlated, signal power at the ADC output increases by 6 dB. However, due the random nature of noise, the noise power increases by only 3 dB. This results in a net 3 dB improvement in SNR at the ADC output. Furthermore, since the half circuits processes complimentary signals, the even order harmonic terms from each half circuit cancel at the final ADC output resulting in improved linearity.

# 4.4 Circuit Design Details

## 4.4.1 Operational amplifier and comparator

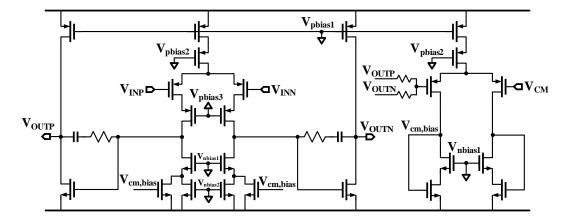

The circuit design details of the loop filter and comparator used in the two level modulator (TLM) are discussed here. The TLM loop filter is implemented with two active-RC integrators since they achieve better linearity than a  $G_M - C$ integrator. Figure 4.13 shows the operational amplifier used in the active-RC

Figure 4.13: Opamp architecture used in NSPWM.

integrator. It employs a two stage Miller compensated architecture wherein the output common mode is set by controlling the current through the first stage. The

| Supply Voltage       | 1.3 V             |

|----------------------|-------------------|

| DC Gain              | $62 \mathrm{~dB}$ |

| Unity Gain Bandwidth | 1.4 GHz           |

| Power                | 0.9 mW            |

Table 4.1: Performance summary of the operational amplifier

performance of the operational amplifier is summarized in Table 4.1.

The comparator architecture is shown in Fig. 4.14. It consists of two gain

Figure 4.14: Comparator architecture used in NSPWM.

stages. The first stage acts as a pre-amplifier and provides additional gain which helps improve the sensitivity of the comparator. The second stage output is passed through inverters to obtain rail-to-rail output swing. Operating from a 1.3 V supply and with 80 MHz carrier frequency, the comparator consumes about 0.3 mW power.

#### 4.4.2 VCO phase sampler

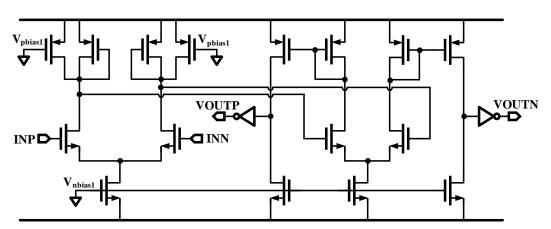

Phase samplers are used within the VCO quantizer to sample and quantize the VCO phase. Figure 4.15(a) shows a conventional implementation where the ring-VCO phases denoted by  $P_{H1}$ ,  $P_{H2}$  etc., are sampled by an array of senseamp flip-flops [23]. Here, quantization is performed by comparing these phases to a reference voltage,  $V_{REF}$ . If  $V_{REF}$  is not at the center of the voltage swing of the VCO phases, it results in non-uniform quantization steps [19]. This is elucidated with the waveforms in Fig. 4.15(b), where phases  $P_{H1}$ ,  $P_{H2}$ ,  $P_{H3}$  and  $\mathrm{P}_{\mathrm{H4}}$  corresponding to four consecutive delay stages in the ring-VCO. Since  $\mathrm{V}_{\mathrm{REF}}$  is at the lower half of the phase swing, the quantization steps arising from the phases going low, such as  $P_{H2}$  and  $P_{H4}$  are wider than the quantization steps arising from the phases going high such as  $P_{H1}$  and  $P_{H3}$ . In practice, since the voltage swing at these phases varies with the input signal, it is difficult to set  $V_{REF}$  at the center. Though error due to non-uniform quantization is first order noise shaped by the digital differentiator that follows the phase sampler, it can be eliminated with an improved phase sampler. Figure 4.16(a) shows the improved phase sampler used in this design. Instead of inverters, pseudo-differential delay cells are used in the ring VCO. Furthermore,  $V_{\text{REF}}$  is eliminated by feeding the sense-amp flipflops with complimentary phases available from the pseudo-differential delay cells. Since in this implementation quantization steps are defined by two complementary phases, the resulting quantization steps are uniform as depicted by the waveforms in Fig. 4.16(b).

Figure 4.15: Conventional phase sampler. (a) Simplified block diagram. (b) Phase waveforms depicting non-uniform quantaization steps.

# 4.4.3 Complete VCO Quantizer

Figure 4.17 shows the complete VCO quantizer architecture. As discussed earlier, it consists of two identical half circuits each digitizing complimentary two

Figure 4.16: Proposed pseudo-differential phase sampler. (a) Simplified block diagram. (b) Phase waveforms depicting uniform quantization steps.