# AN ABSTRACT OF THE THESIS OF

<u>Chao Ma</u> for the degree of <u>Master of Science</u> in <u>Electrical and Computer Engineering</u> presented on <u>September 13, 2012</u>.

Title: <u>Energy-Efficient Clock Generation for Communication and Computing</u> <u>Systems Using Injection Locking.</u>

Abstract approved:

Patrick Y. Chiang

The design of high-performance, high-speed clock generation and distribution becomes challenging in terms of phase noise, jitter and power consumption, due to the fast development of communication and computing systems. Injection locking is a promising clocking technique since it can significantly improve the energy efficiency, suppress the phase noise of the ring oscillator, enable a fast startup and conveniently generate multiple time-interleaved phases.

A quasi-linear model of injection-locked ring oscillator (ILRO) is utilized to mathematically formulate the frequency and time domain characteristics of the system, as well as the phase noise shaping and jitter tracking behavior. The settling behavior of ILRO is also exploited and shows a strong dependence on the locking range and the initial phase difference of the injected and the resultant oscillation signals.

A forwarded-clock synchronization based on injection locking is designed for a 10 Gb/s photonic interconnect according to the specific features of optical links. A single clock recovery can be used for all the four channels, resulting in a large amount of power and area saving. The applications of sub-harmonic and super-harmonic injection locking in wireless communications for frequency multiplying and division are also discussed.

©Copyright by Chao Ma September 13, 2012 All Rights Reserved

# Energy-Efficient Clock Generation for Communication and Computing Systems Using Injection Locking

by Chao Ma

# A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Presented September 13, 2012 Commencement June 2013 Master of Science thesis of Chao Ma presented on September 13, 2012

APPROVED:

Major Professor, representing Electrical and Computer Engineering

Director of the School of Electrical Engineering and Computer Science

Dean of the Graduate School

I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request.

Chao Ma, Author

#### ACKNOWLEDGEMENTS

I really appreciate that there are always lots of people helping and supporting me in my life. Without them, it would be impossible for me to finish this thesis. I would like to express my sincere appreciation to my advisors, the VLSI research group members, friends, and family.

First, I would like to thank my major advisor, Prof. Patrick Y. Chiang for the opportunity to study in his group. I am always inspired by his broad knowledge, great ideas, and infinite passions for academic research. What I leaned is beyond the specific major, which are the foreseeing and global visions, critical analysis and how to collaborate with each other. His advice will definitely influence my career and whole life.

Secondly, I would like to extend my gratitude to Prof. Sam Palermo of Texas A&M University for his advice on joint projects. I would like to thank Prof. Gabor C. Temes and Prof. Huaping Liu for being in my academic committee, and their valuable advices on my coursework and oral exam. I also want to thank Prof. Pavan K. Hanumolu, Prof. Karti Mayaram, and Prof. Un-Ku Moon for their great helps in and after classes. I am grateful to Prof. Merrick C. Haller for taking the time to serve as graduate council representative.

I would like to thank the group members, Lingli Xia, KangMin Hu, Changhui Hu, Nariman Moezzi, Tao Jiang, Jacob Postman, Rui Bai, Jiao Cheng, Joe Crop, Robert Pawlwski, Ben Goska, Ryan Albright, Thomas Ruggeri and Sam House, for the help and collaboration. I also want to thank my friends, Fanghui Ren, Fang Yuan, Weiyang Li, Ce Cheng, and others who have been spending the excellent time with me.

Finally, I would like express the deepest gratitude to my family members for their love and support, especially my parents and boyfriend. No matter where I am, they are always with me.

# TABLE OF CONTENTS

Page

| CHAPTER 1. INTRODUCTION                                     | 1  |

|-------------------------------------------------------------|----|

| 1.1 Clocking in Communication and Computing Systems         | 1  |

| 1.1.1 Clocking for Wireline Communications                  | 4  |

| 1.1.2 Clocking for Wireless Communications                  | 5  |

| 1.2 Design Considerations                                   | 6  |

| 1.2.1 Jitter                                                | 6  |

| 1.2.2 Phase Noise                                           | 7  |

| 1.2.3 Deskewing and Multi-Phase Generation                  |    |

| 1.2.4 Power Consumption                                     | 9  |

| 1.2.5 Motivation of Injection-Locked Ring Oscillator (ILRO) | 9  |

| 1.3 Thesis Organization                                     | 10 |

| CHAPTER 2. RING OSCILLATOR                                  |    |

| 2.1 Introduction                                            | 12 |

| 2.2 Type of Ring Oscillator                                 | 15 |

| 2.2.1 Sing-Ended Signal Ring Oscillator                     | 15 |

| 2.2.2 Differential Ring Oscillator                          | 17 |

| 2.2.3 Pseudo-Differential Ring Oscillator                   | 19 |

| 2.3 Phase Noise and Jitter of Ring Oscillator               |    |

| 2.4 Design Considerations of Ring Oscillator                |    |

| 2.4.1 Frequency                                             | 25 |

| 2.4.2 Phase Noise                                           |    |

# TABLE OF CONTENTS (Continued)

| 2.5 Summary                                                         | <u>Page</u><br>29 |

|---------------------------------------------------------------------|-------------------|

| CHAPTER 3. INJECTION LOCKING                                        | 30                |

| 3.1 Introduction                                                    | 30                |

| 3.2 Modeling of Injection Locking                                   | 31                |

| 3.3 Phase Noise and Jitter of Injection-Locked Ring Oscillator      | 35                |

| 3.3 Fast Wakeup                                                     | 40                |

| 3.4 Harmonic Injection Locking                                      | 43                |

| 3.4.1 Implementation in Wireless Transmitter                        | 44                |

| 3.4.2 Implementation in Wireless Receiver                           | 47                |

| 3.5 Summary                                                         | 49                |

| CHAPTER 4. PHOTONIC FORWARDED-CLOCK INTERCONNECT                    |                   |

| SYNCHRONIZATION USING INJECTION-LOCKED RING OSCILLATOR              | 51                |

| 4.1 Introduction                                                    | 51                |

| 4.2 Photonic Interconnect Features                                  | 54                |

| 4.2.1 Photodiode                                                    | 55                |

| 4.2.2 Optical Front-End                                             | 57                |

| 4.3 Architecture of Optical Clock Receiver                          | 59                |

| 4.3.1 Current-Integrating Clock Receiver with Super-Harmonic Inject | ction             |

| Locking                                                             | 60                |

| 4.3.2 Proposed Architecture                                         | 62                |

| 4.4 Circuit Implementations                                         | 64                |

# TABLE OF CONTENTS (Continued)

|                                         | Page |

|-----------------------------------------|------|

| 4.4.1 TIA and Limiting Amplifier        | 64   |

| 4.4.2 Single-to-Differential Converter  | 65   |

| 4.4.3 ILRO                              | 67   |

| 4.4.4 Other Building Blocks for Testing | 69   |

| 4.5 Results                             | 69   |

| 4.6 Summary                             | 75   |

| CHAPTER 5. CONCLUSION                   | 77   |

| Bibliography                            | 80   |

# LIST OF FIGURES

| <u>Figure</u> <u>Page</u>                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.1. NoC projections about number of cores and per-channel I/O bandwidth2                                                    |

| Figure 1.2. NoC projections about (a) on-chip and (b) off-chip clock frequency 3                                                    |

| Figure 1.3. Clocking in a basic electrical link                                                                                     |

| Figure 1.4. Time-division multiplexing in a serial link                                                                             |

| Figure 1.5. Clocking in a typical wireless transceiver                                                                              |

| Figure 1.6. Illustration of the clock jitter                                                                                        |

| Figure 1.7. Illustration of the phase noise: (a) typical profile and (b) its effects on producing the adjacent channel interference |

| Figure 2.1. Simplified ring oscillator model                                                                                        |

| Figure 2.2. Unity-gain negative feedback system                                                                                     |

| Figure 2.3. Delay cell of the ring oscillator with single-ended signal structure 15                                                 |

| Figure 2.4. "Current-starved" delay cell of ring oscillator                                                                         |

| Figure 2.5. Ring oscillator with differential structure and even number of stages 18                                                |

| Figure 2.6. Delay cell of a differential ring oscillator with symmetric loads                                                       |

| Figure 2.7. Pseudo-differential ring oscillator with (a) odd stages and (b) even stages.                                            |

| Figure 2.8. Pseudo-differential delay cell with (a) cross-coupled load and (b) cross-<br>coupled input stage                        |

| Figure 2.9. Delay modulation of pseudo-differential signals                                                                         |

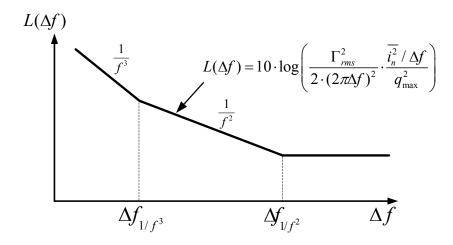

| Figure 2.10. Modeled single-sideband phase noise spectrum                                                                           |

| Figure 2.11. Frequency tuning of a current-starved ring oscillator with supply voltage.                                             |

| Figure 2.12. Phase noise of a current-starved ring oscillator with different power consumption                                      |

# LIST OF FIGURES (Continued)

| Figure                                                                                                                                         | <u>Page</u> |

|------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Figure 2.13. Phase noise of a current-starved ring oscillator at different supple vo                                                           | -           |

| Figure 3.1. Model of first-harmonic injection locking                                                                                          | 32          |

| Figure 3.2. Phase noise of a ring oscillator with and without injection locking                                                                | 39          |

| Figure 3.3. Injection-locked ring oscillator                                                                                                   | 39          |

| Figure 3.4. Settling behavior of ILRO with different locking ranges                                                                            | 41          |

| Figure 3.5. Settling behavior of ILRO with different initial phase difference betwee the resultant oscillation signal and the injected signal. |             |

| Figure 3.6. Model of super-harmonic injection locking.                                                                                         | 44          |

| Figure 3.7. Schematic of the sub-harmonic injection-locked oscillator                                                                          | 45          |

| Figure 3.8. Phase noise with and without injection locking at VDD=0.6V, 1V for ILFM.                                                           |             |

| Figure 3.9. 5-stage ring oscillator based ILFD.                                                                                                | 48          |

| Figure 4.1. A WDM photonic interconnect.                                                                                                       | 52          |

| Figure 4.2. One channel of an embedded-clock architecture                                                                                      | 53          |

| Figure 4.3. Equivalent electrical model of a reverse-biased photodiode                                                                         | 56          |

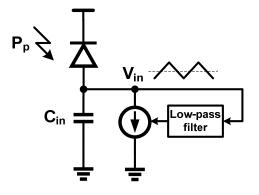

| Figure 4.4. Current-integrating clock receiver front-end.                                                                                      | 58          |

| Figure 4.5. TIA based clock receiver front-end.                                                                                                | 59          |

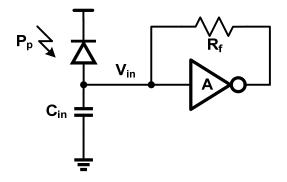

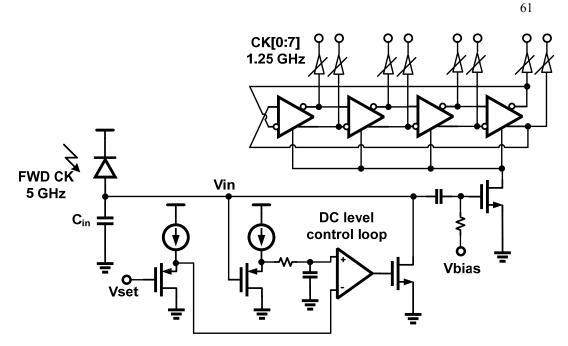

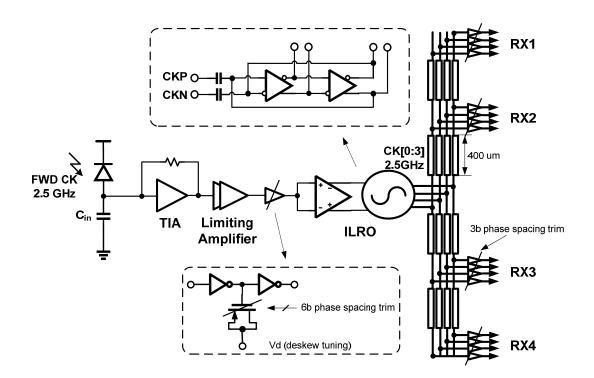

| Figure 4.6. Current-integrating clock receiver with super-harmonic injection lock                                                              | -           |

| Figure 4.7. TIA based clock receiver with first-harmonic injection locking                                                                     | 63          |

| Figure 4.8. Single-to-differential conversion with CML buffer.                                                                                 | 65          |

| Figure 4.9. Proposed single-to-differential conversion with transmission gate                                                                  | 66          |

# LIST OF FIGURES (Continued)

| <u>Figure</u>                                                                                                                                                                                                                              | Page |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 4.10. Monte Carlo simulation of duty cycle caused by single-to-differential conversion: (a) 100 runs of transient simulations and (b) distributions of half-cycle the output ( $\mu = 201.2 \text{ ps}, \sigma = 1.1 \text{ ps}$ ). | of   |

| Figure 4.11. Schematic of ILRO.                                                                                                                                                                                                            | 67   |

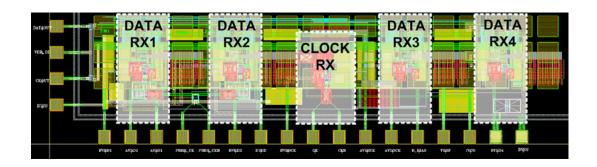

| Figure 4.12. Layout of (a) the whole receiver bank and (b) the clock receiver                                                                                                                                                              | 70   |

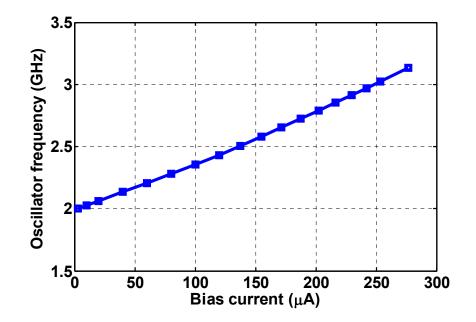

| Figure 4.13. Frequency tuning of ILRO with bias current                                                                                                                                                                                    | 71   |

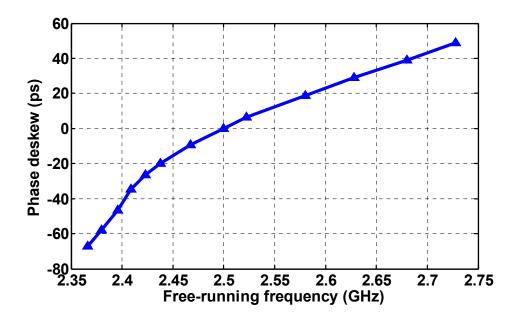

| Figure 4.14. Deskewing of ILRO by tuning free-running frequency.                                                                                                                                                                           | 72   |

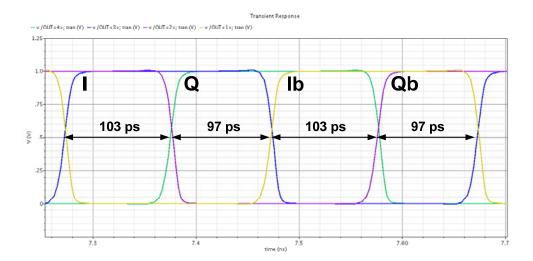

| Figure 4.15. Phase spacings when 2.5 GHz clock is injected                                                                                                                                                                                 | 72   |

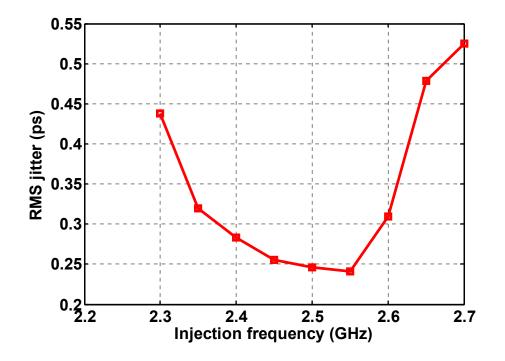

| Figure 4.16. Jitter performance of ILRO.                                                                                                                                                                                                   | 73   |

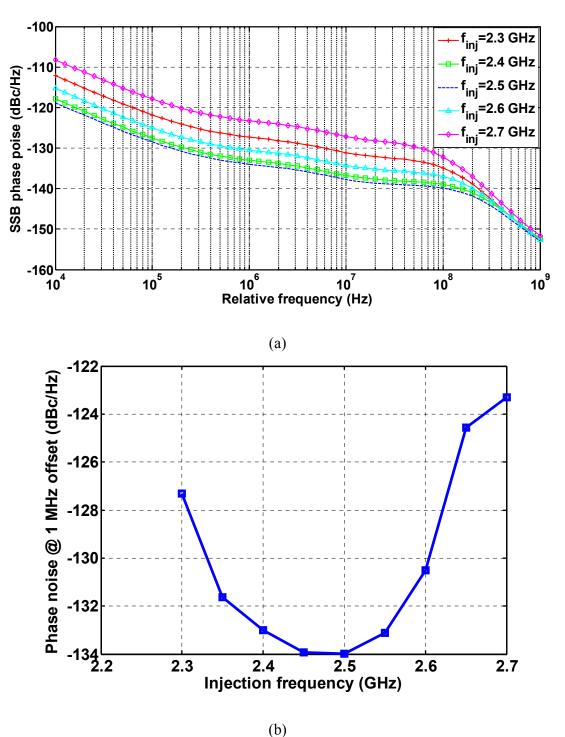

| Figure 4.17. Phase noise performance of ILRO: (a) single-sided band phase noise profile and (b) phase noise at frequency offset of 1 MHz for different injection frequencies.                                                              | 74   |

# LIST OF TABLES

| Table                     | Page |

|---------------------------|------|

| Table 4.1 Power Breakdown | 76   |

# Energy-Efficient Clock Generation for Communication and Computing Systems Using Injection Locking

# **CHAPTER 1. INTRODUCTION**

Recently, the continuous developments of high-performance microprocessors, wireline and wireless communications enable the fast data transfers at different distances and through different transmission media. The clock signal, which is the common signal for these systems, has been pushed to multi-gigahertz frequency range due to the rapid advancing. New challenges have been arrived for the high-performance clocking considering jitter, phase noise, skew, and power consumption. Clocking generation and distribution techniques other than the conventional PLL/DLL have drawn much attention recently, and injection locked ring oscillator is a promising one of them.

### **1.1 Clocking in Communication and Computing Systems**

Communication and computing systems are the foundations for modern information technology. The speed of these systems has increased dramatically in the past few decades. The speed of Ethernet, the most widely used wireline communication standard, is increased from 3 Mb/s in 1973-1975 to 10 Gb/s widely used nowadays, and faster 40- and 100-GbE standard has been standardized by the IEEE 802.3 High Speed Study Group (HSSG) [1]. At the same time, the wireless systems are expanding

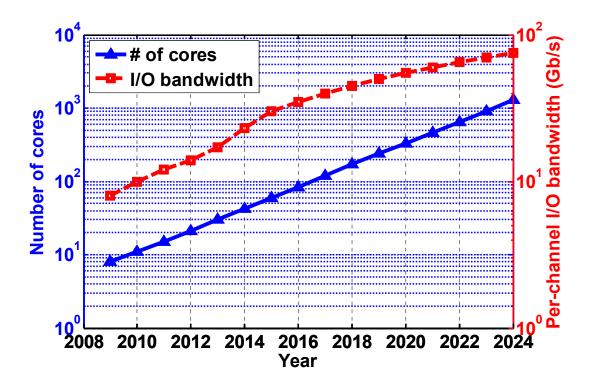

form crowed sub- and low-gigahertz range to multi-gigahertz range due to the introductions of wireless local area network (WLAN) and wireless personal area network (WPAN). The speed of computing system, advanced by the fabrication and many-core technology, also increases at an astounding trend. According to the recent ITRS (International Technology Roadmap for Semiconductors) [2], the number of cores is projected to increase 1.4x per year and the per-channel I/O bandwidth is also projected over 70 Gb/s in 2024, as shown in Fig. 1.1. Even though, there is still a huge gap between the aggregate I/O bandwidth and the total NoC throughput due to

Figure 1.1. NoC projections about number of cores and per-channel I/O bandwidth.

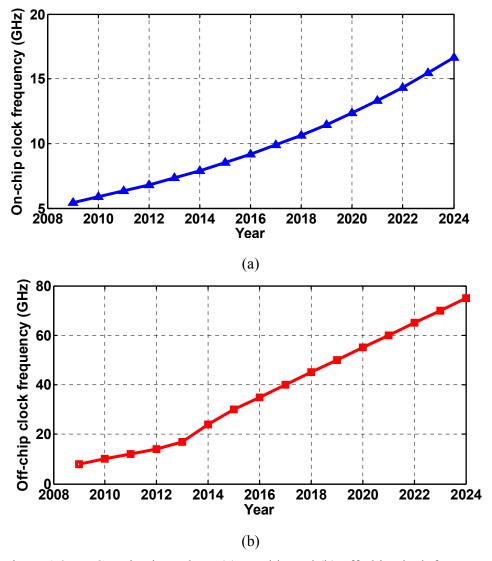

packaging technology allowing a modest increase in I/O channel number (about 2x to 4x during this period) [2]. ITRS 2010 also predicts that the processor clock speed will increase at a speed of 1.25x per year and the off-chip clock will increase at a faster speed and reach 75 GHz in 2024 (Fig. 1.2). Besides, the clock frequency is limited by the power budget, a high energy-efficient design is quite demanding.

Figure 1.2. NoC projections about (a) on-chip and (b) off-chip clock frequency.

#### **1.1.1 Clocking for Wireline Communications**

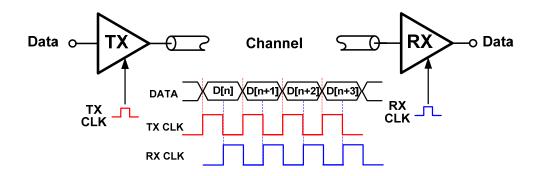

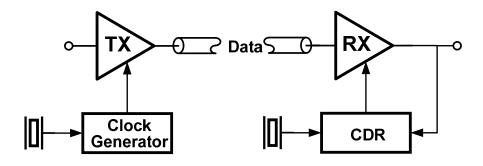

Both the electrical and optical interconnects are commonly used wireline communications and many internal blocks and principles are identical for these two links. Therefore, we show the clocking in electrical links for example in Fig.1.3. A transmitter (TX) relies on a TX clock to convert the digital data into electrical signal that travels through the channel, and then a receiver (RX) converts the incoming electrical signal back into digital data also depending on a RX clock [3]. Based on the schemes of clock generation and recovery, the links are usually characterized as synchronous (common clock), mesochronous (forwarded clock) and plesiochronous (embedded clock) transmission.

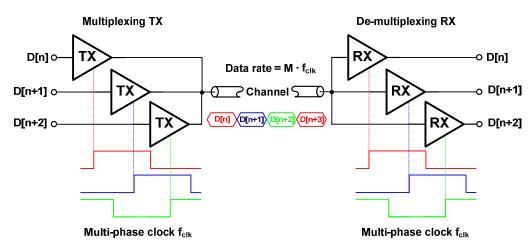

The data transmission rate of a serial links can be dramatically increased without being limited by the clock frequency if we use a time-division multiplexing [4] as shown in Fig.1.4. The *M* branches of transmitters and receivers as well as *M* phases of the clock, which are equally spaced, make the data rate *M* times of clock frequency.

Figure 1.3. Clocking in a basic electrical link.

Figure 1.4. Time-division multiplexing in a serial link.

The timing of the data transmission needs a very precise control in order to minimize the bit error rate (BER) and achieve a very high data rate. The optimum sampling point of the data receiver is usually close to the middle of the bit-period and both the frequency and phase stability of the clock signal should be maintained.

#### 1.1.2 Clocking for Wireless Communications

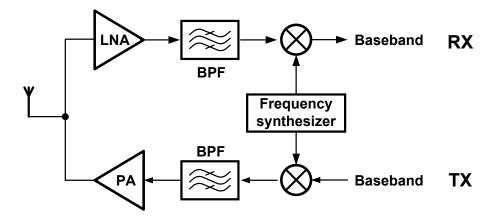

In the wireless communications, the clock signal is RF carrier or LO signal that determines the RF transmission frequency. A typical wireless transceiver is shown in Fig. 1.5. The output frequency of a local frequency synthesizer up converts the low-frequency baseband signal to radio signal in the TX, and down converts the received signal from radio frequency to low frequency in RX. The main consideration is the interferences of adjacent channels caused by phase noise.

Figure 1.5. Clocking in a typical wireless transceiver.

## **1.2 Design Considerations**

In high-speed communication and computing systems, the tolerable timing error is reduced as the clock cycle time is decreased. Jitter for wireline communication and computing systems, and phase noise for wireless communication systems are used separately to describe the clock timing errors. Together with skew, power consumption and multi-phase generation, all these design considerations of clocking should be investigated.

### 1.2.1 Jitter

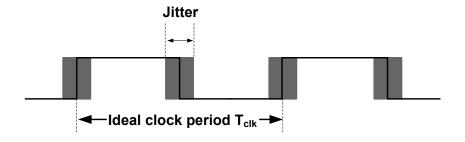

Jitter can be defined as "the short-term variation of a signal from its ideal position in time" as shown in Fig. 1.6 [5]. The deterministic jitter usually caused by duty-cycle distortion and data dependent jitter is predictable, and the peak-to-peak value of this jitter is bounded. However, the random jitter originated from device noise is unbounded and can be modeled with a Gaussian distribution, the RMS value  $\sigma_{RMS}$  of which is used to characterize the jitter performance. Jitter transfer is another important characteristic, which is the relationship between the applied input jitter and the resulting output jitter as a function of frequency. Its tracking bandwidth is usually determined by the loop bandwidth of clock recovery.

Figure 1.6. Illustration of the clock jitter.

### 1.2.2 Phase Noise

The frequency domain representation of jitter is phase noise [6], which is usually characterized by the single-sideband noise spectral density (dBc/Hz):

$$L(\Delta f) = 10\log \frac{P_{sideband}(f_0 + \Delta f, 1Hz)}{P_{carrier}}$$

(1.1)

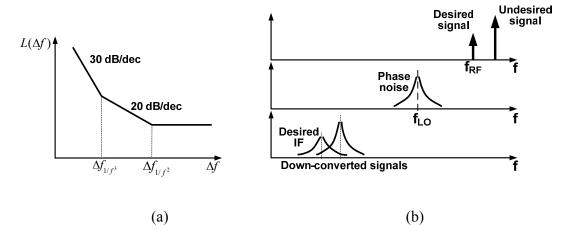

where  $P_{sideband}(f_0 + \Delta f, 1Hz)$  is the single-sideband power at a frequency offset of  $\Delta f$  from the carrier in a measurement bandwidth of 1 Hz. The typical phase noise profile is shown in Fig. 1.7(a).

Phase noise results in the spectral purity degradation of the LO signal in wireless communication systems which will produce adjacent channel interference as shown in Fig. 1.7(b). When an LO signal down converts the desired RF signal, adjacent undesired signal also gets convolved with the LO signal and down converted near the desired signal and overlaps its spectra with that of the desired signal.

Figure 1.7. Illustration of the phase noise: (a) typical profile and (b) its effects on producing the adjacent channel interference.

#### 1.2.3 Deskewing and Multi-Phase Generation

As discussed in 1.1.1, it is necessary to control the relative positions of sampling clock and the received data to minimize the BER, and generate multiple clock phases to achieve time-division multiplexing. In a forwarded-clock receiver of a serial link, for example, the conventional way of clock generation and phase deskewing is using local delay/phase locked loop (DLL/PLL) [7] to generate multiple time-interleaved phases and proceeding phase rotator to interpolate the appropriate phase position to

sample the received data in the center. However, it consumes significant power as each link needs a local, phase rotator-based PLL to generate and deskew the clock phases for recovery of the data and [8] shows that the phase rotation alone occupies almost half of the total power of the receiver.

### **1.2.4 Power Consumption**

Power consumption is one of the most critical requirements for future wireless body-area network (WBAN) sensors [9], [10], especially those battery-powered medical implanted devices. In the transceiver of these devices, frequency synthesizer consumes a large portion of the total radio power, especially when high frequency and low phase noise are required. In the wireline communication and computing systems, the power consumption limitation is also prominent which requires an energy-efficient implementation to comply with power budgets that have plateaued near 100 W due to heat constraint [2]. Therefore, an energy-efficient clock generation and distribution scheme is desired for both communication and computing systems, while maintains the adequate performance regarding the considerations discussed above.

#### 1.2.5 Motivation of Injection-Locked Ring Oscillator (ILRO)

Among the alternative frequency synthesis techniques other than the conventional PLL/DLL, injection locking which synchronizes the frequency and phase of a free running oscillator with a source, has attracted much attention recently [11], [12]. This

technique can significantly suppress the phase noise of the ring oscillator, improve the energy efficiency, enable a fast startup and conveniently generate multiple timeinterleaved phases for the time-division multiplexed applications. An ILRO only consumes 1.08 mW of power at 1.8 GHz in a forwarded-clock receiver [12], while the phase rotation only in a software CDR based receiver needs about 4 mW of the power [8]. The disadvantages may be the inferior frequency stability to PLL and the increased reference spurs. Most of the applications we apply the ILRO to can tolerate with or eliminate these advantages by adding specific calibration blocks.

## **1.3 Thesis Organization**

The following parts of the thesis are organized as follows.

Chapter 2 introduces the background knowledge of ring-based voltage-controlled oscillator (VCO) and the design intuitions are discussed with some simulation results.

Chapter 3 presents a model of injection locking to understand this phenomenon and guide the circuit design. The issues such as fast wakeup, phase noise suppression and jitter tracking, and harmonic injection are also discussed. The applications of ILRO in wireless communication systems are briefly discussed.

In Chapter 4, a forwarded-clock synchronization based on first-harmonic injection locking is designed for a 10 Gb/s photonic interconnect according to its specific features. TIA based front-end is chosen in order to satisfy the requirement of sensitivity. Significant power and area savings are achieved by the ring oscillator without degrading the phase noise and jitter performance.

Finally, Chapter 5 concludes the thesis and proposes some suggestions for future work.

# **CHAPTER 2. RING OSCILLATOR**

Ring oscillator has been a crucial building block in many communication systems because of its integrated nature. In this chapter, an overview of the basic concepts of ring-based voltage-controlled oscillator (VCO) is presented, and then design intuitions considering the frequency, power, phase noise and jitter are discussed.

# **2.1 Introduction**

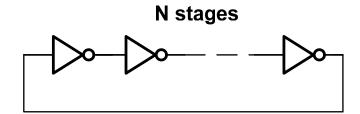

A ring oscillator can be modeled as a chain of delay cells where the output of the last stage is fed back to the input of the chain (Fig. 2.1). The oscillation period can be intuitively viewed as the time it takes a transition to propagate twice around the loop. In an *N*-stage ring oscillator, the oscillation frequency is approximately as:

Figure 2.1. Simplified ring oscillator model.

$$f_{osc} = \frac{1}{2NT_D} \tag{2.1}$$

where  $T_D$  is the propagation delay of each delay cell, which is sensitive to variations of process, supple and control voltage, and temperature according to different implementation of the delay cells.

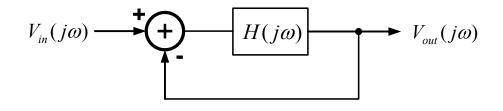

A feedback system satisfying "Barkhausen Criteria" has the potential of oscillation. Consider the unity-gain negative feedback system shown in Fig. 2.2, where the closed-

Figure 2.2. Unity-gain negative feedback system.

loop transfer function can be written as

$$\frac{V_{out}(j\omega)}{V_{in}(j\omega)} = \frac{H(j\omega)}{1 + H(j\omega)}.$$

(2.2)

If  $\omega = \omega_0$ ,  $H(j\omega_0) = -1$ , then the closed-loop gain approaches infinity at  $\omega = \omega_0$ . Under this condition, the noise component at  $\omega_0$  will be amplified by the circuit, resulting in oscillation [13]. Thus, the necessary but not sufficient conditions for a negativefeedback circuit to oscillate are:

$$|H(j\omega_0)| \ge 1 \tag{2.3}$$

13

$$\angle H(j\omega_0) = 180^{\circ} \tag{2.4}$$

In the real implementations, the loop gain should be chosen as more than 2-3 in order to ensure oscillation in the presence of temperature and process variation [13].

A ring oscillator can be simply constructed by using a chain of inverters to create the needed phase shift. Assume each inverter contributes one dominant 3-dB pole, the open loop transfer function of an *N*-stage ring oscillator is:

$$H(j\omega) = \left(\frac{-H_0}{1 + j\omega/\omega_{3dB}}\right)^N \tag{2.5}$$

where  $H_0$  and  $\omega_{3dB}$  is the gain and 3-dB pole of an inverter stage. According to the "Barkausen Criteria", it can be derived as:

$$\left|H(j\omega_0)\right| = \left(\frac{H_0}{\sqrt{1 + (\omega/\omega_{3dB})^2}}\right)^N \ge 1 \Longrightarrow H_0 \ge \sqrt{1 + (\tan(\frac{\pi}{N}))^2}$$

(2.6)

$$\Phi(j\omega_0) = -N \tan^{-1}(\omega_o / \omega_{3dB}) = -\pi \Longrightarrow \omega_{3dB} = \frac{\omega_o}{\tan(\pi / N)}$$

(2.7)

Each inverter stage contributes  $\pi/N$  to the phase, so that a total phase shift of  $2\pi$  is around the loop (including the inversion). Thus at least three cascaded inverter stages are needed in the implementation of  $H(j\omega)$  ideally, to form an oscillator. The implementation of an oscillator with even number of stages will be discussed in the following sections.

14

# 2.2 Type of Ring Oscillator

## 2.2.1 Sing-Ended Signal Ring Oscillator

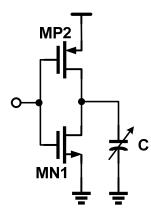

The simplest ring oscillator is implemented as the single-end signal structure, with each of its delay cell shown in Fig. 2.3. The number of stage N should be odd, and equal or larger than 3 for oscillation to build up. A practical 2-stage ring oscillator will oscillate if the stages have very high gain with special efforts to shape the phase of the open-loop transfer function.

Figure 2.3. Delay cell of the ring oscillator with single-ended signal structure.

The expression of propagation delay  $T_D$  of each inverter cell should be derived in order to calculate the oscillation frequency according to 2.1. It can be calculated as:

$$T_D = C \int_{\nu_1}^{\nu_2} \frac{d\nu}{i}$$

(2.8)

where *i* is the current charging or discharging the load capacitor,  $v_1$  and  $v_2$  are initial and final voltages of this capacitor. The full output swing of the inverter is assumed, thus the output voltage is changing between 0 and  $V_{DD}$ . For simplicity, we assume *i* is constant and is the average of the current at the endpoints of the voltage transition. Since the propagation delay is defined as the time it takes for the output to reach the half of the transition, the propagation delay  $T_D$  can be expressed as:

$$T_D = \frac{CV_{DD}}{2I_{av}} \tag{2.9}$$

Therefore, the frequency of the ring oscillator can be tuned by several ways: 1) tuning supple voltage  $V_{DD}$ ; 2) tuning capacitive load *C*; 3) varying the current available for charging and discharging the load capacitance as shown in Fig. 2.4, which is the "current-starved" structure. Tuning the supply voltage and the load driving strength

Figure 2.4. "Current-starved" delay cell of ring oscillator.

usually has a wide tuning range which is necessary to cover PVT variations (PVT variation can cause more than 50% frequency variation), while varying the load capacitor does not since the range of capacitance variation available in most varactor technologies is limited. Thus, this approach is usually used as a fine tuning method of oscillation frequency. Basically, a good tuning scheme should provide: 1) wide tuning range; 2) good linearity; 3) no jitter degradation [14].

The advantages of the single-ended signal ring oscillator are the good power efficiency as the delay stage only draws current when there is a signal transition, and the full output swing. However, its disadvantage is also obvious as signal-ended stage intrinsically susceptible to supply and substrate interference. Both the amplitude coupling and delay modulation exit in this structure and cause variation in the oscillation waveform appearing as jitter.

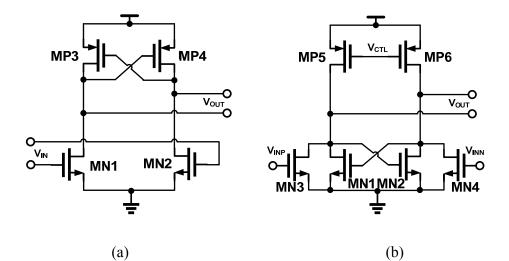

#### 2.2.2 Differential Ring Oscillator

To reject common-mode noise and supply/subtract noise, differential structure will be used as shown in Fig. 2.5. The delay cell usually uses a differential pair as the input and different types of load to get enough gain and frequency tuning. An example of delay cell is shown in Fig. 2.6, it employs the load with symmetric I-V characteristics about the center of the voltage swing, thereby improving the power supple rejection ratio (PSRR) and the linearity of frequency tuning [15].

The number of stages is not limited to be odd now since wire inversion can be used

Figure 2.5. Ring oscillator with differential structure and even number of stages.

Figure 2.6. Delay cell of a differential ring oscillator with symmetric loads.

to meet the oscillation criterion. Even-stage is useful in wireless communication systems while both in-phase and quadrature signals are needed. Although the differential structure is immune to common-mode noise, the single swing should be limited to small value to keep all devices in the saturation region. It also consumes more power and has poor jitter performance since the transistors contribute noise all the time [14].

#### 2.2.3 Pseudo-Differential Ring Oscillator

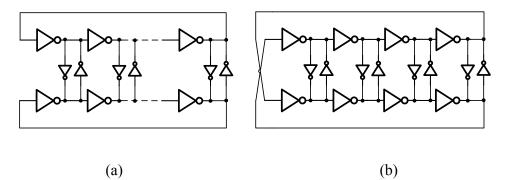

Pseudo-differential ring oscillator has the advantages of the above two types of ring oscillator, having some degree of common-mode rejection while maintaining large output swing. One example is shown in Fig. 2.7(a), in which small latches couple the two single-ended ring oscillator, forcing differential operation. However, the oscillation frequency is usually slower than that of the single-ended ones, since the latch will fight with the delay cell [14]. It can also be implemented with even delays stage as in Fig. 2.7(b), by inverting the wires. Another implementation of pseudo-differential ring oscillator is shown in Fig. 2.8, with the same structure as differential ring while eliminating the tail current source. Both the input pair and load of the delay cells can be configured as cross-coupled structures in order to operate with the pseudo-differential performance [15].

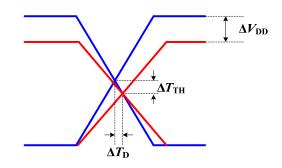

Although the pseudo-differential ring oscillator performs some degree of common mode rejection, there is no rejection of delay modulation due to supply voltage signals variation as shown in Fig. 2.9 [14]. The same delay change  $\Delta T_{\rm D}$  occurs for both signals with supply voltage variation  $\Delta V_{\rm DD}$ .

Figure 2.7. Pseudo-differential ring oscillator with (a) odd stages and (b) even stages.

Figure 2.8. Pseudo-differential delay cell with (a) cross-coupled load and (b) cross-coupled input stage.

Figure 2.9. Delay modulation of pseudo-differential signals.

## 2.3 Phase Noise and Jitter of Ring Oscillator

The spectrum of an ideal oscillator should be an impulse function at the oscillation frequency, while in fact it exhibits phase noise "skirts" around the center frequency. Phase noise is the random fluctuations in the phase of a signal due to time-domain instabilities in an oscillator which is caused by intrinsic thermal and flicker noise. It is usually expressed as the relative value of noise power density to carrier power (dBc), normalized to a 1-Hz bandwidth (dBc/Hz) at a specified offset frequency from the carrier [6].

Jitter is the time domain uncertainty of the transition spacing of the oscillation and is increasing with measurement interval  $\Delta T$ . The standard deviation of the jitter after  $\Delta T$  seconds is shown in [16]:

$$\sigma_{\Delta T} = \kappa \sqrt{\Delta T} \tag{2.10}$$

where  $\kappa$  is a proportionality constant determined by circuit parameters.

There has been many work on modeling phase noise and jitter, some in the time domain [16], [17], and some in frequency domain [18], [19]. One of the time-domain models for the phase noise of oscillator is derived by Leeson [20], showing the phase noise at a frequency offset of  $\Delta \omega$  is:

$$L(\Delta\omega) = \frac{1}{4Q^2} \left(\frac{\omega_0}{\Delta\omega}\right)^2 \tag{2.11}$$

where  $\omega_0$  is the center frequency, Q is the quality factor of the oscillator. According to Razavi in [18] the quality factor Q can be defined as:

$$Q = \frac{\omega_0}{2} \frac{d\Phi}{d\omega}$$

(2.12)

where  $\Phi$  is the phase of the open-loop transfer function of the oscillator. With the expression given by (2.7), quality factor can be calculated as

$$Q = \frac{\omega_0}{2} \left| \frac{d\Phi}{d\omega} \right|_{\omega = \omega_0} = \frac{N}{4} \sin \frac{2\pi}{N}$$

(2.13)

where N is the number of delay stages.

Hajimiri in [21] develops a general model for phase noise and jitter which gives us some design intuitions. Based on the impulse sensitivity function (ISF)  $\Gamma(x)$ , which is time-varying proportionality constant, the phase noise in the  $1/f^2$  region (Fig. 2. 10) is quantitatively predicted as:

$$L(\Delta f) = 10 \cdot \log\left(\frac{\Gamma_{rms}^2}{2 \cdot (2\pi\Delta f)^2} \cdot \frac{\overline{i_n^2} / \Delta f}{q_{max}^2}\right)$$

(2.14)

where  $\Gamma_{rms}$  is the RMS value of the ISF,  $\overline{t_n^2} / \Delta f$  is the single-sideband power spectral density of the noise current source,  $q_{max}$  is the maximum charge of the node of interest and  $\Delta f$  is the frequency offset from the carrier. Phase noise in the  $1/f^3$  region is caused by the device 1/f noise upconverted by the DC value of the ISF and phase noise in the  $1/f^2$  region is due to upconverted thermal noise around the frequency of the carrier and its harmonics. The corner frequency between  $1/f^3$  and  $1/f^2$  region ( $f_{1/f^3}$ ) is relative to the 1/f noise corner  $f_{1/f}$  with the following expression:

22

Figure 2.10. Modeled single-sideband phase noise spectrum.

$$\Delta f_{1/f^3} = \Delta f_{1/f} \cdot \frac{\Gamma_{dc}^2}{\Gamma_{rms}^2}$$

(2.15)

where  $\Gamma_{dc}$  is the DC value of the ISF. Hajimiri also derives an equation for the proportionality constant  $\kappa$  to calculate jitter:

$$\kappa = \frac{\Gamma_{rms}}{q_{max}\omega_0} \sqrt{\frac{1}{2} \frac{\overline{i_n^2}}{\Delta f}}$$

(2.16)

The Hajimiri's model is accurate for predicting phase noise and jitter, while it is hard to calculate the ISF value. However, the paper derives some expressions for phase noise and jitter based on different types of ring oscillator, which clarifies the design tradeoffs. For the single-ended signal ring oscillator, its phase noise and jitter are expressed as:

$$L(\Delta f) = \frac{8}{3\eta} \cdot \frac{kT}{P} \cdot \frac{V_{DD}}{V_{char}} \cdot \frac{f_0^2}{\Delta f^2}$$

(2.17)

$$\kappa \approx \sqrt{\frac{8}{3\eta}} \cdot \sqrt{\frac{kT}{P} \cdot \frac{V_{DD}}{V_{char}}}$$

(2.18)

where  $\eta$  is a proportionality constant (close to one), *P* is the power consumption of the ring oscillator and  $V_{char}$  is the characteristic voltage of the device. It should be noticed that the phase noise is inversely proportional to the power dissipation and increases quadratically with the oscillation frequency, while the phase noise does not depend on the number of stages and load capacitor *C*. Thus, *C* is a free parameter for designer, yuning the oscillation frequency without affecting the phase noise and jitter performance.

In contrast with the single-ended signal ring oscillator, the phase noise of differential signal ring oscillator degrades as the number of stages increases for a given frequency and power consumption. Besides, for *N*-stage ring oscillator, the phase noise of the differential ring oscillator is approximately  $N \cdot \{1 + V_{char} / (R_L \cdot I_{tail})\}$  times larger than that of a single-ended signal ring oscillator, with the same value of *N*, *P* and *f*<sub>0</sub>. For large number of stages *N*, the difference will be even more significant, thus 3 to 5 stage differential ring oscillator is commonly used. Single-ended structure has better fundamental phase noise and jitter performance since it intrinsically has larger swing and lower average current and needs no bias current which contributes additional noise.

24

# 2.4 Design Considerations of Ring Oscillator

# 2.4.1 Frequency

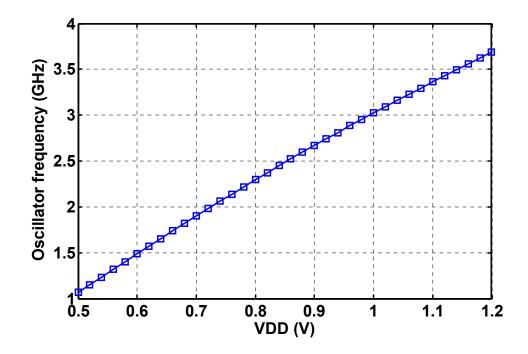

Equation (2.9) shows that the frequency of the ring oscillator can be tuned by varying supple voltage  $V_{DD}$ , capacitive load *C* and by current-starved structure. Fig. 2.11 shows the frequency versus supple voltage of current-starved ring oscillator.

Figure 2.11. Frequency tuning of a current-starved ring oscillator with supply voltage.

When the current starving transistors are operating in saturation region, (2.9) can be modified as:

$$T_D = \frac{CV_{SW}}{2I_{av}} \tag{2.19}$$

where  $V_{SW}$  ( $\langle V_{DD}\rangle$ ) is the voltage swing of the inverter stage. However, the delay of each stage will be determined by the resistance of the current starving transistors rather than the delay cell ( $T_D \propto (R_{triod} + R_{SW})C$ ), when the current starving transistors are operating in the triode regime, which is usually the case when operating in the low supply voltage. Therefore, some techniques such as pre-distorting linearization technique are needed to linearize the tuning range of the oscillation frequency.

Higher oscillation frequency can be achieved by increasing the bias current, thus there is a tradeoff between the power dissipation and the frequency. Smaller length of transistors can lead to higher frequency, while changing the width of the device cannot help with since the bias current and the capacitance may be equally changed in theory.

#### 2.4.2 Phase Noise

Both the systemic noise and the random noise contribute to the phase noise of the ring oscillator. The systemic noise such as common-mode supple noise can be avoided by using symmetric architectures, while the influence of the random noise such as thermal noise and flicker noise cannot be easily alleviated.

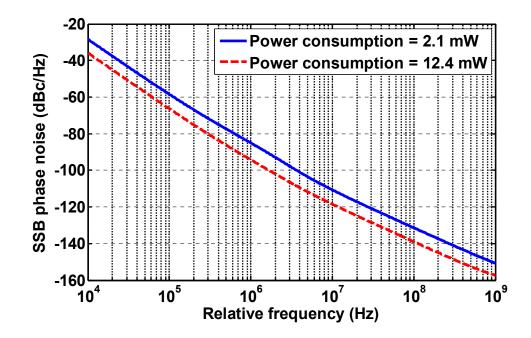

Phase noise performance can be improved by enlarging the power consumption as discussed before. It can be predicted from (2.17) and (2.18) that the phase noise and jitter of the ring oscillation will decrease as the power consumption increases. There are other ways of improving phase noise such as increasing the width of the device and minimizing the channel length, which also add the power dissipation. The phase

noise of a current-starved ring oscillator is simulated with different transistor widths, as shown in Fig. 2.12. The widths of the NMOS transistors are 3  $\mu$ m and 30  $\mu$ m respectively in the two cases. The power consumption increases from 2.1 mW to 12.4 mW when transistor width changes to 10 times larger, while the phase noise decreases from -85.13 dBc/Hz to -94.25 dBc/Hz at a frequency offset of 1 MHz.

Figure 2.12. Phase noise of a current-starved ring oscillator with different power consumption.

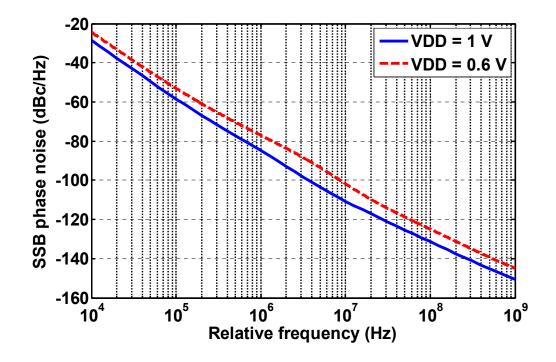

Dynamic power consumption is proportional to  $V^2 f$ , and thus is reduced quadratically as the supply voltage is decreased. However, problems such as constrained headroom, device variation, and leakage current become significant as the supply voltage approaches this near-threshold region. It has been already shown in the previous section that low supple voltage will introduce nonlinear frequency tuning. Phase noise degradation of the ring oscillator is another important factor that will limit the potential supply scaling. As the supply voltage decreases, the intrinsic thermal noise (kT/C), relative to the linear reduction in the capacitor voltage-swing, results in degraded signal-to-noise ratio and therefore larger oscillator phase noise. Furthermore, the slower inverter rise/fall edge rates degrade the impulse sensitivity function (ISF), resulting in higher phase noise [21]. Fig. 2.13 shows the simulated phase noise of the ring oscillator running at different supply voltage, while maintaining the same oscillation frequency by changing the transistor size. The phase noise at a frequency offset of 1 MHz for  $V_{\rm DD}$ = 1.0 V ring oscillator is -85.13 dBc/Hz, while for  $V_{\rm DD}$ = 600

Figure 2.13. Phase noise of a current-starved ring oscillator at different supple voltage.

mV is -77.67 dBc/Hz. The integrated jitter also changes from 289.37 ps (RMS) to 459.28 ps (RMS) when supple voltage is decreased from 1.0 V to 0.6 V.

# 2.5 Summary

By exploiting the basic concepts of VCO, pseudo-differential structure is a compromising choice of three different kinds of ways to implement a ring oscillation, regarding the trade off of power, voltage swing, phase noise and jitter. The design considerations such as frequency tuning, phase noise and jitter are discussed and the relative conclusions are verified by some simulation results.

# **CHAPTER 3. INJECTION LOCKING**

Recently, injection locking has attracted much attention in the applications including clock recovery, frequency synthesis, phase lock and quadrature generation. In this chapter, a model of injection locking is presented to understand this phenomenon and guide the circuit design. The issues such as fast wakeup, phase noise suppression and jitter tracking, and harmonic injection are also discussed.

### **3.1 Introduction**

Injection locking is when the oscillation systems with close-frequency environmental couplings can have interaction leading to change of their phases and frequencies. It was first observed by Christiaan Huygens in 17<sup>th</sup> that the pendulum of two clocks hung on the same wall would eventually swing at exactly the same frequency and 180 degrees out of phase [22]. This phenomenon has been studied for years and is proved to be very useful in a number of applications such as clock recovery, frequency synthesis, synchronization, and so on. Its intrinsic properties of energy-efficiency and phase noise reduction are very attractive, especially for these low power applications such as medical implants and wireline interconnects.

Basically, injection locking can be categorized into three groups, first-harmonic, super-harmonic, and sub-harmonic injection locking. These three different types of injection locking can be utilized for different applications based on the relationship between injection and oscillation frequency. In a first-harmonic injection locking, the injection frequency is the fundamental frequency of oscillation frequency, while in the super-harmonic and sub-harmonic injection locking, the injection frequency is a harmonic or sub-harmonic of the oscillation frequency. However, all these three types of injection locking can be explained by the general model of first-harmonic injection locking, thus the behavior of first-harmonic injection locking will be firstly analyzed and then extended to other two types.

## **3.2 Modeling of Injection Locking**

In order to understand the phenomenon of injection locking, different kinds of models have been developed from frequency domain to time domain. The most intuitive modeling of injection locking is given by Adler [23] in frequency domain, which is usually accurate for harmonic oscillator. Analyzing ring oscillator, transient waveform-based methods are needed as shown in [24], [25]. However, these time-domain methods usually require a full circuit description and do not give an intuitively analytical expression.

In this section, injection-locking model of ring oscillator is built using the frequency domain model assuming quasi-linear operation of the circuit [26], where the large-

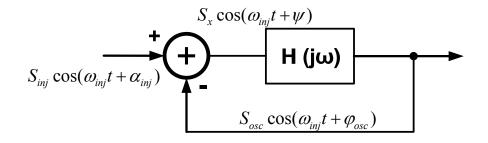

signal operation of each stage of non-harmonic oscillator is similar to its small-signal ac behavior. Then, based on the liner open-loop transfer function  $H(j\omega)$  of ring oscillator derived in Section 2.1, the model of first-harmonic injection locking is shown in Fig. 3.1 [26], [27]. The injected signal  $S_{inj} \cos(\omega_{inj}t + \alpha_{inj})$  is modeled as an additive input and the output  $S_{osc} \cos(\omega_{inj}t + \varphi_{osc})$  has a carrier frequency of  $\omega_{inj}$  (rather than  $\omega_0$ ).

Figure 3.1. Model of first-harmonic injection locking.

Calculating  $S_x \cos(\omega_{inj}t + \psi)$ , which is the input to the open-loop transfer function  $H(j\omega)$  of the ring oscillator, is shown as:

$$S_x \cos(\omega_{inj}t + \psi) = S_{inj} \cos(\omega_{inj}t + \alpha_{inj}) + S_{osc} \cos(\omega_{inj}t + \varphi_{osc})$$

(3.1)

$$= (S_{inj} + S_{osc} \cos \theta) \cos(\omega_{inj}t + \alpha_{inj}) - S_{osc} \sin \theta \sin(\omega_{inj}t + \alpha_{inj})$$

(3.2)

where  $\theta = \varphi_{osc} - \alpha_{inj}$ . So the phase  $\psi$  can be calculated as:

$$\tan(\psi - \alpha_{inj}) = \frac{S_{osc} \sin \theta}{S_{inj} + S_{osc} \cos \theta}$$

(3.3)

Assuming weak injection, which is  $\,S_{\rm inj} << S_{\rm osc}$  ,

$$\frac{d\psi}{dt} \approx \frac{d\theta}{dt} \tag{3.4}$$

Upon travelling through  $H(j\omega)$ ,  $S_x \cos(\omega_{inj}t + \psi)$  experiences a phase shift given by:

$$S_{osc}\cos(\omega_{inj}t+\varphi_{osc})\approx S_x\cos\left(\omega_{inj}t+\psi+\tan^{-1}(\frac{2Q}{\omega_0}(\omega_0-\omega_{inj}-\frac{d\psi}{dt}))\right)$$

(3.5)

where Q is the quality factor of ring oscillator. The phases of the right and left expressions should be the same, thus

$$\varphi_{osc} = \psi + \tan^{-1}\left(\frac{2Q}{\omega_0}\left(\omega_0 - \omega_{inj} - \frac{d\psi}{dt}\right)\right)$$

(3.6)

Combining (3.4) and

$$\tan \Phi = \tan(\varphi_{osc} - \psi) = \tan(\theta - (\psi - \alpha_{inj})) = \frac{S_{inj} \sin \theta}{S_{osc} + S_{inj} \cos \theta} \approx \frac{S_{inj}}{S_{osc}} \sin \theta \qquad (3.7)$$

( $\Phi$  is the phase shift of the open-loop transfer function), (3.6) can be reformed as:

$$\frac{d\theta}{dt} = \omega_0 - \omega_{inj} - \frac{\omega_0}{2Q} \frac{S_{inj}}{S_{osc}} \sin \theta = \omega_0 - \omega_{inj} - \omega_L \sin \theta$$

(3.8)

The phase difference  $\theta$  between the resultant oscillation signal and the injected input signal can be deskewed with the different values of free-running oscillation frequency  $\omega_0$ . This achieves the same results as Adler's equation, where the single-sided locking range is:

34

$$\omega_L = \frac{\omega_0}{2Q} \frac{S_{inj}}{S_{osc}}$$

(3.9)

Obviously, larger injection strength and smaller quality factor of the ring oscillator will results in a larger locking range. Quality factor Q of ring oscillator can be simply expressed as:

$$Q = \frac{\omega_0}{2} \left| \frac{d\Phi}{d\omega} \right|_{\omega = \omega_0}$$

(3.10)

Based on the expression of  $\Phi$  derived in Section 2.1 for *N*-stage ring oscillator, quality factor is:

$$Q = \frac{N}{4} \sin \frac{2\pi}{N} \tag{3.11}$$

Thus the locking range  $\omega_{\rm L}$  can be expressed as:

$$\omega_{L} = \frac{2\omega_{0}}{N\sin(2\pi/N)} \frac{S_{inj}}{S_{asc}}$$

(3.12)

The locking range is inversely proportional to the stage number of ring oscillator N. It can be explained that as the N increases, the slope of the phase transfer function of ring oscillator becomes steeper leading to the reduced locking range. Therefore, large injection strength and minimum number of stages are preferred to achieve a wide locking range.

Based on (3.7), the total phase shift in an oscillation loop is changed by the injection locking and can be calculated in another way as follows [28]:

$$\Phi(j\omega_{inj}) = -N\tan^{-1}(\frac{\omega_{inj}}{\omega_o}\tan\frac{\pi}{N}) = -N\tan^{-1}\left((1+\frac{\Delta\omega}{\omega_o})\tan\frac{\pi}{N}\right)$$

(3.13)

where  $\Delta \omega$  is the frequency difference between the injection frequency and the oscillation frequency, and it is assumed that  $\Delta \omega \ll \omega_0$ , then by using first-order Taylor approximation, equation (3.13) can be written as:

$$\Phi(j\omega_{inj}) = -N\left(\tan^{-1}(\tan\frac{\pi}{N}) + \frac{\Delta\omega}{\omega_o}\tan\frac{\pi}{N}\frac{1}{1 + \tan^2\frac{\pi}{N}}\right) = -\pi - \frac{\Delta\omega}{\omega_o}\frac{N}{2}\sin(\frac{2\pi}{N}) (3.14)$$

The phase shift of the open-loop transfer function  $\Phi$  decreases as the increase of the number of inverter stages *N*.

# 3.3 Phase Noise and Jitter of Injection-Locked Ring Oscillator

The phase noise of an injection-locked ring oscillator (ILRO) mainly comes from two sources: the phase noise of free running oscillator ( $L_{osc}$ ) and the phase noise of the injected signal ( $L_{inj}$ ). The final output phase noise can be calculated by adding two uncorrelated random process to the noiseless system in the previous section.

Equation (3.14) can be rewritten by replacing the expression of *Q*:

$$\Phi(j\omega_{inj}) = -\pi - \frac{\Delta\omega}{\omega_o} 2Q \tag{3.15}$$

From (3.7), the total phase shift in an oscillation loop  $\Phi$  can also be expressed as:

35

36

$$\Phi(j\omega_{inj}) \approx \tan^{-1}(\frac{S_{inj}}{S_{osc}}\sin\theta)$$

(3.16)

So, combining (3.15) and (3.16), we can have

$$-\frac{2Q}{\omega_o}(\omega_{inj}-\omega_0) \approx \tan^{-1}\left(\frac{S_{inj}}{S_{osc}}\sin(\varphi_{osc}-\alpha_{inj})\right)$$

(3.17)

The noise caused by the free running oscillator is added to (3.17) by phase perturbation  $\Delta \Phi$ , the noise generated by injected signal is presented by the added phase perturbation  $\Delta \alpha_{inj}$ , and the resultant output phase is  $\varphi_{osc}+\Delta\varphi_{osc}$  [28]. Equation (3.17) is modified as:

$$-\frac{2Q}{\omega_o}(\omega_{inj} + \frac{d\Delta\varphi_{osc}}{dt} - \omega_0 - \frac{d\Delta\Phi}{dt}) \approx \tan^{-1}\left(\frac{S_{inj}}{S_{osc}}\sin(\varphi_{osc} + \Delta\varphi_{osc} - \alpha_{inj} - \Delta\alpha_{inj})\right) (3.18)$$

The right side of (3.18) can be expanded by first-order Taylor approximation as:

$$\tan^{-1}\left(\frac{S_{inj}}{S_{osc}}\sin(\theta + \Delta\theta)\right) \approx \tan^{-1}\left(\frac{S_{inj}}{S_{osc}}\sin\theta\right) + \frac{\frac{S_{inj}}{S_{osc}}\cos\theta}{1 + \left(\frac{S_{inj}}{S_{osc}}\sin\theta\right)^2}\Delta\theta \qquad (3.19)$$

Assume weak injection,  $S_{inj} / S_{osc} <<1$ , so (3.19) is approximated as

$$-\frac{2Q}{\omega_o}(\omega_{inj} + \frac{d\Delta\varphi_{osc}}{dt} - \omega_0 - \frac{d\Delta\Phi}{dt}) \approx \tan^{-1}(\frac{S_{inj}}{S_{osc}}\sin\theta) + \frac{S_{inj}}{S_{osc}}\cos\theta\Delta\theta \qquad (3.20)$$

Combining (3.9), (3.20) can be rewritten as

$$\frac{d\Delta\varphi_{osc}}{dt} + \omega_L \cos\theta\Delta\varphi_{osc} = \omega_L \cos\theta\Delta\alpha_{inj} + \frac{d\Delta\Phi}{dt}$$

(3.21)

After Laplace transform, (3.21) is

$$\Delta \varphi_{osc}(s) = \frac{\omega_L \cos\theta}{s + \omega_L \cos\theta} \Delta \alpha_{inj}(s) + \frac{s}{s + \omega_L \cos\theta} \Delta \Phi(s)$$

(3.22)

In order to get noise power spectral density of the injection-locked oscillator  $|\Delta \varphi_{\rm osc}|^2$ , *s* in (3.22) is substituted by  $j\Delta \omega$ , and  $|\Delta \alpha_{\rm inj}|^2$  and  $|\Delta \Phi|^2$  are the noise spectral densities of injected signal ( $L_{\rm inj}$ ) and free running oscillator ( $L_{\rm osc}$ ), therefore the total phase noise after injection locking is

$$L_{out}(\Delta\omega) = \frac{\omega_L^2 \cos^2 \theta}{(\Delta\omega)^2 + \omega_L^2 \cos^2 \theta} L_{inj}(\Delta\omega) + \frac{(\Delta\omega)^2}{(\Delta\omega)^2 + \omega_L^2 \cos^2 \theta} L_{osc}(\Delta\omega) \quad (3.23)$$

If the injection-locked system is stable which is when  $d\theta/dt = 0$ , (3.8) can be solved as:

$$\sin\theta = \frac{\omega_0 - \omega_{inj}}{\omega_L} \tag{3.24}$$

Assuming  $\omega_0$  is very close to  $\omega_{inj}$ ,  $\cos^2\theta$  is approximated as 1, so (3.23) can be simplified as:

$$L_{out}(\Delta\omega) = \frac{1}{1 + (\Delta\omega/\omega_L)^2} L_{inj}(\Delta\omega) + \frac{1}{1 + (\omega_L/\Delta\omega)^2} L_{osc}(\Delta\omega)$$

(3.25)

Equation (3.25) shows that ILRO will low-pass the noise from injected signal, while high-pass the noise from itself, which is very similar to the phase noise shaping of a  $1^{\text{st}}$ -order PLL, with the loop bandwidth of  $\omega_{\text{L}}$ . A similar equation describes jitter tracking behavior is shown as:

$$\sigma_{out}^{2} = \frac{1}{1 + (\Delta \omega / \omega_{L})^{2}} \sigma_{inj}^{2} + \frac{1}{1 + (\omega_{L} / \Delta \omega)^{2}} \sigma_{osc}^{2}$$

(3.26)

If the injection frequency is at the edge of the locking range, (3.23) can be reduced to

$$L_{out}(\Delta \omega) = L_{osc}(\Delta \omega) \tag{3.27}$$

in which case, the total phase noise is that of the free-running oscillator. Therefore, the in-band phase noise of ILRO will be reduced significantly if the oscillator is locked to a low-phase-noise source at the center of the locking range.

The jitter of ILRO  $\sigma_{\Delta T}$  can be expressed in terms of its phase noise power spectral density  $S_{\phi}(f)$ , as shown from [19], [29]:

$$\sigma_{\Delta T}^{2} = \frac{8}{\omega_0^2} \int_0^\infty S_{\phi}(f) \sin^2(\pi f \Delta T) df \qquad (3.28)$$

where  $\omega_0$  is the free-running oscillation frequency. Assume long delays ( $\Delta T \rightarrow \infty$ ), (3.28) can be simplified as

$$\sigma_T^{\ 2} = \frac{4}{\omega_0^2} \int_0^\infty S_{\phi}(f) df$$

(3.29)

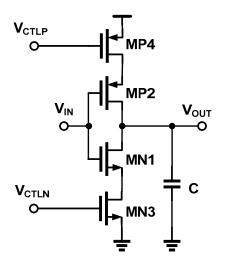

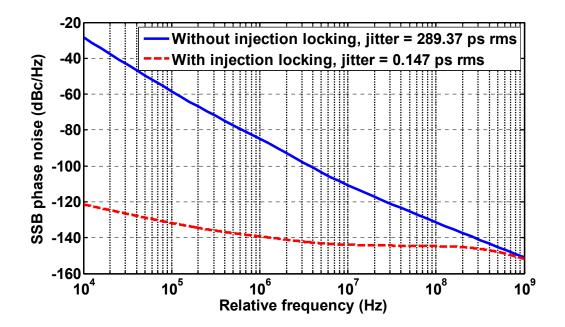

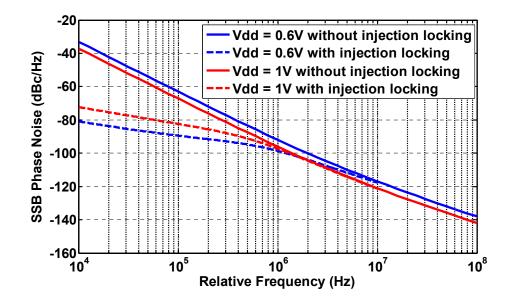

where  $\sigma_T$  is the RMS jitter. (3.29) shows the jitter is determined by the area under the phase noise profile of the output spectrum. Injection-locking to a low-phase-noise source is also beneficial to reduce jitter since the noise power under phase noise profile is decreased. This is especially advantageous for ring oscillator as it has high intrinsic phase noise, however it is easily implemented on chip with very small area. The phase noise of a ring oscillator with and without injection locking is shown in Fig. 3.2, the integrated jitter is decreased from 289.37 ps(RMS) to 0.147 ps(RMS) with an ideal injected signal. The locking range can be read from the transition point of phase

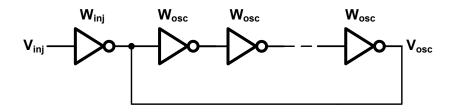

noise profile after injection-locked (red line). For a ring oscillator, the injection strength  $S_{inj}/S_{osc}$  is approximately as the size ratio of injection buffer versus the inverter forming the oscillator ( $W_{inj}/W_{osc}$ ) as shown in Fig. 3.3. The locking range of a 4-delay-cell ring oscillator running at 3 GHz is simulated as 340 MHz, which is close to the calculation from (3.12) as 375 MHz ( $W_{inj}/W_{osc} = 1/4$ ).

Figure 3.2. Phase noise of a ring oscillator with and without injection locking.

Figure 3.3. Injection-locked ring oscillator.

#### 3.3 Fast Wakeup

In the applications with multiple links, not all the links are fully occupied all the same, therefore, it is energy-efficient to idle the un-used links and wake up them fast if burst data comes. It is important to understand the transient behavior of the ILRO, especially when it is start up.

When the ILRO system reaches the stable point  $(d\theta / dt = 0)$ , the solution of (3.8) is:

$$\theta_{ss} = \sin^{-1}(\frac{\omega_0 - \omega_{inj}}{\omega_L}). \tag{3.30}$$

where  $\theta_{ss}$  is the steady-state phase difference between the resultant oscillation signal and the injected signal, while  $\pi - \theta_{ss}$  is the meta-stable point. In order to simplify the calculation, a linearized solution of (3.8) is presented in [30], which is valid when the injection frequency is very close to the free running frequency ( $\omega_0 - \omega_{inj} \approx 0$ ). The settling of the phase difference and the frequency difference exhibits exponential behavior in nature, as shown:

$$\theta(t) = \theta_{ss} + (\theta(0) - \theta_{ss}) \cdot e^{-\omega_L t}$$

(3.31)

$$\omega_{osc}(t) = \omega_{inj} + \omega_L \cdot (\theta_{ss} - \theta(0)) \cdot e^{-\omega_L t}$$

(3.32)

where  $\theta(t)$  and  $\omega_{osc}(t)$  are the instantaneous phase and frequency differences between the resultant and injected signal, and  $\theta(0)$  is the initial phase difference at the point of injection. We can drew the conclusion from the above two equations that the ILRO will lock instantaneously if the initial phase difference  $\theta(0)$  equals to the steady-state phase difference  $\theta_{ss}$ . The locking time of ILRO is determined by two factors: 1) the time constant of exponential decay  $1/\omega_{\rm L}$  and 2) the initial phase difference  $\theta(0)$ . The locking of ILRO is potentially faster than PLL since it usually has larger loop bandwidth  $\omega_{\rm L}$  and further maximizing the locking range can result in a fast locking. When the initial phase difference between the resultant and the injected signal equals to the steady-state phase difference, ILRO will lock immediately, while if  $\theta(0) = \pi - \theta_{\rm ss}$ , the resultant oscillation frequency  $\omega_{\rm osc}$  will equal to the injection frequency  $\omega_{\rm inj}$  and the  $\theta$  will remains at  $\pi - \theta_{\rm ss}$  forever. In reality, phase noise will disturb the meta-stable point and slowly changes phase difference to  $\theta_{\rm ss}$ , leading to a large locking time.

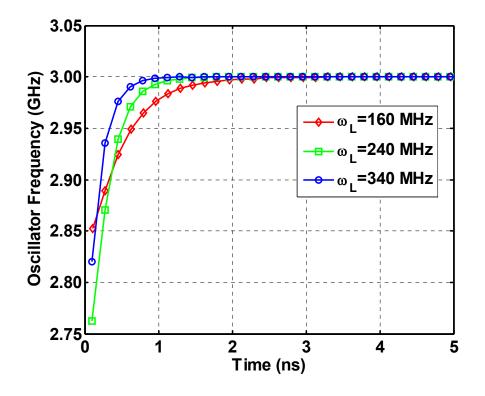

Figure 3.4. Settling behavior of ILRO with different locking ranges.

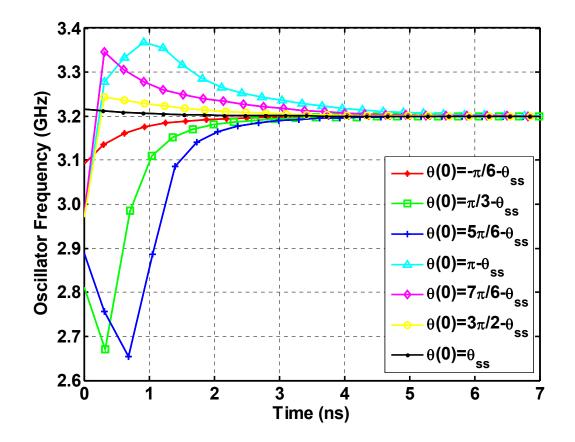

Fig. 3.4 shows the settling behavior of ILRO with different single-sided locking range  $\omega_{\rm L}$ . Larger locking range will lead to a faster settling. The influence of initial phase difference  $\theta(0)$  on the settling behavior is shown in Fig. 3.5. The minimum locking time is observed when the initial phase difference  $\theta(0)$  is close to the final stable phase difference  $\theta_{\rm ss}$ , while the maximum one occurs at  $\theta(0) = \pi - \theta_{\rm ss}$ . From this conclusion, we can think about ways to control the initial phase difference, in order to get great improvement in the locking speed.

Figure 3.5. Settling behavior of ILRO with different initial phase difference between the resultant oscillation signal and the injected signal.

### **3.4 Harmonic Injection Locking**

There are the cases that the injection frequency is the sub-harmonics and harmonics of free running frequency of ring oscillator, such as the frequency multiplier and divider. Their behaviors can also be predicted by the previously discussed firstharmonic injection-locking theory with some modification.

For the sub-harmonic injection locking, the incident frequency is a sub-harmonic of the oscillator free-running frequency ( $\omega_{inj} = \omega_0/n$ ), which means the injection occurs once every *n* cycles. The locking range  $\omega_L$  can be easily modified by dividing the injection strength in (3.12) by a factor of *n*, as follows:

$$\omega_L = \frac{2\omega_0}{N\sin(2\pi/N)} \frac{S_{inj}}{S_{osc}} \frac{1}{n}.$$

(3.33)

The in-band phase noise is constrained to  $L_{inj}+20 \log_{10} n$ , according to the derivations in [31]. As the division ratio *n* increases, the noise rejection degrades accordingly, as corrections from the injected signal are too sparse to clean-up the oscillation.

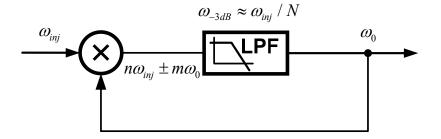

In the modeling of super-harmonic injection locking, Fig. 3.1 should be modified as Fig. 3.6 [32], [33]. It consists of an injector which mixes the injected signal ( $\omega_{inj}$ ) with the output signal ( $\omega_0$ ) and generates harmonic tones ( $n\omega_{inj} \pm m\omega_0$ ), and a frequency selective block filtering the undesired tones and passing tone with the frequency of  $\omega_{inj}/N$ . The single-sided locking range  $\omega_L$  can be expressed as [33], [34]:

$$\omega_{L} = \gamma \cdot \alpha_{N} \frac{2\omega_{0}}{N\sin(2\pi/N)} V_{inj}$$

(3.34)

Figure 3.6. Model of super-harmonic injection locking.

where  $\gamma$  is the injection efficiency,  $\alpha_N$  is the *N*-th order harmonic coefficient, *N* is also the number of stages, and  $V_{inj}$  is the amplitude of the excitation signal.

#### 3.4.1 Implementation in Wireless Transmitter

Frequency multiplying is usually needed for the generation of RF carrier and local oscillator (LO). Injection locking frequency multiplier (ILFM) based on sub-harmonic injection locking and edge combining has attracted much attention recently, especially for the applications allowing very small power consumption and only requiring very relaxed frequency stability.

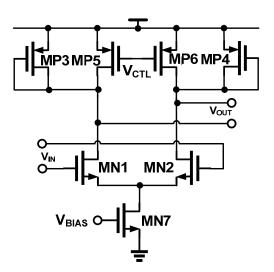

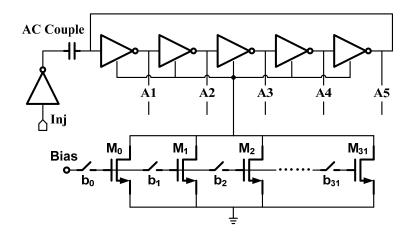

One example [35] is shown in Fig. 3.7 used in a MICS (Medical Implant Communications Service) band near-threshold transmitter. It consists of an ACcoupled injection stage with a pulse generator, and a five-stage single-ended currentstarved ring oscillator, where each stage shares a tunable current source. Phase noise degradation of the injection-locked ring oscillator is one important factor that will limit the potential supply scaling. Fig. 3.8 shows the simulated phase noise of the ring oscillator running at two operating conditions, both with their 5<sup>th</sup> sub-

Figure 3.7. Schematic of the sub-harmonic injection-locked oscillator.

Figure 3.8. Phase noise with and without injection locking at VDD=0.6V, 1V for an ILFM.

harmonics used as the input injection frequencies: VDD = 1.0 V,  $f_{osc}$  = 400 MHz; VDD = 0.6 V,  $f_{osc}$  = 80 MHz. These two cases are compared as the 400 MHz frequency can generated either directly by the 1V-400MHz-SHILRO with higher power consumption, or by the 0.6V-80MHz-SHILRO with edge combiner. Note that in order to compare these two conditions for a required similar output frequency (400 MHz), the phase noise of the multiplied output for the 80 MHz oscillator should be higher than in Fig. 3.8 (blue line) by 20 log<sub>10</sub> 5  $\approx$  14 dB. At 300 kHz offset, the injection-locked oscillator phase noise is -87.91 dBc/Hz, when VDD = 1.0 V,  $f_{osc}$  = 400 MHz. For VDD = 0.6 V and  $f_{osc}$  = 80 MHz, the phase noise is -81.31 dBc/Hz. As the spectral mask of MICS band only requires the attenuation of 20 dB at the edge of the 300 kHz-channel, the phase noise requirement of the transmitter is relaxed. Therefore, the phase noise degradation is tolerable at VDD = 0.6 V, while ~3x power saving is achieved.

Spur suppression is another important consideration for wireless communication. With sub-harmonic injection locking, the injected signal is typically a square-wave pulse waveform consisting of large harmonic content. However, only the *n*-th harmonic locks the oscillator while the others appear at the output as spurs with limited suppression. The relative spur level is as follows [36]:

$$\frac{\left|A_{spur}\right|}{\left|A_{out,\omega_{inj}}\right|} = \frac{\omega_L}{\omega_m},\tag{3.35}$$

where  $\omega_{\rm L}$  is the locking range and  $\omega_{\rm m}$  is the frequency difference between the spurious tone and the desired one. Hence, decreasing the locking range can increase the spur suppression, at the cost of increased locking time and the increased probability of losing lock. There is also a tradeoff with phase noise performance, since the locking range  $\omega_{\rm L}$  also determines the loop bandwidth for the amount of phase noise rejection. Multi-phase asymmetry can also contribute to significant increases in spur-to-carrier ratio. These unequal phase spaces can arise due to asymmetric single-phase injection into the ring [11], [12], device variations such as  $V_{\rm TH}$  mismatches under low supply voltage, and capacitive layout mismatches observed in the wiring breakout from the ring oscillator. These phase offsets are low-frequency in nature and can be minimized at chip startup.

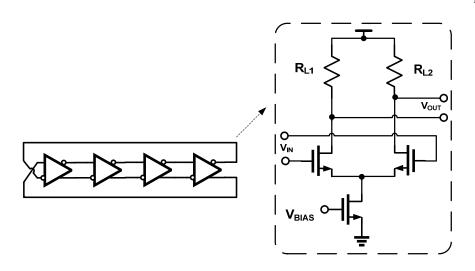

#### 3.4.2 Implementation in Wireless Receiver

Super-harmonic injection locking or injection-locked frequency divider (ILFD) can be utilized in wireless receiver for synchronized clock generation. It can significantly reduce the power and area of frequency division, which has been verified by [32] in MICS band (~400 MHz) to divide the input wireless clock by 5. It only consumes 3  $\mu$ W of power at a 1.0 V supply and 100  $\mu$ m<sup>2</sup> of area.

A divide-by-5 ILFD is shown in Fig. 3.9, which consists of a 5-stage ring oscillator and an injection stage at the tail connected with all the 5 delay cells. Therefore, each of the 5 stages draws current sequentially when the external signal is applied to the

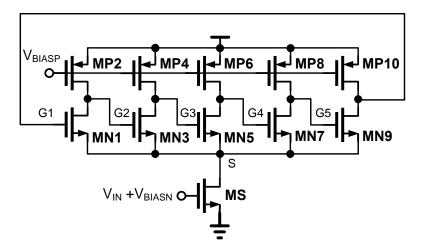

Figure 3.9. 5-stage ring oscillator based ILFD.

common point. The non-linearity occurs in the circuit when  $V_{G1}$  is applied at the gate of MN1 and the injected signal  $V_{inj}$  is applied to the tail transistor MS. Assuming weak injection, the harmonics of injected signal can be ignored so that *n* equals to 1. Therefore, harmonic of  $\omega_0$  will mix with the fundamental component of  $\omega_{inj}$ . The parasitic capacitance and the output resistance of the delay cell form the low-pass filtering with a cut-off frequency close to  $\omega_0$ . High-frequency components are filtered and the DC and low-frequency components are rejected by the oscillation loop. Thus, only the component has a frequency of  $\omega_0$  left, where m equals to (*N*-1). It can also be analyzed in another way that the lowest operating frequency sustained at V<sub>S</sub> is *N*-th harmonic of V<sub>Gj</sub> (j=1,2..5). Therefore, when an injected signal at the vicinity of N $\omega_0$  is incident, locking occurs. The injection efficiency  $\gamma$  in (3.34) for this implementation is the ratio of the current caused by the injected signal and the DC bias current. Therefore, reducing the number of delay stage, improving the injection efficiency and using large-swing injected signal can increase the locking range.

A divide-by-5 ILFD is applied to a MICS band super-regenerative receiver [35], [37] to generate periodic quench signal from the synchronized wireless clock. It was measured that only -32 dBm sensitivity is required when the injection frequency is close to the *N*-th harmonic of free-running frequency. Therefore, a very small voltage swing of injected signal is desired for the super-harmonic injection locking.

### 3.5 Summary

A quasi-linear model of ILRO is used to mathematically formulate the frequency and time domain characteristics of the system, as well as the phase noise shaping and jitter tracking behavior. After injection locked, the system shows a great improvement of in-band phase noise and the total integrated jitter decreases in an order of 10<sup>3</sup>. The settling behavior of ILRO is also exploited and shows a strong dependence on the locking range and the initial phase difference of the injected and the resultant signals. Some simulation results are presented to certify the accuracy of theoretical model. A sub-harmonic injection-locked ring oscillator and a super-harmonic injection-locked ring oscillator are applied to a wireless transmitter for frequency multiplying and to a wireless receiver for frequency division respectively. Prominent power and area savings are achieved with tolerable phase noise and spur degradation.

# CHAPTER 4. PHOTONIC FORWARDED-CLOCK INTERCONNECT SYNCHRONIZATION USING INJECTION-LOCKED RING OSCILLATOR

In the previous two chapters, design considerations of ring oscillator and injection locking have been discussed. In this chapter, an injection-locked ring oscillator is applied to a photonic interconnect system to perform clock synchronization. Simulation results of a 2.5 GHz first-harmonic ILRO based clock receiver specially designed for optical interconnect are shown. The ILRO occupies 970  $\mu$ m<sup>2</sup> of die area and consumes 2 mW of power under 1.0 V supple voltage. The input-referred locking range is 350 MHz, the locked phase noise is -134 dBc/Hz at a frequency offset of 1 MHz, and the corresponding integrated jitter is 0.246 ps (RMS) excluding input reference clock jitter.

# 4.1 Introduction

Monolithic silicon photonic interconnects have emerged recently that show great potentials for on-chip core-to-core [38] and off-chip core-to-memory and core-to-other processors [39] applications in future many-core systems. They exhibit significant advantages over electrical interconnects especially for bandwidth×distance over 100 Gbps×meters [40], as the electrical communications suffer from severe high-frequency loss of electrical traces, reflections from impedance discontinuities, and signal crosstalk, limiting the energy efficiency. Besides, features of silicon photonic such as wavelength-division-multiplexing (WDM), THz-bandwidth low-loss waveguide [41] and distance-insensitive energy-per-bit are beneficial to meet the bandwidth requirements without exceeding the power budget.

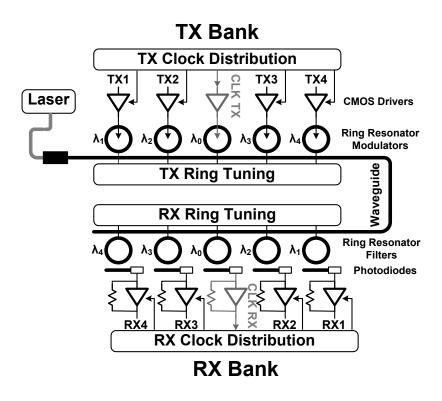

Fig. 4.1 shows a WDM link, multiple channels of data can be transmitted along a single waveguide without interference so that much greater bandwidth and lower

Figure 4.1. A WDM photonic interconnect.

latency can be achieved [42]. A continuous-wave (CW) laser couples multiple wavelengths to the TX through a fiber. Each of the ring resonators is tuned to a separate wavelength and modulates the data of each channel. Each of the wavelengths propagates along the same waveguide until it is routed through a matching ring to a photodiode (PD)/amplifier which outputs the digital electrical data based on the PD photocurrent. Clock signal is also routed through the same waveguide occurring on  $\lambda_0$ and converted to electrical signal by the optical clock receiver to sample the received data. The resonances of the modulator and drop rings are tuned by the ring tuning control circuits.

The clock generation in Fig. 4.1 is based on the forwarded-clock architecture [12] that the clock in the receiver is propagated directly from the transmitter and synchronizes the channel's data transmission. It ensures that the frequencies of the receiver and transmitter are exactly the same and the clock recovery just needs to rotate the phases so that the clock samples the data at the center. In the traditional embedded-clock architecture shown in Fig. 4.2, the clock is recovered from the

Figure 4.2. One channel of an embedded-clock architecture.

received data and needs to tolerate the frequency offset of the TX and RX caused by the variations of different crystal oscillators. The jitter of the recovered clock will tracks that of the data up to the CDR loop bandwidth; however, the bandwidth is usually smaller than the jitter tracking range of the forwarded-clock structure [43]. The embedded-clock architecture generally consumes much more power than the forwarded-clock one, since recovering clock from the data typically requires 2x oversampling [44]. The forwarded-clock synchronization provides advantages of low power and complexity, while at the cost of an additional forwarded link. However, the power and pin overhead of the clock link can be amortized by many parallel channels.

#### **4.2 Photonic Interconnect Features**

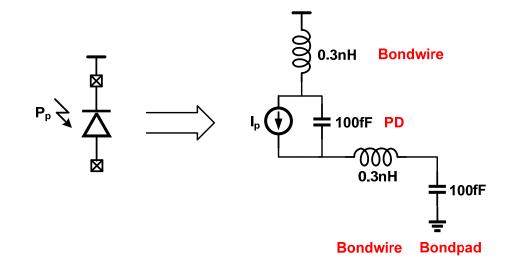

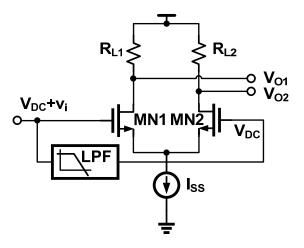

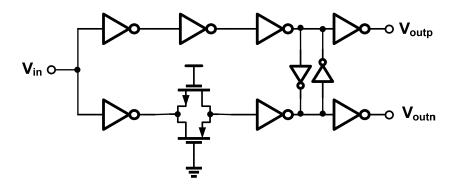

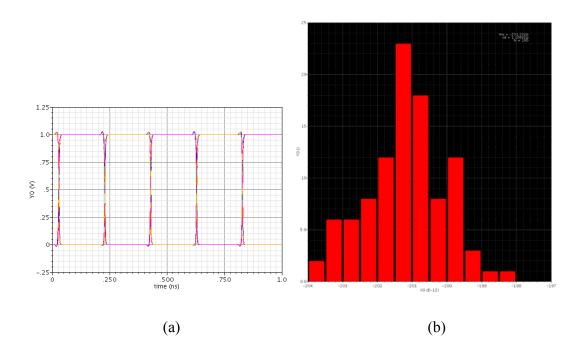

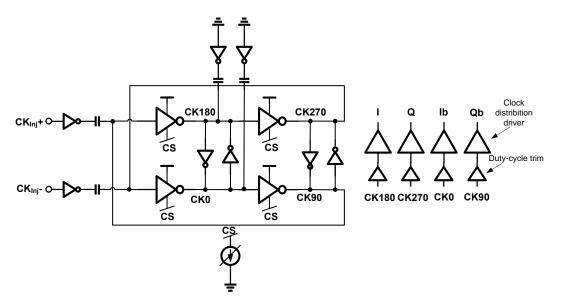

Compared with electrical link, photonic interconnect for short-haul communication has some unique features making forwarded-clock architecture more advantageous. Electrical interconnects usually require timing adjustment for each channel as there are inter-channel delays, while for the optical links, single clock recovery can be used for the whole receiver bank due to optical clock and data signals travelling on a single low-latency waveguide, leading to a large amount of power and area saving. Furthermore, the relative jitter between the clock and data is very small since clock TX and data TX share the same clock fabric and no jitter is added in the channel (optical signaling does not suffer from rail injected noise and crosstalk) [42]. It is very beneficial as the phase/delay locked loop (PLL/DLL) and phase rotator deskewing the clock phase for recovery of the data can be eliminated, signifiantly saving power and area overheard. Phase rotation itself occupies almost half the total receiver power in [8].