#### AN ABSTRACT OF THE THESIS OF

Guoiin Liang for the degree of Doctor of Philosophy in Electrical and Computer Engineering presented on December 19, 1990.

Title: Current Mode Analog and Digital Circuit Design

Abstract approved: \_\_\_\_\_Redacted for privacy

In this dissertation, two important current mode circuit design subjects have been explored. In the first part, the switched-current circuit technique has been investigated. The fundamental performance and limitations of this technique are explored. One of the major limitations, the signal distortion caused by clock feedthrough has been substantially reduced by a newly developed clock feedthrough cancellation technique. In addition, a filter synthesis technique has been developed by directly simulating the structure of digital filter. Several experimental CMOS prototypes have been designed and fabricated. The measured frequency and phase responses demonstrated the feasibility of this synthesis technique. In the second part, a new logic family called current-steering logic has been developed. The fundamental performance and characteristics of this technique have been discussed including the basic inverter and NOR gate with DC analysis, transient analysis and power-delay product. It has been shown that the currentsteering logic has a much smaller current spike than conventional CMOS logic circuits, which is especially desirable in mixed-mode applications. Several experimental prototypes have verified the functionality and performance of this new technique.

### Current Mode Analog and Digital Circuit Design

by

Guojin Liang

A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Completed December 19, 1990

Commencement June 1991

#### APPROVED:

## Redacted for privacy

Professor of Electrical and Computer Engineering in charge of major

## Redacted for privacy

Head of Department of Electrical and Computer Engineering

Redacted for privacy

Dean of Graduate School

Date thesis is presented

December 19, 1990

Typed by Guojin Liang for

Guojin Liang

#### **ACKNOWLEDGEMENTS**

I would like to express my upmost gratitude and respect to my major professor Dr. David J. Allstot for his superior advice, constant encouragement and support. This dissertation could not be accomplished without benefiting greatly from the excellence of his teaching and research.

I am indebted to many of my colleagues and friends. I especially wish to thank Howard C. Yang (now with National Semiconductor), Terri S. Fiez (now with Washington State University), Sifen Luo, Vivek Subramanian, San-Wha Chee (now with Linear Technology) and Ayse Gul Yesilyurt. This research was partially supported by a grant from the National Science Foundation Center for Analog-Digital Integrated Circuits (CDADIC) at the University of Washington, Seattle, WA., and Washington State University, Pullman, WA.

I would also like to thank my graduate committee members, Prof. Donald Amort, Prof. James Herzog, Prof. Stephen Goodnick, and Prof. William Hertherinton for their patience and help.

Finally I would like to dedicate this dissertation to my parents and family for their love, support and understanding throughout all these years.

## TABLE OF CONTENTS

| INTRODU | CTION   |                                                  |    |

|---------|---------|--------------------------------------------------|----|

| PART 1  | SWIT    | CHED-CURRENT FILTER DESIGN                       | 4  |

| CH      | APTER 1 | OVERVIEW                                         |    |

| CH      | APTER 2 | BASIC BUILDING BLOCKS                            | 8  |

|         | 2.1     | Definitions                                      |    |

|         | 2.2     | Building Blocks                                  | 8  |

|         | 2.3     | Voltage-Current Converters                       | 13 |

| CH      | APTER 3 | PERFORMANCE ANALYSIS OF                          |    |

|         |         | SWITCHED-CURRENT CIRCUITS                        | 19 |

|         | 3.1     | Finite Output Resistance Effects                 | 19 |

|         | 3.2     | Nonideal MOS Switch Effects                      | 24 |

|         | 3.3     | MOSFET Mismatch Effects                          | 24 |

|         | 3.4     | Frequency Response                               | 28 |

|         | 3.5     | Noise and Dynamic Range                          | 30 |

|         | 3.6     | Conclusions                                      | 36 |

| CH      | APTER 4 | CLOCK FEEDTHROUGH AND CANCELLATION               | 37 |

|         | 4.1     | Clock Feedthrough Analysis                       | 37 |

|         | 4.2     | Clock Feedthrough Cancellation                   | 41 |

| CH      | APTER 5 | SWITCHED-CURRENT FILTER DESIGN AND               |    |

|         |         | SOME EXPERIMENTAL RESULTS                        | 50 |

|         | 5.1     | Switched-Current Doubly-Terminated Ladder Filter | 5( |

|         | 5.2     | Switched-Current Digital Filter                  | 52 |

|            | 5.3   | Namideal Factors and Experimental Desults       | 62  |

|------------|-------|-------------------------------------------------|-----|

|            | 3.3   | Nonideal Factors and Experimental Results       | 02  |

| CHAP       | TER 6 | CONCLUSIONS                                     | 68  |

|            |       |                                                 |     |

| PART II    | CURR  | ENT-STEERING LOGIC CIRCUIT DESIGN               | 70  |

| СНАР       | TER 1 | OVERVIEW                                        | 70  |

| СНАР       | TER 2 | CURRENT-STEERING LOGIC CIRCUITS                 | 73  |

|            | 2.1   | Basic Inverter                                  | 73  |

|            | 2.2   | Current-steering NOR Gate and Some Applications | 76  |

| СНАР       | TER 3 | TRANSIENT ANALYSIS                              | 87  |

|            | 3.1   | Transfer Characteristics and Noise Margins      | 87  |

|            | 3.2   | Transient Analysis and Power Delay Product      | 92  |

|            | 3.3   | Scaling of Current Steering Logic               | 96  |

| СНАР       | TER 4 | POWER SUPPLY NOISE                              | 100 |

| СНАР       | TER 5 | CONCLUSIONS                                     | 107 |

| SUMMARY    |       |                                                 | 108 |

| BIBLIOGRAI | PHY   |                                                 | 110 |

### LIST OF FIGURES

| <u>Figure</u> |                                                                      | <u>Page</u> |

|---------------|----------------------------------------------------------------------|-------------|

| Fig. 1        | Definition of positive current signal direction.                     | . 9         |

| Fig. 2        | Current signal summation circuit.                                    | 9           |

| Fig. 3        | Current signal inversion circuit.                                    | 11          |

| Fig. 4        | Current signal scaling circuit.                                      | 12          |

| Fig. 5        | Current signal track-and-hold circuit.                               | 14          |

| Fig. 6        | Current signal track-and-hold circuit.                               | 15          |

| Fig. 7        | Voltage-to-current converters using ideal operational amplifiers.    | 17          |

| Fig. 8        | Current-to-voltage converter using ideal operational amplifier.      | 18          |

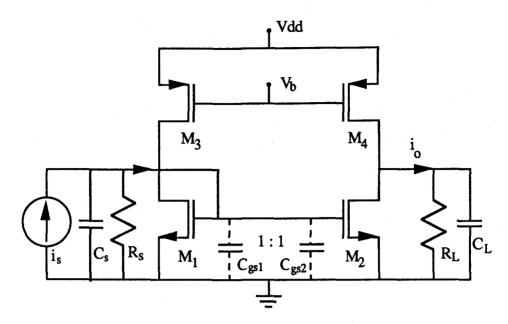

| Fig. 9(a)     | Simple current mirror amplifer with source and loading.              | 20          |

| Fig. 9(b)     | Small-signal equivalent circuit of simple current mirror amplifer.   | 20          |

| Fig. 10       | SPICE simulation of finite output resistance effects for circuit of  |             |

|               | Fig. 9(a), with $(W/L)_1=(W/L)_2=(W/L)_3=(W/L)_4=100\mu m/10\mu m$ , |             |

|               | $R_s = R_L = 0$ , and bias current $I = 100\mu A$ .                  | 22          |

| Fig. 11       | Low-voltage cascode current mirror.                                  | 23          |

| Fig. 12       | Models of the SI T/H circuit with the sampling switch ON             |             |

|               | and modelled as a linear resistor, R <sub>c</sub> .                  | 25          |

| Fig. 13       | Calculated total harmonic distortion of Eq. 25 under                 |             |

|               | different signal current to bias current ratio.                      | 29          |

| Fig. 14(a)    | Frequency response of simple current mirror with                     |             |

|               | $(W/L)_1 = (W/L)_2 = (W/L)_3 = (W/L)_4 = 100 \mu m/10 \mu m,$        |             |

|               | $R_s = R_L = 0$ , and bias current $I = 200\mu A$ .                  | 31          |

| Fig. 14(b) | Frequency response of simple current mirror with                               |    |

|------------|--------------------------------------------------------------------------------|----|

|            | $(W/L)_1 = (W/L)_2 = (W/L)_3 = (W/L)_4 = 20 \mu m/2 \mu m$                     |    |

|            | $R_s = R_L = 0$ , and bias current $I = 200\mu A$ .                            | 32 |

| Fig. 15    | Noise equivalent circuit of a simple current mirror.                           | 33 |

| Fig. 16    | Noise equivalent circuit of a SI delay stage.                                  | 35 |

| Fig. 17    | Lumped RC-model of clock feedthrough                                           | 38 |

| Fig. 18    | Simple model of SI track-and-hold circuit.                                     | 40 |

| Fig. 19    | Clock feedthrough effect on the output current signal of                       |    |

|            | a SI delay stage with $(W/L)_1 = (W/L)_2 = (W/L)_3 = (W/L)_4$                  |    |

|            | = $100\mu m/10\mu m$ , and MOS switch (W/L) <sub>s</sub> = $6 \mu m/2 \mu m$ , |    |

|            | $R_s = R_L = 0$ , and bias current $I = 100\mu A$ .                            | 42 |

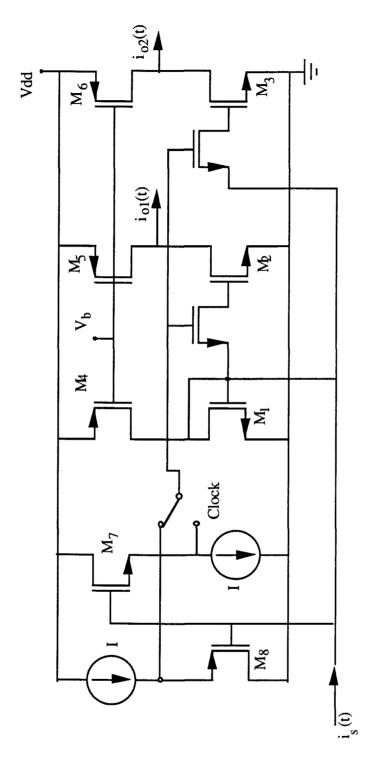

| Fig. 20    | Simple SI track-and-hold circuit incorporating new clock                       |    |

|            | feedthrough cancellation technique.                                            | 44 |

| Fig. 21    | Simple SI track-and-hold circuit incorporating                                 |    |

|            | adaptive clock feedthrough cancellation circuit                                | 47 |

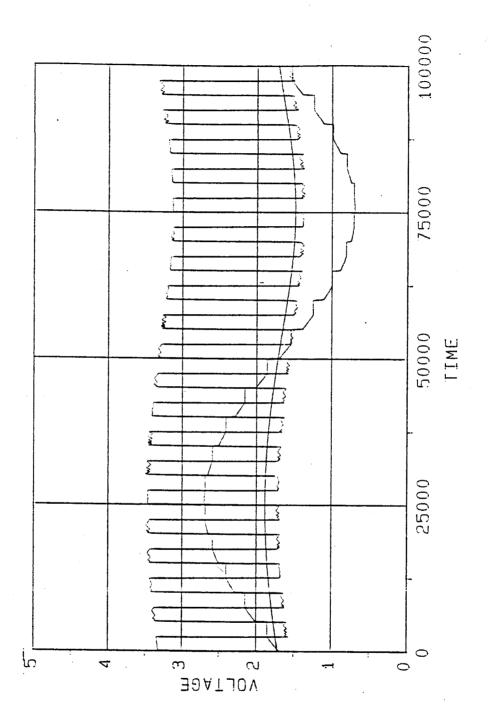

| Fig. 22    | Signal waveforms of adaptive clock feedthrough                                 |    |

|            | cancellation circuit.                                                          | 48 |

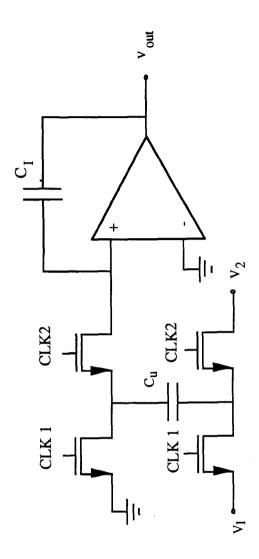

| Fig. 23    | Switched-capacitor differential integrator.                                    | 51 |

| Fig. 24    | First-generation switched-current integrator.                                  | 53 |

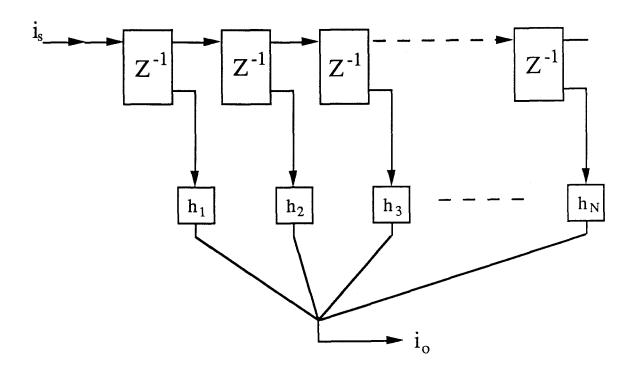

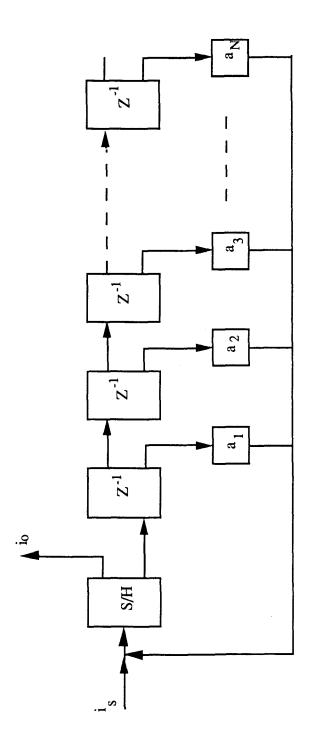

| Fig. 25    | Block diagram of an Nth order switched-current FIR filter.                     | 55 |

| Fig. 26    | The full delay stage of switched-current filter                                |    |

|            | with two unity-gain outputs.                                                   | 56 |

| Fig. 27    | Cascaded current signal scaling stage with overall                             |    |

|            | current gain of K <sub>1</sub> K <sub>2</sub> .                                | 58 |

| Fig. 28 | Digitally-programmable binary-weighted scaling stage                          |    |

|---------|-------------------------------------------------------------------------------|----|

|         | with symbols of a <sub>0</sub> - a <sub>2</sub> represent ideal MOS switches. | 59 |

| Fig. 29 | Switched-current implementation of a direct form IIR filter.                  | 60 |

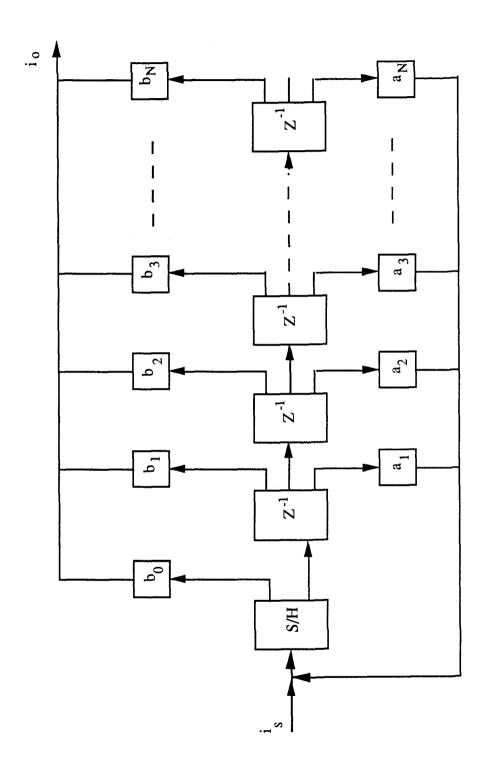

| Fig. 30 | Switched-current implementation of an ARMA filter.                            | 61 |

| Fig. 31 | The simulated effects of gain errors on the magnitude                         |    |

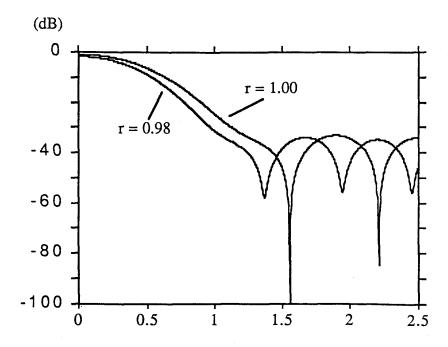

|         | response of an eleventh-order FIR filter.                                     | 63 |

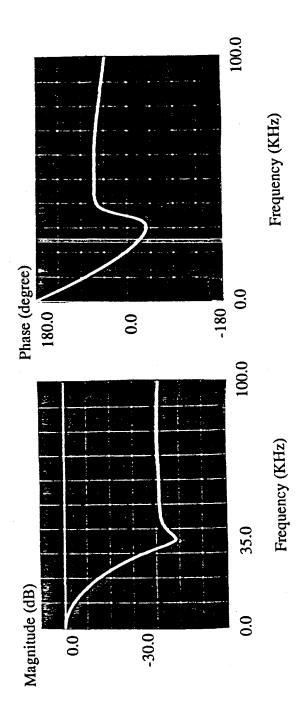

| Fig. 32 | Measured magnitude and phase responses of the 11th-order FIR                  |    |

|         | filter implemented in the 2 $\mu m$ P-well MOSIS CMOS technology.             | 65 |

| Fig. 33 | Measured magnitude and phase responses of the 8th-order FIR                   |    |

|         | filter implemented in the 2 $\mu m$ P-well MOSIS CMOS technology.             | 66 |

| Fig. 34 | Die photo of the 11th order FIR filter implemented in the 2 $\mu m_{\odot}$   |    |

|         | MOSIS P-well CMOS technology.                                                 | 67 |

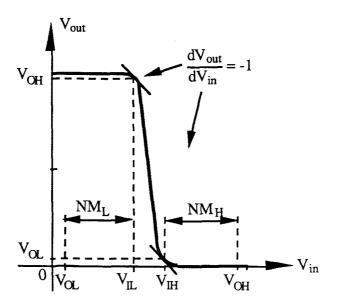

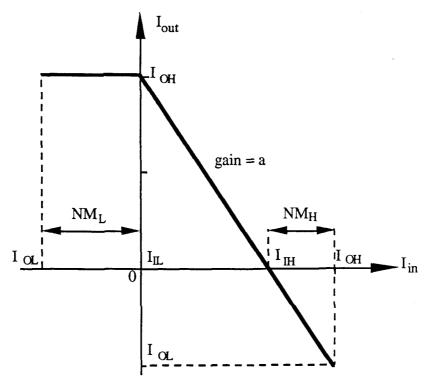

| Fig. 35 | Transfer functions of voltage and current mode logic inverter.                | 74 |

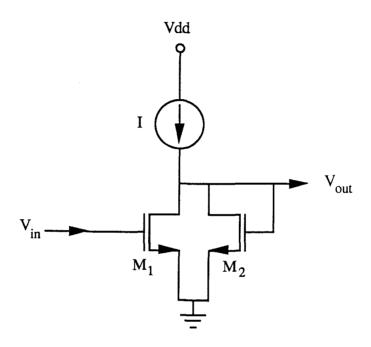

| Fig. 36 | Simplified schematic of a CMOS current-steering inverter                      |    |

|         | with a current gain of one.                                                   | 75 |

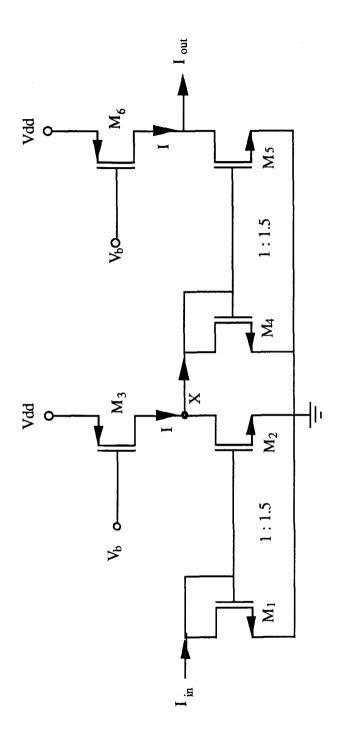

| Fig. 37 | Complete schematic of a CMOS current-steering inverter                        |    |

|         | with a current gain of one. PMOS M <sub>3</sub> provides a nearly             |    |

|         | constant bias current I.                                                      | 77 |

| Fig. 38 | Simplified schematic of a current-steering inverter with                      |    |

|         | a fanout of two.                                                              | 78 |

| Fig. 39 | Simplified schematic of a CMOS current-steering                               |    |

|         | two-input NOR gate with a fanout of one.                                      | 79 |

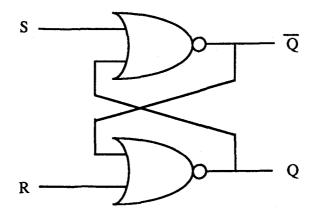

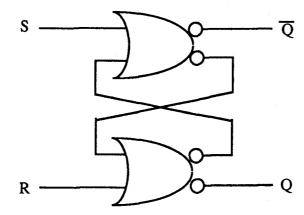

| Fig. 40 | Implementation of voltage and current mode RS flip-flops.                     | 82 |

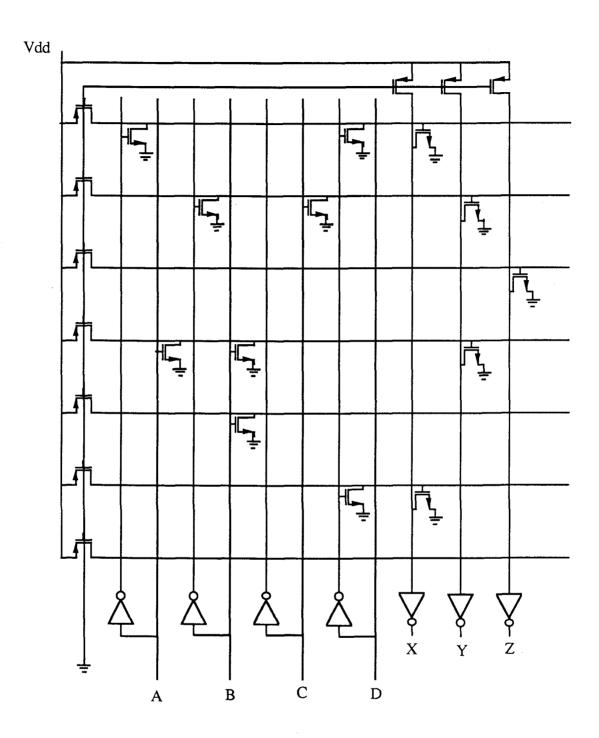

| Fig. 41 | Conventional pseudo-static CMOS PLA with five product                         |    |

|         | terms and three sum terms actually implemented.                               | 83 |

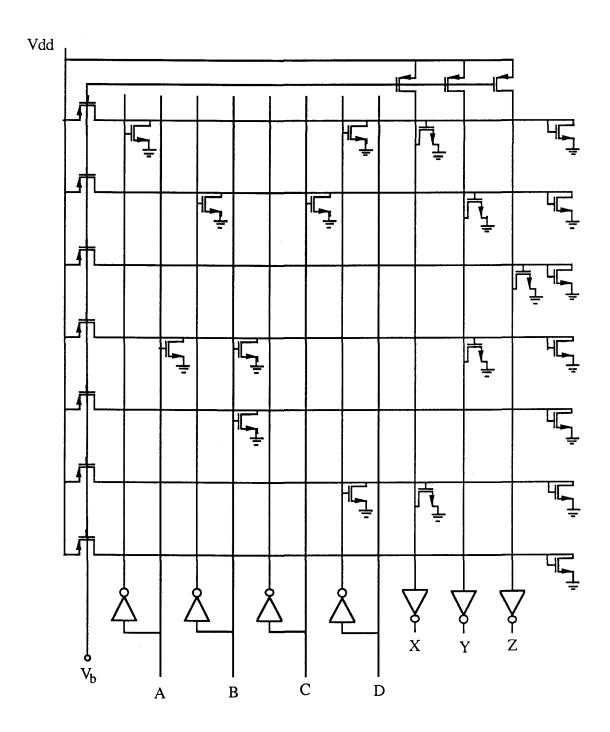

| Fig. 42 | Current-steering implementation of the NOR PLA with                               |     |

|---------|-----------------------------------------------------------------------------------|-----|

|         | five product terms and three sum terms. Voltages are                              |     |

|         | used to represent logic levels within the PLA.                                    | 84  |

| Fig. 43 | Equivalent voltage mode current-steering inverter.                                | 85  |

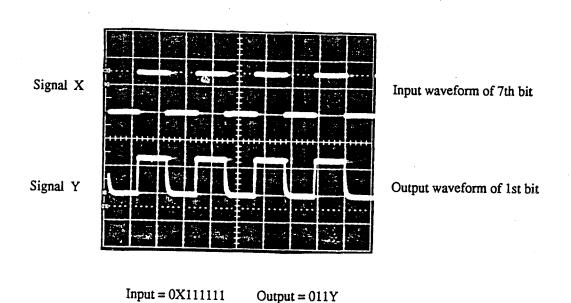

| Fig. 44 | Measured transition waveform of one output of a current-steering                  |     |

|         | PLA implemented in a 2 µm MOSIS CMOS technology.                                  | 86  |

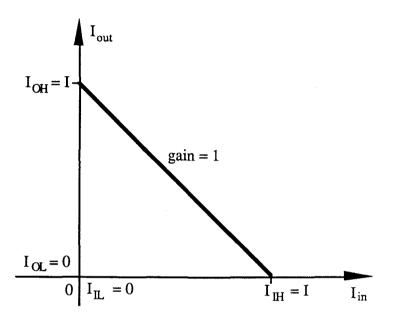

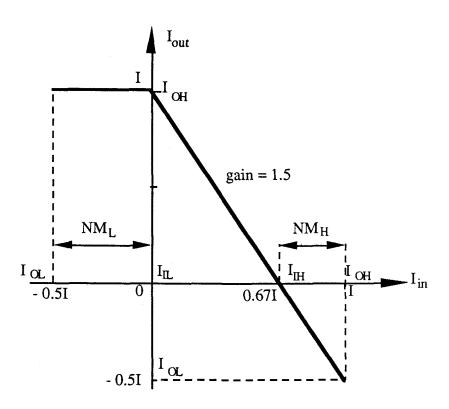

| Fig. 45 | Transfer characteristic of unit-gain current-steering inverter                    |     |

|         | with $I_{OH}(I_{IH})$ and $I_{OL}(I_{IL})$ define the output (input) logic high   |     |

|         | and low levels respectively.                                                      | 88  |

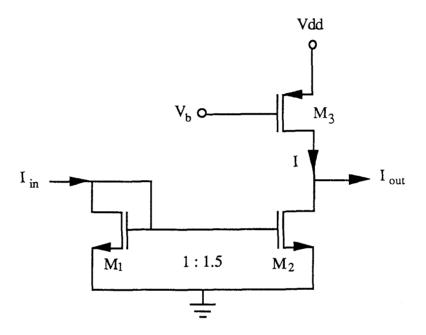

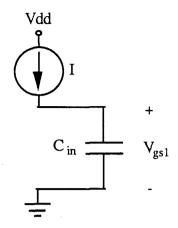

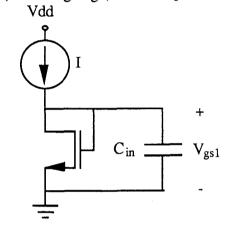

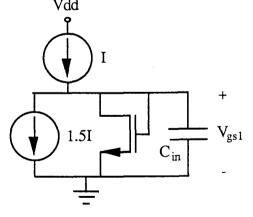

| Fig. 46 | Practical implementation of a current-steering inverter                           |     |

|         | with a current gain of 1.5.                                                       | 90  |

| Fig. 47 | Transfer characteristics of a practical CS inverter                               |     |

|         | with a current gain of 1.5.                                                       | 91  |

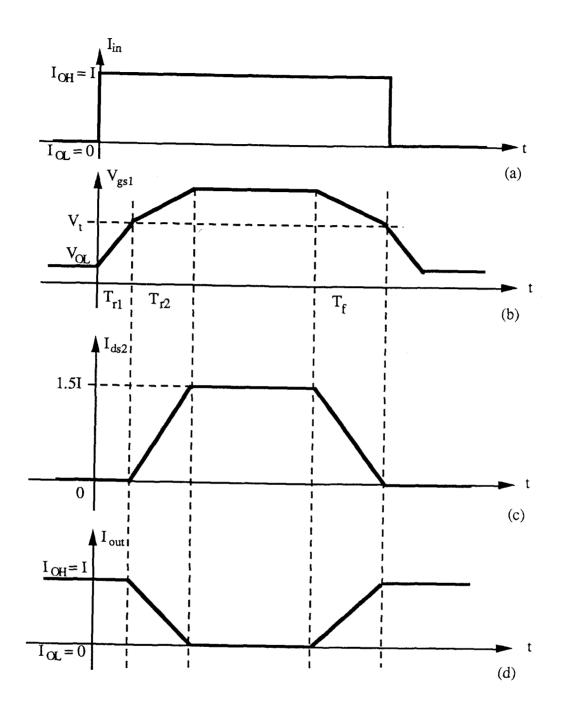

| Fig. 48 | Simplified transition waveform of the current-steering                            |     |

|         | logic inverter.                                                                   | 93  |

| Fig. 49 | Equivalent circuits of current-steering inverter                                  |     |

|         | at different transition period.                                                   | 94  |

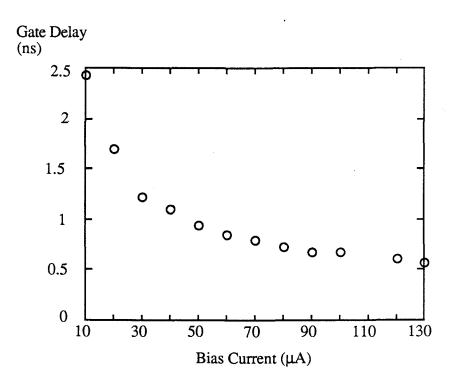

| Fig. 50 | Measured average gate delay of a prototype current-steering ring                  |     |

|         | osillator at different bias currents with $(W/L)_1 = 3\mu m/2\mu m$ ,             |     |

|         | $(W/L)_2$ =4 $\mu$ m/2 $\mu$ m, $(W/L)_3$ =6 $\mu$ m/2 $\mu$ m and $V_{dd}$ = 5V. | 97  |

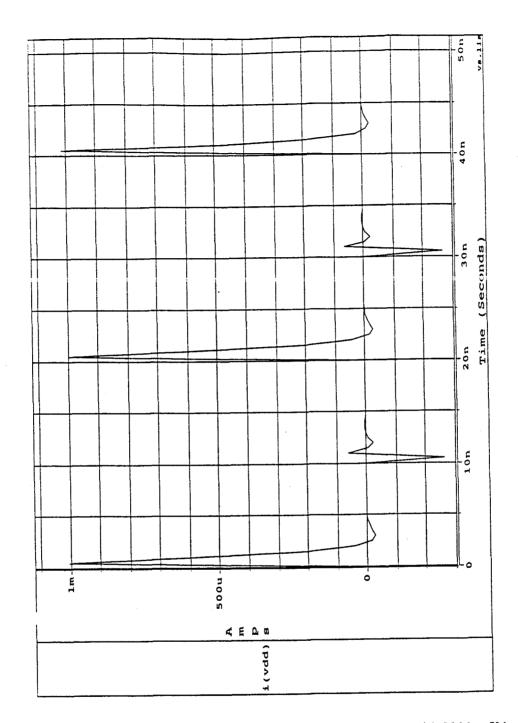

| Fig. 51 | Simulated V <sub>dd</sub> current spike of a static CMOS inverter with            |     |

|         | Vdd = 5V, $(W/L)_n = 10\mu m/2\mu m$ , $(W/L)_p = 6\mu m/2\mu m$ ,                |     |

|         | and $C_L = 0.1 pf$ .                                                              | 101 |

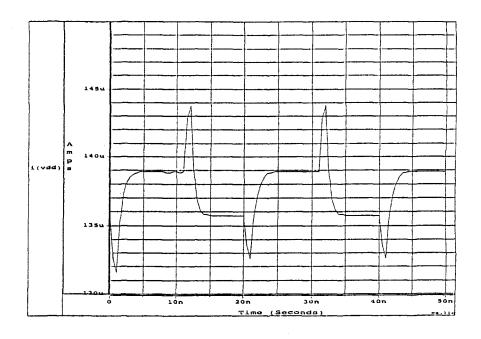

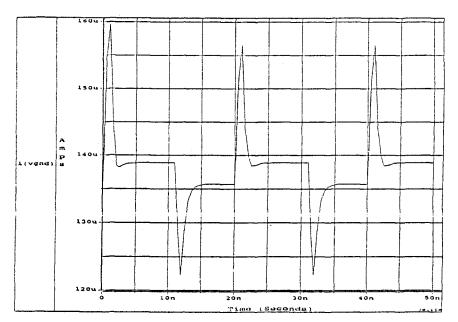

| Fig. 52 | Cascaded current-steering inverters with fanout of one, with                                       |     |  |

|---------|----------------------------------------------------------------------------------------------------|-----|--|

|         | $(W/L)_1=(W/L)_4=4 \mu m/2 \mu m$ , $(W/L)_2=(W/L)_3=(W/L)_5=(W/L)_6$                              |     |  |

|         | = 6 $\mu$ m/2 $\mu$ m, Vdd = 5 V, and bias current I = 135 $\mu$ A.                                | 102 |  |

| Fig. 53 | Simulation results of current-spike for circuit of Fig. 52.                                        | 104 |  |

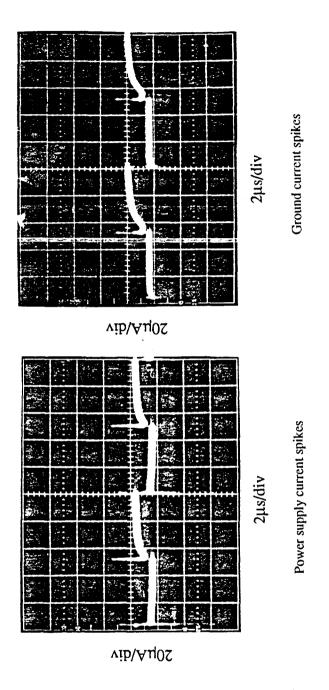

| Fig. 54 | Measured current spike of a current-steering inverter, with (W/L) <sub>1</sub>                     |     |  |

|         | = $(W/L)_4$ = 4 $\mu$ m/2 $\mu$ m, $(W/L)_2$ = $(W/L)_3$ = $(W/L)_5$ = $(W/L)_6$                   |     |  |

|         | = $6  \mu \text{m/}2  \mu \text{m}$ . Vdd = $5  \text{V}$ and bias current I = $125  \mu \text{A}$ | 105 |  |

## LIST OF TABLES

| <u>Table</u> |                                                          | Page |

|--------------|----------------------------------------------------------|------|

| Table 1.     | The parameters of the switched-current FIR filter        |      |

|              | prototypes with sampling frequency of F <sub>s</sub> .   | 64   |

| Table 2.     | Truth table of the two-input current-mode NOR gate.      | 80   |

| Table 3      | The scaling relations of current-steering logic circuits | 99   |

## CURRENT MODE ANALOG AND DIGITAL CIRCUITS DESIGN

#### INTRODUCTION

The Integrated Circuit (IC) is the most important and commonly used component in today's electronic systems. It was invented by Jack Kilby of Texas Instruments in 1958 [1]. Since then, many different IC technologies have been developed. A majority of today's IC's are made of the silicon metal-oxide-semiconductor field effect transistors (MOSFET). The MOS technology was first developed to implement digital ICs in the early 1960's. Since then, the evolution of scaled MOS digital processes has pushed the level of integration to more than a million transistors on a single chip. With such capability, a complex digital system can now be easily integrated on a single silicon chip. To interface with the external world, it is usually required to perform various analog operations such as amplification, modulation, filtering, etc. Therefore, in order to increase system functionality as well as performance, and to reduce the total manufacturing cost, it is often necessary to integrate analog and digital circuits together on a single mixed-mode chip [30].

The first analog MOS IC was developed in 1969 by Chalfan and Looney at Oregon State University [2]. With the further development of the MOS operational amplifier in the early 1970's, and the switched-capacitor (SC) technique in the late 1970's [3][4][7][8][9], analog MOS technology provided efficient and accurate analog signal processing techniques. It used nearly ideal MOS switches, accurate voltage operational amplifiers and excellent capacitor matching properties to achieve the first high-performance CMOS analog signal processing technique. Currently,

switched-capacitor circuits play a major role in analog and mixed-mode integrated circuits and systems.

For economic reasons, the analog part of a mixed-mode IC has to be fully compatible with a semiconductor process technology tailored for digital circuits. This means that in mixed-mode applications, the analog circuits must operate at high speeds and lower power supply voltages. For example, in the newly developed submicron processes, the power supply voltage has been reduced from 5.0 volts to 3.3 volts. Moreover, in mixed-mode applications, the analog circuits are required to reject the interference of high-frequency power supply noise generated by CMOS digital circuits. In this high-frequency mixed-mode environment, the performance of commonly-used operational amplifiers is unsatisfactory resulting in switched-capacitor circuits that have reduced accuracy.

To resolve this dilemma, current instead of voltage, can be used to represent the signal [5][6][14][15][16][28][29]. By using current, the required voltage swing can be reduced for a given signal swing due to the inherent nonlinear I-V relationship of most active devices. For example, the drain current of a saturated MOS device is proportional to the square of its gate voltage. Therefore, if drain current is used to represent the signal, a four times change of signal current causes only a doubling of the excess gate voltage. Current-mode processing also increases the bandwidth and reduces the requirement for high power supply voltage analog circuits.

Based upon the same consideration, especially in the submicron processes, the reduced power supply voltage also reduces the voltage swing of a digital circuit, and results in a lower noise margin. In addition, the higher operating speeds will cause higher power supply noise due to the switching current spike of static CMOS

logic circuits. To improve the performance of mixed analog/digital integrated circuits, current can also be used to represent the digital "1" and "0" logic levels. A technique called current-steering logic is developed here [16]. Our analysis shows that compared to static CMOS logic, the current-steering circuit reduce power supply and ground current spikes by nearly two orders of magnitude, operate under lower power supply voltages, and achieve similar switching speeds.

This dissertation is divided into two parts. In the first part, it focuses on one of the most important current-mode analog signal processing techniques, switched-current circuits. The basic operating principle and building blocks of switched-current circuits are presented. Then, most of the important circuit performance parameters are analyzed. Following that, it discusses the major limitation on the accuracy of switched-current circuits--the clock feedthrough problem. A clock feedthrough cancellation technique is developed to substantially reduce the harmonic distortion and linear gain error caused by clock feedthrough. Finally, based on the switched-current circuit building blocks, a direct sampled-data filter synthesis approach is discussed. Rather than simulating an active-RC or switched-capacitor filter prototype [5][6], the switched-current filter is synthesized by mapping the digital filter structure directly. A switched-current Finite Impulse Response (FIR) filter is given as an example, and the deviations in its frequency response due to nonideal circuit effects are discussed.

In the second part, the current-steering logic technique is developed and analyzed. First, the digital "1" and "0" logic levels are defined in the current domain. Then the current-steering inverter is introduced as well as the current-steering NOR gate; some common digital applications using current-steering logic circuits such as flip-flop and Programmable Logic Array (PLA) are presented. In

addition, the dc transfer and transient delay characteristics of current-steering circuits are discussed. It is shown that the current-steering logic circuits have a much smaller switching current spike and comparable operating speed to static CMOS logic circuits. Its operation and performance are independent of power supply voltages over a wide range.

#### PART I

#### SWITCHED-CURRENT FILTER DESIGN

#### CHAPTER 1. OVERVIEW

Monolithic precision integrated filters are widely used in many different types of electronic systems. Due to the rapid advancement of VLSI technology, it is often desirable to integrate various precision filters together with other analog or digital circuits on a single silicon chip usually using complementary metal on silicon (CMOS) technology. In addition, it is also required that the integrated filters occupy a small silicon area, are insensitive to processing and operating parameter variations, and operate at high speeds with high accuracy.

In the early 1970's, Charge-Transfer Devices (CTD) were introduced and used to implement analog sampled-data transversal filters; this approach has two major disadvantages. First, the transversal filter was the only type of filter that CTD devices could implement accurately and efficiently. Although the transversal filter has the advantage of a linear phase response, it requires a very high order filter when a large stopband attenuation is needed. Moreover, the requirements for high-performance CTD transversal filter, in terms of high charge-transfer efficiency and low insertion loss usually mandate the use of a non-standard MOS technology. Furthermore, the low doping levels required for high-performance CTD's are contrary to the trend to higher doping levels as MOS technology is scaled to smaller feature sizes. Hence, the technology required to implement high-performance CTD transversal filters is not compatible with scaled VLSI analog and digital integrated circuits which are essential for modern system applications.

Since the late 1970's, Switched-Capacitor (SC) circuits have dominated the analog sampled-data signal processing area. They are reliable, precise and (with the inclusion of linear capacitors) compatible with other analog and digital MOS circuits, and have been applied to a wide range of analog signal processing applications. Switched-capacitor circuits do not fit the standard digital VLSI processing technology as extra options such as two layers of polysilicon are needed for precision capacitors. In addition, as the VLSI feature size shrinks, the size of operational amplifiers cannot be reduced proportionally. So in mixed-mode integrated systems, the cost of switched-capacitor filters rises, and the required low power supply voltage limits circuit performance.

Since the explosion of VLSI technology, in the mid-1980's, many low frequency signal processing applications have been implemented using purely digital signal processing techniques. Although it is less silicon-area-efficient and dissipates more power than analog techniques such as switched-capacitor circuits, the digital approach offers the flexibility and high accuracy of digital signal processing, easier application of computer aided design tools, and simpler test procedures. These advantages are usually realized only in low frequency applications. The complexity and cost of high-speed A/D and D/A converters and high-speed digital multipliers usually prohibit most applications in the middle to high-frequency regions.

The Switched-Current (SI) filtering technique was first proposed in 1989 [5]. Since then, different types of switched-current filters have been developed, and it has been shown that the SI technique has several advantages over the other filtering techniques discussed above. It is entirely compatible with standard CMOS digital processing technology, and achieves reasonable accuracy using low power

supply voltages. The high bandwidth capability of the MOS current mirrors used to implement SI circuits provides the potential to operate at higher frequencies than switched-capacitor circuits.

Chapter 2 explains the configurations and operation of the basic building blocks of SI circuits. In Chapter 3, the practical design aspects of SI circuits are discussed including the finite output resistance effects, nonideal MOS switch effects, MOSFET threshold mismatch effects, and noise and dynamic range considerations. In Chapter 4, the clock feedthrough mechanism is presented, and a cancellation technique is proposed to reduce its effects of linear current gain error and harmonic distortion. In Chapter 5, one method to implement SI filters is reviewed based on the first-generation SI integrator. Synthesis procedures starting from various digital filter structures are presented. Finally, some experimental results of CMOS SI FIR filters are presented, and a summary of this research project is presented in Chapter 6.

#### CHAPTER 2. BASIC BUILDING BLOCKS

This chapter begins by introducing the basic definition of current-domain signal processing. Followed by the switched-current circuit implementations of several essential analog signal processing functions are presented. Finally, in order to interface with the existing voltage-domain circuits, the voltage-to-current and current-to-voltage converters are discussed.

#### 2.1. Definitions

A switched-current (SI) circuit is defined as an analog sampled-data circuit which uses currents instead of voltages to represent analog signals; thus all analog signal processing tasks are performed in the current domain. Although there are always voltages existing within the SI circuit, these voltages are an indirect consequence of current signals, and are only used as intermediate media for signal processing.

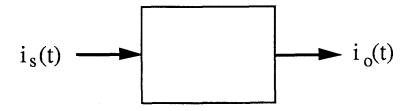

Because the signal current flows in either direction, the positive direction of a current signal must be defined. For convenience, the signal flowing into the input node and out of the output node are defined as positive as shown in Fig. 1.

#### 2.2. Building Blocks

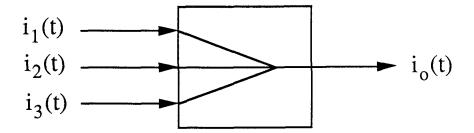

A circuit which performs the summation operation in the current domain is easily constructed as shown in Fig. 2. By applying Kirchoff's Current Law (KCL), it is clear that

$$i_0(t) = i_1(t) + i_2(t) + i_3(t).$$

(1)

Fig. 1 Definition of positive current signal direction.

Fig. 2 Current signal summation circuit.

Unlike voltage signal processing, an important advantage in current domain is that signal summation is easily implemented by simply connecting all signals together as shown.

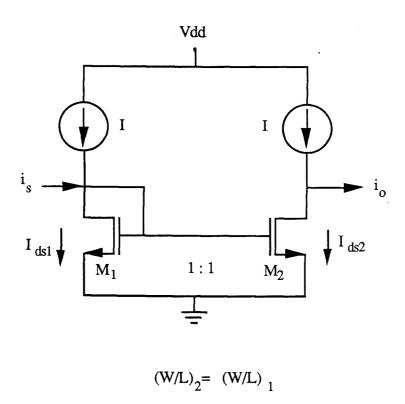

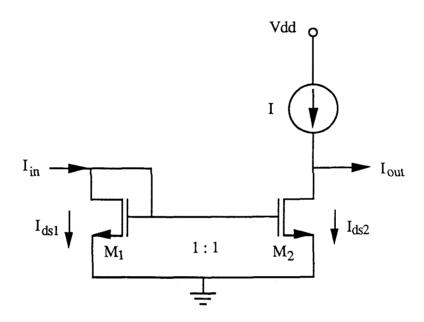

Next, consider the simple biased current mirror amplifier shown in Fig. 3, and assume both MOSFETs are saturated:

$$I_{ds1} = \frac{1}{2} K'_n(W/L)_1 (V_{gs1} - V_{t1})^2$$

(2a)

$$I_{ds2} = \frac{1}{2} K'_n(W/L)_2(V_{gs2} - V_{t2})^2$$

(2b)

With  $V_{gs1} = V_{gs2}$  under ideal matching between  $M_1$  and  $M_2$ , and ignoring channel length modulation effects,  $I_{ds2} = I_{ds1}$ . Apply KCL to Fig. 3 we see that

$$I_{ds1} = I + i_s \tag{3a}$$

$$I_{de2} = I - i_0 \tag{3b}$$

and therefore

$$i_0 = -i_s. (4)$$

Hence, the simple biased current mirror amplifier performs the signal inversion operation in the current domain.

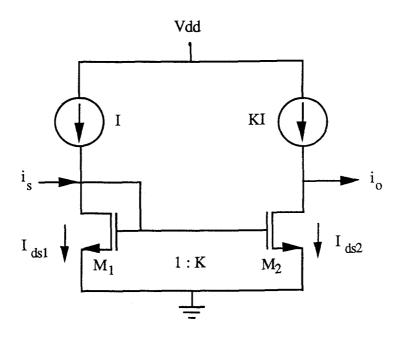

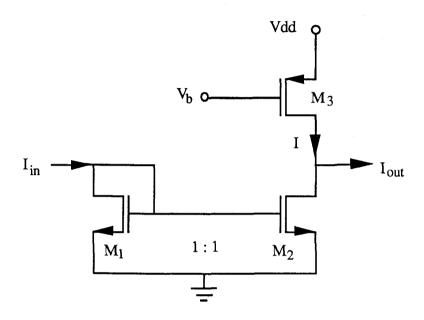

By using a similar circuit as shown in Fig. 4 with  $(W/L)_2 = K(W/L)_1$  and KI as biased current in the output branch, we see from (2a) and (2b) that

$$V_{gs1} = \sqrt{\frac{2I_{ds1}}{K'_{n}(W/L)_{1}}} + V_{t1}$$

(5a)

$$V_{gs2} = \sqrt{\frac{2I_{ds2}}{K'_{n}(W/L)_{2}}} + V_{t2}$$

(5b)

Again, with

$$V_{gs1} = V_{gs2}$$

, and also assuming matched process parameters, then

$$I_{ds2} = \frac{(W/L)_2}{(W/L)_1} I_{ds1}$$

(6)

Using (3a) with  $I_{ds2} = KI - i_0$ , from KCL where  $K = \frac{(W/L)_2}{(W/L)_1}$ , then

$$i_o = -\frac{(W/L)_2}{(W/L)_1} i_s$$

(7)

Fig. 3 Current signal inversion circuit.

$$(W/L)_2 = K(W/L)_1$$

Fig. 4 Current signal scaling circuit.

Hence a simple biased current mirror with ratioed output device and output bias current performs the scaling operation in the current domain. With CMOS VLSI technology, relatively accurate MOSFET pair matching is achieved, which means the accuracy of all the current signal processing circuits discussed above is also relatively high.

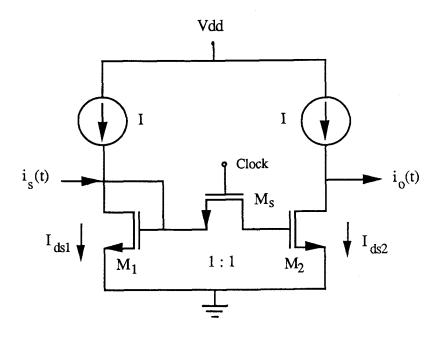

By adding a switch between the two gates of the MOSFETs in the biased current mirror amplifier as shown in Fig. 5, the current track-and-hold (T/H) circuit is configured. When Clock is HIGH and the switch  $M_s$  is turned ON,  $V_{gs1} = V_{gs2}$ , and the circuit is equivalent to the simple biased inverter shown in Fig. 6(a); since  $i_o(t) = -i_s(t)$ , the output current simply <u>tracks</u> the input current with inversion. When at time  $T_1$  Clock goes LOW and the switch  $M_s$  is turned OFF, the instantaneous gate voltage of  $M_2$  is <u>held</u> on the gate capacitance  $C_{gs2}$ , so that  $V_{gs2}(t) = V_{gs1}(T_1)$  for  $t > T_1$ . In the current domain,  $i_o(t) = -i_s(T_1)$ . If the switch is implemented using an n-channel MOSFET with its gate controlled by a clock signal of pulse width  $T_1$  and period  $T_2$ , then the output of this circuit is

$$i_o(t) = -i_s(t)$$

$0 \le t < T_1$  (8a)

$$i_o(t) = -i_s(T_1)$$

$T_1 \le t < T_2.$  (8b)

One interpretation of Eq. (8) is that the switched-current track-and-hold circuit delays the input current signal by a half clock period to the output, so that this circuit is useful as an analog sampled-data delay circuit.

### 2.3. Voltage-Current Converters

For historical reasons, almost all of the existing signal-processing circuits and systems are designed and operated in the voltage domain. In order to implement the emerging current signal processing techniques together with other existing circuits and systems, it is essential to convert between the voltage and current

Fig. 5 Current signal track-and-hold circuit.

Fig. 6 Current signal track-and-hold circuit.

(The switch symbol represents an ideal NMOS switch)

domains. The ideal voltage/current (V-I) converter is defined as a circuit which has a linear transfer characteristics between input voltage and output current; ideally then, no harmonic distortion is introduced during the V/I conversion.

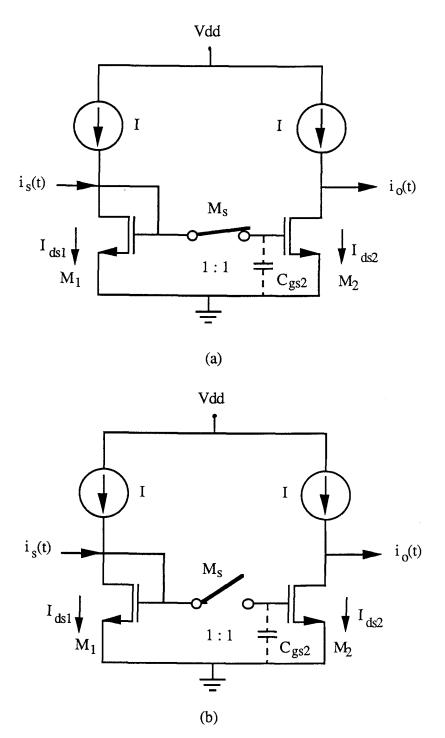

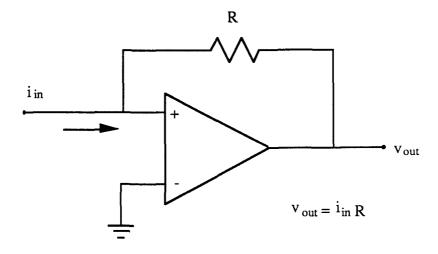

Two circuits which perform the voltage-to-current conversion are shown in Fig. 7. In Fig. 7(a), assuming an ideal operational amplifier,  $v+=v-=v_{in}$ , Hence  $V_R=v_{in}$ , and  $I_R=V_R/R$  due to the infinite input impedance of opamp. Hence  $i_{out}=I_R=\frac{v_{in}}{R} \tag{9}$

To the degree that R is linear, a linear V/I conversion is achieved.

A second voltage-to-current converter is shown in Fig. 7(b). The basic principle is that the input current  $I_R = v_{in}/R$  flows into the drain of  $M_1$  due to the negative feedback action around the operational amplifer. If any current error is produced in  $M_1$ , the voltage on v+ changes, and is amplified by the open-loop gain of opamp, so that the gate voltage of  $M_1$  is adjusted to reduce its current error. The V/I relation is the same as in Eq. (9).

The output current-to-voltage (I-V) conversion is implemented using the simple circuit as shown in Fig. 8. Assuming an ideal opamp, it is obvious that

$$\mathbf{v}_{\mathbf{out}} = \mathbf{i}_{\mathbf{in}} \, \mathbf{R}. \tag{10}$$

In this section we have shown various switched-current circuit building blocks which are used to implement the basic analog signal processing functions such as summation, inversion, scaling, and delay. We also showed some simple circuits which are used to implement voltage/current and current/voltage conversions.

Fig. 7 Voltage-to-current converters using ideal operational amplifiers.

Fig. 8 Current-to-voltage converter using ideal operational amplifier.

# CHAPTER 3. PERFORMANCE ANALYSIS OF SWITCHED-CURRENT CIRCUITS

The CMOS switched-current circuits discussed in the previous chapter can be used to implement various analog sampled-data signal processing systems including SI filters [5][6][14][15]. In order to achieve high accuracy and performance similar to switched-capacitor filters, many nonideal factors must be considered, including finite output resistance effects, MOSFET threshold and size mismatch effects, nonidealities associated with the MOS switches, clock feedthrough effects, etc. These practical design issues and performance limitations of switched-current circuits are discussed in this chapter.

#### 3.1. Finite Output Resistance Effects

From the previous discussion, the basic building block of switched-current circuits is the simple biased current mirror amplifier shown in Fig. 9(a) where the input source is represented as a Norton equivalent and the output loading resistance is R<sub>L</sub>. Its small-signal ac model is shown in Fig. 9(b). At low frequencies ignoring all capacitances, its current-domain transfer function is given by

$$\frac{i_0}{i_s} = \frac{-g_{m2}g_L}{(g_{ds2} + g_{ds4} + g_L)(g_{m1} + g_{ds1} + g_{ds3} + g_s)}$$

(11)

It is evident from Eq. (11) that even if the two MOSFETs match with  $g_{m1} = g_{m2}$ , the nonideal input and output conductances,  $g_{ds1}$ ,  $g_{ds2}$ ,  $g_{ds3}$ ,  $g_{ds4}$ ,  $g_s$ , result in a lossy current mirror, which means the output current signal is always less than the input current signal. With this gain error, the basic circuit blocks such as the inverting, scaling and delay stages also exhibit gain errors. These gain errors usually cause a frequency response error for the entire filter. For example, if the channel length modulation constant is  $\lambda = 0.05$ , the bias current  $I = 100 \mu A$ , and

Fig. 9(a) Simple current mirror amplifer with source and loading.

Fig. 9(b) Small-signal equivalent circuit of simple current mirror amplifier.

W/L =  $100\mu m/10\mu m$  for M<sub>1</sub> and M<sub>2</sub>, then  $g_{ds} = \lambda I = 5\mu S$ ,  $g_{m} = 300\mu S$ , and the gain error is about eight percent. Figure 10 shows the simulation results of a simple current mirror where the output signal amplitude is reduced by about seven percent relative to the inputs.

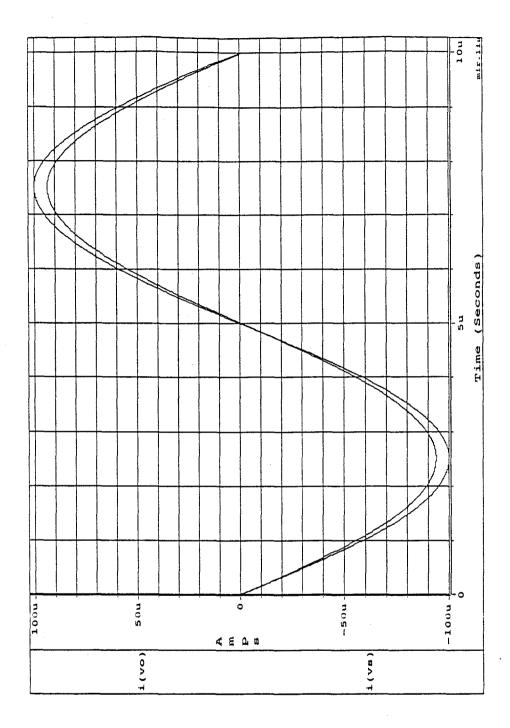

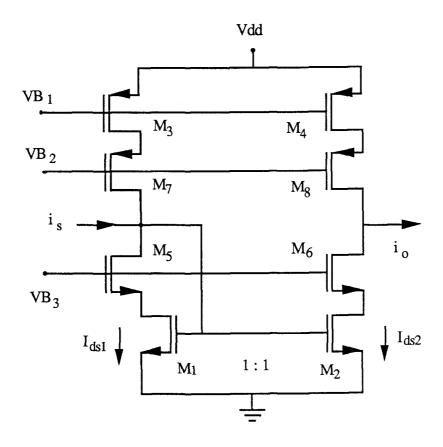

In high-frequency applications, short-channel lengths must be used to increase transconductances and reduce gate capacitances. Unfortunately, the stronger channel-length modulation effects increase the output conductance of each MOSFET proportionally and result in a higher gain error for each stage. To improve the performance in these applications, a cascode current mirror (Fig. 11) should be adopted as the basic building block. Two cascoded MOSFETs are used to replace each MOSFET of previous circuit. The output conductance of each cascoded MOSFET pair can be easily calculated. For example, the equivalent output conductances of MOSFET pair M<sub>3</sub>, M<sub>7</sub> is  $g_{out3,7} = \frac{g_{ds3} g_{ds7}}{g_{ds3} + g_{ds7} + g_{m7}} \approx \frac{g_{ds3} g_{ds7}}{g_{m7}}$

$$g_{out3,7} = \frac{g_{ds3} g_{ds7}}{g_{ds3} + g_{ds7} + g_{m7}} \approx \frac{g_{ds3} g_{ds7}}{g_{m7}}$$

(12a)

The equivalent output conductance is substantially reduced without affecting the high-frequency performance. Hence, the transfer function of this cascode current mirror is

$$\frac{\dot{i}_{0}}{\dot{i}_{s}} = \frac{-g_{m2}gL}{(g_{out2,6} + g_{out4,8} + g_{L})(g_{m1} + g_{out1,5} + g_{out3,7} + g_{s})}$$

(12b)

Using the same parameters as above, from Eq. (12a), the equivalent output conductances g<sub>out1,5</sub>, g<sub>out2,6</sub>, g<sub>out3,7</sub> g<sub>out4,8</sub>, are about 0.08µS, then the gain error of this cascode current mirror is about 0.15 percent, which is adequate for most applications.

Fig. 10 SPICE simulation of finite output resistance effects for circuit of Fig. 9(a), with  $(W/L)_1 = (W/L)_2 = (W/L)_3 = (W/L)_4 = 100 \mu m/10 \mu m$ ,  $R_s = R_L = 0$ , and bias current  $I = 100 \mu A$ .

Fig. 11 Low-voltage cascode current mirror.

#### 3.2 Nonideal MOS Switch Effects

Since MOSFETs are used as switches in switched-current delay circuits, the channel resistance of MOSFETs limits the rate that charge is transferred to the holding capacitor, and thus limits the maximum operating speed.

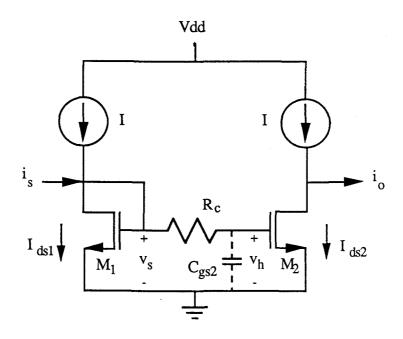

During the sampling period, the channel resistance of the switch can be represented as a simple linear resistor as shown in Fig. 12. Assume the maximum channel resistance of the switch is  $R_c$ , and the holding capacitance is  $C_{gs2}$ . If the input current signal is small relative to the bias current, then the signal voltage on the gate of  $M_1$  is

$$\mathbf{v}_{g1} = \frac{\mathbf{i}_{s}}{\mathbf{g}_{m1}} \tag{13}$$

and the hold voltage after time period  $t = T_s$  is

$$v_{g2} = v_{gs1} (1 - \exp(-\frac{T_s}{R_c C_{gs2}}))$$

(14)

Then the output signal current is

$$i_o = g_{m2} v_{g2} = \frac{g_{m2}i_s}{g_{m1}} (1 - \exp(\frac{-T_s}{R_c C_{gs2}}))$$

(15)

where  $T_s$  is the ON time of the clock period. So a certain amount of error will be generated due to the channel resistance of the switch, and the error is

$$i_{error} = \exp(-\frac{-T_s}{R_c C_{gs2}})i_s. \tag{16}$$

Hence incomplete charge transfer during the clock sampling results in an additional current gain error for each delay stage. To reduce this error, a longer sampling period is required. For example, a raio of  $\frac{T_s}{R_c C_{gs2}} = 6.9$  results in a 0.1 percent current gain error.

#### 3.3. MOSFET Mismatch Effects

From the previous discussion, it is also evident that unlike switchedcapacitor circuits where the filter response is determined by capacitor ratios, the

Fig. 12 Models of the SI T/H circuit with the sampling switch ON and modelled as a linear resistor,  $R_{\rm c}$ .

accuracy of switched-current circuits depends entirely on the matching accuracy of the transistor aspect ratios.

There are several factors affecting the accuracy of the biased current mirror amplifier. Consider a MOSFET that has a size of WxL  $\mu m^2$ . In a square-law saturation condition, the MOSFET is approximately modeled as

$$I_{d} = \frac{\mu C_{ox}}{2} (\frac{W}{L}) (V_{gs} - V_{t})^{2} = \beta (V_{gs} - V_{t})^{2}$$

(17)

where  $I_d$  is the drain current,  $\mu$  is the effective electron mobility,  $C_{ox}$  is the gate capacitance per unit area,  $V_t$  is the threshold voltage, W and L are the effective width and length of the channel, B is the conductance constant.

It has been shown that the mismatching of the conductance constants between two nominally identical MOSFETs is mainly caused by following factors [19][20][31]:

- a. Mismatch due to the edge variations of the channel which is proportional to  $(\frac{1}{1^2} + \frac{1}{W^2})^{1/2}$ ;

- b. The gate oxide capacitance variation;

- c. The carrier mobility variation. Due to the damage in the substrate caused by the threshold adjust implant.

In Fig. 3, assuming two MOSFETs of different conductance constant  $\beta_1$  and  $\beta_2$ , but same threshold voltage  $V_{t1} = V_{t2} = V_t$ , their drain currents are

$$I_{d1} = \beta_1 (V_{gs1} - V_t)^2$$

(18a)

$$I_{d2} = \beta_2 (V_{gs2} - V_t)^2.$$

(18b)

With  $V_{gs1} = V_{gs2} = V_{gs}$ ,  $\beta = \beta_1 + \beta_2$ , and  $\Delta\beta = \beta_1 - \beta_2$ , then the difference of two drain current is

$$\Delta I = I_{d1} - I_{d2} = \Delta \beta (V_{gs} - V_t)^2 = \frac{\Delta \beta}{\beta} I_a,$$

(19)

where  $I_a = \beta(V_{gs} - V_t)^2 = \frac{I_{d1} + I_{d2}}{2}$ . From Eq. 3, we have

$$i_{o} = -i_{s} + \frac{\Delta B}{\beta} I_{a} = -i_{s} + \frac{2\Delta B}{2\beta + \Delta \beta} i_{s} + \frac{2\Delta B}{2\beta + \Delta \beta} I, \tag{20}$$

where I is the bias current. Hence, any deviation of the conductance constant B will generate a current gain error of

$$i_{error} = \frac{2\Delta\beta}{2\beta + \Delta\beta} i_s, \tag{21a}$$

and a current offset of

$$I_{\text{offset}} = \frac{2\Delta\beta}{2\beta + \Delta\beta} I. \tag{21b}$$

On other hand, it had also been shown that the deviation of the threshold voltage in the MOSFET is mainly caused by:

- a. The nonuniform distribution of fixed oxide charge;

- b. The nonuniform distribution of depletion charge;

- c. The nonuniform distribution of implanted ions; and

- d. The variation of gate oxide capacitance.

It has been observed for an n-channel device with a 6μm/3μm size that the standard deviation of the threshold mismatch is about 4 to 5 mV. The threshold mismatch for p-channel devices is about 6 to 10 mv due to the additional threshold adjust implantation [31].

Assuming two MOSFETs have the same conductance constant  $\beta$ , but different threshold voltages  $V_{t1}$ ,  $V_{t2}$ , with  $\Delta V_t = V_{t1} - V_{t2}$  and  $V_{gs1} = V_{gs2} = V_{gs}$ , then the drain current of  $M_2$  is

$$\begin{split} I_{d2} &= \beta (V_{gs} - V_{t2})^2 \\ &= \beta (V_{gs} - V_{t1} + \Delta V_t)^2 \\ &= I_{d1} + \beta \Delta V_t^2 + 2\beta \Delta V_t \sqrt{\frac{I_{d1}}{\beta}} \\ &= I + i_s + \beta \Delta V_t^2 + 2\Delta V_t (\frac{I}{(V_{GS1} - V_{t1})}) (1 + \frac{i_s}{I})^{1/2}, \end{split}$$

(22)

where  $(V_{GS1}-V_{t1}) = \sqrt{\frac{I}{B}}$  is the bias excess voltage of the current mirror. By applying the binomial expansion to the above equation, the output current is [15]

$$i_{o} = i_{s} + \beta \Delta V_{t}^{2} + \left(\frac{2\Delta V_{t}I}{V_{GS} - V_{t1}}\right) \left[1 + \frac{1}{2} \left(\frac{i_{s}}{I}\right) - \frac{1}{8} \left(\frac{i_{s}}{I}\right)^{2} + \frac{1}{16} \left(\frac{i_{s}}{I}\right)^{3} + \dots\right]. \tag{23}$$

Equation (23) shows that threshold voltage mismatch generates a dc current offset of

$$I_{\text{offset}} = \beta \Delta V_t^2 + (\frac{2\Delta V_t I}{V_{\text{GS}} - V_{t1}}), \tag{24a}$$

a linear gain error of

$$i_{error} = (\frac{\Delta V_t}{V_{GS} - V_{t1}})i_s, \tag{24b}$$

and harmonic distortion. The second and third harmonic distortion terms are

$$HD_2 \approx \frac{1}{8} \frac{\Delta V_t}{V_{GS} - V_t} (\frac{i_S}{I})$$

(25a)

$$HD_3 \approx \frac{1}{16} \frac{\Delta V_t}{V_{GS} - V_t} (\frac{i_S}{I})^2$$

(25b)

and the total harmonic distortion is

$$THD = (HD_2^2 + HD_3^2 + ...)^{1/2}$$

(25c)

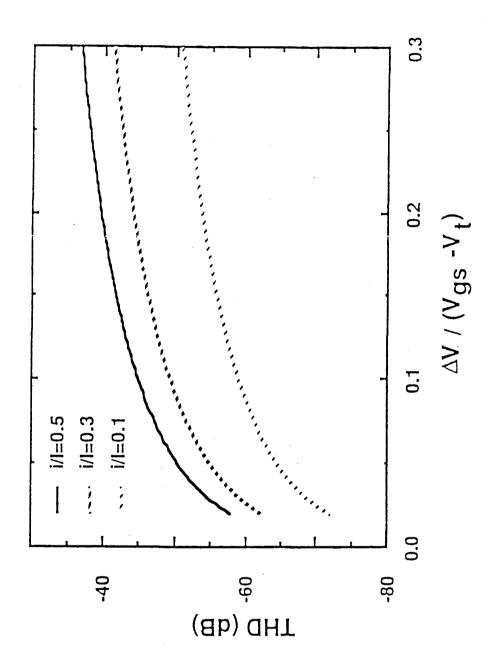

Fig. 13 shows the total harmonic distortion under different bias currents, and threshold voltage mismatches.

### 3.4. Frequency Response

The small-signal equivalent circuit of a simple biased current mirror amplifer with identical stages as its source and load was shown in Fig. 9. Using the small-signal model of Fig. 9(b), it can be shown that the frequency response is

$$H(s) = \frac{(g_L + SC_L)(SC_{gd2} - g_{m2})}{(g_L + SC_L + SC_{gd2})(g_{in} + SC_{gs} + SC_{gd2}) - SC_{gd2}(SC_{gd2} - g_{m2})}$$

(26)

where  $g_{in} = g_s + g_{m1} + g_{ds1} + g_{ds3} \approx g_{m1}$ , and  $C_{gs} = C_{gs1} + C_{gs2} + C_s$ .

After ignoring the small gate-to-drain capacitance of  $M_{2}$ , the dominant pole can be approximated as

$$\omega_{\rm c} \approx \frac{g_{\rm m2}}{C_{\rm gs}} \tag{27}$$

Hence, the small-signal bandwidth of the current amplifier is determined by the transconductance of  $M_2$  and total capacitance of input node. In the previous

Fig. 13 Calculated total harmonic distortion of Eq. 25 under different signal current to bias current ratio.

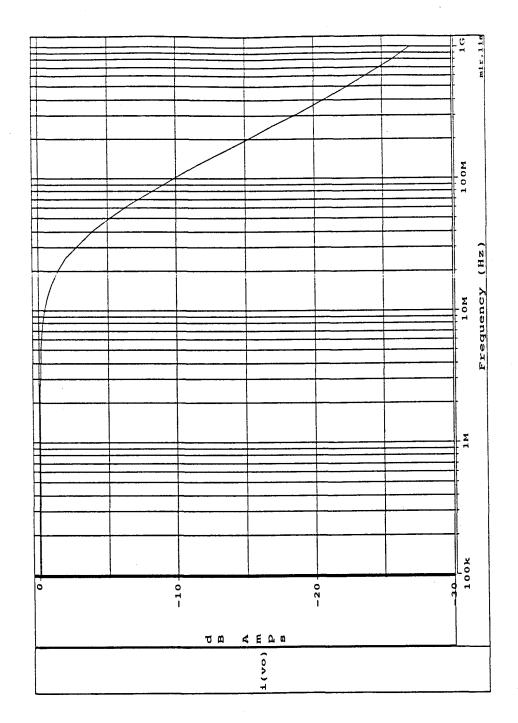

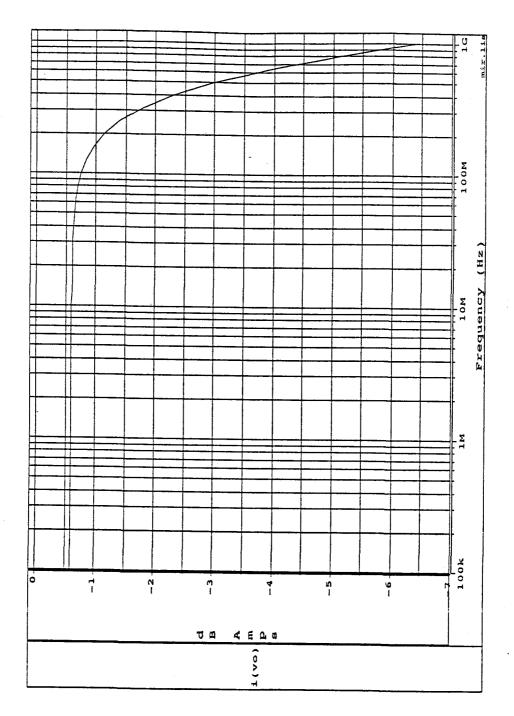

analysis, it was stated that the matching error is inversely proportional to the device feature size. Therefore, the bandwidth of the current mirror is increased by reducing the gate capacitance, but with a decrease in accuracy. Fig. 14 shows the simulated frequency responses of two different current mirrors. Under the same bias current of  $200\mu A$ , when the feature size changes from  $20/2 \mu m$  to  $100/10 \mu m$ , the current mirror bandwidth is reduced from about 650 MHz to about 40 MHz.

# 3.5. Noise and Dynamic Range

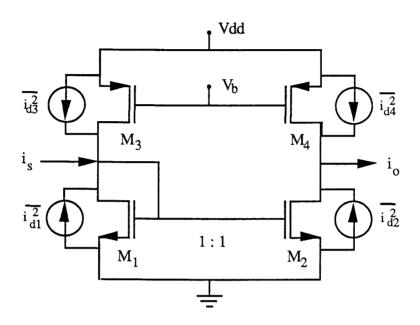

It has been shown that the two dominant noise sources in the MOSFET are the flicker noise and thermal noise [13]. Both are modeled by a single noise current generator from drain to source in the small-signal equivalent circuit as shown in Fig. 15 with a value of .

$$\overline{i}_d^2 = 4kT(\frac{2}{3}\frac{1}{g_m})\Delta f + K_f \frac{I_d^{\alpha}}{f}\Delta f, \qquad (28)$$

where constants  $K_f$  and  $\alpha$  are process dependent,  $i_d$  is the RMS noise drain current, and  $g_m$  is the small-signal transconductance at the dc operating point. The flicker noise is inversely proportional to frequency and has its greatest impact at low frequencies. It can be ignored for high-frequency applications of switched-current circuits.

Based on the equivalent circuit of Fig. 15, the total output noise current of a simple current mirror can be calculated as

$$\bar{i}_{no}^{2} = (\bar{i}_{d1}^{2} + \bar{i}_{d3}^{2})(\frac{g_{m2}}{g_{m1}})^{2} + \bar{i}_{d2}^{2} + \bar{i}_{d4}^{2}$$

(29)

where  $i_{d1}$ ,  $i_{d2}$ ,  $i_{d3}$ ,  $i_{d4}$  are the equivalent RMS noise generators of the four MOSFETs. Assuming unity current gain for the current mirror, then  $g_{m1}=g_{m2}$ , and the input-referred equivalent current noise is

$$\bar{i}_{ni}^2 = \bar{i}_{no}^2 = 4kT(\frac{2}{3})\Delta f(\sum_{i=1}^4 \frac{1}{g_{mi}})$$

(30a)

Fig. 14(a) Frequency response of simple current mirror with  $(W/L)_1 = (W/L)_2 =$   $(W/L)_3 = (W/L)_4 = 100 \mu m/10 \mu m$ ,  $R_s = R_L = 0$ , and bias current  $I = 200 \mu A$ .

Fig. 14(b) Frequency response of simple current mirror with  $(W/L)_1 = (W/L)_2 = (W/L)_3 = (W/L)_4 = 20\mu m/2\mu m$ ,  $R_s = R_L = 0$ , and bias current  $I = 200\mu A$ .

Fig. 15 Noise equivalent circuit of a simple current mirror.

For example, with the feature size W/L =  $100\mu m/10\mu m$ , and bias current I =  $200\mu A$ , then the input refereed noise spectral density is about  $1.48\times10^{-16}A/\sqrt{Hz}$ .

For the cascode current mirror, two MOSFETs are used in each branch. The input referred equivalent current noise is

$$\bar{i}_{ni}^2 = \bar{i}_{no}^2 = 4kT(\frac{2}{3})\Delta f(\sum_{i=1}^8 \frac{1}{g_{mi}})$$

(30b)

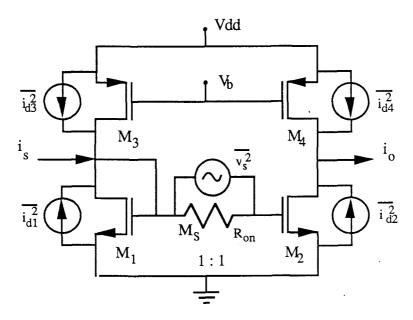

For the delay stage of Fig. 16(a), MOS switch  $M_S$  introduces an extra noise source. Assuming the switch channel resistance is  $R_{on}$ , then the thermal noise power is

$$v_{ns}^{2} = 4kTR_{on}\Delta f, (31a)$$

which generates an output noise current of

$$\bar{i}_{nos}^2 = 4kTR_{on}g_{m2}^2\Delta f. \tag{31b}$$

Hence, the total input-referred current noise of a simple delay stage is

$$\bar{i}_{ni}^2 = 4kT(\frac{2}{3})\Delta f(\sum_{i=1}^4 \frac{1}{g_{mi}}) + 4kTR_{on}g_{m2}^2 \Delta f,$$

(32)

as shown in Fig. 16(b). In general, the sampling frequency must be much less than the noise bandwidth in order to avoid current gain errors caused by the finit circuit bandwidth and switch channel resistance. Because the noise generated by  $M_1$  and  $M_3$  is sampled by the analog switch  $M_s$ . After considering noise aliasing effects, the total input-referred noise spectral density is [32]

total input-referred noise spectral density is [32]

$$S_{i} \approx 4kT \left[ (\frac{BW_{n}}{f_{s}})(\frac{4}{3})(\frac{1}{g_{m1}} + \frac{1}{g_{m3}}) + (\frac{2}{3})(\frac{1}{g_{m2}} + \frac{1}{g_{m4}}) + R_{on}g_{m2}^{2} \right]$$

(33)

where  $BW_n$  is the equivalent noise bandwidth, and  $f_s$  is the sampling frequency. For example, at room temperature if the noise bandwidth is five times higher than the sampling frequency  $f_s$ , and the MOSFETs of the current mirror have  $W/L = 100\mu m/10\mu m$ , bias current  $I = 200\mu A$ , and the maximum channel resistance of the switch is  $10K\Omega$ , then  $S_i \approx 1.48 \times 10^{-15} A/\sqrt{Hz}$ . If the circuit equivalent noise

(a) Simple SI delay circuit with equivalent current noise sources.

(b) Simple SI delay circuit with input-referred current noise source.

Fig. 16 Noise equivalent circuit of a SI delay stage.

bandwidth is 1MHz, then the input-referred RMS noise level is approximately 1.48nA. If the maximum signal level is  $100\mu$ A, then the dynamic range will be about 96dB.

#### 3.6. Conclusions

In this chapter, we analyzed the basic performance of a switched-current circuit. It was shown that the nonideal input/output resistances, and MOSFET mismatches affect the accuracy of SI circuits. Although the resistance loading effects can be reduced using a cascode current mirror, the MOSFET mismatches, especially the threshold mismatch, will degrade the accuracy and cause gain errors and signal harmonic distortion. The switched-current circuits do have the advantages of high operating speed, low power supply voltages, and simpler circuitry.

#### CHAPTER 4. CLOCK FEEDTHROUGH AND CANCELLATION

In the last chapter, it was shown that the difference in excess gate voltages caused by threshold mismatches is one of the major causes of harmonic distortion in switched-current circuits. Unfortunately, there is another large error source which also contributes to this excess gate voltage difference; namely, the clock feedthrough effect. In this chapter, the clock feedthrough effect is analyzed, and a newly developed clock feedthrough cancellation technique is discussed.

## 4.1. Clock Feedthrough Analysis

Clock feedthrough or charge injection is a common problem for all sample-and-hold circuits, and has therefore been investigated by many researchers. Vittoz and Sheu developed the lumped RC-model [30][41]. Kuo and Van Peteghem introduced distributed RC circuits to model the fast turnoff mode of the switch [38], and Kuo also included the charge pumping effects occurring when the gate voltage falls very quickly [17][18].

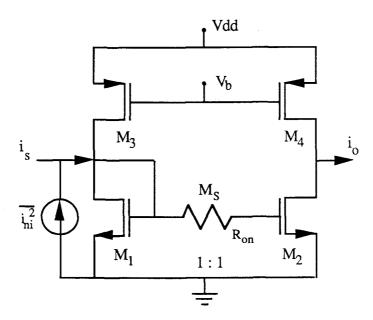

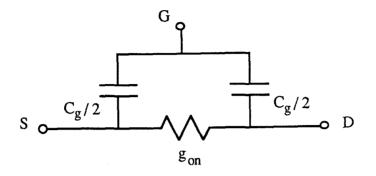

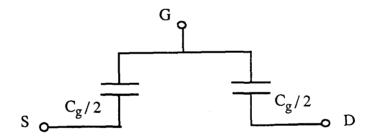

Due to the limitations of circuit bandwidth in switched-current circuit applications, the gate voltage of the analog switch changes much slower than the intrinsic carrier transit time in the transistor. According to the previous work, the analog switch of the sample-and-hold circuit can be described by the lumped RC model as shown in Fig. 17(a) for the ON state and Fig. 17(b) for the OFF state.

For the simple S/H configuration shown in Fig. 18, the gate voltage is assumed to change linearly with time and is expressed as

$$V_{g}(t) = \begin{cases} V_{H} & \text{for } t < 0 \\ V_{H} - \alpha t & \text{for } 0 \le t \le t_{f} \\ V_{L} & \text{for } t > t_{f} \end{cases}$$

(34)

(a) ON state with  $g_{on}$  as channel conductance,  $C_g$  as gate capacitance and  $C_g = 2C_{ovl} + C_{ox}W_{eff}L_{eff}$ .

(b) OFF state with  $C_g$  as gate capacitance  $\label{eq:cg} \text{and } C_g = 2C_{ovl} \; .$

Fig. 17 Lumped RC-model of clock feedthrough

where  $t_f$  is the fall time from the high level  $V_H$  to the low level  $V_L$  of the gate voltage, and  $\alpha$  is the slope of the sampling pulse of period T.

When  $V_g(t) - V_s > V_T$ , the analog switch has a conductive channel with

$$g(t) = \beta(V_g(t) - V_s - V_T)$$

(35)

where  $\beta = \mu_n C_{ox} \frac{W_{eff}}{L_{eff}}$  .is the conductance constant of MOSFET. During the

decrease of the gate voltage, the transistor model of the analog switch is changed from the conductive phase of Fig. 17(a) to the nonconductive phase of Fig. 17(b). For the simple track-and-hold circuit shown in Fig. 18, assume that the error voltages  $v_d$  and  $v_s$  introduced by the clock feedthrough remain small compared to the swing of the gate voltage  $V_H$ - $V_L$ . Then the charge injection can be expressed by two current sources injecting into the drain and source nodes, each of value

$$i_{inj} = C_g \frac{dV_g}{dt} = -\alpha C_g. \tag{36}$$

During the conductive phase,

$$C_g = 2C_{ovl} + C_{ox}W_{eff}L_{eff}$$

(37)

And during the nonconductive phase,

$$C_g = 2C_{ovl} \tag{38}$$

Where C<sub>ov1</sub> is the overlap capacitance between gate and drain or source of the analog switch.

Based on above assumptions, the error voltage of clock feedthrough can be described by the following differential equations:

$$\frac{\partial \mathbf{v}_{\mathbf{S}}}{\partial \mathbf{t}} \, \mathbf{C}_{\mathbf{i}} = \mathbf{g}(\mathbf{t}) (\mathbf{v}_{\mathbf{d}} - \mathbf{v}_{\mathbf{S}}) - \frac{\mathbf{v}_{\mathbf{S}}}{\mathbf{R}_{\mathbf{S}}} + \mathbf{i}_{\mathbf{i}\mathbf{n}\mathbf{j}} \tag{39a}$$

$$\frac{\partial \mathbf{v_d}}{\partial t} C_{\mathbf{L}} = \mathbf{g(t)} (\mathbf{v_s} - \mathbf{v_d}) + \mathbf{i_{inj}}$$

(39b)

By solving two equations above, the clock feedthrough voltage on the hold capacitance can be determined. It has been shown that the clock feedthrough error

$i_{inj} = C_g \frac{dV_g}{dt}$  is the injection current of clock feedthrough,

$V_{\text{d}}$  and  $V_{\text{s}}$  are clock feedthrough error voltages.

Fig. 18 Simple model of SI track-and-hold circuit.

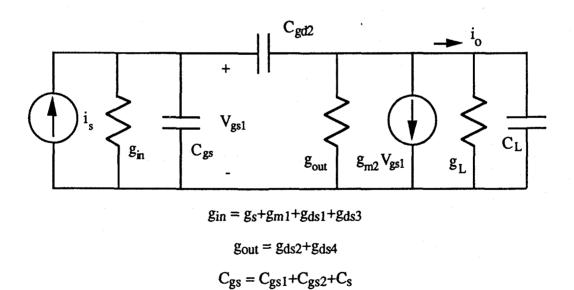

voltage has a typical magnitude of 1 to 20mV, depending on the value of loading capacitance. Fig. 19 shows the effect of clock feedthrough on the output current signal of a delay stage. Combining the clock feedthrough and threshold voltage mismatch term together, the total gate voltage error during the holding period in a switched-current delay stage is

$$\Delta V_{e} = \Delta V_{t} + V_{cf} \tag{40}$$

where  $\Delta V_t$  is contributed by the threshold mismatch, and  $V_{cf} = v_d(t_f)$  is contributed

by the clock feedthrough. Equation (23) can now be rewritten as

$$i_0 = i_s + \beta \Delta V_e^2 + (\frac{2\Delta V_e I}{V_{GS} - V_{II}}) \left[1 + \frac{1}{2} \frac{i_s}{I}\right) - \frac{1}{8} (\frac{i_s}{I})^2 + \frac{1}{16} (\frac{i_s}{I})^3 + \dots \right] \tag{41}$$

From (41), the constant current offset is

$$I_{\text{offset}} = \beta \Delta V_e^2 + (\frac{2\Delta V_e I}{V_{GS} - V_{t1}})$$

(42a)

and the gain error is

$$i_{error} = \frac{\Delta V_e}{V_{GS} - V_{f1}} i_s. \tag{42b}$$

So the current offset, gain error and harmonic distortion are all increased proportionally due to the gate voltage error introduced by clock feedthrough. For example, assuming bias current I = 100  $\mu A$ , (W/L) = 10,  $V_{GS}\text{-}V_{t1}$  = 1 Volt, an error voltage  $\Delta V_e = 10$  mV, will generate offset current of 2  $\mu$ A, and gain error of one percent.

# 4.2. Clock Feedthrough Cancellation

From the previous analysis, it is obvious that the clock feedthrough voltage depends on many different factors such as the source impedance, load impedance, transconductance of the switch, gate voltage slope, source voltage, etc, and most of them are very difficult to precisely control. In conventional voltage-mode circuits, previous cancellation techniques were developed by trying to separate the clock

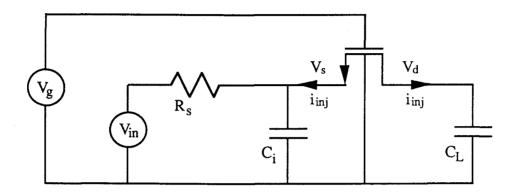

Fig. 19 Clock feedthrough effect on the output current signal of a SI delay stage with  $(W/L)_1 = (W/L)_2 = (W/L)_3 = (W/L)_4 = 100 \mu m/10 \mu m$ , and MOS switch  $(W/L)_s = 6 \mu m/2 \mu m$ ,  $R_s = R_L = 0$ , and bias current  $I = 100 \mu A$ .

feedthrough voltage from the signal voltage. For example, in the dummy switch technique [18], an extra switch is added which is controlled by an opposite polarity clock. The dummy switch turns on while the analog switch is turning off. This technique requires two critically-timed clock phases, and its accuracy depends strongly on interactions between the two clock phase edges which are very difficult to control. In switched-current circuits, it has been shown that by using identical circuit cells, the signal-independent current offset caused by clock feedthrough can be cancelled [11]. In this section, a new circuit is presented to cancel the signal-dependent components in the output current signal.

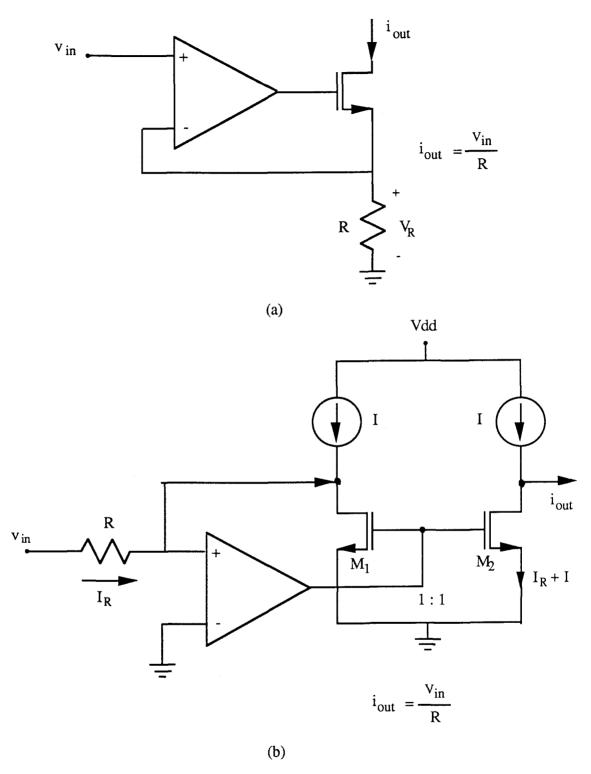

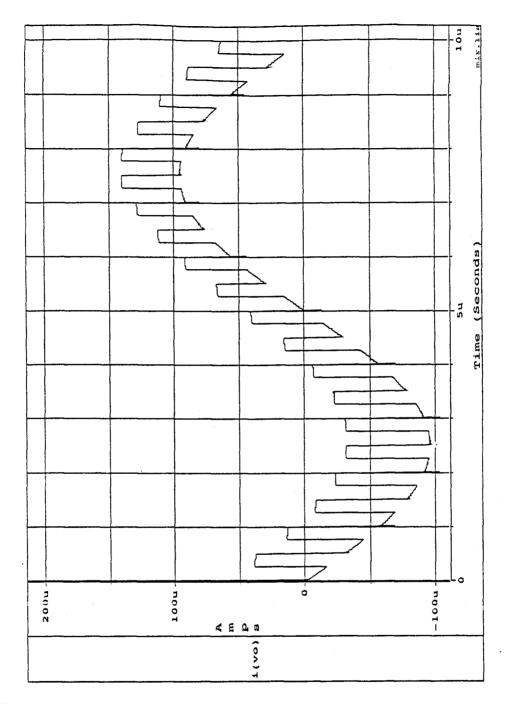

The newly-developed clock feedthrough cancelation circuit is shown in Fig. 20. The sources of two identical MOS switches  $M_{s1}$  and  $M_{s2}$  are connected to the same input node, and their gates are controlled by the same clock signal. Two switches have identical gate and source voltages and identical gate capacitances but different loading capacitance by connecting to MOSFETs of different size. Because the clock feedthrough voltage depends on the loading capacitance, two different clock feedthrough voltage will be generated on the gates of  $M_2$  and  $M_3$  which will cause different error components in the output current signals. By subtracting two different output current signals, the clock-feedthrough error components are canceled.

Assuming

$$M_2$$

,  $M_3$  have the same channel length but different width so that

$$\frac{(W/L)_3}{(W/L)_2} = r \tag{44}$$

where r is a constant. Then the transconductance constants M<sub>2</sub> and M<sub>3</sub> are similarly related

$$\beta_3 = r \beta_2, \tag{45}$$

and the gate capacitances of M2 and M3 are related as

Fig. 20 Simple SI track-and-hold circuit incorporating new clock feedthrough cancellation technique.

$$C_{g3} \approx rC_{g2}. (46)$$

Furthermore, assuming  $V_{cf2}$  and  $V_{cf2}$  are the clock feedthrough voltages on the gates of  $M_2$  and  $M_3$  respectively, because of the different loading capacitance, it can be approximated that

$$V_{cf2} = rV_{cf3} \tag{47}$$

The drain current of M<sub>2</sub> is

$$I_{ds2} = \beta_2 (V_{gs2} - V_{t2} - V_{cf2})^2.$$

(48)

Assuming  $M_1$  and  $M_2$  match,  $\beta_2 = \beta_1$ , and  $V_{t1} = V_{t2} = V_{t3}$ , then

$$I_{ds2} = I_{ds1} - 2\beta_2 (V_{gs1} - V_{t1}) V_{cf2} + \beta_2 V_{cf2}^2$$

(49)

and output current signal is

$$i_{o1} = i_s - 2\beta_2(V_{gs1} - V_{t1})V_{cf2} + \beta_2 V_{cf2}^2.$$

(50)

Similarly since  $V_{gs1} = V_{gs3}$ , the drain current of  $M_3$  is given by

$$I_{ds3} = \beta_3 (V_{gs1} - V_{t3} - V_{cf3})^2.$$

(51)

From (46),  $\beta_3 = r\beta_1$

$$I_{ds3} = rI_{ds1} - 2r\beta_2(V_{gs1} - V_{t1})V_{cf3} + r\beta_2V_{cf3}^{2}$$

(52)

and output current signal is

$$i_{o2} = ri_{s} - 2r\beta_{2}(V_{gs1} - V_{t1})V_{cf3} + r\beta_{2}V_{cf3}^{2}.$$

$$= ri_{s} - 2r\beta(V_{gs1} - V_{T})\frac{V_{cf2}}{r} + r\beta(\frac{V_{cf2}}{r})^{2}.$$

(53)

Subtract equations (49) and (53), the final output current is

$$i_{\text{out}} = i_{\text{o}1} - i_{\text{o}2}$$

=  $(1 - r) i_{\text{s}} - (1 - \frac{1}{r}) \beta_2 V_{\text{cf2}}^2$  (54)

For example, if r = 2, then

$$i_{out} = -i_s - \frac{1}{2} K V_{cf2}^2$$

(55)

Hence, the harmonic distortion and gain error components of the output current signal are cancelled. The clock feedthrough only generates a current offset

$$I_{\text{offset}} = -(1 - \frac{1}{r}) \beta V_{\text{cf2}}^2.$$

(56)

And if the clock feedthrough voltage  $V_{cf2}$  is constant, this constant current offset will not affect circuit performance.

But when input current signal levels varies, MOSFET M<sub>1</sub> has varying gate voltages. Therefore for a constant sampling clock voltage, the gate-to-source voltage of the analog switches is signal dependent. From Eq. (39), the clock feedthrough voltage  $V_{cf2}$  is dependent on the transconductance of the switch. Hence last term of Eq. (55) is signal dependent. To avoid the signal-dependent current offset, an adaptive clock technique is developed as shown in Fig. 21. Two additional source followers are used to track the gate voltage of M<sub>1</sub>. But the PMOS source follower shifts signal voltage up about two volts, and the NMOS source follower shifts the signal voltage down about one volt. And these two signals are used as clock high and low levels respectively to control two analog switches Ms1 and M<sub>s2</sub> as shown in Fig. 22. Because both high and low levels of the clock signal are tracking the gate voltage of M<sub>1</sub>, the transconductances of both switches are kept constant with respect to input signal variations. Therefore the clock feedthrough is independent of input signal, and only a constant current offset is generated after above cancellation circuit. Simulation results have shown that by using the adaptive clock feedthrough

Fig. 21 Simple SI track-and-hold circuit incorporating adaptive clock feedthrough cancellation circuit

Fig. 22 Signal waveforms of adaptive clock feedthrough cancellation circuit.

cancelation circuit with a delay stage of size of W/L =  $20\mu m/2\mu m$ , the total harmonic distortion is reduced from over 10 percent to less than 0.5 percent. Fig. 22 also shows the output current signal waveforms after adaptive clock feedthrough cancellation.

# CHAPTER 5. SWITCHED-CURRENT FILTER DESIGN AND SOME EXPERIMENTAL RESULTS

The conventional approach to switched-current filter synthesis is directly leveraged from switched-capacitor synthesis techniques. It is based on a classic double-terminated LC filter prototype and signal flowgraph techniques. It has the advantage of being directly analogous to existing switched-capacitor circuits. But it has been shown that the unique properties of conventional switched-current circuits limit filter performance [15]. On the other hand, from the previous section it is evident that switched-current circuits have similar functional blocks to that of digital filters. Thus, the synthesis of switched-current filters can also be directly analogous to digital filters, and, many design techniques developed for digital filters can be directly applied to switched-current filter design. In this section, the synthesis of different switched-current digital filters is presented, and the effects of linear gain errors on the filter frequency response are discussed.

### 5.1. Switched-Current Doubly-Terminated Ladder Filter

It has been shown that a passive doubly-terminated LC ladder filter can achieve very low sensitivity to component variations in the passband response [8][9][40]. Many switched-capacitor filters are constructed based on LC ladder filter prototypes. The basic building block is the switched-capacitor differential integrator shown in Fig. 23. Assuming an ideal operational amplifier, its output (sampled on CLK 1) can be expressed as

$$v_{out}(z) = \left(\frac{C_u}{C_I}\right) \frac{(v_1 z^{-1} - v_2 z^{-1/2})}{(1 - z^{-1})}.$$

(57)

Fig. 23 Switched-capacitor differential integrator.

By using the building blocks discussed previously, an analogous switched-current integrator can also be constructed as shown in Fig. 24. Its output signal sampled on CLK 1 is

$$i_{out}(z) = A \frac{(i_1 z^{-1} - i_2 z^{-1/2})}{(1 - z^{-1})}$$

(58)

It is evident that two circuits above have one-to-one correspondence with

$$A = \frac{C_u}{C_I} \tag{59}$$

Therefore by selecting the proper scaling factor A, a switched-capacitor filter can be transformed directly to a switched-current filter. One major difference is that in switched-capacitor circuits only one output node is required, while each input requires a sampling/summing capacitor. In switched-current circuits, the signal summation function is performed by a direct connection of all input current signals to the input node, but each output requires a unique output stage because only one current signal can flow to one destination.

The above switched-current integrator can be used directly to synthesize ladder filters using a modified signal flowgraph method [6]. But it has been shown that due to the limited matching accuracy and more importantly, the clock feedthrough effects of the MOSFET T/H switches, the switched-current technique is unlikely equal the impressive accuracy of switched-capacitor circuits at low frequencies [15].

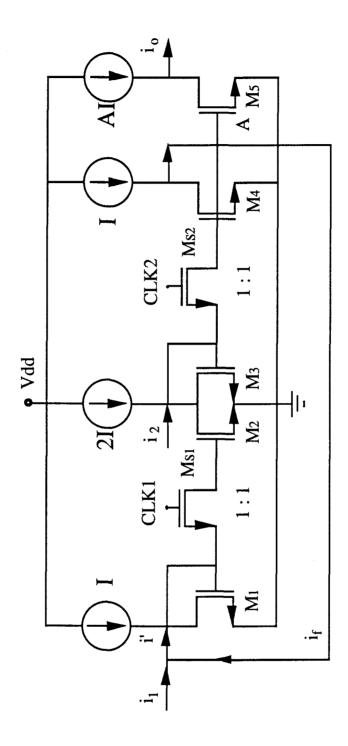

# 5.2. Switched-Current Digital Filter

It is well known that inversion, addition, multiplication and delay are the basic operations required in digital signal processing techniques. From the previous discussion, we see that switched-current circuits can perform similar operations for analog sampled-data signals. Thus, many existing digital signal processing

Fig. 24 First-generation switched-current integrator.

techniques can be directly applied to switched-current circuit design. In this section, different types of switched-current filters are designed based on the same techniques developed for digital filter design.

The simplest digital filter is the Finite-Impuse-Response (FIR) filter. It consists of a number of delay stages determined by the order of the filter. The output of each delay stage is appropriately weighted, and all weighted signals are summed together to produce the final output of the FIR filter.

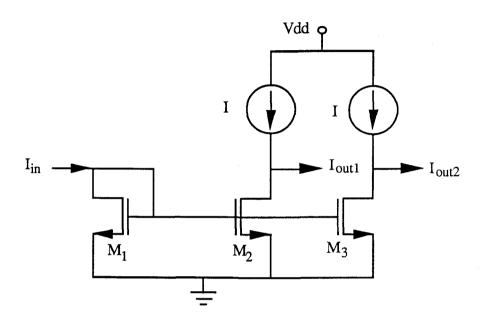

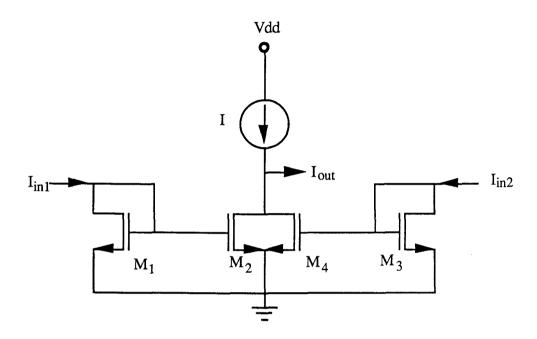

Based on the same structure as the digital filter, the direct-form switched-current FIR filter can be configured as shown in Fig. 25. The input current signal passes through a chain of delay stages. Two identical copies of the current signal are generated by each delay stage. One copy is fed to next delay stage, and the other is forwarded to its scaling stage where it is multiplied by an appropriate weighting coefficient,  $h_k$  (k=0,1,2,... N). Finally, all weighted current signals are then summed in a simple wired-OR fashion to yield the overall output. The frequency response of the FIR filter is given by

$$H(f) = \sum_{k=0}^{N} h_k e^{-j2\pi kf/N}.$$

(60)

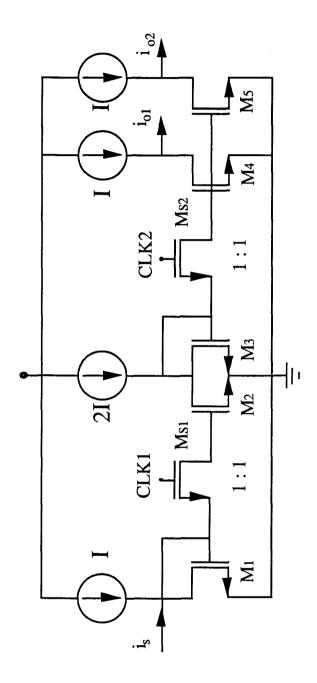

In the above FIR filter, the two output delay stage can be implemented using the circuit shown in Fig. 26. It consists of a cascade of two simple half delay stages driven by two non-overlapping clocks. For the entire filter, all delay stages sample the input current signal during CLK 1 are store a corresponding voltage on the gate capacitance of M<sub>2</sub>. During CLK 2, all delay stages produce output currents which are multiplied by the appropriate coefficients in scaling stages, and finally summed together to generate the output of the filter. Usually, a relatively high scaling ratio is required to implement the different weighting coefficients, but the ratio that is

Fig. 25 Block diagram of an Nth order switched-current FIR filter.

Fig. 26. The full delay stage of switched-current filter with two unity-gain outputs.

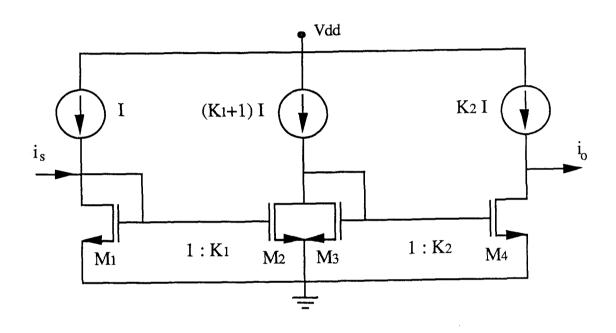

accurately achieved by a single scaling stage is limited by the resolution of the layout and the size of MOSFETs. To implement a high scaling ratio, several scaling stages can be cascaded together as shown in Fig. 27. For a cascade of N stages, the total scaling ratio is

$$K = (-1)^{n} K_{1} K_{2} ... K_{n}$$

(61)

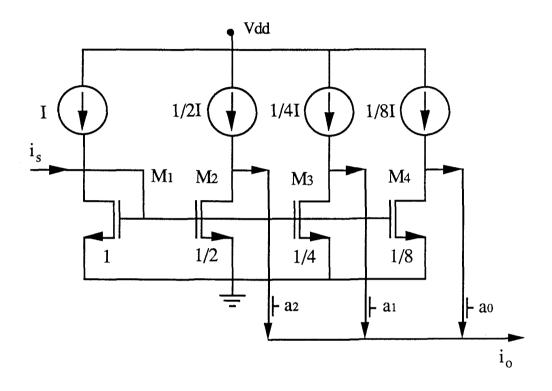

In the special case where the scaling circuitry is binary-weighted, then the scaling ratio can be digitally programmed as shown in Fig. 28. In this example, there are 8 possible scaling ratios that can be selected by controlling the switches  $a_0$ ,  $a_1$  and  $a_2$ . The total scaling ratio is

$$K = -(2^{-1}a_2 + 2^{-2}a_1 + 2^{-3}a_0)$$

(62)

where  $a_i = 1$  when the switch is on, and  $a_i = 0$  when the switch is off. A programmable switched-current filter can be easily implemented using the programmable scaling stage [42].

By using similar techniques, other types of digital filters can also be implemented with switched-current circuits. Fig. 29 shows a direct-form realization of a switched-current Infinite Impulse Response (IIR) filter. An extra input stage is required because the feedback and the input must be added to generate the output signal. This input stage can be implemented by either a current inverter or a delay stage. The frequency response of the IIR filter is

$$H(f) = \frac{1}{\sum_{k=0}^{N} a_k e^{-j2\pi k f/N}}.$$

(63)

Fig. 30 shows a direct-form implementation of a switched-current Auto-Recurssive and Moving Average (ARMA) filter. Hence, each delay stage requires three identical outputs for the feedforward and feedback signal paths, and the input to the next delay stage. Its frequency response is given by

Fig. 27 Cascaded current signal scaling stage with overall current gain of  $K_1K_2$ .

Fig. 28 Digitally-programmable binary-weighted scaling stage with symbols of  $a_0$  -  $a_2$  represent ideal MOS switches.

Fig. 29 Switched-current implementation of a direct form IIR filter.

Fig. 30 Switched-current implementation of an ARMA filter.

$$H(f) = \frac{\sum_{k=0}^{N} b_k e^{-j2\pi kf/N}}{\sum_{k=0}^{N} a_k e^{-j2\pi kf/N}}.$$

(64)

## 5.3. Nonideal Factors and Experimental Results

The frequency response accuracy of a switched-current filter is mostly affected by the gain errors associated with the delay and scaling stages. Eq. (19) shows that any gate voltage mismatch causes a linear gain error. Two major sources of gate voltage mismatch are the threshold mismatch and the clock feedthrough error voltage. Because the threshold mismatches are randomly distributed[19] and clock feedthrough errors are relatively constant, the total gain error can be expressed by a random variable v which has the expected value r.

Assume the gain errors of all delay stages have the same distribution and are independent of each other. For a direct-form FIR filter after considering the gain error of each delay stage, its frequency response can be expressed as

$$H(f) = \sum_{k=1}^{N} h_k v^k e^{-j2\pi kf/N}$$

(65)

where  $v^k$  is the gain error products of previous k stages. The expected value of the filter frequency response is

$$E\{H(f)\} = \sum_{k=1}^{N} h_k E\{v^k\} e^{-j2\pi kf/N}.$$

(66)

If E(v) = r, then

$$E\{H(f)\} = \sum_{k=1}^{N} h_k r^k e^{-j2\pi kf/N}.$$

(67)

So from Eq. (67) the effective filter coefficient  $h_k$ ' is equal to the ideal coefficient  $h_k$  multiplied by an error factor  $r^k$ . If no gain errors are introduced, r = 1, and the ideal

frequency response is achieved. Fig. 32 shows the simulated effects of gain errors on the magnitude response of an eleventh order FIR filter.

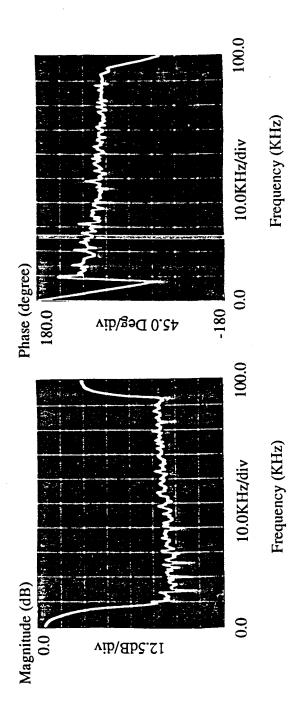

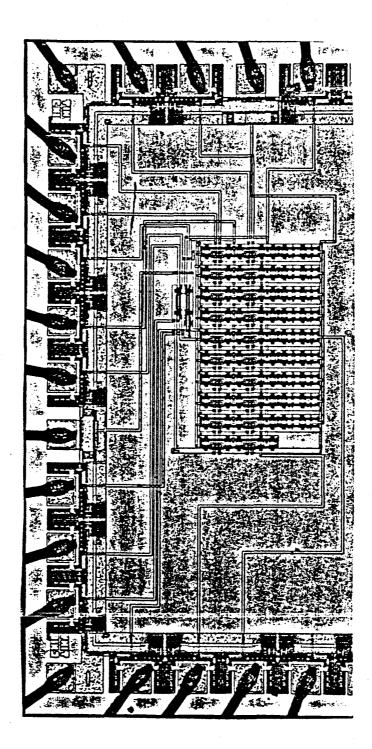

Two switched-current FIR filters have been designed and implemented using the MOSIS 2 µm digital CMOS technology. Table 1 shows the circuit design parameters. Low-voltage cascode current mirrors were used as the basic building block for all delay and scaling stages. Fig. 33 shows the measured magnitude and phase responses of an integrated FIR filter (Lowpass FIR 1) of order 11, Fig. 34 shows the measured magnitude and phase responses of an integrated FIR filter (Lowpass FIR2) of order eight. Finally, Fig. 35 shows the die photo of the 11th-order FIR filter prototype.

Fig. 31 The simulated effects of gain errors on the magnitude response of an eleventh-order FIR filter.

Table 1. The parameters of the switched-current FIR filter prototypes  $\text{with sampling rate of } F_s.$

| Filter Type       | Lowpass FIR1            | Lowpass FIR2            |

|-------------------|-------------------------|-------------------------|

| Order             | 11                      | 8                       |

| Cutoff Frequency  | $0.1F_{\rm s}$          | 0.125F <sub>s</sub>     |

| NMOSFET W/L       | 20μm/2μm                | 20μm/2μm                |

| PMOSFET W/L       | 20μm/2μm                | 20μm/2μm                |

| NMOS Switch W/L   | 4μm/2μm                 | 4μm/2μm                 |

| Bias Current      | 200μΑ                   | 200μΑ                   |

| Power Supply Vdd  | 5V                      | 5V                      |

| Power Dissipation | 24mW                    | 20mW                    |

| Active Die Size   | 550x800 μm <sup>2</sup> | 550x600 μm <sup>2</sup> |

| Maximum Fs Tested | 10MHz                   | 10MHz                   |

Fig. 32 Measured magnitude and phase responses of the 11th-order FIR filter implemented in the 2  $\mu m$  P-well MOSIS CMOS technology.

Fig. 33 Measured magnitude and phase responses of the 8th-order FIR filter implemented in the 2  $\mu m$  P-well MOSIS CMOS technology.

Fig. 34 Die photo of the 11th order FIR filter implemented in the 2  $\mu m$  MOSIS P-well CMOS technology.

### CHAPTER 6. CONCLUSIONS

A new approach for the synthesis of switched-current filters has been developed which uses switched-current building blocks to directly simulate digital filters. This switched-current filter design method has several important advantages over other approaches: (1) By simulating the conventional digital filter, many existing digital filter design techniques can be directly applied to switched-current filter applications. For example, the unique linear phase property of digital FIR filters can now be achieved using analog switched-current FIR filters. (2) The digital switched-current filter has a very simple structure and high modularity since only two basic blocks are required--the delay stage and scaling stage. (3) A digitally-programmable switched-current filter can be easily implemented by using a programmable scaling stage. By changing the coefficients and the filter structure, any filter type can be realized. (4) Since the switched-current filter response depends only on the ratio of MOSFETs as precision components, reasonably accurate frequency responses can be obtained which are insensitive to temperature and processing variations.

The fundamental performance limitations of switched-current filter have been analyzed including the nonideal input/output resistance effects, nonideal switch effects, MOSFET mismatch effects, the limitations of circuit bandwidth, and the performance of noise and dynamic range. Moreover, the relationships among the clock feedthrough voltages, linear gain errors, and harmonic distortion have been investigated. It has been shown that the clock feedthrough and threshold mismatches are the major sources of linear gain errors and harmonic distortion. A clock feedthrough cancellation circuit has been developed to reduce the total linear gain errors and harmonic distortion of switched-current filters.

Several experimental CMOS prototype switched-current filters have been designed and fabricated. These filters demonstrated the advantages of simple structure, easy design procedures, high operating frequency, etc. Several circuit cells were also designed and fabricated to verify the new clock feedthrough cancellation technique which can be used to improve the performance of switched-current filters.

### PART II

### CURRENT-STEERING LOGIC CIRCUIT DESIGN

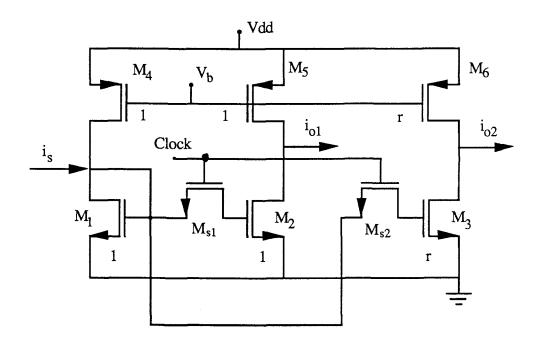

#### CHAPTER 1. OVERVIEW