### AN ABSTRACT OF THE THESIS OF

<u>Christopher Hanken</u> for the degree of <u>Master of Science</u> in Electrical and Computer Engineering presented on August 22, 2007.

Simulation and Modeling of Substrate Noise Generation from

Synchronous and Asynchronous Digital Logic Circuits

Abstract approved:

Terri S. Fiez

Karti Mayaram

Efficient methods for simulating the substrate noise generated by complex synchronous and asynchronous digital logic circuits are presented. By simulating digital logic at the gate level, and precharacterizing the gates, the substrate noise generation can be predicted and used in a transistor level simulation of the sensitive analog blocks. This approach is shown to have better than 20 percent peak-to-peak matching for both traditional CMOS logic and NULL Convention Logic (NCL) by correctly modeling critical gate characteristics. Synchronous and asynchronous versions of a pseudo-random number generator (PRNG) are implemented in a  $0.25\mu$ m CMOS test chip. Simulations validate both a standard transistor level setup and the predictive substrate noise approach against measurements. Simulations of an 8051 processor, with separate synchronous and asynchronous logic cores, are in good agreement with measurements from another  $0.25\mu$ m CMOS test chip, and show validation with a large and complex circuit. ©Copyright by Christopher Hanken August 22, 2007 All Rights Reserved

### Simulation and Modeling of Substrate Noise Generation from Synchronous and Asynchronous Digital Logic Circuits

by

Christopher Hanken

### A THESIS

### submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Presented August 22, 2007 Commencement June 2008 Master of Science thesis of Christopher Hanken presented on August 22, 2007.

APPROVED:

Co-Major Professor, representing Electrical and Computer Engineering

Co-Major Professor, representing Electrical and Computer Engineering

Director of the School of Electric Engineering and Computer Science

Dean of the Graduate School

I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request.

Christopher Hanken, Author

### ACKNOWLEDGEMENTS

I am very grateful for all the experiences and opportunities that I have had at Oregon State University. The staff and faculty have provided me an excellent education and foundation for my career, and life. In particular I would like to thank my advisors, Dr. Terri Fiez and Dr. Kartikeya Mayaram. I have learned so much from both of them, and sincerely appreciate their support throughout my degree.

I would like to thank the institutions which funded my research. In particular the DARPA TEAM and CLASS programs, and SRC under contract 2005-TJ-1299. I also appreciate all the work and technical support provided by the people at Theseus Logic, in particular Mike Hagedorn and Jeff Wilson.

I have had the honor of coming to know a multitude of intelligent students throughout my graduate studies. I would like to thank all of the people in the analog and mixed-signals group for their friendship and mentoring. In particular thanks to Robert Batten, Vova Kratyuk, Min Gyu Kim, Merrick Brownlee, James Ayers, and Thomas Brown for all their help. I would also like to thank everyone I worked with in the substrate coupling group. Martin Held, Kyle Webb, Sasi Kumar Arunachalum, Chenggang Xu, Kavitha Srinivasan, Arthi Sundaresan, Matt McClary, Andrew Tabalujan, Brett Peterson, Waileng Cheong, Jacky Wong, and Bob Shreeve all made working in this research group enjoyable and enlightening.

I have made some very personal friends during my 3 years of graduate study. I would first like to thank Jim Le. Jim and I were together working on classes and research throughout my degree. We were so joined at the hip that, despite our lack of physical similarities, our advisors would continually mix up our names. I would like to thank all of the friends I was fortunate enough to hang out with both at school, and outside of school, including Erik Vernon, Sunwoo Kwon, Nema Talebbeydokhti, Nishant Chadha, Celia Hung, Dave Gubbins, and Jeongseok Chae to name a few. I would also like to give a special thanks to Pavan Hanumolu for his friendship and mentoring. Pavan is a great friend who can just as comfortably discuss a technical problem, or the latest sports news.

Without the support of my family, I would not have been able to accomplish any of this. I would like to thank my brothers Joel and Benjamin, my mother Diane, and my father David, for their love and encouragement. Thank you to Amy, my better half, for always being there. I would also like to thank Amy's family for all their support, including Eddie, Robert, Jen, Beth, and Ed.

I would finally like to thank God for allowing the pieces of my life to come together the way they have. I feel very blessed.

# TABLE OF CONTENTS

|   |       |                                                   | Page |

|---|-------|---------------------------------------------------|------|

| 1 | Intro | oduction                                          | 1    |

|   | 1.1   | Background                                        | . 1  |

|   | 1.2   | Previous Work                                     | . 3  |

|   | 1.3   | Test Chips                                        | . 4  |

|   |       | 1.3.1 Losco Test Chip $\ldots$                    | . 5  |

|   |       | 1.3.2 Eris Test Chip $\ldots$                     | . 6  |

| 2 | Cimu  | lation Sotup                                      | 9    |

| Z |       | llation Setup                                     |      |

|   | 2.1   | Circuit Blocks                                    |      |

|   |       | 2.1.2 8051 Microprocessors                        |      |

|   | 2.2   | Parasitics                                        |      |

|   | 2.3   | Substrate Modeling                                |      |

|   |       |                                                   |      |

| 3 | Digit | tal Macro-Model (DMM)                             | 16   |

|   | 3.1   | Characterization                                  | . 17 |

|   |       | 3.1.1 Substrate Networks                          |      |

|   |       | 3.1.2 Equivalent Parasitics                       |      |

|   |       | 3.1.3 Delay Information3.1.4 Transition Waveforms |      |

|   | 3.2   |                                                   |      |

|   | 3.2   | Simulation Flow                                   |      |

|   |       | 3.2.2 Substrate Noise Simulation                  |      |

|   |       |                                                   |      |

| 4 | Simu  | lation Results                                    | 31   |

|   | 4.1   | Pseudo-Random Number Generators                   | . 31 |

|   |       | 4.1.1 Transistor Level Simulation                 |      |

|   |       | 4.1.2 Digital Macro-Model                         | . 37 |

|   | 4.2   | 8051 Microprocessor                               | . 38 |

| 5 | Criti | cal Aspects of Substrate Noise Simulation         | 41   |

| 0 | 5.1   | On-Chip Buffers                                   |      |

|   | U. 1  |                                                   |      |

# TABLE OF CONTENTS (Continued)

|            |                                   | Page |

|------------|-----------------------------------|------|

| 5.2        | Capacitance Between Interconnects | . 43 |

| 5.3        | Capacitance to Substrate          | . 44 |

| 5.4        | High Frequency Substrate Model    | . 45 |

| 6 Con      | clusions                          | 48   |

| 6.1        | Summary                           | . 48 |

| 6.2        | Lessons Learned                   | . 50 |

| 6.3        | Future Work                       | . 51 |

| Bibliog    | caphy                             | 57   |

| Appendices |                                   | 60   |

# LIST OF FIGURES

| Figure |                                                                                                                     | Page |

|--------|---------------------------------------------------------------------------------------------------------------------|------|

| 1.1    | Model previously used to represent the digital gates                                                                | . 4  |

| 1.2    | Die photo for the Losco test chip.                                                                                  | . 5  |

| 1.3    | Die photo for Eris test chip.                                                                                       | . 7  |

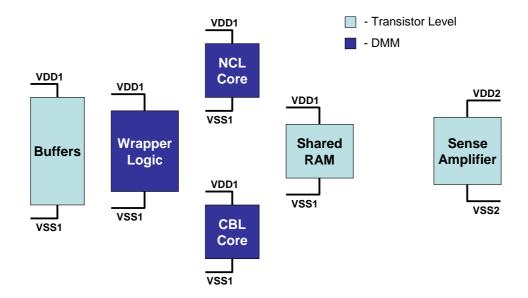

| 2.1    | Block diagram showing the circuit setup for the simulation of the PRNG blocks.                                      | . 10 |

| 2.2    | Block diagram showing the circuit setup for the simulation of the 8051 microprocessor cores.                        | . 12 |

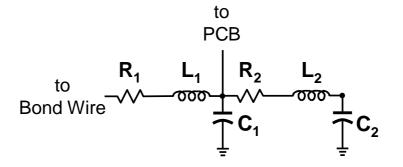

| 2.3    | Model used to represent the parasitics of the package                                                               | . 13 |

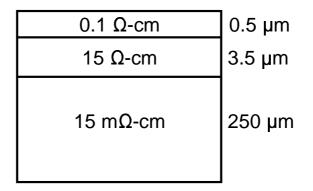

| 2.4    | Approximated 3-layer profile for the TSMC $0.25\mu$ m heavily doped substrate.                                      | . 14 |

| 2.5    | Model used to represent the substrate.                                                                              | . 15 |

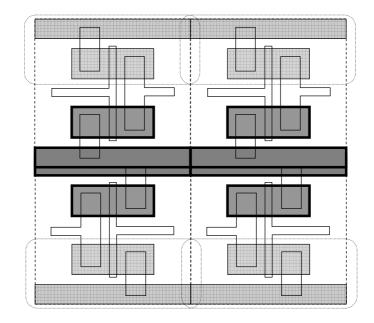

| 3.1    | Flow chart showing all the steps in the digital macro-modeling (DMM) method                                         | . 16 |

| 3.2    | The parasitics of a simple inverter.                                                                                | . 19 |

| 3.3    | Equivalent parasitics of an inverter when the input is held low and<br>the overlap capacitances are ignored.        | . 20 |

| 3.4    | Supply current of a flip-flop for a given input pattern when the output (a) changes state, and (b) remains the same | . 24 |

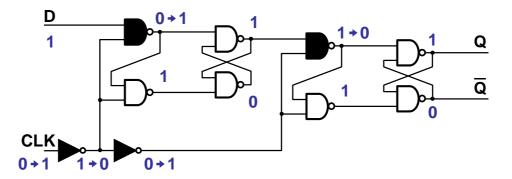

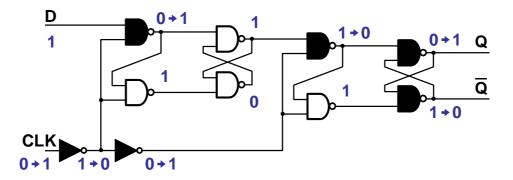

| 3.5    | Internal logic branches switching when a D-type flip-flop does not change states.                                   | . 25 |

| 3.6    | Internal logic branches switching when a D-type flip-flop changes states.                                           | . 26 |

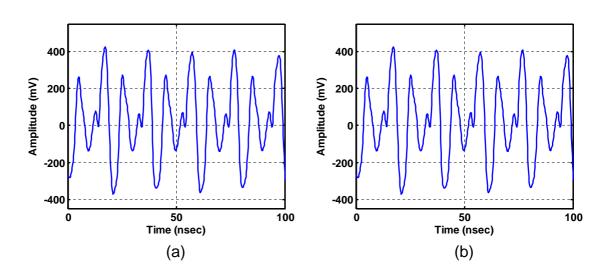

| 4.1    | Comparison of time domain (a) measurements, and (b) simulations for the CBL PRNGs.                                  | . 33 |

| 4.2    | Comparison of frequency domain (a) measurements, and (b) simulations for the CBL PRNGs                              | . 33 |

# LIST OF FIGURES (Continued)

| Figure |                                                                                                                                                        | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.3    | Comparison of time domain (a) measurements, and (b) simulations for the NCL PRNGs                                                                      | 34   |

| 4.4    | Expanded time scale comparison of (a) measurements, and (b) simulations for the NCL PRNGs.                                                             | 35   |

| 4.5    | Comparison of a test setup with the NCL PRNGs with (a) constant Vth, and (b) varied Vth                                                                | 36   |

| 4.6    | Comparison of frequency domain (a) measurements, and (b) simulations for the NCL PRNGs                                                                 | 37   |

| 4.7    | Comparison of time domain (a) transistor level simulations, and (b) DMM simulations for the CBL PRNGs                                                  | 38   |

| 4.8    | Comparison of time domain (a) transistor level simulations, and (b) DMM simulations for the NCL PRNGs.                                                 | 39   |

| 4.9    | Comparison of time domain (a) measurements, and (b) DMM simulations for the CBL 8051 microprocessor core                                               | 40   |

| 4.10   | Comparison of time domain (a) measurements, and (b) DMM simulations for the NCL 8051 microprocessor core.                                              | 40   |

| 5.1    | Comparison between (a) the complete simulation of the CBL PRNGs, and (b) the same simulation with the IO buffers' substrate network removed.           | 42   |

| 5.2    | Comparison between (a) the complete simulation of the CBL PRNGs, and (b) the same simulation with coupling capacitances between interconnects removed. | 43   |

| 5.3    | Comparison between (a) the complete simulation of the CBL PRNGs, and (b) the same simulation with the pad capacitances to substrate removed.           | 45   |

| 5.4    | The substrate $\pi$ -network incorporating higher frequency effects                                                                                    | 46   |

| 5.5    | Comparison between (a) the complete simulation of the CBL PRNGs,<br>and (b) the same simulation with the high frequency substrate model                | . 47 |

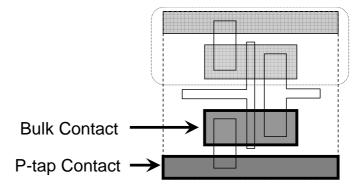

| 6.1    | Substrate contacts defined for a single gate.                                                                                                          | 55   |

# LIST OF FIGURES (Continued)

| Figure |                                                                     | Page |

|--------|---------------------------------------------------------------------|------|

| 6.2    | Example of defined substrate contacts for individual gates overlap- |      |

|        | ping in the layout.                                                 | . 56 |

# LIST OF TABLES

| <u>Table</u> |                                                          |  |  | P | age |

|--------------|----------------------------------------------------------|--|--|---|-----|

| 6.1          | Execution time of different substrate noise simulations. |  |  |   | 49  |

### LIST OF APPENDICES

|                                                      | Pag | ;e            |  |  |

|------------------------------------------------------|-----|---------------|--|--|

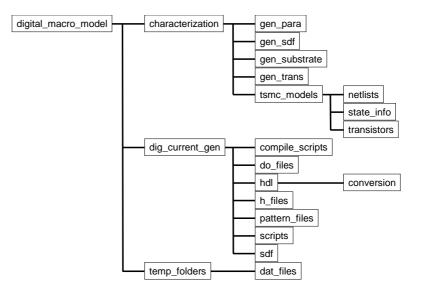

| A Using the DMM Method                               | 6   | 1             |  |  |

| A.1 File System                                      | 6   | 2             |  |  |

| A.2 Characterization                                 |     | 5             |  |  |

| A.2.1 Model Information                              |     | -             |  |  |

| A.2.2 Generate Substrate                             |     | 0             |  |  |

| A.2.3 Generate Transition Waveforms                  |     | 1             |  |  |

| A.2.4 Generate SDF                                   |     | 5             |  |  |

|                                                      |     |               |  |  |

| A.3 Digital Noise Current Generation                 |     | -             |  |  |

| A.4 Making a New Setup                               |     | -             |  |  |

| A.4.1 HDL Simulation                                 |     |               |  |  |

| A.4.2 Library Characterization A.4.3 Generate Script |     | $\frac{2}{5}$ |  |  |

|                                                      |     |               |  |  |

| A.5 A Different Application                          |     | 6             |  |  |

| B Silencer! Adjustments 98                           |     |               |  |  |

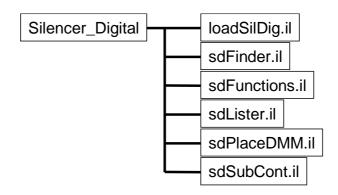

| B.1 Silencer! Digital                                | 9   | 9             |  |  |

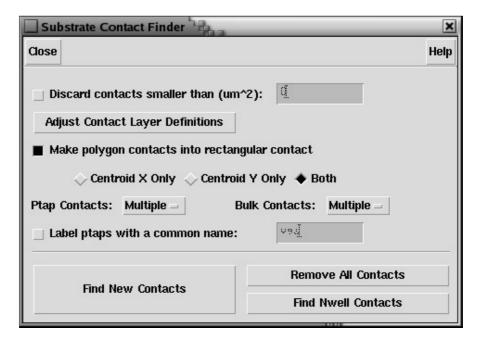

| B.1.1 Contact Finder                                 |     |               |  |  |

| B.1.2 Contact Lister                                 |     |               |  |  |

| B.1.3 DMM Placing Tool                               |     |               |  |  |

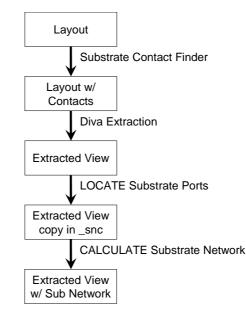

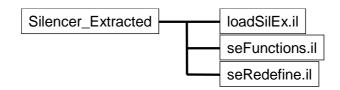

| B.2 Silencer! Extracted                              |     |               |  |  |

| B.2.1 Diva Extraction Rules                          |     |               |  |  |

| B.3 Various Adjustments                              |     |               |  |  |

# LIST OF APPENDIX FIGURES

| Figure | Page                                                                                                         |

|--------|--------------------------------------------------------------------------------------------------------------|

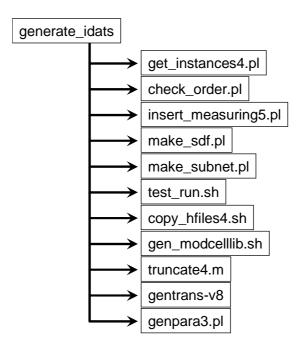

| A.1    | The folder system for the DMM as a tree graph                                                                |

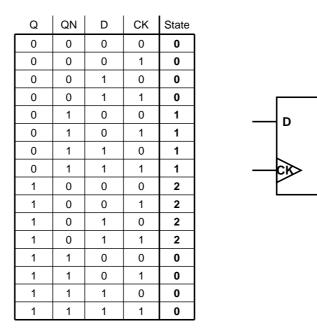

| A.2    | Example of a state map for a simple D-type flip-flop                                                         |

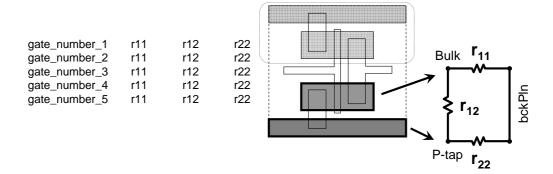

| A.3    | Representation showing the way the resistive substrate model for<br>each gate is saved                       |

| A.4    | The matrix format for saved transition data of a hypothetical gate<br>with one input and two internal states |

| A.5    | The program flow of the digital noise current generation 87                                                  |

| B.1    | The file system for Silencer! Digital as a tree graph                                                        |

| B.2    | GUI of the Contact Finder                                                                                    |

| B.3    | GUI for adjusting the substrate contact layer definitions 104                                                |

| B.4    | GUI of the Contact Lister                                                                                    |

| B.5    | GUI of the DMM Placing Tool                                                                                  |

| B.6    | Flow chart describing the steps to use Silencer! Extracted 112                                               |

| B.7    | The file system for Silencer! Extracted as a tree graph                                                      |

# DEDICATION

To Amy, for always believing in me

# Chapter 1 – Introduction

The prediction of substrate noise coupling effects in Systems-on-a-Chip (SoC) is becoming an increasingly important issue. As larger numbers of circuits are integrated on the same substrate, the differences between ideal simulations and the actual performance of the silicon can become pronounced. If coupling issues are discovered and addressed in simulation, appropriate and adequate steps can then be taken to reduce or isolate the noise.

This thesis describes methods and considerations for the simulation of substrate noise. This chapter examines the background and previous work on which this thesis is based. Chapter 2 describes the setup of the simulation tests. An improved method for modeling digital circuitry for substrate noise simulation is presented in Chapter 3. Results for the simulation tests are presented in Chapter 4. Chapter 5 analyzes different aspects of substrate noise simulation. Finally, conclusions and future work are described in Chapter 6.

#### 1.1 Background

As IC technologies continue to scale down, high power consumption in traditional CMOS digital logic makes the exploration of alternative implementations more appealing. One such alternative is asynchronous digital logic, such as NULL Convention Logic (NCL) [1]. This logic presents advantages in power consumption, synchronous switching, and subsequently, substrate noise [2]. It is, therefore, important to simulate the substrate noise generation from these alternative implementations.

The simulation of substrate noise is most accurate with complete knowledge of how the circuits will be laid out in silicon. Post-layout information provides a substrate network which is complete. By incorporating this substrate network with a full transistor and parasitic description of the circuitry, the substrate noise simulations can be accurately matched with measurements. Several tools are available to facilitate post-layout simulation, including the Cadence tool SNA [3] and Silencer! [4].

In contrast, pre-layout simulation is of particular interest for designers. Earlier discovery of substrate noise issues allows for adjustments not only at the layout level, but also at the schematic level. A methodology is presented which facilitates pre-layout substrate noise simulations. With a Hardware Description Language (HDL) netlist of the digital block, the digital block's substrate noise behavior is simulated using the characterization information generated from a standard cell library. Along with a schematic level netlist of the analog block, substrate noise is estimated without final layout information.

Similar methodologies for substrate noise prediction have been presented in [5, 6, 7, 8]. However, none of these have addressed the simulation of noise in asynchronous circuits. The method presented in this thesis accounts for key issues that are critical for predicting the noise generated in asynchronous circuits. Specifi-

cally, the effect of the delay modeling and state information in asynchronous logic is examined. An advanced delay model and an approach that accounts for the internal states of a sequential gate have been developed. These form the basis for an efficient and accurate approach for simulation of substrate noise.

#### 1.2 Previous Work

The method for modeling the substrate noise behavior of digital blocks, or digital macro-models (DMM), presented in this thesis is based upon previous work [9, 10]. The basic concept behind these models is to simplify the simulation by deriving a model for the digital logic which retains the correct substrate noise injection characteristics. By simulating the digital logic with a HDL, the correct switching behavior of the logic is preserved. This is an idealized simulation which gives no substrate noise information. A mapping of the switching of a digital gate to the amount of current through the ports of the gate allows calculation of the substrate noise. The simulation is now a two step process, the simulation of the HDL for switching and the simulation of the current sources along with the sensitive circuits. The advantage of the two step process is the efficiency and speed increase over the equivalent single simulation at the transistor level. Much of the digital gate information preserved by a full transistor level simulation is not needed in substrate noise simulations.

The DMM presented in [10] requires two library characterization steps. Standard cell libraries for digital gates need to be characterized for the simulation of

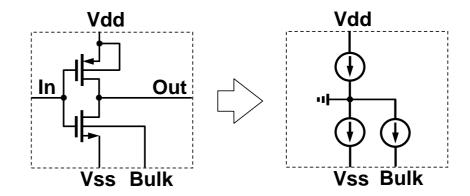

Figure 1.1: Model previously used to represent the digital gates.

substrate noise through this method. The first characterization determines the gate's local substrate network. The second characterization determines the current waveforms used when mapping switching information to the equivalent gate model for the final substrate noise simulation.

The gate model of an inverter for the DMM presented in [10] is shown in Fig. 1.1. In this model, the non-linear transistors are replaced with current sources. The sources model the current passing through the gate ports to the supply lines. The gate model has no input or output ports. The digital signal information passed between gates is represented only by the changes in the current sources.

#### 1.3 Test Chips

Two test chips (Losco and Eris) were fabricated in TSMC's  $0.25\mu$ m logic process. The test chips have clocked Boolean logic (CBL) and NCL versions of digital logic circuitry implemented on each. This section describes the circuits and implementations on the test chips. The lab setup and measurements are presented in more

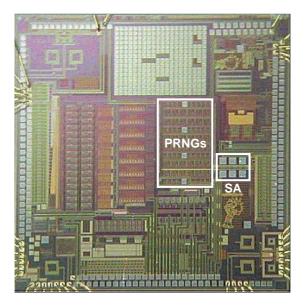

Figure 1.2: Die photo for the Losco test chip.

detail in [11].

#### 1.3.1 Losco Test Chip

The die photo for the Losco test chip is shown in Fig. 1.2. The pseudo-random number generators (PRNGs) are the digital circuitry implemented on this chip in both CBL and NCL versions. There are 72 PRNGs, 36 CBL and 36 NCL, interdigitated in the region indicated in Fig. 1.2. The PRNG block is a combination of an adder, multiplier, and register. When correctly seeded the PRNG generates a pseudo-random number sequence. The sequence repeats every 256 cycles, and generates a digital word representing numbers between 0 and 255.

A sense amplifier was implemented on the Losco test chip in the region labeled

'SA' in Fig. 1.2. This circuit is approximately  $200\mu$ m from the closest edge of the PRNGs. The sense amplifier is a differential low gain, wide bandwidth amplifier, which has one input capacitively coupled to a dedicated 'quiet ground' pin, and another input capacitively coupled to the substrate [12, 13]. The amplifier is designed to drive 50  $\Omega$  loads through ground-signal-ground (GSG) probes placed directly on the die.

The CBL PRNGs are clocked at the equivalent operating frequency of the NCL PRNGs. The equivalent operating frequency is defined as the rate the CBL circuitry must be clocked to complete the same functions as the NCL over the same time period. After testing, this was found to be approximately 50MHz for the PRNGs.

Each version of PRNGs is tested at separate times for comparisons between the CBL and NCL logic. The printed circuit board (PCB) used to test the chip has jumpers for disconnecting any unused pins, so all pins not used in a particular test are left floating. The signal generator used for the CBL clock has rise and fall times of 1.5ns. All circuits were supplied with on-PCB regulation of 2.5V except the buffers which required 3.3V.

#### 1.3.2 Eris Test Chip

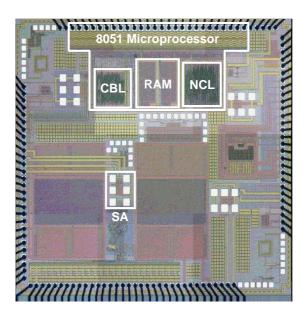

The die photo for the Eris test chip is shown in Fig. 1.3. An 8051 microprocessor was designed with two separate cores in the region indicated. One core was designed using CBL, and the other core with NCL. Both 8051 cores share the RAM,

Figure 1.3: Die photo for Eris test chip.

IO buffers, and wrapper logic. The wrapper logic is a collection of digital gates used to connect and control the signals between the different sections of the microprocessor. The cores can operate separately for characterization of their substrate noise generation. The shared RAM is loaded with a program which generates a random number sequence in an effort to create random substrate noise with limited program memory.

The same sense amplifier implemented on the Losco test chip, is also implemented on the Eris test chip in the region labeled 'SA' in Fig. 1.3. This circuit is approximately 1mm from the 8051 microprocessor cores.

As done in the PRNG setup, the CBL core is clocked at the equivalent operating speed of the NCL core. This equivalent frequency was determined to be 33MHz for the 8051 microprocessor. It may be confusing to note that this frequency is no longer the same as the PRNG blocks, while the technology and logic libraries are exactly the same. However, the NCL and CBL are not directly comparable. The number of gates and configurations are synthesized differently. For this reason, different configurations of digital logic offer slower or faster equivalent operating speeds.

#### Chapter 2 – Simulation Setup

Substrate noise is a deterministic noise source. The transitioning of digital gates injects noise into the substrate at levels much higher than random noise. For this reason, substrate noise can be accurately predicted in a transient simulation. This chapter describes the setup of the transient simulations presented in this thesis. The setup of the circuit blocks is described in the first section. The second section presents the parasitic modeling used in simulations. The final section examines the substrate and its modeling in simulations.

#### 2.1 Circuit Blocks

Transistor level simulations are the most accurate method for transient simulation. Transistors, however, are non-linear devices, and require significant computational time to converge to a solution. Although the full transistor level simulation is accurate, there is a significant trade off in terms of simulation time and convergence issues. Replacing transistor level descriptions of digital blocks with an equivalent DMM reduces both the number of instances and nodes in a substrate noise simulation. However, only digital blocks composed of gates from a standard cell library can be replaced by an equivalent DMM. This section presents a top level description of the circuit blocks used in the simulations.

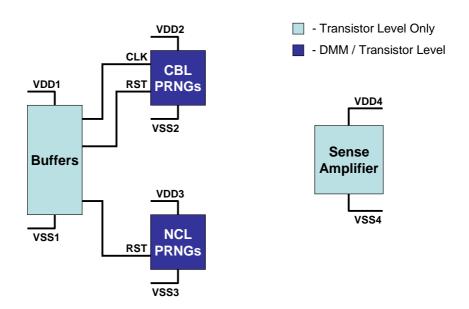

Figure 2.1: Block diagram showing the circuit setup for the simulation of the PRNG blocks.

#### 2.1.1 Pseudo-Random Number Generators

A block diagram of the circuit setup for the PRNG simulations is shown in Fig. 2.1. The IO buffers and sense amplifier are simulated as transistor level blocks. Although the IO buffers are digital blocks, they are not composed of gates from a standard cell library, and cannot be replaced with an equivalent DMM. The CBL and NCL PRNG blocks have both transistor level and equivalent DMM versions. Simulation of the transistor level PRNG blocks is performed for comparison with the measurements. The DMM versions are simulated and compared with the transistor level versions for validation of the DMM methodology.

The connections in the circuit setup are identical to those in the test chip. The supply lines for each circuit block have separate pins for VDD and VSS. The clock and reset lines are connected through the IO buffers to the PRNG circuits. The DMM versions of the PRNGs have the clock and resets aligned correctly with the outputs of the IO buffers. This alignment is required for correct timing of substrate noise injections from the different circuit blocks.

#### 2.1.2 8051 Microprocessors

A block diagram of the circuit setup for the 8051 microprocessor simulations is shown in Fig. 2.2. The sense amplifier is simulated as a transistor level block. The DMM method was used on three separate blocks in the 8051: the NCL core, the CBL core, and the wrapper logic. Each block described as an equivalent DMM is characterized twice, once for the running of the NCL core, once for the running of the CBL core. Although one core is turned off during operation of the other, the equivalent gate parasitics are required for accurate simulation. The IO buffers and RAM blocks are not implemented with discrete gates and must be simulated at the transistor level. Simulation of the complete microprocessor at the transistor level is not possible due to convergence issues of such a large circuit. The circuit setup is simulated and compared with measurements.

Since the RAM is described at the transistor level, it must have the correct stimulus and initial conditions to operate correctly. An adjusted version of the DMM is used to find the input switching voltages to the RAM (described more in Appendix A). This facilitates the simulation of the RAM without simulating the rest of the microprocessor at the transistor level. The initial conditions for the

Figure 2.2: Block diagram showing the circuit setup for the simulation of the 8051 microprocessor cores.

RAM are found by a separate simulation. By simulating the RAM block alone, and with a simpler transistor model, the program memory is loaded. The final conditions for this simulation are used as the initial conditions for the RAM in all 8051 microprocessor simulations.

The p-tap connections of other circuits on the Eris test chip have their ground pins always connected, and must be modeled for the 8051 microprocessor simulations. Two large digital signal processing (DSP) blocks, a delta-sigma modulator (DSM), and the buffers for the DSPs all have low resistance paths from the single node backplane out through their ground pins. All of these connections to the substrate network are included in the simulations.

Figure 2.3: Model used to represent the parasitics of the package.

#### 2.2 Parasitics

The modeling of off-chip parasitics is critical for the simulation of substrate noise. These off-chip parasitics include bond wires, packaging, socket, and PCB. All the simulations in this thesis pay careful attention to accurately modeling these parasitics.

The bond wires are modeled with the approximation that a gold bond wire of 1 mil diameter has 1 nH/mm of inductance and 50 m $\Omega$ /mm of resistance. The length of the bond wires are determined for each setup, and used in simulation.

The package is modeled based on the manufacturer's data. The package for the 8051 microprocessors (Eris) is a Kyocera ceramic PGA132. The package for the PRNG circuits (Losco) is a Kyocera ceramic PGA257. However, there is no available manufacturer's characterization for the PGA257. The next closest size was the PGA132 package, so an extrapolation of the parasitics is used. The package model given on the data sheet is shown in Fig. 2.3. The ground in the model is assumed to be an ideal ground for the simulations.

The socket and PCB parasitics are the most difficult to model for simulation.

Figure 2.4: Approximated 3-layer profile for the TSMC  $0.25\mu$ m heavily doped substrate.

There are not many socket models readily available, and PCB parasitics require the use of more complicated physical modeling to extract a SPICE/Spectre model. For the test cases presented in this thesis, large decoupling capacitors are placed very close to the chip on the PCB. Large ground planes make it possible to assume ideal supply and ground at these decoupling capactors. An inductor in series with a resistor is therefore used as a simple model for the socket and PCB trace. By using the method described in [14], both values are determined and used in simulation.

### 2.3 Substrate Modeling

Heavily doped substrates with a high resistivity epitaxial layer are commonly used to avoid latch-up issues in SoCs. The profile for the TSMC  $0.25\mu$ m logic process (a heavily doped process) was approximated as the 3 layer profile shown in Fig. 2.4. In this substrate, the bottom layer has a much lower resistivity and is considered to be single node for the entire chip [15].

Figure 2.5: Model used to represent the substrate.

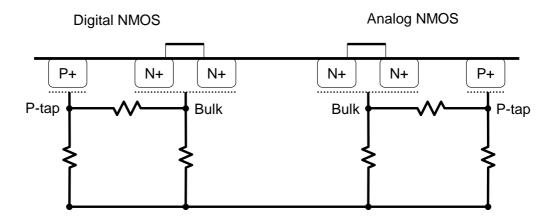

Using this single node approximation, the digital and analog block's substrate networks are extracted separately. As long as the blocks have adequate separation (4 times the epitaxial layer and channel stop layer thicknesses [15]), the crosscoupling can be assumed to be negligible compared to the coupling through the single backplane node.

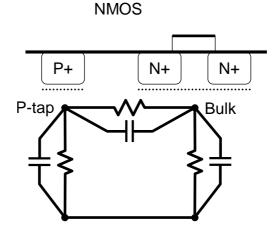

For frequencies below 1GHz, the substrate network is modeled as a resistive network [16]. Since the PMOS transistors are isolated in n-wells, their substrate noise coupling is significantly reduced and, consequently, their connections to the substrate need not be modeled very accurately. A capacitor in series with a resistor from the power supply to the backplane is used. The NMOS transistors are connected to a  $\pi$ -model substrate network as shown in Fig. 2.5. Both the p-taps and the transistor bulk terminals are shown.

The resistive substrate network can be extracted using finite difference [16, 17] or boundary element methods [18, 19]. The extractions for this thesis have used EPIC, a Green's function based boundary element solver [20].

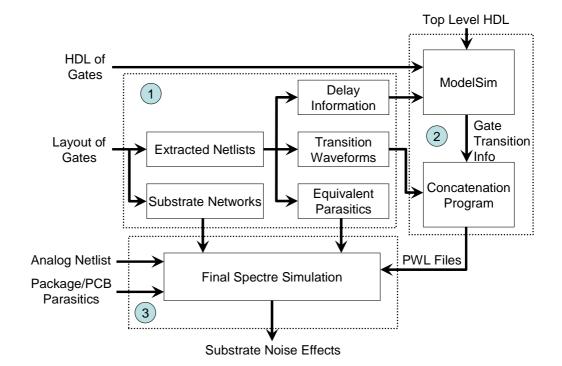

Figure 3.1: Flow chart showing all the steps in the digital macro-modeling (DMM) method.

### Chapter 3 – Digital Macro-Model (DMM)

The improved DMM method presented in this thesis is described with the flow chart shown in Fig. 3.1. The flow is divided into three distinct parts. The first part is the characterization. The second is the digital noise current generation. The third part is the substrate noise simulation. All parts are described in this chapter, with the digital noise current generation and substrate noise simulation both being incorporated in the simulation flow section.

#### 3.1 Characterization

Before the creation of a DMM for a digital block, the standard cell library used must be characterized. The standard cell library implemented in a specific technology is characterized gate by gate. Both a transistor and HDL netlist of each gate in the library is required for characterization.

There are four types of characterization for each gate. These are displayed, along with the extraction of netlists (described briefly in the transition waveforms section), as Part 1 in Fig. 3.1. The following subsections will describe the different characterizations. More specific details on coding and how the characterizations are done is described in Appendix A.

#### 3.1.1 Substrate Networks

The substrate network for the complete digital block is a combination of locally derived gate substrate networks. The local substrate networks for each gate are  $\pi$ -networks representing the resistances between the bulk contact (active region) of the transistor, the p-tap contacts, and the single-node approximated backplane. As in the previous method [10], all bulk regions are approximated as a single node, and an equivalently sized contact is created.

The contact information for each gate is found from the layout information in the Cadence environment (Contact Lister, see Appendix B). EPIC simulations for each gate are run to find the resistive substrate network. A text file containing the resistor network of each gate in the library is saved and used in the simulation flow, described in Section 3.2.

Combining the local substrate networks into a complete substrate network is a valid approximation for several reasons. Since the substrate is a heavily doped substrate, the cross coupling resistances become negligible, compared to the coupling to the single node backplane, for distances larger than 4 times the thickness of the epitaxial and channel stop layers [15]. For the profile used, this equates to distances of approximately  $16\mu$ m. This means only directly adjacent gates will be close enough to be significant. The circuit level connections of the contacts also play a role. The p-tap contacts are all connected together to the digital on-chip ground, making the cross coupling between these contacts of adjacent cells negligible. The other type of contacts, the bulk contacts, are positioned close enough to the p-taps to provide a low coupling resistance. The cross coupling to other contacts outside of the gate will be negligible compared to this low resistance.

#### 3.1.2 Equivalent Parasitics

One of the characteristics of the digital gates which must be preserved in the DMM representation is the equivalent parasitics between the supplies (Vdd and Vss). The equivalent parasitics are formed by a combination of routing capacitances, channel resistances, and junction capacitances. Many digital macro modeling methods presented by other sources appear to neglect these important parameters as well [5, 6, 9, 10]. One reason for this may be that these parasitics do not affect substrate noise simulations in smaller digital circuits. Another reason may be that

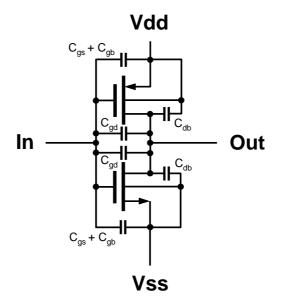

Figure 3.2: The parasitics of a simple inverter.

decoupling capacitances added on-chip can be much larger than some digital circuit's equivalent parasitics. However, as the size of a digital circuit increases, these parasitics become important for an accurate estimation of supply ringing, and subsequently, substrate noise.

To determine the type of equivalent model that should be used, an examination of a simple inverter's parasitics will first be conducted. Neglecting any routing capacitances, an inverter's parasitics are shown in Fig. 3.2. In this figure, the resistance through the substrate is assumed to be zero, making the source and bulk the same node for each transistor. The gate-to-bulk and gate-to-source capacitances are combined under this assumption.

By assuming an input voltage to the inverter, the parasitics can be simplified further. The input to the gate is tied low through a previous logic gate's NMOS

Figure 3.3: Equivalent parasitics of an inverter when the input is held low and the overlap capacitances are ignored.

transistor, and the output is tied to the  $C_{gs}$  of the next logic gate's NMOS transistor. The equivalent parasitics are now represented by Fig. 3.3. The overlap capacitance is assumed to be negligible in this figure. The NMOS transistor of this gate is replaced by an open circuit since it is in cutoff. The PMOS transistor is replaced with an equivalent resistor since it is in deep triode. From this figure it can be seen that a dominant pole between the rails is formed by  $\frac{1}{R_{dsn} C_{gs}}$ . Another similar sized pole between the rails is formed by  $\frac{1}{R_{dsp} (C_{db}+C_{gs})}$ . As this analysis is expanded to larger gates, the problem becomes much more complex. However, the dominant pole or poles will continue to come from the deep triode resistance which holds the output of a gate to either supply, and the capacitances from that output to the opposite supply.

The preceding analysis justifies the characterization of each gate's equivalent

parasitics as a resistor in series with a capacitor between the supply lines. The values of these equivalent parasitics vary depending on the digital state of the gate being modeled. Each gate is characterized for all input combinations and internal states. The parasitics are characterized after settling, with no input or output transitioning occurring. The parasitic information is stored and used in the simulation flow (described in Section 3.2) to construct a complete set of equivalent rail parasitics.

#### 3.1.3 Delay Information

The correct delay information is important in making sure the gate level simulation's timing, and subsequently, the substrate noise waveforms are equivalent to the noise generated in a transistor level simulation. For clocked logic, all combinational logic following the flip-flops needs to be triggered at the correct time after a clock edge. For clockless logic this becomes an even larger issue, since any small error in delay can cause differences not only locally for a proceeding gate, but globally and cumulatively, since the logic is never re-synchronized with a clock.

For these reasons each cell must be correctly characterized to generate a Standard Delay Format (SDF) file that is back annotated during the gate level simulation. The gate level delays are then combined to form a global delay file. One assumption made with this method is that the majority of the delays for the overall digital block will come from the switching of the gates themselves. The delays for the switching of the gates are usually orders of magnitude larger than the delays added from interconnects between gates. A global SDF file is used in the DMM method presented in [10]. This file is not always available or accurate for a specific process.

Multiple SDF files are generated for each gate from an extracted netlist. The delays for different paths through a gate can depend heavily on the number of other gates connected to each output. Therefore, the gates are simulated multiple times and a set of SDF files are created which can be selected when simulating a specific configuration. The gates are loaded with an average-sized gate, since specific loading would require either a pre-known configuration or unacceptable amounts of simulation and storage.

The delays through a gate vary due to internal effects, not just external effects like output loading. The delay from an input to an output can be affected by the value of other inputs or the internal state of the gate. These delay paths are called conditional delays. The best SDF file is one which not only characterizes all delay paths, but also all conditional delays of each of these paths. The characterization first produces this type of SDF file.

Even with the best SDF file, the delay information must be correctly represented in the gate's HDL level model. If the HDL models do not have conditional delay paths described in them, the information in the SDF file will not be used in the simulation. The back annotation will only adjust the delay paths, not add new ones. Some HDL gate models contain conditional delays which may be simplified from several specific conditional delays. To account for all of the preceding issues, the complete SDF file must be tailored to correctly match the delays provided in the HDL model. This adjusted SDF file is saved for later use in the simulation.

The delays are timed from the switching voltage of an input to the switching voltage of an output. The switching voltage can be a difficult parameter to determine. If the switching voltage is defined as the point when the output equals the input, then the switching voltage from high-to-low and low-to-high is equal. However, this voltage can change based on the input and output branches and the sizing of the transistors. Finding when an input switches is based only on the gate being characterized. Determining when an output switches is based on the switching of the connected gate(s). Therefore, the switching voltage is not recorded as a gate by gate specification, but determined as an average switching voltage for a particular gate library.

#### 3.1.4 Transition Waveforms

Perhaps the most important characterization is that of the transition waveforms. When a given gate input transitions, there is a combination of switching and capacitively injected current through the terminals of the gate. This current is recorded and later used along with the switching information to form piece-wise linear (PWL) current sources which represent the active components of the gate in a substrate noise simulation.

A gate is defined as having an internal state if it's outputs are dependent on the current inputs as well as previous inputs. The DMM presented in [10] did not account for the internal states of gates. For circuits where the only gates

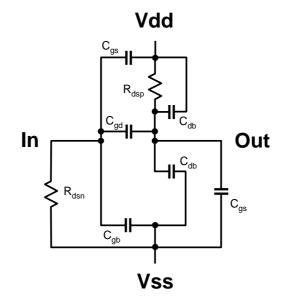

Figure 3.4: Supply current of a flip-flop for a given input pattern when the output (a) changes state, and (b) remains the same.

with internal states are a small number of flip-flops, and most of the logic is combinational, this is an acceptable approximation. However, in logic circuits where many of the blocks have multiple internal states, the differences in injected substrate noise from different states is too significant to ignore. For NCL, multiple states exist for most of the logic gates to enable the passing of NULL and DATA values.

To demonstrate the concept of internal states changing transition waveforms, a simple flip-flop is considered. The simulated supply current is compared for the same input transitions, but with different cell states. The current waveforms are shown in Fig. 3.4. The waveform in Fig. 3.4(a) shows a larger supply current waveform when the inputs and previous state cause a change in the output state. The waveform in Fig. 3.4(b) shows the supply current when the inputs and previous state cause no change in the output state.

Figure 3.5: Internal logic branches switching when a D-type flip-flop does not change states.

The differences in the two waveforms are due to the multiple logic branches in the flip-flop. It can be observed from Figs. 3.4(a) and (b) that the peak current flow is the same at approximately 1.4ns. This initial current peak is due to logic branches switching in response to the incoming clock. The following current peaks found in Fig. 3.4(a) but absent from Figs. 3.4(b) are caused by the output and other internal branches switching as the flip-flop changes states.

In order to visually show the internal branches switching, a combinational logic implementation of a D-type flip-flop is examined. Fig. 3.5 shows the implementation of a D-type flip-flop with its internal state remaining the same after input switching events. The logic levels of each node are shown, and the internal gates, or branches, which switch are shadowed. Fig. 3.6 shows the implementation of a D-type flip-flop with its internal state changing after input switching events. The logic levels and internal branches switching are shown. In this example, the differences in transition waveforms are caused by the output logic branches switching when the internal state changes.

Figure 3.6: Internal logic branches switching when a D-type flip-flop changes states.

Since the internal state can change the transition waveforms, each gate is characterized not only for all possible input switching conditions, but for all possible input switching with different initial states. All of this switching information is stored in files and used in the simulation flow (described in Section 3.2).

Internal states for gates must be clearly defined in this methodology. To keep track of this information, a state map of each gate is created during characterization. The state map defines the internal state that the gate is in, based on its current outputs, and previous input values. The majority of internal states are defined only by the outputs. The previous input values are used in situations where the output values are identical for different internal states. The state map also helps to signal when the gate has entered an undefined state. There are some situations where the gate simulation may generate output or previous input values which do not describe any characterized state of the gate. In these cases, the state map adds some error checking to the simulation flow.

The waveforms are saved in constant time increments, with a fixed time length set in the characterization script. This time length must be long enough for all gates in the library to settle. The length of all gate waveforms must be the same after the characterization. During the simulation flow, the lengths are truncated to the minimum allowable for a particular energy loss, as described in [21]. Performing the truncation later allows for different energy losses to be selected for different simulations, without having to re-characterize the standard cell library. It also alleviates the need to save the length of each truncated waveform. The disadvantages are larger file sizes from the excess data and a slight addition to the simulation flow time because of the truncation.

The time increments with which the waveforms are saved can also be adjusted. This change of resolution increases the file size, but also increases the accuracy of the simulation. The effect of increased file size is actually two-fold. Increasing the transition waveform files is only the first part. If the resolution is increased, then over the same simulation time, the final PWL files describing the gate's switching noise will be proportionally increased. If the length of these PWL files are too long, and the number of gates too large, Spectre may run out of memory when trying to load them. The increased resolution allows for the saving of higher frequency noise which will not be seen in simulations with a lower resolution. This resolution should be adjusted depending on the frequency range of interest in the substrate noise simulation. For the simulations in this thesis, a 100ps time step gave adequate resolution while allowing for reasonable file sizes.

The gates are all simulated with netlists extracted from layout information. The extraction also includes interconnect coupling capacitances for more accuracy. The bulks of all NMOS transistors are disconnected and added together as another pin for the gate. This allows for the saving of the current waveforms through the Vdd, Vss, and bulk connections.

It is important to transition the inputs of the gate correctly. A PWL source is used to model the rising or falling waveforms. The exact waveform exciting the gate will depend on the previous gate, and that gate's output load. It is not reasonable to characterize and store this level of detail for all gate configurations. For this reason, the gates in the standard cell library are each simulated, and an averaged output transition waveform is developed that is used for all input transitions.

## 3.2 Simulation Flow

After the standard cell library characterization is complete, the DMM simulation of any digital block utilizing that library can be performed. This simulation flow is seen in Fig. 3.1, indicated by 2 and 3. These two parts will be described in the following subsection. For more specific information on coding of these parts refer to Appendix A.

## 3.2.1 Digital Noise Current Generation

The digital noise current generation is the process used to create the DMM of a specific digital block for use in the substrate noise simulation. The digital block is analyzed, and individual gate information combined to form the top level substrate network and the global SDF file. The delay information is used in an HDL simulation to determine the gate transitions. The input transitions for each gate are saved during the simulation. For cells which have multiple states, the outputs are also saved when there are input transitions.

One issue confronted during the HDL simulation is matching the gate transitions with the transition waveforms. The delay characterization, as described previously, is timed in reference to switching voltages of the gates. Therefore, the transitions occurring in the gate level simulation are ideal changes that happen when the gate input/output would pass the switching voltage. However, the transition waveforms do not begin when the switching voltage is crossed, but as soon as the input begins to change. To account for this difference, an offset is be subtracted from the gate transition times. This time is a constant for each standard cell library characterization, based on the input switching waveforms and when they pass the determined switching voltage.

The input transitions, output values, and current waveform information is then used in a concatenation program. This program selects the correct current waveform to use at the designated input switching times, and concatenates them together for each gate. If the gate has multiple states, it also uses the output information and the state map of that gate to determine the current waveforms.

The output of the digital substrate noise generation is a set of PWL data that is stored in files. These files describe the current waveforms generated by the gates in the block. By linking these files through PWL current sources, the switching currents of the transistor level digital blocks are correctly modeled.

## 3.2.2 Substrate Noise Simulation

The final substrate noise simulation is performed after the digital noise current generation has been completed. This simulation incorporates the models for the digital gates with the rest of the substrate noise setup. The simulation is performed in the Cadence environment with Spectre. For specific coding and details on the digital model placement script, refer to Appendix B.

Part of the DMM for the digital block is the substrate network. The substrate network created in the digital noise current generation is added into the schematic view with the correct connections.

The equivalent parasitics are also added into the schematic view as part of the digital gate model. The gate transition information of each gate is needed. The input transition information (along with any output information for gates with internal states) is used to determine the equivalent parasitics at different times throughout the simulation. The equivalent parasitics for each gate are averaged over time and placed as constant values.

After the final addition of the PWL current sources, the simulation generates the correct amount of substrate coupling from the modeled digital block to the sensitive circuits modeled at the transistor level. The circuits substrate networks are connected together in the simulation through the common backplane node.

### Chapter 4 – Simulation Results

The simulation results from the setups described in Chapter 2 are presented in this chapter. The PRNG simulations are shown for verification between measurement, transistor level simulation, and the improved DMM method. The 8051 micro-processor simulations are presented to verify the use of the DMM in a large and complex circuit which is not easily simulated at the transistor level.

# 4.1 Pseudo-Random Number Generators

The results for the PRNG test setups are presented in this section. The transistor level simulation subsection compares measurements and transistor level simulations of the PRNGs. This comparison verifies the complete setup of the substrate noise simulation. The digital macro-model subsection compares the transistor level simulation results with simulation results where the PRNGs are replaced with equivalent DMM blocks. This comparison verifies the improved DMM presented in this thesis. Each comparison is performed for the CBL and NCL versions of the PRNGs.

## 4.1.1 Transistor Level Simulation

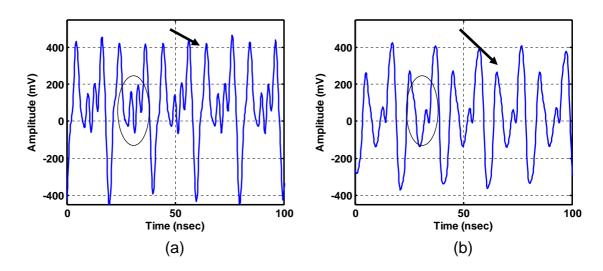

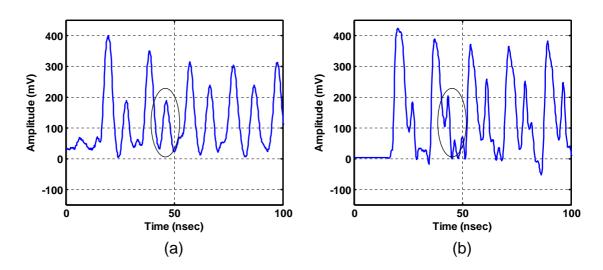

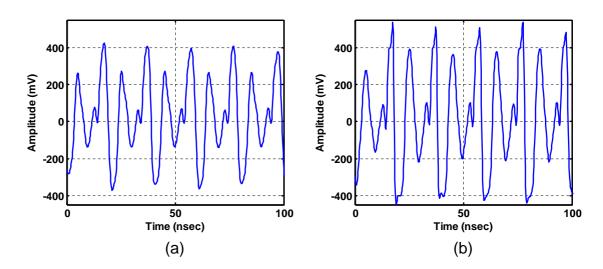

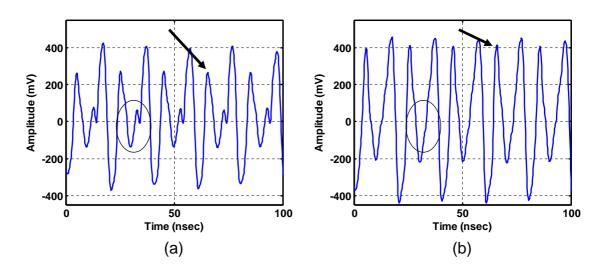

The measurements and transistor level simulation results for the CBL PRNGs are shown in Fig. 4.1. The shape of the noise waveforms in simulation are similar to the shape displayed by the measurements. There are two noteable differences between the measurements and the simulations. The first is the difference in waveform shown by the circled region. The second is the size of the voltage peak, pointed to by the arrows. Both of these differences are believed to be connected. There are two local peaks in the circled region of Fig. 4.1(a). The earlier local peak seems to be missing from the circled region of Fig. 4.1(b). This peak is still in Fig. 4.1(b), however it has shifted to the left. The superposition of this peak and the voltage peak coming just before the circled region have formed a single voltage peak which is lower and wider in the simulations. This timing issue is coming from an inability to model the loaded clock generator perfectly in simulation.

The measurement and simulated data are both processed using a fast Fourier transform (FFT) in Matlab. The results of each in the frequency domain are shown in Fig. 4.2. The spectra are similar, with a noise floor peaking around 100 MHz due to package ringing (circled regions). The clock's fundamental frequency and tones are similar, with some higher frequency tones being higher in the measurements.

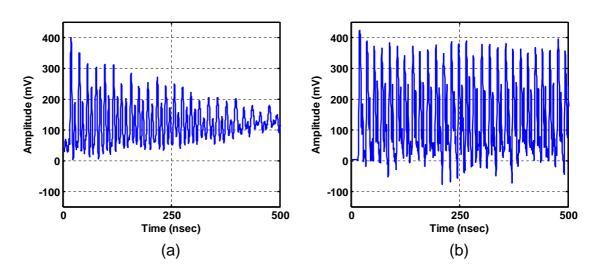

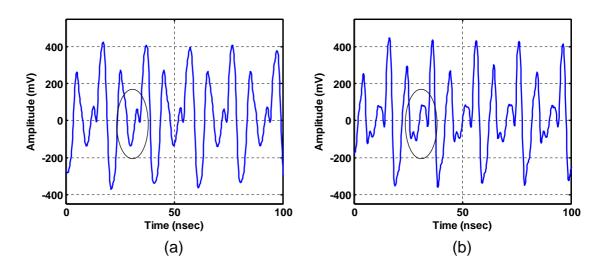

The measurements and transistor level simulation results for the NCL PRNGs are shown in Fig. 4.3. Both waveforms start out at similar peak voltage values. The measurements shown in Fig. 4.3(a) have more separation between the primary and secondary voltage peaks (circled regions). This difference comes from

Figure 4.1: Comparison of time domain (a) measurements, and (b) simulations for the CBL PRNGs.

Figure 4.2: Comparison of frequency domain (a) measurements, and (b) simulations for the CBL PRNGs.

Figure 4.3: Comparison of time domain (a) measurements, and (b) simulations for the NCL PRNGs.

differences in the NCL gates' delays in simulation and measurement. The switching events between gates are occurring faster in the simulation (possibly due to missing parasitics) and are causing the substrate noise injections to happen closer together. Further evidence of this delay difference is noted in the rate at which the voltage peaks occur. Over the same time period, there are nine voltage peaks in the measurement, compared to 10 voltage peaks in the simulation.

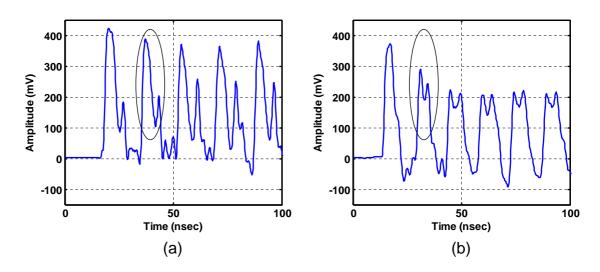

An expanded time scale comparison of measurements and transistor level simulation results for the NCL PRNGs is shown in Fig. 4.4. This figure shows another difference between the measurements and simulations. The measurement voltage peaks decay down significantly, while the simulation peaks stay at approximately the same level. The repetitive placement of the PRNG blocks is responsible for this behavior in measurements. The NCL PRNG blocks have no global clock, and only the reset signal keeps them synchronized. When the reset signal first occurs,

Figure 4.4: Expanded time scale comparison of (a) measurements, and (b) simulations for the NCL PRNGs.

all blocks are injecting noise with the same pattern. However, each block is not identical. Mismatch between the NCL PRNGs cause the blocks to run at different equivalent operating speeds. As time progresses, each block runs at a similar but slightly different frequency, resulting in less addition of switching current peaks. In simulation there is no variation in the NCL PRNG blocks, so the current peaks, and subsequently substrate noise peaks, always add.

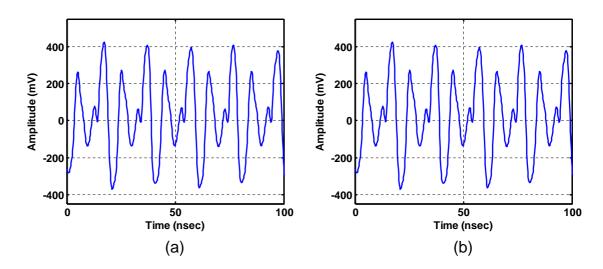

To demonstrate this concept, test simulations are performed. A simulation setup with 5 NCL PRNG blocks is constructed using simple supply parasitics and substrate networks. Fig. 4.5 compares two simulations of this setup. In Fig. 4.5(a) the voltage on the backplane node is shown when the Vth of the transistors is held constant. In Fig. 4.5(b) the voltage on the backplane node is shown when the Vth is varied for each NCL PRNG block. The varied Vth simulation results show similar voltage peaks to those in the constant Vth simulation initially. However,

Figure 4.5: Comparison of a test setup with the NCL PRNGs with (a) constant Vth, and (b) varied Vth.

the peaks quickly degrade as the NCL PRNG blocks fall out of synchronization with each other in the varied Vth simulation.

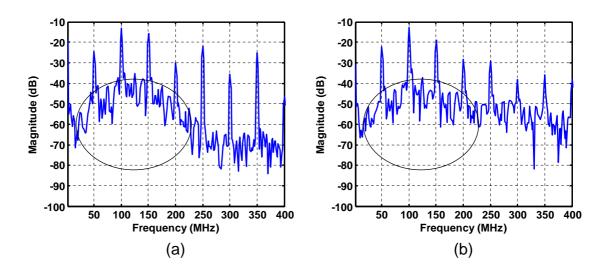

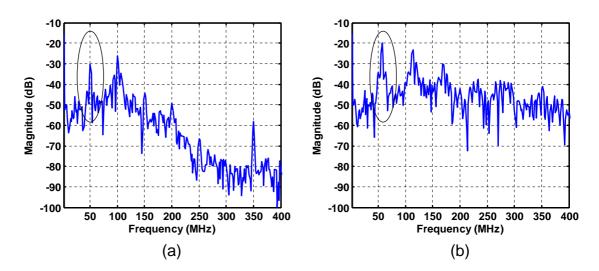

Again, FFTs of the measurement and simulated data are performed in Matlab. The results of each in the frequency domain are shown in Fig. 4.6. As would be expected from the measurement results, there are significant differences in the FFTs. Both FFTs do however display peaks close to the equivalent operating speed of 50 MHz (shown as circled regions) and it's harmonics. The magnitude of the peaks in the FFT of the simulation results is at higher levels as expected from the time domain results.

Figure 4.6: Comparison of frequency domain (a) measurements, and (b) simulations for the NCL PRNGs.

### 4.1.2 Digital Macro-Model

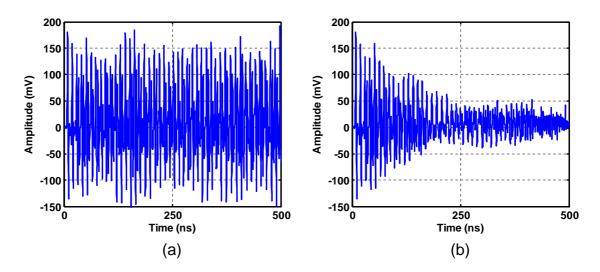

The transistor level and DMM simulation results for the CBL PRNGs are shown in Fig. 4.7. The voltage peaks are slightly higher in the DMM simulations than in the transistor level simulations. The noise shapes and timing compare closely between the simulations.

The transistor level and DMM simulation results for the NCL PRNGs are shown in Fig. 4.8. The DMM simulation's first voltage peak is similar in magnitude to that of the transistor level simulation's first voltage peak. All other voltage peaks are slightly lower in magnitude in the DMM simulation. The difference comes from the delay modeling in the DMM simulations. The NCL block's have no conditional delay paths defined in their HDL descriptions. The generalized delay paths cause the switching activity peaks to occur closer together in the gate level simulation.

Figure 4.7: Comparison of time domain (a) transistor level simulations, and (b) DMM simulations for the CBL PRNGs.

The difference in the time separation of the voltage peaks is shown by the circled regions in Fig. 4.8. Further evidence of this difference in delay modeling is seen by the rate at which the voltage peaks occur. Over the same time period, the DMM simulation shows 6 sets of the same double peaked waveform, the transistor level simulation shows only 5.

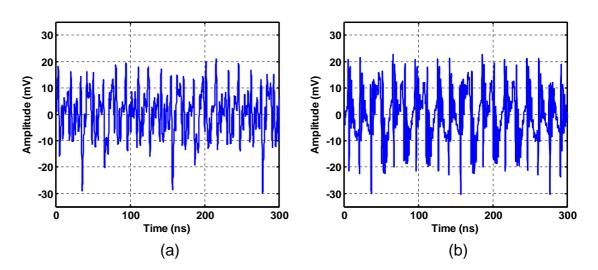

# 4.2 8051 Microprocessor

The results for the 8051 microprocessor test setups are presented in this section. The equivalent DMM simulations of the PRNGs show good agreement with transistor level simulations. As a larger and more complex simulation, the 8051 microprocessor will verify the improved DMM methodology for a more realistic circuit implementation. Comparisons between the measurements and DMM simulations

Figure 4.8: Comparison of time domain (a) transistor level simulations, and (b) DMM simulations for the NCL PRNGs.

are presented for both the CBL and NCL cores.

The measured and simulated results for the CBL core are shown in Fig. 4.9. Good agreement between simulations and measurements is seen. The simulations have similar noise waveforms as those seen in measurements. The peak-to-peak values in the simulation are similar but slightly higher for some sections of the waveform than the measurements.

The measured and simulated results for the NCL core are shown in Fig. 4.10. Again, the simulations are in good agreement with the measurements. The noise waveforms and peak-to-peak voltages are similar. The measurements for the NCL core were taken without averaging. Since the transition times can vary significantly over long time intervals with clockless logic, any averaging would corrupt the noise measurements by averaging misaligned voltage peaks. However, without averaging, noise from the measurement setup cannot be removed. This noise is evident in the

Figure 4.9: Comparison of time domain (a) measurements, and (b) DMM simulations for the CBL 8051 microprocessor core.

Figure 4.10: Comparison of time domain (a) measurements, and (b) DMM simulations for the NCL 8051 microprocessor core.

measurement results of the NCL core.

## Chapter 5 – Critical Aspects of Substrate Noise Simulation

Substrate noise simulations can be very difficult to setup. There are many different parasitics and non-idealities that may have to be included in a simulation for matching with measurements. In this chapter, various aspects of accurate substrate noise simulations will be addressed. The CBL PRNG simulations in Chapter 4 are used as a baseline. By adjusting a single parameter at a time, the effects on the overall accuracy can be carefully examined.

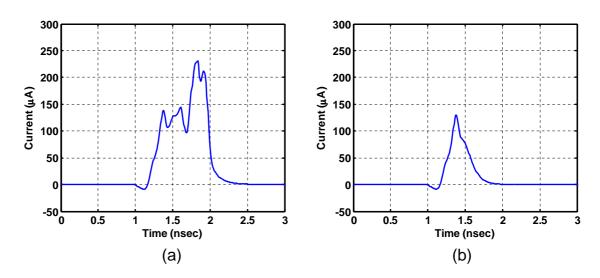

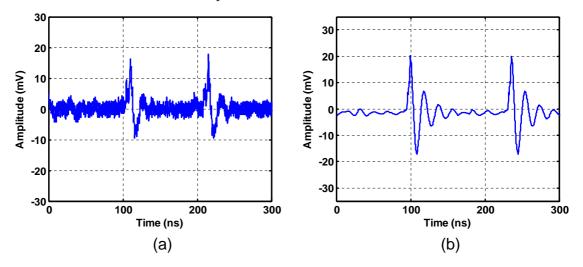

#### 5.1 On-Chip Buffers

The core digital blocks may not be the only circuits injecting noise into the substrate. Clock and data lines are often buffered before coming on-chip or going off-chip. These IO buffers can be very large digital circuits with substantial current switching. In a substrate noise simulation, the inclusion of the noise from these circuits is very important.

On-chip buffers were used in the CBL PRNG test setup to buffer the clock and reset lines coming from the PCB. To analyze the effect of the substrate noise generated by these buffers, the CBL PRNG simulation is performed without including the substrate network for the buffers. A comparison in the time domain between the CBL PRNG transistor level simulations is shown in Figs. 5.1(a) with and (b)

Figure 5.1: Comparison between (a) the complete simulation of the CBL PRNGs, and (b) the same simulation with the IO buffers' substrate network removed.

without the substrate noise from the IO buffers included.

The results without the IO buffers' substrate network in Fig. 5.1(b) show two significant differences from the complete simulation of Fig. 5.1(a). The first difference is the missing smaller peak, shown by the circled regions. The second is the larger secondary peak, pointed to by the arrows. Since the IO buffers' substrate noise is directly proportional to the incoming clock, this example shows the significance of modeling the incoming clock and IO buffers in substrate noise simulations. It also supports the earlier claim that differences between measurement and complete CBL PRNG simulations are due to the clock waveform.

Figure 5.2: Comparison between (a) the complete simulation of the CBL PRNGs, and (b) the same simulation with coupling capacitances between interconnects removed.

## 5.2 Capacitance Between Interconnects

One of the most common parasitic extractions is the extraction of capacitive coupling between different interconnect layers. Parasitic interconnect capacitances can have significant effects on simulation results. To analyze how much this type of parasitic capacitance changes substrate noise simulations, the CBL PRNG simulation is performed again without the capacitance extracted between interconnect layers. A comparison in the time domain between the the CBL PRNG transistor level simulations is shown in Figs. 5.2(a) with and (b) without the interconnect coupling capacitances.

The noise waveform of the simulation without parasitic interconnect capacitances, Fig. 5.2(b), has one significant difference from the complete simulation in Fig. 5.2(a). The noise shape is changed within the circled regions of Fig. 5.2. The voltage peaks are slightly sharper in Fig. 5.2(b), but remain at similar levels as the voltage peaks in Fig. 5.2(a). This example shows the capacitance between interconnects affects substrate noise simulations, but only to a limited extend for this test setup and this clock frequency.

## 5.3 Capacitance to Substrate

Parasitic capacitors are also present between the interconnect layers and the substrate. This coupling can be much weaker, but can add up cumulatively for very large areas. Structures such as bond pads, and large low level metal traces can add up not only in area capacitance, but also in fringing capacitance, to form a path for high frequency noise injection in the substrate.

For the CBL PRNG simulations, the bond pads and probe pads were the only structures large enough to form any significant capacitance to the substrate. To analyze the effects of modeling these structures, a simulation of the CBL PRNGs is performed again without the extraction of the bond pad and probe pad coupling to substrate. Fig. 5.3 shows a comparison in the time domain between the CBL PRNG simulations with and without the pad coupling capacitances.

The results show similar waveforms for both comparison cases. The substrate noise in this setup is neither coupling through, or being dampened by, the bond and probe pad capacitances. Substrate noise injected by other sources is much larger for this test setup and clock frequency.

Figure 5.3: Comparison between (a) the complete simulation of the CBL PRNGs, and (b) the same simulation with the pad capacitances to substrate removed.

### 5.4 High Frequency Substrate Model

As described in Section 2.3, the p-type substrate is modeled as a purely resistive network. This network is found from the use of a particular version of EPIC. By using a different version of EPIC, a higher frequency substrate model can be obtained. For frequencies up to 5GHz, the substrate can be modeled with the structure shown in Fig. 5.4 [22]. The permittivity of the substrate is required for calculating this model. The permittivity of silicon is given as:

$$\epsilon_{Si} = \epsilon_0 \ \epsilon_r = 1.0359 \times 10^{-10} F/m$$

(5.1)

To test the effects of using the higher frequency substrate model on simulations, the CBL PRNG simulation is repeated with the substrate network replaced with the higher frequency model. The results of the CBL PRNG transistor level

Figure 5.4: The substrate  $\pi$ -network incorporating higher frequency effects.

simulation with the purely resistive network and with the high frequency network are shown in Fig. 5.5.

The results show no noticeable difference with the use of the higher frequency substrate model. For this test setup and clock frequency, the use of a purely resistive substrate model is both sufficient and accurate.

Figure 5.5: Comparison between (a) the complete simulation of the CBL PRNGs, and (b) the same simulation with the high frequency substrate model.

## Chapter 6 – Conclusions

The substrate noise simulation methods presented in this thesis have many advantages. This chapter summarizes the advantages and accomplishments of this work. Then a discussion of some lessons learned is presented. Finally, issues and future work with the methods presented are described.

# 6.1 Summary

In this thesis, the setup of substrate noise simulations is discussed. Several test setups are presented which modeled microchips fabricated in TSMC's  $0.25\mu$ m logic process. The test setups contained both clocked and unclocked digital logic circuits.

A method for modeling the digital block in a substrate noise simulation is presented. This method is presented not only as a way to overcome some of the issues with a full transistor level simulation, but also as a way to perform pre-layout substrate noise simulations. The method is described in three steps: characterization, digital noise current generation, and substrate noise simulation. The characterization step only needs to be completed once per gate library. The digital current generation needs to be performed once per digital block setup. The final substrate noise simulation is then performed with an equivalent digital model which runs faster and more efficiently in the simulator.

|               | Transistor Level | DMM       |

|---------------|------------------|-----------|

| CBL PRNG      | 33h, 52m         | 14h, 57m  |

| NCL PRNG      | 49h, 21m         | 11h, 3m   |

| 8051 CBL Core | -                | 702h, 13m |

| 8051 NCL Core | -                | 531h, 2m  |

Table 6.1: Execution time of different substrate noise simulations.

Table 6.1 shows the execution times of the substrate noise simulations presented in chapter 4 of this thesis. The PRNG simulations show a definitive advantage in execution time with the use of the DMM method. The NCL PRNG simulations show an increase in simulation speed by over 4 times. The CBL PRNG simulations show an increase in simulation speed by over 2 times. The CBL PRNG's DMM simulations are slowed significantly by the need to simulate the switching clock buffers at the transistor level. All PRNG circuits are run for  $1\mu$ s transient simulations.

The 8051 microprocessor will not simulate at the transistor level due to convergence issues for such a large circuit. The DMMs for the 8051 microprocessor circuits are run for  $15\mu$ s transient simulations.

The digital macro modeling method presented in this thesis is not only able to simulate large static CMOS blocks, but is general and applicable to different types of digital logic, such as asynchronous NCL. In fact, this is the first method to address noise generation from asynchronous blocks. Validations with measured results demonstrate the accuracy and efficacy of the method.

## 6.2 Lessons Learned

External parasitics are important for an accurate prediction of substrate noise. The off-chip parasitics are often more important than the on-chip parasitics. The package, bond wires, and PCB parasitics may all include large inductances and capacitances. The series inductances will increase the magnitude of the supply bounce seen on-chip when switching events occur. These inductances, along with parasitic and decoupling capacitances, will also influence the ringing on the supplies after a switching event. All of this activity on the supply lines will couple through the NMOS or PMOS taps to the substrate, and form the majority of the substrate noise. The one exception to off-chip parasitics having more influence on simulation results than on-chip parasitics is the on-chip trace resistances. If critical lines are not made sufficiently wide, but are considerably long, the on-chip series resistance can easily grow larger than any off-chip resistances.

The exact test setup has to be accurately modeled. The input sources used in the lab drastically change the substrate noise waveforms. Knowing which equipment and connections were used, or are going to be used, for a particular substrate noise measurement is essential in getting simulations that match. Many of the manuals for the different test equipment have sections describing the properties of the signals they generate, or the equivalent models that should be used when they are connected. It is important to decide which models and characteristics are critical, and which are unnecessary at the frequencies of interest in the simulation.

Ground connections of other on-chip circuits make a significant difference in

substrate noise. The simulation of the 8051 microprocessor cores produces unmatched results when the other substrate connections on the die are not modeled. In substrate noise simulations it is a common mistake to include only the circuits of interest in a setup. However, when there are multiple circuits on the same die, and their pins are connected, these can provide pathes for noise to exit the substrate. Noise currents injected into the substrate can use these alternative paths to couple off-chip instead of coupling to the sensitive analog nodes. This will manifest as different peaks and ringing frequencies in the simulation than those seen in measurements.

An exact match of clockless circuits in simulation is difficult. There are many modeling parameters in simulation that can not be perfectly matched with actual silicon. Random noise or variations in process, voltage, and temperature can cause differences from simulation. One benefit of simulating clocked circuits is the ability of the clock to 're-align' simulated and measured waveforms. With clockless logic, even small differences in modeling can lead to larger variations over long periods of time through accumulation. This is particularly demonstrated in the differences between the test simulations for the NCL PRNGs, shown in Fig. 4.5.

#### 6.3 Future Work

The parasitic extractions used in this thesis were done with the help of modified Diva extraction rules. These rules are relatively simple to modify. However, they are no longer supported by Cadence or commonly used in industry. To make future substrate noise simulation setups more up to date and applicable to industry use, the extraction should be done with a more commonly used tool. Assura is the currently supported parasitic extraction method from Cadence. This would be a logical choice for developing adjusted extraction rules to be used for substrate noise simulation. The rules for Assura are very similar to the rules for Diva, so the method of adjustment may be the same. The exact adjustments made to the Diva rules are explained in more depth in Appendix B. These adjustment were done manually to the rules as well, but a method for automatically adjusting the rules would be very convenient for easy setup with new processes.