#### AN ABSTRACT OF THE DISSERTATION OF

<u>Hyuk Sun</u> for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and Computer Engineering</u> presented on <u>December 8, 2016.</u>

Title: <u>A Wide Modulation Range and PVT-Tolerant Spread-Spectrum Modulation Clock Generator</u>

| Abstract approved: |            |  |

|--------------------|------------|--|

|                    |            |  |

|                    | Un-Ku Moon |  |

This dissertation presents a phase domain in-loop-bandwidth spread-spectrum clock generation technique. In this proposed technique, a charge-based discrete-time loop filter is proposed to enable the phase domain in-loop-bandwidth spread-spectrum modulation without a delta-sigma modulator or time-to-digital converter. The in-loop-bandwidth modulation technique maximizes the loop bandwidth to improve phase noise suppression in a ring-based voltage-controlled oscillator. The phase domain modulation is established to eliminate a delta-sigma modulator that presents an undesirable power and noise trade-off. An analog-domain phase modulation in this proposed modulation technique eliminates a time-to-digital converter that results in inevitable quantization noise.

The proposed technique delivers a wide spread-spectrum modulation range with significantly relaxed PVT sensitivity. Since the proposed discrete time loop filter acquires and filters signals in the charge domain, this loop filter supports good linearity for a wide modulation range. PVT variations in the loop filter and the voltage-controlled oscillator are attenuated by the loop gain. The nonlinearity of the voltage-controlled oscillator gain (K<sub>VCO</sub>) and loop filter is also attenuated due to the loop gain. In addition, a correlated double sampling technique is leveraged to minimize 1/f noise and DC offset of the proposed discrete-time loop filter.

This dissertation discusses design trade-offs: between reference frequency and spread-spectrum modulation range, and between the spread-spectrum modulation range and jitter performance. From time and spectral measurements for various reference frequencies, a higher reference frequency results in better jitter performances, but also a narrow spread-spectrum modulation range. Time domain jitter measurements are compared to spectral domain jitter calculations to observe design intuitions.

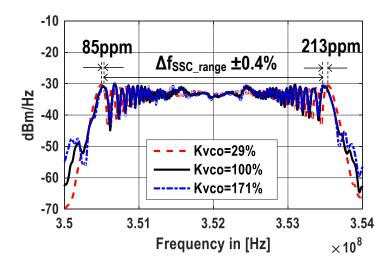

This wide modulation range and PVT-tolerant spread-spectrum modulation technique is implemented in a 0.18µm CMOS, while consuming 9.93mW with a 1.8V power supply. The proposed charge-based discrete time loop filter consumes less than 10% of the total power, and the spread-spectrum modulation component requires less than 5% of the total power. This wide range spread-spectrum clock generation technique achieves 0.8% and 3.2% spread-spectrum modulation range with 22.76dB and 26.51dB spread-spectrum attenuation for 2MHz and 8MHz reference frequencies, respectively. The measured absolute jitter is 62.72ps<sub>rms</sub> and 18.72ps<sub>rms</sub> for 2MHz and 8MHz reference frequencies, respectively. The measured period jitter is 961.2fs<sub>rms</sub> and 988.1fs<sub>rms</sub> for 2MHz and 8MHz reference frequencies, respectively. Finally, a 142% change in K<sub>VCO</sub> results in less than 298ppm modulation range error, which confirms the PVT-tolerant modulation.

©Copyright by Hyuk Sun December 8, 2016 All Rights Reserved

# A Wide Modulation Range and PVT-Tolerant Spread-Spectrum Modulation Clock Generator

by Hyuk Sun

#### A DISSERTATION

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Presented December 8, 2016 Commencement June 2017

| <u>Doctor of Philosophy</u> dissertation of <u>Hyuk Sun</u> presented on <u>December 8, 2016.</u>                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                           |

| APPROVED:                                                                                                                                                                                                 |

|                                                                                                                                                                                                           |

| Major Professor, representing Electrical and Computer Engineering                                                                                                                                         |

|                                                                                                                                                                                                           |

|                                                                                                                                                                                                           |

| Director of the School of Electrical Engineering and Computer Science                                                                                                                                     |

|                                                                                                                                                                                                           |

| Dean of the Graduate School                                                                                                                                                                               |

|                                                                                                                                                                                                           |

|                                                                                                                                                                                                           |

|                                                                                                                                                                                                           |

|                                                                                                                                                                                                           |

| I understand that my dissertation will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my dissertation to any reader upon request. |

|                                                                                                                                                                                                           |

| Hyuk Sun, Author                                                                                                                                                                                          |

#### **ACKNOWLEDGEMENTS**

I would like to thank Professor Un-Ku Moon for the opportunity to resume my doctorate in Oregon State University. When I jointed his 'stone shiner' in September 2013, I was an obstinate student who desperately was polishing my stone by myself and naïvely wished this is how it works. However, my lesson from him is that it can be done from seemingly endless crashing and pounding interactions among other stones. This is the time to jump into another stone shiner, which must be harder.

I would like to give thanks to my co-advisor Professor Tejasvi Anand, who has taken time to sit beside me for revising papers and helping setups for instruments. I would like to give thanks to the committee members, Professor Gabor Temes, Professor Karti Mayaram, and Professor Andreas Weisshaar for taking time out of their busy schedule to serve.

I would like to thank my group members Allen Waters, Jason Muhlestein, Spencer Leuenberger, Yang Xu, Praveen Kumar Venkatachala, Ahmed El-Shater, and Calvin Lee. Allen showed me how to live in Oregon as a real Oregonian, such as no shaving in Novembers, and surviving without a smart phone as a 'smart' Electrical and Computer Engineering Ph.D student. Jason shows me how to survive as a delightful engineering Ph.D student, who never surrenders his sense of humor. Spencer shows me why I need to come down myself for everything except my research. Yang is a good companion through my Ph.D journey since we joined the group together. Praveen shows me that it is not a shame to ask silly things, since if you knew it is a silly question, you would not have asked at all. Not knowing hings is not silly, but it is silly to pretend knowing without truly knowing. Ahmed shows me how difficult to live as a father and Ph.D student, because he comes to the office when I leave to home. Calvin reminds me how I was naïve and ambitious when I first time dreamed about being a Ph.D student. Finally, I would like to thank Mr. Kazuki Sobue and Koichi Hamashita from Asahi Kasei Microdevies (AKM) Corporation to support

my study, and especially thank to Sobue-san for providing timely help and invaluable advice for last three and half years.

This endeavor would not have been possible without support of my parents, Byeong-Tae Sun and Mi-soon Ko, and my elder brother and younger sister, In Sun and Young Sun. My father gave his special wish to my given name, Hyuk (shining like a star), and never surrenders his responsibilities as a father through all hardships he has gone through. Although I feel a little bit of shame to him since it takes too long to end my Ph.D journey, I proud of him so much. My mother is a pioneer for me since she resumed her studies for the GED and college in her middle of 50's. As a mom and student, she is always supportive to me and praying for her second son, who cannot promise anything in the United States. In addition, I would like to thank to my parentin-raw, Sang-Kyo Lee and Saeng-Kum Moon. They welcomed me as a third son-inraw, although I had nothing as a poor Ph.D student, who had to drop his study in UCLA. They gave me their unconditional support and allowed me to build my own beautiful family from ashes. I would like to give my special thanks to my wife, Dr. Sung-Ji Lee, who sacrifices herself because of the husband's Ph.D study in Corvallis, where she never heard about before coming. Her own life-experiencing advice has been possible for me to finish up this journey. I remember one time she said to me that 'No one would have known that I am stupid if I did not do my Ph.D'. She is a best counselor and supporter for my journey, and she always embraces my cranky bumpy moments with a full heart. Finally, thanks to God. I don't know how many times I have to repeat, 'I can do everything through him who gives me strength, Philippians *4:13* '.

## TABLE OF CONTENTS

|                                                             | Page |

|-------------------------------------------------------------|------|

| 1 Introduction                                              | 1    |

| 1.1 Spread-Spectrum Clock (SSC)                             | 6    |

| 1.2 Qualitative Analysis for the SSC                        | 7    |

| 1.3 Definition of the Loop Bandwidth (BW) in a PLL          | 9    |

| 1.4 Prior SSC Architecture                                  | 11   |

| 1.4.1 Out-of-Loop-BW Direct SSC Modulation                  | 11   |

| 1.4.2 In-Loop-BW SSC Modulation                             | 12   |

| 1.4.3 Two-Points SSC Modulation                             | 15   |

| 1.5 Observations and Motivations                            | 15   |

| 2 Proposed SSC Architecture                                 | 16   |

| 2.1 Proposed Phase Domain In-Loop-BW SSC Modulation         | 17   |

| 2.2 Limitations of a Conventional Passive Loop Filter       | 18   |

| 2.3 Proposed Charge-Based Discrete Time Loop Filter (DT-LF) | 21   |

| 2.4 PVT-Tolerant SSC Modulation                             | 23   |

| 2.5 Correlated Double Sampling (CDS) Transconductor         | 24   |

| 2.6 Range Limitation of the SSC Modulation                  | 25   |

| 3 Modeling the Proposed SSC Architecture                    | 28   |

| 3.1 z-Domain Model                                          | 29   |

| 3.2 Hybrid-Domain Model                                     | 32   |

| 4 Circuit Implementations                                   | 37   |

| 4.1 Phase Frequency Detector (PFD)                          | 37   |

## TABLE OF CONTENTS (Continued)

|                                                                     | <u>Page</u> |

|---------------------------------------------------------------------|-------------|

| 4.2 Charge Pump (CP)                                                | 39          |

| 4.3 Proposed Charge-Based Discrete-Time Loop Filter (DT-LF)         | 42          |

| 4.4 Voltage-to-Current Converter and VCO                            | 47          |

| 4.5 SSC Current Digital-to-Analog Converter (I-DAC <sub>SSC</sub> ) | 50          |

| 4.5.1 LSB of I-DAC <sub>SSC</sub>                                   | 50          |

| 4.5.2 FCW <sub>SSC</sub> Resolution                                 | 51          |

| 4.5.3 I-DAC <sub>SSC</sub> Resolution                               | 51          |

| 4.5.4 I-DAC <sub>SSC</sub> Implementation                           | 52          |

| 4.5.5 I-DAC <sub>SSC</sub> Mismatch Analysis                        | 54          |

| 4.6 Programmable Frequency Divider (FD)                             | 56          |

| 4.7 Clock Generator                                                 | 56          |

| 5 Jitter Analysis and Estimation                                    | 57          |

| 5.1 Definition of Random Jitter                                     | 57          |

| 5.1.1 Absolute Jitter                                               | 57          |

| 5.1.2 Period Jitter                                                 | 58          |

| 5.1.3 Cycle-to-Cycle Jitter                                         | 58          |

| 5.1.4 Jitter Relationships                                          | 59          |

| 5.2 Phase Noise vs. Integrated Absolute Phase Jitter                | 59          |

| 5.3 Other Jitter Calculatins from Phase Noise                       | 61          |

| 5.4 Simple Phase Noise Estimation for Targeted Absolute Jitter      | 62          |

| 5.5 Spectral Phase Jitter Estimations from the Hybrid-Domain Model  | 64          |

## TABLE OF CONTENTS (Continued)

| 5.5.1 Power Spectral Density of Input Noise Sources       | <u>Page</u><br>66 |

|-----------------------------------------------------------|-------------------|

| 5.5.2 Final Closed-Loop Output Phase Noise Calculation    | 69                |

| 6 Measurement Results and Discussions                     | 73                |

| 6.1 Measurement Setups                                    | 73                |

| 6.2 Measurement Results in Spectral Domain                | 74                |

| 6.3 Measurement Results in Time Domain                    | 77                |

| 6.4 Comparisons for Spectral and Time Domain Measurements | 78                |

| 6.5 Spread-Spectrum Measurements                          | 80                |

| 6.6 Summary and Comparisons                               | 82                |

| 7 Conclusions                                             | 85                |

| Bibliography                                              | 87                |

### LIST OF FIGURES

| <u>Figure</u>                                                                          | <u>Page</u> |

|----------------------------------------------------------------------------------------|-------------|

| 1.1 Conventional Serializer and Deserializer Operations                                | 4           |

| 1.2 Open-Loop Oscillator with and without the SSC Modulation                           | 6           |

| 1.3 Simulated SSC Spectrum for Different SSC Modulation Profiles                       | 8           |

| 1.4 Basic Block Diagarm of a PLL                                                       | 9           |

| 1.5 Block Diagram of a Out-of-Loop-BW Direct SSC Modualtion                            | 12          |

| 1.6 Block Diagram of a In-Loop-BW Frequency Domain SSC Modualtion                      | 13          |

| 1.7 Block Diagram of a In-Loop-BW Frequency Domain SSC Modulation with a Selector.     |             |

| 1.8 Block Diagram of a In-Loop-BW Phase Domain SSC Modualtion                          | 14          |

| 2.1 Block Diagram of the Proposed SSC Architecture                                     | 16          |

| 2.2 Proposed In-Loop-Bw SSC Modulation Technique.                                      | 17          |

| 2.3 Test-Bench of a Conventional Passive Loop Filter transient response                | 19          |

| 2.4 Transient Simulation Results for Various T <sub>W</sub> in the Passive Loop Filter | 20          |

| 2.5 Sampled Loop Filter                                                                | 21          |

| 2.6 Block and Timing Diagrams of the Proposed Charge-Based DT-LF                       | 22          |

| 2.7 Block Diagram for the SSC Modulation Transfer Function (TF <sub>SSC</sub> )        | 24          |

| 2.8 Correlated Double Sampling (CDS) Scheme in the Transconductors                     | 25          |

| 2.9 Signal Diagram of the Proposed SSC Modulation at the Feedback Path                 | 26          |

| 3.1 Details of the Block Diagram in the Proposed SSC Architecutre                      | 28          |

| 3.2 z-Domain Model of the Proposed PLL                                                 | 30          |

| 3.3 PVT Sensitivity Simulations                                                        | 31          |

| 3.4 DT-to-CT and CT-to-DT Conversions around the VCO                                   | 33          |

## LIST OF FIGURES (Continued)

| <u>Figure</u>                                                                           | <u>Page</u> |

|-----------------------------------------------------------------------------------------|-------------|

| 3.5 Hybrid-Domain Model of the Proposed PLL.                                            | 34          |

| 3.6 Comparions for Different PLL Modeling Techniques                                    | 35          |

| 4.1 Block and Timing Diagrams of the Phase Frequency Detector (PFD)                     | 37          |

| 4.2 Schematic of the Charge Pump (CP).                                                  | 39          |

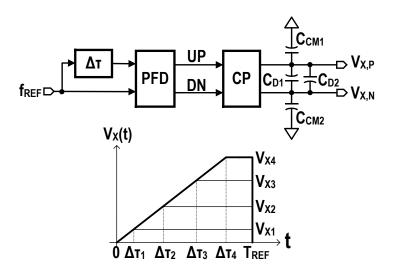

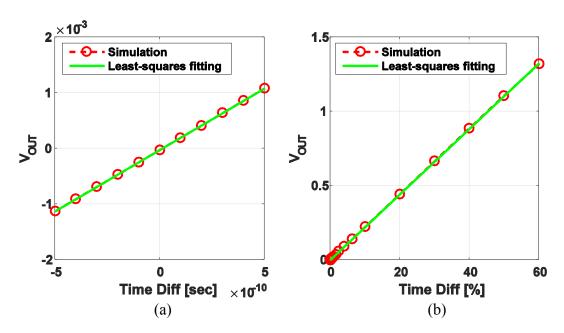

| 4.3 Test-Bench for PFD+CP Linearity Simulations                                         | 40          |

| 4.4 Simulated Voltage at the Node $V_X$ for Various Delay Differences $(\Delta \tau_i)$ | 41          |

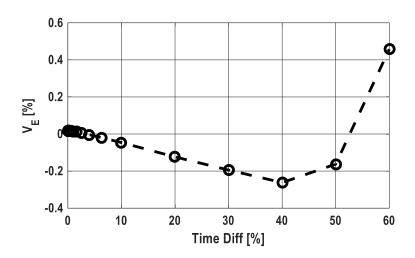

| 4.5 Simulated Linearity Error in the Proposed PFD+CP.                                   | 42          |

| 4.6 Frequency Response from 1/f Noise of the Proposed DT-LF to the Output Pha           | se 43       |

| 4.7 Schematic of the Proposed CDS Transconductor                                        | 44          |

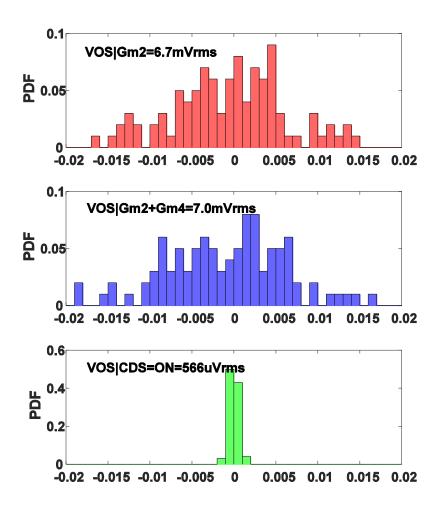

| 4.8 Block Diagram of a CDS Scheme with Noise Sources                                    | 45          |

| 4.9 Monte-Carlo Simulation Results for the Proposed CDS Transconductor                  | 46          |

| 4.10 Simulated Linearity Error in the Proposed CDS Transconductor                       | 47          |

| 4.11 Block Diagram of the Voltage-to-Current Converter and VCO                          | 48          |

| 4.12 Schematic of the Voltage-to-Current Converter                                      | 49          |

| 4.13 Simulated Linearity in K <sub>VCO</sub>                                            | 50          |

| 4.14 Operation Diagram of the SSC Modulation Singal Path                                | 51          |

| 4.15 Schematic of the Unit Current Cell Driver in I-DAC <sub>SSC</sub>                  | 53          |

| 4.16 I-DAC <sub>SSC</sub> Schematic for the Mismatch Analysis.                          | 54          |

| 4.17 Monte-Carlo Simulation Results for the Unit Current Cell in I-DAC <sub>SSC</sub>   | 55          |

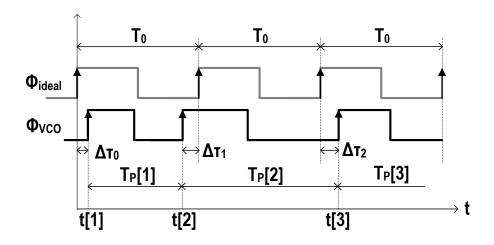

| 5.1 Clock Edge Diagrams to Define the Random Jitter                                     | 57          |

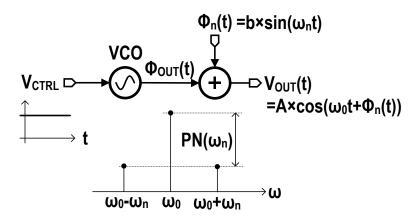

| 5.2 Clock Generator with Phase Noise                                                    | 60          |

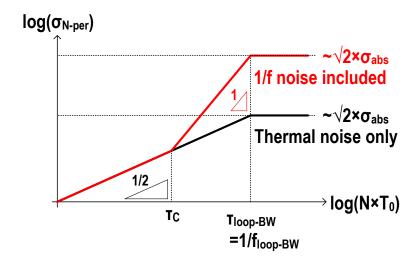

| 5.3 N-Period Jitter vs. the Number of Period (N)                                        | 62          |

## LIST OF FIGURES (Continued)

| <u>Figure</u>                                                                        | <u>Page</u> |

|--------------------------------------------------------------------------------------|-------------|

| 5.4 Hybird-Domain Block Diagram of the Proposed Architecture                         | 64          |

| 5.5 Phase Noise Simulation with Open-Loop Spot Measurements                          | 66          |

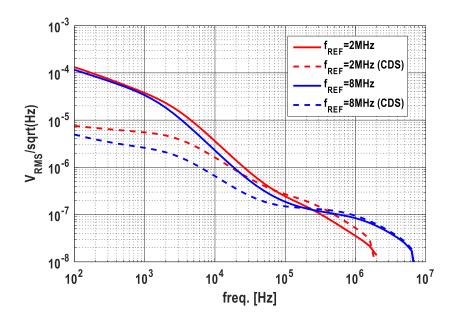

| 5.6 Sampled Noise Simulation of the Proposed DT-LF                                   | 67          |

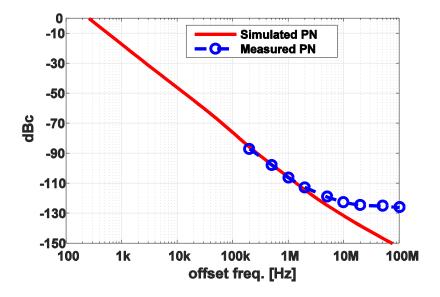

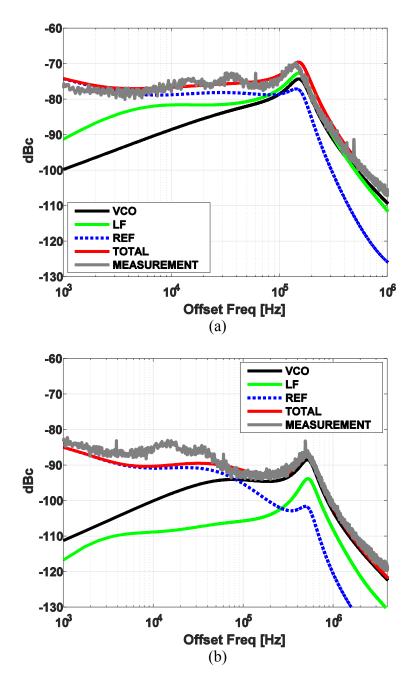

| 5.7 Simulated and Measured Closed-Loop Phase Noise Plots                             | 68          |

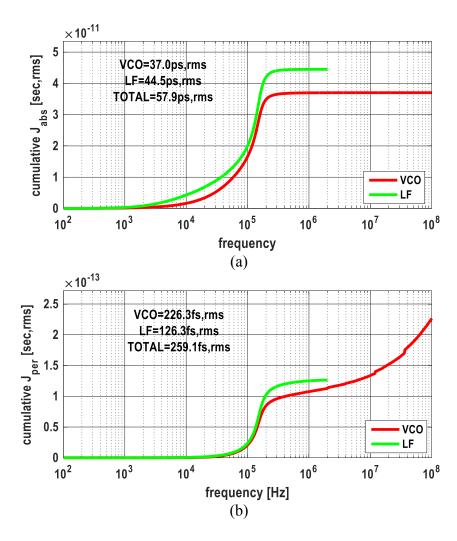

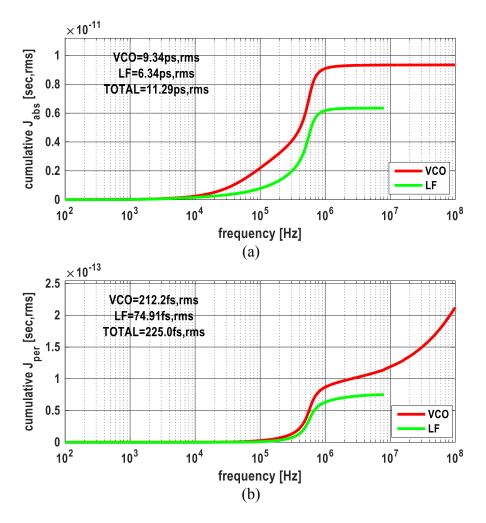

| 5.8 Simulated Cumulative Absolute and Period Phase Jitter for f <sub>REF</sub> =2MHz | 70          |

| 5.9 Simulated Cumulative Absolute and Period Phase Jitter for f <sub>REF</sub> =8MHz | 71          |

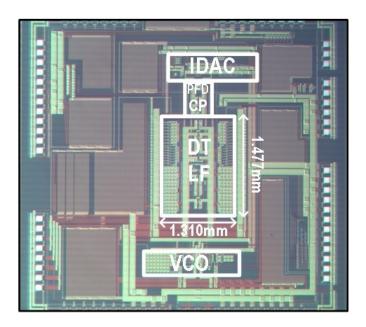

| 6.1 Die Microphotograph                                                              | 73          |

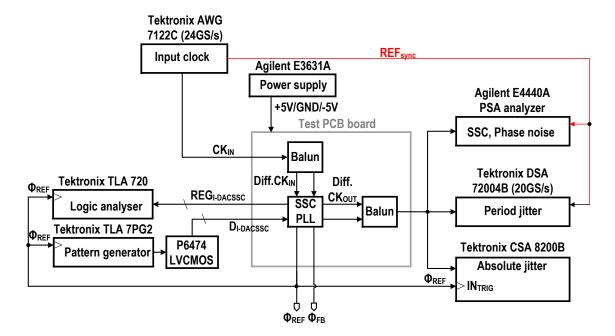

| 6.2 Test Setups for the Proposed SSC Architecture                                    | 74          |

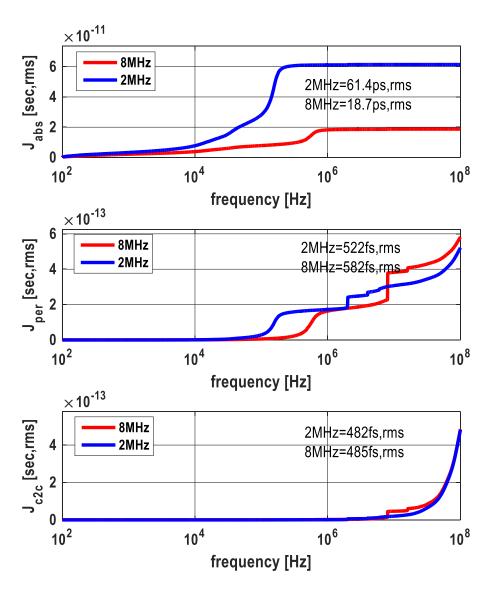

| 6.3 Cumulative Absolute, Period, and Cycle-to-Cycle Phase Jitter Measurements        | 75          |

| 6.4 Mesured Closed-Loop Phase Noise with a First- and Second-Order Differences.      | 76          |

| 6.5 Time Domain Absolute Jitter Mesurements                                          | 78          |

| 6.6 Time Domain Period Jitter Measurements                                           | 78          |

| 6.7 N-Period Jitter vs. N from the Spectral and Time-Domain Measurements             | 80          |

| 6.8 Mesured SSC Spectra with and without the SSC Modulation                          | 81          |

| 6.9 PVT Sensitivity Measurements for Various K <sub>VCO</sub>                        | 82          |

## LIST OF TABLES

| <u>Table</u>                                                      | <u>Page</u> |

|-------------------------------------------------------------------|-------------|

| 1.1 Comparisons between Parallel- and Serial-ATA.                 | 1           |

| 1.2 SerDes Scheme Comparions for Wireline Communication Standards | 3           |

| 5.1 Total Integrated Sampled Noise Summary for the Proposed DT-LF | 67          |

| 6.1 Summary and Comparisons of the Jitter Measurements            | 79          |

| 6.2 Summary and Comparisons of the Proposed SSC Architecture      | 83          |

#### A Wide Modulation Range and PVT-Tolerant Spread-Spectrum Modulation Clock Generator

#### **Chapter 1 - Introduction**

A serializer/deserializer (SerDes) technique is pervasively used to trade speed overhead for physical overhead in a modern wireline communication system. This technique reduces the number of transceivers, but also requires a higher transmission rate. The basic idea behind this technique is to serialize the multi-bit data to a single-bit stream at a transmitter, and then deserialize this single-bit stream back to the original multi-bit data at a receiver. The transmission rate has to be faster than the multi-bit data rate for the equivalent throughput. However, a single transceiver can be used to send the multi-bit data. This significantly relaxes hardware design overheads such as I/O pin count, number of traces, and physical footprint.

Western Digital introduced a parallel advanced technology attachment (P-ATA) interface standard in 1986 for the connection of storage devices such as hard disk, floppy disk, and optical disc drives in a computer. The specifications for this interface standard were initially a 16-bit data width at a rate of 16.7MB/sec without the SerDes technique from Table 1-1. In addition, the P-ATA ribbon cable has 40-pin connectors to send a 16-

|                              | Mode         | # of<br>pins | Data<br>width | Line encoding | Transmission rate | Data<br>rate |

|------------------------------|--------------|--------------|---------------|---------------|-------------------|--------------|

|                              | Ultra DMA -1 | 40           | 16 bits       | N/A           | 16.7 MT/s*        | 16.7 MB/s    |

|                              | Ultra DMA -2 | 40           | 16 bits       | N/A           | 33.3 MT/s*        | 33.3 MB/s    |

| Parallel                     | Ultra DMA -4 | 40           | 16 bits       | N/A           | 66.7 MT/s*        | 66.7 MB/s    |

| ATA <sup>(1)</sup>           | Ultra DMA -5 | 40           | 16 bits       | N/A           | 100 MT/s*         | 100 MB/s     |

|                              | Ultra DMA -6 | 40           | 16 bits       | N/A           | 133 MT/s*         | 133 MB/s     |

|                              | Ultra DMA -7 | 40           | 16 bits       | N/A           | 167 MT/s*         | 167 MB/s     |

|                              | Revision 1.0 | 7            | 16 bits       | 8b/10b        | 1.5 GT/s*         | 150 MB/s     |

| Serial<br>ATA <sup>(2)</sup> | Revision 2.0 | 7            | 16 bits       | 8b/10b        | 3.0 GT/s*         | 300 MB/s     |

|                              | Revision 3.0 | 7            | 16 bits       | 8b/10b        | 6.0 GT/s*         | 600 MB/s     |

|                              | Revision 3.2 | 7            | 16 bits       | 128b/130b     | 16 GT/s*          | 1969 MB/s    |

<sup>\*</sup> MT/GT = Mega-transfer/Giga-transfer

Table 1-1: Comparison between Parallel- and Serial-ATA.

<sup>(1)</sup> https://en.wikipedia.org/wiki/parallel ATA

<sup>(2)</sup> https://en.wikipedia.org/wiki/serial ATA

bit data. Without the SerDes technique, this parallel transmitting protocol requires an individual physical channel (or pin connector) for each transmitting bit, and the transmission rate is equivalent to the data rate.

Since its first invention, there have been six revisions on this P-ATA standard. From Table 1-1, examination of the data rate reveals a 10× improvement from 16.7 MB/sec (Ultra DMA-1) to 167 MB/sec (Ultra DMA-7). However, the maximum achievable data transfer rate on a traditional P-ATA ribbon cable was limited to less than 66MB/sec. Then, several design innovations in both hardware and software had been proposed to overcome this speed limitation, such as differential signaling, equalization, encoding/decoding, and error detection. The speed enhancement from these innovations increased the design complexity and cost of a transceiver as well as its size. On the other hand, the maximum achievable data transfer rate in a mechanical hard disk drive was around 150MB/sec at that time. This speed bottleneck in the hard disk drive made further speed improvement in the data rate less attractive. Therefore, the SerDes technique was leveraged to increase the transmission rate (instead of the data rate) with a single advanced transceiver (instead of 16 transceivers) over a pair of transmission lines (instead of 40-pin connector cable). This SerDes technique saves significant hardware design resources, which is critical for a highly-integrated wireline communication system.

The first transition from the P-ATA (Ultra DMA-7) to the serial-ATA (S-ATA) revision 1.0 was made in 2003. Since the first S-ATA standard was equipped with the SerDes technique, the number of pins went down from 40 to 7, and the transmission rate increased from 167MT/sec to 1.5GT/sec with a similar data rate. The continual increase in the data rate has been empowered thanks to recent technological advances in a storage device such as a high-speed solid-state drive. Following this data rate improvement, the transmission rate has to be increased. This is possible due to the recent advances in the transceiver design mentioned before.

The SerDes technique has been used in almost every modern wireline communication system, such as peripheral component interconnect (from PCI to PCI-

express), and universal serial bus (USB). The brief historical developments of popular interface standards are summarized in Table 1-2. The S-ATA and PCI-express (or PCIe) were evolved from their prior standards, P-ATA and PCI, and both have the SerDes capability. Every revision almost doubles the transmission and date rate simultaneously, and the latest specifications for both standards are the 16GT/sec transmission rate and 1969MB/sec data rate, respectively. This implies that there has been a significant and continual increase at the hardware design overhead for a high-performance application. Therefore, the SerDes technique is essential to relax this hardware overhead. In addition, a very high-speed transceiver design with the SerDes technique becomes an economical solution because a single fast versatile transceiver can replace an array of transceivers.

|                     | Revision | Line encoding | Transmission rate | Data<br>rate |

|---------------------|----------|---------------|-------------------|--------------|

|                     | 1.0      | 8b/10b        | 1.5 GT/s          | 150 MB/s     |

| S-ATA               | 2.0      | 8b/10b        | 3.0 GT/s          | 300 MB/s     |

| S-ATA               | 3.0      | 8b/10b        | 6.0 GT/s          | 600 MB/s     |

|                     | 3.2      | 128b/130b     | 16 GT/s           | 1969 MB/s    |

| PCIe <sup>(1)</sup> | 1.0      | 8b/10b        | 2.5 GT/s          | 250 MB/s     |

|                     | 2.0      | 8b/10b        | 5 GT/s            | 500 MB/s     |

|                     | 3.0      | 128b/130b     | 8 GT/s            | 984.6 MB/x   |

|                     | 4.0      | 128b/130b     | 16 GT/s           | 1969 MB/s    |

|                     | 1.1      | N/A           | 12 MT/s           | 1.5MB/s      |

| USB <sup>(2)</sup>  | 2.0      | N/A           | 280 MT/s          | 35 MB/s      |

|                     | 3.0      | 8b/10b        | 4 GT/s            | 400 MB/s     |

|                     | 3.1      | 128b/132b     | 10 GT/s           | 1.21 GB/s    |

<sup>(1)</sup> https://en.wikipedia.org/wiki/PCI Express

Table 1-2: SerDes scheme comparions for wireline communication systems.

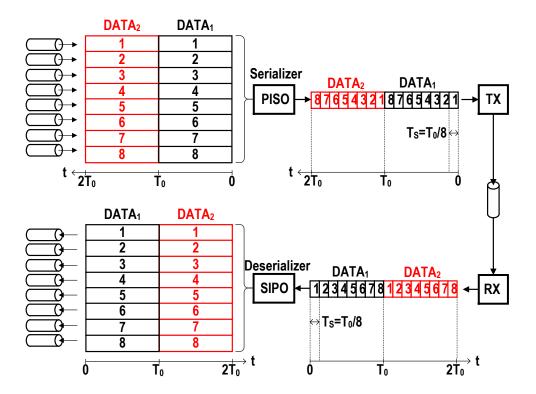

Fig. 1-1 describes general SerDes operation. In the transmitter side, multi-bit data (8-bit in this example) is updated from a data bus, and delivered to the serializer. The serializer is the parallel-in serial-out (PISO) block, and multiplexes the parallel data into a

<sup>(2)</sup> https://en.wikipedia.org/wiki/USB

single serial bit steam at a rate of 8× faster than the original update rate f<sub>0</sub>. This serialized stream is sent to the receiver over a single channel. The received bit stream is recovered to the original parallel data using a deserializer, which is the serial-in parallel-out (SIPO) block. Therefore, this SerDes technique basically trades the physical overhead with the speed overhead. There are several SerDes techniques described in [1]. They include i) parallel clock SerDes, ii) 8b/10b SerDes, iii) embedded clock bits SerDes, and iv) bit interleaving SerDes. In the parallel clock SerDes technique, the clock signal is transmitted in a separated channel to synchronize wireline systems. In the embedded clock bits SerDes technique, the clock signal is embedded in the data stream. In order to obtain DC balance, extra line encoding bits are added using an encoding algorithm in the 8b/10b SerDes technique. Lastly, in the bit interleaving SerDes technique, several slower serial data streams are interleaved into a faster serial stream.

Figure 1-1: Conventional serializer and deserializer operation.

One major drawback of the SerDes technique is that they exacerbate electromagnetic interference (EMI) since a higher transceiver rate creates stronger radiated emission to adjacent systems [2]. The definition of the EMI from [3] is "the impairment of the extraction of information from a wanted electromagnetic signal caused by electromagnetic noise, where the electromagnetic noise is all electromagnetic energy from both intentional and unintentional radiators except the desired signal for a specific system of interest." In general, interference can be categorized into conducted disturbances and radiated disturbances, and the radiated disturbance can be distinguished into capacitive and inductive couplings. From a crosstalk example between two parallel traces on a printed circuit board (PCB) in [2], voltage disturbance at a victim's trace is proportional to incident frequency and capacitive coupling coefficient. As seen from Table 1-2, the transceiver rates (for both S-ATA and PCI express) are increasing up to 16GT/sec, which is more than 100× increase from the first revision (SATA revision 1.0). The USB, which is the most popular interface system, can support up to 10 GT/sec. This rate is 1/6 of the radiating frequency in an mmWave radar system.

In addition, the capacitive coupling coefficient has been increasing, too. The capacitive coupling coefficient is a function of physical proximity and relative permittivity in a PCB. Following miniaturizing integrations in a PCB, the pitch size of chips and the width of traces has been scaling down. To keep the same characteristic impedance in traces, the thickness of the dielectric has been decreasing, whereas the relative permittivity of a dielectric has been increasing. This results in an inevitable increase of the capacitive coupling coefficients among traces and chips. Therefore, regulating EMIs and isolating cross-couplings in multiple high speed clocks/signals across a jammed PCB module is very critical and demanding in a modern highly-integrated wireline system. There are several pervasive remedies: shielding [4], pulse shaping or slew rate control [5], low-voltage differential signaling (LVDS), staggering, special layout techniques, and spread-spectrum clocking (SSC) [6]. Particularly, the SSC technique becomes an essential solution to mitigate EMI issues.

#### 1.1 Spread-spectrum Clock (SSC)

The SSC technique modulates the output frequency of a clock generator, and this is a variant of a frequency modulation. This technique slowly modulates the output frequency with a designated frequency modulation profile, and spreads the output power spectral density (PSD) into the designated frequency modulation range.

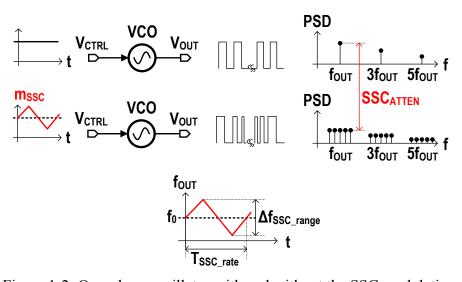

Figure 1-2: Open-loop oscillator with and without the SSC modulation.

In an open-loop clock generator as shown in the top of Fig. 1-2, if the nominal input of a VCO is constant, it generates the unmodulated PSD tones at not only the output frequency ( $f_{OUT}$ ), but also odd harmonics ( $3 \times f_{OUT}$ ,  $5 \times f_{OUT}$ , and so on). As shown in the bottom of Fig. 1-2, if the modulating SSC signal ( $m_{SSC}(t)$ ) is superimposed on top of the nominal input at the control voltage ( $V_{CTRL}$ ), this modulation signal stimulates the VCO to deviate the output frequency from the center frequency and spread the output tone along the SSC modulation range.

The SSC modulation range ( $\Delta f_{SSC\_range}$ ) determines how wide the output tones are spread. The SSC modulation rate ( $f_{SSC\_rate}$ ) determines how fast the SSC modulation signal changes. In addition, the amount of attenuation due to the SSC is the SSC attenuation ( $SSC_{ATTEN}$ ). For example, if there is a carrier at 1GHz with the total power of

0dBm, and one can evenly spread this single tone into ten multiple spreading tones (from 0.91GHz to 1.09GHz with a 20MHz step), the output PSD of the spreading tones becomes -10dBm. Then, this results in the 10dB SSC<sub>ATTEN</sub> from the SSC technique. In the S-ATA,  $\Delta f_{SSC\_range}$ ,  $f_{SSC\_rate}$ , and SSC<sub>ATTEN</sub> specifications are +0.035~-0.5%, 30~33kHz, and  $\geq$ 7dB, respectively.

Although the shape of  $m_{SSC}(t)$  is a triangular waveform in Fig. 1-2, there are three popular types of  $m_{SSC}(t)$ : sinusoid, triangular, and cubic (Hershey kiss).

#### 1.2 Qualitative Analysis for the SSC

Since the SSC is one special case of the frequency modulation, the qualitative analysis for the SSC can be borrowed from the wideband frequency modulation bandwidth analysis [7]. Let  $m_{SSC}(t) = A_{SSC} \times \cos(\omega_{SSC\_rate}t)$ , which is the sinusoid SSC modulation. The output of the clock  $(V_{OUT}(t))$  is written as:

$$V_{OUT}(t) = A_{OUT} \cdot \sum_{n = -\infty}^{+\infty} J_n(\beta) \cdot \cos(\omega_{OUT} + n\omega_{SSC\_rate})t$$

(1)

where  $J_n(\beta)$  is the Bessel function of the first kind and the n-th order,  $\beta$  is  $K_{VCO} \times A_{SSC\_rate}/\omega_{SSC\_rate}$ , which is equivalent to  $0.5 \times \Delta f_{SSC\_range}/f_{SSC\_rate}$ ,  $A_{OUT}$  is the amplitude of the output  $V_{OUT}(t)$ , and  $K_{VCO}$  is the frequency gain of a VCO in rad×Hz/Volt. There are two observations from (1): i) the magnitude of the sidebands is  $J_n(\beta)$ , and  $J_n(\beta)$  is negligible for  $n > \beta + 1$ , and ii) there are infinite sidebands through  $f_{OUT,0} \pm n \times f_{SSC\_rate}$ , where  $f_{OUT,0}$  is the center frequency of  $V_{OUT}(t)$ . From the first observation, the SSC modulation bandwidth (BW<sub>SSC</sub>) is written as:

$$BW_{SSC} \cong 2 \cdot (\beta + 1) \cdot f_{SSC\_rate} = 2 \cdot \left(\frac{\Delta f_{SSC\_range} / 2}{f_{SSC\_rate}} + 1\right) \cdot f_{SSC\_rate} = \Delta f_{SSC\_range} + f_{SSC\_rate}$$

(2)

Since  $\Delta f_{SSC\_range}$  is generally much larger than  $f_{SSC\_rate}$ ,  $BW_{SSC}$  is approximately equal to  $\Delta f_{SSC\_range}$ . From the second observation, the SSC modulation tones are allocated every  $f_{SSC\_rate}$  step through the  $BW_{SSC}$ . Therefore, the total number of the spreading tones is  $\Delta f_{SSC\_range}/f_{SSC\_rate}$ . Then, if the modulated output tones are evenly spread through  $BW_{SSC}$ ,

the SSC<sub>ATTEN</sub> can be written as:

$$SSC_{ATTEN|dB} = 10 \cdot log_{10} \left( \Delta f_{SSC \text{ range}} / f_{SSC \text{ rate}} \right).$$

(3)

These results for the sinusoidal SSC modulation can be applicable to both the triangular and cubic SSC profiles, which are easily decomposed into  $\pm n \times \omega_{SSC\_rate}$  sinusoidal tones from the Fourier series analysis.

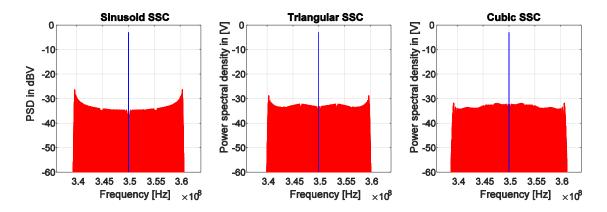

The output SSC PSD results for three different SSC profiles are shown in Fig. 1-3, which are plotted using 5.34kHz of the resolution bandwidth (RBW), 11.35kHz of  $f_{\rm SSC\_rate}$ , and  $\pm 3\%$  (or  $\pm 10.5$ MHz) of  $\Delta f_{\rm SSC\_range}$ . From (2)-(3), BW<sub>SSC</sub> and SSC<sub>ATTEN</sub> are calculated to 21MHz and 32.67dB, respectively. The flatness of the spread spectrum is dependent on how to set the higher order Fourier series coefficients in the SSC profile. By tailoring the higher order terms, one can engineer the shape of the spread spectrum. In addition, in order to obtain further dispersed spread tones, the work in [8]-[9] superimposed a random dithering signal on top of the deterministic SSC modulation signal.

Figure 1-3: Simulated SSC spectrum for different SSC modulation profiles: sinusoid, triangular, and cubic (Hershey Kiss).

#### 1.3 Definition of the Loop Bandwidth (BW) in a PLL

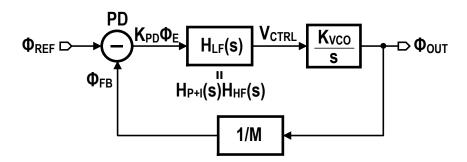

Achieving an accurate and reliable clock above a few hundred MHz generally requires a negative feedback loop. From a crystal reference clock source, which is supposed to be very accurate and reliable, the negative feedback loop in a PLL tries to lock the output phase ( $\phi_{OUT}$ ) of a VCO to the clean reference phase ( $\phi_{REF}$ ) as shown in Fig. 1-4. The PLL generally consists of a phase detector (PD), loop filter (LF), VCO, and frequency divider (FD). Two phases ( $\phi_{OUT}$  and  $\phi_{REF}$ ) are compared in the PD, and the resulting phase error ( $\phi_{E}$ ) is filtered through the loop filter. The filtered output appears at the control voltage ( $V_{CTRL}$ ), which drives the VCO. When the loop is locked properly, the control voltage  $V_{CTRL}$  sets the divided average frequency of the VCO output (= $f_{OUT}/M$ ) to the input frequency ( $f_{REF}$ ).

Figure 1-4: Basic block diagram of a PLL.

In wireline communication systems, designing a PLL strongly relies on jitter specifications, and the loop bandwidth (BW) is a key design parameter to optimize these jitter specifications. It is well-known that a wider loop BW is desirable to give larger suppression of the VCO phase noise, whereas a narrower loop BW is preferred to attenuate jitter contributions from a reference clock, phase detector, and loop filter. This is because if the phase noise from the VCO is fluctuating slower than the loop BW, the negative loop can track this noisy output phase  $\phi_{OUT}$  and correct it with respect to the clean input reference phase  $\phi_{REF}$ . However, if the output phase noise is moving faster

than the loop BW, the negative loop cannot correct the noisy output phase due to insufficient loop gain and tracking speed. Therefore, The VCO phase noise, which disturbs faster than the loop BW, directly appears at the output phase  $\phi_{OUT}$  without noise filtering, indicating that the frequency response from the VCO phase noise ( $\phi_{VCO}$ ) to the output phase  $\phi_{OUT}$  is a high-pass response. On the other hand, if the reference phase noise is perturbing faster than the loop BW, this noisy perturbation is filtered out at the loop filter, indicating that the frequency response from the input reference phase noise to the output phase  $\phi_{OUT}$  is a low-pass response. Therefore, the loop BW is a critical design variable to determine rolling-off frequency for both phase noise transfer functions. In general, a wider loop BW is typically preferred in a PLL with a ring-based VCO, whereas a narrow loop BW is preferred in a PLL with a low noise LC VCO.

There is no single definition of the loop BW to fulfill for all purposes, and natural frequency, loop gain, noise bandwidth, and 3-dB bandwidth can be a reasonable candidate [10]. However, as following [10], a loop gain ( $K_{LG}$ ) is defined as the loop BW in this work. The definition of the loop gain  $K_{LG}$  is the proportional path gain coefficient in the loop. In general, the loop filter can be formulated into the combination of a low frequency loop filter, which consists of proportional and integral filters ( $H_{P+I}(s)$ ), and high frequency loop filter ( $H_{HF}(s)$ ). The proportional and integral filter combination  $H_{P+I}(s)$  is dominant below the loop BW because their poles and zeros are located in relatively less or equal to the loop BW. This low frequency loop filter  $H_{P+I}(s)$  can be rewritten as  $K_1+K_2/s$  in a Type-II PLL. On the other hand, since the high frequency loop filter  $H_{HF}(s)$  has poles and zeros in higher frequencies, which are much larger than the loop BW, this filter can be approximated to  $H_{HF}(0)$  inside the loop BW. Then, the loop BW (or loop gain  $K_{LG}$ ) can be written as:

$$K_{LG} = K_{PD} \cdot \frac{K_{VCO}}{2\pi} \cdot K_1 \cdot H_{HF}(0) / M$$

(4)

where K<sub>PD</sub>, K<sub>VCO</sub>, K<sub>1</sub>, and M are the phase detector gain, the VCO gain, the proportional path gain, and the frequency division ratio in the frequency divider, respectively. The

loop gain  $K_{LG}$  has a dimension of Hz, whose unit is equivalent to the loop BW. In addition, the gain crossover frequency (Hz) in an open-loop bode plot is approximately same to  $K_{LG}$  [10].

#### 1.4 Prior SSC Architectures

The next question is how to inject the SSC modulation signal inside a PLL. The SSC modulation signal m<sub>SSC</sub>(t) is generally a periodic signal with a finite BW, and the SSC modulation signal needs to be properly placed inside the pass band of SSC transfer function (TF<sub>SSC</sub>). The SSC transfer function TF<sub>SSC</sub> is from the modulation signal m<sub>SSC</sub>(t) to the output clock frequency f<sub>OUT</sub>. Since the transfer function TF<sub>SSC</sub> relies on the loop BW, one needs to set the loop BW by taking into account both the phase noise transfer functions and the SSC transfer function TF<sub>SSC</sub>.

There are three popular ways to generate a SSC modulation: out-of-loop-BW direct SSC modulation, in-loop-BW SSC modulation, and two-point SSC modulation.

### 1.4.1 Out-of-Loop-BW Direct SSC Modulation

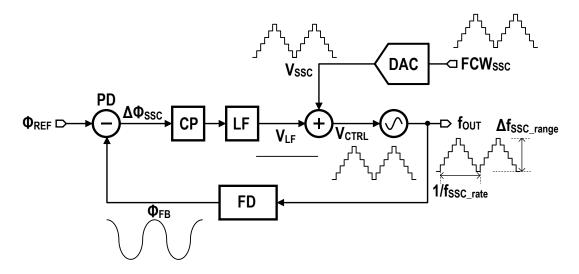

The most convenient method to implement the SSC modulation is to directly inject the SSC modulation signal at the control voltage  $V_{CTRL}$  of a VCO. This SSC scheme is called the out-of-loop-BW direct SSC modulation [11]-[13]. As shown in Fig. 1-5, the SSC modulation signal directly modulates the  $V_{CTRL}$  of the VCO, and the returning phase modulated signal  $\Delta \varphi_{SSC}$  is attenuated in the narrow BW loop filter. Therefore, the SSC modulation signal has to be carried outside of the loop BW. In other words, the loop BW has to be sufficiently smaller than the SSC modulation pass band. Because the SSC modulation rate  $f_{SSC\_rate}$  is around 10kHz to 300kHz, the loop BW in this out-of-loop-BW SSC modulation technique must be sufficiently smaller than the lowest bound of the modulation pass band, which is 10kHz in this work. This results in a prohibitively large loop filter and limited suppression of the VCO phase noise. Another critical drawback of this direct SSC modulation technique arises because the SSC modulation range changes as the VCO gain  $K_{VCO}$  varies due to PVT variations.

Figure 1-5: Block diagram of an out-of-loop-BW direct SSC modulation.

#### 1.4.2 In-Loop-BW SSC Modulation

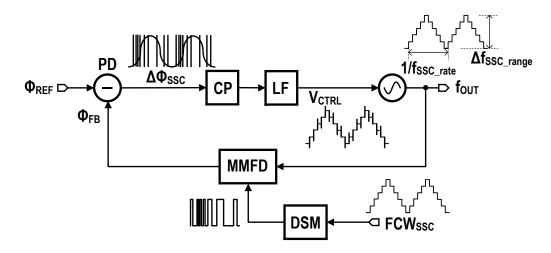

The in-loop-BW SSC modulation technique employs either frequency domain SSC modulation with a delta-sigma modulator (DSM) [14]-[17] or phase domain SSC modulation with a time-to-digital converter (TDC) in all-digital PLLs [18]-[19]. In this in-loop-BW SSC modulation technique, the SSC modulation signal is injected inside the loop BW.

Fig. 1-6 shows the in-loop-BW frequency domain SSC modulation with a DSM. The SSC modulation frequency control word (FCWssc) drives the DSM, which determines the frequency division ratio for the multi-modulus frequency divider (MMFD). This dithered instantaneous frequency division ratio, which is an integer ratio, is averaged to a fractional ratio through the loop filter. Based on this fractional-N frequency synthesis technique, one can obtain the target SSC frequency modulation by using the frequency control word FCWssc. One drawback is that all in-band DSM dithering noise leaks inside the loop BW and appears at the control voltage (Vctrl). This results in a trade-off between the VCO phase noise and DSM dithering noise. By

increasing the loop BW, one can increase the suppression of the VCO phase noise while the DSM dithering noise leaks more inside the loop BW, and vice versa.

Figure 1-6: Block diagram of an in-loop-BW frequency domain SSC modulation.

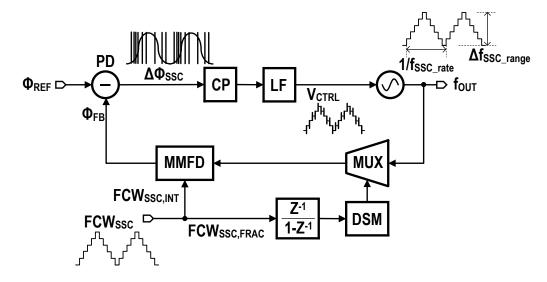

Figure 1-7: Block diagram of an in-loop-BW frequency domain SSC modulation with a phase selector.

One can obtain a smaller dithering step size by using a phase selector or phase interpolator [16] as shown in Fig. 1-7. By either subdividing the output phase into multiple phase levels  $\phi_{OUT,0\sim N-1}$  or generating multiple phases from a ring-based VCO, the

dithering step size of the DSM is subdivided. This technique helps to mitigate both the dithering noise and spurs.

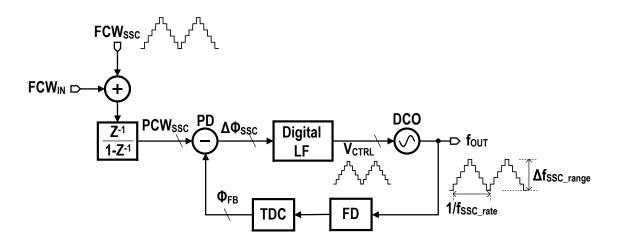

Fig. 1-8 shows the phase domain in-loop-BW SSC modulation technique with a time-to-digital converter (TDC) or phase quantizer [18]-[19] in all-digital PLLs. This technique requires a TDC or phase quantizer to quantize the output phase  $\phi_{FB}$  from the VCO. The input frequency control word FCW<sub>IN</sub> with the additional SSC frequency control word FCW<sub>SSC</sub> are digitally accumulated and converted to the corresponding phase control word (PCW<sub>SSC</sub>). The phase control word PCW<sub>SSC</sub> and the quantized output phase  $\phi_{FB}$  are compared with a digital phase detector, and the residual digital phase difference  $\Delta\phi_{SSC}$  is filtered in the digital loop filter. This filtered digital control voltage  $V_{CTRL}$  drives the digitally controlled oscillator (DCO). However, there are two quantization errors from a TDC (or phase quantizer) and DCO in this phase domain SSC technique, and these two quantization errors create a undesirable trade-off between accuracy and power.

These in-loop-BW SSC techniques can achieve a robust SSC frequency modulation from PVT variations of  $K_{VCO}$ . This is because either the DSM based fractional frequency divider or the digitally controlled phase accumulation guarantees the desired frequency division ratio between the input reference frequency  $f_{REF}$  and the output frequency  $f_{OUT}$  using a strong loop gain.

Figure 1-8: Block diagram of an in-loop-BW phase domain SSC modulation.

#### **1.4.3** Two-Points SSC Modulation

The two-point SSC modulation technique is a combination of both the out-of-loop-BW and in-loop-BW SSC modulation schemes [20]-[22]. Two separate modulation signals are injected at the VCO (or DCO in an all-digital PLL) and at the MMFD (or FCW<sub>SSC</sub> in an all-digital PLL). In this way, this two-point SSC modulation technique allows one to determine the loop BW independently from the SSC modulation pass band. However, matching the SSC modulation gains for two different modulation injection points is not trivial, and the out-of-loop-BW SSC modulation gain is still susceptible to the PVT variations of Kyco.

#### 1.5 Observations and Motivations

A multifunctional print module requires demanding SSC specifications such as more than  $\pm 3\%$  modulation range with 10kHz modulation rate on multiple clock phases, which is exceptionally demanding, compared to other conventional SerDes systems, such as the S-ATA, which requires 0~0.5% SSC modulation range with 33kHz SSC modulation rate. For this particular application, a ring-based oscillator is preferred to achieve the multiple clock phases. The out-of-loop-BW direct SSC modulation is not a good candidate because the inevitable narrow loop BW results in a prohibitively large loop filter and significant jitter contribution from a VCO. In the frequency domain inloop-BW SSC modulation with a DSM, additional spurs and in-band dithering noise from the DSM are inevitable. In the phase domain in-loop-BW SSC modulation technique, this larger SSC modulation range requirement needs demanding acquisition range of the TDC with a sub-pico second time step, which could result in unacceptable power dissipation in a 0.18µm CMOS technology. For example, the work in [19], which was implemented in a 22nm CMOS technology, requires 24bits FCW<sub>SSC</sub> to support 0~2% SSC modulation range and 25kHz modulation rate by consuming 15.4mA total current. Therefore, to overcome these limitations, a new in-loop-BW SSC modulation architecture is required.

#### **Chapter 2 – Proposed SSC Architecture**

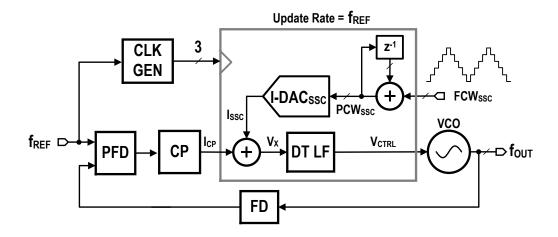

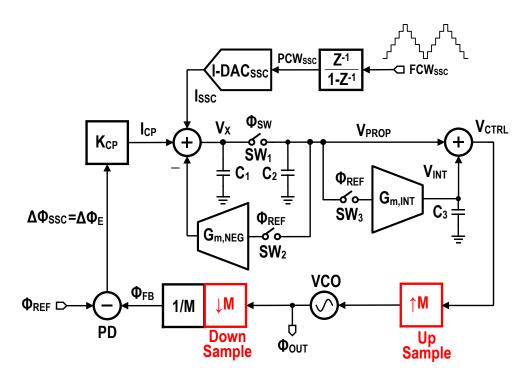

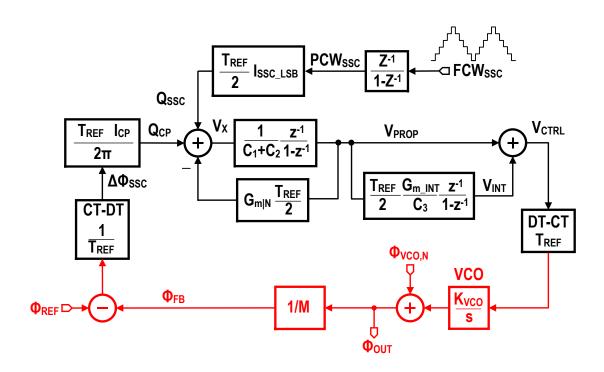

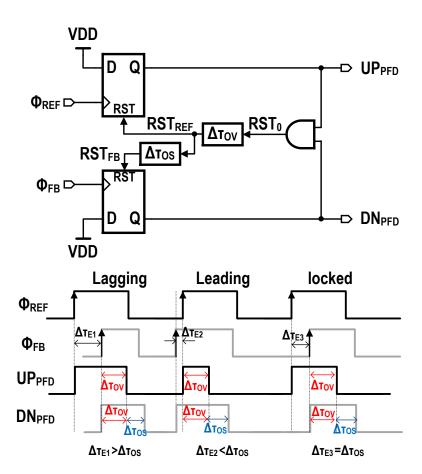

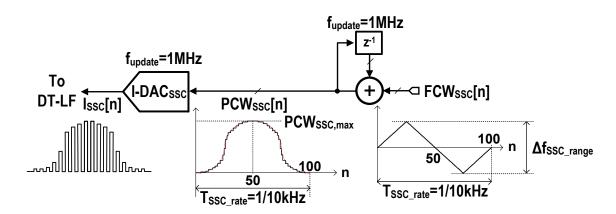

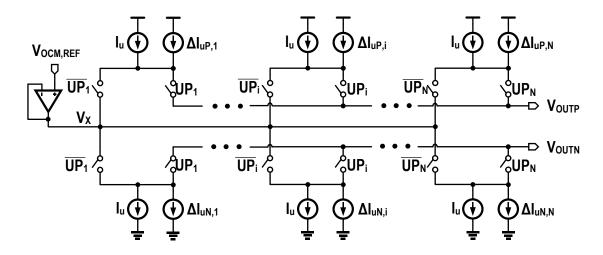

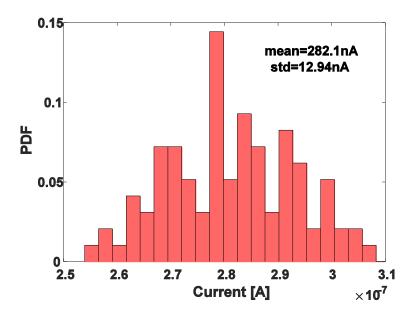

Fig. 2-1 shows the block diagram of the proposed phase domain in-loop-BW SSC architecture. This proposed architecture consists of a phase frequency detector (PFD), charge pump (CP), discrete time loop filter (DT-LF), SSC return-to-zero (RZ) current digital-to-analog converter (I-DAC<sub>SSC</sub>), digital integrator, ring VCO, and frequency divider (FD). The CLK GEN block creates three clock phases for the proposed charge-based DT-LF and I-DAC<sub>SSC</sub> at the rate of f<sub>REF</sub>. The SSC frequency control word FCW<sub>SSC</sub> is a triangular spread-spectrum modulation signal, and this FCW<sub>SSC</sub> is digitally accumulated to convert to a phase domain modulation signal PCW<sub>SSC</sub>. This accumulated PCW<sub>SSC</sub> drives the I-DAC<sub>SSC</sub>, which injects the phase domain SSC modulation signal into the loop. The charge-based DT-LF combines both the I-DAC<sub>SSC</sub> modulation current (I<sub>SSC</sub>) and charge pump current (I<sub>CP</sub>), and updates V<sub>CTRL</sub>.

Figure 2-1: Block diagram of the proposed SSC architecture.

Similar to the phase domain in-loop-BW SSC modulation technique in all digital PLLs [18]-[19], this proposed scheme performs the SSC modulation in the phase domain. However, the phase domain operations are performed in the analog domain without the help of a TDC or phase quantizer. In addition, this proposed SSC architecture achieves

significant relaxed PVT sensitivity as other conventional in-loop-BW DSM-based or TDC-based SSC architectures achieve [14]-[19].

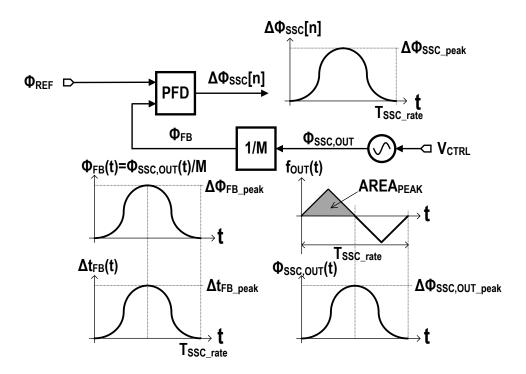

Figure 2-2: Proposed in-loop-BW SSC modulation technique.

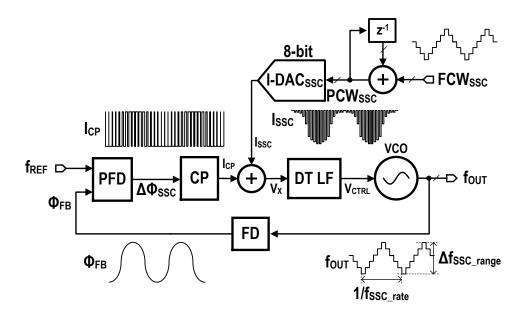

### 2.1 Proposed Phase Domain In-Loop-BW SSC Modulation

Fig. 2-2 shows the proposed in-loop-BW SSC modulation technique. The SSC modulation of the output clock is achieved by providing a triangular ramp on the FCW<sub>SSC</sub>. The digitally accumulated PCW<sub>SSC</sub> is converted to the return-to-zero I<sub>SSC</sub> in I-DAC<sub>SSC</sub>, whose magnitude is proportional to PCW<sub>SSC</sub> and the width is fixed to 50% of the reference period T<sub>REF</sub>. Due to the SSC frequency modulation of the VCO, a SSC phase difference  $\Delta \phi_{SSC}$ , which is the difference between the divided VCO phase output  $\phi_{FB}$  and the input reference frequency phase  $\phi_{REF}$ , is created. This SSC phase difference  $\Delta \phi_{SSC}$  results in the pulse-width modulated I<sub>CP</sub> at the output of the charge pump. Since this SSC charge pump current I<sub>SSC</sub> cancels a part of the I-DAC<sub>SSC</sub> current I<sub>CP</sub>, the residual current is integrated and converted to a charge signal on a sampling capacitor in the

proposed DT-LF. This sampled charge signal is filtered to generate a triangular SSC signal at V<sub>CTRL</sub>, which modulates the VCO output frequency f<sub>OUT</sub>.

In the proposed architecture, the loop filter input is the sum of  $I_{SSC}$  and  $I_{CP}$ . The  $I_{SSC}$  is a return-to-zero current pulse, whereas the  $I_{CP}$  is a pulse-width modulated current pulse. Filtering these two different types of current signals with a conventional passive loop filter creates unacceptable spurs at the output, which destroys the shape of the spread spectrum. Therefore, a new charge-based DT-LF is proposed. Before presenting details of the proposed DT-LF, it is useful to examine the limitations of a conventional charge-pump PLL with a passive loop filter in the proposed in-loop-BW SSC modulation technique.

#### 2.2 Limitations of a Conventional Passive Loop Filter

In a charge-pump PLL with a conventional passive loop filter, it is common to model the PFD, CP, and loop filter as s-domain linear transfer functions [10], [23]. However, the PFD operation is discrete-time because the PFD samples phases and updates the difference at a rate of f<sub>REF</sub>. In addition, the resulting current (I<sub>CP</sub>) from the charge pump is a pulse-width modulated current, which maintains the information in its width. This charge pump current information is also updated at a rate of f<sub>REF</sub>. Therefore, the PFD and CP are operating in a discrete-time manner.

When the SSC modulation is disabled, absolute jitter in the PLL creates phase error in the PFD, and results in very narrow current pulses at the output of the CP, whose standard deviation of the width is on the order of tens of pico-second. This very thin pulse-width modulated current pulse can be approximated as a corresponding impulse signal, whose magnitude is weighted by the phase error information. With this approximation, the linear s-domain transfer function for the PFD, CP, and passive LF can be obtained from the weighted impulse response of the passive LF, which is equivalent to convolving the weighted impulse signal with the s-domain transfer function of the passive loop filter.

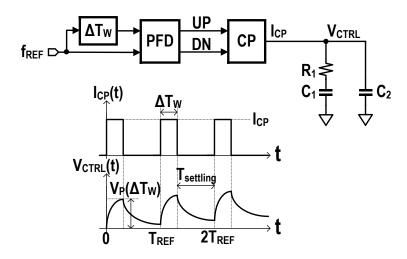

However, when the SSC modulation is enabled, this continuous-time impulse approximation cannot be valid. Fig. 2-3 shows the one example of the transient response at the control voltage  $V_{CTRL}$  due to the SSC modulation with a conventional passive loop filter. First, the width  $T_W$  of the pulse-width modulated current pulses  $I_{CP}$  is too large (could be 75% of the update period  $(T_{REF})$ ) to make the approximation. In addition, since the time constant of the loop filter  $(\tau_{LF})$  is relatively large with respect to the update period  $T_{REF}$ , the significant transient glitches appear at the control voltage  $V_{CTRL}$ . Finally, the transient glitches create unacceptable spurs at the output spectrum, and they destroy the shape of the spread-spectrum.

Figure 2-3: Test-bench of a conventional passive loop filter transient response.

To quantitatively elaborate this transient glitch, the peaking voltage  $(V_P)$  of the transient response at  $V_{CTRL}$  is calculated to:

$$V_{P}(T_{W}) = \frac{I_{CP}}{C_{1} + C_{2}} \cdot T_{W} + I_{CP}R_{1} \cdot \frac{C_{1}^{2}}{(C_{1} + C_{2})^{2}} \cdot (1 - e^{-T_{W}/\tau_{LF}})$$

$$\cong \frac{I_{CP}}{C_{1} + C_{2}} \cdot T_{W} + I_{CP}R_{1} \cdot (1 - e^{-T_{W}/\tau_{LF}})$$

(5)

where T<sub>W</sub>, I<sub>CP</sub>, and  $\tau_{LF}$  are width of the charge pump current due to the SSC phase

difference  $\Delta\phi_{SSC}$ , the gain of the charge pump, and  $R_1 \times C_1C_2/(C_1+C_2)$ , respectively. The first term in (5) is the wanted output result at node  $V_{CTRL}$ , which is proportional to  $T_W$ , whereas the second term in (5) is unwanted transient glitch due to finite time constant  $\tau_{LF}$ . This second term in (5) roots from the voltage drop across  $R_1$  when the current  $I_{CP}$  goes through  $R_1$  during  $T_W$ .

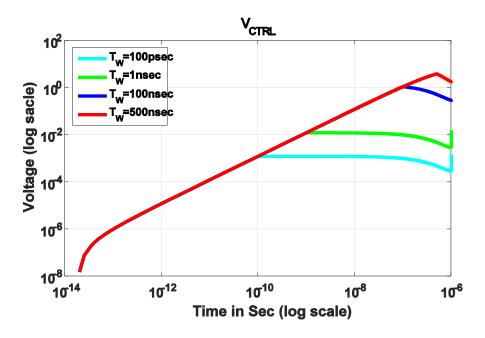

Figure 2-4: Transient simulation results for various T<sub>W</sub> in the passive loop filter.

There are three important observations from (5): i) the undesired transient peaking is proportional to the product of  $I_{CP}$  and  $R_1$ , ii) a larger  $T_W$  delivers larger peaking voltage  $V_P$ , and iii) a larger  $T_W$  results in worse incomplete settling error due to shorter settling time ( $T_{REF}$ - $T_W$ ). Fig. 2-4 compares the transient simulation results for various  $T_W$  values in the conventional passive loop filter, whose design variables are  $R_1$ =5.65kohm,  $C_1$ =398pF, and  $C_2$ =79.6pF.  $I_{CP}$ =1mA,  $T_{REF}$ =1 $\mu$ sec, phase margin = 60°, and loop BW =  $f_{REF}$ /10 are used in the simulations. In this example, the loop filter time constant  $\tau_{LF}$  is 0.375 $\mu$ sec in  $T_{REF}$ =1 $\mu$ sec, and this reveals that 100psec or 500nsec (50% of  $T_{REF}$ ) of  $T_W$  gives 1.25mV or 3.93V voltage glitch  $V_P$  with 72.89 $\mu$ V or 0.763V incomplete settling

error, respectively. Therefore, these severe glitch and incomplete settling error are not acceptable for the proposed SSC modulation technique since the achievable maximum tuning range of the control voltage  $V_{CTRL}$  should be less than 500mV (or even smaller for a better linearity of  $K_{VCO}$ )

#### 2.3 Proposed Charge-Based Discrete Time Loop Filter (DT-LF)

In a conventional fractional-N synthesizer with a conventional passive loop filter, strong spurs due to the DSM dithering noise are well-known problem. Although the DSM dithering phase error at the PFD is not as large as the SSC modulation phase difference  $\Delta\phi_{SSC}$ , one can find some valuable insights from loop filter topologies in low spur fractional-N synthesizers.

Figure 2-5: Sampled loop filter.

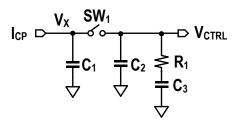

Particularly, the work in [24] presents the sampled loop filter as shown in Fig. 2-5. When SW<sub>1</sub> is open, the pulse-width modulated current pulse  $I_{CP}$  is integrated in a capacitor  $C_1$ . Then, when SW<sub>1</sub> is closed, the accumulated charge is shared to the conventional passive loop filter. Using this sampled loop filter, the second term of the glitch voltage  $V_P$  in (5) is significantly reduced. The glitch  $V_P$  is proportional to the voltage difference ( $V_X$  -  $V_{CTRL}$ ), instead of the  $I_{CP} \times R_1$  product. It is because when SW<sub>1</sub> is closed, the initial voltage drop across  $R_1$  is  $V_X$  -  $V_{CTRL}$ . Generally, both  $I_{CP}$  and  $R_1$  are important design parameters, and the loop gain  $K_{LG}$  (and loop BW) is proportional to the  $I_{CP} \times R_1$  product. Therefore, there is a trade-off between the magnitude of the undesired transient glitch  $V_P$  and the loop gain  $K_{LG}$  (loop BW) in a conventional loop filter.

However, the sampled loop filter breaks this trade-off. In addition, since the voltage difference ( $V_X$  -  $V_{CTRL}$ ) is generally much smaller than the  $I_{CP} \times R_1$  product, this sampled loop filter significantly mitigates the spurs in a fractional-N synthesizer. However, similar to the conventional passive loop filter, the large time constant  $\tau_{LF}$ , of this sampled loop filter is a bottleneck for the proposed DSM-free SSC modulation technique.

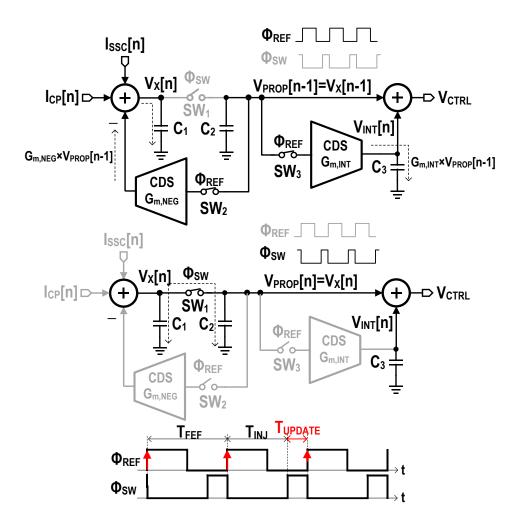

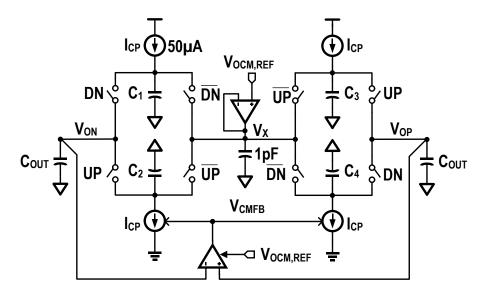

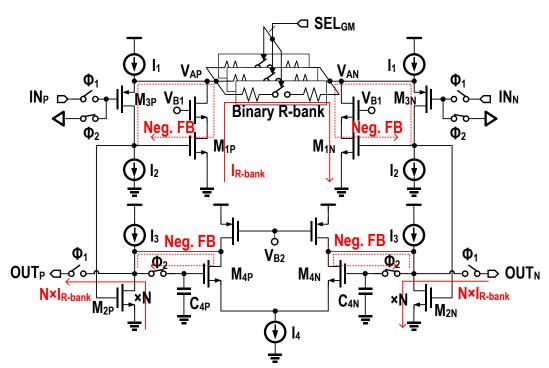

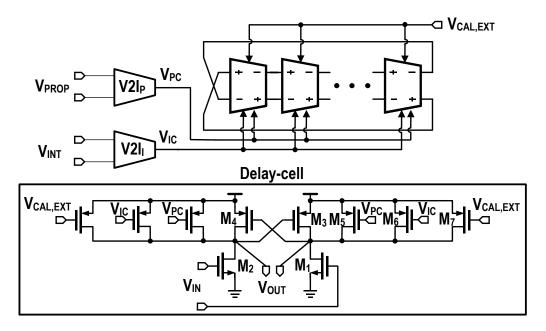

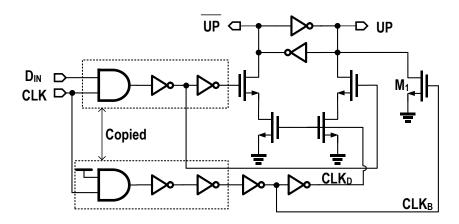

Figure 2-6: Block and timing diagram in the proposed charge-based DT-LF.

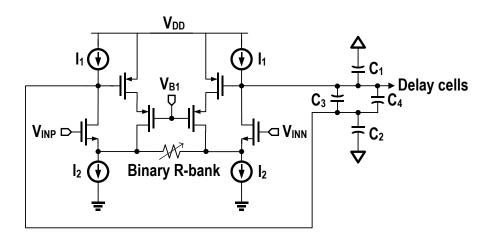

Fig. 2-6 shows the block and timing diagrams of the proposed DT-LF. It consists of two transconductors ( $G_{m,NEG}$  and  $G_{m,INT}$ ), three capacitors ( $C_1$ ,  $C_2$ , and  $C_3$ ), and three switches ( $SW_1$ ,  $SW_2$  and  $SW_3$ ). The negative feedback  $G_{m,NEG}$  is added to synthesize a stabilizing zero in the loop instead of a passive resistor  $R_1$ . This negative feedback loop also reduces the swing on the node  $V_X$ , improving the linearity of the charge pump and I-DAC<sub>SSC</sub>. In addition, the  $G_{m_INT}$  integral path makes the proposed PLL a Type-II PLL. Any PVT variations from the VCO can be absorbed to the integral path at the node  $V_{INT}$ , and the proportional path  $V_{PROP}$  is nulled if the SSC modulation is disabled. This relaxes the charge pump,  $G_{m_INEG}$ , and I-DAC<sub>SSC</sub> designs.

The proposed DT-LF operates in two phases:  $\phi_{REF}$  and  $\phi_{SW}$ . During  $\phi_{REF}$ , the currents from  $I_{SSC}[n]$ ,  $I_{CP}[n]$ , and the negative feedback current  $(G_{m\_NEG} \times V_{PROP}[n-1])$  are accumulated on the capacitor  $C_1$ . At the same time, the  $SW_3$  is closed and the current from  $G_{m\_INT}$   $(G_{m\_INT} \times V_{PROP}[n-1])$  is integrated on the capacitor  $C_3$ . During  $\phi_{SW}$ , the voltage  $V_X[n]$  on capacitor  $C_1$  is transferred to  $C_2$   $(C_1 \approx 10C_2)$ . This switched mode operation of the proposed DT-LF helps to isolate the node  $V_{CTRL}$  from the large transient glitches, which appear at node  $V_X$  during  $\phi_{REF}$ . Therefore, with the help of linear charge domain signal filtering, the proposed DT LF achieves in-loop-BW phase domain SSC modulation in analog domain.

#### 2.4 PVT-Tolerant SSC Modulation

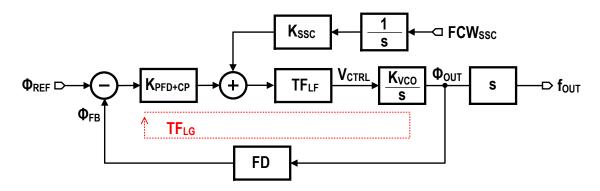

The proposed SSC architecture significantly relaxes any PVT variations in the proposed DT-LF and the VCO. This is because any PVT variations in the proposed DT-LF and the VCO are compensated by the loop gain of the PLL. This is key advantage of the proposed SSC modulation technique over the out-of-loop-BW direct SSC and two-point SSC modulations, where any change in K<sub>VCO</sub> directly appears at the output f<sub>OUT</sub>. Fig. 2-2 can be further simplified as Fig. 2-7 in order to derive a general form of the SSC modulation transfer function (TF<sub>SSC</sub>) from the SSC modulation signal FCW<sub>SSC</sub> to the output frequency f<sub>OUT</sub>. The SSC modulation transfer function TF<sub>SSC</sub> can be written as:

$$TF_{SSC} = \frac{K_{SSC} \cdot TF_{LF} \cdot \frac{K_{VCO}}{s}}{1 + TF_{LG}}$$

$$\approx \frac{K_{SSC} \cdot TF_{LF} \cdot \frac{K_{VCO}}{s}}{K_{PFD+CP} \cdot TF_{LF} \cdot \frac{K_{VCO}}{s} \cdot \frac{1}{M}} = \frac{K_{SSC}}{K_{PFD+CP} \cdot \frac{1}{M}}$$

(6)

where  $K_{SSC}$ ,  $K_{PFD+CP}$ , and  $TF_{LF}$  are the gain of the SSC block, gain of the PFD and CP, and the transfer function of the loop filter, respectively. When the open-loop gain  $TF_{LG}$  is much larger than unity, the denominator of  $TF_{SSC}$  can be approximated to the open-loop gain  $TF_{LG}$ . Since  $TF_{LF}$  and  $K_{VCO}/s$  terms are common for both the numerator and denominator in  $TF_{SSC}$ , the transfer function  $TF_{SSC}$  does not rely on both  $TF_{LF}$  and  $K_{VCO}$ . In fact, the proposed SSC modulation technique is the in-loop-bandwidth SSC modulation, and the open-loop gain  $TF_{LG}$  has to be much larger than unity inside the loop BW. Therefore, one can guarantee that the condition in (6) is satisfied in the proposed SSC architecture.

Figure 2-7: Block diagram for the SSC modulation transfer function (TFssc).

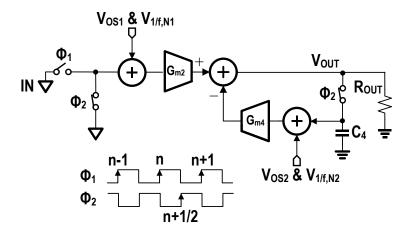

### 2.5 Correlated Double Sampling (CDS) Transconductor

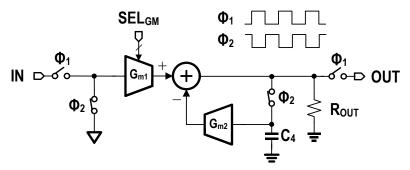

The use of active elements in the proposed DT-LF results in inevitable DC offset and 1/f noise. Therefore, the correlated double sampling (CDS) scheme in [25] is

implemented in  $G_{m,NEG}$  and  $G_{m,INT}$  blocks, as shown in Fig. 2-8. The CDS transconductor consists of the main and auxiliary transconductor  $G_{m1}$  and  $G_{m2}$  with a sampling capacitor  $C_4$ . First, the auxiliary  $G_{m2}$  forms a negative feedback to sample the DC offset and 1/f noise during  $\phi_2$ . Then the auxiliary  $G_{m2}$  loop compensates the sampled DC offset and 1/f noise during  $\phi_1$ . When the CDS scheme is enabled, a significant reduction of 1/f noise is obtained on top of the DC offset cancellation.

Figure 2-8: Correlated double sampling (CDS) scheme in the transconductors.

### 2.6 Range Limitation of the SSC Modulation

Fig. 2-9 shows the signal diagram of the proposed SSC modulation technique at the feedback path of a PLL. When the proper SSC modulation is obtained at the VCO, the output frequency  $f_{OUT}(t)$  is slowly modulated as a triangular waveform. The corresponding output phase  $\phi_{SSC,OUT}(t)$  is an integral of the triangular output frequency  $f_{OUT}(t)$ . The output phase  $\phi_{SSC,OUT}(t)$  is then divided in the frequency divider, and it results in the modulated feedback phase  $\phi_{FB}(t)$  or modulated time difference  $\Delta t_{FB}(t)$  with respect to the reference input clock  $\phi_{REF}$ .

The modulation phase  $\phi_{FB}(t)$  or modulated time difference  $\Delta t_{FB}(t)$  are slowly increasing when the modulated output frequency  $f_{OUT}(t)$  is ramping. The  $\phi_{FB}(t)$  and  $\Delta t_{FB}(t)$  will reach at the peak phase or time modulations ( $\phi_{FB\_peak}$  and  $\Delta t_{FB\_peak}$ ) at the half of the SSC modulation period ( $T_{SSC\_rate}$ ). Note that the peak phase modulation value is equivalent to the area (AREA<sub>peak</sub>) in the output frequency  $f_{OUT}$  waveform. Therefore, a

simple equation for an achievable maximum SSC modulation range  $\Delta f_{SSC\_range(\%)}$  in percent can be written as:

$$\Delta f_{\text{SSC\_range(\%)}} \le \frac{4 \times \Delta t_{\text{FB\_peak}}}{T_{\text{SSC\_rate}}} \times 100 = 400 \times \Delta t_{\text{FB\_peak}} \times f_{\text{SSC\_rate}}$$

(7)

Therefore, for a given  $f_{SSC\_rate}$ , a larger  $\Delta f_{SSC\_range(\%)}$  is achieved by increasing the maximum time modulation range  $\Delta t_{FB\_peak}$ . Note that larger  $\Delta t_{FB\_peak}$  results in larger update period  $T_{REF}$ , indicating a slower update frequency  $f_{REF}$ . This is because the peak time SSC modulation  $\Delta t_{FB\_peak}$  (or  $\phi_{FB\_peak}$ ) cannot exceed to the update period  $T_{REF}$  (or  $2\pi$ ), and this limits the maximum achievable SSC modulation range in (7). Therefore, to achieve wider spread spectrum modulation range  $\Delta f_{SSC\_range}$ , one needs to use a lower  $f_{REF}$ . Since the maximum loop BW is typically less than  $f_{REF}/10$  due to stability concerns, lowering  $f_{REF}$  reduces the maximum achievable loop BW and results in less suppression of the VCO phase noise. Therefore, there is a trade-off between the reference frequency

Figure 2-9: Signal diagram of the proposed SSC modulation at the feedback path.

$f_{REF}$  (or jitter suppression of the VCO phase noise) and the SSC modulation range  $\Delta f_{SS,range}.$

# **Chapter 3 – Modeling the Proposed SSC Architecture**

In this chapter, two linear equivalent models of the proposed SSC architecture will be derived. These derived linear models (z-domain and hybrid-domain models) will be discussed to inspect limitations of their practice. The z-domain linear model will be exploited to analyze the loop stability, such as the phase margin and root locus analysis. In addition, the hybrid-domain linear model will be used for jitter analysis, and this jitter analysis will be carried on in chapter 4.

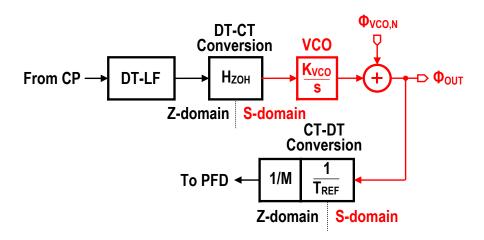

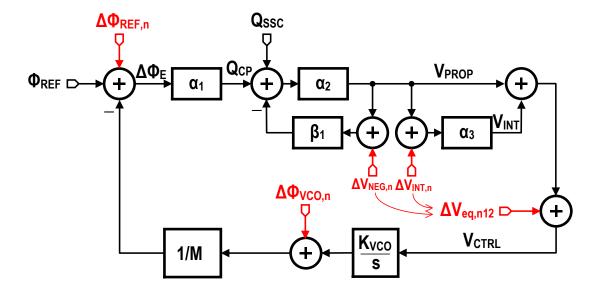

Figure 3-1: Details of the block diagram in the proposed SSC architecture.

Fig. 3-1 shows the details of the block diagram in the proposed SSC modulation architecture. Based on Fig. 2-1, there are up-sampling and down-sampling operations before and after the VCO since the output frequency of the VCO is M-time faster than the update rate  $f_{REF}$ .

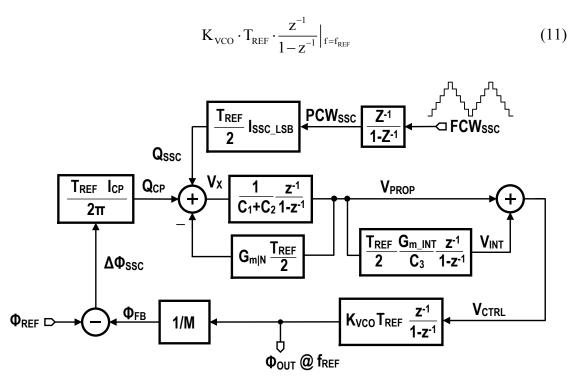

#### 3.1 z-Domain Model

To derive transfer functions of a linear PLL model in the proposed SSC architecture, one needs to analyze charge domain signal operations at the proposed charge-based DT-LF. First, the amount of charges injected into the capacitor C<sub>1</sub> are

$$Q_{CP}[n] = \frac{I_{CP}}{2\pi} \cdot T_{REF} \cdot \Delta \phi_{SSC}[n-1]$$

$$Q_{SSC}[n] = \frac{T_{REF}}{2} \cdot I_{SSC,LSB} \cdot PCW_{SSC}[n-1]$$

$$Q_{GM_{NEG}}[n] = -\frac{T_{REF}}{2} \cdot G_{m_{NEG}} \cdot V_{PROP}[n-1]$$

(8)

where  $Q_{CP}[n]$ ,  $Q_{SSC}[n]$ , and  $Q_{GM\_NET}[n]$  are updated charges from the charge pump, I-DAC<sub>SSC</sub>, and transconductor  $G_{m\_NEG}$ , respectively. The  $\Delta \varphi_{SSC}$  and  $I_{SSC,LSB}$  are the phase modulation difference at the PFD and the least-significant bit current in the I-DAC<sub>SSC</sub>, respectively. There is  $T_{REF}/2$  gain factor at  $Q_{SSC}[n]$  and  $Q_{GM\_NEG}[n]$ , since both I-DAC<sub>SSC</sub> and  $G_{m\_NEG}$  are enabled during only half of the update period  $T_{REF}$ . Therefore, the updated  $V_{PROP}(z)$  can be written as:

$$V_{PROP}(z) = \frac{I_{CP}}{2\pi} \cdot \frac{T_{REF}}{C_{12}} \cdot \frac{z^{-1}}{1 - \kappa_1 z^{-1}} \cdot \Delta \phi_{SSC}(z) + \frac{T_{REF}}{2} \cdot \frac{I_{SSC, LSB}}{C_{12}} \cdot \frac{z^{-1}}{1 - \kappa_1 z^{-1}} \cdot PCW_{SSC}(z)$$

(9)

where,  $\kappa_1$ =1– $(T_{REF}/2)\times(G_{m_NEG}/C_{12})$  and  $C_{12}$ = $C_1$ + $C_2$ , respectively. Due to the local feedback  $G_{m_NEG}$ , the position of the pole at DC is modulated to  $\kappa_1$ , and this modulated pole at  $\kappa_1$  can be cancelled when  $(T_{REF}/2)\times(G_{m_NEG}/C_{12})$ =1. Moreover, the pole position  $\kappa_1$  is a function of the ratio between the  $G_{m_NEG}$  and  $C_{12}$ , indicating that design scaling for both power and area can be achieved without disturbing the transfer function.

The transfer function of the proportional and integral dual-path loop filter can be written as:

$$V_{CTRL}(z) = \frac{1 - \kappa_2 z^{-1}}{1 - z^{-1}} \cdot V_{PROP}(z)$$

(10)

where,  $\kappa_2=1-(T_{REF}/2)\times(G_{m_{INT}}/C_3)$ . This dual-path loop filter establishes one pole at DC and one zero at  $\kappa_2$ , and a type-II PLL is achieved. Note that the position of the additional

zero  $\kappa_2$  is also a function of the ratio between the  $G_{m\_INT}$  and  $C_3$ .

As shown in Fig. 3-1, the VCO update rate is M-times faster than the reference frequency  $f_{REF}$ . However, since  $V_{CTRL}$  is only updated in every  $f_{REF}$ , one can derive the linear z-domain transfer function for the VCO as:

Figure 3-2: z-domain model of the proposed PLL.

Therefore, the block diagram of the z-domain linear PLL model for the proposed SSC architecture can be redrawn as in Fig. 3-2. This simplified discrete-time z-domain PLL model is sufficient to analyze PLL loop dynamics such as the loop gain K<sub>LG</sub>, phase margin PM, and pole-zero locations. Note that although the Bode analysis originated with continuous-time system which can be described in s-domain, interpretations of the z-domain Bode plot for a PLL are accurate enough to give good estimations [26].

The transfer function for the open-loop gain  $TF_{LG}(z)$  and the SSC modulation  $TF_{SSC}(z)$  are written as:

$$TF_{LG}(z) = \frac{T_{REF}}{2\pi} \cdot \frac{I_{CP}}{C_{12}} \cdot K_{VCO} \cdot T_{REF} \cdot \left(\frac{z^{-1}}{1 - z^{-1}}\right)^{2} \cdot \frac{1 - \kappa_{2}z^{-1}}{1 - \kappa_{1}z^{-1}}.$$

(12)

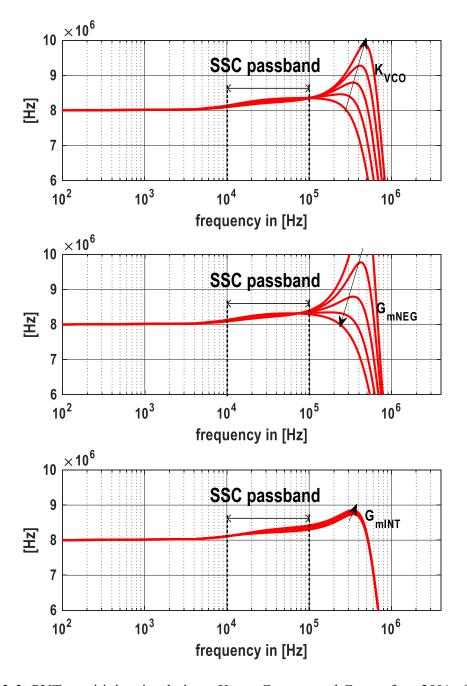

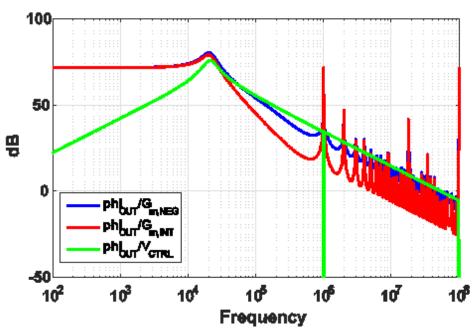

Figure 3-3: PVT sensitivity simulations:  $K_{VCO}$ ,  $G_{m\_NEG}$ , and  $G_{m\_INT}$  for  $\pm 20\%$  of the nominal value for  $f_{REF}$ =8MHz.

$$TF_{SSC}(z) = \frac{f_{OUT}}{FCW_{SSC}} = \frac{K_{VCO}}{2\pi} \cdot \frac{V_{CTRL}}{FCW_{SSC}}(z) \Rightarrow \frac{I_{SSC,LSB}/2}{I_{CP}/M} \cdot f_{REF}$$

(13)

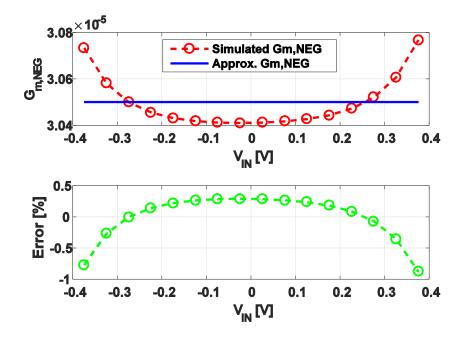

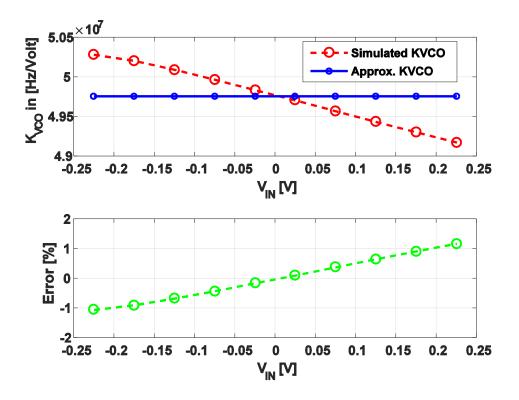

From (13), when the frequency is lower than the loop BW,  $TF_{SSC}(z)$  is a function of  $I_{SSC,LSB}/I_{CP}$ , and the gain of the SSC modulation is proportional to  $f_{REF}$ . This indicates that the magnitude frequency response of  $TF_{SSC}$  below the loop BW does not depend on either design parameters of the proposed DT-LF or  $K_{VCO}$ . Fig. 3-3 shows the PVT sensitivity simulation results due to  $K_{VCO}$ ,  $G_{m\_NEG}$ , and  $G_{m\_INT}$  variations which is  $\pm 20\%$  of the nominal value. Because all three variables ( $K_{VCO}$ ,  $G_{m\_NEG}$ , and  $G_{m\_INT}$ ) modulate the loop gain  $K_{LG}$  and the damping ratio of the loop, the magnitude frequency response of  $TF_{SSC}$  around the loop BW is varied due to their changes. However, when a frequency band is relatively smaller than the loop BW (less than 10kHz in Fig. 3-3), a fixed and consistent  $TF_{SSC}$  magnitude gain is observed. Therefore, if one can push the loop BW much higher than the SSC modulation pass band, the PVT insensitive modulation gain in  $TF_{SSC}$  can be achieved. This limitation is generally true for all conventional in-loop-BW SSC techniques.

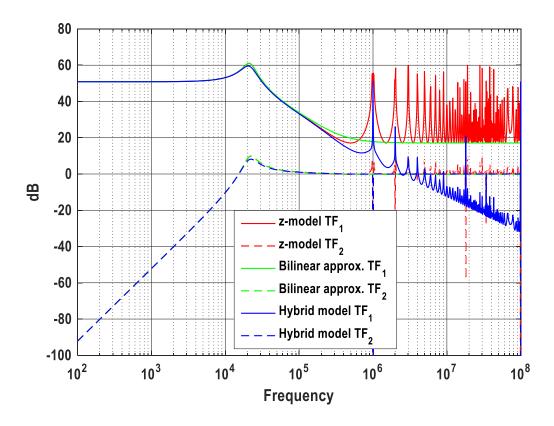

## 3.2 Hybrid-Domain Model

Since the derived z-domain PLL model in Fig. 3-2 is valid up to  $f_{REF}/2$ , this PLL model should not be sufficient for jitter estimations. It is because the output phase noise is generally integrated up to a few hundred MHz to calculate the integrated phase jitter. There are several advanced modeling techniques [27]-[28] to overcome this limitation. The work in [27] up-samples the control voltage  $V_{CTRL}$  from  $f_{REF}$  to  $f_{OUT}$  at a VCO, and down-samples the output phase  $\phi_{OUT}$  to the feedback phase  $\phi_{FB}$  of the PFD as did in Fig. 3-1, and this modeling technique supports the phase noise transfer function up to  $f_{OUT}/2$ . In [28], the CT-to-DT and DT-to-CT conversion steps are added before and after a VCO, and the linear model of the VCO is built in s-domain. This hybrid-domain modeling technique provides the unbounded modeling range with the proposed DT-LF. In addition, jitter calculations are generally done in a numerical tool, and evaluating frequency

responses of this hybrid-domain PLL model is easily performed using a numerical tool. Therefore, the simpler z-domain PLL model in (12) is exploited for the stability and root locus analysis, while this extensive hybrid-domain PLL model is necessary for jitter calculations.

Fig. 3-4 shows the DT-to-CT and CT-to-DT conversions around the VCO. The zero-order-hold block is well-known as the DT-to-CT conversion, and its transfer function  $H_{\text{DT-CT}}$  can be approximated as:

$$\left|H_{\text{DT-CT}}(s)\right| = \left|T_{\text{REF}} \cdot e^{-j\omega T_{\text{REF}}/2} \cdot \text{sinc}\left(\omega T_{\text{REF}} / 2\right)\right| \underset{\omega T_{\text{REF}} << 1}{\Longrightarrow} T_{\text{REF}}$$

Figure 3-4: DT-to-CT and CT-to-DT conversions around the VCO.

Similarly, the CT-to-DT conversion can be modeled using an impulse train sampling, and its transfer function  $H_{CT-DT}$  can be approximated as:

$$\left| H_{\text{CT-DT}}(s) \right| = \left| \frac{1}{T_{\text{REF}}} \sum_{n=-\infty}^{\infty} \delta(f - nf_{\text{REF}}) \right| \underset{\omega T_{\text{REF}} << 1}{\Longrightarrow} \frac{1}{T_{\text{REF}}}$$

Finally, Fig. 3-5 shows the final hybrid-domain PLL model for the proposed SSC architecture. The CT-to-DT conversion block can be moved to in front of the phase detector because the phase detector also samples the input reference clock phase  $\phi_{REF}$  and subtracts it from the sampled feedback phase  $\phi_{FB}$ . Based on this hybrid-domain PLL

model, four major transfer functions are written as:

$$TF_{LG}(z,s) = \frac{T_{REF}}{2\pi} \cdot \frac{I_{CP}}{C_{12}} \cdot \frac{K_{VCO}}{s} \cdot \frac{1}{M} \cdot \left(\frac{z^{-1}}{1-z^{-1}}\right) \cdot \frac{1-\kappa_2 z^{-1}}{1-\kappa_1 z^{-1}}$$

(14)

$$TF_{1}(z,s) = \frac{\phi_{OUT}}{\phi_{REE}} = \frac{\frac{T_{REF}}{2\pi} \cdot \frac{I_{CP}}{C_{12}} \cdot \frac{K_{VCO}}{s} \cdot \left(\frac{z^{-1}}{1-z^{-1}}\right) \cdot \frac{1-\kappa_{2}z^{-1}}{1-\kappa_{1}z^{-1}}}{1+TF_{LG}(z,s)}$$

(15)

$$TF_2(z,s) = \frac{\phi_{OUT}}{\phi_{VCO}} = \frac{1}{1 + TF_{LG}(z,s)}$$

(16)

$$TF_{SSC}(z,s) \Rightarrow \frac{I_{SSC,LSB}/2}{I_{CP}/M} \cdot f_{REF}$$

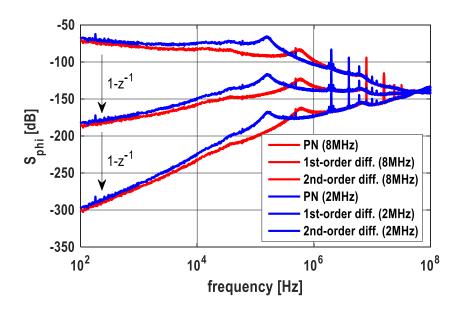

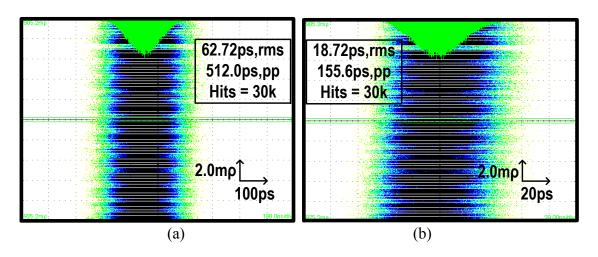

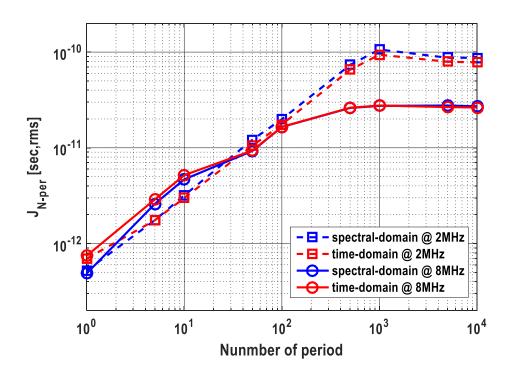

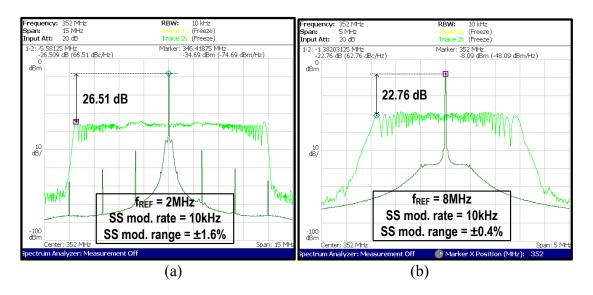

(17)