#### AN ABSTRACT OF THE THESIS OF

Nam Hwang for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and Computer</u> Engineering presented on <u>November 29</u>, 1993.

Title: Physical Mechanisms, Device Models, and Lifetime Projections of Hot-Carrier

Effects in CMOS Transistors

Redacted for Privacy

Abstract approved:

Leonard Forbes

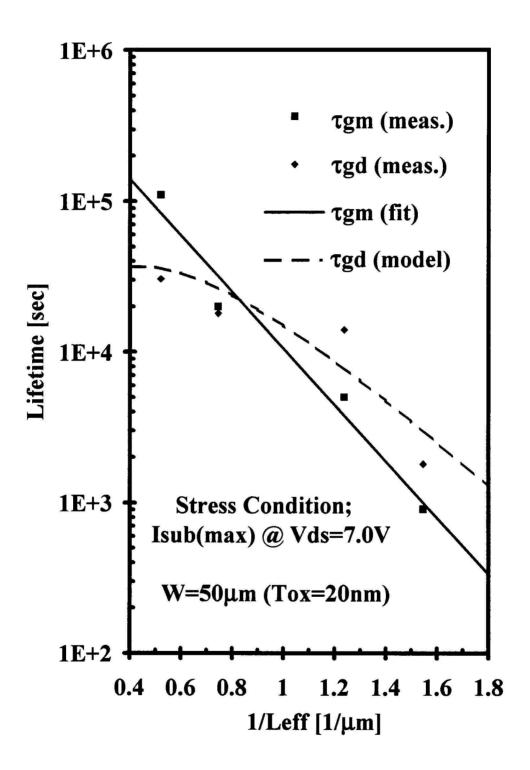

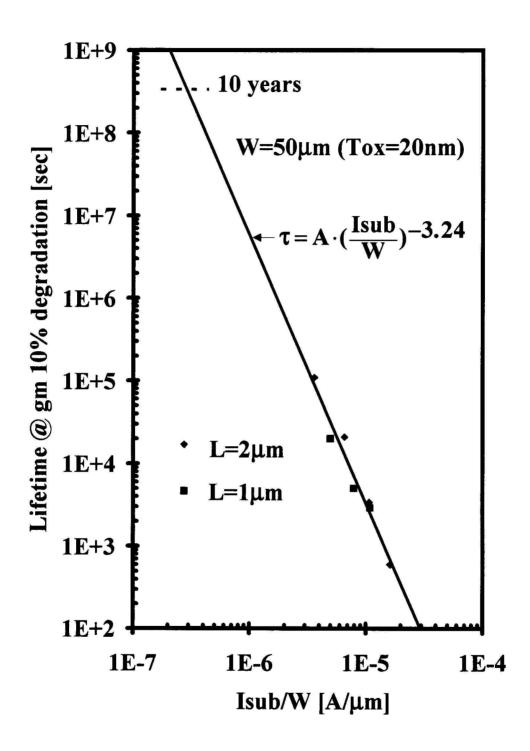

The purpose of this work is to investigate the theoretical and practical aspects of reliability analysis including physical mechanisms, parameter mismatches, lifetime projections, circuit analysis, and reliability improvement techniques. A spectral analysis of oxide trap energy distributions after hot-electron injection in LDD n-MOSFET's at room temperature and above has been performed by using both electric field stimulated (or tunneling) and thermal emission methods. It has been found that the trapping mechanisms of both deep levels (2.4eV) at room temperature and shallow levels (0.9eV) below room temperature are similar. Two new reliability models for analog IC designs and reliability projections have been proposed by applying channel mobility reduction due to hot carrier induced interface states. One of the proposed reliability models is a drain conductance (gd) degradation model which is a function of the transconductance (gm) degradation in the linear region which is then used to determine parameter mismatches in analog IC designs. This is then applicable to lifetime predictions of analog circuits. It has been found that the gd degradation lifetime (i.e., \tau gd) is less dependent on Leff than tgm, and is shorter than tgm when Leff is longer than 1.2μm. The other model is the hot-carrier induced series (drain) resistance (ΔRd) enhancement model for reliability projections of analog IC designs. The proposed  $\Delta Rd$  model, based on the increase of the hot-carrier induced interface trapped charge ( $\Delta Nit$ ), shows a good agreement between the increase of the series resistance in the drain region and the degradation of device characteristics. A specific example of a reliability projection has been given to show that the  $\Delta Rd$  model (one parameter) is much simpler and more applicable in analog IC designs rather than the commercial reliability simulator (i.e., BERT) which requires a set of stressed device parameter files (6 parameters). In order to demonstrate reliability projections using the proposed reliability models, a conventional CMOS differential amplifier has been employed as an example of analog and mixed-mode IC designs.

# Physical Mechanisms, Device Models, and Lifetime Projections of Hot-Carrier Effects in CMOS Transistors

by

Nam Hwang

**A THESIS**

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Completed November 29, 1993

Commencement June 1994

| Redacted for Privacy                                                                      |

|-------------------------------------------------------------------------------------------|

| Professor of Electrical and Computer Engineering in charge of major  Redacted for Privacy |

| Head of Department of Electrical and Computer Engineering                                 |

| Redacted for Privacy                                                                      |

| Dean of Graduate School                                                                   |

|                                                                                           |

Date thesis is presented November 29, 1993

Typed for Nam Hwang by Seunghee Hong and Nam Hwang

<sup>c</sup> Copyright by Nam Hwang November 29, 1993

All Rights Reserved

### **ACKNOWLEDGMENTS**

First of all, I would like to express my gratitude to my advisor, Dr. Leonard Forbes, who has provided me with generous support, constant encouragement, and invaluable advice throughout this study. I would also like to thank Drs. John Arthur, Ben Lee, Jack Kenney, and Michael Quinn for serving on my Ph.D. committee and for their guidance, inspiration, and support during my academic career at Oregon State University. The giving of their time and advice were instrumental to my success. In addition, my very special thanks to Mr. Ikuo Kurachi, OKI Electric Co. Ltd., Tokyo, Japan, for helping me to get started with this study and encouraging my research work.

Finally, I must thank my wife, Seunghee, who supported me with unsparing love and encouragement during this study, and typed the "millions" of data entries enabling me to make the plots of charge pumping currents. Without her constant support, this study could not have been accomplished. I am also thankful to my son, Jinsoo, who always cheers and sparkles me up with unexpected surprises.

# TABLE OF CONTENTS

|    |      |                                                         | <u>Page</u> |

|----|------|---------------------------------------------------------|-------------|

| 1. | INTE | RODUCTION                                               | 1           |

|    | 1.1  | Literature Review                                       | 2           |

|    | 1.2  | Technology Trends                                       | 6           |

|    | 1.3  | Overview of Reliability Analysis                        | 11          |

|    | 1.4  | Motivation and Objectives                               | 12          |

| 2. | нот  | -CARRIER EFFECTS ON DEVICES                             | 16          |

|    | 2.1  | Introduction                                            | 16          |

|    | 2.2  | Hot-Carrier Induced Device Degradation                  | 20          |

|    | 2.3  | Substrate Current Model                                 | 25          |

|    | 2.4  | Summary                                                 | 30          |

| 3. | PHY  | SICAL MECHANISMS OF TRAPS AND SURFACE STATES            | 34          |

|    | 3.1  | Introduction                                            | 34          |

|    | 3.2  | Thermal Re-Emission                                     | 35          |

|    | 3.3  | Tunneling Emission                                      | 37          |

|    | 3.4  | Electric Field Stimulated Emission                      | 37          |

|    | 3.5  | Charge Pumping Current Measurements                     | 40          |

|    | 3.6  | Summary                                                 | 48          |

| 4. | LIFE | ETIME PROJECTIONS                                       | 51          |

|    | 4.1  | Introduction                                            | 51          |

|    | 4.2  | Accelerated Lifetime Test                               | 53          |

|    | 4.3  | Lifetime Projections                                    | 59          |

|    | 4.4  | Hot-Carrier Induced Degradation of SPICE MOS3 Parameter | rs 68       |

|    | 45   | Summary                                                 | 81          |

# TABLE OF CONTENTS (Continued)

|      |       |             |                                  | <u>Page</u> |

|------|-------|-------------|----------------------------------|-------------|

| 5.   | PHY   | SICAL MOD   | EL OF DRAIN CONDUCTANCE          |             |

|      | DEG   | RADATION    |                                  | 82          |

|      | 5.1   | Introductio | n                                | 82          |

|      | 5.2   | Model Deri  | vations                          | 83          |

|      | 5.3   | Experiment  | tal and Simulation Results       | 91          |

|      | 5.4   | Summary     |                                  | 103         |

| 6.   | SERI  | ES RESISTA  | ANCE ENHANCEMENT MODEL           | 104         |

|      | 6.1   | Introductio | n                                | 104         |

|      | 6.2   | Derivation  | of the ΔRd Model                 | 107         |

|      | 6.3   | Experimen   | tal and Simulation Results       | 111         |

|      | 6.4   | Summary     |                                  | 122         |

| 7.   | CON   | CLUSIONS    |                                  | 125         |

| BIBI | LIOGR | APHY        |                                  | 128         |

| APP  | ENDIC | ES          |                                  |             |

|      | APP   | ENDIX A:    | COMPOSITE nMOSFET                | 140         |

|      | APP   | ENDIX B:    | HOTPEX: HOT-CARRIER ANALYSIS AND |             |

|      |       |             | PARAMETER EXTRACTION PROGRAM     | 156         |

# LIST OF FIGURES

| <b>Figure</b> |                                                                | <u>Page</u> |

|---------------|----------------------------------------------------------------|-------------|

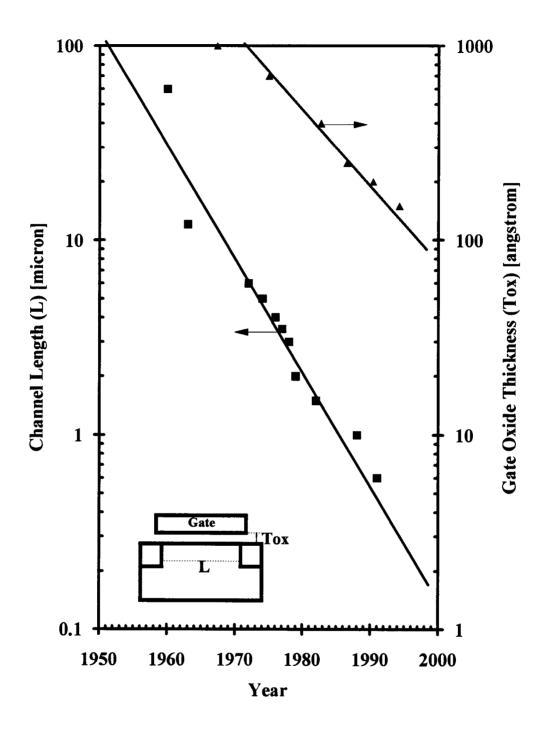

| 1-1           | CMOS technology trend.                                         | 7           |

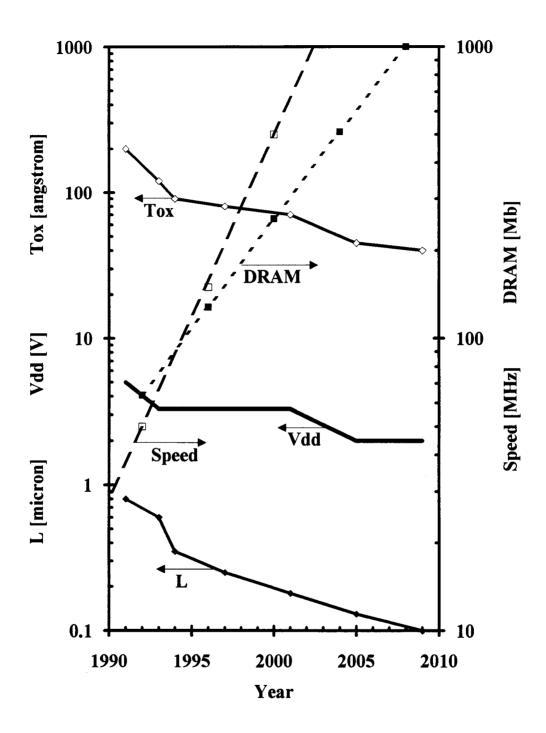

| 1-2           | Projection of CMOS technology.                                 | 10          |

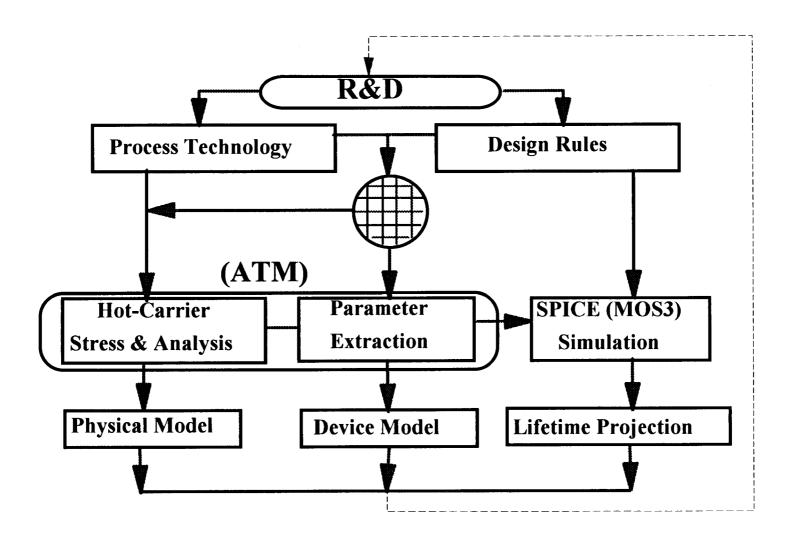

| 1-3           | Structure of reliability analysis of hot-carrier effects.      | 13          |

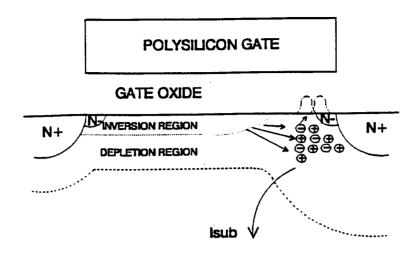

| 2-1           | Schematic diagram of hot-carrier mechanisms.                   | 17          |

| 2-2           | Hot-carrier induced currents of an nMOSFET in terms of         |             |

|               | drain, substrate, and gate currents.                           | 21          |

| 2-3           | Substrate currents and threshold voltage shifts under hot-     |             |

|               | carrier injection as a function of channel lengths.            | 23          |

| 2-4           | Ids-Vgs characteristic curves of an nMOSFET device under       |             |

|               | hot-carrier injection.                                         | 24          |

| 2-5           | Ids-Vds characteristic curves of an nMOSFET device under       |             |

|               | hot-carrier injection.                                         | 26          |

| 2-6           | Saturation drain voltage (Vdsat) measurements.                 | 29          |

| 2-7           | Measured (marks) and simulated (lines) substrate currents.     | 32          |

| 3-1           | The Arrhenius plot of the drain-to-source current recovery     |             |

|               | mechanism; thermal emission of trapped electrons.              | 36          |

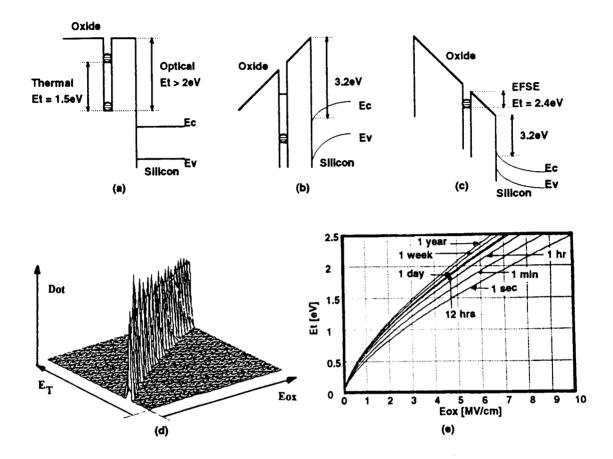

| 3-2           | Tunneling model for re-emission of trapped electrons at        |             |

|               | different gate bias conditions: (a) thermal recovery with zero |             |

|               | or negative gate voltages, (b) the trapped electrons will not  |             |

|               | recover with positive gate voltages, (c) tunneling (EFSE)      |             |

|               | from ground state at large negative gate voltages at room      |             |

|               | temperature, (d) trap energy distribution from Price-Sah       |             |

|               | emission equations (not to scale), and                         | 38          |

| <b>Figure</b> |                                                            | <b>Page</b> |

|---------------|------------------------------------------------------------|-------------|

| 3-2           | (e) the projection of oxide trap density as a function of  |             |

|               | applied oxide electric field and trap energy level.        | 38          |

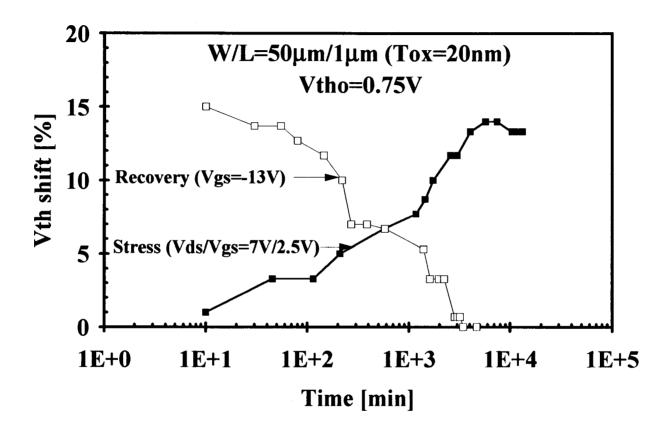

| 3-3           | Recovery of the threshold voltage under negative gate      |             |

|               | voltage.                                                   | 41          |

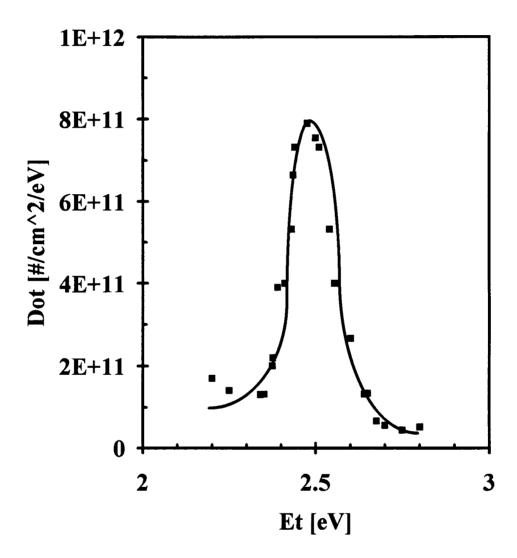

| 3-4           | The density of charged oxide electron traps versus trap    |             |

|               | energy.                                                    | 42          |

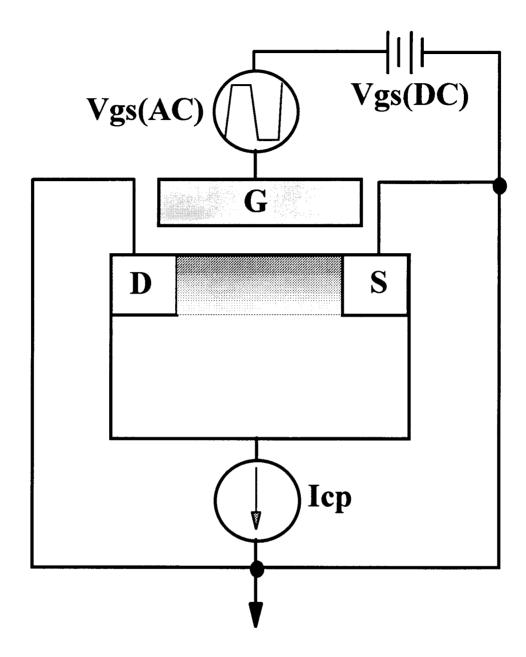

| 3-5           | Schematic diagram of charge-pumping current measurement    |             |

|               | set-up.                                                    | 43          |

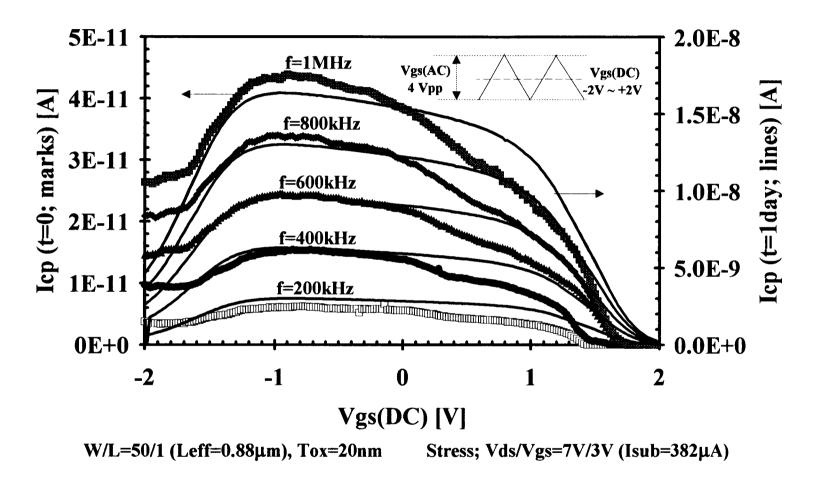

| 3-6           | Charge pumping current measurements as a function of gate  |             |

|               | voltages with different frequencies.                       | 46          |

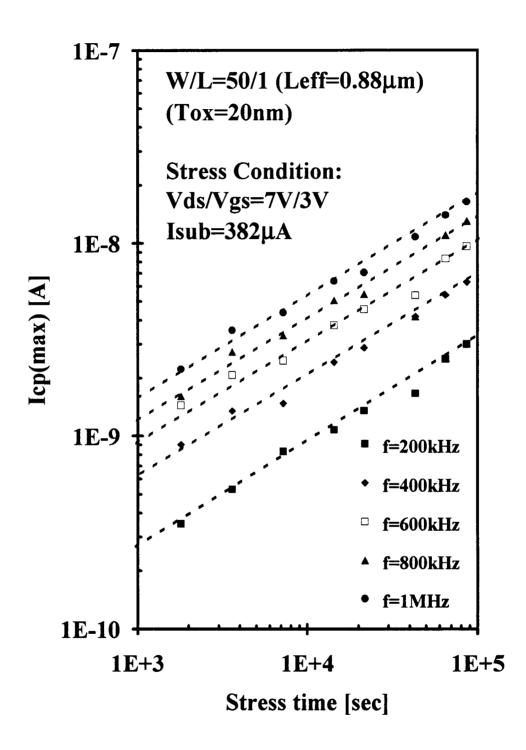

| 3-7           | The increase of Icp(max) under hot-carrier stress.         | 47          |

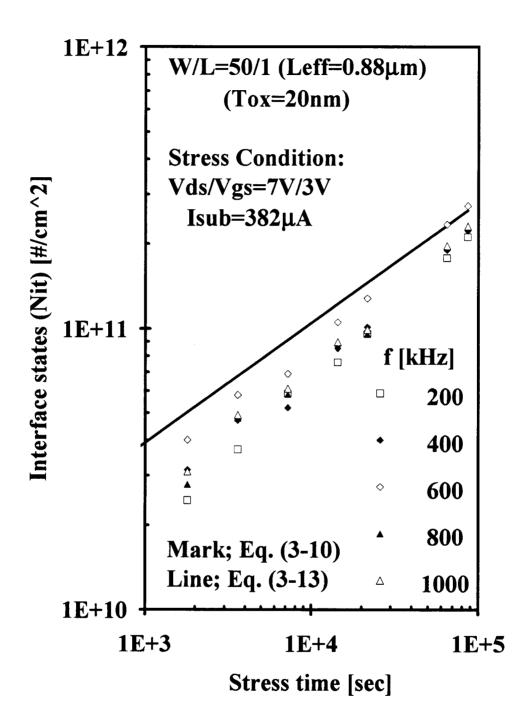

| 3-8           | The increase of interface states with stress time.         | 49          |

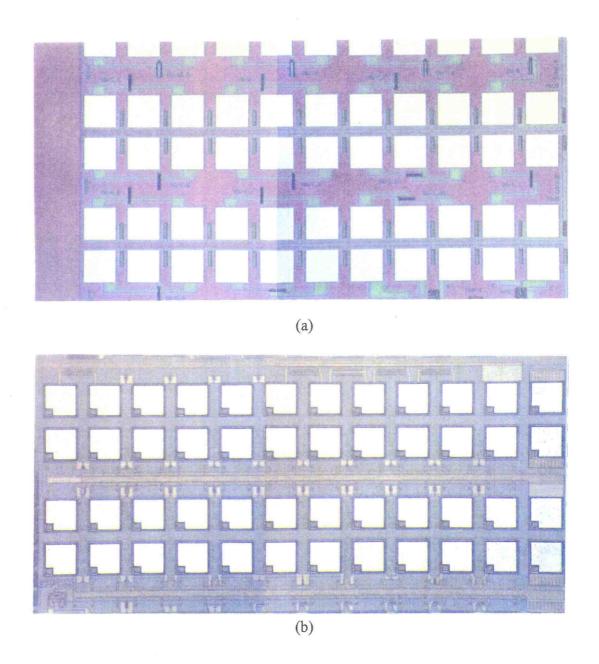

| 4-1           | Photomicrograph of the test device patterns for (a) MOSIS- |             |

|               | HP-CMOS34 and (b) MOSIS-HP-CMOS26B.                        | 54          |

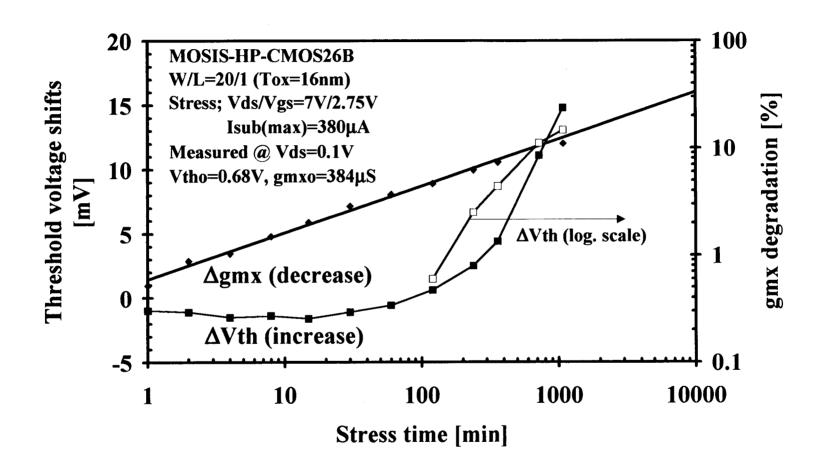

| 4-2           | $\Delta V$ th and $\Delta g$ mx under hot-carrier stress.  | 56          |

| 4-3           | Ids degradation under hot-carrier stress.                  | 57          |

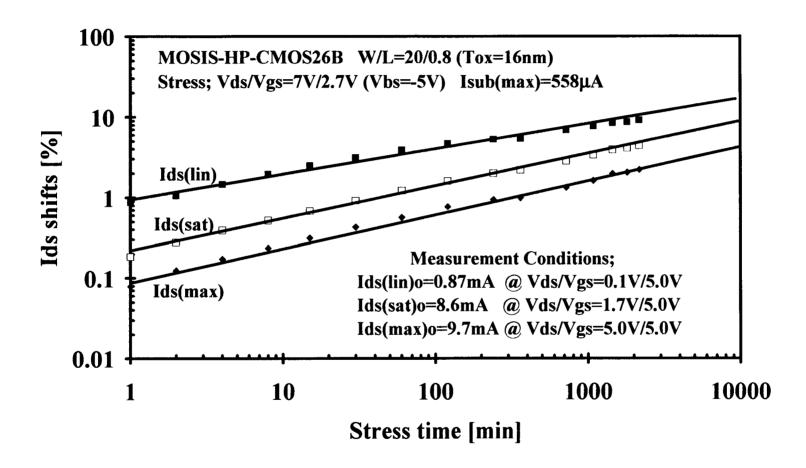

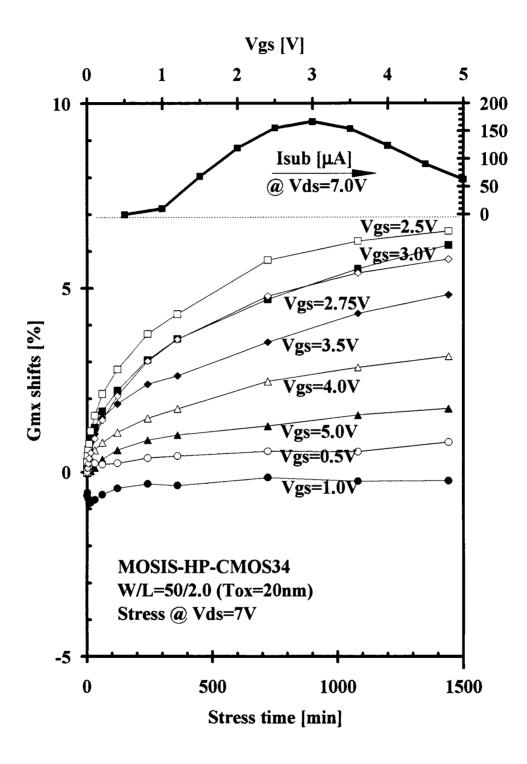

| 4-4           | Ids degradation in terms of gmx degradation.               | 58          |

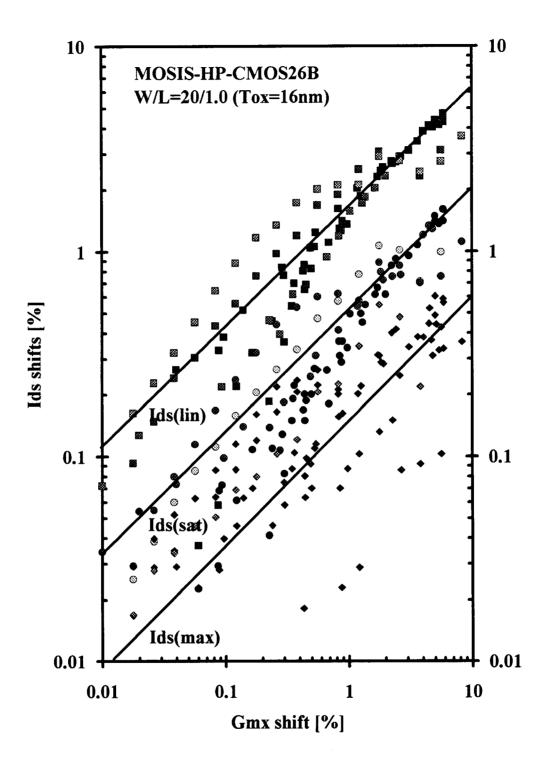

| 4-5           | gmx degradation trend during accelerated lifetime tests.   | 60          |

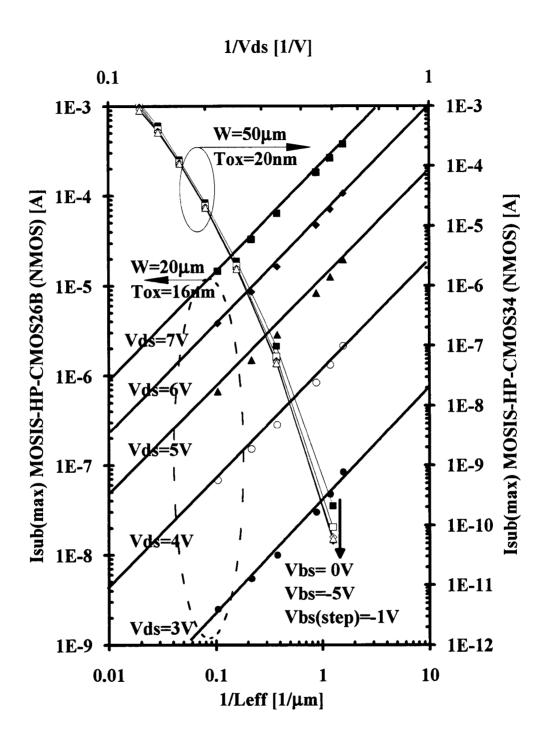

| 4-6           | Isub(max) as a function of 1/Leff, 1/Vds, and Vbs.         | 61          |

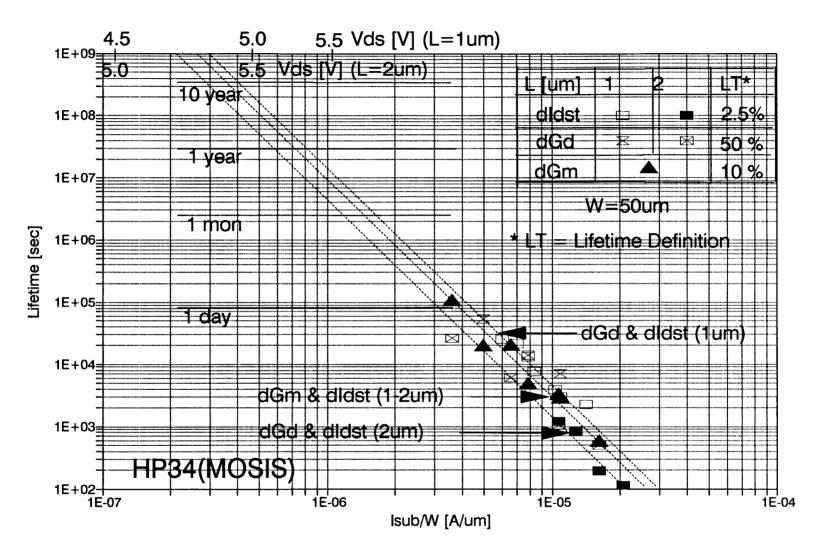

| 4-7           | Lifetime projections on MOSIS-HP-CMOS34.                   | 64          |

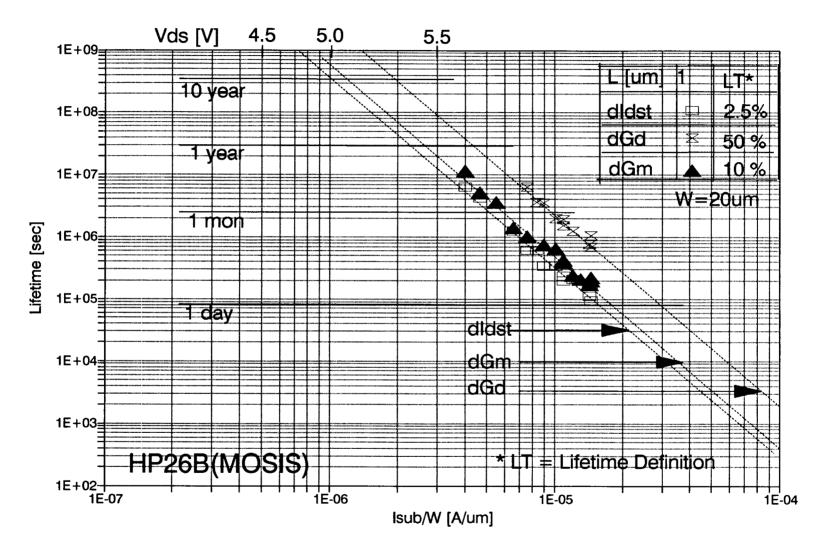

| 4-8           | Lifetime projections on MOSIS-HP-CMOS26B.                  | 65          |

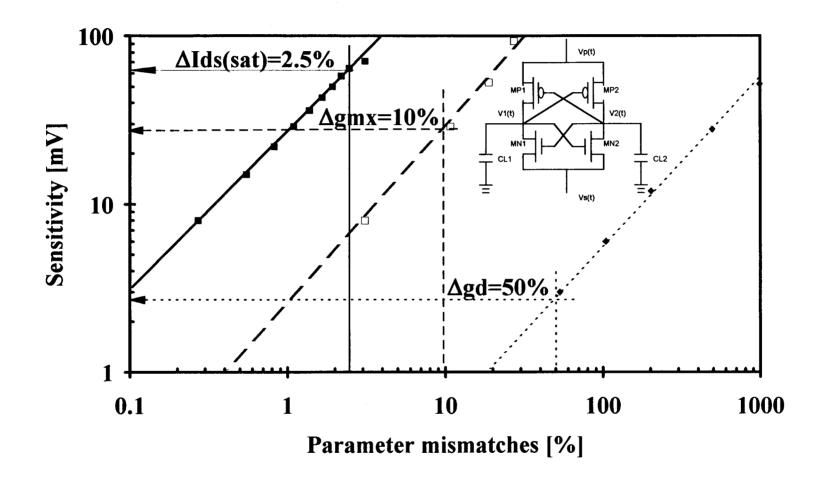

| 4-9           | Parameter mismatches of a CMOS sense amplifier for         |             |

|               | reliability projections.                                   | 67          |

| <b>Figure</b> |                                                                           | <u>Page</u> |

|---------------|---------------------------------------------------------------------------|-------------|

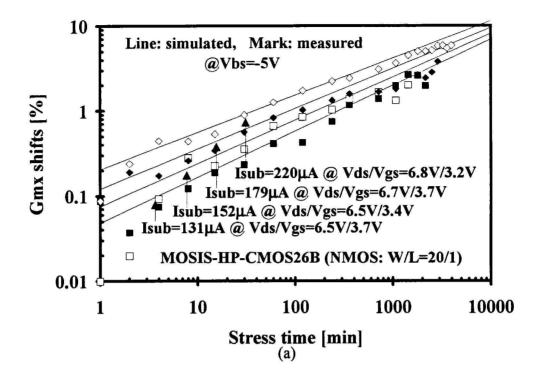

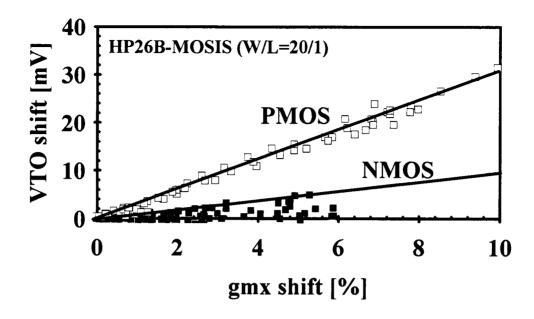

| 4-10          | Empirical Δgmx model for MOSIS-HP-CMOS26B: (a)                            |             |

|               | NMOS and (b) PMOS.                                                        | 69          |

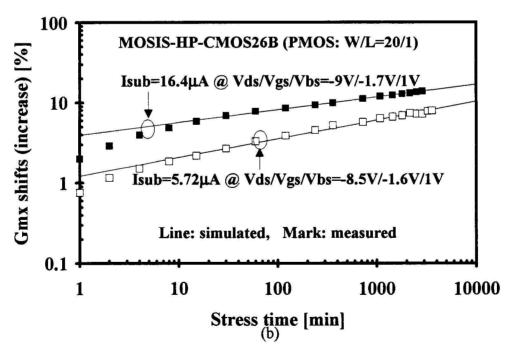

| 4-11          | Schematic diagram of SPICE MOS3 parameter extraction.                     | 72          |

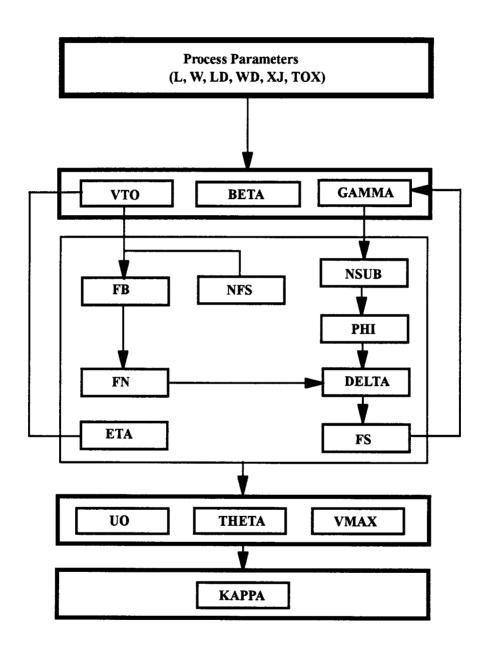

| 4-12          | VTO shifts as a function of gmx degradation.                              | 74          |

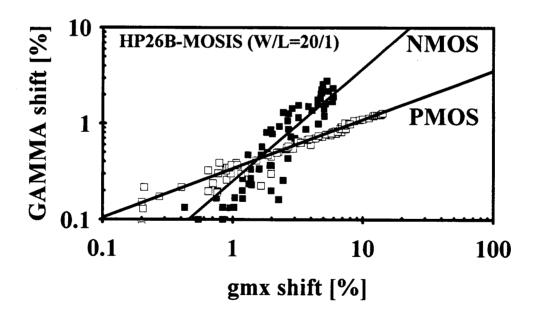

| 4-13          | GAMMA shifts as a function of gmx degradation.                            | 74          |

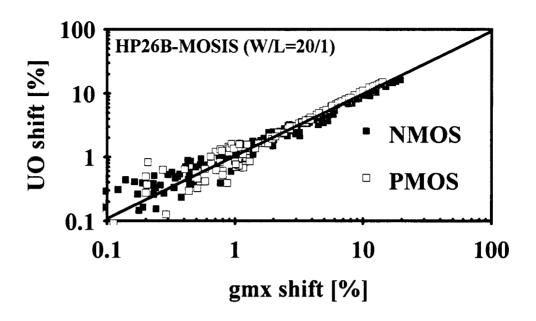

| 4-14          | UO shifts as a function of gmx degradation.                               | 76          |

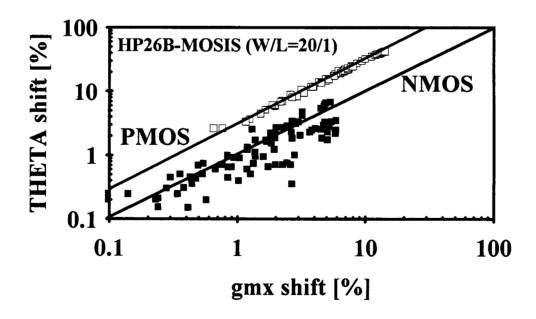

| 4-15          | THETA shifts as a function of gmx degradation.                            | 76          |

| 4-16          | VMAX shifts as a function of gmx degradation.                             | 77          |

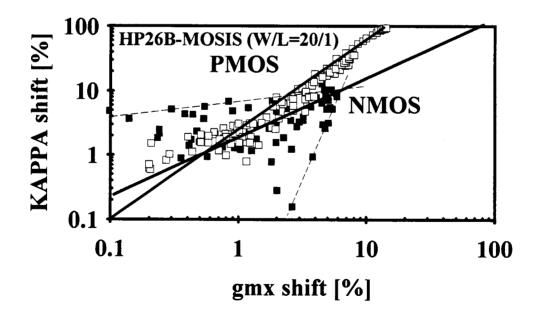

| 4-17          | KAPPA shifts as a function of gmx degradation.                            | 77          |

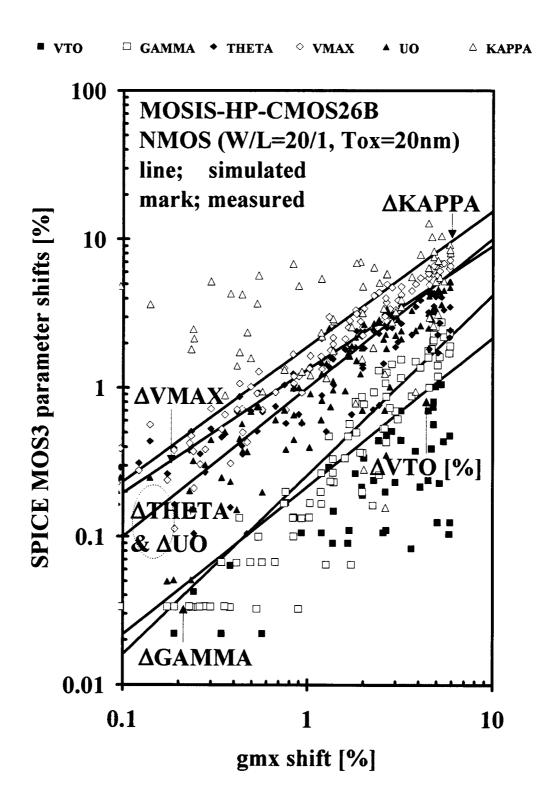

| 4-18          | Hot-carrier induced degradation of SPICE MOS3 (NMOS)                      |             |

|               | parameters as a function of gmx shifts.                                   | 80          |

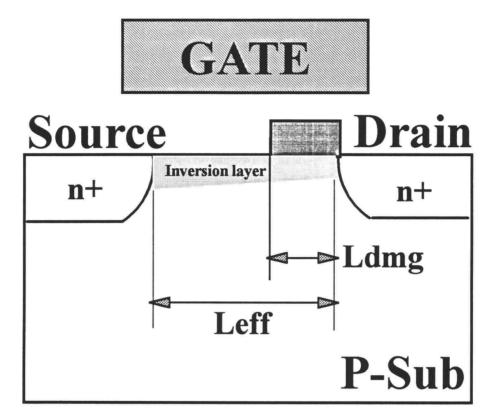

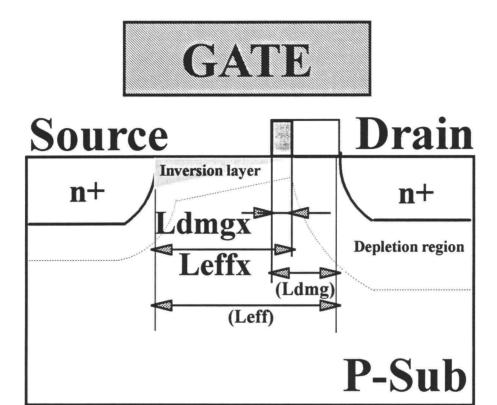

| 5-1           | Schematic cross-section of the damaged MOSFET in linear                   |             |

|               | region.                                                                   | 84          |

| 5-2           | Schematic cross-section of the damaged MOSFET in                          |             |

|               | saturation region.                                                        | 88          |

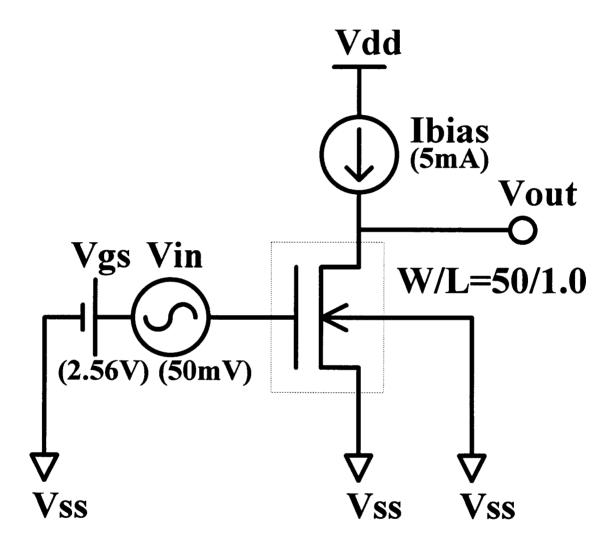

| 5-3           | Circuit diagram of a single nMOSFET amplifier.                            | 92          |

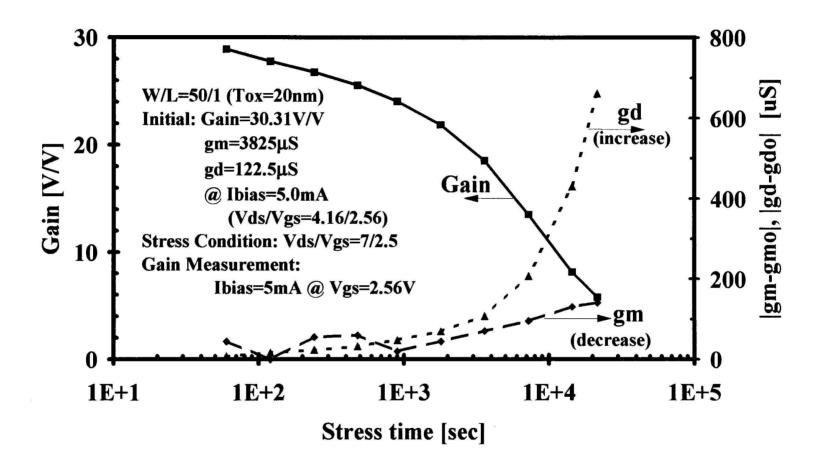

| 5-4           | Gain degradation of a single nMOSFET amplifier as a                       |             |

|               | function of stress time.                                                  | 93          |

| 5-5           | Relationship between $\Delta gm/gm$ and $\Delta gd/gdo$ for L=1.0 $\mu m$ |             |

|               | and 2.0µm.                                                                | 95          |

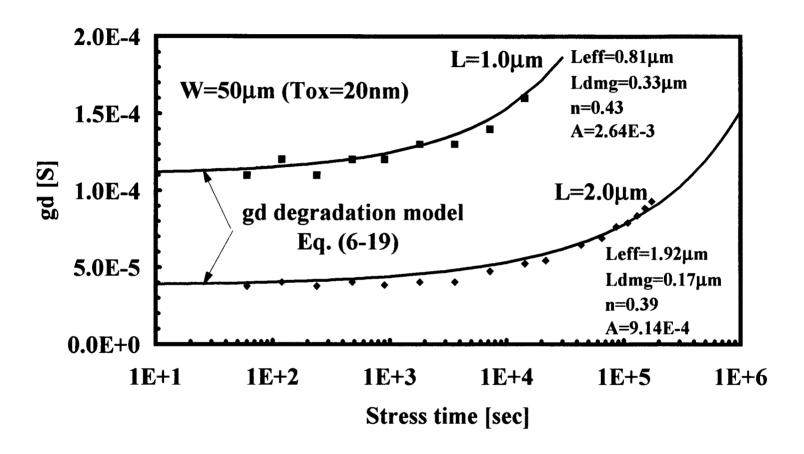

| 5-6           | Comparison between drain conductance model and                            |             |

|               | experimental data as a function of stress time.                           | 96          |

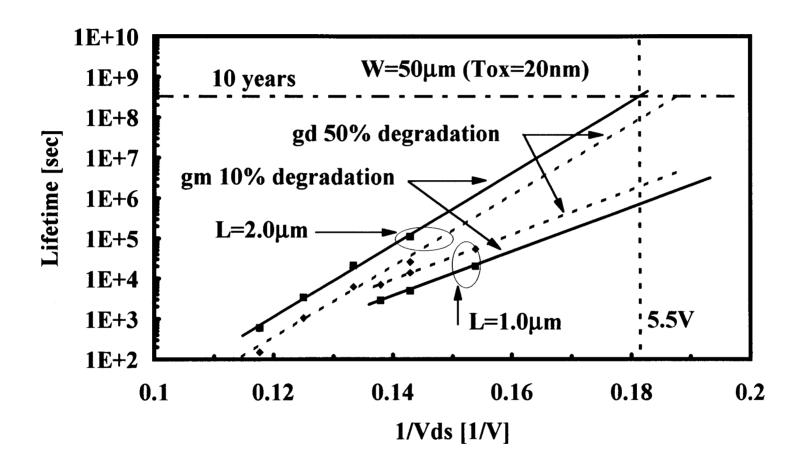

| 5-7           | Lifetime dependence on 1/Vds.                                             | 98          |

| <u>Figure</u> |                                                                    | <b>Page</b> |

|---------------|--------------------------------------------------------------------|-------------|

| 5-8           | Channel length dependence of $\tau gm$ and $\tau gd$ .             | 99          |

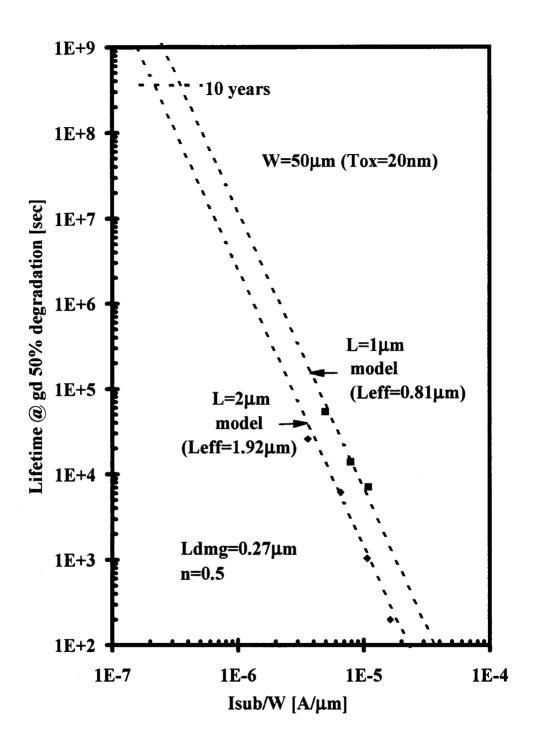

| 5-9           | Lifetime projection of gm degradation.                             | 101         |

| 5-10          | Lifetime projection of gd degradation.                             | 102         |

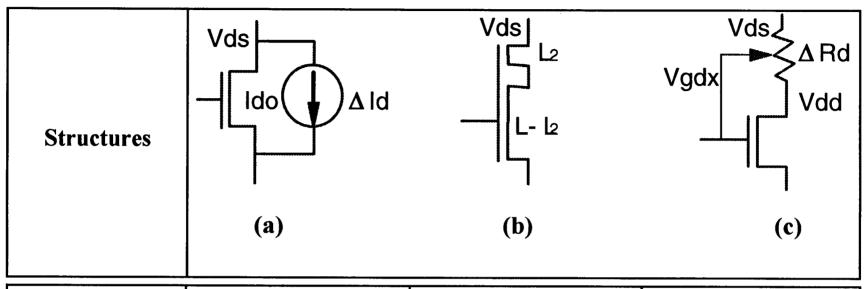

| 6-1           | Structures of reliability models and the proposed hot-carrier      |             |

|               | induced series (drain) resistance (ΔRd) enhancement model.         | 105         |

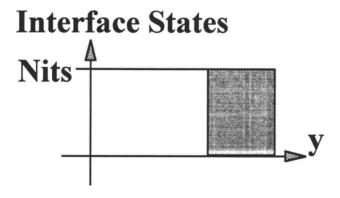

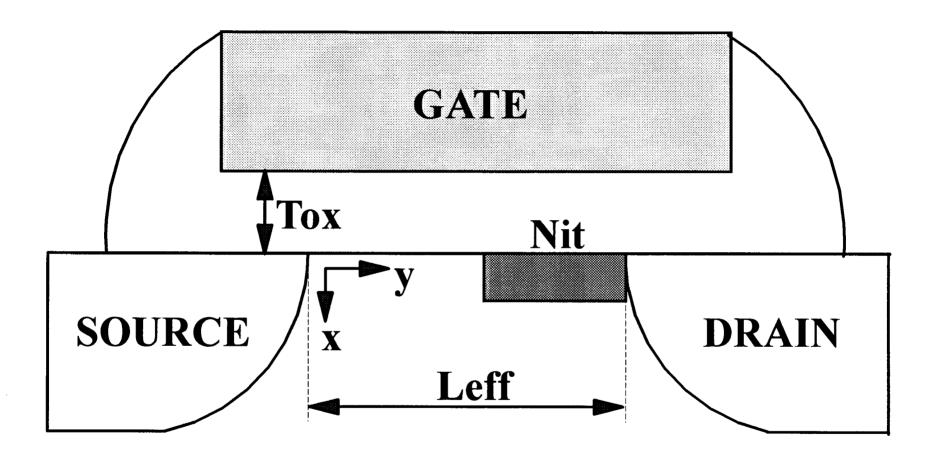

| 6-2           | Schematic illustration of the device structure for the $\Delta Rd$ |             |

|               | model derivation and the hot-carrier induced interface trap        |             |

|               | charge.                                                            | 108         |

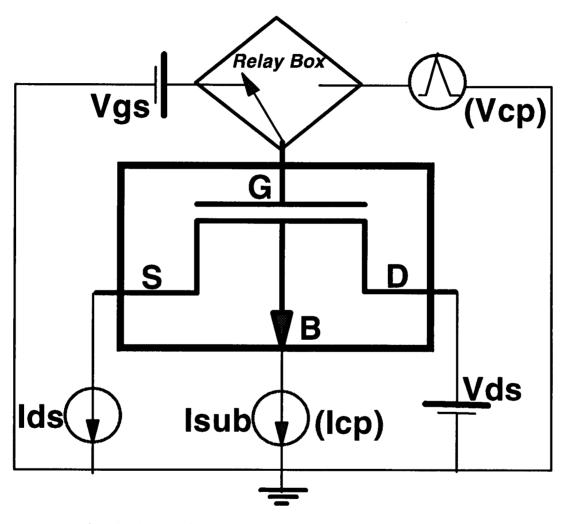

| 6-3           | Experimental setup for the hot-carrier stress and device           |             |

|               | characterization which includes charge pumping current             |             |

|               | measurements.                                                      | 112         |

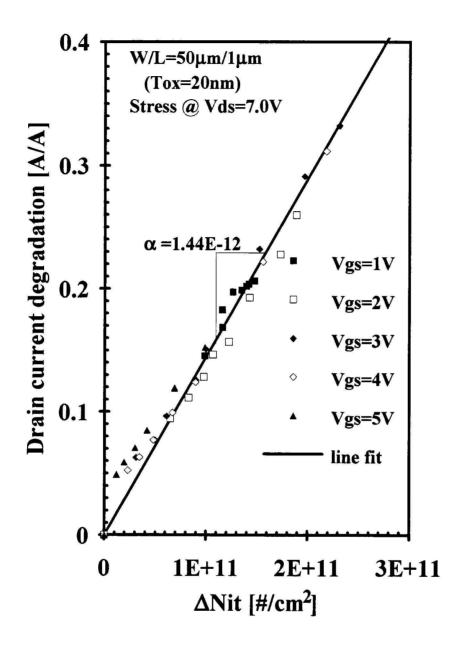

| 6-4           | Linear region drain current degradation and charge pumping         |             |

|               | current shifts as a function of stress time.                       | 113         |

| 6-5           | Correlation between the hot-carrier induced interface trap         |             |

|               | density and the linear region drain current degradation.           | 115         |

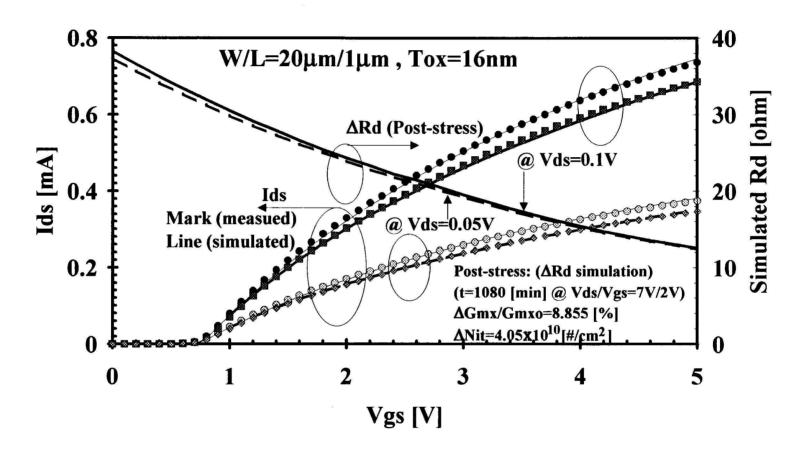

| 6-6           | Id-Vg characteristics of the hot-carrier induced drain             |             |

|               | current degradation and the simulation results of the $\Delta Rd$  |             |

|               | model.                                                             | 116         |

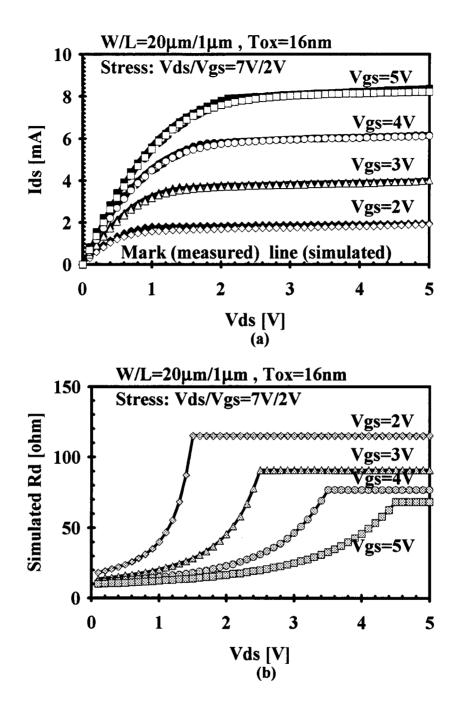

| 6-7           | Hot-carrier induced drain current degradation and the              |             |

|               | simulation results of the $\Delta Rd$ model; (a) Id-Vd             |             |

|               | characteristics and (b) the simulation results of $\Delta Rd$ .    | 117         |

| <b>Figure</b> |                                                                    | <u>Page</u> |

|---------------|--------------------------------------------------------------------|-------------|

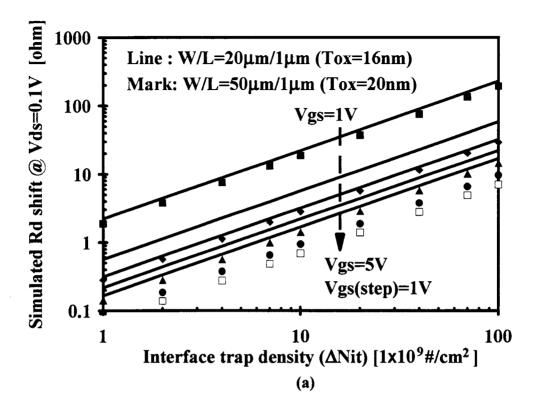

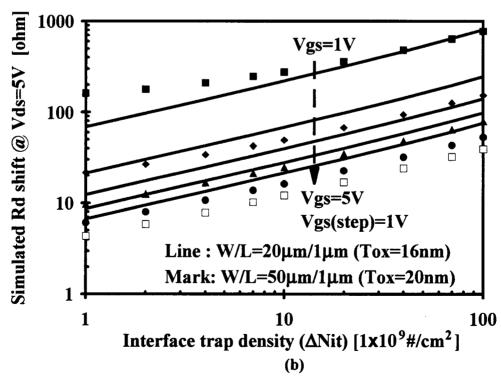

| 6-8           | The $\Delta Rd$ simulations as a function of hot-carrier induced   |             |

|               | interface trap density (a) in the linear region and (b) in the     |             |

|               | saturation region.                                                 | 119         |

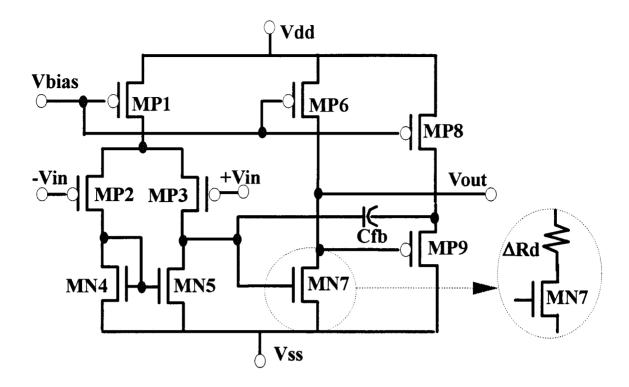

| 6-9           | Circuit diagram of a conventional CMOS Op-Amp and the              |             |

|               | application of the $\Delta Rd$ model.                              | 120         |

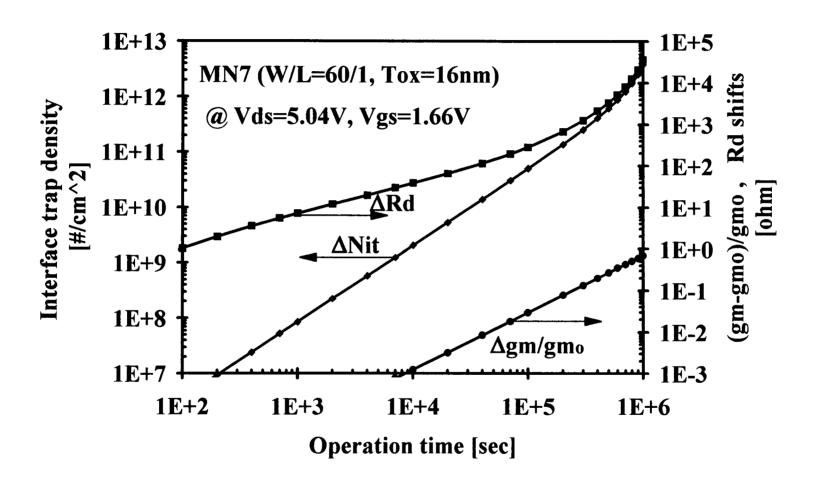

| 6-10          | Simulation results of $\Delta Rd$ for MN7 in Fig. 6-9 from Eq. (6- |             |

|               | 10) under the operating condition.                                 | 121         |

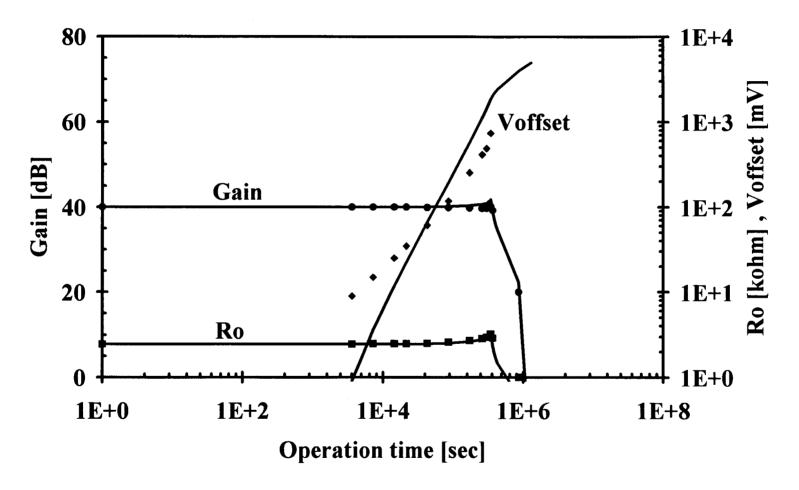

| 6-11          | Comparison of the $\Delta Rd$ model (mark) and the BERT model      |             |

|               | (line) reliability projections of the CMOS Op-Amp.                 | 123         |

# LIST OF TABLES

| <u>Table</u> |                                                          | <u>Page</u> |

|--------------|----------------------------------------------------------|-------------|

| 1-1          | Comparison of technology developments for hot-carrier    |             |

|              | effects.                                                 | 5           |

| 1-2          | CMOS device design rules and device parameters [53].     | 9           |

| 2-1          | CMOS device characteristics after hot-carrier injection. | 19          |

| 2-2          | Summary on substrate current model parameters of         |             |

|              | nMOSFET's.                                               | 31          |

| 4-1          | Lifetime models and power law of nMOSFET.                | 62          |

| 4-2          | SPICE MOSFET level 3 (MOS3) drain current equation       |             |

|              | [113].                                                   | 71          |

| 4-3          | Empirical model parameters of hot-carrier induced SPICE  |             |

|              | MOS3 parameter shifts as a function of gmx degradation.  | 79          |

## LIST OF APPENDIX FIGURES

| <u>Figure</u> |                                                             | <u>Page</u> |

|---------------|-------------------------------------------------------------|-------------|

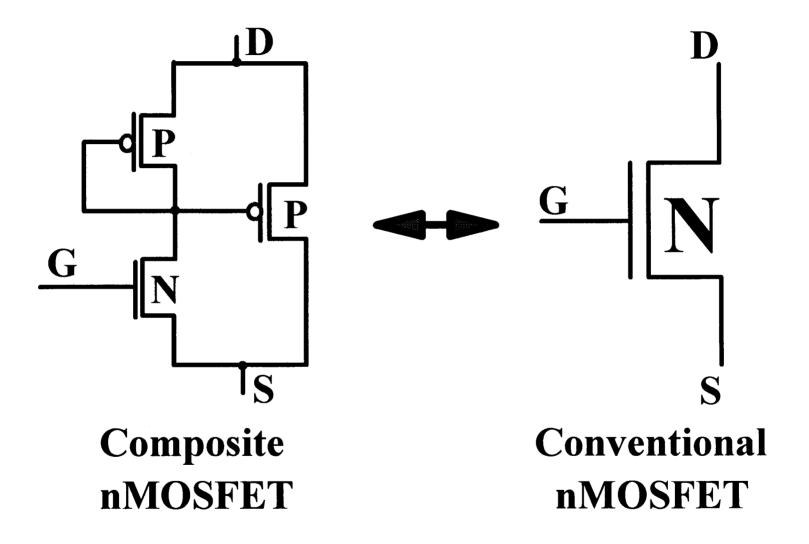

| A-1           | Schematic comparison between composite and conventional     |             |

|               | nMOSFET implementation.                                     | 142         |

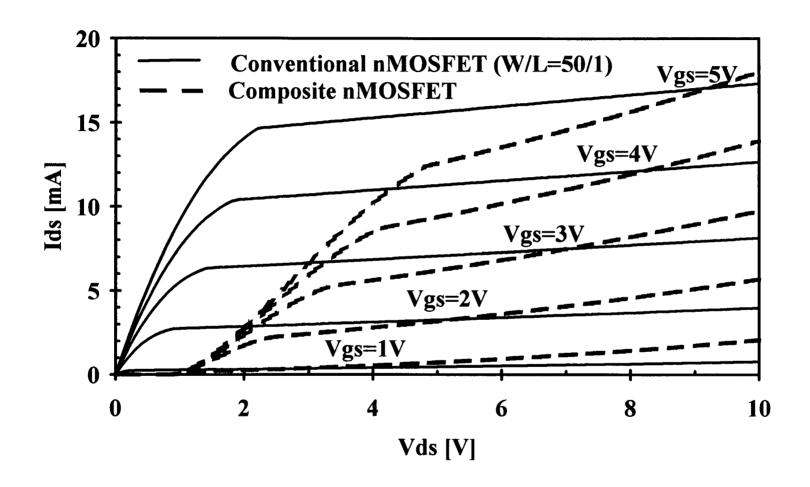

| A-2           | I-V characteristic curves of conventional and composite     |             |

|               | nMOSFET's.                                                  | 144         |

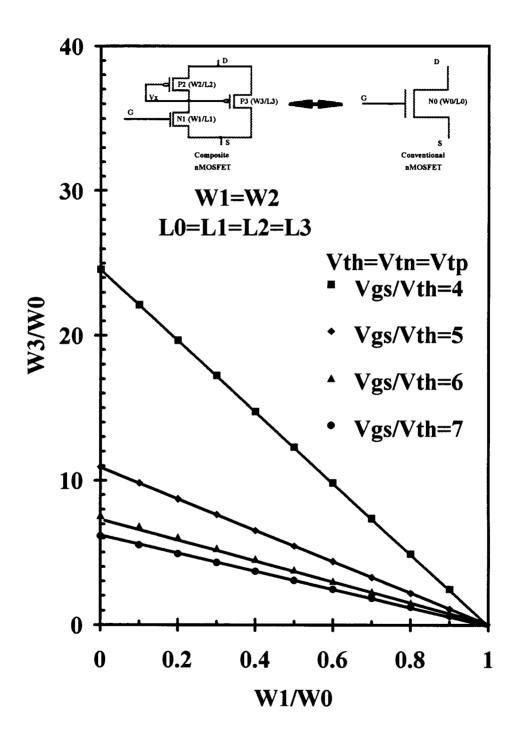

| A-3           | Design chart of a composite nMOSFET in analog IC's.         | 145         |

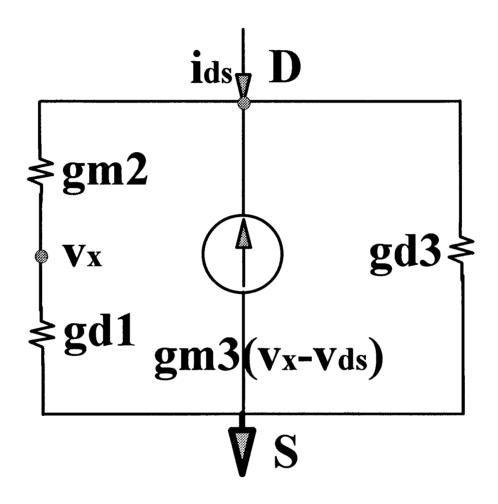

| A-4           | Small-signal model of a composite nMOSFET for the output    |             |

|               | resistance calculation.                                     | 147         |

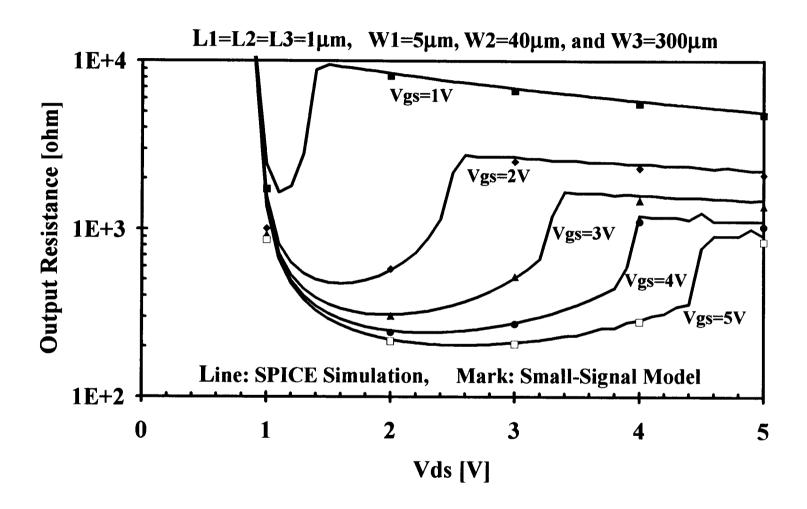

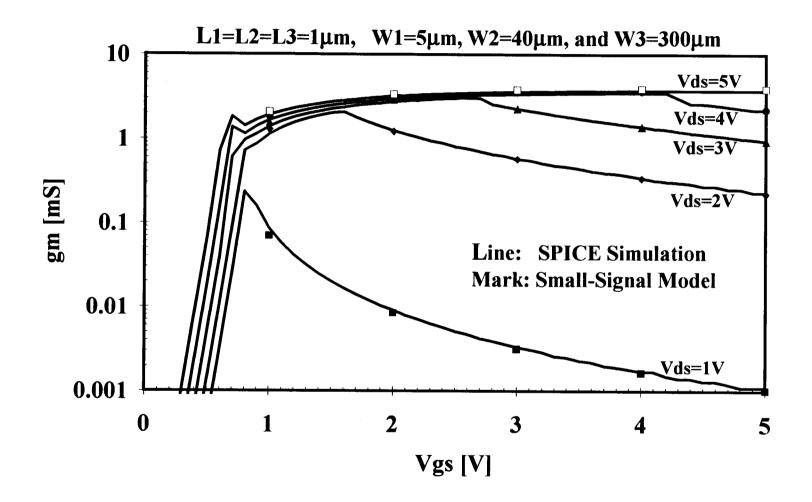

| A-5           | Output resistance of a composite nMOSFET.                   | 148         |

| A-6           | Transconductance (gm) of composite nMOSFET.                 | 150         |

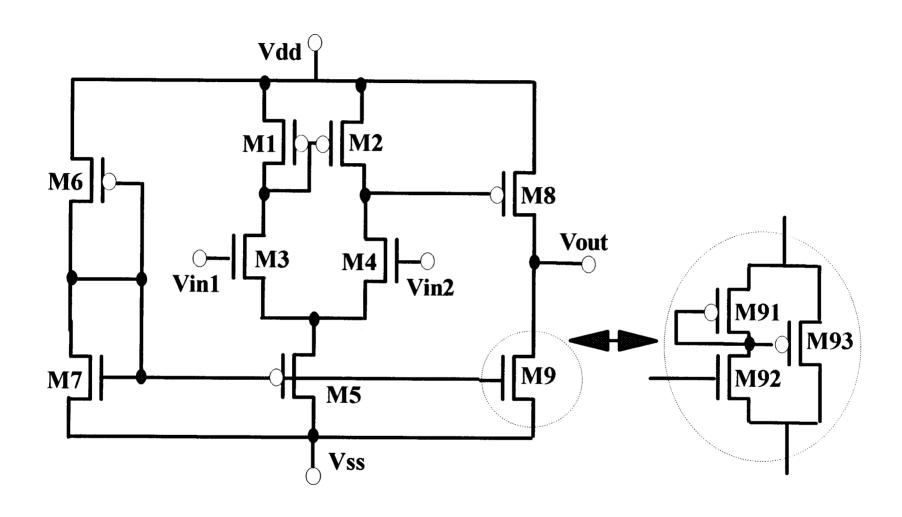

| <b>A-7</b>    | CMOS single-ended output differential amplifier.            | 151         |

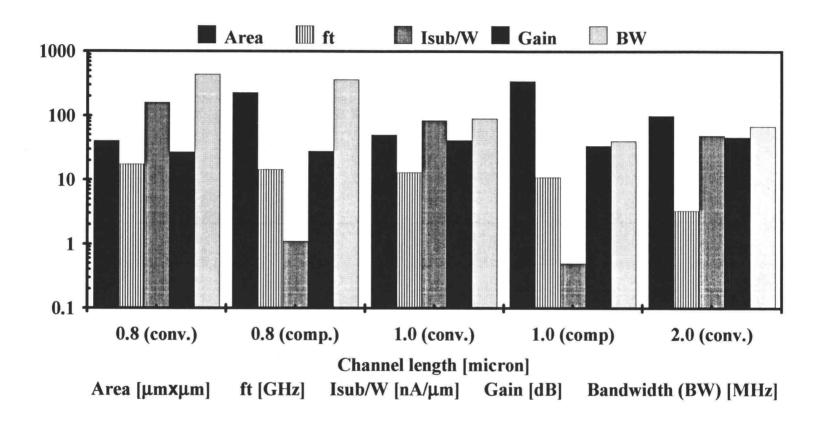

| A-8           | Device characteristics and circuit performance of composite |             |

|               | and conventional nMOSFET's.                                 | 152         |

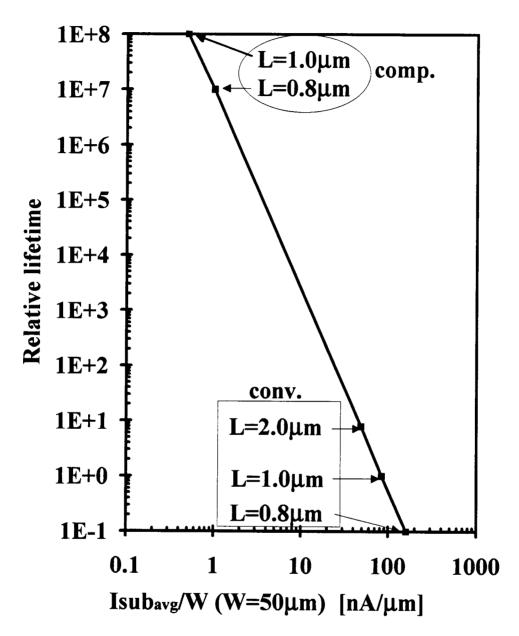

| <b>A-9</b>    | Relative lifetime projection of composite and conventional  |             |

|               | nMOSFET's.                                                  | 154         |

# PHYSICAL MECHANISMS, DEVICE MODELS, AND LIFETIME PROJECTIONS OF HOT-CARRIER EFFECTS IN CMOS TRANSISTORS

### 1. INTRODUCTION

The technical advances in the semiconductor industry have been accompanied by the development of the physics for device operation. The metal oxide semiconductor field effect transistor (MOSFET) has been chosen as a representative type of silicon device and is commonly used in contemporary very large scale integrated circuits (VLSI). In addition, the complimentary MOSFET technology (CMOS) has high-speed and allows low-power operation, the integration scale achievable with CMOS is the greatest strength of leading semiconductor technologies. As a consequence, this MOSFET technology has been the most challenging and active area in the IC industry over the last three decades [1]-[3].

As the size of silicon devices is reduced into the range of sub-micron dimensions, the injection of hot electrons from the silicon into the gate silicon dioxide layer generates electron oxide traps and surface state damage. This is one of the main physical mechanisms that determines the reliability of MOS structure-based device performance. The hot-carrier effects in CMOS devices can be summarized by an increase of threshold voltage (surface trapping and recombination) and a decrease of transconductance (channel mobility degradation) resulting in decreased drain current. Substrate current has become a major parameter to monitor hot-carrier effects under

operating conditions and in determining the lifetime projection of CMOS devices and IC's.

Much of the applicability of the study of hot-carrier effects in the field of semiconductor devices rests upon the progress made in physical analysis and model of hot-carrier effects. Moreover, reliability considerations due to hot-carrier effects of size-constrained devices (i.e., deep sub-micron devices) in VLSI circuits provide design guidelines and alternatives to maintain reliability assurance during device operation.

### 1.1 Literature Review

The hot-carrier is defined under the influence of the high electric field as the effective carrier (both electrons and holes) temperature based on the carrier energy becomes much greater than ambient temperature in equilibrium with the lattice. The concept of the hot-electron is very important in modeling device characteristics under the high electric fields, where the electron drift velocity becomes saturated and comparable to the thermal velocity (~10<sup>7</sup>cm/sec). As the size of the device decreases with a constant power supply voltage (i.e., 5V), the increase of the internal electric field becomes unavoidable. Thus, hot-carrier effects including both the hot-electron and the hot-hole become the main cause of CMOS device degradation. Consequently, lifetime projections and reliability models of hot-carrier induced MOSFET degradation have been developed under operating conditions (i.e., AC/DC operation conditions) including the worst case of operation and/or power supply [4]-[49]. The recent studies of hot-carrier effects on device degradation can be summarized as follows;

| Region   | Location | Organization       | References |

|----------|----------|--------------------|------------|

| U. S. A. | CA       | U. C. Berkeley     | [4]-[5]    |

|          |          | Hewlett-Packard    | [8]-[10]   |

|          |          | Intel              | [11]-[13]  |

|          | TX       | U. T. Austin       | [14]-[17]  |

|          |          | Texas Instrument   | [18]-[19]  |

|          |          | Motorola           | [20]-[21]  |

|          | NJ       | AT&T Bell Lab.     | [22]-[25]  |

|          | NY/VT:   | IBM                | [26]-[27]  |

|          | MA       | Digital Equip. Co. | [28]-[29]  |

| Europe   | German   | Siemens AG         | [30]-[33]  |

|          | France   | BULL Co.           | [34]-[36]  |

|          | Belgium  | IMEC               | [37]-[38]  |

| Japan    |          | Hitachi Ltd.       | [39]-[43]  |

|          |          | Toshiba Corp.      | [44]-[45]  |

This summary was based on literature from IEEE Trans. Electron Devices, IEEE Electron Device Lett., IEDM Tech. Dig., and Proc. of Int. Reliability Phys. Symp..

Among these research groups, U. C. Berkeley, Siemens, and Hitachi have been most active in reliability modeling and studying the device structure and the process induced hot-carrier effects. The detailed works of these three groups can be summarized as follows;

U. C. Berkeley Physical and empirical modeling of MOSFET's degradation under DC [7], and AC [5], [6], stress conditions.

Siemens Degradation modeling under various AC stress waveforms [30], [33].

Hitachi Degradation modeling [43], and structure [39], and process induced hot-carrier effects [40]-[42].

The device physics and reliability modeling of the hot-carrier induced device degradation have been developed under DC operating conditions [7], [43], and are still being developed under AC conditions with various waveforms, [5], [6], [8], [9], [28], [30]-[33], [38], including the temperature dependence of hot-electron effects [10], [37], [45]. The complete physical and empirical AC modeling of the hot-electron-induced device degradation under various waveforms and stress conditions is expected to be achieved.

The conventional technologies to suppress the hot-carrier effects are summarized in Table 1-1. The primary guidelines to reduce the hot-carrier effects are, then, summarized as follows;

- 1) reduce the high electric field near the drain region (low hot-carrier injection),

- 2) reduce the damage sites (i.e., less trapping centers in either oxide or interface),

- 3) improve hot-carrier immunity (i.e.; high binding energy).

The MOSFET device structure [29], [39], [44], [46], which induces the hot-electron effect has been well summarized by J. J. Sanchez et al., [46], and this issue will be continuously discussed as new technologies which result in the scaling of devices are developed. Recently, various processing technologies have been generating new insight into the hot-electron effect (i.e., oxidation growth conditions [14], [16], [17], [40],

Table 1-1

Comparison of technology developments for hot-carrier effects.

| Level   | Method           | Technology              | Highs                        | Lows                                                |

|---------|------------------|-------------------------|------------------------------|-----------------------------------------------------|

|         |                  | DDD (1.5μm)             | Simple                       | Bigger Lateral<br>Diffusion                         |

|         | Structure        | LDD (0.8 μm)            | Controllability of n- Region | Sidewall Effects                                    |

| Device  |                  | GOLD (0.5 μm)           | Reduced Emax                 | Complicated Proc.<br>Increased C                    |

|         | Process          | Ge, F, C, etc.          | Enhanced<br>Hot-Carrier      | Low $\mu_{\text{eff}}$ (Ge & C) $\Delta t_{OX}$ (F) |

|         |                  | Gate Oxide<br>Formation | Immunity                     | High Temp. Proc.                                    |

| Circuit | Extra<br>Device  | Digital                 | Conventional .               | Extra Transistors                                   |

|         | Shield<br>Device | Mixed-Mode              | Process Tech.                |                                                     |

radiation [47] or irradiation [48] treatments, and doping methods [23], [41], [43], [49].) The results have been quite promising and may be useful in future applications.

## 1.2 Technology Trends

As shown in Figure 1-1, the IC industry has been doubling the circuit density every two years based on the reduction of the channel length and gate oxide thickness. Recently, Micro Tech 2000, recommended by the National Advisory Committee on Semiconductors (NACS), has been proposed providing the US industry with 0.12μm IC technology by the 21st century [50]. Also, IBM Thomas J. Watson Research Center, Yorktown Heights, N.Y., has announced 0.1μm design rules, whose minimum active area MOSFET is 0.7μm×0.15μm, for 4G-bit DRAM's [51]. Furthermore, in some research laboratories the channel length of MOSFET has been already scaled down to beyond 0.1 μm which is a limit of the classical scaling of MOSFETs. However, the circuit properties were seriously affected by poor subthreshold characteristics, causing the logic swing to decrease with short-channel devices due to the increase of subthreshold current in short channel devices.

The electric field of the oxide breakdown and the typical maximum allowable gate leakage current specification (~1µA/cm²) lowers the maximum allowable electric field of a gate oxide to 7MV/cm [52] which is less than the physical breakdown electric field of 10MV/cm. However, the future trends cannot follow a simple mathematical reduction in channel length and oxide thickness without supporting processing technology such as oxidation and fine pattern lithography which are approaching, or may have already reached their tolerance limits. Also, effects of statistical fluctuation on device edge definition in fabrication and dopant distribution on minimum size

Figure 1-1 CMOS technology trend.

devices has become problematic; for instance, a technical breakthrough for precisely controlling dopant distribution must be achieved.

Power dissipation in a compact chip is well known to limit the maximum density of devices integrated on the chip [53]. As channel length decreases, an increasing electric field with the unscaled power supply (i.e., Vdd=5V) has been a primary cause of hot-carrier effects in past. However, the electric field in the devices can be kept constant by scaling down the power supply to 3.3V or below while reducing the threshold voltage and the logic swing in proportion to the decreasing power supply. In spite of technical difficulties in maintaining the same performance while lowering the IC power supply, the concept of the low power supply has two major commercial advantages in the IC industry. One is the further miniaturization of micro-computers such as battery-operated laptops and palm-sized computers with light-weight and extended operating time. The second advantage is the improvement in reliable operation of the internal circuitry which cannot sustain normal operation with a 5V power supply. Kakumu et. al., Toshiba, Japan, [54] has reported the optimum power supply voltage of CMOS devices for each set of design rules based on hotcarrier induced degradation as shown in Table 1-2. From an engineering and physical perspective, the importance of a lower power supply is to reduce the internal electric field, thus, improving IC reliability by reducing the hot-carrier effects.

Therefore, the future trend of CMOS technology is strongly affected by the state-of-the-art technology in the IC industry as well as the design rules and an optimum choice of the power supply voltage. In the digital IC industry, a 128M DRAM at 100MHz with 3.3V will be available in micro-computer chips no later than the year 2000, possibly sooner, as projected in Figure 1-2.

**Table 1-2** CMOS device design rules and device parameters [53].

| Design Rule | [µm]  | 2             | 1.2   | 0.8   | 0.6          | 0.5          | 0.3          |

|-------------|-------|---------------|-------|-------|--------------|--------------|--------------|

| Vdd [V]     | Conv. | 5             | -     |       | 3.3          | 3            | 2.3          |

|             | LDD   |               | 5     | 5     | 4.5          | 4            | -            |

| Tox [nm]    | Conv. | 48            | -     | •     | 11           | 10           | 8            |

|             | LDD   | -             | 26    | 15    | 13           | 13           | -            |

|             |       | 0.12          | 0.21  | 0.40  | 0.40 (Conv.) | 0.44 (Conv.) | 0.52 (Conv.) |

|             | NMOS  | 0.78          | 0.76  | 0.58  | 0.58         | 0.56         | 0.55         |

|             |       |               |       |       | 0.48 (LDD)   | 0.51 (LDD)   |              |

| Ids [mA/μm] |       |               |       |       | 0.68         | 0.68         |              |

| Vth [V]     |       | 0.06          | 0.13  | 0.24  | 0.22 @ 3.2V  | 0.24 @ 3.0V  | 0.28         |

|             | PMOS  | <b>-</b> 0.79 | -0.77 | -0.71 | -0.59        | -0.56        | -0.55        |

|             |       |               |       |       | 0.28 @ 4.5V  | 0.26 @ 4.0V  |              |

|             |       |               |       |       | -0.68        | -0.68        |              |

Optimum power supply voltage of CMOS devices can be empirically determined as follows where L is the channel length [µm] in the design rule.

Conventional MOSFET

$$V_{DD}[V] = 6.1 \times \sqrt{\frac{L}{2}}$$

$I_{DD}$   $I_{DD}[V] = 8.4 \times \sqrt{\frac{L}{2}}$

Figure 1-2 Projection of CMOS technology.

## 1.3. Overview of Reliability Analysis

In the early stages of the semiconductor industry, the initial value of yield was used as a measure of reliability since the statistical variations of device characteristics induced by operation conditions such as hot-carrier effects were negligible and infinitesimal as a result of the relaxed design rules and wide tolerance levels. However, the scaling of feature size has progressed more rapidly than the scaling of process tolerance resulting in the degradation of device characteristics under operating conditions which can no longer be neglected any more ( $L \ll 2\mu m$ ). Parameter mismatches and consequent IC functional failures have become a consequence of process fluctuations during fabrication and the operating conditions of the IC's [55].

Therefore, the definition of reliability [56] has become different than that of yield which is a measure of the fraction of manufactured units that are functional at the time of manufacture. For instance, even if the semiconductor devices or IC's may still pass the yield test (i.e., burn-in) conducted at the manufacturing plant, they can malfunction in real-world operations with a shorter operational lifetime than the customary lifetime. The definition for reliability is then the probability that an initially functional device or circuit will perform as designated, under predetermined conditions, for a projected lifetime. From this definition, any time dependent aspect that degrades the effective functioning of a device is a legitimate issue of reliability analysis for today's custom-oriented IC industry.

Reliability models can be classified into two general categories: empirical models and physical models. Empirical models attempt to determine, through mathematical tests, the probability distribution underlying observed life test data. For example, an empirical reliability model can be obtained from monitoring the amount of device parameter shifts as a function of the stress time (i.e., [29], [43]). However,

physical models attempt to describe the degradation, with time, of the same physical parameters which is used as a measure of reliability. Such device parameters are related to physical attributes such as dimensions and material properties of the device, and operating or environmental conditions. The discrepancy between empirical and physical reliability models is due to the fact that there is an underlying probability distribution which governs the values of the physical parameters which enter into fundamental properties of the device. As a consequence of the difficulty of physical models, semi-empirical models are commonly adopted by measuring the change with time of a particular parameter.

One of the most important reliability analysis techniques is the accelerated lifetime test in which the reliability data within a reasonable time can be obtained by acceleration of the degradation or aging process. The validity of the results of accelerated lifetime tests strongly depends upon the assumption that the degradation process is only accelerated and not altered. Therefore, reliability analysis in the IC industry is a concurrent field of semiconductor devices and IC design as shown in Figure 1-3.

### 1.4 Motivation and Objectives

The main scheme and impact of this research in the field of semiconductor devices and IC design is illustrated in Figure 1-3. The purpose of this research consists of developing a physical reliability model which can assure simple and versatile applicability in the IC industry, and proposing reliability projection techniques based on the physical analysis of hot-carrier induced degradation mechanisms in CMOS transistors.

Figure 1-3 Structure of reliability analysis of hot-carrier effects.

In chapter 2, the fundamental physical mechanisms of degradation have been reviewed including substrate current models. Comparisons have been made between p- and n-channel devices of different drawn channel lengths in terms of hot-carrier induced degradation based on substrate current models for reliability projections.

In chapter 3, the device part of this work has been to analyze the effects of using drain avalanche hot carrier injection (DAHI) and electric field stimulated reemission (EFSE) techniques on CMOS sub-micron devices. The physical mechanisms of hot-carrier induced device degradation have been studied by investigating the electron trapping energy levels in CMOS gate oxides. Also, hot-carrier induced interface trap charge has been investigated by using the charge pumping method.

In chapter 4, the lifetime projections for current foundry service technologies have been investigated by accelerated lifetime tests, and comparisons have been made between HP34-CMOS and HP26B-CMOS processes. Also, empirical models of hot-carrier induced device characteristics and the device model parameters of SPICE MOS level 3 have been developed for reliability simulations.

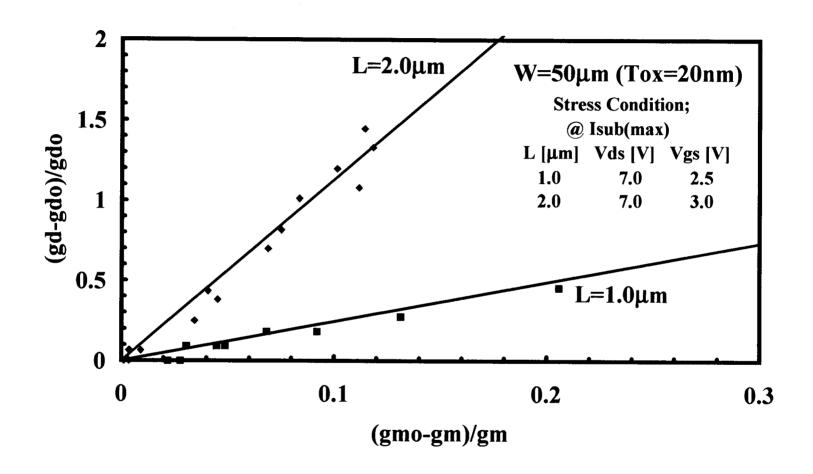

In chapter 5, a physical model of drain conductance degradation due to hot-carrier injection is proposed for lifetime projections in analog IC's. The proposed drain conductance (gd) degradation model has been found to be a function of the gm degradation in the linear region. This results in parameter mismatches in analog IC designs, which are then applicable to the lifetime prediction for analog IC design. Also, design guidelines based on the gd degradation model have been described for analog IC's.

In chapter 6, a hot-carrier induced series resistance enhancement ( $\Delta Rd$ ) model of nMOSFET's is proposed for reliability projections in analog IC design. The proposed  $\Delta Rd$  model is based on the increase of the hot-carrier induced interface trap charge ( $\Delta Nit$ ). Furthermore the reliability projection is demonstrated to show the  $\Delta Rd$

model (one parameter) is much simpler and more applicable in analog IC design rather than the commercial reliability simulator which requires to extract a set of stressed process files (6 parameters in the BERT).

In chapter 7, concluding remarks on this study have been summarized and future work has been suggested.

In appendix A, a new design technique using a composite nMOSFET is introduced to reduce the effects of substrate current and hot electron injection; thus, improving circuit reliability. Comparisons have been made between the performance of this design technique and other alternatives.

In the device models and the reliability projections (Chapt. 4, 5, and 6), a CMOS single-ended output differential amplifier has been adopted as representative analog IC designs. Although digital IC design is more concerned with speed and performance in circuit simulations, analog IC design requires more accuracy. The performance of an analog IC is strongly related to its DC bias condition, at which parameter mismatches can affect every aspect of the circuit performance. Hence, the concentration of this work is to analyze the performance and investigate the effect of hot electron injection on devices in both types of circuits.

## 2. HOT-CARRIER EFFECTS ON DEVICES

### 2.1 Introduction

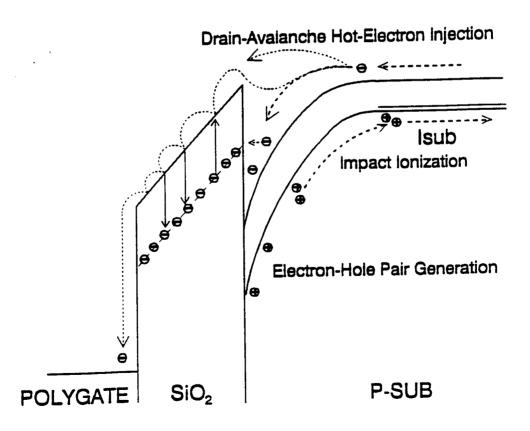

The down scaling of integrated circuit device dimensions and layouts has been driven by the desire to reduce die costs, increase chip performance, and to increase the number of functions available on a single chip (chip complexity). The threshold electric field for the hot-carrier injection is around 100 kV/cm [54] in silicon devices, which limits the device shrinking process. Above the threshold electric field, the effective carrier temperature increases much higher than the ambient temperature, that is, the energy gain rate of electrons and holes from the field is greater than the energy loss rate to the optical phonons. During device operation, hot-carrier effects result in several reliability problems as previously described. Fig. 2-1 illustrates a schematic diagram of the hot-carrier mechanisms showing the impact ionization and the avalanche multiplication processes [58]-[60]. Impact ionization is a collision process by which carriers gain sufficient energy from an electric field to create electron-hole pairs upon colliding with atoms in the lattice as shown in Fig. 2-1. The channel carriers (electrons in nMOSFET's or holes in pMOSFET's) gain energy as they travel through the highfield region. Some of the carriers gain sufficient energy (at least the bandgap energy) to ionize the atoms upon collision resulting in carrier multiplication. This excess carrier generation is called avalanche multiplication. In nMOSFET's, the electrons created are swept by the field toward the drain, while the holes become the substrate current.

Hot-carrier injection can be divided into two categories [21]: channel hot-carrier injection (CHI) and drain-avalanche hot-carrier injection (DAHI). Once the surface of a transistor is inverted, the applied drain voltage accelerates channel carriers

## P-TYPE SILICON

Figure 2-1 Schematic diagram of hot-carrier mechanisms.

from the source to the drain. Before reaching the drain edge, some of the channel carriers gain enough energy to surmount the Si-SiO<sub>2</sub> interface potential barrier. Thus, this mechanism is called CHI. Some of channel hot-carriers collide with atoms of the lattice in the pinch-off region during saturation operation and excite electron-hole pairs by impact ionization. Some of the impact ionization induced carriers will have a high enough energy to overcome the Si-SiO<sub>2</sub> interface potential barrier. This mechanism is then called DAHI. Both CHI and DAHI generate carriers traversing the gate oxide in which the injected carriers are accelerated and monitored as gate current. The hot carriers injected into gate oxide can lead to the formation of interface states and trapped oxide charge. The resulting degradation which is referred to hot-carrier effects can lead to device failure. Additionally, the substrate current produced by impact ionization can produce 4 terminal latch-up in CMOS structures [62]-[63].

Due to the inherent differences of the majority carriers in CMOS devices; in nMOSFET's, electrons and in pMOSFET, holes; and the potential barrier of electrons (3.1eV) and holes (4.8eV) [59]-[60]; the transistors in a CMOS circuit experience different amounts of hot-carrier induced degradation as shown in Table 2-1. Although both CHI and DAHI occur in both p- and n-MOSFET's, hot-carrier induced degradation of pMOSFET's in terms of threshold voltage shifts, transconductance shifts, and drain current shifts is much less than that of nMOSFET's [64]-[65]. For the nMOSFET case, electron injection into the oxide near the drain is responsible for interface state generation and negatively charged traps, and that the positive charge is due to trapped holes being injected into the same region. In order to improve process optimization and assess device reliability in CMOS technology, hot-carrier effects in nMOSFET's only have been investigated in this study.

Another limitation to the device shrinking process has been imposed by equipment and processes (i.e., fine pattern lithography) which the IC industry is using.

Table 2-1

CMOS device characteristics after hot-carrier injection.

| MOSFET                | Type                  | N        | P        | P       |

|-----------------------|-----------------------|----------|----------|---------|

| (W=50μm, Tox=20nm)    | L [µm]                | 1        | 1        | 0.6     |

|                       | Vds                   | 7.0V     | -7.0V    | -7.0V   |

| Stress Condition      | Vgs                   | 2.5V     | -2.0V    | -2.0V   |

| (DAHI)                | Isub(max)             | -490μA   | 7μΑ      | 22μΑ    |

|                       | Stress time           | 1441 min | 1441 min | 961 min |

| Threshold Voltage     | Vtho                  | 0.746V   | -0.873V  | -0.864V |

|                       | $\Delta  Vth $        | +74.4%   | -2.3%    | -15.4%  |

| Max. Transconductance | gm <sub>O</sub> (max) | 592μS    | 154μS    | 227μS   |

|                       | $\Delta$ gm(max)      | -23.2%   | +18.3%   | +36.2%  |

| Sat. Drain Current    | Idss <sub>0</sub>     | 18.17mA  | -8.51mA  | -11.8mA |

| Vds =6.5V,  Vgs =5.5V | Δ Idss                | -11.4%   | +5.0%    | +13.0%  |

The trade-off issues are largely those of performance and density versus manufacturability. Thus, technical progress is necessary in understanding the role of key physical parameters on these degradation mechanisms and ultimately on their control within safe limits [66]-[68].

The purpose of this chapter is, hence, to offer an introductory review of hotcarrier effects on devices. Some basic concepts and measurement techniques will be explained and discussed.

## 2.2 Hot-Carrier Induced Device Degradation

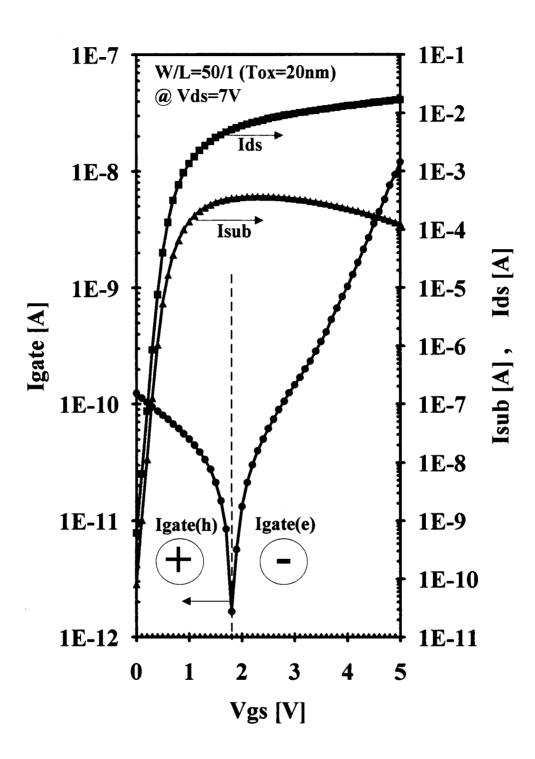

Figure 2-2 shows a schematic representation of the hot-carrier induced currents which have been monitored as gate, drain, and substrate currents. The most important feature of the hot-carrier induced currents is that the currents are composed of both electrons and holes and vary as functions of gate voltage. The drain voltage (Vds) represented here is high and in the order of 7V which is the typical stress condition for hot-carrier injection.

The gate current in Fig. 2-2 is a good example of the both electron and hole injection. Hot-carrier injection starts even with low gate voltages. The carriers can turn around inside the oxide and come back to the interface again, and then go back into the channel, at least a major portion of them because of the orientation of the electric field inside the oxide. The electric field is in this instance determined by a high drain voltage and a low gate voltage. On the other hand, since the barrier height of holes for injection into the oxide is higher than that of electrons, hole injection will require a higher field. Hence, as the electric field becomes higher with the increase of gate voltage, holes can be still injected into the oxide, but not as readily as electrons. Hole injection

Figure 2-2 Hot-carrier induced currents of an nMOSFET in terms of drain, substrate, and gate currents.

predominantly occurs at low gate voltage while electron injection becomes dominant at high gate voltage. It should be noted that, even at very low gate voltages (Vgs<1.5V), electron injection already exists. Hence, in the MOSFET due to the inhomogeneous field distribution, it is impossible to achieve and analyze a situation where either hole or electron injection exists exclusively. Thus, there is no way to measure experimentally the maximum injected current of either electrons or holes.

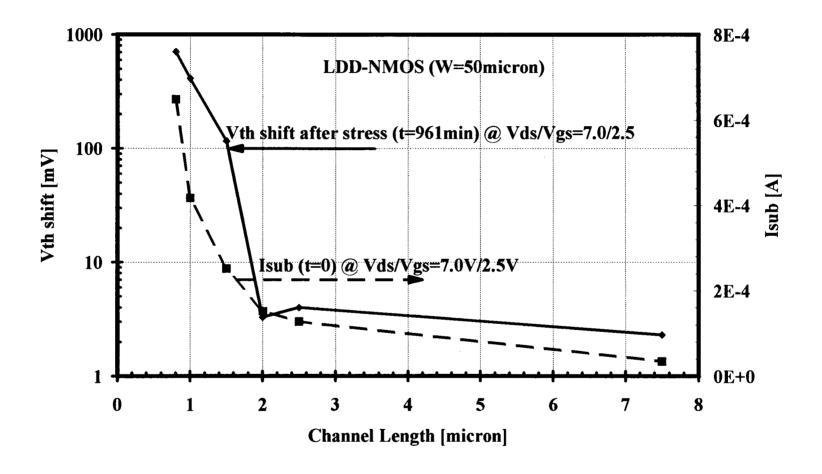

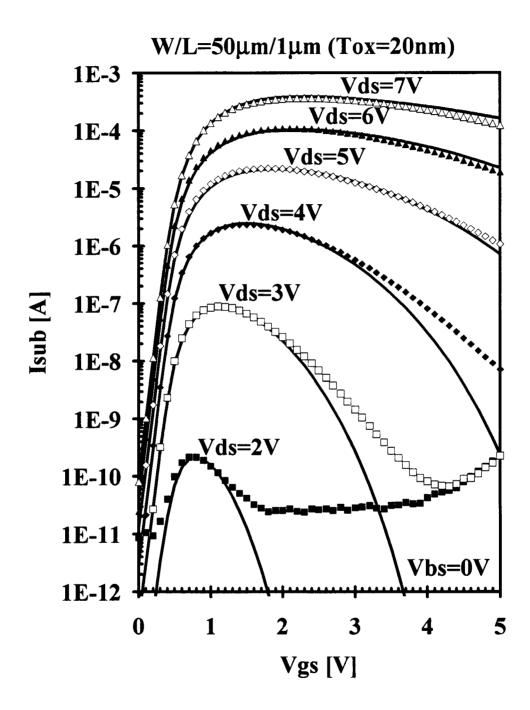

The number of carriers in the channel increases with increasing gate voltage but there is no step at the threshold voltage but rather a gradual increase. For higher gate voltages, since the gate and drain voltages become comparable, this increase of the gate voltage reduces the net electric field inside the oxide near the drain. Hence, the substrate current and the gate current decrease for higher gate voltage, Vgs>6V, as the electric field goes down as shown in Fig. 2-2. This combination of applied electric fields and carrier generations causes a maximum condition of hot-carrier injection. Fig. 2-3 shows the hot-carrier induced threshold voltage shifts of nMOSFET"s as a function of channel length with W=50µm. It should be pointed out that the hot-carrier induced threshold voltage shifts become most noticeable at channel lengths below 2µm. Hence, the hot-carrier effects are mainly as result of small geometry devices. Also, as shown in Fig. 2-3, the threshold voltage shifts are very closely related to the substrate currents induced by hot-carrier generation. For that reason, in the study of hot-carrier effects (mainly in nMOSFET's), the maximum in the substrate current, which is around Vgs≤ 0.5 Vds, has been the primary parameter used for monitoring the hot-carrier effects and correlating with lifetime projections.

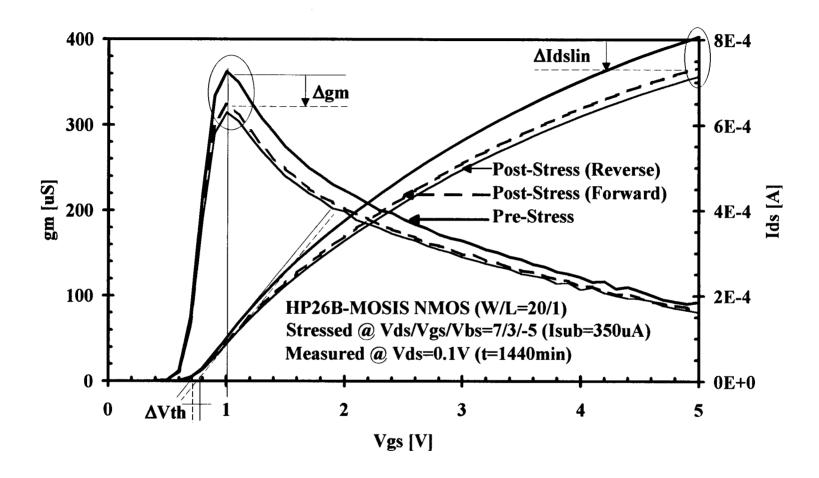

Figure 2-4 shows a comparison of the Ids-Vgs characteristic curves for pre- and post-stress. After hot-carrier injection, the I-V characteristic curves are not totally symmetrical with respect to the source-drain terminals because the damage caused by hot-carrier injection is localized at the drain region. The device parameter shifts are

Figure 2-3 Substrate currents and threshold voltage shifts under hot-carrier injection as a function of channel lengths.

Figure 2-4 Ids-Vgs characteristic curves of an nMOSFET device under hot-carrier injection.

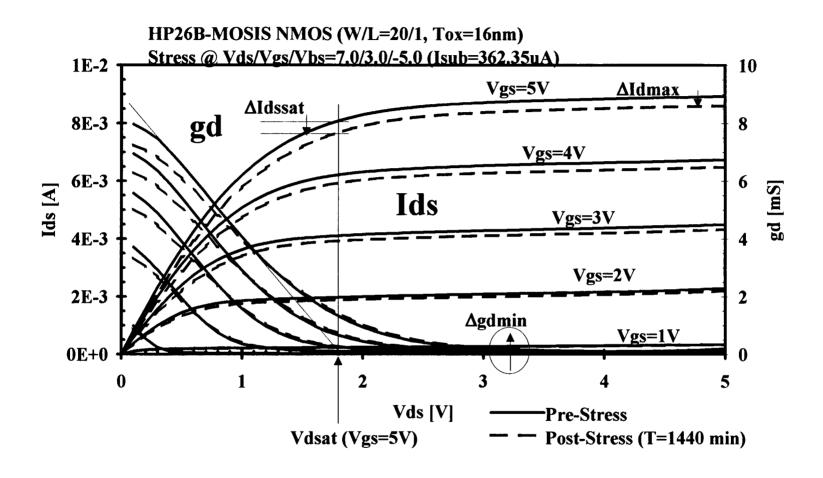

slightly larger in the reverse mode than forward mode, where reverse mode means that the source and drain terminals are reversed during measurement and the forward mode means that the source and drain terminals are the same during hot-carrier stress and measurement. Also, Ids-Vds characteristic curves of pre- and post-stress are shown in Fig. 2-5. For simplicity, mainly the forward mode device characteristics have been studied. The device parameters of interest in the linear region are the threshold voltage ( $\Delta$ Vt), the maximum transconductance in linear region ( $\Delta$ gm at Vds=0.1V), and the linear drain current ( $\Delta$ Idslin at Vgs/Vds=5.0V/0.1V) as illustrated in Fig. 2-4. In the saturation region the device parameters of interest are the minimum drain conductance in the saturation region ( $\Delta$ gd at Vds=5.0V), the saturation drain current ( $\Delta$ Idssat at Vds/Vgs=Vdsat/5.0V), and the maximum saturation current ( $\Delta$ Idsmax at Vds/Vgs=5.0V/5.0V) as illustrated in Fig. 2-5. These device parameters have been chosen for lifetime projections of hot-carrier induced degradation which will be discussed in Chapter 4 in more detail.

## 2.3 Substrate Current Model

In nMOSFET's, the hot-carrier (or electron) induced substrate current is the hole current generated by impact ionization in the drain high-field region where electron-hole pairs are generated by the high energy channel electrons. This can cause long-term device degradation. Hence, the more severe the impact ionization, the higher the substrate current which is produced, and the more hot-carrier induced damage. The purpose of this session is then to investigate and establish a substrate current model which will correlate with hot-carrier induced device degradation and then develop lifetime projections in this study.

Figure 2-5 Ids-Vds characteristic curves of an nMOSFET device under hot-carrier injection.

There have been a number of substrate current models [69]-[77]. Since these models employ various types (at least a couple) of process dependent parameters (i.e., ionization constants and saturation region parameters), some of the substrate current models are too unnecessarily complicated to allow a fitting between measured and the simulated data. For the purpose of lifetime projections, then a simple and reasonably accurate substrate current model is more suitable for correlations between hot-carrier induced device degradation and circuit simulations. Hence, in this work, the substrate current model has been selected based on the physical phenomena in association with a minimum number of empirical parameters.

A simple but efficient expression accepted for the substrate current (Isub) model which is a function of DC biases is given by [64];

$$Isub = \frac{Ids \cdot Ai \cdot Em \cdot l_d}{Bi} \cdot \exp(-\frac{Bi}{Em})$$

(2-1),

where Ids is the drain-to-source current, Em is the maximum channel electric field,  $l_d$  is an effective ionization length [cm], and Ai and Bi are the pre- and post- exponential ionization coefficients, respectively. There have been quite numbers of studies of these ionization coefficients as shown below;

| MOS | $Ai [10^6/cm]$ | <i>Bi</i> [10 <sup>6</sup> V/cm] | Ref. |  |

|-----|----------------|----------------------------------|------|--|

| N   | 2.45           | 1.92                             | [69] |  |

| N   | 2              | 1.7                              | [71] |  |

| N   | 9              | 1.3                              | [74] |  |

| N   | 2              | 1.76                             | [77] |  |

| P   | 2.25           | 3.26                             | [59] |  |

| P   | 8              | 3.7                              | [71] |  |

The large variations in the ionization coefficients indicate that these coefficients are the most process and geometrical dependent constants. Hence these coefficients should be determined in order to construct the Isub model.

Also,  $l_d$  and Em in Eq. (2-1) can be physically modeled as;

$$l_d = \sqrt{\frac{\varepsilon_{si}}{\varepsilon_{ox}} \cdot Tox \cdot Xj}$$

(2-2),

where  $\varepsilon_{si}$  and  $\varepsilon_{ox}$  are the dielectric permittivities of SiO<sub>2</sub> and Si ,respectively, Tox is the gate oxide thickness, and Xj is the junction depth. And,

$$Em = \frac{Vds - Vdsat}{l_d} \tag{2-3},$$

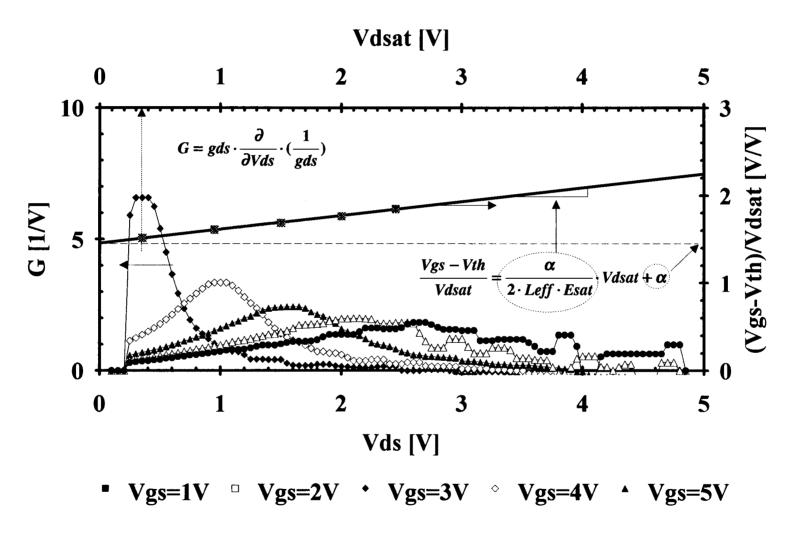

where Vds is the drain voltage and Vdsat is the saturation drain voltage. Although Ai and Bi are the major empirical parameters which are process dependent constants, Vdsat must be precisely defined to obtain Ai and Bi. As shown in Fig. 2-6, Vdsat has been determined by using the method developed by Jang et al. [78]. In this method the peak position of the function G [64] as defined in Fig. 2-6 corresponds to Vdsat. This Vdsat can be modeled as,

$$Vdsat = Leff \cdot Esat \cdot \left[ \sqrt{1 + \frac{2 \cdot (Vgs - Vth)}{\alpha \cdot Leff \cdot Esat}} - 1 \right]$$

(2-4),

where Leff is the effective channel length, Esat is the channel field at which the carriers reach velocity saturation, Vth is the threshold voltage, and  $\alpha$  is the body factor in the saturation region (i.e., Vdsat=Vgs- $\alpha$ ·Vth(Vds)). The experimental methods used to obtain  $\alpha$  and Esat are shown in Fig. 2-6. Since Vdsat is a circuit parameter which is important during device operation, once Vdsat is known, then a Isub model which is suitable for lifetime projections in circuit simulations can be easily determined from Eq. (2-1) by using the following empirical expression of the Isub model;

Figure 2-6 Saturation drain voltage (Vdsat) measurements.

$$Isub = C_1 \cdot Ids \cdot (Vds - Vdsat) \cdot \exp(-\frac{C_2}{Vds - Vdsat})$$

(2-5),

where  $C_1$ =Ai/Bi and  $C_2$ =Bi· $I_d$ . Table 2-2 shows a summary of measured values of  $C_1$  and  $C_2$  on various channel length devices and with different bulk-biases. Although, the Vdsat model parameters ( $\alpha$  and Esat in Eq. (2-4)) are included in Table 2-2, Vdsat is pre-determined by the given operating conditions prior to Ids simulations during device simulations. Hence,  $C_1$  and  $C_2$  are the main parameters used to simulate substrate currents. It should be pointed out that Table 2-2 has been obtained for two different processes which will be described in chapter 4. By using the Vdsat and Isub model parameters, the simulation results of the Isub model have been obtained as shown in Fig. 2-7. The measured data is in marks and the simulation results are in lines. The simulated substrate currents match well the measured data over a wide range of drain and gate voltages. This is the substrate current model will be used in this study to calculate degradation and provide lifetime projections from circuit simulations due to hot-carrier injection.

# 2.4 Summary

Hot carrier injection mechanisms have been reviewed. Hot-carrier induced device degradation has been caused by the increase of trap charge and surface states induced by hot-carrier injection during device operation. Substrate current due to hot-carrier injection has been shown to be the best lifetime monitor of hot-carrier induced degradation in submicron devices. For lifetime projections in circuit simulations, an Isub model has been obtained by employing two empirical model parameters. Although the Isub model presented in this study has been limited to nMOS devices, it can be also

**Table 2-2** Summary on substrate current model parameters of nMOSFET's.

| W [µm]  | =50      | (HP34-    | (EMOS)      | Tox [nm]             | =20                | W [µm]  | =20      | (HP26B-   | CMOS)        | Tox [nm]             | =16                |

|---------|----------|-----------|-------------|----------------------|--------------------|---------|----------|-----------|--------------|----------------------|--------------------|

|         |          | Leff [µm] | =0.7        |                      |                    |         |          | Leff [µm] | =0.44        |                      |                    |

| Vsb [V] | Vth [V]  | α         |             | C <sub>1</sub> [1/V] | C <sub>2</sub> [V] | Vsb [V] | Vth [V]  | α         | Esat [V/cm]  | C <sub>1</sub> [1/V] | C <sub>2</sub> [V] |

| 0       | 0.468802 | 1.553007  | 142544.40   | 0.690978             | 25.50692           | 0       | 0.627759 | 1.580099  | 30239.15     | 0.736713             | 24.21416           |

| 1       | 0.783112 | 1.378801  | 113798.70   | 1.027110             | 28.20998           | 1       | 0.794410 | 1.468854  | 27075.46     | 1.004180             | 25.52987           |

| 2       | 0.950668 | 1.318937  | 90196.66    | 1.113107             | 29.16711           | 2       | 0.864985 | 1.405008  | 24882.74     | 1.103829             | 25.98674           |

| 3       | 1.037171 | 1.295385  | 79933.51    | 1.156754             | 29.69413           | 3       | 0.894910 | 1.334591  | 19186.11     | 1.124120             | 26.17007           |

| 4       | 1.068467 | 1.221862  | 57316.74    | 1.470327             | 30.27213           | 4       | 0.907839 | 1.273453  | 16781.63     | 1.124002             | 26.14533           |

| 5       | 1.091894 | 1.155907  | 42076.29    | 1.167915             | 29.59434           | 5       | 0.918526 | 1.207371  | 13561.92     | 1.106147             | 26.12332           |

|         |          | Leff [µm] | =0,9        |                      |                    |         |          | Leff [µm] | <b>=0.64</b> |                      |                    |

| Vsb [V] | Vth [V]  | α         | Esat [V/cm] | C <sub>1</sub> [1/V] | C <sub>2</sub> [V] | Vsb [V] | Vth [V]  | α         | Esat [V/cm]  | C <sub>1</sub> [1/V] | C <sub>2</sub> [V] |

| 0       | 0.4959   | 1.394703  | 69389.16    | 0.712541             | 25.51048           | 0       | 0.682390 | 1.391658  | 35643.20     | 1.088489             | 26.00688           |

| 1       | 0.8261   | 1.263337  | 61448.16    | 0.921148             | 27.89681           | 1       | 0.964753 | 1.334323  | 33918.83     | 1.558872             | 28.22865           |

| 2       | 1.0196   | 1.203302  | 51603.53    | 1.036313             | 29.14562           | 2       | 1.122386 | 1.293616  | 29633.66     | 1.802634             | 29.34054           |

| 3       | 1.1359   | 1.123705  | 40760.93    | 1.037790             | 29.48735           | 3       | 1.218545 | 1.263101  | 27978.82     | 2.026591             | 30.11887           |

| 4       | 1.1875   | 1.037262  | 31731.72    | 1.152489             | 32.97653           | 4       | 1.261872 | 1.241450  | 25137.18     | 2.113124             | 30.45892           |

| 5       | 1.2131   | 1.014073  | 21951.20    | 1.708095             | 31.79782           | 5       | 1.276403 | 1.225144  | 23256.70     | 1.998561             | 30.26946           |

|         |          | Leff (µm) | <b>=1.7</b> |                      |                    |         |          | Leff [µm] | <b>=0.84</b> |                      |                    |

| Vsb [V] | Vth [V]  | α         | Esat [V/cm] | $C_1$ [1/V]          | C <sub>2</sub> [V] | Vsb [V] | Vth [V]  | α         | Esat [V/cm]  | $C_1$ [1/V]          | $C_2[V]$           |

| 0       | 0.6327   | 1.273663  | 107798.00   | 0.817625             | 25.96492           | 0       | 0.693172 | 1.288127  | 38504.26     | 0.982391             | 25.72086           |

| 1       | 0.9914   | 1.166476  | 89522.28    | 1.546527             | 30.29492           | 1       | 1.009039 | 1.229441  | 34600.92     | 1.398005             | 28.18276           |

| 2       | 1.2181   | 1.085157  | 74530.30    | 2.343795             | 32.94198           | 2       | 1.209604 | 1.203092  | 32548.94     | 1.544260             | 29.33704           |

| 3       | 1.3839   | 0.985214  | 60856.79    | 3.495428             | 34.94418           | 3       | 1.350822 | 1.161338  | 31108.99     | 2.315544             | 31.53143           |

| 4       | 1.5023   | 0.957824  | 44999.50    | 4.243279             | 36.53851           | 4       | 1.449231 | 1.142610  | 30025.51     | 2.837087             | 32.80015           |

| 5       | 1.5803   | 0.890766  | 23862.96    | 4.733346             | 37.34192           | 5       | 1.487988 | 1.091908  | 25024.04     | 2.879591             | 32.92197           |

Figure 2-7 Measured (marks) and simulated (lines) substrate currents.

easily adopted for pMOS devices [70]. Using such parameters, this Isub model can then be used to calculate the degree of hot-carrier induced device degradation of MOSFET's under operating conditions.

## 3. PHYSICAL MECHANISMS OF TRAPS AND SURFACE STATES

#### 3.1 Introduction

As the dimensions of devices become smaller, hot-carrier induced device degradation has become a major concern in the long-term reliability of sub-micron CMOS technology and applications. Hot electron trapping in gate oxides and surface (or interface) states due to hot-carrier injection cause a threshold voltage shift [79] and reduction of drain to source current, and consequently an increase in the switching time in VLSI/ULSI circuits [80]. Recently, the electric field stimulated emission (EFSE) method [81] was introduced to characterize the shallow level traps (0.9eV) at low temperature (77°K~200°K). In this chapter, a simple model of injection and thermal reemission is shown to be adequate for predicting the hot-carrier injection induced degradation on sub-micron nMOSFET technology.

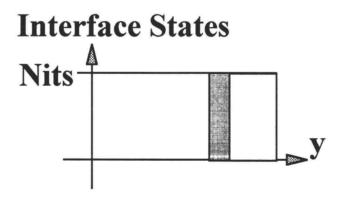

The ability to analyze charge trapping and surface states in semiconductor devices is critical to the accurate simulation of devices such as deep sub-micron devices. As the quality of gate oxide increases, the generation of interface states has been another main cause of MOSFET degradation in devices [82]-[89]. The interface states are electronic states in the forbidden gap of the semiconductor energy bands on the boundary between the gate oxide and the semiconductor. The origin of the interface states may be stretched Si-O bond, stretched Si-Si bond, oxygen vacancy, or silicon dangling bond [90]. Hot-carrier effects become severe as internal electric field increases. The increased possibilities of Si-SiO2 interfacial damage lead to create interface trap charge (electrons and/or holes). These trap charge strongly effect the electrical performance of devices by trapping carriers and reducing the mobility. As an

example, the subthreshold region (subthreshold swing;  $S=\partial \log(Ids)/\partial Vgs$ ) is greatly extended ( $\Delta S>0$ ), since the interface trap states within the energy band must be filled with electrons before the channel can form.

The purpose of this chapter has been to determine the deep oxide trap level distribution (2.4eV) in our devices and the tunneling emission of the trapped electrons at room temperature by employing the EFSE method, and then investigate surface states by using a charge pumping method during hot-carrier stress.

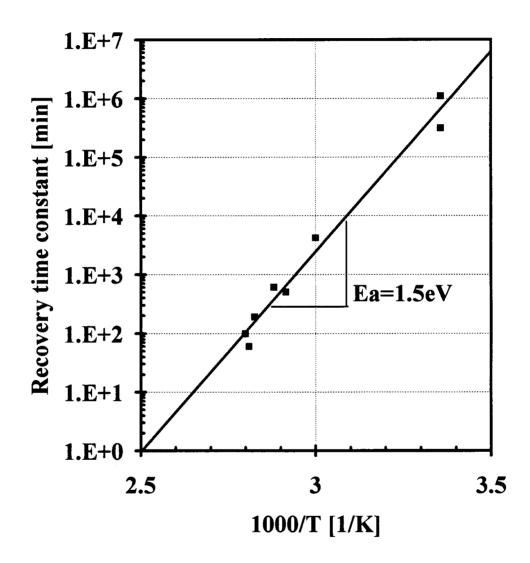

#### 3.2 Thermal Re-Emission

To obtain the energy spectrum of oxide traps the oxide electron traps were created at room temperature by applying a gate voltage of 2.5V and drain voltage of 7.0V at which maximum substrate current was obtained for long time periods (typically two or three days), and then, devices have been tested under various temperatures for recovery to show the thermal re-emission mechanism. The time constant  $(\tau)$  of the thermal re-emission of electrons from oxide traps with zero gate voltage, [91]-[92], was determined as a function of temperature. From the Arrhenius plot of the recovery phase in Fig. 3-1, a 1.5eV activation energy of the trapped electrons in SiO<sub>2</sub> has been obtained. Also, Fig. 3-1 shows that the time constant of recovery (re-emission of oxide trapped electrons) at room temperature is around  $10^5$  minutes, while it is around 600 minutes at  $70^{\circ}$ C.

The mechanism for the self-limiting or saturation [93] in drain current degradation appears to be the thermal re-emission of the trapped electrons in the gate oxide. In fact, self-heating during AC stress causes a detrapping of electrons that leads to the self-limiting or saturation in the drain current.

Figure 3-1 The Arrhenius plot of the drain-to-source current recovery mechanism; thermal emission of trapped electrons.

# 3.3 Tunneling Emission

Figure 3-2 (a) and (b) show the energy band diagrams in order to visualize the internal mechanism of the thermal recovery of trapped electrons under different bias conditions. We have been able to determine that the trap level (thermal activation energy) is 1.5eV below the conduction band in the oxide and its photoionization energy is greater than 2eV by optical stimulation by using a laser light source (HeNe) as shown in Fig. 3-2 (a). It is clear that the trapped electron first makes a transition to the excited state and then tunnels out to the semiconductor. This tunneling mechanism involves some lattice relaxation (Jahn-Teller Effect [94]-[95]). The dynamic Jahn-Teller effects is thought to be the origin of the differences in the thermal activation energy and the photoionization and photoemission energy of an electron bound to a trap. It has also been observed that the devices do not recover with positive gate voltage as shown in Fig. 3-2 (b). Therefore, the recovery and self-limiting mechanism can only be observed under AC stress conditions (Fig. 3-2 (c)) but never under DC stress conditions.

## 3.4 Electric Field Stimulated Emission

The density of oxide trap (Not(t)) after a time t at an oxide field Eox is known as [81];

$$Not(t) = \int_{E_{V}}^{E_{C}} (1 - e^{-\omega \cdot t}) \cdot Dot(Et) \partial Et$$

(3-1),

where Ec and Ev are the conduction and valence energy, respectively. Using the Price-Sah tunneling emission model [81], [91]-[92], the tunneling rate,  $\omega$ , out of a group of traps located below the conduction band in the oxide is given as

Figure 3-2 Tunneling model for re-emission of trapped electrons at different gate bias conditions: (a) thermal recovery with zero or negative gate voltages, (b) the trapped electrons will not recover with positive gate voltages, (c) tunneling (EFSE) from ground state at large negative gate voltages at room temperature, (d) trap energy distribution from Price-Sah emission equations (not to scale), and (e) the projection of oxide trap density as a function of applied oxide electric field and trap energy level.

$$w = \frac{8 \cdot \pi^5}{h^3} \cdot q \cdot m^* \cdot \frac{Eox}{Et} \cdot W^2 \cdot \exp(-2 \cdot \theta)$$

(3-2),

where

$$\theta = \frac{4 \cdot \pi}{3} \cdot \sqrt{2 \cdot m^*} \cdot \frac{\text{Et}^{1.5}}{\text{q} \cdot \text{h} \cdot \text{Eo x}}$$

(3-3),

Eox is the maximum electric field in the gate oxide, Et is the energy level of the oxide electron trap measured from the oxide conduction band, W<sup>2</sup> is the matrix element of the trap potential energy [91], and m\* is the effective mass of carriers in the oxide [81], [96].

$$w = 7.93 \times 10^{10} \cdot \frac{Eox}{Et} \cdot \exp(-68.31 \cdot \frac{Et^{1.5}}{Eox})$$

(3-4).

The density of oxide electron traps at energy, Dot(Et), is then

$$Dot(Et) = \frac{Cox}{q} \cdot \frac{\Delta Vot}{\Delta Et}$$

(3-5),

and the density of state (Dot) of oxide electron traps at energy, Eti, is then determined experimentally;

$$Dot(Et_i) = \frac{Cox}{q} \cdot \frac{\Delta Vg_{i-1} - \Delta Vg_i}{Et_i - Et_{i-1}}$$

(3-6),

where Cox is the gate oxide capacitance per unit area [F/cm<sup>2</sup>], Vot is the voltage shift due to the oxide traps, and Et<sub>i</sub> at each applied electric field (Eox=Vg/Tox) is calculated from Eq. (3-4) at  $\omega t \approx 1$  [81].

Fig. 3-2 (d) shows the trap energy distribution of trapped electrons in the oxide indicating the tunneling rate is a strong function of applied oxide electric field. The relationship between applied oxide electric field and monitored time are shown in Fig. 3-2 (e). It should be pointed out that the limitations of the maximum trap energy spectrum obtained by field-induced re-emission consists of not only the applied electric field but also the monitoring time.

The EFSE method consists of the following steps;

- (1) Hot-carrier stress: the oxide electron traps in the n-channel device are first created at room temperature.

- (2) Field induced re-emission: a negative gate voltage is increased in uniform steps and maintained constant for preset period at each step.

- (3) Measurement: at the end of each step, the thresh-old voltage and gate voltage at constant drain current are monitored.

Fig. 3-3 shows the threshold voltage shifts versus detrapping oxide electric field upon increasing the negative gate voltage in 0.2V steps. As the oxide electric field steps up, the threshold voltage recovers gradually. It is clear that the large numbers of electrons are detrapped at an oxide field of approximately 5.8 MV/cm. Fig. 3-4 shows the energy spectrum for the oxide traps or the density of states of electron traps versus energy that is given by Eq. (3-4). The maximum oxide electron trap density appears at an energy of 2.4eV. However, this trap depth from tunneling is larger than the thermal activation energy of 1.5eV, and the difference is due to the lattice relaxation during thermal activation.

## 3.5 Charge Pumping Current Measurements

Figure 3-5 shows a basic charge pumping measurement set-up. When the transistor is pulled into inversion, the surface becomes deeply depleted and electrons will flow from both the source and drain regions into the channel, where some of electrons will be captured by the interface states. As the gate pulse drives the surface

Figure 3-3 Recovery of the threshold volatge under negative gate voltage.

Figure 3-4 The density of charged oxide electron traps versus trap energy.

Figure 3-5 Schematic diagram of charge-pumping current measurement set-up.

back into accumulation, the mobile charge drifts back to the source and drain under the influence of the reverse bias, but the charges trapped in the interface states will recombine with the majority carriers from the substrate and give rise to a net flow of negative charge into the substrate. The negative charge (Qss) is given by [89]

$$Qss = A \cdot q \int Dit(E) \ \partial E \tag{3-7 (a)},$$

or

$$Qss = A \cdot q^2 \cdot Dit \cdot \Delta \psi_s$$

(3-7 (b)),

where A is the gate area of the transistor [cm<sup>2</sup>], q is the electron charge  $(1.6 \times 10^{-19} \text{ C})$ , Dit(E) is the interface state density at the energy, E, [#/cm<sup>2</sup>/eV], and  $\Delta \psi$ s is the total sweep of the surface potential [V]. The interface states can be described by Dit which is the average interface state density over the range of energy levels swept [#/cm<sup>2</sup>]. When applying repetitive pulses to the gate with frequency (f), this charge (Qss) will give rise to a current in the substrate given by,

$$Icp = f \cdot Qss = f \cdot A \cdot q^2 \cdot Dit \cdot \Delta \psi_s \tag{3-8},$$

where Icp is the charge pumping current. Since Dit is an approximation over the energy range in the bandgap swept by the charge pumping waveform, then,

$$Nit = q \cdot Dit \cdot \Delta \psi_{S} \tag{3-9},$$

where  $q \cdot \Delta \psi_S$ =Eg(si). Thus, the interface state shift ( $\Delta$ Nit) is described by;

$$\Delta Icp = q \cdot f \cdot A \cdot \Delta Nit \tag{3-10}.$$

This simple experimental derivation is quite suitable for the studies of the hot-carrier induced degradation since interface state generation becomes a dominant degradation mechanism due to hot-carrier injection as the gate engineering becomes more sophisticated. Moreover, charge pumping current information on the interface state distribution is important since the interface states consist of both donor-like states (below mid-gap) and acceptor-like states (above mid-gap). In order to determine the distribution of the interface states, the rise time  $(t_f)$  and the fall time  $(t_f)$  of the pulses has to be changed. The interface states at energy level E, Dit(E) are given by [89]

$$Dit(E) = -\frac{t_f}{q \cdot A \cdot k \cdot T} \cdot \frac{\Delta Icp}{\Delta t_f}$$

(3-11)

for a constant rise time with varying falling time, and

$$Dit(E) = -\frac{t_r}{q \cdot A \cdot k \cdot T} \cdot \frac{\Delta lcp}{\Delta t_r}$$

(3-12)

for a constant fall time with varying rising time, where k is the Boltzmann constant  $(1.38\times10^{-23} \text{ [J/K]})$  and T is the ambient temperature [K]. By changing  $t_f$  and  $t_r$ , the distribution of the interface states can be obtained. The charge pumping current measurement has been adopted in the studies of interface state generation due to hot-carrier injection.