#### AN ABSTRACT OF THE THESIS OF

<u>Jianjun J. Zhou</u> for the degree of <u>Doctor of Philosophy</u> in <u>Electrical and Computer Engineering</u> presented on <u>August 18, 1998</u>. Title: <u>CMOS Low Noise Amplifier Design Utilizing Monolithic Transformers</u>.

| Abstract approved: _ | · · · · · · · · · · · · · · · · · · · |                  |  |

|----------------------|---------------------------------------|------------------|--|

| riositact approved.  |                                       | David J. Allstot |  |

Full integration of CMOS low noise amplifiers (LNA) presents a challenge for low cost CMOS receiver systems. A critical problem faced in the design of an RF CMOS LNA is the inaccurate high-frequency noise model of the MOSFET implemented in circuit simulators such as SPICE. Silicon-based monolithic inductors are another bottleneck in RF CMOS design due to their poor quality factor.

In this thesis, a CMOS implementation of a fully-integrated differential LNA is presented. A small-signal noise circuit model that includes the two most important noise sources of the MOSFET at radio frequencies, channel thermal noise and induced gate current noise, is developed for CMOS LNA analysis and simulation. Various CMOS LNA architectures are investigated. The optimization techniques and design guidelines and procedures for an LC tuned CMOS LNA are also described.

Analysis and modeling of silicon-based monolithic inductors and transformers are presented and it is shown that in fully-differential applications, a monolithic transformer occupies less die area and achieves a higher quality factor compared to two independent inductors with the same total effective inductance. It is also shown that monolithic transformers improve the common-mode rejection of the differential circuits.

©Copyright by Jianjun J. Zhou<sup>1</sup>

August 18, 1998

All Rights Reserved

<sup>&</sup>lt;sup>1</sup> Portions of this thesis have been submitted to the IEEE J. Solid-State Circuits for possible publication. Copyright may be transferred from the author to the IEEE without notice.

## CMOS Low Noise Amplifier Design Utilizing Monolithic Transformers

by

Jianjun J. Zhou

## A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

Completed August 18, 1998 Commencement June 1999

| Doctor of Philosophy thesis of Jianjun J. Zhou presented on August 18, 1998                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APPROVED:                                                                                                                                                                                     |

| •                                                                                                                                                                                             |

| Major Professor, representing Electrical and Computer Engineering                                                                                                                             |

|                                                                                                                                                                                               |

| Head of Department of Electrical and Computer Engineering                                                                                                                                     |

|                                                                                                                                                                                               |

| Dean of Graduate School                                                                                                                                                                       |

|                                                                                                                                                                                               |

|                                                                                                                                                                                               |

| I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request. |

| Redacted for Privacy                                                                                                                                                                          |

| Jianjun J. Zhou, Author                                                                                                                                                                       |

#### **ACKNOWLEDGMENTS**

As I look back to my first day at Oregon State, to my first college day at Shanghai Jiao Tong University, to my first elementary-school day in my mother's arms, I finally realize how truly fortunate I am. I am not sure if such a couple of pages, appearing in the front of my thesis with the same style and format, could possibly express my thankful and sincere heart. So many terrific individuals have contributed to the education I have received throughout the years which made it possible!

First and foremost, I would like to thank my major advisor Professor David J. Allstot for his encouragement, patience, and support of the work and of my education. I hope he realizes how much I gained from his excellent teaching and great insight into almost every problem an IC engineer could possibly have encountered.

Thanks are due Professor Kartikeya Mayaram, Professor Virginia Stonick, Professor Andreas Weisshaar, and Professor Dwight Bushnell for taking time to serve on my committee, for reviewing the thesis, and for helpful guidance. Thanks also go to Professor Un-Ku Moon, for many enlightening and enjoyable discussions. In addition, I would like to thank many teachers I have had over the years for providing many helpful and engaging lectures and for their devotion to Electrical and Computer Engineering.

I would especially like to thank Richard Li, Enrique Ferrer, and Georgia Salgado of Motorola Inc., Ft. Lauderdale, Florida, for providing useful discussions and test and measurement assistance. Helpful discussions and technical exchanges with fellow researchers and graduate students Brian Ballweber, Hairong Gao, Ravi Gupta, Anping Liu, Hiok-Hion Ng, Hiok-Tiaq Ng, Yihai Xiang, and Ramsin Ziazadeh of Oregon State University are also deeply appreciated.

Special thanks to Wenjun Su and his wife Wenjing Zhang, Rugang Ding and his wife Lian Song, Yun Ge, Jeff Ward, Yunteng Huang, Bo Zhang, Bo Wang, and Haiqing Lin for their constant help and encouragement throughout my years at Oregon State University. Much thanks go to my old high-school and JiaoDa buddies Haiwen Xi, Xiaojie Yuan, Gong Jun, Xiao Bei, Lu Da, Omega, Zhang Zhenfan, Li Zuxin, and Lei Ming who have been providing numerous laughs and good times since 10+ years ago.

No words, however, could possibly be enough to express my thanks to my family: my great parents Zhou Wanyao and Yi Xueying, my little brother Zhou Jianmin, and my best friend and wife Qin, for their love and guidance, for supporting me through every step in my life. And I am here to say: I did it and it is for you!

# TABLE OF CONTENTS

|            |                                                                                                                                    | <u>Page</u> |

|------------|------------------------------------------------------------------------------------------------------------------------------------|-------------|

| CHAPTER 1. | GENERAL INTRODUCTION                                                                                                               | 1           |

| 1.1        | Scope                                                                                                                              | 1           |

| 1.2        | Wireless Receivers                                                                                                                 | 1           |

| 1.3        | Integration of CMOS LNA's                                                                                                          | 4           |

| 1.4        | Thesis Outline                                                                                                                     | 5           |

| CHAPTER 2. | NOISE CHARACTERISTICS OF MOS TRANSISTORS                                                                                           | 8           |

| 2.1        | Introduction                                                                                                                       | 8           |

| 2.2        | Channel Thermal Noise                                                                                                              | 9           |

| 2.3        | Induced Gate Current Noise                                                                                                         | 11          |

| 2.4        | Resistive Gate Thermal Noise                                                                                                       | 13          |

| 2.5        | Additional Noise Sources                                                                                                           | 16          |

|            | <ul><li>2.5.1 Flicker (1/f) Noise and Shot Noise</li><li>2.5.2 Substrate Resistance Noise</li></ul>                                |             |

| 2.6        | Small-Signal Noise Circuit Model                                                                                                   | 19          |

| 2.7        | Modified Noise Simulation in SPICE                                                                                                 | 22          |

| CHAPTER 3. | PRINCIPLES OF CMOS LNA DESIGN                                                                                                      | 25          |

| 3.1        | Basic Concepts                                                                                                                     | 25          |

|            | <ul><li>3.1.1 Noise Factor and Noise Figure</li><li>3.1.2 Nonlinearity</li></ul>                                                   | 25<br>26    |

| 3.2        | CMOS LNA Architectures                                                                                                             | 31          |

|            | <ul> <li>3.2.1 Single-Transistor CMOS LNA</li> <li>3.2.2 LC Tuned CMOS LNA</li> <li>3.2.3 Inductive Source Degeneration</li> </ul> | 36          |

| 3.3        | Design Considerations of CMOS LNA                                                                                                  | 44          |

|            | 3.3.1 Optimization of Device Parameters                                                                                            |             |

| CHAPTER 4. | SILICON-BASED MONOLITHIC INDUCTORS                                                                                                 | 51          |

| 4.1        | Implementations of Monolithic Inductors                                                                                            | 52          |

# **TABLE OF CONTENTS (Continued)**

|            |                                                             |                                                                                                                                                                                           | <u>Page</u>    |

|------------|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|            | 4.1.1<br>4.1.2<br>4.1.3                                     | Active Inductors                                                                                                                                                                          | 53             |

| 4.2        | Model                                                       | ling of Spiral Inductors                                                                                                                                                                  | 56             |

|            | 4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.2.6          | Scalable Circuit Model Self- and Mutual Inductance Resistive Losses Parasitic Capacitances Substrate Parasitics Summary                                                                   | 59<br>64<br>71 |

| 4.3        | Induct                                                      | or Circuit Performance                                                                                                                                                                    | 76             |

|            | 4.3.1<br>4.3.2                                              | Compact Circuit Model  Quality Factor and Self-Resonant Frequency                                                                                                                         | 76<br>78       |

| 4.4        | Altern                                                      | ative Spiral Inductor Designs                                                                                                                                                             | 82             |

|            | 4.4.1<br>4.4.2<br>4.4.3<br>4.4.4<br>4.4.5                   | Suspended Spiral Inductors Multilevel Spiral Inductors Stacked Spiral Inductors Spiral Inductors with Active Compensation Spiral Inductors with Ground Shields                            |                |

| 4.5        | Concl                                                       | usions                                                                                                                                                                                    | 89             |

| CHAPTER 5. | SILIC                                                       | ON-BASED MONOLITHIC TRANSFORMERS                                                                                                                                                          | 90             |

| 5.1        | Introd                                                      | uction to Monolithic Transformers                                                                                                                                                         | 90             |

| 5.2        | Model                                                       | ling of Spiral Transformers                                                                                                                                                               | 93             |

|            | 5.2.1<br>5.2.2<br>5.2.3                                     | Scalable Circuit Model  Compact Circuit Model  Quality Factor and Self-Resonant Frequency                                                                                                 | 97             |

| 5.3        | Optim                                                       | ization of Spiral Transformers and Inductors                                                                                                                                              | 101            |

|            | 5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5<br>5.3.6<br>5.3.7 | Circuit Performance v/s Frequency Effects of Number of Spiral Turns Effects of Metal Width Effects of Trace Spacing Effects of Spiral Center Spacing Simulations v/s Measurements Summary |                |

| 5.4        | Compa                                                       | arison Between Transformers and Inductors                                                                                                                                                 | 116            |

# **TABLE OF CONTENTS (Continued)**

|            |                                           |                                                                                            | Page              |

|------------|-------------------------------------------|--------------------------------------------------------------------------------------------|-------------------|

|            | 5.4.1<br>5.4.2<br>5.4.3                   | Simulation Results  Differential-Mode Circuit Performance  Common-Mode Circuit Performance | 117               |

| 5.5        | Concl                                     | usions                                                                                     | 121               |

| CHAPTER 6. | CIRC                                      | UIT IMPLEMENTATION AND EXPERIMENTAL RESULTS                                                | . 122             |

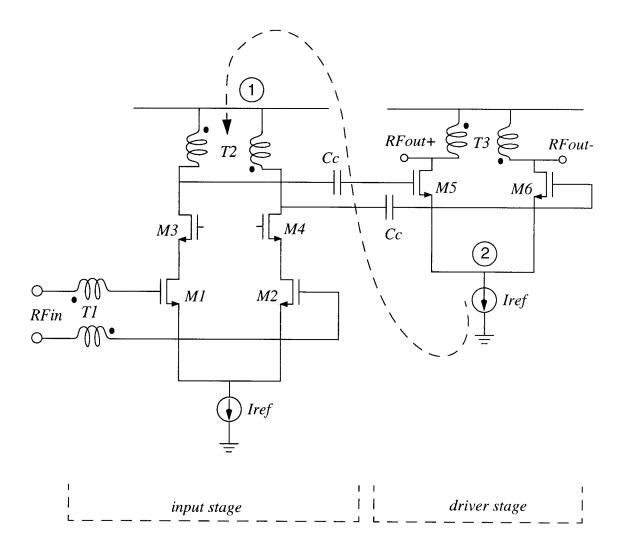

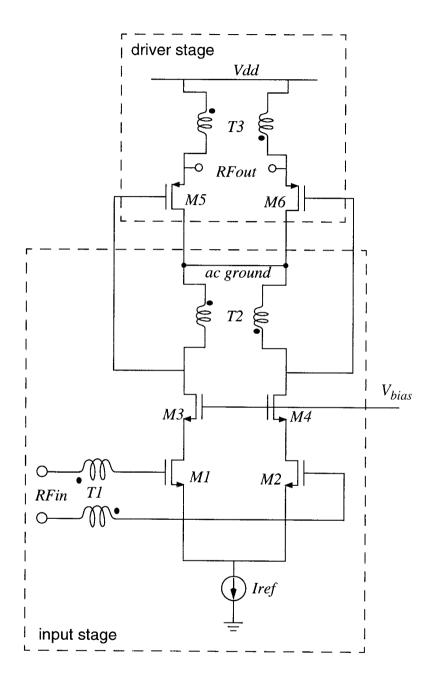

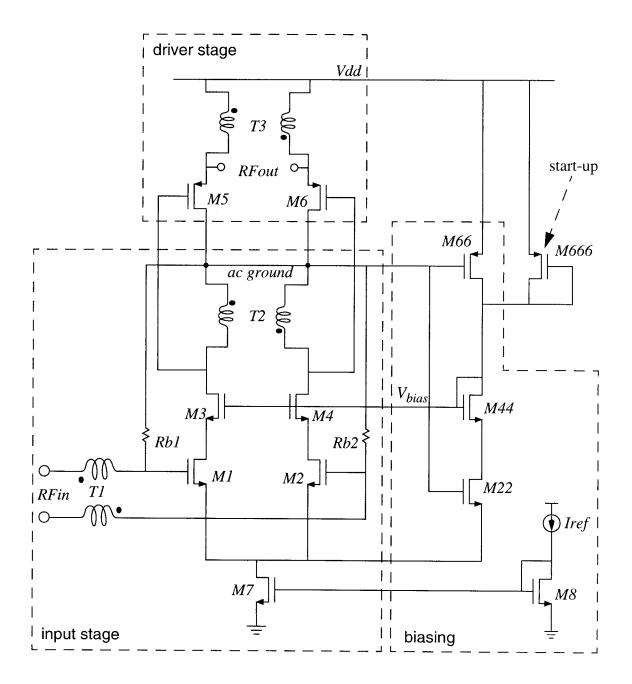

| 6.1        | Comp                                      | lete Circuit Implementation                                                                | 122               |

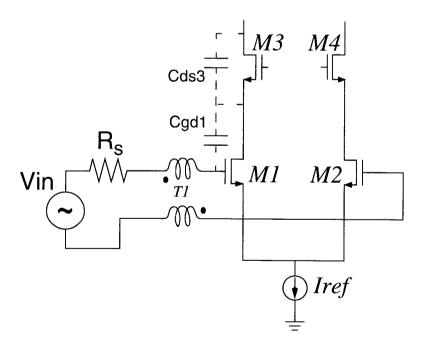

|            | 6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5 | Basic Input Circuit Low Power Techniques Biasing Circuit Device Parameters Layout Issues   | 124<br>128<br>130 |

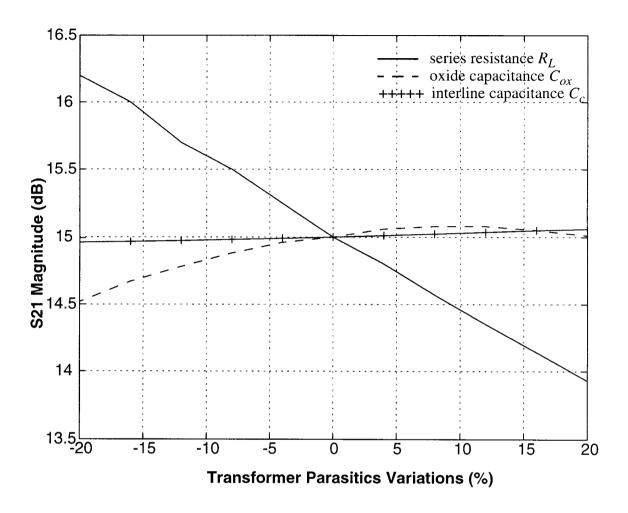

| 6.2        | Simula                                    | ation Results and Sensitivity Analysis                                                     | 134               |

| 6.3        | Experi                                    | mental Results                                                                             | 136               |

| CHAPTER 7. | CONC                                      | CLUSIONS                                                                                   | 143               |

| BIBLIOGRAI | PHY                                       |                                                                                            | 147               |

| APPENDICES | s                                         |                                                                                            | 155               |

| Appen      | dix A                                     | Matlab Programs for Inductor and Transformer Simulations                                   | 156               |

| Appen      | dix B                                     | Unity-Gain Frequencies of RF MOSFETs                                                       | 173               |

# LIST OF FIGURES

| <u>Figure</u> | <u>P</u>                                                                                         | age  |

|---------------|--------------------------------------------------------------------------------------------------|------|

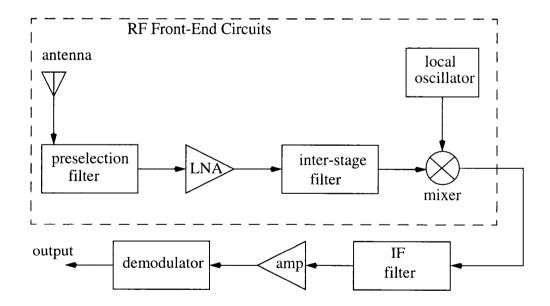

| 1.1           | Block diagram of superheterodyne receiver.                                                       | 3    |

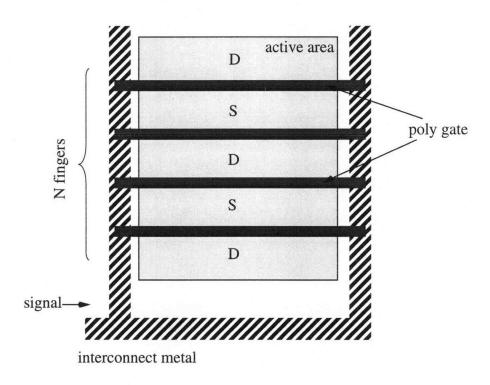

| 2.1           | Finger structure of a MOS transistor with large W/L.                                             | . 14 |

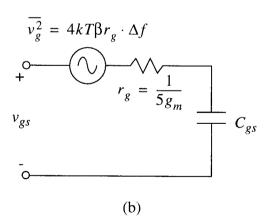

| 2.2           | Representations of the induced gate current noise in MOS transistor.                             | . 20 |

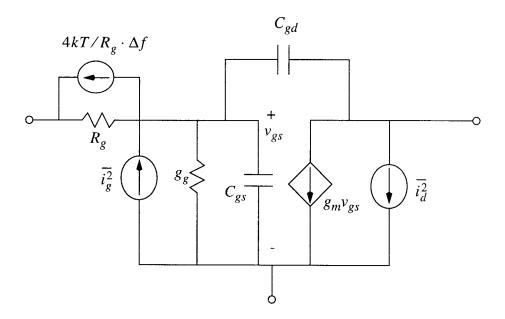

| 2.3           | Small-signal noise circuit of a MOS transistor.                                                  | . 22 |

| 3.1           | Graphical interpretation of the nonlinearity of an amplifier.                                    | . 30 |

| 3.2           | Single-transistor CMOS LNA.                                                                      | . 33 |

| 3.3           | LC tuned CMOS LNA.                                                                               | . 37 |

| 3.4           | LC tuned CMOS LNA with inductive source degeneration.                                            | . 42 |

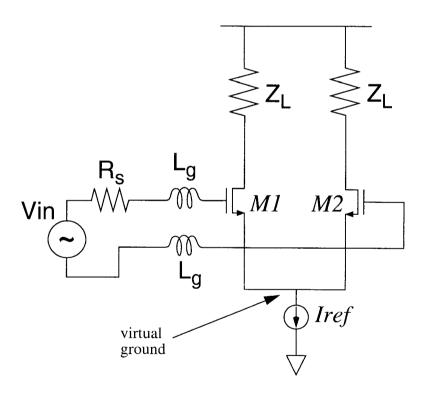

| 3.5           | Single-ended and fully-differential CMOS LNA's.                                                  | . 49 |

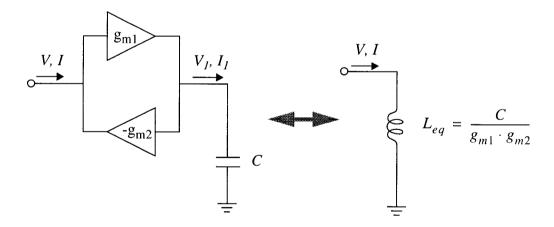

| 4.1           | General implementation of an active inductor.                                                    | . 52 |

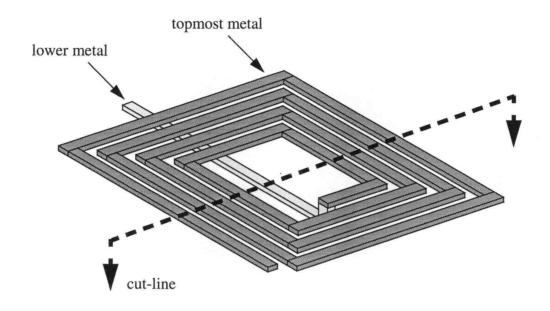

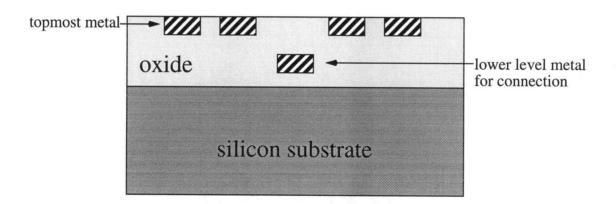

| 4.2           | Layout and cross-section of a square spiral inductor.                                            | . 55 |

| 4.3           | Lumped-element circuit model for a microstrip line.                                              | . 57 |

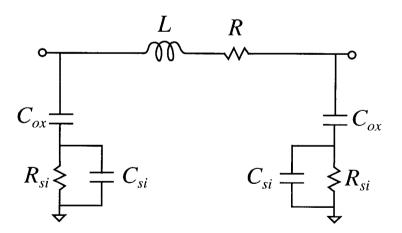

| 4.4           | Scalable lumped-element circuit model for a spiral inductor.                                     | . 58 |

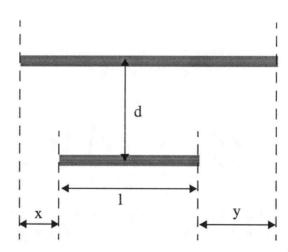

| 4.5           | Two parallel microstrip lines.                                                                   | . 60 |

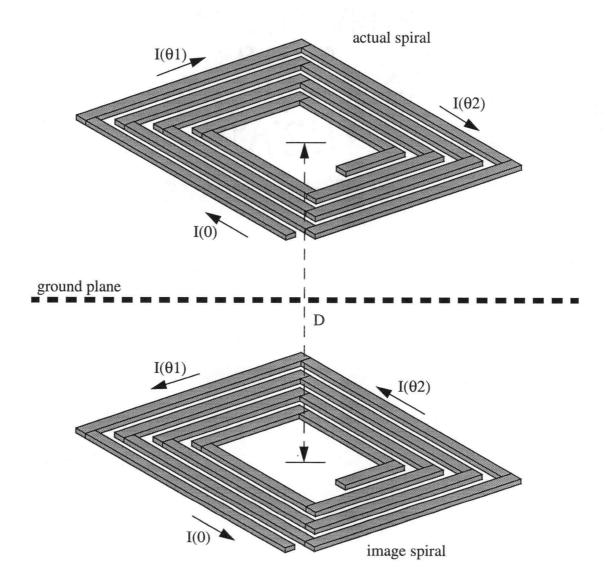

| 4.6           | Effects of the image spiral and the phase shift in current.                                      | . 62 |

| 4.7           | Modified lumped-element circuit model for a microstrip line                                      | . 64 |

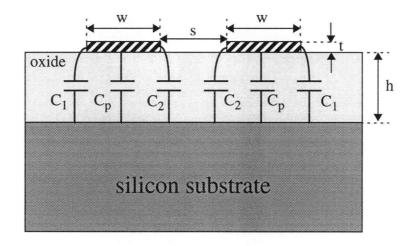

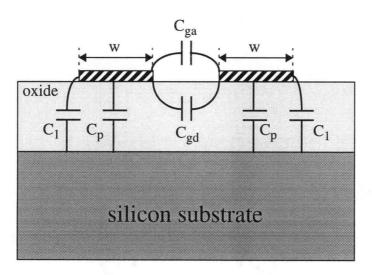

| 4.8           | Decomposition of the total capacitance of coupled microstrip lines.  (a) Even-mode. (b) Odd-mode | . 68 |

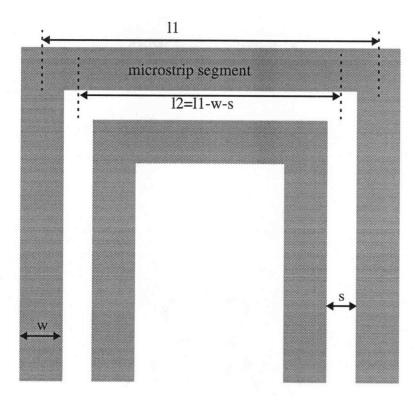

| 4.9           | Effective microstrip lengths for the calculation of various capacitances                         | . 72 |

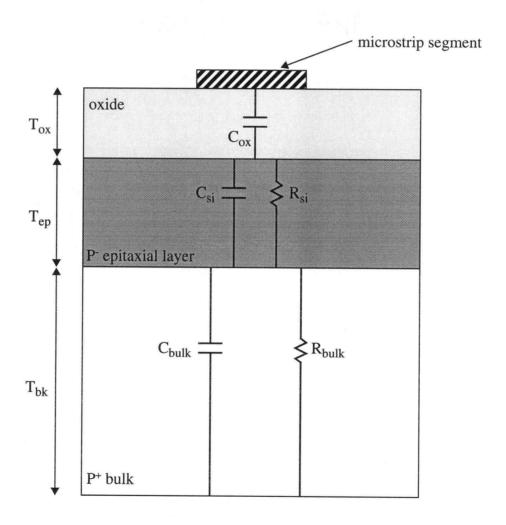

| 4.10          | Schematic cross-section of the substrate in CMOS technology.                                     | . 73 |

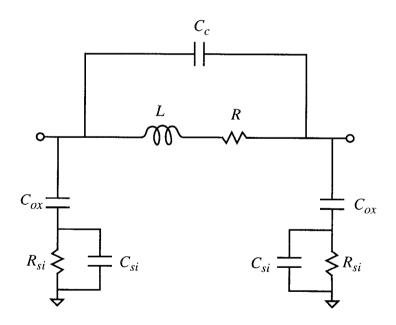

| 4.11          | Compact lumped-element circuit model for a spiral inductor.                                      | . 77 |

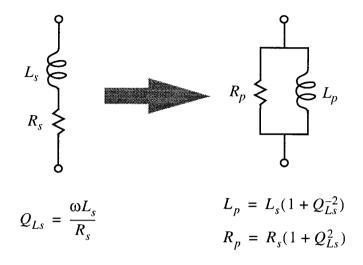

| 4.12          | Series/parallel impedance transformation formulas. (a) RL network. (b) RC network.               | . 80 |

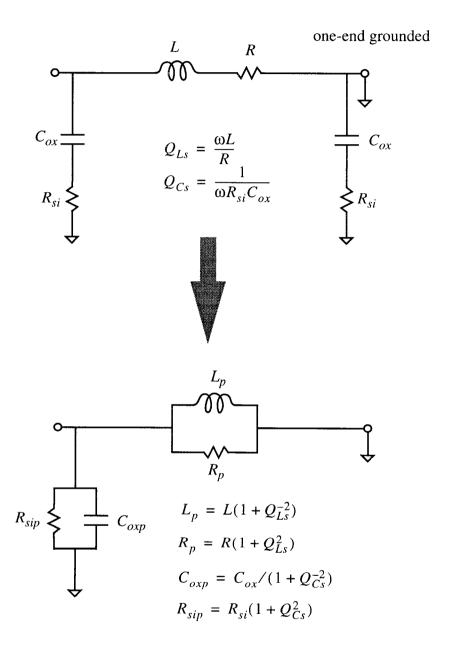

| 4.13          | Equivalent circuit of an inductor's compact circuit model.                                       | . 81 |

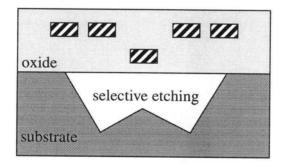

| 4.14          | Cross-section of a suspended spiral inductor.                                                    | . 83 |

# **LIST OF FIGURES (Continued)**

| <u>Figure</u> |                                                                                              | <u>Page</u> |

|---------------|----------------------------------------------------------------------------------------------|-------------|

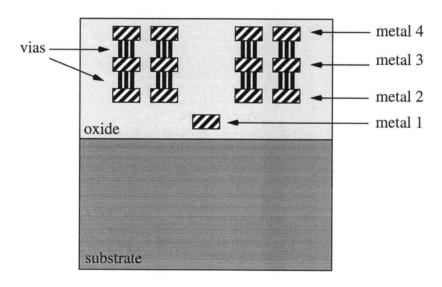

| 4.15          | Cross-section of a multilevel spiral inductor in a 4-metal process                           | 85          |

| 4.16          | A stacked spiral inductor.                                                                   | 86          |

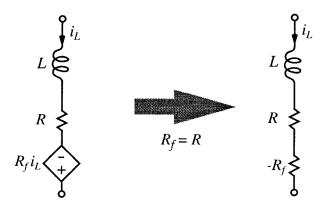

| 4.17          | Spiral inductors with active compensation.                                                   | 87          |

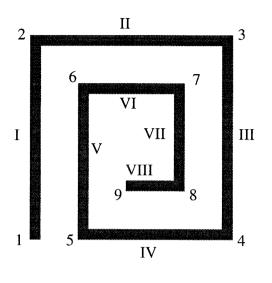

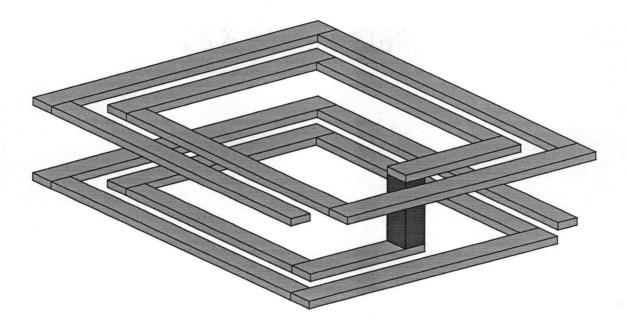

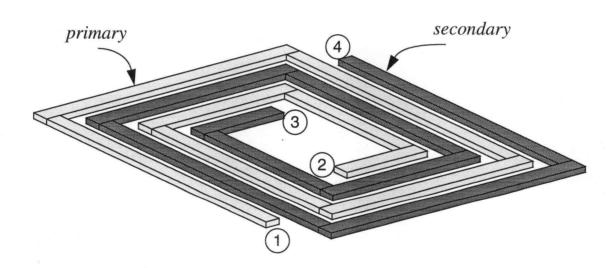

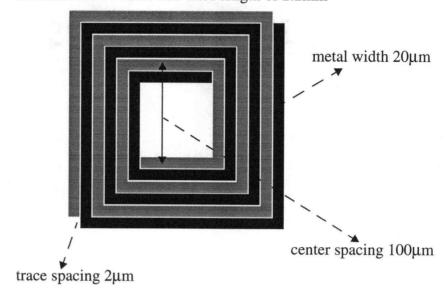

| 5.1           | Layout of a transformer consisting of two identical spiral inductors                         | 92          |

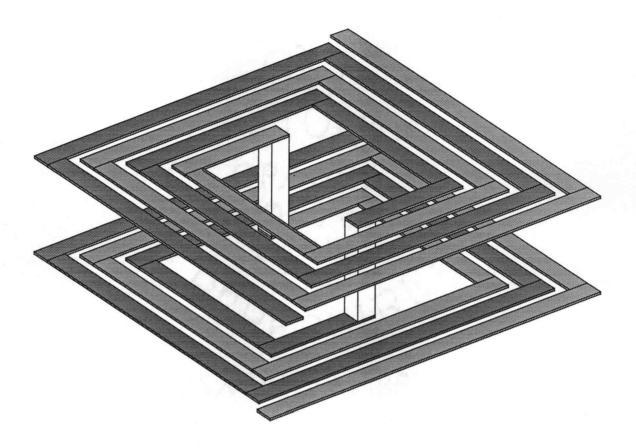

| 5.2           | A stacked spiral transformer.                                                                | 93          |

| 5.3           | Lumped-element circuit model for two coupled microstrip lines.                               | 94          |

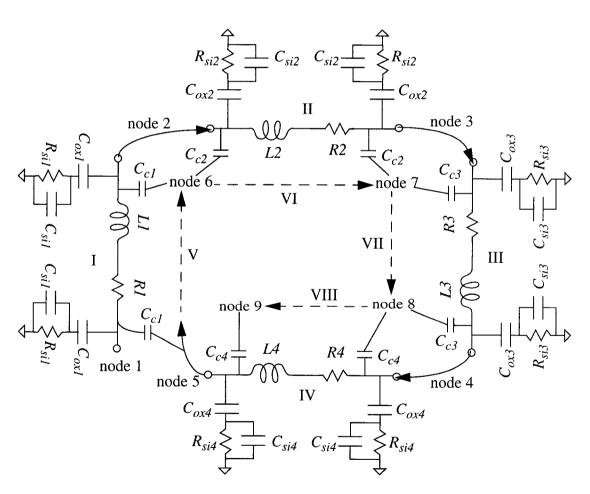

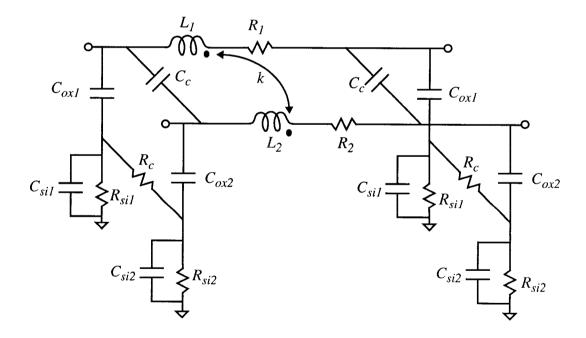

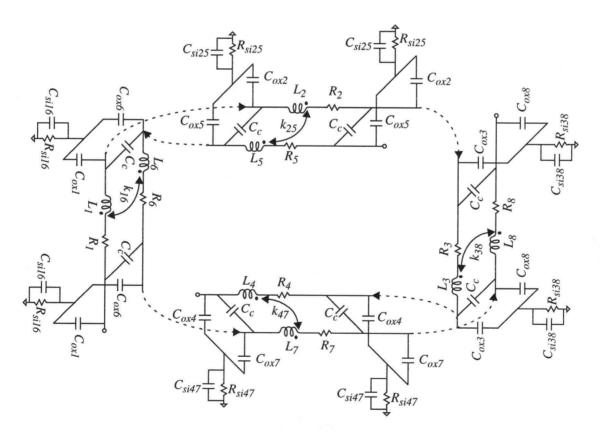

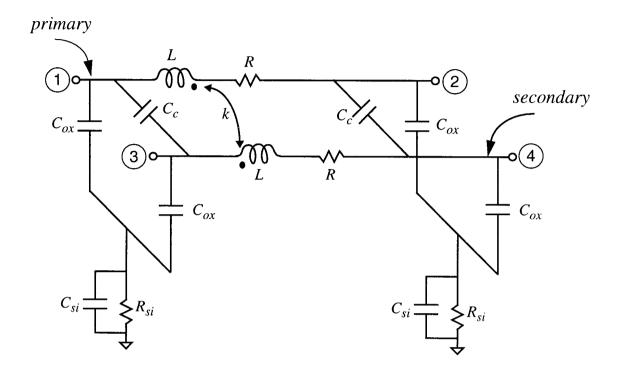

| 5.4           | Scalable lumped-element circuit model for a spiral transformer.                              | 96          |

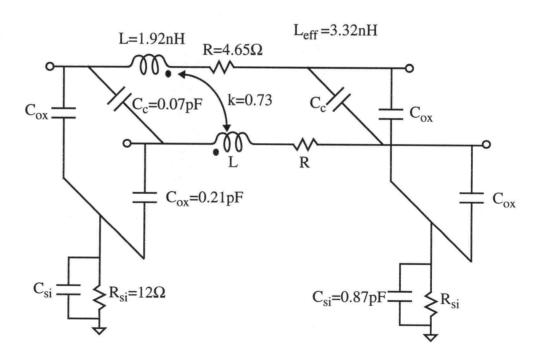

| 5.5           | Compact circuit model for a spiral transformer.                                              | 98          |

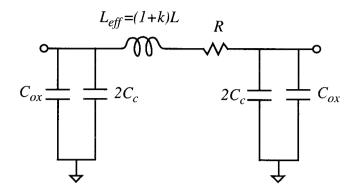

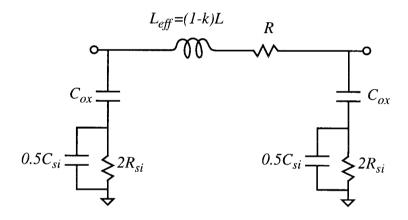

| 5.6           | Equivalent half-circuits for a spiral transformer in (a) differential-mode; (b) common-mode. | 99          |

| 5.7           | A six-turn spiral transformer at 900MHz.                                                     | . 104       |

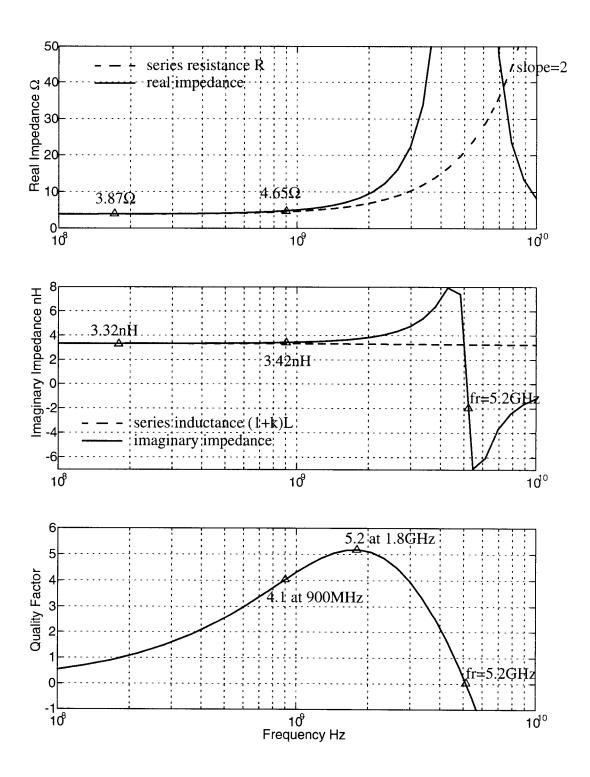

| 5.8           | Simulated circuit performance of the primary.                                                | . 105       |

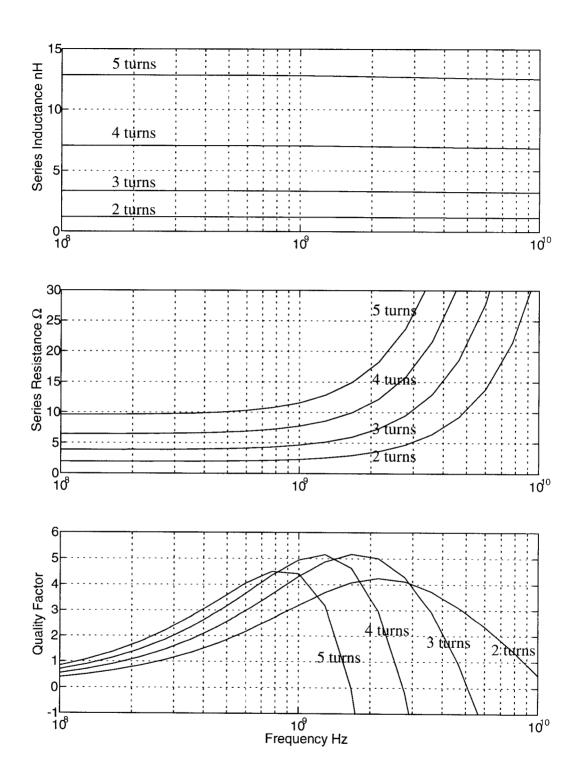

| 5.9           | Effects of the number of spiral turns.                                                       | . 107       |

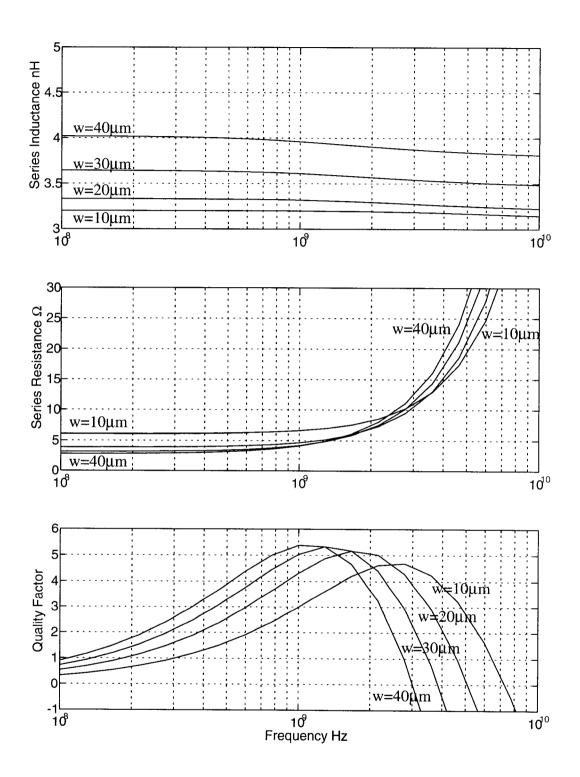

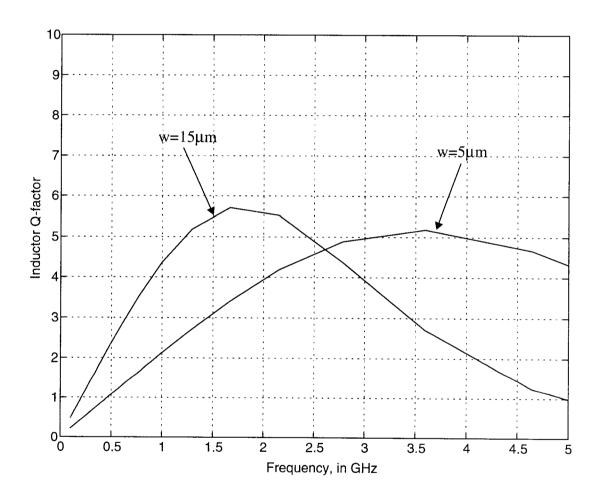

| 5.10          | Effects of the metal width.                                                                  | . 109       |

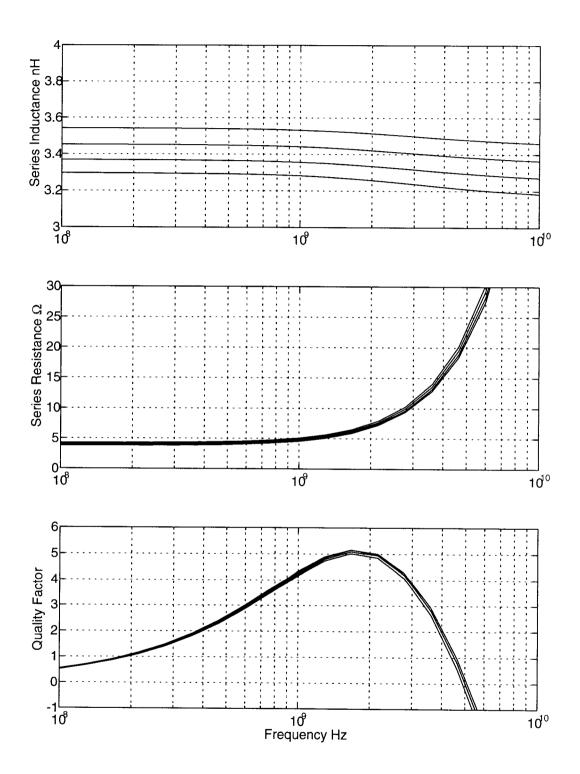

| 5.11          | Effects of the trace spacing.                                                                | . 111       |

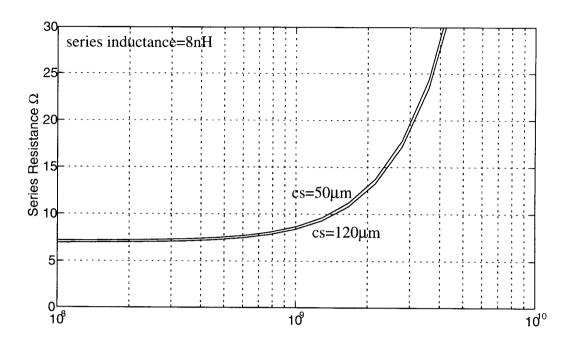

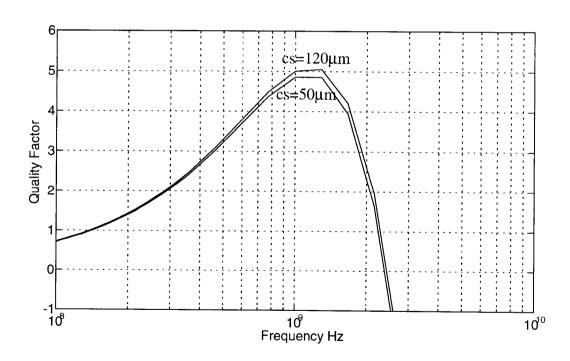

| 5.12          | Effects of the spiral center spacing.                                                        | . 113       |

| 5.13          | Simulated Q-factor for two inductors fabricated in a 0.8-µm BiCMOS process.                  | . 114       |

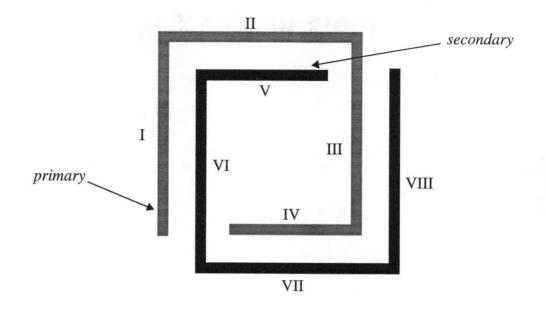

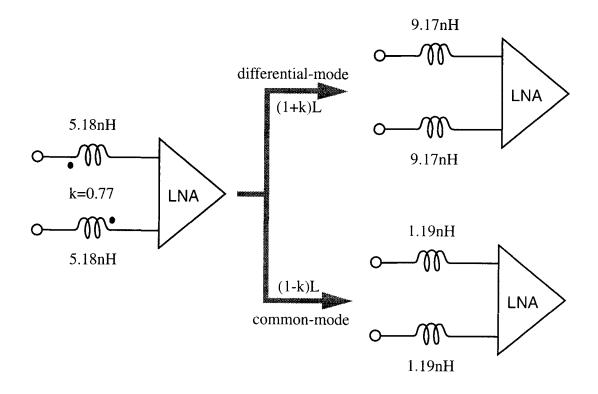

| 5.14          | A spiral transformer in a differential LNA circuit.                                          | . 120       |

| 6.1           | Cascode input circuit of the LC tuned CMOS LNA.                                              | . 123       |

| 6.2           | Two-stage LC tuned CMOS LNA.                                                                 | . 125       |

| 6.3           | Stacked LC tuned CMOS LNA.                                                                   | . 127       |

| 6.4           | Complete circuit schematic of the LC tuned CMOS LNA.                                         | . 129       |

| 6.5           | Sensitivity simulations of the LC tuned CMOS LNA.                                            | . 136       |

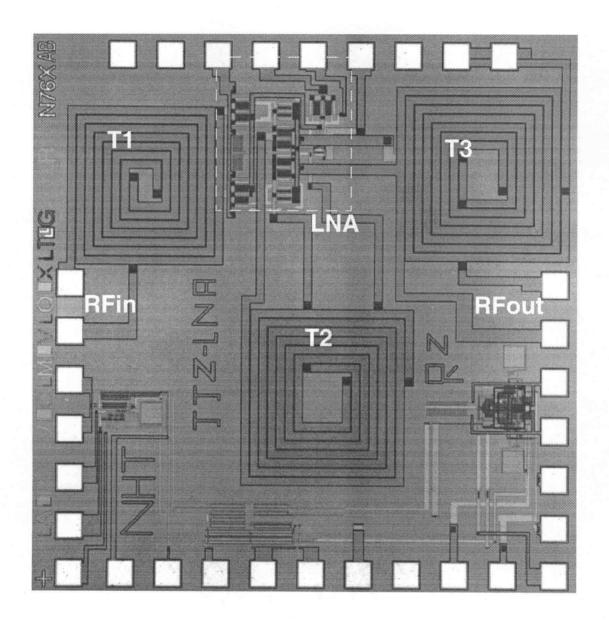

| 6.6           | Chip micrograph of the CMOS LNA.                                                             | . 137       |

# **LIST OF FIGURES (Continued)**

| <u>Figure</u> |                                      | <u>Page</u> |

|---------------|--------------------------------------|-------------|

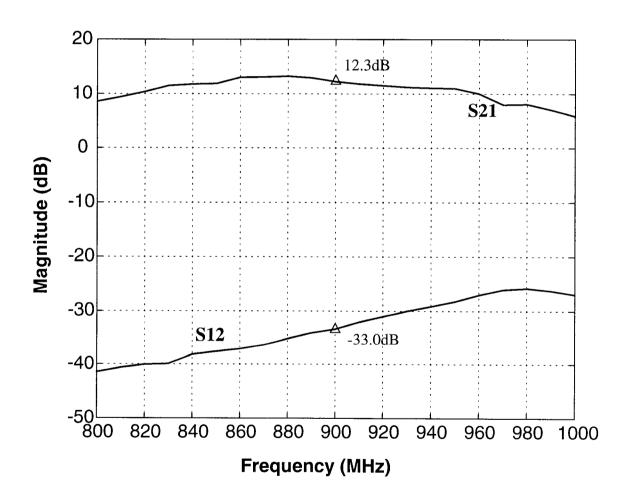

| 6.7           | S21 and S12 measurements.            | 139         |

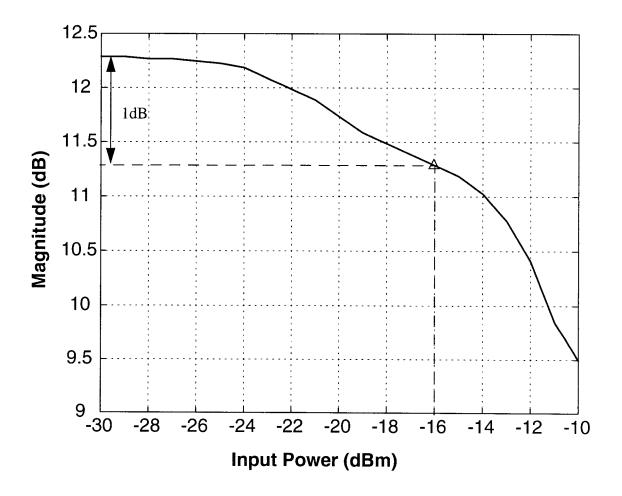

| 6.8           | 1-dB compression point measurements. | 140         |

# LIST OF TABLES

| <u>Table</u> | <u>Page</u>                                                           |

|--------------|-----------------------------------------------------------------------|

| 5-1          | Process parameters of a 3-metal CMOS technology                       |

| 5-2          | Common geometric layout parameters for transformers and inductors 118 |

| 5-3          | Simulation results of three transformers (primary only)               |

| 5-4          | Simulation results of three inductors                                 |

| 5-5          | Differential-mode circuit performance                                 |

| 6-1          | Design parameters of the LNA components                               |

| 6-2          | Simulation Results of Transformer- and Inductor-Tuned CMOS LNA's 134  |

| 6-3          | Measured and Simulated LNA performance                                |

# CMOS LOW NOISE AMPLIFIER DESIGN UTILIZING MONOLITHIC TRANSFORMERS

#### **CHAPTER 1. GENERAL INTRODUCTION**

#### 1.1 Scope

With the recent proliferation of wireless communication applications, there is an extensive effort to develop low cost, highly integrated CMOS RF circuits which meet the performance requirements of current and future communication system standards. This research is to support the development and implementation of low-power CMOS RF low noise amplifiers (LNA), which are a critical building block at the front-end of wireless communication systems.

The primary goal of this research is to design a fully-integrated 900MHz CMOS LNA with 15-20mW power consumption using a 3V power supply. To accomplish this goal, the high-frequency noise characteristics of the MOS transistor, high quality passive elements, and low-power circuit techniques have been exploited.

#### 1.2 Wireless Receivers

The capability of electromagnetic waves to provide wireless distant communications has been a major factor in the explosive growth of communications during the twentieth century. In 1862, Maxwell predicted the existence of electromagnetic waves which was proven by Hertz 26 years later. The first wireless receiver was probably built with a tuned antenna and some iron dust at the end to observe a tiny spark generated by activating the transmitter [1]. Then with the advent of vacuum tube (replaced quickly by

transistor after its invention in 1947), active amplifiers were introduced into receivers to improve system sensitivity and selectivity (tuned amplifiers). Frequency translation schemes were employed thereafter to build so-called homodyne (coherent) and heterodyne (non-coherent) receivers which provided a potential improvement and cost reduction over previous receivers. Soon after that, the superheterodyne receiver was invented by Armstrong (this "poor" guy spent half of his life in the court to fight for his royalties and concluded his life with a suicide [2]).

The superheterodyne receiver makes use of the heterodyne principle of mixing an incoming signal with a local oscillator (LO) signal in a nonlinear element called a mixer (Fig. 1.1). However, rather than synchronizing the frequencies, the superheterodyne receiver uses a LO frequency offset by a fixed intermediate frequency (IF) from the desired signal. Although it does introduce a problem of spurious responses not present in other receiver types, the superheterodyne receiver predominates in most modern wireless communication applications in that it offers many advantages:

- i) RF tuning can be done by varying the LO frequency, which eases the design of bandpass filters (BPF) and amplifiers at the RF front-end.

- ii) Channel selectivity is accomplished at the IF section where narrow high-order filtering is more easily achieved.

- iii) Amplification can be provided primarily at lower frequencies where high gain is generally more economical.

As shown in Fig. 1.1, the RF signal is fed from the antenna to a preselection filter which serves to attenuate the image signal and the undesired signals outside the service band. Insertion loss of the filter decreases the sensitivity of receiver and thus the filtering is often broken into two or more parts with intervening low noise amplifiers (LNA) to

provide sufficient selectivity, while minimizing the effects of the filter loss on noise performance. The gain of the low noise amplifier is needed to overcome the filter loss but must not be too high to retain system dynamic range. Next, the local oscillator converts the RF signal to the fixed IF at the mixer. The output from the mixer is applied to the IF filter for channel selectivity and then to the IF amplifier to obtain a suitable power level for demodulation.

There are several alternative receiver architectures worthy of mention [3]. A double-conversion superheterodyne receiver converts the incoming RF signal first to an IF

Figure 1.1: Block diagram of superheterodyne receiver.

at a relatively high frequency, and then to a lower second IF. This architecture further relaxes the bandpass filter design at the cost of more circuit complexity and power consumption. An ultra-low IF receiver uses carefully selected RF and LO frequencies so that the image signal falls within an unused portion of the RF spectrum. As a result, no image rejection bandpass filter is required. The homodyne (zero-IF) receiver, re-claiming its lost popularity in low-power integrated design, eliminates the need for image-rejection bandpass filters in that it makes the image signal exactly the same as the desired signal.

## 1.3 Integration of CMOS LNA's

A typical wireless receiver is required to perform selection, amplification and demodulation of received signals. The noise factor F (called noise figure NF if in decibel) of a receiver is a measure of its ability to amplify and demodulate weak signals and can be defined as the ratio of the input signal-to-noise-ratio (SNR) to the output signal-to-noise-ratio (SNR)

$$F = SNR_{in}/SNR_{out} (1.1)$$

and the overall noise factor of a cascade system is given by

$$F = F_1 + \frac{F_2 - 1}{G_1} + \dots + \frac{F_k - 1}{G_1 G_2 \dots G_{k-1}}$$

(1.2)

where  $F_k$  and  $G_k$  are the noise factor and power gain, respectively, of the kth block in the system.

From Equation (1.2), it is clear that system noise performance depends primarily on the first function block which is the filtering block including the low noise amplifier as shown in Fig. 1.1. The minimum signal level that can be detected in a wireless receiver is the required output SNR (determined by the bit error rate in the following DSP block) plus the system noise floor which is equal to the sum of the input noise power in decibels and the system noise figure. Therefore, the noise performance of the LNA is crucial in achieving high system sensitivity for a wireless receiver.

Design issues surrounding integrated CMOS receiver have been addressed in many articles [3]-[6]. While fine-line CMOS technology easily provides high frequency active devices for use in RF applications (e.g., 800MHz-2.4GHz), high quality passive components, especially inductors, present serious challenges to silicon integration. Several previous RF CMOS low noise amplifiers have reported impressive results [7]-[12]. However, since many of the CMOS implementations require inductors for narrowband tuning or matching, off-chip inductors have often been used owing to the relatively poor quality of monolithic inductors. In addition, the existing noise model for the MOS transistor in standard circuit simulators, such as SPICE, is insufficient to accurately predict the circuit noise performance at high frequencies. A lack of comprehensive understanding of the noise characteristics of MOS transistors at high frequencies is still an obstacle to the development and optimization of CMOS RF LNA designs [11].

Efforts towards the full integration of a CMOS LNA are described in this thesis. The inductance required to implement a fully-differential CMOS LNA is provided by monolithic transformers, instead of monolithic inductors, to achieve better circuit performance [13]. High frequency noise characteristics of the MOS transistor are investigated and a compact noise model is developed for circuit simulation. In addition, low-power circuit techniques have also been investigated.

## 1.4 Thesis Outline

High-frequency noise characteristics of the MOS transistor are investigated in Chapter 2. Various noise sources are carefully studied. The channel thermal noise and the induced gate current noise are integrated into a compact noise circuit model for the MOS transistor used for hand analysis and SPICE simulations.

Basic principles of CMOS LNA design are presented in Chapter 3. Two measures of CMOS LNA circuit performance, i.e., noise figure and linearity, are discussed in detail. Basic architectures of CMOS LNA's are analyzed based on the compact noise circuit model developed in Chapter 2. The LC tuned CMOS LNA is found to have the best noise performance. Finally, design considerations of CMOS LNA's are discussed and design guidelines and procedures for CMOS LNA optimization are summarized.

Throughout the investigation of CMOS LNA architectures in Chapter 3, the importance of high-quality monolithic inductors is illustrated. Chapter 4 thus turns to the study of silicon-based monolithic inductors. First, a review of various implementations of monolithic inductors is given. Detailed analysis and modeling of the square spiral inductors is then described. The inductor circuit model developed can be used directly in an IC simulator, such as SPICE. Based on the circuit model, the inductor performance is analyzed and formulated to facilitate hand analysis. In addition, some alternative designs of spiral inductors are also discussed. It is concluded that the quality factor and self-resonant frequency of a monolithic spiral inductor are mainly limited by the parasitic series resistance and shunt capacitance.

In Chapter 5, a brief introduction to monolithic spiral transformers on silicon substrate is given first, followed by a detailed description of the characterization and modeling of a transformer consisting of two identical spiral inductors. Design guidelines for transformer optimization are then described, based on extensive simulation results. Computer simulation is also conducted to compare circuit performance between various transformers and inductors. When utilized in a differential application, it is found that a

transformer occupies less die area and thus has less parasitic series resistance and shunt capacitance, compared to two independent inductors with the same equivalent differential-mode inductance. As a consequence, the quality factor and the self-resonant frequency are improved. The improvements become more significant as the required equivalent inductance increases. In addition, a transformer provides additional common-mode rejection for the differential circuits.

Taking advantage of the transformers identified in Chapter 5, a 900MHz fully-differential CMOS LNA design is implemented and experimental results are presented in Chapter 6. The complete circuit and layout description are illustrated. The LNA which is fully integrated in a standard digital 0.6µm CMOS technology utilizes three monolithic transformers for on-chip tuning networks. Bias current re-use is used to reduce power dissipation and process-, voltage-, and temperature-tracking biasing techniques are employed. This chapter concludes with the discussion of experimental results.

Finally, conclusions are presented in Chapter 7.

#### CHAPTER 2. NOISE CHARACTERISTICS OF MOS TRANSISTORS

#### 2.1 Introduction

The sensitivity of a wireless receiving system is mainly determined by the noise performance of the front-end circuits, specially, the low noise amplifier (LNA). Since the noise performance of an integrated circuit is determined by the noise behavior of the active components, it is important to understand the noise characteristics of MOS transistors in order to analyze and optimize CMOS LNA designs.

Conventional noise models for CMOS devices are deficient for RF circuit design. At high frequencies, the induced gate current noise is comparable to the channel thermal noise in MOS transistors. Additionally, gate resistance may contribute significant noise in a large transistor if it is not properly laid out. Furthermore, in submicron MOS transistors, there are many second-order noise mechanisms, such as hot carrier effects and substrate coupling, which may result in a large amount of excess device noise. Unfortunately, these effects are poorly modeled in the existing commercially available CAD tools such as HSPICE (version H96.1).

A detailed investigation of MOS noise characteristics is given in this chapter. All major noise mechanisms are studied and a compact noise circuit model of MOS transistors at high frequencies is developed based on previously reported research results. The noise model is then integrated with HSPICE, using a popular script program (Awk/Perl), for simulation of the noise performance of CMOS RF circuits.

## 2.2 Channel Thermal Noise

Channel thermal noise which is one of the most significant noise sources in a MOS transistor has been well studied and documented [14]-[15]. It is caused by a random motion of free carriers in the conductive channel, analogous to that in normal resistors. The current flowing between the drain and the source terminals in a MOS transistor is based on the existence of a conductive channel formed by an inversion layer. If the drain-source voltage  $V_{DS} = 0V$ , this conductive channel can be treated as a normal resistance. In such a case, the thermal noise drain current  $\overline{i_d^2}$  is given by Nyquist [16]

$$\overline{i_d^2} = 4kTg_0 \cdot \Delta f \tag{2.1}$$

where k is the Boltzman constant (1.38 × 10<sup>-23</sup> J/°K), T is the absolute temperature,  $g_0$  is the channel conductance at zero drain-source voltage, and  $\Delta f$  is the bandwidth of interest.

Inspection of Equation (2.1) reveals that this expression is nonphysical since it indicates that the total current noise power approaches infinity if the bandwidth is increased without limit, which is contradictory to what is found in the real world. The more complete expression for the resistive thermal noise is [17]

$$\overline{i_d^2} = 4kTg_0p(f) \cdot \Delta f \tag{2.2}$$

where p(f) is the Planck factor, given by

$$p(f) = \frac{hf/kT}{e^{hf/kT} - 1} \tag{2.3}$$

where h is Planck's constant,  $6.63 \times 10^{-34}$  J-s. As long as hf/kT <<1, p(f) is very close to 1. Therefore, Equation (2.1) will remain valid for all practical frequencies. For example, at 290°K, p(f) is greater than 0.999 up to 10GHz. However, as the frequency increases further, p(f) decreases rapidly. Based on Equation (2.2), the total thermal noise power over an infinite bandwidth available from a resistor is approximately  $4 \times 10^{-8}$ W for T=290°K.

In most applications, MOS transistors operate in the saturation region in which the conductive channel cannot be considered as a resistance. It has been shown that the thermal noise drain current for a MOS transistor in saturation can be expressed as [18]

$$\overline{i_d^2} = 4kT \frac{\mu}{L_{eff}^2} Q_N \cdot \Delta f \tag{2.4}$$

where  $\mu$  is the effective carrier mobility,  $L_{eff}$  is the effective channel length, and  $Q_N$  is the total inversion layer charge.  $Q_N$  is a complex function of the gate-bulk voltage, drain potential, source potential, drain-source current, channel width and length, gate oxide capacitance, and bulk doping concentration. A complete and precise expression for  $Q_N$  is given in [19]. For simplicity, however, the channel thermal noise in a MOS transistor in saturation is often written as [20]

$$\overline{i_d^2} = 4kT\gamma g_m \cdot \Delta f \tag{2.5}$$

where  $g_m$  is the transconductance of the device and  $\gamma$  is the noise coefficient. In general,  $\gamma$  depends on all the terminal bias voltages and the basic transistor parameters. A numerical approach is required to interpret the dependencies of  $\gamma$  in expression (2.5). It has been shown that  $\gamma$  falls between 2/3 and 1 for long-channel MOSFETs (in which the effective channel length can be approximated by the drawn channel length between the drain and the source) if the bulk doping concentration is low and the gate oxide thickness is small [21]. When the bulk effect can be completely ignored, the value of  $\gamma$  is about 2/3.

For short-channel devices, however,  $\gamma$  may increase since channel length modulation is more pronounced and the effective channel length is relatively much shorter than the drawn channel length [22]. In addition, the carrier temperature increases with increasing field strength in the channel. Therefore, the high electric fields in submicron MOS devices produces hot carriers with temperatures higher than the lattice temperature. The presence of excess thermal noise that has been experimentally verified [23]-[24] is

attributed to this hot carrier effect. For example,  $\gamma$  was measured as high as 2 to 7 for a 0.7- $\mu$ m channel length MOSFET depending on bias conditions [23].

#### 2.3 Induced Gate Current Noise

At high frequencies the MOSFET should be considered as an RC distributed network. The conductive channel can be treated as a distributed resistance while the gate oxide capacitance represents a distributed capacitance. This means that the gate impedance of the device will exhibit a resistive component at high frequencies. This can be accounted for by shunting the gate oxide capacitance with a conductance  $g_g$  which can be expressed as [25]-[27]

$$g_g = \frac{4}{45} \frac{\omega^2 (C_{ox} \cdot WL)^2}{g_m}$$

(2.6)

In saturation,  $g_g$  can be simplified to

$$g_g = \frac{1}{5} \frac{\omega^2 C_{gs}^2}{g_m} \tag{2.7}$$

assuming  $C_{gs} = \frac{2}{3}(C_{ox} \cdot WL)$ .

The conductance  $g_g$  has noise associated with it. Called induced gate current noise  $\overline{i_g^2}$ , this noise is caused by the random motion of free carriers in the channel coupling through the gate capacitance. If the device were a passive device, the noise would simply be the resistive thermal noise  $\overline{i_g^2} = 4kTg_g \cdot \Delta f$ . However, since the resistive channel can not be considered as a homogeneous resistance when the device is in saturation, the calculation of the induced gate current noise is rather complex. As has been shown in [25]-[27], it is approximately given by

$$\overline{i_g^2} = 4kT\beta g_g \cdot \Delta f \tag{2.8}$$

where  $\beta$  is the coefficient of gate noise, equal to 4/3 for a long-channel MOSFET. For short channels in which hot carrier effects cannot be ignored,  $\beta$  may be larger.

The current fluctuations through the gate and drain are correlated since both are generated by the random motion of free carriers in the channel. The correlation coefficient has a complex value. For long-channel devices, a first-order approximation to the correlation coefficient c is given theoretically by [27]

$$c = \frac{\overline{i_g i_d}^*}{\sqrt{\overline{i_g^2} \cdot \overline{i_d^2}}} = 0.395j \tag{2.9}$$

More accurate calculation shows that the correlation coefficient c has a real part which is significant at high frequencies and can be approximated by [28]

$$c = \frac{\overline{i_g i_d}^*}{\sqrt{\overline{i_g^2 \cdot i_d^2}}} = 0.13 \frac{\omega C_{gs}}{g_m} + 0.35j$$

(2.10)

For typical radio frequencies, however, c can be simply assumed to be 0.35j.

Assuming the transfer functions of  $i_g$  and  $i_d$  are  $H_g$  and  $H_d$  respectively, the output noise due to the current fluctuations through the gate and drain can be calculated by

$$\begin{split} N_o &= \overline{(H_g i_g + H_d i_d) \times (H_g i_g + H_d i_d)^*} \\ &= |H_g|^2 \overline{i_g^2} + |H_d|^2 \overline{i_d^2} + \overline{H_g i_g H_d^* i_d^*} + \overline{H_d i_d H_g^* i_g^*} \\ &= |H_g|^2 \overline{i_g^2} + |H_d|^2 \overline{i_d^2} + 2Re(cH_g H_d^*) \cdot \sqrt{\overline{i_g^2 \cdot i_d^2}} \end{split} \tag{2.11}$$

where Re stands for the real part. It is clear from Equation (2.11) that the correlation between  $\overline{i_g^2}$  and  $\overline{i_d^2}$  can be computed if the transfer functions of them are known.

## 2.4 Resistive Gate Thermal Noise

The thermal noise generated in the resistive gate of the MOS device is an often overlooked additional noise component which should be taken into consideration when laying out wide MOS devices [29]-[31].

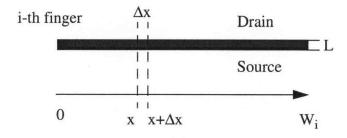

To calculate the resistive gate thermal noise, consider a general layout for the gate structure shown in Fig. 2.1. We shall only calculate the thermal noise contributed from the poly-gate over thin oxide (active area). The resistance of interconnect metal and the polygate over the thick oxide are neglected due to their small value. An elementary section  $\Delta x$  at position x in the i-th poly-gate finger, as shown in Fig. 2.1, has a thermal noise voltage  $\Delta V$  given by

$$\Delta V = \sqrt{4kT \frac{R_{sq} \cdot \Delta x}{L} \cdot \Delta f}$$

(2.12)

where  $R_{sq}$  is the sheet resistance of the poly-gate and L is the channel length. This thermal noise voltage  $\Delta V$  will cause a voltage fluctuation along the i-th gate finger. At position x, the voltage fluctuation  $\delta V_i(x)$  is given by

$$\delta V_i(x') = \delta V_i(0) + \frac{x'}{W_i} \Delta V, \qquad 0 < x' < x \qquad (2.13)$$

$$\delta V_i(x') = \delta V_i(W_i) - \frac{W_i - x'}{W_i} \Delta V, \qquad x < x' < W_i$$

(2.14)

where  $W_i$  is the width of the *i*-th gate finger, equal to W/N.  $\delta V_i(0)$  and  $\delta V_i(W_i)$  are the voltage fluctuation at two ends of the *i*-th gate finger. Since both ends are tied together and have a dc path to ground via interconnect metal,  $\delta V_i(0)$  and  $\delta V_i(W_i)$  are equal to zero. Therefore, the channel current fluctuation  $\Delta i_c$  due to  $\Delta V$  can be calculated by

Figure 2.1: Finger structure of a MOS transistor with large *W/L*.

$$\Delta i_c = \int_0^{W_i} g_{m0} \cdot \delta V_i(x') dx'$$

$$= g_{m0} \left[ \int_0^x \left( \frac{x'}{W_i} \Delta V \right) dx' - \int_x^{W_i} \left( \frac{W_i - x'}{W_i} \Delta V \right) dx' \right]$$

$$= g_{m0} \Delta V \cdot (x - W_i/2)$$

(2.15)

where  $g_{m0}$  is unit-width transconductance of the transistor, defined as  $g_{m0} = g_m/W$ .

Since the thermal noise voltage generated by every section  $\Delta x$  in the *i*-th gate finger can be considered un-correlated, the total channel current noise generated by the *i*-th gate finger is given by

$$\overline{i_c^2} = \int_0^{W_i} (\Delta i_c)^2

= \int_0^{W_i} g_{m0}^2 \cdot (x - W_i/2)^2 \cdot 4kT \frac{R_{sq} \cdot \Delta x}{L} \cdot \Delta f

= 4kT \frac{R_{sq}g_{m0}^2 W_i^3}{L} \cdot \Delta f$$

(2.16)

Hence the channel current noise generated by all N gate fingers is

$$\sum_{1}^{N} \overline{i_{c}^{2}} = 4kT \frac{R_{sq} g_{m0}^{2} W_{i}^{3}}{L} \cdot \Delta f \cdot N$$

$$= 4kT \frac{R}{12N^{2}} g_{m}^{2} \cdot \Delta f$$

(2.17)

where  $R = R_{sq} \cdot W/L$  is the total poly-gate resistance. Equation (2.17) indicates that the resistive gate thermal noise can be modeled by a series resistance at the gate given by

$$R_g = \frac{R}{12N^2} (2.18)$$

From Equation (2.18) it is clear that in order to minimize the noise associated with the resistive poly-gate, the number of gate fingers N should be chosen as large as possible. For example, assuming the total poly-gate resistance R of a large device is  $500\Omega$ , the effective gate thermal resistance  $R_g$  is only about  $0.4\Omega$  if N is chosen as 10.

It is worthy of mention that the above equations hold only if both sides of the gate fingers are tied together. If one side of the gate fingers is left open (assuming at x'=0), the voltage fluctuation due to  $\Delta x$  along the i-th gate finger would be  $\Delta V$  for 0 < x' < x and 0 for  $x < x' < W_i$ . As a consequence, the channel current fluctuation  $\Delta i_c$  due to  $\Delta x$  is  $g_{m0}\Delta V \cdot x$  and the total channel current noise generated by the i-th gate finger is now given by

$$\overline{i_c^2} = \int_0^{W_i} (\Delta i_c)^2

= 4kT \frac{R_{sq}g_{m0}^2 W_i^3}{2} \cdot \Delta f$$

(2.19)

This indicates the series gate resistance is increased by a factor of four to

$$R_g = \frac{R}{3N^2} \tag{2.20}$$

Therefore, for low noise design, it is desirable to tie both sides of the gate fingers together using a low-resistance interconnect such as metal.

#### 2.5 Additional Noise Sources

## 2.5.1 Flicker (1/f) Noise and Shot Noise

Flicker noise was first observed by Johnson in 1925 [32]. Since its spectrum varies as  $1/f^{\alpha}$ , with  $\alpha$  close to unity, it is also often called 1/f noise. Despite continuous pursuit, the physical mechanism behind flicker noise is still not very clear. Since flicker noise decreases rapidly with an increase in frequency, it is negligible in RF CMOS LNA's compared to the thermal noise. Hence, the treatment of flicker noise will not be discussed in this thesis. There are many papers in the literature on the subject of flicker noise in MOSFETs both theoretical and experimental [33]-[35], where detailed analysis and modeling of flicker noise can be found.

Shot noise, also known as Schottky noise, is a result of the discontinuous character of electronic charges that constitute a dc current flowing through a potential barrier, such as a *pn* junction. A simple yet general form of the shot noise is [36]

$$\overline{i_q^2} = 2qI_{DC} \cdot \Delta f \tag{2.21}$$

where q is the electronic charge,  $1.6\times10^{-19}\,\mathrm{C}$ , and  $I_{DC}$  is the dc current in amperes. Formula (2.21) is valid for the frequencies lower than  $f_T = 1/(2\pi\tau)$ , where  $\tau$  is the electron transit time in the device. Beyond  $f_T$ , the shot noise rolls off rapidly. Shot noise is one of the dominant noise sources in a bipolar transistor. Fortunately, in MOSFETs, shot noise is generally negligible since only the dc gate leakage current contributes shot noise and this gate leakage current is very small.

## 2.5.2 Substrate Resistance Noise

The thermal noise voltage across the distributed substrate resistance induces a fluctuating substrate potential. These random variations couple to the MOSFET channel, giving rise to fluctuations in the channel current [37]. In a standard CMOS process, a lightly doped epitaxial layer generates a significant resistance to ac ground under the device channel. The noise voltage generated across this resistance  $R_{sub}$  is given by

$$\overline{v_{sub}^2} = 4kTR_{sub} \cdot \Delta f \tag{2.22}$$

Thus, the device channel experiences current fluctuations given by

$$\overline{i_{sub}^2} = 4kTR_{sub}g_{mb}^2 \cdot \Delta f \tag{2.23}$$

where  $g_{mb}$  is the substrate transconductance, given by

$$g_{mb} = \frac{\alpha g_m}{2\sqrt{V_{SB} + |2\phi_F|}} \tag{2.24}$$

where  $\phi_F$  is the difference between the quasi-Fermi level and the intrinsic level and  $\alpha$  is the body-effect constant, with a typical value about  $0.5V^{1/2}$ .

Estimation of  $R_{sub}$  is quite complicated due to its distributed nature and its dependence on device layout. For a certain device, experiments showed that the substrate resistance noise added 25% more noise power to that already existing due to the channel thermal noise [37]. Two approaches can be used to minimize its contribution. First, reduce  $R_{sub}$  by changing device layout or by using a thinner and less lightly doped epitaxial material. Second, bias the substrate at high potential to reduce  $g_{mb}$ . In a typical CMOS process,  $g_{mb}$  is practically reduced to zero when  $V_{SB}$  is about -2V. In such a case, the substrate contribution to the channel noise is negligible.

In addition, impact ionization in the channel gives rise to an additional noise mechanism in MOSFETs. This impact-ionization-generated current appears as gate (or substrate) current flowing between the gate (or substrate) and the drain of the MOS transistor [38]-[39]. Also, noise from other components and its coupling through the chip interconnects, substrate, and package, can be detrimental to circuit performance [40].

High precision noise calculations including all noise sources is not only problematic given the disparate properties of the many noise sources as discussed above, it is also unnecessary from a practical viewpoint. First, many existing noise models are either qualitative or first-order approximations. Second, there are inevitable process variations of the parameters, and third, the noise performance of a circuit is typically determined by one or two dominant noise sources.

#### 2.6 Small-Signal Noise Circuit Model

Having investigated the noise sources in a MOSFET, we are ready to develop a general small-signal noise circuit model of a MOSFET in order to facilitate the analysis and design of low noise CMOS circuits.

The induced gate current noise can be accounted for by placing a noise current source  $\overline{i_g^2}$  in parallel with the gate capacitance. Note that the conductance  $g_g$  should also be included in the gate circuit to account for the distributed nature of the MOSFET channel at high frequencies. Such a circuit model is shown in Fig. 2.2 (a) where a shunt noise current  $\overline{i_g^2}$  and a shunt conductance  $g_g$  have been added. Shaeffer and Lee [11] have derived the Thevenin equivalent circuit for (a), as shown in Fig. 2.2 (b). First, transform the parallel RC network into an equivalent series RC network. The impedance looking into the parallel RC network is

$$Z = \frac{1}{g_g + j\omega C_{gs}}$$

$$= \frac{1}{5g_m[1 + (\omega C_{gs}/5g_m)^2]} + \frac{1}{j\omega C_{gs}[1 + (\omega C_{gs}/5g_m)^2]}$$

(2.25)

We observe that

$$(\omega C_{gs}/5g_m)^2 = \left(\frac{\omega}{5\omega_T}\right)^2 \ll 1 \tag{2.26}$$

usually holds for all practical frequencies. Here  $\omega_T = g_m/C_{gs}$  is the transistor unity-gain frequency which indicates an upper limit on the maximum frequency at which the transistor can be effectively used (Appendix B). Thus Equation (2.25) can be simplified as

$$Z \approx \frac{1}{5g_m} + \frac{1}{j\omega C_{gs}} = r_g + \frac{1}{j\omega C_{gs}}$$

(2.27)

This indicates the equivalent series RC network consists of a frequency-independent resistance  $r_g = 1/5g_m$  and the gate capacitance  $C_{gs}$ .

The Thevenin equivalent noise voltage is then given by

$$\overline{v_g^2} = \overline{i_g^2} \cdot \left| \frac{1}{j\omega C_{gs}} + r_g \right|^2$$

$$= 4kT\beta r_g \cdot \Delta f \cdot \left[ 1 + \left( \frac{\omega}{5\omega_T} \right)^2 \right] \approx 4kT\beta r_g \cdot \Delta f$$

(2.28)

where

Figure 2.2: Representations of the induced gate current noise in MOS transistor.

$$r_g = \frac{1}{5g_m} \tag{2.29}$$

This may seem attractive at first because  $\overline{v_g^2}$  is similar to a resistive thermal noise, unlike  $\overline{i_g^2}$  which is frequency-dependent. However, further observation shows that this treatment does not guarantee convenience in the analysis of circuit noise performance because, as shown in Fig. 2.2 (b), the critical voltage  $v_{gs}$  (which determines the output noise current) is still frequency-dependent, considering the impedance of the driving-source is usually not capacitive. Moreover, it is difficult to adopt Fig. 2.2 (b) into a circuit simulator since  $v_{gs}$  is no longer the voltage across  $C_{gs}$ . Therefore, we will not use Fig. 2.2 (b) in the following noise analysis.

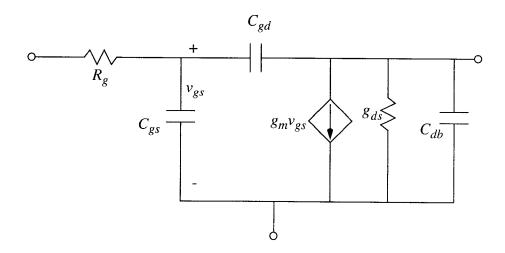

Fig. 2.3 shows the complete small-signal noise circuit of a MOSFET based on the previous discussion. As shown, the channel thermal noise and the induced gate noise are included. The resistive gate thermal noise is modeled by the series resistance  $R_g$ . Flicker noise is not included since this noise model is intended to be used for RF CMOS LNA circuits. In addition, substrate resistance noise and other second-order noise sources are not included since they are mainly concerned with the layout or process parameters and have little connection with the circuit design parameters.

Given the noise circuit model, it is possible to calculate the noise performance of any RF LNA circuit composed of MOS transistors by the superposition of contributions of the individual noise sources. For more accurate analysis, the correlation between  $i_g^2$  and  $i_d^2$  should be taken into account and the substrate transconductance  $g_{mb}$ , the drain-source conductance  $g_{ds}$ , and bulk capacitances should also be added to the noise circuit. An optimal choice of the basic design parameters for each MOS transistor in low-noise CMOS circuits, such as W, L, and  $I_{DS}$ , can then be made with the aid of computer simulation.

Finally, the layout should be optimized in order to minimize additional noise contributions related to the layout parameters, such as the resistive gate thermal noise and substrate resistance thermal noise.

## 2.7 Modified Noise Simulation in SPICE

Though much progress has been achieved in high-frequency integrated circuit simulation using the standard circuit simulator SPICE, the noise models implemented in SPICE are not accurate enough at radio frequencies. The existing MOS noise models in

Figure 2.3: Small-signal noise circuit of a MOS transistor.

SPICE account for neither the gate resistance  $R_g$  nor the conductance  $g_g$  and its associated induced noise  $\overline{i_g^2}$ . Therefore, some modifications should be made when using SPICE to simulate the noise performance of RF circuits, in order to accommodate the high-frequency noise characteristics of MOS transistors.

To include the effect of the resistive gate in SPICE simulations, resistance  $R_g$  can be simply added in series with the gate of each MOS transistor in the circuit. Effects of the gate conductance  $g_g$  and its associated induced noise  $\overline{i_g^2}$  on circuit performance are more complicated due to their frequency dependence. However, using a script program such as Awk or Perl, we can easily modify SPICE simulations to include the effects of the gate conductance  $g_g$  and the gate induced noise  $\overline{i_g^2}$  at every single frequency point. Post-simulation data processing can then be adopted by extracting and plotting the single-frequency results to get a good presentation of the frequency response of the circuit. The following procedure is listed to illustrate one such method of the modified noise simulation using HSPICE.

- Step 1. Form HSPICE input file with gate resistance  $R_g$  included: input1

- Step 2. Conduct ac noise simulation in HSPICE at N frequency points over a specified frequency range (f1 to f2) using input1: result1

- Step 3. Extract  $C_{gs}$  and  $g_m$  from result1 for all MOSFETs in the circuit; compute corresponding  $g_g = (\omega^2 C_{gs}^2)/(5g_m)$  and  $\overline{i_g}^2 = 4kT\beta g_g$  (noise power within 1Hz) at N frequency points from £1 to £2

- Step 4. For a single frequency, modify input1 to add  $g_g$  between the gate and source of all MOSFETs: input2

- Step 5. Modify input2 to add an unit ac current source in parallel with  $g_g$  for one MOSFET; conduct ac analysis in HSPICE at the specified single frequency; multiply the output voltage power by  $\overline{i_g^2}$

- Step 6. Repeat step 5 for all MOSFETs (to save simulation time, we may only repeat with MOSFETs that have significant noise contribution)

- Step 7. Repeat steps 4-6 for N frequency points from £1 to £2: result2

- Step 8. Total output noise = output due to the resistive thermal noise: noise1 (in result1) + output due to the channel thermal noise: noise2 (in result1) + output due to the induced gate current noise: noise3 (in result2)

# Step 9. Data processing and plotting

The above procedure is elementary and somewhat tedious. For accurate noise simulation of CMOS RF circuits, it is an effective approach to include the effects of the induced gate current noise. Note that the correlation between the channel thermal noise and the induced gate current noise can also be computed using the transfer functions of the two noise sources obtained in SPICE (refer to Equation (2.11)). Nevertheless, efforts need to be made to improve the noise models of MOSFETs implemented in SPICE so that the noise simulation will be more convenient and accurate.

#### CHAPTER 3. PRINCIPLES OF CMOS LNA DESIGN

In this chapter, we shall discuss the basic principles of CMOS LNA design. Beginning with the discussion of some basic concepts, such as noise figure and linearity, we will study various CMOS LNA topologies in the radio frequency range (e.g., 800MHz-2.4GHz). It is concluded that a CMOS LNA with LC series tuning at its inputs offers the possibility of achieving the best noise performance. The design considerations of the LC tuned CMOS LNA are then discussed and a detailed description of the optimization techniques for basic device parameters is presented.

## 3.1 Basic Concepts

# 3.1.1 Noise Factor and Noise Figure

Before studying a CMOS LNA, it is necessary to understand the most popular figure of merit for noise performance, noise figure (NF). Friis [41] defined the noise factor (F) of a network to be the ratio of the signal-to-noise-ratio (SNR) at the input to the signal-to-noise-ratio (SNR) at the output; the noise figure (NF) is the logarithmic equivalent in decibels

$$NF = 10\log\left(\frac{SNR_{in}}{SNR_{out}}\right) = 10\log(F)$$

(3.1)

Thus the noise figure of a network is the decrease or degradation in the signal-to-noise ratio as the signal passes through the network. A perfect amplifier would amplify only the noise at its input along with the signal. A realistic amplifier, however, also adds some extra noise from its own components and degrades the signal-to-noise ratio. Equation (3.1) implies that a lower NF is achieved when the device noise contributes less to the total output noise; i.e., the input noise contributes a larger portion to the total output noise.

Noise figure is a meaningful parameter if and only if the input noise is well defined. The usual assumption is that input noise is the thermal noise power available from a resistor (typically  $50\Omega$  for wireless receiving systems) at a reference temperature, usually taken as  $290^{\circ}$ K [42] (close to the temperature seen by receiving antennas directed across the atmosphere at the transmitting antenna). Noise figure is generally a function of frequency but it is usually a bandwidth invariant parameter so long as the bandwidth is narrow enough to resolve variations with frequency. If the bandwidth is large, a frequency average of the spot noise figures over the band of measurement should be used. The spot noise figure, however, is the viable measure of a device, such as an LNA, for most wireless receiver applications due to the narrow-band characteristics.

It is worthwhile to mention what the noise figure does not characterize. The noise figure is not a measure of the noise performance of networks with one port, e.g., oscillators. Noise figure also has nothing to do with modulation. It is independent of the modulation format and of the fidelity of modulators and demodulators. One weakness of the noise figure is its being meaningful for a given device only in conjunction with a specified source impedance. Thus it cannot be used as a basis for evaluating the noise performance or for comparison of devices with different source impedances.

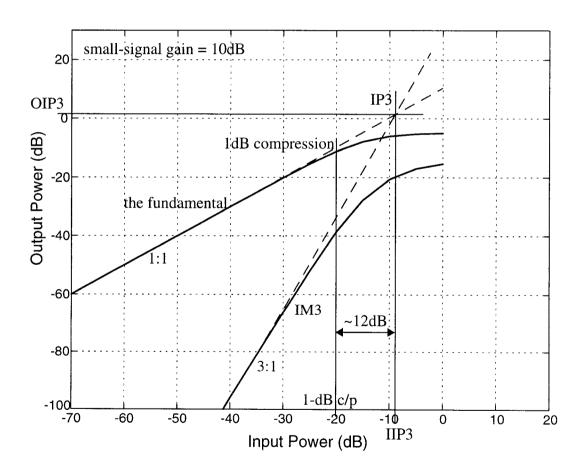

## 3.1.2 Nonlinearity

The nonlinearity of a device limits the maximum signals that may be processed. For a CMOS LNA, nonlinearity can be characterized either by the 1-dB compression point, defined as the input power at which the output power gain drops by 1-dB relative to the small-signal gain, or by the input-referred third-order intercept point (IIP3), the input power at which the third-order intermodulation term extrapolated from the small-signal values is equal to the fundamental.

Any pseudo-linear network can be characterized by a transfer function, the output voltage/current as a function of an input voltage/current. The transfer function may be characterized as a power series

$$S_o = a_0 + a_1 \cdot S_i + a_2 \cdot S_i^2 + a_3 \cdot S_i^3 + \dots$$

(3.2)

assuming an input signal  $S_i$  and an output signal  $S_o$ .

Using Equation (3.2), the nonlinearity of an amplifier may be analyzed. Two types of input signals will be considered in the analysis. The first is a single frequency input (single-tone),  $S_i=A\cos\omega t$ . The other is a pair of unrelated inputs added to form a two-tone input,  $S_i=A(\cos\omega_1 t+\cos\omega_2 t)$ . A practical amplifier may, of course, be subjected to more complicated inputs. It is sometimes useful to consider more complicated input signals, containing three or more input tones. However, the analysis would become predictably messy [43]. Fortunately, most of the salient features of the nonlinearity are suitably characterized with the single-tone or two-tone inputs.

# 3.1.2.1 Gain Compression

The gain of a circuit can be obtained based on Equation (3.2). Let  $S_i$  be a single-tone signal ( $A\cos\omega t$ ), then

$$\begin{split} S_o &= a_0 + a_1 \cdot A \cos \omega t + a_2 \cdot A^2 \cos^2 \omega t + a_3 \cdot A^3 \cos^3 \omega t + \dots \\ &= a_0 + \frac{a_2 A^2}{2} + \left(a_1 A + \frac{3a_3 A^3}{4}\right) \cos \omega t + \frac{a_2 A^2}{2} \cos 2\omega t + \frac{3a_3 A^3}{4} \cos 3\omega t + \dots \end{split} \tag{3.3}$$

From the above expansion, we can see that the gain of the circuit is  $\left(a_1 + \frac{3a_3A^2}{4}\right)$ , neglecting other higher-order terms. The small-signal gain is  $a_I$  when the effect of the amplitude A of the input signal  $S_i$  can be ignored. In most circuits, as A increases, the gain begins to drop from the small-signal gain  $a_I$ , which is usually referred to as gain

compression or saturation. The 1-dB compression point, defined as the input signal amplitude that causes the gain to drop by 1dB from the small-signal power gain, can then be calculated by

$$20\log\left|a_1 + \frac{3a_3A^2}{4}\right| = 20\log\left|a_1\right| - 1\tag{3.4}$$

which indicates that the amplitude of  $S_i$  at the 1-dB compression point is approximately

$$A_{cp} = \sqrt{0.145 \left| \frac{a_1}{a_3} \right|} \tag{3.5}$$

Please note Equation (3.5) is the first-order approximation for a pseudo-linear circuit. When higher-order terms are taken into consideration, the 1-dB compression point is usually lower than that expected from Equation (3.5) (refer to Fig. 3.1).

#### 3.1.2.2 Intermodulation

Now, let  $S_i$  be a two-tone signal  $A(\cos\omega_1 t + \cos\omega_2 t)$ . We have

$$S_o = a_0 + a_1 A (\cos \omega_1 t + \cos \omega_2 t) + a_2 A^2 (\cos \omega_1 t + \cos \omega_2 t)^2 + a_3 A^3 (\cos \omega_1 t + \cos \omega_2 t)^3 + \dots$$

(3.6)

After simplification and collection of terms, we obtain

$$\begin{split} S_o &= a_0 + a_2 A^2 + \left(a_1 A + \frac{9a_3 A^3}{4}\right) (\cos \omega_1 t + \cos \omega_2 t) \\ &+ a_2 A^2 [\cos(\omega_1 + \omega_2) t + \cos(\omega_1 - \omega_2) t] \\ &+ \frac{a_2 A^2}{2} (\cos 2\omega_1 t + \cos 2\omega_2 t) + \frac{a_3 A^3}{4} (\cos 3\omega_1 t + \cos 3\omega_2 t) \\ &+ \frac{a_3 A^3}{4} [\cos(\omega_1 + 2\omega_2) t + \cos(\omega_1 - 2\omega_2) t \\ &+ \cos(2\omega_1 + \omega_2) t + \cos(2\omega_1 - \omega_2) t] + \dots \end{split}$$

It is seen that the output signal exhibits some components that are not harmonics of the input frequencies when a two-tone signal is applied to the network. This phenomenon is called intermodulation (IM). Intermodulation is a troublesome effect in a wireless receiving system. For example, the third-order intermodulation (IM3)

$$\frac{a_3A^3}{4}[\cos(\omega_1+2\omega_2)t+\cos(\omega_1-2\omega_2)t+\cos(2\omega_1+\omega_2)t+\cos(2\omega_1-\omega_2)t]$$

is of great importance for a superheterodyne receiver (IM2 is more important for a zero-IF or direct-conversion receiver). If the input tones ( $\omega_1$  and  $\omega_2$ ) are close to each other, the sum frequency terms in IM3 are close to the third harmonic and no more of a problem than harmonic distortion, for it may be filtered from the system. However, the difference frequency terms in IM3 are very close to that of the input tones and may eventually lie in the signal band. In a wireless receiving system, a weak signal accompanied by two strong interferers (for example, from an adjacent channel) would be corrupted by the third-order intermodulation terms.

A valuable figure of merit is the third-order intercept point (IP3). As illustrated in Fig. 3.1, the third-order intercept point is defined to be at the intersection of two extrapolated lines from the small-signal fundamental and IM3 curves. Please note we do not need to consider the higher-order effects for the third-order intercept point since the intercept is evaluated by extrapolating trends observed with sufficiently small amplitude inputs in both simulations and experiments. By this definition, we can easily compute the input-referred third-order point (IIP3) by setting the amplitude of the IM3 equal to the amplitude of the fundamental using small-signal results from Equation (3.7)

$$\left|a_1 A\right| = \left|\frac{a_3 A^3}{4}\right| \tag{3.8}$$

which gives the amplitude of the input signal at IP3 as

$$A_{IP3} = \sqrt{\frac{4}{3} \left| \frac{a_1}{a_3} \right|} \tag{3.9}$$

Fig. 3.1 shows the simulation results for an amplifier with a 10dB small-signal gain, modeled by a hyperbolic tangent function. As shown, the fundamental curve has a slope of 1:1 and the IM3 curve has a slope of 3:1 when the input signal is sufficiently small, because, as indicated in Equation (3.7), the amplitude of fundamental  $(a_1A)$  increases in proportion

Figure 3.1: Graphical interpretation of the nonlinearity of an amplifier.

to A, while the amplitude of the IM3 ( $a_3A^3/4$ ) increases in proportion to  $A^3$ . It is clear that the input-referred third-order intercept point (IIP3) is different from the output-referred third-order intercept point (OIP3) by the small-signal gain of the amplifier, i.e., 10dB in this example.

It is also observed the 1-dB compression point occurs at a lower input power than IIP3. This is usually true for most practical circuits. The relationship between the 1-dB compression point and IIP3 can be determined based on the foregoing analysis [44]. Combining Equations (3.5) and (3.9), we obtain

$$\frac{A_{IP3}}{A_{cp}} = \sqrt{\frac{4}{3}} / \sqrt{0.145} = 9.64 \text{dB}$$

(3.10)

Equation (3.10) indicates that the input-referred third-order intercept point is expected to be about 10dB higher than the 1-dB compression point. However, as mentioned before, the 1-dB compression point may be lower than that expected from Equation (3.5), taking higher-order effects into consideration. As a consequence, the difference between the 1-dB compression point and IIP3 may be higher than 10dB. For example, Fig. 3.1 shows that the amplifier has an IIP3 of about 12dB higher than its 1-dB compression point. Typically IIP3 is about 10-15 dB beyond the 1-dB compression point for amplifiers in current CMOS technologies [45].

#### 3.2 CMOS LNA Architectures

The essential theory and practical considerations for the design of low-noise amplifiers and various architectures for practical implementations have been discussed in the literature [46]-[47]. The selection of the best LNA topology involves complex trade-offs between noise performance, power consumption, available gain, input matching, and

linearity. For a CMOS LNA, the common-gate input stage has the same noise sources as a common-source stage. However, the total performance is inferior. For this reason, we shall focus on the study of CMOS LNA topologies with a common-source input stage. Based on the noise model of MOS transistors established in Chapter 2, we will analyze the noise performance of various CMOS LNA's using the concept of noise figure.

Please note that the noise performance of a CMOS LNA, besides being dependent on the amplifier, is also a function of the signal source impedance. A classical approach is to obtain the minimum noise figure from a given device by using the optimum source impedance [46], [48]. Though extensively used in discrete RF LNA designs, this approach does not offer guidance for the optimization of active devices.

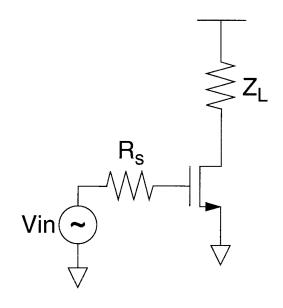

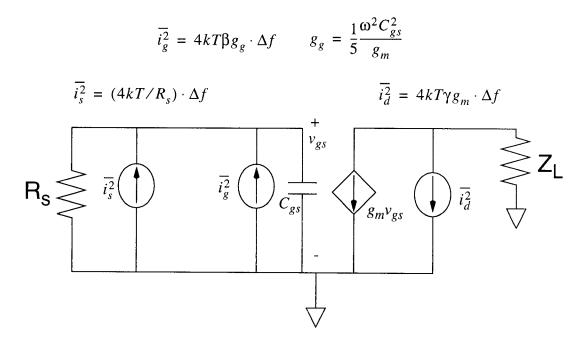

## 3.2.1 Single-Transistor CMOS LNA

The simplest architecture of a CMOS LNA is the single-transistor implementation, as shown in Fig. 3.2. The small-signal noise equivalent circuit for the single-transistor CMOS LNA is developed based on the high-frequency noise model of MOS transistors. Note we neglect the gate-drain capacitance to simplify the analysis. In addition, since

$$g_g = \frac{\omega^2 C_{gs}^2}{5g_m} = \omega C_{gs} \cdot \frac{\omega}{5\omega_T}$$

is usually much smaller than  $\omega C_{gs}$  for all practical frequencies, it is ignored here. The gate resistance  $R_g$  is a layout-related parameter and can always be reduced to a negligible value by a special gate structure, such as multi-finger gate as discussed in Sec. 2.4. It is also ignored here to further simplify the analysis.

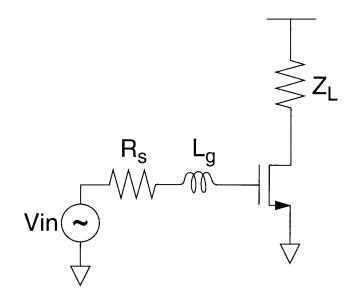

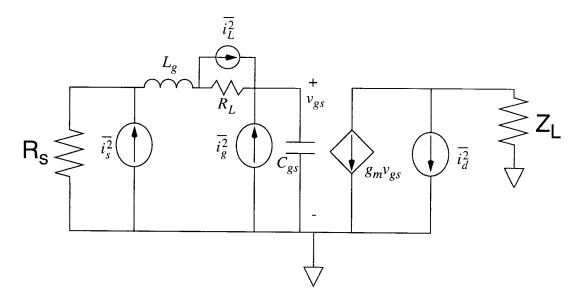

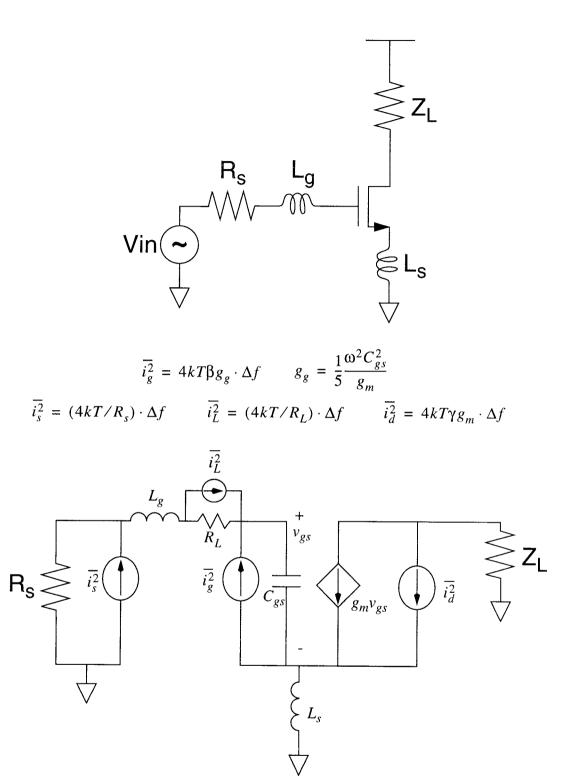

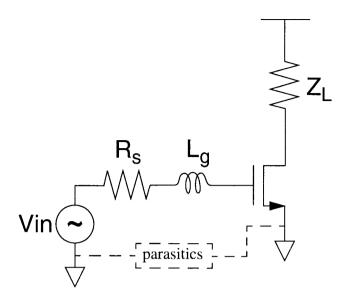

Figure 3.2: Single-transistor CMOS LNA.

The computation of noise figure is troublesome when using the definition directly. By simple arrangements of Equation (3.1), however, we can obtain a more useful formula for noise figure calculation, as shown below

$$NF = 10\log\left(\frac{S_i/N_i}{S_o/N_o}\right)$$

$$= 10\log\left(\frac{N_o}{N_i \cdot Gain}\right)$$

$$= 10\log(F)$$

(3.11)

where  $N_o$  is the total output noise into load  $Z_L$  and  $N_i$  is the input noise, which is the thermal noise associated with the source impedance  $R_s$ , modeled by a noise current source,  $\overline{i_s^2} = (4kT/R_s) \cdot \Delta f$ . Neglecting the noise contribution from the load impedance  $Z_L$  and assuming the correlation coefficient c between the induced gate current noise and the channel thermal noise is purely imaginary, we can derive the total output noise current  $N_o$  using KCL/KVL

$$\begin{split} N_o &= \overline{i_d^2} + (\overline{i_s^2} + \overline{i_g^2}) \frac{g_m^2 R_s^2}{1 + Q^{-2}} + \frac{2|c|g_m R_s}{Q + Q^{-1}} \sqrt{\overline{i_d^2} \cdot \overline{i_g^2}} \\ &= 4kT\Delta f \left[ \gamma g_m + \left( \frac{1}{R_s} + \beta g_g \right) \frac{g_m^2 R_s^2}{1 + Q^{-2}} + \frac{2|c|g_m R_s}{Q + Q^{-1}} \sqrt{\gamma g_m \beta g_g} \right] \\ &= 4kT\Delta f \left[ \gamma g_m + \frac{g_m^2 R_s}{1 + Q^{-2}} + \frac{\beta g_m}{5} \frac{1}{1 + Q^2} + \frac{2|c|g_m}{1 + Q^2} \sqrt{\frac{\gamma \beta}{5}} \right] \end{split} \tag{3.12}$$

where Q is the quality factor of the input capacitance  $C_{gs}$ , given by

$$Q = \frac{1}{\omega R_s C_{gs}} \tag{3.13}$$

The output noise current due to the source impedance  $R_s$   $(N_i \cdot Gain)$  is obtained as

$$N_i \cdot Gain = \overline{i_s^2} \frac{g_m^2 R_s^2}{1 + Q^{-2}} = 4kT \frac{g_m^2 R_s}{1 + Q^{-2}} \Delta f$$

(3.14)

Combining Equations (3.11)-(3.14), the noise factor F can be obtained as

$$F = \frac{N_o}{N_i \cdot Gain}$$

$$= 1 + \frac{\gamma}{R_s} \cdot \frac{1 + Q^{-2}}{g_m} + \frac{\beta}{5R_s} \cdot \frac{Q^{-2}}{g_m} + 2|c| \sqrt{\frac{\gamma\beta}{5}} \cdot \frac{Q^{-2}}{R_s g_m}$$

(3.15)