#### An Abstract Of The Thesis Of

Kevin Djang for the degree of Master of Science in Computer Science presented on May 11, 2000. Title: An Alternative Architecture For Performing Basic Computer Arithmetical Operations.

Abstract approved: Redacted for privacy

Paul Cull

The arithmetic portions of almost all modern processor architectures are of very similar design. We use the term "traditional" to describe this design, the primary characteristics of which are native support for integer and floating-point number types and special disjoint instructions and hardware for each supported type. Decades of refinement have endowed this traditional arithmetic architecture with high performance, but also certain inherent limitations.

The highly-specific instruction sets and circuitry that provide optimized performance for supported number types, also make it difficult to synthesize unsupported number types and manipulate them in an efficient manner. This trait also applies when using supported number types for arbitrary ranges greater than those directly implemented by the processor.

In this thesis we present an alternative to the traditional computer arithmetic architecture, designed to address the limitations of the traditional approach while preserving most of its benefits.

Instead of the specific number representation support provided by the instructions, hardware and native data types in a traditional ALU/FPU pair, we define a single data type, the XLU digit that forms a base from which other number types may be easily derived, along with a set of instruction primitives from which basic arithmetic operations may be efficiently realized.

Our data type has a signed-digit representation, which allows algorithms for addition, subtraction and multiplication to achieve a high degree of parallelism at the primitive instruction level. The instruction primitives and algorithms are designed to hide or eliminate as much branching as possible, further increasing instruction-level independence.

We provide details of the data type, an overview of the set of instruction primitives, and a discussion of how to use those instruction primitives to perform basic arithmetic algorithms for addition, subtraction and multiplication. We also give examples for three derived number representations; integer, fixed-point and floating-point numbers.

We believe that our approach of building from a unified base provides flexibity and scalability beyond that of the traditional arithmetic architecture.

Our data type, the XLU digit, and the primitive operations to manipulate it may be implemented with modest amounts of circuitry, and this, together with the highly parallel nature of the entire design means that many XLU circuit blocks can be realized in the same silicon area as one traditional ALU/FPU pair. An ALU or FPU may only work when it has the correct type to work on, whereas we believe any and all XLUs available to the processor can be kept busy almost all of the time, achieving greater utilization of the available silicon.

©Copyright by Kevin Djang May 11, 2000 All Rights Reserved

# An Alternative Architecture For Performing Basic Computer Arithmetical Operations

by

Kevin Djang

A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Presented May 11, 2000 Commencement June 2001 Master of Science thesis of Kevin Djang presented on May 11, 2000.

APPROVED:

# Redacted for privacy

Major Professor; representing Computer Science

# Redacted for privacy

Chair of Department of Computer Science

# Redacted for privacy

Dean of Graduate School

I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of thesis to any reader upon request.

# Redacted for privacy

Kevin Djang, Author

#### Acknowledgements

Without Dr. Lawrence Crowl there would have been no beginning to this thesis and without Dr. Paul Cull there would have been no ending. Dr. Crowl's ideas form the basis for this thesis and it is his guidance that turned those ideas into a cohesive body of work. Dr. Cull's patience and persistence carried me and the work forward to completion. I offer my thanks to them both.

The company I work for, Rogue Wave Software, has supported me throughout the difficult process of balancing a full-time job with writing a thesis.

I would also like to thank my parents for their love and support, and my wife Rebecca, who figures deeply in all the aspects of my life.

# **Table of Contents**

| 1 | In  | troduction                                 | 1  |

|---|-----|--------------------------------------------|----|

|   | 1.1 | Background                                 | 1  |

|   | 1.2 | Motivation                                 | 2  |

|   | 1.3 | Outline                                    | 4  |

| 2 | Hi  | storical Contexts                          | 7  |

|   | 2.1 | Number Representation                      | 7  |

|   | 2.2 | Instruction Set Designs                    | 10 |

|   | 2.3 | A Note Concerning Floating-Point Support   | 14 |

|   | 2.4 | Parallelism                                | 14 |

| 3 | Ke  | ey Points                                  | 16 |

|   | 3.1 | Representation                             | 16 |

|   | 3.2 | Details of the XLU Representation          | 19 |

|   | 3.3 | Algorithms for Basic Arithmetic Operations | 21 |

| 4 | Co  | omposite Representations                   | 37 |

|   | 4.1 | Fixed-Point Numbers                        | 37 |

|   | 4.2 | Floating-Point Numbers                     | 44 |

# Table of Contents (Continued)

| 5  | Ha    | ardware Considerations                    | 60 |

|----|-------|-------------------------------------------|----|

|    | 5.1   | Small Implementation Footprint            | 60 |

|    | 5.2   | High Speed and Multiple-Instruction Issue | 60 |

|    | 5.3   | Take Advantage of the Short Carry         | 61 |

| 6  | Su    | mmary and Evaluation                      | 62 |

|    | 6.1   | A Summary of Things Done and Not Done     | 62 |

|    | 6.2   | Questions Raised by the Design            | 64 |

|    | 6.3   | Summary of the XLU Architecture           | 66 |

|    | 6.4   | How to Evaluate the Design                | 68 |

| 7  | Co    | onclusion                                 | 75 |

| Re | feren | ces                                       | 77 |

| Ap | pend  | ices                                      | 86 |

|    | App   | endix A - Small Glossary of Terms         | 87 |

|    | App   | endix B - The XLU Simulator               | ดก |

# List of Figures

| Figure |                                                               | <u>Pa</u> | age |

|--------|---------------------------------------------------------------|-----------|-----|

| 1      | Addition Primitives – Sum of two digits                       |           | 23  |

| 2      | Multi-digit Addition Example                                  |           | 25  |

| 3      | A multi-digit Squash "Cascade" Example                        |           | 27  |

| 4      | Subtraction-by-negation Example                               |           | 29  |

| 5      | Subtraction Example                                           |           | 30  |

| 6      | Multiplication Primitives – Product of two digits             |           | 32  |

| 7      | 3x2 Multiplication Example "By Pencil"                        |           | 33  |

| 8      | 3x2 Multiplication Example "By Pencil" Symbols                |           | 35  |

| 9      | Partial Product Accumulation                                  |           | 36  |

| 10     | An example XLU digit Implementation                           |           | 41  |

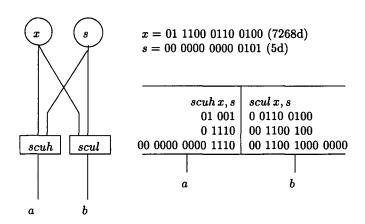

| 11     | The scuh and scul operations                                  |           | 41  |

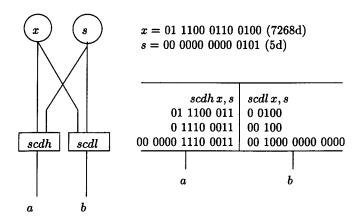

| 12     | The scdh and scdl operations                                  |           | 42  |

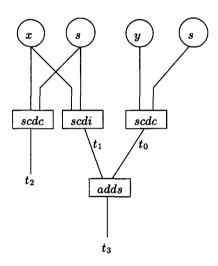

| 13     | Multi-digit scale-down example                                |           | 43  |

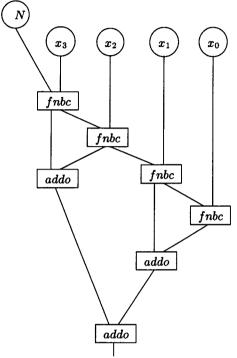

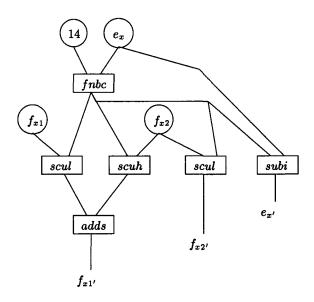

| 14     | Multi-digit fnbc example                                      |           | 50  |

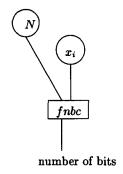

| 15     | Single-digit fnbc example                                     |           | 51  |

| 16     | Pre-normalization example                                     |           | 53  |

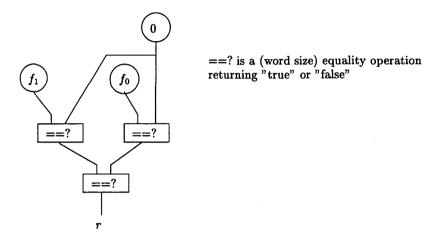

| 17     | Testing if $f=0$ for a two-digit value $f.$                   |           | 57  |

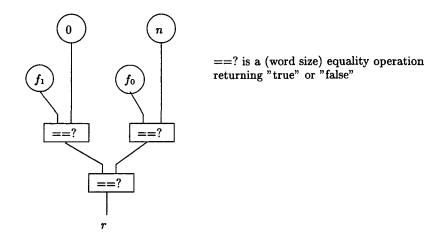

| 18     | Testing if $f = n$ for a two-digit value $f$ where $n \neq 0$ |           | 58  |

# List of Tables

| Figure |                                           | Pa | age |

|--------|-------------------------------------------|----|-----|

| 1      | XLU Digit Bit Patterns                    | •  | 20  |

| 2      | XLU Addition Operation Primitives         |    | 23  |

| 3      | The XLU Squash Operation Primitive        |    | 26  |

| 4      | XLU Subtraction Operation Primitives      |    | 27  |

| 5      | XLU Multiplication Operation Primitives   |    | 31  |

| 6      | XLU Scaling Operation Primitives          |    | 40  |

| 7      | XLU Normalization and Rounding Primitives |    | 49  |

| 8      | An example XLU floating-point number      |    | 52  |

#### An Alternative Architecture For Performing Basic Computer Arithmetical Operations

## 1 Introduction

# 1.1 Background

The manipulation of numbers lies at the center of every computer processor. The predecessors of electronic, digital computers such as Pascal and Leibniz's mechanical adding machines and Babbage's difference engine were designed specifically to help people perform basic arithmetic operations.

The potential of computing machines as "universal simulators" was recognized early (Babbage, Lovelace, Turing, et al. [Ran82]), and nowadays people regard them as much more than sophisticated adding machines. Nevertheless, the heart of any computer is a device that "knows" how to add, subtract, multiply and divide. (And often one or more of these four things are understood in terms of one or two of the others.)

Since basic arithmetic lies at the center of any computer, how computers perform basic arithmetic operations and the number representations they use when performing them has been an area of continual study and development for as long as there has been computing machinery.

Over the decades, as computer hardware and software have evolved, the methods through which computers perform arithmetic have converged from many, diverse methods to a few, similar methods. New improvements and innovations occur on a regular basis but the focus of attention has shifted from broad inquiry to narrow refinement.

Despite this narrowing of focus, there are many methods of representing numbers, and many ways of implementing basic arithmetic. In this thesis, we describe and explore the details of one such alternate implementation.

Our work uses no "new" discoveries or principles. At its center is a number representation first proposed over thirty years ago. What is new is the resulting whole; our overall design is a significant departure from the currently established norms for how a processor "should" do basic arithmetic.

In our alternative design we consider a computer arithemetic architecture based upon a number representation and arithmetic first described in the 1960s [Avi61], coupled with concepts taken from the Reduced Instruction Set movement of the 1980s, [CM90], [PH90] and ideas from the multiple, parallel-instruction execution units that have been incorporated into some computer designs from early mainframes (e.g. the CDC 6600 [BH92]) to present day high-performance microsprocessors (e.g. HP's PA-RISC [AAD+93], Intel's Pentium [AA93] and the Motorola/IBM PowerPC [BAM+93] architectures).

We believe that our ideas, which we collectively refer as "the XLU¹ architecture" provide an interesting and viable alternate to the established norm.

#### 1.2 Motivation

The work we present here was motivated and shaped by the following observations, the questions those observations raised, and the subsequent conclusions we drew from considering those questions.

A survey of the arithmetical portions of current microprocessor architectures DEC Alpha, Motorola/IBM PowerPC, Intel Pentium, Sun SPARC [PH90] reveals that all of them have these traits in common:

1. Hardware to directly support two number representations; integer and floating-point.

<sup>&</sup>lt;sup>1</sup>Following Knuth's naming convention for  $T_EX$ , We pronounce "XLU" as *clue*, giving X the  $\chi$  ("chi") sound.

- 2. CISC-type instructions embedded in special-pupose hardware to perform the floating-point arithmetic.

- 3. A set of (usually) simpler instructions, disjoint from the floating-point set, to perform the same operations for integers.

- 4. Although fixed-point arithmetic is the preferred representation for some situations, it is not supported as a native type (like integer and floating-point). Using fixed-point arithmetic means resorting to software. (The same observation holds true for complex arithmetic, etc.)

- 5. Double-precision arithmetic is often available, but there is no apparent consideration at the hardware level for handling arbitrary-precision numbers (e.g. if you need double-double-precision, you must resort to software).

These observations raised the following questions:

- 1. In light of observations 1, 4 and 5, can we design the arithmetic portion of a computer to use a single number representation (early machines got by with only one) yet efficiently support integer, fixed-point, floating-point and multiprecision representations and operations? If so, what characteristics would that number representation need to have?

- 2. Observation 2 applies even to machines that are otherwise completely RISC-based (e.g. the MIPS processor architecture [Cho89]). Research [Dal89] shows that there are advantages to exposing the sub-operations of floating-point arithmetic to compiler optimization but none of the commercially available architectures we know of do this.

- 3. Taken together, observations 2 and 3 imply that portions of the computers arithmetic hardware go unused some of the time. Special-purpose floating-point hardware is unused during integer-only calculations, and vice-versa. Some machines can make use of at least some of their

floating-point hardware for integer calculations, but the question raised remains interesting; can we design a machine that uses a maximal amount of its available arithmetical hardware for any/every calculation?

Exploring possible answers to these questions led us to design the arithmetical portion of a hypothetical microprocessor. This design encompasses the following distinct – yet related – attributes.

- 1. A single number representation that can serve as a base for a wide range of simple or complicated numerical types.

- 2. A set of algorithms to perform basic arithmetic (addition, subtraction, and multiplication division is shown to be possible but we do not address it) using this number representation.

- 3. The arithmetic op-codes for our hypothetical microprocessor. These op-codes, or *primitive operations* may be used to realize the algorithms mentioned above.

- 4. A software simulation of the op-code set, which was used to test the correctness of the algorithms and provide a base from which a larger simulator could be created.

- 5. Overall guidelines for how the processor might be organized to best take advantage of the number representation, algorithms and its op-codes.

#### 1.3 Outline

The following sections of this work describe the historical context from and around which our ideas evolved, the key points of the XLU architecture, how composite number representations may be derived from it, a discussion of hardware considerations for implementing it, a summary and evaluation, concluding remarks, a glossary, and a brief description of the simulator software we wrote to help form and test our ideas as we developed the work.

The history section gives an overview of how the task of doing basic arithmetic has evolved through the preceding decades. It focuses on number representations, instruction set architecture, some aspects of floating-point numbers (the peculiarity of CISC FP instructions, on otherwise purely RISC instruction sets is noted), and some aspects of parallelism within computer systems.

The evolution of these particular topics; number representation, instruction sets and parallelism informed and guided our own design efforts, which are presented in the key points section. Of central importance to our design is the reliance upon a single unifying number representation. We list the requirements that the representation must possess, note the work during the 1960s by Algirdas Avizienis that provided us with a suitable candidate, and describe the details of our *XLU digit* along with the primitive operations used to add, subtract, and multiply it.

Since the XLU architecture provides only one number representation, others deemed necessary must be derived from it. We discuss how this may be done in the composite representations section. Two representations are discussed as examples; fixed-point and floating-point. In doing so, the scalability and high degree of instruction-level independence of the XLU digit and its primitive operations is illustrated.

The hardware considerations section contains remarks and observations about the general requirements for actually implementing our design onto hardware. The XLU architecture specifies only a portion of an overall processor design and is meant to allow as much flexibility as possible to a processor architect, so the comments in this section are mostly guidelines, not specific directives.

The summary and evaluation section summarizes what we present in this work and addresses some of the things that we do not include, and why. The XLU architecture is evaluated in terms of feasibility, expected performance, and positive versus negative characteristics. Concluding remarks, the glossary and the description of the simulator round out the work.

## 2 Historical Contexts

Early digital computers managed to perform various types of arithmetic with one number representation and modest hardware. Since this is what we hoped to achieve<sup>2</sup>, a review of how computer arithmetic has evolved is worthwhile.

The subject of computer arithmetic is very large, so we confine our remarks to a brief overview of the topics especially pertinent to our own lines of inquiry. Our purpose is to set our own work in the context of what has been tried before, rather than present a detailed historical account. With that goal in mind we briefly sketch past practice and thought regarding the evolution of number representations, arithmetic algorithms and the hardware and software that implement them.

# 2.1 Number Representation

From the earliest mechanical devices that performed arithmetic through the first "real" computers of the 1930s and 1940s, the number representations used by computing machinery seem to have been kept fairly close to the number representation the user would work with (i.e. radix-10). Apart from magnitude, early representations carried little "auxillary" information per number. It was often left up to the user, for instance, to assign and track the radix point or sign of a particular quantity.

The flurry of electro-mechanical and electronic computers designed and/or built during the 1940s prompted investigation of how numbers could "best" be represented inside the machines.

Eckert and Mauchly's ENIAC [GG96] represented numbers as radix-10 integers (or fixed point numbers, if the user tracked the radix-point) and ex-

<sup>&</sup>lt;sup>2</sup>Albeit, with greater flexibility and performance than those early machines.

pressed negative numbers through a form of 10's-complement. The machine also appears to have had a "double-precision" capability:

The equipment normally handles signed 10-digit numbers expressed in the decimal system. It is, however, so constructed that operations with as many as 20 digits are possible.

ENIAC notwithstanding, the advantages of designing a computer's number representation around radix-2 were understood early on. Von Neumann's "First Draft of a Report on the EDVAC" [vN45] succintly articulates the primary tradeoffs inherent in the choice of a radix:

It takes more binary digits (hence more operations) to perform an arithmetic operation like addition or subtraction, etc., but using decimal arithmetic results in complex circuitry.

Von Neumann understood the tradeoff between computing run-time and component complexity. The inherent speed advantage the early electronic computers enjoyed over their electro-mechanical contemporaries, and the relatively high price and complexity of their individual components (vacuum tubes) led designers like Von Neuman to seek hardware simplicity first. Binary numbers looked like a good way to achieve this:

A consistent use of the binary system is likely to simplify the operations of multiplication and division considerably ... Binary arithmetics [sic] has a simpler and more one-piece logical structure than any other, particularly than the decimal one.

Around ten years earlier, in 1936, Konrad Zuse must have come to similar conclusions. His Z1 through Z4 series of computers were all based upon binary number representations. Several other early machines were also designed to represent binary number (Atanasoff's machine, the Harvard Mark-I, and

the Manchester Mark-I [Roj97, tables 2 and 3]) and by the 1950s, binary numbers for internal representation were the norm<sup>3</sup>.

Although the radix of choice (binary) was settled early on and with fairly rapid unanimity, general acceptance of the desirability for hardware support of floating-point numbers in addition to integers took more time and argument. This is unsurprising. Early electronic computing machinery had strictly limited hardware resources.

Floating-point arithmetic is convenient for users (like radix-10 numbers) and provides a large dynamic range for a given number of digits, but (again, like radix-10 numbers) it requires more information per number, hence more complex circuitry to implement. Floating-point arithmetic algorithms are more complex than their integer or fixed-point counterparts, which once again requires larger amounts of both time and space resources.

Among the early machines, only Zuse's Z1-Z4 machines supported floating-point as their native number type. Early computer designers only dreamed of having the hardware resources to support two or more native types on the same machine. The available machinery was just too precious.

Floating-point number representations were viewed as important and desirable, but too costly – "luxury" items, given secondary consideration, or second-tier support, if at all. The CDC 6600, for example, provided the instructions to produce either floating-point or integer results, but internally supported only one number representation – a 60-bit format that could be interpreted as either floating-point or integer, depending upon the instruction context [BH92].

As time passed the amount of circuitry that could be crammed into a given amount of surface area increased with a rapidity matched only by the drop in cost for that same amount of circuitry. As space and complexity became less expensive and more available, the constraints that argued against supporting

<sup>&</sup>lt;sup>3</sup>Von Neumann's report mentions the necessity (for human convenience) of incoporating decimal-binary and binary-decimal conversion hardware into input/output devices. The memory and processor internals, however "use strictly binary procedures." [vN45]

floating-point relaxed, and the argument shifted from whether to include it to how to include it efficiently, or what format to use. In the past decade this last question has been resolved in a majority of the available CPU designs through adoption of the IEEE-754 and IEEE-854 floating-point standards.

## 2.2 Instruction Set Designs

Arithmetic instructions formed a larger percentage of the instruction set for early computers than for their more powerful descendants. Computers were originally conceived as high-speed calculating engines and getting the machine to perform arithmetic correctly and quickly was the paramount aim. In fact prior to Wilkes et al.'s EDSAC (operational in 1949) and the notion of the "stored program computer", there wasn't much of a concept of instruction set architecture at all [PH90].

Tanenbaum [Tan90] writes:

The earliest digital computers were extremely simple. They had to be. It was hard enough to get them to work at all. From the ENIAC through the IBM 7094, and on to the CDC 6600, computers had relatively few instructions ...

Hardware rapidly developed greater potential capability per unit of space. The entire capabilities of the machine were no longer required to simply do arithmetic. As a result, designers had the freedom to incorporate more types of "basic" operations into their machines. Examples include floating-point and BCD arithmetic, character handling operations, multi-tasking and/or memory-protection primitives, etc.

Naturally, as instruction sets became increasingly large, multifaceted, and complex, the complexity of their hardware implementation increased. Implementing instruction sets by wiring the instructions directly into the hardware

became more and more difficult, costly, and error prone. All these factors led computer designers to establish a level of abstraction between the actual hardware capabilities of the machine, and the instruction-set interface as seen by the programmer. This abstraction was microcode and microprogramming.

With the advent of the IBM 360 architecture (in 1964) microprogramming took off in a big way. In a microprogrammed architecture, each machine instruction is actually a sequence of smaller, simpler instructions. Individual instructions may perform rather involved, complex tasks, the details of which are spelled out by the simpler, individual microperations of the instructions microprogram.

Two factors encouraged actually creating the sort of complex instructions made possible by microprogramming. The instruction-execution speed of a typical 1960s-1970s processor was quite high relative to memory access time. This situation encouraged minimizing fetches to and from memory. Since each instruction costs a significant amount of time to fetch, designers strove to supply instructions that individually performed a lot of work.

Also, computers were still frequently programed directly through the processor's instruction-set, rather than indirectly through a high-level language and translator. This situation led designers to favor "complex" or "powerful" instructions; i.e. instructions that offer many modes of usage or perform fairly complicated operations (e.g. add the contents of a register with the contents of a memory location pointed at by another register, storing the result to yet another memory location). Such instruction sets seek to provide abstraction away from the complexities of the processor internals while still directly presenting the processor's capabilities to the programmer.

Nearly all the prominent processor architectures of the 60s and 70s were built around relatively "high-level", complex instruction sets of the type that are now characterized as Complex Instruction Set Computers (CISC).

During the late 1970s and early 1980s, semiconducter technology brought ever-increasing gains in both time and space and designers began to question the premises upon which CISC designs were based. The cost to fetch an instruction from memory dropped (primarily due to caches). This implied that the tradeoff of fewer, slower instructions, each performing a complicated task versus many, faster instructions each performing part of the same complicated task should be re-evaluated.

As software projects expanded in size and scope, high-level languages gained increasing popularity and the quality of machine code they produced approached ever-closer the quality of hand-tooled assembly language.

Also, the complexity of microprogrammed assembly-language instruction sets had become increasingly significant. Microprogramming had been employed as an abstraction between the complexity of the instruction set and its hardwired manifestation in the machine. Microcode itself had grown so complex that proposals appeared for adding a "nanocode" abstraction level between the microcode and the bare hardware.

Several groups of computer designers idenpendently arrived at the same alternate solution. Observing that the complex instructions of the then-popular computer architectures were in fact often under-utilized, they proposed returning to a computer architecture based upon a few, simple instructions, each of which would be heavily utilized. Then, instead of adding extra levels of complexity to the machine's instruction set, they proposed adding extra complexity to the optimization portions of high-level language translators, to optimize sequences of the few, simple instructions. In short, simplify the hardware and deal with complexity in the more malleable medium of software.

The ever-increasing speed and sophistication of both memory and processors insured that although these new machines would have to execute many instructions to mimic the operations performed by one CISC instruction, the time to perform the overall task would be comparable, if not better.

Three designs from the early 1980s; the IBM 801, the Berkeley RISC-1 and the Stanford MIPS all differed from the status quo and form a basis for

the so-called Reduced Instruction Set Computer (RISC) design movement that followed.

RISC designs can vary significantly from one another, but all of them share common hallmarks. Among these are:

- 1. Simple instructions, designed to execute rapidly.

- 2. No microcode level the instruction set runs directly on the hardware.

- 3. Complex operations are short sequences of the provided simple instructions. The burden of efficiently executing these sequences is placed upon the compiler's optimizer.

- 4. Simple memory access model operands are LOADed from memory to registers, processed via an instruction, and the results are STOREd back into memory from registers. The LOAD/STORE instructions are decoupled from other instructions, which in turn only "know" about the registers.

The benefits this sort of design, as implied in the preceding paragraphs are that the burden of complexity is shifted to the very malleable medium of software (the language translator). This simplifies the hardware, and if the instruction set is carefully designed, allows that hardware to be as versatile as a good language translator will allow.

This is, of course, a tradeoff. Overall complexity is not dimished. It is shifted from a medium that is very static (the hardware) to one that is easier to change (the software).

In some ways, RISC computers are a return to earlier designs. Whereas in the early days, simplicity was sought because there was no alternative (due to the physical devices of the day), in recent years, simplicity was sought because it provided the best performance and the most versatility.

In both cases – early computers or latter-day RISC designs – the end result is a small, straightforward, simple architecture relative to the CISC machines developed in the intervening years.

## 2.3 A Note Concerning Floating-Point Support

It is interesting to note that while RISC design principles have become widely accepted and put into practice during the last decade, not all parts of modern processors are RISC-based.

Some recent processor designs (such as Intel's Pentium or Motorola's Coldfire architecture) are termed "hybrid" architectures, because they combine some RISC practices with some CISC. The motivation in hybrid designs is often to achieve both high performance and high code density, but even processor designs that are RISC throughout the rest of their instruction set and layout look like CISC machines in their support of floating-point.

### 2.4 Parallelism

The term "parallelism" has progressively encompassed several meanings as computer hardware has evolved.

In most early computers, all operations were performed one bit at time. Parallelism at the level of bitwise operations was an aspiration, but often not a practical reality.

The response times of the earliest electronic computers were extremely rapid, relative to their electromechanical forebears, while at the same time, their circuit complexity was limited by the fragility and size of their components relative to their silicon descendents.

Von Neuman addressed this matter in sections 5.5 and 5.6 of the EDVAC draft report [vN45]. He refers to performing arithmetic on all the bits representing a quantity at once as "telescoping operations", and while asserting the obvious attraction and value of such, offers cogent (for the time) reasons why "accelerating these arithmetical operations does therefore not seem necessary."

As circuit integeration and reliability increased, doing more at once became the order of the day at increasingly higher levels of the hardware design.

Processors began to work on chunks of bits at a time, instead of considering each bit individually. "Increasing the level of parallelism" during this era most often meant widening the number of bits the processor could handle at once – i.e., creating machines with ever larger data-words. The level of sequentalism rose to word-level. The bits of the word were processed in parallel, the words were processed in serial.

However, quite early on some pioneering designers attempted the next logical step of processing several words in parallel. Notable among these is the CDC 6600, capable of performing several instructions in parallel.

At this level of abstraction (machine word-level) the task of providing parallelism may be shared by both hardware and software, and there are combinations that use more or less of both. New specialized fields of study such as instruction scheduling arose.

The logical progression from one processor with multiple function units, exemplified in the early 1960s by the CDC 6000, and currently by nearly all high-end CPU's (e.g. the Intel Pentium, Motorola PowerPC and HP PARISC architectures) is to provide several processors connected via efficient communcations channels and all working in concert. Venerable examples of this "true-multiprocessor" design are the ILLIAC IV, the Cray-XMP, the Connection Machine of Thinking Machines Incorporated, and more recently, the Sequent Balance/Symmetry and the Intel Paragon architectures [BH92].

# 3 Key Points

In this section we present the central design ideas of the XLU architecture. We introduce the number representation that forms a base for the design, and arithmetic algorithms that can efficiently manipulate the number representation.

## 3.1 Representation

### 3.1.1 Representation Requirements

The XLU's number representation is of central importance. It must meet the following criteria:

- 1. It must carry enough information to allow it to serve as a basis upon which various other number representations (integer, floating-point, fixed-point, etc.) may be efficiently realized by the software or firmware utilizing the XLU primitive operations.

- 2. Efficiently realizing other number representations with multiple instructions implies rapid execution of those instructions. Therefore, our base number representation must lend itself to manipulation in a manner promoting as much instruction-level parallelism as possible. Since we must execute more instructions to perform, say, a floating-point addition than a traditional FPU would, we must perform those instructions faster i.e., in parallel.

- 3. The number representation must scale well. That is, the performance of multiples of the XLU machine word size must perform well relative

to the performance of operations involving only the XLU machine word size.

We believe that a signed-digit number, modified to carry additional information for signalling overflow or special conditions such as  $+/-\infty$  or IEEE NaN (Not-a-Number) fulfills all the requirements listed above.

A complete treatment of computer arithmetic using a signed-digit number representation first appeared in Avizienis 1961 IRE paper [Avi61]. In chapter 3 of Computer Arithmetic, Swartzlander [Jr.90a] lists the characteristics which make this representation attractive for our own work:

By reducing carry propagation to one digit position, signed-digit arithmetic forms the basis for cascadable on-line arithmetic algorithms.

and

Elimination of carry propagation allows online operations to be overlapped ... arithmetic operations can be overlapped by starting operations as soon as digits become available from previous operations (i.e., it is not necessary to wait until the previous operations have been completed).

## 3.1.2 Signed-Digit Number Representations

Chapter 2 of Koren's Computer Arithmetic Algorithms contains a concise summary of signed-digit number systems. We quote liberally from that source and Avizienis' original paper in this section.

A signed-digit system allows the following digit set:

$$x_i \in \{\overline{(r-1)}, \overline{(r-2)}, \dots, \overline{1}, 0, 1, \dots, (r-1)\}$$

(1)

where  $\bar{i}$  equals -i, and r is the radix of the particular number system. This is a relaxation of the requirement in conventional number systems that members of the digit set all be greater-than or equal-to zero. It provides signed-digit systems with the characteristic of redundant number representations.

As an example: If r = 10 and we restrict ourselves to two-digit numbers, there are 19 possibilities ( $[\bar{9}, ..., 9]$ ) for each digit of each two-digit number. This means for instance, that  $(01) = (1\bar{9}) = 1$ , and  $(0\bar{2}) = (\bar{1}8) = -2$ . Not every number representable in this example has redundant representations – the representation of zero is unique. Koren writes:

... adding some redundancy in a number system can be very beneficial. On the other hand, a high level of redundancy might be too costly, since a larger digit set requires a larger number of bits to represent each digit.

The redundancy of the number system as a whole may be reduced by restricting the digit set to a subset of the complete set available. The XLU representation is *maximally redundant*, that is, the complete set of available digits is used, so we will not discuss reduced digit sets here.

As an example, here are two signed-digit representations along with their "normal" decimal equivalent values. Both examples assume the following maximally redundant signed-digit (SD) number system:

radix:

$$r = 10$$

digit set:  $[\bar{9}, \bar{8}, \dots, \bar{2}, \bar{1}, 0, 1, 2, \dots, 8, 9]$

SD value  $1\bar{8}2 = (1)10^2 + (-8)10^1 + 2$

$= 100 - 80 + 2$

$= 22$

SD value  $\bar{1}53 = (-1)10^2 + (5)10^1 + 3$

SD value

$$\bar{1}53 = (-1)10^2 + (5)10^1 + 3$$

=  $-100 + 50 + 3$

=  $-47$

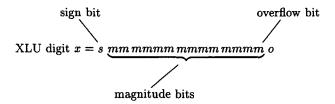

### 3.2 Details of the XLU Representation

XLU's number representation is thus based upon the signed-digit representation first discussed in Avizienis' [Avi61] paper. Henceforth, when we refer to an XLU digit we mean an entity having sign, overflow and magnitude bits. A particular XLU digit is defined as having the same number of bits as a particular XLU processor implementation's word size. For instance, if the XLU architecture is implemented on a 32-bit processor, with 32 bits per word, the XLU digit for this machine will have 32 bits.

However many bits are available, an XLU digit must encode the following three pieces of information; a value representing a magnitude, an indication of the sign of that magnitude (positive or negative) and an overflow indicator. The overflow indicator requires one bit. The remainder of the bits in the digit represent the magnitude of the digits value in two's-complement form which provides both sign and magnitude. For a word size of n total bits, the digit will have n-1 bits devoted to the digit's sign and magnitude, and the one remaining 1 bit to the overflow indicator.

Our choice of two's-complement form for the magnitude is somewhat arbitrary. The signed-digit representation properties that we wish to take advantage of are oblivious to the magnitude's encoding, and we could have used whatever we wished. We felt using an integral power of two would simplify our work (for example, in writing a software simulator) and among the common binary representations, two's-complement has "nice" properties and is the default encoding for integers on most modern machines.

The actual position of the overflow bit relative to the magnitude portion is not specified by the XLU design. Magnitude and overflow may be arranged within the digit/word in whatever way the implementor deems most suitable. (For example: The XLU simulator we created during the course of our work places the overflow bit in the low-order position, because this happened to make it easy to manipulate.)

Although the magnitude portion of the digit represents a numerical value in two's complement form, an XLU digit with m bits of magnitude has a range that is one less than a standard, m-bit, two's-complement integer. The range differs because the "extra-negative" pattern, characteristic of two's-complement representation is reserved as a *special pattern* by the XLU definition. For a value I, represented by m bits, the two's-complement range would be:

$$-2^{m-1} \le I \le 2^{m-1} - 1 \tag{3}$$

but the XLU digit range is:

$$-2^{m-1} - 1 \le I \le 2^{m-1} - 1 \tag{4}$$

The combination of the leading bit of the magnitude (the sign bit), the overflow bit, and whether or not all magnitude bits are equal provides twelve distinct patterns. What these patterns repesent is given in table 1.

Table 1: XLU Digit Bit Patterns

| s | magnitude | o | condition of the XLU digit       |

|---|-----------|---|----------------------------------|

| 0 | all zeros | 0 | zero                             |

| 0 | nonzero   | 0 | positive numeric value           |

| 0 | all ones  | 0 | maximum numeric value            |

| 0 | all zeros | 1 | positive overflow                |

| 0 | nonzero   | 1 | positive overflow                |

| 0 | all ones  | 1 | positive overflow                |

| 1 | all zeros | 0 | NaN (for $n/0$ )                 |

| 1 | nonzero   | 0 | negative numeric value           |

| 1 | all ones  | 0 | minimum numeric value            |

| 1 | all zeros | 1 | NaN (for $n + \text{overflow}$ ) |

| 1 | non zero  | 1 | negative overflow                |

| 1 | all ones  | 1 | negative overflow                |

In table 1, the s column shows the value of the sign bit, the magnitude column describes the state of the magnitude bits excluding the sign, and the o column shows the value of the overflow bit. The column entitle "condition of the XLU digit" gives the meaning of a particular combination of sign, magnitude and overflow bits. Apart from the "NaN" entries, the conditions should be self-explanatory.

The "NaN" (Not-a-Number) patterns allow the XLU digit to be used as a base for IEEE floating-point arithmetic. Note that there are two distinct patterns and two distinct NaNs. One signals the result of an illegal arithmetic operation (such as division-by-zero) and the other signals the result of a binary operation where at least one of the two operands was in an overflow state. Both types of NaNs are "sticky" – i.e. should the result of an operation produce a NaN, any future operation using that result will also produce NaN as *its* result.

## 3.3 Algorithms for Basic Arithmetic Operations

#### 3.3.1 Addition

According to Koren, "the original motivation for introducing SD numbers was to eliminate carry propagation chains in addition and subtraction" and this property shapes the way the XLU performs addition as well. We reproduce the general algorithm here as Koren [Kor93] <sup>4</sup> describes it.

We wish to perform the operation X + Y = S, for a signed-digit number system of radix r, where X, Y, S consist of signed-digits  $x_i, y_i, s_i$ :

$$X = (x_{n-1}, \ldots, x_0)$$

$Y = (y_{n-1}, \ldots, y_0)$   $S = (s_{n-1}, \ldots, s_0)$

<sup>&</sup>lt;sup>4</sup>As noted, the algorithm is first described in Avizieni's 1961 paper. We follow (and quote) from Koren's book here because its notation is more up-to-date.

The addition operation consists of two steps:

1. For each  $x_i$  and  $y_i$ , compute an interim sum  $u_i$  and a carry digit  $c_i$ :

$$u_i = x_i + y_i - rc_i \tag{5}$$

where:

$$c_{i} = \begin{cases} 1 & \text{if } (x_{i} + y_{i}) \geq a \\ 0 & \text{if } |x_{i} + y_{i}| < a \\ \bar{1} & \text{if } (x_{i} + y_{i}) \leq \bar{a} \end{cases}$$

$$(6)$$

with (for a maximally redundant system):

$$\overline{r-1} = \bar{a} \quad \text{and} \quad a = r - 1 \tag{7}$$

2. For each interim sum  $u_i$  and carry digit  $c_i$  compute a final sum  $s_i$ :

$$s_i = u_i + c_{i-1} \tag{8}$$

By removing the carry propagation chain, this algorithm effectively renders the addition algorithm *totally-parallet* at the digit level. Avizienis writes:

...each sum ...digit is the function only of the digits in two adjacent digital positions of the operands. The addition time for signed-digit numbers of any length is equal to the addition time for two digits. [Avi61]

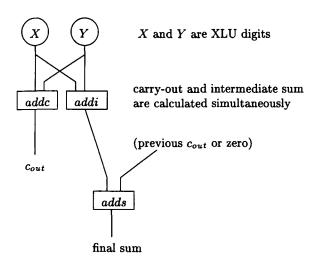

The XLU primitive operations for addition directly implement the various steps of the signed-digit addition algorithm. Table 2 lists the addition primitives and the parts of the signed-digit addition algorithm they perform.

The flow diagram in figure 1 shows how the XLU addition primitives may be employed to compute the sum of two XLU digits. As the flow diagram shows, for the case of two single digit numbers, the sum is immediately

<sup>&</sup>lt;sup>5</sup>I believe Avizienis originated the use of this term in this context.

Table 2: XLU Addition Operation Primitives

| Name                      | opCode                   | Function                             |

|---------------------------|--------------------------|--------------------------------------|

| Addition Intermediate Sum | addi $x_i, y_i, z_i$     | $z_i \leftarrow u_i$ , by equation 5 |

| Addition Carry Digit      | addc $x_i, y_i, z_i$     | $z_i \leftarrow c_i$ , by equation 6 |

| Addition Final Sum        | adds $u_i, c_{i-1}, z_i$ | $z_i \leftarrow s_i$ , by equation 8 |

Figure 1: Addition Primitives - Sum of two digits

available after the addi operation. In fact, since the addi operation will set the overflow bit of  $I_{sum}$  for cases where an addc would return 1, the addc operation is also only required for multi-digit work. For a single-digit-by-single-digit (i.e. word-by-word) addition, with a single-digit result, the XLU can deliver the result via a single addi operation. "Integer addition" as it is commonly available on conventional processors is therefore also available

under the XLU as a natural consequence of the design, and as a specific subset of the general scheme.

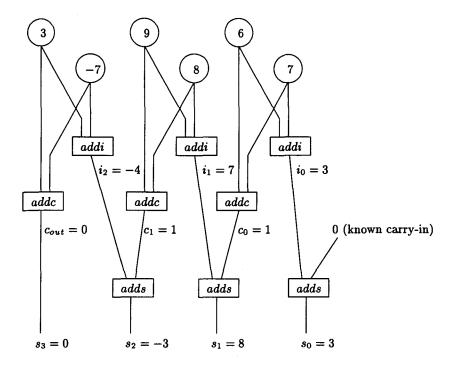

The completely parallel nature of addition at the digit-level provided by the signed-digit representation and choice of addition primitives is illustrated in the following 3-digit number by 3-digit number addition example. In these examples we will use the same digit set and radix used for signed-digit representation examples<sup>6</sup> on page 18.

The sum S of the 3-digit numbers:

$$X = 396$$

and  $Y = 787$

is computed by the following sequence of XLU addition primitive operations. The sequence makes use of temporary storage digits  $i_2, i_1, i_0$  and  $c_{out}, c_1, c_0$ . The final result is stored in  $s_3, s_2, s_1, s_0$ :

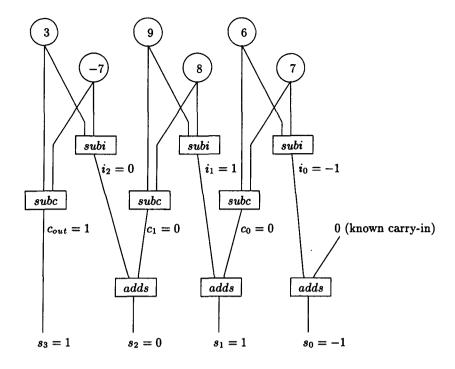

The sequence may be more easily visualized by the equivalent flow diagram shown in figure 2. Notice that regardless of the number of digits involved, all addi and addc operations may be performed in parallel (assuming adequate processor resources). All adds operations may be performed in parallel, pending completion of the addi and addc operations.

In general, the addition of two N-digit numbers can produce an N+1-digit result. For number schemes that allow dynamic scaling, overflow is handled

<sup>&</sup>lt;sup>6</sup>The radix-10 example from page 18 is used here rather than a radix-2 SD representation (as the XLU design specifies) because it makes the arithmetic examples easier to read. We will present examples that use "real" XLU digits later.

Figure 2: Multi-digit Addition Example

naturally (at least until the resources available on the system give out). For number schemes that require results to fit into a fixed number of digits (if our example's result had been constrained to three, for instance) some decision must be made about which portion of the result will be "lost".

Notice also, that our result of  $\bar{3}83$  is in a redundant form. It has the correct magnitude (-217), but in a signed-digit format. In general, signed-digit numbers may require extra processing to convert them to a non-redundant form. In general this may or may not be of concern, and the extra steps may be applied as seen fit.

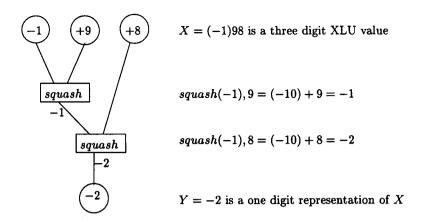

A slightly more important, and related case, however, is transforming a signed-digit number from a redundant form to a redundant form that requires fewer digits. For example; consider the three digit, radix-10, SD number 198,

which may also be represented by the single-digit number -2. The XLU squash primitive operation (see table 3) provides the ability to perform this conversion on multi-digit XLU values.

Table 3: The XLU Squash Operation Primitive

| Name                      | opCode                 | Function                                  |

|---------------------------|------------------------|-------------------------------------------|

| Convert multi-digit value | squash $x_i, y_i, z_i$ | $z_i \leftarrow (x_i \times radix) + y_i$ |

The squash primitive takes two XLU digits, assumed to be the neighboring digits of a multi-digit number. It returns the combination of the two as a single-digit value. The result may have its overflow bit set, if the two-digit input is not "squashable". The flow diagram in figure 3 shows how multiple squash primitives may be used in a "cascade" to attempt to compress an n-digit representation down to an (n-m)-digit representation. Unlike the highly parallel addition operations previously described, the squash instruction cascade is completely sequential. Each squash primitive must wait for its predecessor's result.

#### 3.3.2 Subtraction

The XLU instruction set performs subtraction through negative addition. The addend takes the part of the subtrahend and the negative of the augend takes the part of the minuend. The XLU primitive operations provided for support of subtraction are listed in table 4.

Figure 3: A multi-digit Squash "Cascade" Example

Table 4: XLU Subtraction Operation Primitives

| Name                         | opCode                         | Function                                          |

|------------------------------|--------------------------------|---------------------------------------------------|

| Negation                     | $\operatorname{neg}\ x_i, y_i$ | $\mid \text{neg } y_i \leftarrow \bar{x_i}$       |

| Subtraction Intermediate Sum | subi $x_i, y_i, z_i$           | $z_i \leftarrow \text{addi } x_i, \bar{y}_i, z_i$ |

| Subtraction Carry Digit      | subc $x_i, y_i, z_i$           | $z_i \leftarrow \text{addc } x_i, \bar{y}_i, z_i$ |

In early versions of the XLU design, the neg operation was provided to allow subtraction. It is a unary operation, taking an XLU digit as input, and returning the negative of that value. For example:

$${\rm neg}\ \bar{7} \to 7$$

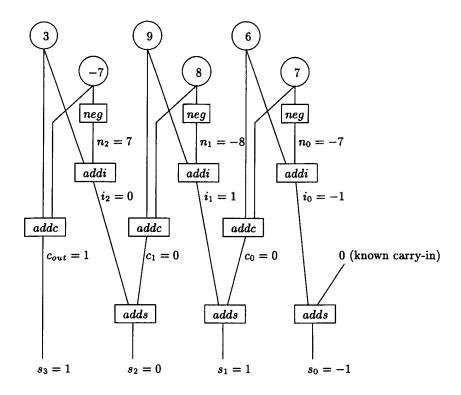

Inserting neg operations into the code sequences in the addition section converts them into subtraction algorithms.

Here is the XLU code sequence from the three-digit addition example, with neg operations inserted to convert it to subtraction. (Note the inclusion of three additional temporary storage values;  $n_2$ ,  $n_1$  and  $n_3$ ):

```

neg

7

n_0

8

neg

n_1

7

n_0

neg

addi

6,

n_0

i_0

addc

6,

n_0

c_0

9,

addi

n_1

i_1

addc

9,

n_1

c_1

3,

addi

n_2

i_2

addc

3,

n_2

c_{out}

adds

0

s_0

in,

adds

i<sub>1</sub>,

s_1

adds

c_1

s_2

(leftmost carry-out)

s_3

```

The flow diagram for our modified example is shown in figure 4. Notice that the result,  $101\overline{1}$ , of this example requires the full four-digit sum a 3x3 digit addition (subtraction) can incur. In this instance, if a maximum of less than three digits was allowable, a decision would have to be made as to what digit to throw away.

The neg operation alone is enough to provide support for subtraction, but the XLU defines two more operations for subtraction (see table 4). They are exact analogues of the addition intermediate sum and addition carry-digit operations, except that they perform the negation of the second argument prior to calculation. In effect, they encapsulate the neg portion of the subtraction example given above. No subtraction analogue for the addition final sum operation is needed or provided, since at that point in the computation sequence, the operation is identical for both addition and subtraction.

Figure 5 illustrates our subtraction example again, this time implemented with subi and subc operations instead of neg, addi, and addc. Encapsulating the negation operation removes a discrete step in the calculation sequence,

Figure 4: Subtraction-by-negation Example

reducing the required time, instruction count and intermediate storage, all at a minimal complexity cost for the underlying subi and subc implementation. Nevertheless, in order to provide the compiler with the largest possible set of options for code generation, the subi, subc and neg operations are all provided in the primitive operations set.

Figure 5: Subtraction Example

### 3.3.3 Multiplication

Multiplication is the repeated addition of partial products. For the addition portion of this task the parallelization potential of the signed-digit addition algorithm provides a good foundation to build upon. There remains the task of computing the partial products for the digits of the multiplication.

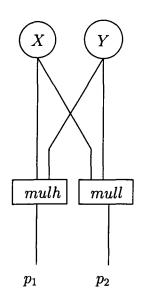

The result of multiplying an XLU digit by another XLU digit may be one or two digits. In order to keep the primitive operations regular (and therefor easier to process efficiently) we perform two "multiply" operations per XLU digit of the multiplicand and multiplier. One operation returns the value of the high-order digit of the product, the other returns the value of the low-order digit of the product. These operations are listed in Table 5.

Table 5: XLU Multiplication Operation Primitives

| Name                  | opCode                           | Function                                                           |

|-----------------------|----------------------------------|--------------------------------------------------------------------|

| multiply (high-digit) | $\texttt{mulh}\ x_i, y_i, z_i$   | $z_i \leftarrow p_1 \text{ of } p_1 p_0 \leftarrow x_i \times y_i$ |

| multiply (low-digit)  | $  \text{mull } x_i, y_i, z_i  $ | $z_i \leftarrow p_0 \text{ of } p_1 p_0 \leftarrow x_i \times y_i$ |

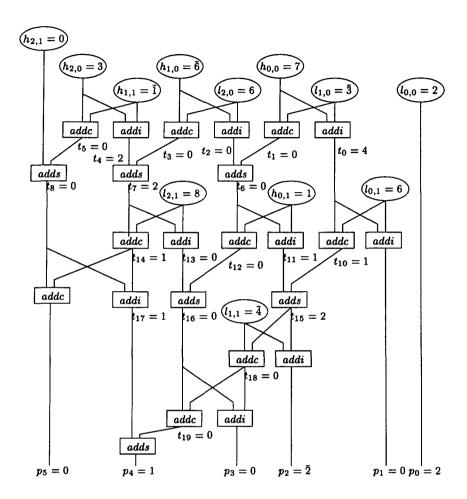

Here is an example of how these operations may be used to compute the high and low order results of the product of an digit-by-digit multiplication. For the simplest complete case, a 1-digit-by-1-digit multiplication, this flow diagram shows the sequence of operations: The 2-digit case in figure 6 forms the basic "multiplication cell" of multiple-digit XLU multiplication arithmetic.

For an n-digit multiplicand and an m-digit multiplier,  $n \times m$  multiplication cells are generated; one for each combination of multiplier digit and multiplicand digit. Each multiplication cell is complete independent of any other, and (assuming enough resources) all may be generated in parallel. The results of the multiplication cells are the partial products of the multiplication, and are then added together (using the addition operations described in section 3.3.1) to for the final product.

As an example, consider the product P of a 3-digit multiplicand X and a 2-digit multiplier Y where

$$X = 4\bar{7}8$$

and  $Y = 29$

Figure 7 shows the partial product generation, intermediate sum accumulation and final product as they might be generated if the intermediate values were generated "by pencil". Two sequences of XLU primitive operations

X and Y are XLU digits

high and low order product results can be calculated simultaneously

Figure 6: Multiplication Primitives - Product of two digits

comprise this 3x2 multiplication. First, the following sequence generates the necessary partial products.

mull  $l_{0,0}$  $h_{0,0}$ mulh  $\bar{7}$ , 9  $\rightarrow$   $l_{1,0}$ mull mulh mull  $9 \rightarrow h_{2,0}$ mulh  $2 \rightarrow l_{0,1}$ mull 8, 2  $\rightarrow h_{0,1}$ mulh mull

|   |   |   | 4         |           | 8 | (X)                |

|---|---|---|-----------|-----------|---|--------------------|

|   |   | × |           | 2         | 9 | $\frac{(Y)}{(Y)}$  |

|   |   |   | =         | 7         | 2 | (partial products) |

|   |   |   | $\bar{6}$ | $\bar{3}$ |   |                    |

|   |   | 3 | 6         |           |   |                    |

|   |   |   | 1         | 6         |   |                    |

|   |   | Ī | $\bar{4}$ |           |   |                    |

|   | 0 | 8 |           |           |   |                    |

|   | 0 | 3 | <u></u>   | 7         | 2 | re-arranging terms |

|   |   | Ī | 6         | $\bar{3}$ |   |                    |

|   |   | 8 | 1         | 6         |   |                    |

|   |   |   | $\bar{4}$ |           |   |                    |

|   | 0 | 3 | <u></u>   | 7         | 2 | accumulate         |

| + |   | ī | 6         | $\bar{3}$ |   |                    |

|   | 0 | 2 | 0         | 4         | 2 |                    |

| + |   | 8 | 1         | 6         |   |                    |

|   | 1 | 0 | 2         | 0         | 2 |                    |

|   |   |   | 4         |           |   |                    |

|   | 1 | 0 | $\bar{2}$ | 0         | 2 |                    |

Figure 7: 3x2 Multiplication Example "By Pencil"

Next, the following sequence accumulates final product from partial products through repeated application of the totally parallel addition algorithm.

$$\begin{array}{ccccc} \text{addi} & h_{0,0} & l_{1,0} & \rightarrow & t_0 \\ \text{addc} & h_{0,0} & l_{1,0} & \rightarrow & t_1 \end{array}$$

```

addi

t_2

h_{1.0}

l_{2.0}

addc

h_{1.0}

l_{2,0}

t_3

addi

h_{2.0}

h_{1,1}

t_4

addc

h_{2,0}

h_{1,1}

t_5

adds

t_1

t_2

t_6

adds

t_3

t_4

t_7

adds

h_{2.1}

t_5

t_8

l_{0,1}

addi

t_0

p_1

addc

t_{10}

t_0

l_{0,1}

\rightarrow

addi

t_{11}

h_{0,1}

\rightarrow

t_6

addc

t_{12}

t_6

h_{0,1}

addi

t_7

l_{2,1}

\rightarrow

t_{13}

addc

t_7

l_{2,1}

t_{14}

t_{15}

adds

\rightarrow

t_{10}

t_{11}

adds

t_{12}

t_{13}

t_{16}

addi

t_8

t_{14}

t_{17}

addc

t_8

t_{14}

p_5

addi

l_{1,1}

t_{15}

\rightarrow

p_2

addc

t_{15}

l_{1.1}

t_{18}

\rightarrow

addi

t_{16}

t_{18}

p_3

\rightarrow

addc

t_{16}

t_{18}

\rightarrow

t_{19}

adds

t_{17}

t_{19}

\rightarrow

p_4

```

Regarding the notation used in this sequence: The original digits of X and Y are shown in the primitive operations arguments as their values. Partial products are shown as either an  $h_{x,y}$  for the high-order value (generated by mulh) of digits  $X_x$  and  $Y_y$ , or an  $l_{x,y}$  for the low-order value (generated by mull) of digits  $X_x$  and  $Y_y$ . Intermediate sums and carry digits are notated by temporaries  $(t_n)$ .

To help clarify the sequence of XLU primitive operations, figure 8 shows a variation of figure 7. The partitial products and intermediate sums are represented by their temporary value labels from the sequence of XLU primitive operations.

Figure 9 shows a flow diagram corresponding to the sequence of XLU primitive operations that accumulate the partial products of the multiplication example into a final sum.

|         |                 |                                  |                                                                        | $x_2$                                                                                                       | $x_1$                                                               | $x_0$                                                  |

|---------|-----------------|----------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------|

| X       |                 |                                  |                                                                        |                                                                                                             | $y_1$                                                               | $y_0$                                                  |

|         |                 |                                  |                                                                        |                                                                                                             | $h_{0,0}$                                                           | $l_{0,0}$                                              |

|         |                 |                                  |                                                                        | $h_{1,0}$                                                                                                   | $l_{1,0}$                                                           |                                                        |

|         |                 |                                  | $h_{2,0}$                                                              | $l_{2,0}$                                                                                                   |                                                                     |                                                        |

|         |                 |                                  |                                                                        | $h_{0,1}$                                                                                                   | $l_{0,1}$                                                           |                                                        |

|         |                 |                                  | $h_{1,1}$                                                              | $l_{1,1}$                                                                                                   |                                                                     |                                                        |

|         |                 | $h_{2,1}$                        | $l_{2,1}$                                                              |                                                                                                             |                                                                     |                                                        |

|         |                 |                                  |                                                                        |                                                                                                             |                                                                     |                                                        |

|         |                 | $h_{2,1}$                        | $h_{2,0}$                                                              | $h_{1,0}$                                                                                                   | $h_{0,0}$                                                           | $l_{0,0}$                                              |

|         |                 |                                  | $h_{1,1}$                                                              | $l_{2,0}$                                                                                                   | $l_{1,0}$                                                           |                                                        |

|         |                 |                                  | $l_{2,1}$                                                              | $h_{0,1}$                                                                                                   | $l_{0,1}$                                                           |                                                        |

|         |                 |                                  |                                                                        | $l_{1,1}$                                                                                                   |                                                                     |                                                        |

|         |                 | 1                                | L                                                                      | $h_{1,0}$                                                                                                   | $h_{0,0}$                                                           | $\overline{p_0}$                                       |

|         |                 | $n_{2,1}$                        | $n_{2,0}$                                                              | 101,0                                                                                                       | ,,0                                                                 | PU                                                     |

| +       |                 | $h_{2,1}$                        | $h_{2,0}$ $h_{1,1}$                                                    | $l_{2,0}$                                                                                                   |                                                                     | PU                                                     |

| +       |                 | $\frac{h_{2,1}}{t_8}$            | $\frac{h_{2,0}}{h_{1,1}}$                                              | $l_{2,0}$                                                                                                   | $\frac{l_{1,0}}{t_0}$                                               | $\frac{p_0}{p_0}$                                      |

| ++      |                 | $t_8$                            | $\frac{h_{1,1}}{t_7}$                                                  | $\frac{l_{2,0}}{t_6}$                                                                                       | $\frac{l_{1,0}}{t_0}$                                               |                                                        |

| +       | $(p_5)$         |                                  | $egin{array}{c} h_{1,1} \ t_7 \ l_{2,1} \ \end{array}$                 | $egin{array}{c} l_{2,0} \ \hline t_6 \ h_{0,1} \ \hline t_{15} \ \hline \end{array}$                        | $l_{1,0}$                                                           |                                                        |

| + + + + | $(p_5)$         | $t_8 \ t_{14}$                   | $\frac{h_{1,1}}{t_7}$                                                  | $egin{array}{c} l_{2,0} \ \hline t_6 \ h_{0,1} \ \hline t_{15} \ \hline \end{array}$                        | $egin{array}{c} l_{1,0} \ t_0 \ l_{0,1} \ \end{array}$              | $p_0$                                                  |

| + + +   | $(p_5)$ $(p_5)$ | $t_8 \ t_{14}$                   | $egin{array}{c} h_{1,1} \ t_7 \ l_{2,1} \ \end{array}$                 | $\frac{l_{2,0}}{t_6} \\ h_{0,1}$                                                                            | $egin{array}{c} l_{1,0} \ t_0 \ l_{0,1} \ \end{array}$              | $p_0$                                                  |

| + + + + |                 | $t_8 \ t_{14} \ t_{17}$          | $egin{array}{c} h_{1,1} \ t_7 \ l_{2,1} \ t_{16} \ \hline \end{array}$ | $egin{array}{c} l_{2,0} \ \hline t_6 \ h_{0,1} \ \hline t_{15} \ l_{1,1} \ \hline \end{array}$              | $egin{array}{c} l_{1,0} \ t_0 \ l_{0,1} \ \hline p_1 \ \end{array}$ | $p_0$                                                  |

|         |                 | $t_8 \ t_{14} \ t_{17}$          | $egin{array}{c} h_{1,1} \ t_7 \ l_{2,1} \ \hline t_{16} \ \end{array}$ | $egin{array}{c} l_{2,0} \ \hline t_6 \ h_{0,1} \ \hline t_{15} \ l_{1,1} \ \hline \end{array}$              | $egin{array}{c} l_{1,0} \ t_0 \ l_{0,1} \ \hline p_1 \ \end{array}$ | $p_0$                                                  |

|         | $(p_5)$         | $t_8 \ t_{14} \ t_{17} \ t_{17}$ | $egin{array}{c} h_{1,1} \ t_7 \ l_{2,1} \ t_{16} \ \end{array}$        | $egin{array}{c} l_{2,0} \ \hline t_6 \ h_{0,1} \ \hline t_{15} \ l_{1,1} \ \hline p_2 \ \hline \end{array}$ | $egin{array}{c} l_{1,0} & & & & & & & & & & & & & & & & & & &$      | $egin{array}{c} p_0 \ \hline p_0 \ \hline \end{array}$ |

Figure 8: 3x2 Multiplication Example "By Pencil" Symbols

Figure 9: Partial Product Accumulation

# 4 Composite Representations

This section demonstrates how the XLU number representation and primitive operations may be used as a base from which other number representations may be created. We refer to such representations as *synthesized* representations, and in this sections we describe two examples: fixed-point and floating-point. We also introduce the XLU primitive operations provided specifically to support the needs of synthetic representations such as these.

#### 4.1 Fixed-Point Numbers

We use the definition of fixed-point numbers given in Koren [Kor93]: A fixed-point number X is a sequence of n radix r digits  $x_{n-1}x_{n-2}...x_1x_0$  that is partitioned into a fractional part of m digits as well as an integral (integer) part of k digits, with k + m = n. Quoting Koren:

The value of an n-tuple with a radix point between the k most significant digits and the m least significant digits

$$\underbrace{(x_{k-1}x_{k-2}\cdots x_1x_0}_{integral part} \cdot \underbrace{x_{-1}x_{-2}\cdots x_{-m}}_{fractional part})r \tag{9}$$

is

$$X = x_{k-1}r^{k-1} + x_{k-2}r^{k-2} + \dots + x_1r + x_0 + x_{-1}r^{-1} + \dots + x_{-m}r^{-m}$$

$$= \sum_{i=-m}^{k-1} x_i r^i$$

(10)

The radix point is not stored in the register but is understood to be in a fixed position between the k most significant digits and the m least significant digits. Therefore, we call such representations

fixed-point representations. The programmer of the digital computer is not necessarily restricted to the use of numbers having the predetermined position of the radix point but can properly scale the operands. As long as the same scaling factor is used for all operands, the add and subtract operations yield the correct results, since  $aX \pm aY = a(X \pm Y)$ , where a is the scaling factor. However, corrections are required when performing multiplication and division, since  $aX \cdot aY = a^2XY$  and aX/aY = X/Y.

It should be clear that integers are the subset of fixed-point numbers that have no fractional part. Koren writes "Commonly used positions for the radix are at the rightmost side of the number (i.e., pure integers, m=0) and at the leftmost side of the number (i.e. pure factions, k=0)."

#### 4.1.1 XLU Fixed-Point Number Representation

Substituting "XLU digit" for "digit" in the discussion above shows how naturally Fixed-Point numbers may be represented by the XLU architecture. A fixed-point number may be represented by one or more XLU digits, with the additional constraint that the radix point lies somewhere to the right of the leftmost bit of the leftmost digit, and somewhere to the left of the rightmost bit of the rightmost digit. (Otherwise, the value of digit or digits would be either a pure fraction or a pure integer.)

We leave tracking the position of the radix point to the higher-level (compiler, interpreter, other code-generation) abstraction layers, so the representation itself requires no additional complexity.

The information carried by the XLU digit, and the particular bit-pattern it shows at a given point in time does not change, although the interpretation of what it represents at that point in time may differ, depending upon where the higher-level abstraction chooses to "place" the radix point.

As an example, consider a hypothetical 16-bit implementation of an XLU digit X. Seen as a pure integer, 16 bits gives us a magnitude in the range of  $\pm 2^{14} - 1$  and a radix  $r = 2^{14}$  with the digit's radix point understood to be adjacent to the rightmost (low-order) magnitude bit.

But we can equally view the 14 bits of the magnitude as having the radix point positioned in the middle (i.e. between the 7th and 8th magnitude bits). The XLU digit now represents both integer and fractional parts, each with representable values according to equation (10) with k=m=7. The radix point could equally be placed between any of the other bits of the XLU digit (with k and m changed appropriately).

#### 4.1.2 Fixed-Point Arithmetic

The arithmetic operations given in section 3.3 apply without modification to an XLU digit sequence whether it represents a pure-integer, pure-fraction, or fixed-point number. However fixed-point arithmetic differs from pure-integer and pure-fraction arithmetic because of the possibility of scaling the operands.

When the scaling involves changing the radix point by an integral number of XLU digits, the change is "transparent" to the digits themselves. Whatever higher-level abstraction is keeping track of the radix position is expected to remember the fact that the radix is now between two different digits.

However, scaling by an integral number of digits is likely to be the exception. For cases where scaling involves changing the radix point's position by less than one digit's amount of bits, XLU primtives are provided. They accept an XLU digit x, and a value s to scale it by.

The scaling primitives work by shifting the magnitude bits of x s positions in the appropriate direction. The sign and overflow bits may play a part in a given scaling primitive's operation, but they are never shifted themselves.

Since both x and s are XLU digits, the range of s (i.e. the number of bit positions to shift) will far exceed the number of magnitude bits in x. For example, an XLU digit implemented in a 16-bit binary word has a total of fourteen magnitude bits, but can specify a maximum shift value of 16383 positions. The scaling primitives handle this discrepency by "maxing-out" at the number of magnitude bits for the particular implementation. Using the same example XLU digit, when an s value exceeds 14, all the magnitude bits are shifted, but "no more" shifting is done, i.e., s effectively equals 14 for values of [15, 16...16383]. Negative values in s equal a shift value of 0.

Name opCode **Function**  $y_i \leftarrow (x_i \times 2^{s_i}) - \text{maximum}(x_i)$ Scale up (high digit)  $\operatorname{scuh} x_i, s_i, y_i$ Scale up (low digit)  $y_i \leftarrow x_i \times 2^{s_i}$  $scul x_i, s_i, y_i$ Scale down (high digit)  $\operatorname{scdh} x_i, s_i, y_i$  $y_i \leftarrow x_i \div 2^{s_i}$ Scale down (low digit)  $\operatorname{scdl} x_i, s_i, y_i$  $y_i \leftarrow \text{maximum}(x_i) - (x_i \times 2^{s_i})$ Scale down intermediate "signed-digit-aware" scdl  $scdi x_i, s_i, y_i$

$scdc x_i, s_i, y_i$

"signed-digit-aware" scdh

Scale down carry

Table 6: XLU Scaling Operation Primitives

The individual scaling primitives are summarized in table 6. Like the multiply instructions, they are designed to be used primarily in pairs, with a given pair returning the high-word and low-word results of a given operation.

In the following paragraphs we explain each of these operations and provide simple examples of their use. For the examples, we use the 16-bit XLU digit implementation mentioned in the discussion above and summarized in figure 10.

In the examples that follow, we ignore the sign (s) and overflow (o) bits as the scaling primitives do<sup>7</sup> and show only the 14 magnitude bits in the diagrams.

<sup>&</sup>lt;sup>7</sup>This is actually only *mostly* true. The scdc and scdi pair are sign-aware.

Bit layout within each digit: