## AN ABSTRACT OF THE THESIS OF

<u>Gerald Lai</u> for the degree of <u>Master of Science</u> in <u>Electrical and Computer</u> <u>Engineering</u> presented on <u>August 25, 2006</u>.

Title: Development Test Suite for FPGA TekBot Learning Platform.

Abstract approved:

Roger L. Traylor

As the TekBots<sup>®</sup> program expands into senior and graduate level classes at Oregon State University, so does the need arise for more complex learning platforms. These complex hardware platforms cannot be adequately tested in a manufacturing environment as we have done previously. Also, due to their complexity, these platforms require substantial collateral documentation to allow first-time users to quickly become productive learners.

This thesis details the development of a post-manufacturing test suite, known as OMICRON, to comprehensively test an FPGA learning platform. It also documents the development of a user guide for the board that explains user accessible features as well as providing the necessary startup information so students can quickly become acquainted with the new learning platform.

While developing OMICRON, a new feature surfaced that provides a cycleaccurate hardware testbench debugger for testing student component modules that are implemented within the FPGA. This functionality serves a practical as well as an educational use by enabling test generation for detecting logic errors at a hardware level. Students can probe their own designs from an intuitive low-level command line interface once the designs have been loaded into the FPGA. The debugger can also be used to probe external circuits connected to the FPGA.

In addition to simple probes, the hardware debugger is able to output testbench bit vectors in a continuous flow, and simultaneously receive cycle-accurate vector results. These test vectors can either be manually constructed, or extracted from simulation software. This thesis shall also demonstrate this unique test flow. ©Copyright by Gerald Lai August 25, 2006 All Rights Reserved

## Development Test Suite for FPGA TekBot Learning Platform

by

Gerald Lai

## A THESIS

submitted to

Oregon State University

in partial fulfillment of the requirements for the degree of

Master of Science

Presented August 25, 2006 Commencement June 2007 Master of Science thesis of Gerald Lai presented on August 25, 2006

APPROVED:

Major Professor, representing Electrical and Computer Engineering

Director of the School of Electrical Engineering and Computer Science

Dean of the Graduate School

I understand that my thesis will become part of the permanent collection of Oregon State University libraries. My signature below authorizes release of my thesis to any reader upon request.

Gerald Lai, Author

## TABLE OF CONTENTS

| 1 TEKBOTS PROGRAM AT OREGON STATE UNIVERSITY                    | 1  |

|-----------------------------------------------------------------|----|

| 1.1 TekBots – An engineering initiative                         | 1  |

| 1.2 Summary of common terms                                     | 3  |

| 1.3 Goals of the TekBots program                                | 4  |

| 2 PLATFORM FOR LEARNING                                         | 9  |

| 2.1 The Platform for Learning <sup>TM</sup> concept             | 9  |

| 2.2 Learning platforms                                          | 12 |

| 2.2.1 Integration of educational strategies                     | 13 |

| 2.2.2 Attributes of effective learning platforms                | 14 |

| 3 FPGA LEARNING PLATFORM                                        | 19 |

| 3.1 Introduction of a new FPGA-based learning platform          | 19 |

| 3.2 Features of FPGA learning platform                          | 20 |

| 3.3 Advantages of FPGA learning platform                        | 24 |

| 4 FPGA BOARD TEST ENVIRONMENT                                   | 27 |

| 4.1 FPGA core in a self-testable system                         | 27 |

| 4.2 Development test suite for FPGA board                       | 28 |

| 4.2.1 OMICRON development test suite implementation             | 29 |

| 4.2.2 How OMICRON performs tests on FPGA board                  | 37 |

| 4.2.3 OMICRON modes of operation                                | 41 |

| 4.3 Post-manufacturing requirements and test flow using OMICRON | 44 |

# TABLE OF CONTENTS (Continued)

Page

| 5 OMICRON CYCLE-ACCURATE TESTBENCH DEBUGGER   | 47 |

|-----------------------------------------------|----|

| 5.1 Description of OMICRON testbench debugger | 47 |

| 5.2 Testbench debugger implementation         | 49 |

| 5.3 Module debugging using OMICRON            | 51 |

| 5.3.1 Using command line interface            | 51 |

| 5.3.2 Using testbench vectors                 | 53 |

| 5.4 Comparison with work by Niggemeyer et. al | 68 |

| 6 CONCLUSION                                  | 71 |

| Bibliography                                  | 73 |

| Appendix                                      | 77 |

| USER GUIDE FOR FPGA LEARNING PLATFORM         | 78 |

# LIST OF FIGURES

| Figure                                                              | Page |

|---------------------------------------------------------------------|------|

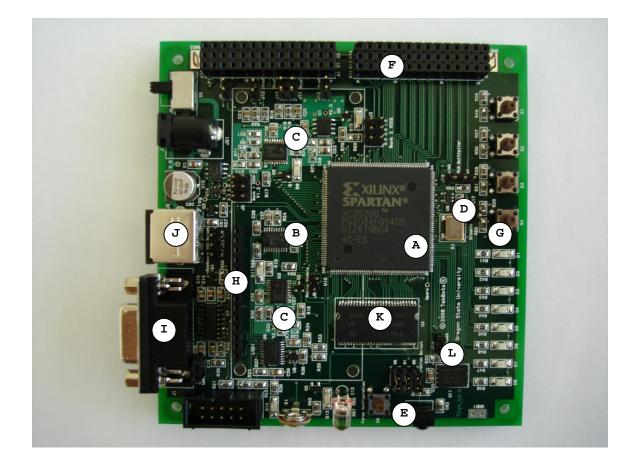

| 1. FPGA learning platform board                                     | 21   |

| 2. Structure of OMICRON                                             | 30   |

| 3. PicoBlaze microcontroller core                                   | 32   |

| 4. OMICRON data output register                                     | 33   |

| 5. 8-bit walking-ones/zeroes example                                | 40   |

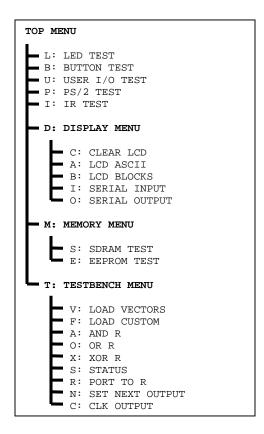

| 6. OMICRON terminal menu hierarchy                                  | 42   |

| 7. OMICRON non-terminal options                                     | 43   |

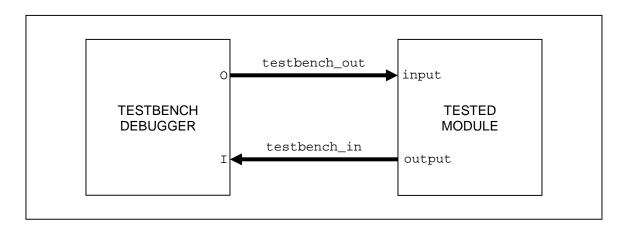

| 8. Testbench debugger operation                                     | 48   |

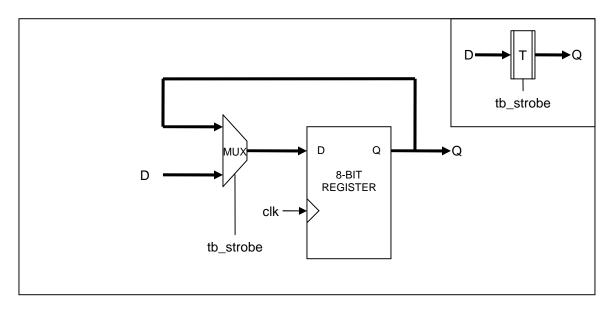

| 9. OMICRON testbench output register                                | 50   |

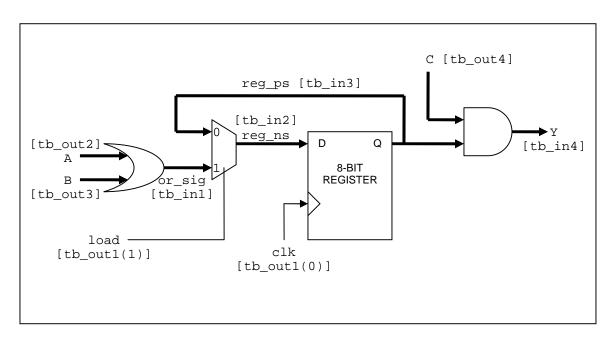

| 10. OMICRON testbench menu commands                                 | 51   |

| 11. Status of testbench debugger                                    | 52   |

| 12. Tested module example                                           | 54   |

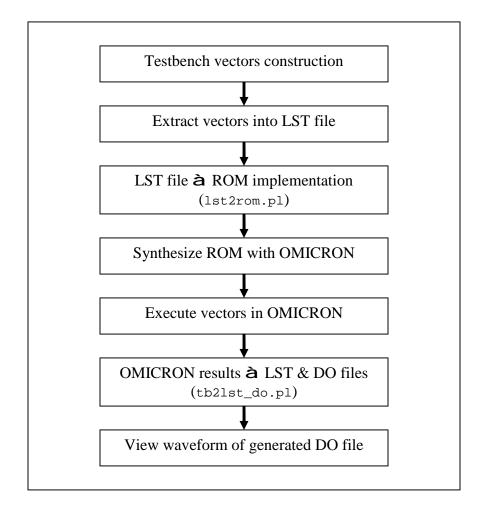

| 13. Testbench vector test flow                                      | 55   |

| 14. DO file (testmodule.do) to create vectors and generate waveform | 56   |

| 15. ModelSim waveform of original simulation                        | 57   |

| 16. ModelSim extracted list window                                  | 58   |

| 17. LST file (omi_vector.lst) of extracted vectors                  | 58   |

# LIST OF FIGURES (Continued)

| <u>Figure</u> Page                                                            |

|-------------------------------------------------------------------------------|

| 18. VHDL file (omi_vector0.vhd) of ROM implementation                         |

| 19. Synthesize ROM implementation with OMICRON61                              |

| 20. Saved testbench debugger output (debug.tb)63                              |

| 21. LST file (debug.lst) of testbench debugger output64                       |

| 22. DO file (tb_wave.do) to generate waveform of testbench debugger signals65 |

| 23. VHDL file (omicron.vhd) of OMICRON mock system to view waveform           |

| 24. ModelSim waveform of mock system vs. original simulation (bottom)67       |

| 25. HP83000 IC tester base69                                                  |

# LIST OF TABLES

| Table                                                            | Page |

|------------------------------------------------------------------|------|

| 1. Educational strategies that enhance engineering education [2] | 9    |

| 2. Platforms to teach digital logic fault detection              | 70   |

## **Development Test Suite for FPGA TekBot Learning Platform**

## **1 TEKBOTS PROGRAM AT OREGON STATE UNIVERSITY**

## 1.1 TekBots – An engineering initiative

In what began as a simple class-based project at Oregon State University (OSU), the TekBots program [1] has grown and matured into an innovative, and effective, means of educating upcoming student engineers. Under the TekBots program, Electrical and Computer Engineering (ECE) students keep their TekBot throughout their years in college, and continue to build on them as they take additional classes. When complemented with the traditional in-class methods of learning, the TekBots program helps to capture the essence of education. For instance, intangible qualities such as a student's commitment and tenacity to excel in her or his school assignments are evident in the work of a student's TekBot.

TekBots are learning platforms that students build to reinforce engineering concepts they learn in class. Specifically, a TekBot for an ECE student currently takes the form of an electronic robot. Since the TekBots stay with the students throughout the curriculum, this encourages personal ownership and attachment of the students for their TekBots. This fact alone yields many advantages. Once students are passionate about the work that is required to build a TekBot, they work harder, learn better, and interact more with peers [2, 3]. When students are engaged in the multitude of learning activities the TekBots program has to offer, they begin to work more intensely on their projects, and are able to learn and absorb more of the lecture material.

The class project that eventually led to the creation of the TekBots program was influenced by a program to teach ECE topics in context at Carnegie Mellon University (CMU) [4, 5, 6]. The goal that Carley et. al. was trying to achieve was to teach ECE courses to first semester freshmen without relying on an extensive background in mathematics or physics. This was done by taking a behavioral, or top down, modeling approach for the devices that were taught in class. For example, the behavior of nonlinear electronic devices was characterized using piecewise linear modeling techniques. By learning these simplified behavioral models for nonlinear devices such as diodes and transistors, rather than complex nonlinear equations, they believed that students may actually develop a better insight into the operation of electronic circuits.

The CMU program focused its effort of contextual teaching around a small programmable robot. This idea was adopted at OSU as a practical laboratory tryout for a class project in a freshman-level ECE course. While working on the project, students found the hands-on experience of physically building an extensible electronic robot to be fun and fulfilling. The extensibility of the robot meant that more circuit boards were allowed to be stacked on top of the original circuit board base. This continued to engage students in improving the functionality of the robot well beyond what was intended for the project in the first place.

From the enthusiasm the students showed, OSU faculty recognized that they had stumbled upon an opportunity to integrate the dynamic learning environment, which was observed in the laboratory, to the entire curriculum. The next major step was to take the approach of incorporating the project into the existing syllabi such that it would tie together the subjects being taught into a coherent whole. This would involve having a project that evolves with the students as they progress through the curriculum.

At the same time, a proposal to Tektronix was secured for a grant of USD\$500k that would allow OSU to continue its pursuit in creating a learning platform based curriculum for ECE students. This was the birth of the TekBots program at OSU in which the original robot project was given the catchy name "TekBot". The grant from Tektronix was the boost that allowed additional grants and parts donations to be subsequently leveraged towards the improvement of the program.

So far, the TekBots program has already been implemented for many engineering classes at OSU since 2002, including five Electrical & Computer Engineering classes, two College of Engineering courses, and one Mechanical Engineering class. It has also been adopted by other universities, such as Texas A&M, the University of Nebraska, and the Fukuoka Institute of Technology in Japan.

With the help of the learning platform, the TekBots program incorporates real-world instances to help students develop competencies in innovation, community, design, troubleshooting, and professionalism [2, 3, 7]. This adaptability of the Platform for Learning<sup>TM</sup> concept makes it a powerful catalyst that could reinvent not only engineering education as a whole, but also education for other disciplines besides engineering. Chapter 2 of this thesis shall expound the concept and ideals for effective learning platforms in more detail.

## 1.2 Summary of common terms

Before proceeding further, common terms used throughout this thesis will be defined to prevent misinterpretations. A brief description for each of the terms is given below:

**Platform for Learning**<sup>TM</sup> concept: This concept refers to the educational strategy that is comprised of ideals to teach students effectively in a dynamic learning environment. It is also known as the **Platform for Learning**<sup>TM</sup> model.

*Learning platform*: A learning platform is an object used to implement the educational strategy of the Platform for Learning<sup>TM</sup> concept. Sometimes, it can also be referred to as a *platform for learning*. Depending on the context, this is not to be confused with the actual concept that is a proper noun. Students usually begin with a bare bones learning platform. As they progress through their curriculum (e.g., a 4-year college program), they continue to build on it. The platform can be a physical or virtual object.

*TekBots*® *program*: The TekBots program is an engineering educational initiative that uses learning platforms as well as other proven learning methods to attain the goals of the program.

*TekBot*: A TekBot is one of the learning platforms presently used at OSU. It consists of electronic circuitry mounted on a sheet metal base with motors attached to wheels. This type of TekBot is loosely referred to as a robot. ECE students use this platform to apply and validate the knowledge they have acquired in class.

*TekBots*: The word "TekBots" has different interpretations depending on the context. It can be used to indicate more than one TekBot. It is also used to refer to the TekBots program that was created at OSU. One of the most common misinterpretations is to use "TekBots" to refer to a robotics program. The TekBots program at OSU is not a robotics educational program. However, the robot learning platform is (correctly) referred to as a robotics platform.

#### **1.3 Goals of the TekBots program**

The TekBots program is directed towards a central set of objectives. Listed below are the main goals for the TekBots program and how they are reached. For each goal, it is clear to see how the use of a learning platform is vital.

#### (a) <u>Improved learning</u>

The TekBots program aims to improve learning by adopting several proven teaching strategies. The most obvious strategy, given a physical learning platform, is to increase the retention of knowledge in students by adopting a *hands-on* learning style. By having students apply concepts learned in class towards building physical robots, the class knowledge is then "converted" into a more useful and concrete form. The physical robot becomes the result of the application of that knowledge. As long as the student remembers how the robot was constructed, the concepts acquired in class that were used to build the robot can be recalled in a natural manner.

The learning platform also enhances learning by *giving purpose* to what students have learned in every class. For example, freshmen ECE students are usually taught how to read voltage drops across resistors in a passive resistor-only circuit. A learning platform at this stage may be a simple flashlight made from an ultra-bright light-emitting diode (LED), a switch, a battery, and some odd valued resistors in order to test the student's knowledge of creating a resistor network with the right Thevenin resistance. The product of this simple project is a cheap flashlight that students can take home. A small competition can even be held to see which student can achieve the lowest cost with the brightest flashlight that lasts the longest, given that the students are to purchase each of the odd valued resistors for a certain price.

By giving theoretical concepts a practical home, student intuition is also improved tremendously. Practical demonstrations give students a better insight and "feel" into engineering concepts. As a follow-up from the previous example, students who proceed on to learn about capacitors can modify their flashlight resistor-only circuit to include capacitors, more resistors, and an extra LED. From this, a blinker circuit can be constructed to alternately blink 2 LEDs one at a time. This can be useful to demonstrate the concept of a time constant by having students tweak RC values to affect the rate of the blinker.

Another learning strategy used is *just-in-time learning* [2, 8]. Students are led through a problem to a place where no obvious solution can be obtained with their present level of knowledge. At that point, a new solution method or approach is introduced. This gives students new ways to overcome the problem.

Some of the old methods of teaching may lack appeal to the younger generation of upcoming students that were raised in the age of media globalization and the Internet. The old tried-and-true ways of teaching engineering subjects have encouraged a staunch tradition to continue teaching new students using methods that have been around for a long time. This presents challenges in attracting and retaining engineering students who often lose interest in engineering because of the slow build-up to the upper-level courses where they finally learn and apply discipline-specific knowledge [3].

One of the main reasons for the lack of interest is that these new students that are introduced to engineering concepts are given very little guidance in terms of the direction they are heading in with the knowledge they are attempting to learn. The build-up of knowledge in lower-level courses offers no end in sight. Many do not persevere to the upper-level courses when "things start to get interesting". This is because topics are usually taught in isolation, perhaps for the unspoken reason to ease the topic separation process for the sake of exam coverage.

Topics taught in isolation form islands of knowledge in a student's understanding that are not very useful on their own and degrade quickly over time. The TekBots program enhances learning by *linking islands of knowledge* together through the use of a learning platform. This linking occurs within a class and also between classes in a curriculum.

#### (b) Produce work-ready graduates

When students are immersed in fun *real-world projects* complete with real problems, they end up gaining useful practical experience. There are a host of skills learned in the context of a real project that are directly applicable in the real world but are not taught in traditional curriculums. For example, a real-world project can teach students how to troubleshoot a malfunctioning system, how to choose the correct capacitor for a circuit, or how to setup an oscilloscope in delayed sweep mode. These skills set them apart from students who come from a traditional lecture-homework-test-based education system.

TekBots program projects make use of *contemporary tools and practices* that mimic established design flow processes often found in the engineering industry. Crippled simulators and stripped-down tools are not part of the curriculum. An atmosphere of the real engineering world is kept intact by having students use the tools they will use after leaving the university.

When working in a real-world setting, students are exposed to interaction within a *community of learners*. The mutual benefits that are generated within the community foster a warm and welcoming environment where students can learn and experiment at their own pace, and be encouraged along the way. The community of learners also serves an indirect purpose of teaching students the life-long communication and cooperation skills. Studies have shown that cooperative learning tends to stimulate academic diversity and personal growth [9]. This would result in work-ready graduates who are more likely to succeed because of social interaction within the community of learners as well as the community at the work place. In contrast, graduates who are unprepared often find

themselves rushing to acquire skills in the competitive work-place environment without realizing how vital it is to have community support.

It is important to point out that not all graduates go out to find jobs. Some may choose to remain in academia. Nonetheless, the experience that the TekBots program offers still applies in producing graduates who are ready to join and support the academic research community.

#### (c) Create innovative students

The TekBots program sees innovation as something that needs to be nurtured steadily. It is a worthy investment because even though innovation takes time to build, it is a trait that is hard to relinquish once the student has earned it.

Current teaching methods that churn students through the cycle of lectures, assignments and exams only measure the retention level of students for the knowledge they have acquired throughout the duration of the class. These teaching methods deal mostly with the quantitative aspects of education (i.e., assignment and test scores) in the hopes that the qualitative aspects will improve. This passive education approach of ignoring the qualitative aspects, such as innovation, creativity, craftiness, maturity, and professionalism, creates an environment that is detrimental to these intangible traits.

When it comes to students flexing their innovative skills at problem-solving, the exercises offered on paper are often found to be boring, contrived, and sanitized with no loose ends or real constraints, and typically have only one correct solution [2]. If students find that they keep arriving at the same solutions as their peers for the problems presented in class, they will be discouraged from looking for other better solutions and begin to take the problem-solving process for granted.

Instead, students should be allowed the freedom of *multiple solution paths* to a given open-ended problem, much like how it would be in a real-world situation. This vital factor does not stifle growth and would encourage the students' capacity for innovation.

To nurture innovation, first, students are *inspired at the freshman level*. They are introduced to great work that has been done in the past by engineers, and shown what heights can be achieved by good innovation. From the beginning, students should be provided with easy avenues accessible for academic development. New students need to be shown creative possibilities in a direct manner to give them that extra push to explore an innovative solution. This is different from spoon-feeding students into performing the same solution task repeatedly term after term.

Innovation is *fueled by the flexibility* of the learning platform. For this reason, a TekBot is modular and is composed of replaceable modules. These modules function a lot like LEGO [10] building blocks that could be put together. Parts of the robot circuitry can be customized, within reasonable constraints, by students any way they wish. In fact, similar work has been done before by Jadud with LEGOBots at Indiana University [11]. He has proposed TeamStorms as a way to teach robotics by making use of the LEGO Mindstorms Robotics Invention System [12]. According to Jadud, the problem-solving process should allow room for creativity, and be fun, open-ended and challenging at the same time.

## **2 PLATFORM FOR LEARNING**

## 2.1 The Platform for Learning<sup>TM</sup> concept

The Platform for Learning<sup>TM</sup> concept described in the previous chapter defines how the TekBots program is executed. It is an educational strategy that strives to bring together other effective and successful educational strategies into one combined package. It anchors its own educational strategy plan in an omnipresent learning platform to bring out the best practices in a dynamic learning environment. The general underlying idea of having a student apply what she or he has learned in class to a platform, and then having that platform relate back to the student as they both evolve, is key to the TekBots program at OSU. An electronic robot acts as the learning platform for the ECE program at OSU, and the TekBots program acts as the vehicle that carries out the educational strategy outlined by the Platform for Learning<sup>TM</sup> concept.

| Educational<br>Strategy        | Description                                                                                        | Impact                                                                                                                                                    |

|--------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Active/cooperative<br>learning | Instructional activities engage<br>students in doing and thinking<br>instead of passive listening. | Improved retention.<br>Higher academic achievement.<br>Improved individual accountability.<br>Improved small-group skills.<br>Enhanced creative thinking. |

| Technology<br>enhancement      | Computing resources introduced into<br>classroom to enhance learning by<br>using software tools.   | Increased comfort level using<br>computers as tools.<br>Mundane tasks reduced to allow focus<br>on higher-order thinking.                                 |

| Just-in-time learning          | Theoretical concepts introduced<br>when students' experiences create<br>a demand for them.         | Improved academic performance.<br>Life-long learning skill development.<br>Theory and practice kept in context.                                           |

| Curriculum<br>integration      | Learning activities restructured to<br>build contextual connections<br>between topics.             | Enhanced ability to transfer<br>knowledge to new situations.<br>Better program retention because of<br>material relevance.<br>Better recall of material.  |

Table 1: Educational strategies that enhance engineering education [2]

By definition, a platform for learning is a *common unifying object or experience* that weaves together the various classes in a curriculum [2]. It is a concrete yet dynamic system that is built upon as students progress through the curriculum. This helps students to better grasp the connection between concepts presented in a variety of classes and gain a much richer understanding of a discipline as a whole [7].

The Platform for Learning<sup>TM</sup> concept also applies effectively to other fields of study besides engineering. For other fields of study, a learning platform can be something that is non-physical. For example, a business student may use a business plan as a learning platform. That business plan would be modified and adapted accordingly to the syllabus that is currently being taught. A computer science student, on the other hand, may start with a basic shell program that would eventually be built into a full-fledged OS (Operating System).

The ideals of the Platform for Learning<sup>TM</sup> model advocate a fresh perspective in education organization. This is to incorporate the learning platform into the entire curriculum in order to energize and consolidate the engineering topics that are taught in class and in laboratory work. By using a common learning platform throughout a degree program, the integration of knowledge is enhanced. The platform also provides the conceptual "glue" between lecture topics [2].

In a practical sense, the syllabi for the entire curriculum are tweaked slightly in such a way as to arrange the engineering topics to provide a coherent flow between the core courses and the learning platform activities. When topics are introduced to students in an incremental logical manner, the students are able to get more out of the entire experience. When that experience is coupled with a valuable platform that is used to experiment and demonstrate the concepts that are learned in class, this will solidify the students' understanding and increase retention of knowledge.

As mentioned in the previous chapter, the TekBots program capitalizes on the Platform for Learning<sup>TM</sup> concept by introducing a robot as the learning platform that ties experiences together from various different areas in engineering such as electronics,

mechanics, communications, systems programming, and testing. The robot motivates lecture topics and meshes them with laboratory experiences. This expands the learning opportunities and effectiveness in multiple dimensions by providing a context for learning that connects the knowledge among classes, develops innovative abilities, and enhances troubleshooting skills [2].

One goal is to have students realize that even though there exists a hierarchy of knowledge which stems from basic fundamentals, the application of engineering knowledge is inevitably interrelated and interwoven with other disciplines of knowledge. The transition of engineering education to embrace a *transdisciplinary* model that integrates the use of the tools, techniques, and methods from various disciplines is vital for its future welfare.

At the moment, educational programs face many difficulties because of the rapid change of technology in today's environment [13]. According to Ertas et. al., the *transdisciplinary* model does not mean that the traditional engineering disciplines must be completely disassembled. It does mean, however, that the areas of knowledge typically included in each of the disciplines will be presented within the transdisciplinary structure, and that the boundaries between the knowledge areas will be much more porous.

While there is a need to push forward in the multi-discipline direction, studies have shown other directions of adapting learning effectiveness that we also need to centralize our efforts on. For instance, one area of study focuses on a *learner-centered* approach to education which states that knowledge must be actively constructed by learners and not passively transmitted by teachers [14]. Catalano et. al. proposed using visual tools in a learner-centered environment to assist students in "seeing" how information can be connected, and to teach them to use these tools independently themselves [15]. This was accomplished in a group-learning setting that provided a non-threatening "no risk" mechanism for indirect dialogue between teachers and students. There has also been a lot of research in the area of *cooperative learning*. Clark found that when a multimedia group project format was evaluated against the traditional lecture/homework format, student satisfaction increased while student learning either remained constant or may have increased slightly [16]. Even though Clark's study seems to suggest that the effect of cooperation on student learning may be less than significant, it should be noted that the improvement in student satisfaction would highly be in favor of motivating students who find certain subjects rather technical, dry, and boring [17].

What we notice from most of these engineering education studies is that the different adaptations of engineering education seem to converge at a proactive and synergistic effort to enrich learning. This convergence point is what the Platform for Learning<sup>TM</sup> is attempting to characterize. So far, we realize that we have to merge both traditional and modern education methods in order to produce a more wholesome and beneficial education experience. The Platform for Learning<sup>TM</sup> model puts forth the notion of a learning platform to deal with that merger.

### 2.2 Learning platforms

A learning platform is an object or experience, based on the Platform for Learning<sup>TM</sup> model, that is introduced into an entire curriculum to unify the various classes and knowledge of a discipline. It gives practical application to the knowledge that students acquire in-class to consolidate concepts in the students' understanding.

What is different about the learning platform as compared to a standard laboratory exercise is that it assimilates and executes effective educational strategies to provide students with concrete experience. These strategies were derived from numerous research studies on academic education [8, 9, 11, 13-18] in addition to the discoveries made by OSU faculty while working on the TekBots program [2, 3, 7].

In section 2.2.1, we shall provide the general context of how a learning platform integrates the current educational strategies that have been presented in the previous section 2.1. Then, in section 2.2.2, we shall introduce the attributes of effective learning

platforms. Through these attributes, the Platform for Learning<sup>TM</sup> concept defines its ideals to teach students effectively in a dynamic learning environment.

## 2.2.1 Integration of educational strategies

Conceptually, the learning platform itself is *learner-centered* in the general context of its use. It has to be able to get students actively involved in knowledge construction. The main idea is to allow students to be in control of their lessons. Concepts that need to be taught should never be forced upon students. Instead, the concepts should be presented in small digestible amounts that would allow students to attain the next-in-line design goal of the platform's current project. In other words, information should be provided to students just-in-time for their needs and does not need to be complete. This will give students enough of an incentive to make a continual effort of applying concepts to the learning platform to reinforce what they have learned.

As the construction of knowledge unfolds as a result of the students' own efforts, the experience they receive will increase their retention of knowledge and further engage them in the learning activity. To get students actively involved in knowledge construction, learning activities should focus around a set of intrinsically motivating problems that are situated in real-world tasks [14].

The platform itself is taught in a *cooperative learning* environment that employs a *proactive* learning style. Learning should take place in a collaborative environment that involves social interaction and negotiation [14]. This would help create the atmosphere of a large engineering team where students can engage in formulating and evaluating problems, conjectures, arguments, and explanations, just as professional engineers do in the workplace [2].

Finally, the platform takes on a *transdisciplinary* teaching approach. For instance, the project assignment structure that is presented in each class would encourage students to ask questions, to cross disciplines in seeking information, and to be creative in defining a problem and developing solution alternatives [18]. In addition, concepts and knowledge

from traditionally non-engineering areas, such as business, economics, human relations, etc., will be included in the learning mix much more naturally. Thus, the engineers produced by the transdisciplinary educational process will be well-rounded and capable of dealing with complex problems which involve many issues that span the educational spectrum [13].

### 2.2.2 Attributes of effective learning platforms

Listed below are the attributes which define an effective learning platform that is conducive towards enhancing learning.

#### (1) Inspires exploration and innovation

An effective learning platform is able to inspire students to explore different design decisions when solving an engineering problem. This can be achieved by providing students with a strong background and understanding of the fundamentals required to analyze and construct a solution method. The platform should then stimulate students into thinking outside the box and beyond the given problem at hand.

The platform is also able to inspire innovation. The learning platform encourages students to begin the journey of exploration on their own. For example, early projects of the platform provide small but exciting hurdles of problems for new students to accomplish in order to engage the students and boost their confidence.

#### (2) Puts theory into practice

The learning platform represents a practical implementation of theoretical knowledge. It should challenge students to tasks that involve practical usage of the knowledge they have learned so far in the curriculum.

As students continue to work on the learning platform, they can begin to appreciate how the knowledge components learned in class can come together to help them achieve goals of their project. This subtly strings together the class syllabus into an interconnected web of knowledge that is much more useful than the knowledge derived from fragmented topics taught in isolation. According to Hadjerrouit, the process of constructing interrelated knowledge requires higher order thinking skills, such as analysis and design skills [14]. With the help of an effective learning platform, students are able to cultivate those skills.

#### (3) <u>Keeps focus on core topics of a class</u>

The learning platform needs to be faithful to the course syllabus and not stray from what is intended to be taught. When implementing a platform for learning, we also need to reduce the amount of redundant work that students have to do. Redundant activities are those that take away the focus from the core topics of the current class. For example, too much soldering work can really dampen the objectives of an electronics project. Instead, a prefabricated circuit board can ease the work of the students and free them to concentrate on higher level tasks such as design and testing.

#### (4) Deepens understanding

When students face minor problems while working on a learning platform project, they are required to study the subject in more detail in order to rectify those problems. The platform acts as a feedback mechanism that informs the student just how much understanding is required for the project. This will deepen a student's understanding of the discipline.

Students begin to appreciate the deviation of practical implementations from ideal theory when they perceive results based on first-hand experience. Paper assignments rarely encourage students to think about real-world improvisations and their implications. With a learning platform, students have an authoritative practical reference that supplements other references such as textbooks, lectures, and online material.

### (5) Reusable in other classes to leverage scaffolding of knowledge

The continuous development of the learning platform in future classes encourages students to find solutions to a given problem using a new set of tools and knowledge that has bearings on past knowledge. Experience and knowledge gained from one project can be reused to form a knowledge scaffold from topic to topic or from class to class. Once a strong base is built, incorporating new knowledge onto an existing scaffold is easier.

#### (6) Flexible, expandable, and does not limit extensibility

It is absolutely essential for any learning platform to be flexible in terms of use and expandable in terms of functionality. These two criterions provide avenues for innovation and variations of design solutions that cannot otherwise be achieved by a strictly specialized platform or exercise.

With overly specialized platforms, students are limited in terms of the number of goals that can be achieved. Specialized hardware that only serves one purpose is an educational dead end. For example, a microcontroller circuit board that has every imaginable support part wired to the microcontroller itself leaves very few input/output ports for expansion by students. This will limit the extensibility of the learning platform by fixing the number of solution sets that is determined by the hardware. On the other hand, a more flexible platform can incorporate concept applications from future classes as it is reused to leverage scaffolding of knowledge.

A learning platform should be treated as an ongoing system that gives students the freedom to breed new ideas. It should be composed of configurable parts that students can fully customize. The building blocks of the platform must be understood by the students and be easy to form into something useful [2]. A sufficiently flexible platform would allow multiple solution paths to a given open-ended problem. The vast freedom of solutions closely resembles the real-world environment and encourages student creativity.

#### (7) <u>Hands-on wherever possible</u>

Students can gain a better "feel" of acquired knowledge when they apply in-class concepts to the platform using a hands-on learning style as a way of involving more human senses. From a psychological perspective, students have a higher likelihood of absorbing knowledge when more human senses are involved in the learning process. For example, a powerful way to teach new students about signal frequency is to show them what the signal looks like when measured by an oscilloscope, and what the signal sounds like when it is fed into a speaker. This provides visual and auditory stimuli that will increase retention of knowledge.

When students engage in hands-on work, the amount of material retained and the ability to integrate that knowledge is greatly improved when the course material relates to personal experience [2]. Studies have shown that students with practical experience scored better in the final exam than those without practical experience [17].

#### (8) Fun to use

An effective learning platform is fun to use. Fun instills in students the motivation to learn and explore, as opposed to making them feel as though they are relearning the wheel. The platform needs to be structured so that it makes learning the basics fun, exciting and engaging.

#### (9) Portable

A learning platform needs to be compact and lightweight. It should be portable so that students can quickly access the platform conveniently when a design inspiration strikes. Students can also bring it around to impress friends, demonstrate to family, and prove to future employers of their engineering skills.

#### (10) <u>Inexpensive to purchase</u>

Affordability is necessary for the purpose of education. When a learning platform is sufficiently low in price, every student is able to afford one. This encourages personal ownership of the learning platform and avoids congested sharing of a common platform.

If the platform is physical in nature, the parts that build the platform need to be easily reproduced for production and restoration purposes. Also, cheap replacement parts ease the burden on students who accidentally destroy them.

#### (11) Useful in a community of learners

A platform for learning enriches the learning experience for the entire *community of learners* that include students, parents, teachers, schoolchildren, enthusiasts and employers alike. Members of the community learn from each other, derive pleasure from the work being done, and give support back in return.

Learning platforms show inherent qualities in students who build them. These qualities capture the attention of other members in the community who, in turn, act as catalysts for the student's learning experience. This would reduce the burden on teachers by relinquishing the cultivation of student-learning morale to the community. Others can then help teach and motivate the students in their own ways. For instance, students who perform well would elicit praises from amazed parents. This will boost confidence and motivation.

The platforms also remain useful long after the lessons are over. They can be used to show creation and achievement. For example, employers tend to look for students who are passionate about interesting projects they have worked on in the past. To those employers, a learning platform that has accompanied a student throughout the entire curriculum represents many qualities, among which are the student's tenacity and dedication to an ongoing project. These are highly prized qualities valued in the job world.

## **3 FPGA LEARNING PLATFORM**

#### **3.1 Introduction of a new FPGA-based learning platform**

An FPGA (Field Programmable Gate Array)-based learning platform that encompasses the attributes described in Chapter 2.2.2 is being introduced to undergraduate students. This platform is intended for an upper-level SoC (System-on-Chip) design course. The objectives of this course are to teach students about the organization of VLSI (Very Large-Scale Integration) systems, and to bring them through the design flow of building a chip. This exposes students to the different types of constraints involved, such as area and timing issues, which they need to consider. The FPGA provides programmable logic hardware for the learning platform to facilitate the course's objectives.

Currently, the teaching method used for this course is to have students develop virtual prototypes of their VLSI systems. Unfortunately, virtual prototypes only provide students with a feel of their designs from the perspective of the CAD (Computer-Aided Design) tools they use. There is no hardware realization to give students a practical use for their work of designing, simulating, and synthesizing the entire system.

The new platform can provide practical experience by allowing each student to program an FPGA circuit board with her or his design. Students can then see their work in action as the designs perform actual tasks while operating on the FPGA learning platform.

#### **3.2 Features of FPGA learning platform**

The FPGA learning platform is an electronic circuit board that is centered around an FPGA chip that utilizes a set of software tools. The hardware is designed to give students as much freedom of expansion as possible while providing some common components on the main board for students to quickly get started. The philosophy of this approach is to provide a bare bones system that students can fully customize as they see fit, and to avoid giving students every bell and whistle. This adheres to the ideals for effective learning platforms outlined by the Platform for Learning<sup>TM</sup> concept.

If students require more functionality from the FPGA board, they can make use of a daughterboard that plugs on top of the main board. The daughterboard is a bare prototype PCB (Printed Circuit Board) that connects to the user I/O of the main board. Once connected, added components on the daughterboard essentially extend the circuitry of the main board. This motivates students to innovate their own designs on the daughterboard while driving them to do the significant work of adding components.

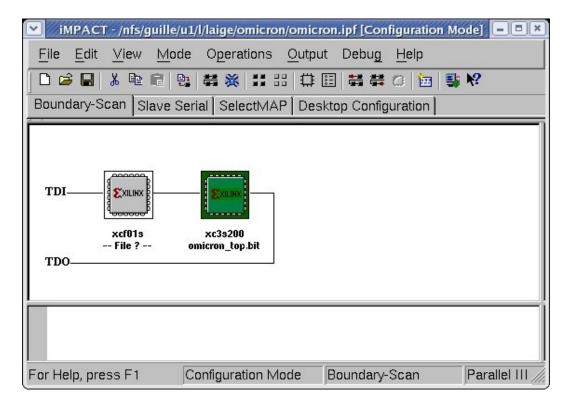

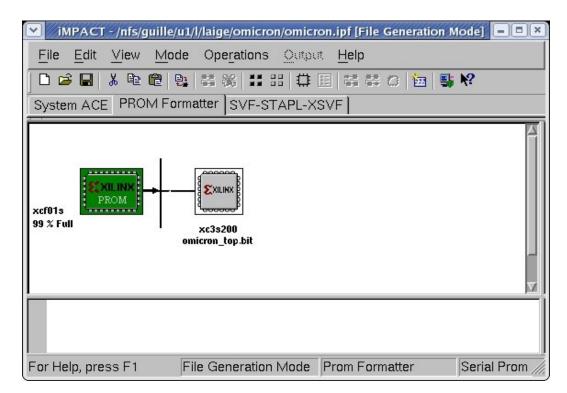

Xilinx<sup>®</sup>, the company that produces the FPGA, provides a free set of industry-grade software tools to be used with the FPGA. The software tools are bundled as a graphical IDE (Integrated Development Environment) known as Xilinx ISE<sup>TM</sup>. The main tool of ISE is the Project Navigator. It houses all the other tools, and is used to structure the hierarchy of an FPGA design. The navigator also allows design constraints to be set. From the navigator, the PACE tool can be loaded to assign package pins that connect core I/O to external I/O. Then, the design is synthesized using the XST tool. Finally, the FPGA can be configured by programming the synthesized design with the iMPACT tool.

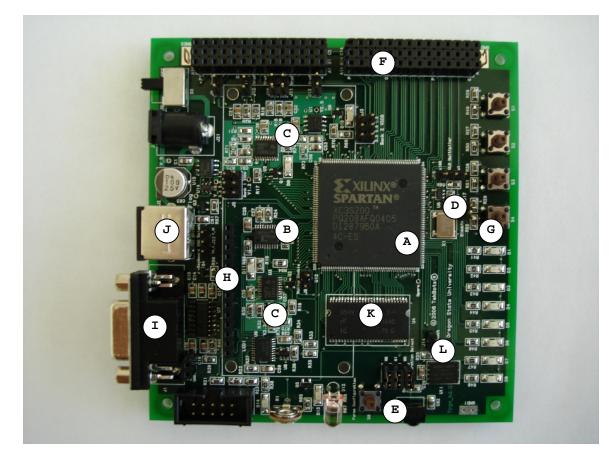

Fig. 1: FPGA learning platform board

Listed below are the hardware features of the FPGA board:

## (A) FPGA as main processor

The FPGA chip used is the Xilinx Spartan-3 XC3S200 [19]. This chip provides a large 200K-gate design capacity, and is optimized for Xilinx RISC (Reduced Instruction Set Computer)-based cores such as the PicoBlaze microcontroller [20] and the MicroBlaze microprocessor [21] cores. Programming is achieved by downloading the configuration bitstream into the FPGA using JTAG (Joint Test Action Group) boundary scan.

#### (B) Flash PROM (Programmable Read-Only Memory)

A Xilinx XCF01S [22] flash PROM with a 1Mbit density is provided as a means to store a non-volatile configuration bitstream for the FPGA. Upon power up, the PROM will automatically program the FPGA with the bitstream. It will also appear as part of the JTAG scan chain for the FPGA board.

### (C) Power regulators

The board supports 4 different voltage regulators with ratings of 1.2V, 2.5V, 3.3V, and 5.0V [23]. They supply power to the main board components and daughterboard expansion.

#### (D) Oscillators

A crystal oscillator drives the main clock signal for the FPGA chip that runs at 100MHz. Another oscillator [24] is provided for custom use. The output signal of the oscillator can be controlled by a jumper setting to produce 3 different frequencies from 607kHz to 6.07MHz.

#### (E) <u>IR (InfraRed) transceiver</u>

The board is equipped with an IR transmitter and an IR receiver. The IR transmitter is an IR LED pointing off the side of the board. The IR receiver is a miniature Vishay TSOP32138 [25] that is located on the same side of the board. The receiver is receptive towards IR signals with a carrier frequency of 38kHz. This frequency can be generated by dividing a 607kHz frequency (generated by the auxiliary oscillator) by 16.

#### (F) User I/O

The board has 84 user I/O pins located on the side. 64 are allocated for signal I/O, 12 are ground and power connections, and 4 are unconnected.

#### (G) LEDs (Light-Emitting Diodes) and pushbuttons

There are 8 LEDs and 4 pushbuttons on the board.

#### (H) LCD (Liquid Crystal Display) interface

The board provides 14 signal lines to interface with a 16x2 LCD that is provided with the learning platform. The interface could be extended to other types of LCDs with the common Hitachi HD44780 instruction set [26]. 10 of the 14 signal lines can also be used as general I/O.

#### (I) Serial port

A serial port allows serial communication using the RS232 protocol. The most common use of this type of communication is to send and receive data from a computer.

#### (J) PS/2 port

A PS/2 port is provided to enable interfacing with a keyboard, mouse, or any compliant devices. It supports both 3.3V and 5.0V operation.

#### (K) SDRAM (Synchronous Dynamic Random Access Memory)

The SDRAM chip on board is a single Micron MT48LC4M16A2 [27] with a capacity of 64M bits. This type of memory is volatile.

#### (L) <u>EEPROM (Electrically Erasable Programmable Read-Only Memory)</u>

The EEPROM chip on board is an Atmel AT45DB161B [28] with a capacity of 16M bits. This type of memory is non-volatile. Data is sent and retrieved from the EEPROM via SPI (Serial Peripheral Interface).

## 3.3 Advantages of FPGA learning platform

The advantages of using this FPGA platform corresponds to the attributes of effective learning platforms described in Chapter 2.2.2. Listed below are the advantages of using this platform:

## (1) Can be used to teach a variety of topics

The FPGA board gives students great flexibility for systems design. It can be used to teach a wide variety of engineering topics. Some examples are provided below:

- **v** Basic digital hardware

- Combinatorial logic

- Sequential logic

- **§** Mealy and Moore state machines

- Logic fault detection

- § Stuck-at fault

- **§** Functional fault

- **v** Core integration techniques

- Microcontroller design

- **§** 3-stage pipeline implementation

- **§** PicoBlaze soft core with internal memory

- Microprocessor design

- **§** 5-stage pipeline implementation

- **§** Superscalar implementation

- **§** Data bus construction

- § MicroBlaze soft core running uCLinux OS

- **∨** Mixed signal processing

- DSP (Digital Signal Processing)

- **§** Digital multiplier for image processing

- § FIR (Finite Impulse Response) filtering

- Analog / digital interaction

- **§** Signal generation and integration

- § Phase-locked loop

#### (2) <u>Reusable to leverage scaffolding of knowledge</u>

The FPGA board is great for linking together knowledge from previous classes. For example, the knowledge of how to use a microcontroller learned in a previous class can be reused to implement a soft core into the FPGA device. This allows the FPGA learning platform to build nicely upon the existing body of knowledge.

#### (3) <u>Affordable to students</u>

The FPGA platform will be available as an inexpensive alternative to available FPGA boards. Boards sold by commercial manufacturers are usually expensive, and their design specifics are often proprietary. Also, they usually leave few FPGA I/O ports for expansion, and incorporate too many advanced features that serve applications too specific for educational purposes.

#### (4) Speedy design and testing for a low cost

In order to implement a hardware realization of an ASIC (Application-Specific Integrated Circuit) design, a fabrication process is needed to create the chip. This process requires a lot of time (i.e., approximately 6 months or more) and money (i.e., in the order of thousands of US dollars). The FPGA, on the other hand, provides a hardware programmable chip that has already been fabricated. The implementation of hardware on an FPGA equates to the programming of the chip. This allows fast development turnaround time in the order of seconds. In addition, the cost of an FPGA chip is relatively low (i.e., below USD\$10 when purchased in quantities of 100).

#### (5) <u>Portable</u>

With FPGA learning platforms, students can quickly implement and test their designs without requiring specialized development equipment. The software that is used to program the FPGA is free. Thus, students can use their platforms anywhere at anytime. The software tools are also widely adopted in industry, allowing the platform to be utilized in the commercial work environment.

#### (6) Hands-on to demonstrate details of concepts

The type of hands-on work involved with the FPGA learning platform requires students to dive into the intricacies of low-level hardware design. As such, the complexity of the FPGA device makes it inappropriate for use at introductory level courses [29]. With the FPGA, students can observe how "software" interacts with "hardware" at the device level. In the process of learning, they would also be exposed to the use of CAD tools, and HDLs (Hardware Design Languages) employed in industry.

#### (7) <u>Very extensible</u>

The FPGA learning platform is also very powerful in terms of expandability. Modern FPGA devices provide for large design capacity that is well within the boundaries of educational use. Often, students assume they must work with only one processor core. With an FPGA, this restriction has been loosened to expose students to multi-core applications on a chip. The end result would be the creation of more elaborate embedded systems that extend the functionality of the learning platform.

# **4 FPGA BOARD TEST ENVIRONMENT**

### 4.1 FPGA core in a self-testable system

The flexibility of the FPGA platform introduced in the previous chapter allows for a different approach to be taken for testing the new board. The main processor of the FPGA board is "brainless" to begin with. The brains of the FPGA can then be configured with an intelligent core to test the on-board peripherals in order to produce a *self-testable* system. The board is able to test itself without requiring an additional tester built onto it. The self-test is achieved by employing the FPGA, the central part of the entire system to be tested, as the core component that facilitates the testing of the rest of the system. This method of testing is an alternative for exhaustive test methods that flood the board with test signals using a bed-of-nails type of setup.

An FPGA is inherently different from a microprocessor when used as the core component for a *self-testable* system. A microprocessor has a permanent core that only provides functionality general enough to cover a set of basic operations. An FPGA, however, can have its core optimized for application-specific tests. It can be customized for accuracy to implement timing-critical tests because of its logic-level architecture. It also allows multi-core implementations to be embedded on-chip, reducing its dependency on off-chip systems. For instance, an SPI core can be implemented seamlessly into the FPGA for components that require the interface. Conventional ASICs do not allow such pliability.

The on-board flash PROM that holds the bitstream configuration for the FPGA chip is initially empty. This is where the implemented core that performs the tests of the FPGA board components is stored. Whenever the board is powered up, the PROM will program the FPGA chip with the stored bitstream. This effectively provides the illusion that the FPGA device was tailored with a permanent core for testing purposes, and that the FPGA has "brains" by default. In the learning environment, the content of a configured PROM is not intrusive. It does not get in the way of the students' FPGA designs. When students wish to implement their designs, they can bypass the PROM in the scan chain to program the FPGA directly. However, this type of programming is volatile. After a power reset, the FPGA board is flashed anew with the test suite. Students are, of course, given the choice of making their designs permanent by overwriting the PROM.

## **4.2 Development test suite for FPGA board**

A major part of the work involved in this thesis is the development of the FPGA core that is used to test the FPGA board. This specialized core is able to test a variety of onboard components as well as student component modules and circuit designs. It has two objectives, which are to

- $\emptyset$  facilitate the development of the FPGA board while it is being manufactured.

- Ø assist students with testing their FPGA designs in the learning environment using a cycle-accurate hardware testbench debugger (see Chapter 5).

The core provides a composition of tools to perform these objectives seamlessly. These tools are collectively known as the "development test suite". In particular, the development test suite for the FPGA learning platform is given the name "OMICRON".

The primary emphasis of the manufacturing tests conducted by OMICRON is mainly to verify solder connections of board components and traces that connect them together. As it is, the FPGA board has very few macro components. Most of the components connected to the FPGA are either interface ports or the user I/O. Available macro components such as the IR transceiver, SDRAM and EEPROM are tested for their basic functionalities.

The conducted tests are simple and quick. There is no need for elaborate tests that have results that are hard to decipher. We only need to know whether or not a problem exists with one of the board components. After that, further work to troubleshoot the exact problem is relatively straightforward. OMICRON assumes a fully functional FPGA chip (and flash PROM) whereby each of the components connected to the FPGA is systematically tested. This is a reasonable assumption made in order to manage and contain the complexity of the test suite. Assuming otherwise would entail testing the core exhaustively, which is beyond the scope of objectives for this test suite.

In section 4.2.1, we shall explain the structure of OMICRON and how it is built internally to provide the test suite. Next, in section 4.2.2, we shall describe how OMICRON performs tests on the various peripherals on-board. Then, in section 4.2.3, the two different modes of operation for OMICRON are presented.

# **4.2.1 OMICRON development test suite implementation**

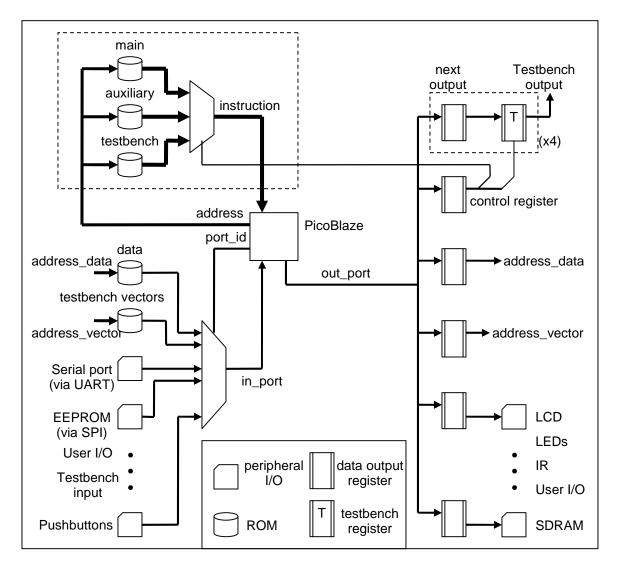

The development test suite core, OMICRON, is essentially a large state machine implemented in the FPGA. It is implemented around the popular Xilinx PicoBlaze microcontroller core [20]. The hardware of OMICRON running within the FPGA is composed of the PicoBlaze core, instruction and data-type ROMs, output registers, an input MUX (multiplexer), and supplemental core modules. The software of OMICRON manages the hardware by supplying PicoBlaze with instructions to control the entire state machine. OMICRON is written entirely in VHDL (for the hardware) and PicoBlaze assembly (for the software).

Shown below is a block diagram of OMICRON's datapath layout:

Fig. 2: Structure of OMICRON

Listed below are detailed descriptions of each part of the structure:

### (1) <u>PicoBlaze microcontroller core</u>

PicoBlaze is an 8-bit microcontroller intended for use in Spartan-3 FPGA devices. It was chosen for its simple architecture which makes it a good candidate for applications requiring a complex, but non-time critical, state machine. The core is totally embedded within the target FPGA and requires no external support. It is supplied as a synthesizable VHDL macro that is handled by place-and-route tools to merge with the logic of a design.

The PicoBlaze core is optimized for low deployment cost and efficiency on Xilinx FPGAs. It only occupies 5% of the XC3S200 device capacity. Its small size allows other large designs to co-exist alongside it, which is ideal for the purpose of a testbench (more in Chapter 5). The performance of PicoBlaze is respectable at approximately 43 to 66 MIPS (Millions of Instructions Per Second) even with such size constraints [30].

All instructions under all conditions will execute in 2 clock cycles. The constant execution rate is of great value when determining the execution time of a program [30]. There are 57 types of instructions in the instruction set. CALL and RETURN instructions support a stack depth of 31 levels.

Internally, the PicoBlaze microcontroller provides 16 x 8-bit registers with 64 bytes of scratch-pad memory. It also provides abundant flexible I/O. From this, its basic functionality is easily extended and enhanced by connecting additional logic to the microcontroller's input and output ports.

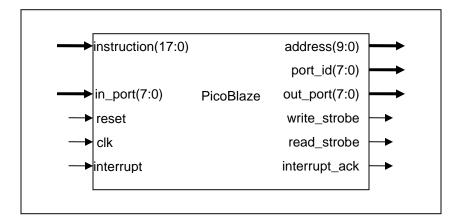

Shown below is a diagram of PicoBlaze and its interface I/O:

Fig. 3: PicoBlaze microcontroller core

As seen from the figure above, each PicoBlaze instruction is 18 bits long, and is addressed by 10 bits for a maximum of 1024 instructions in a single 18kbit ROM. Its input and output ports are 8 bits each, and are addressed by an 8-bit port\_id to allow 256 locations of inputs and outputs. Read and write strobes are provided to inform an external module when a read or write operation is performed. A level-triggered interrupt pin is also provided.

### (2) Microcontroller I/O

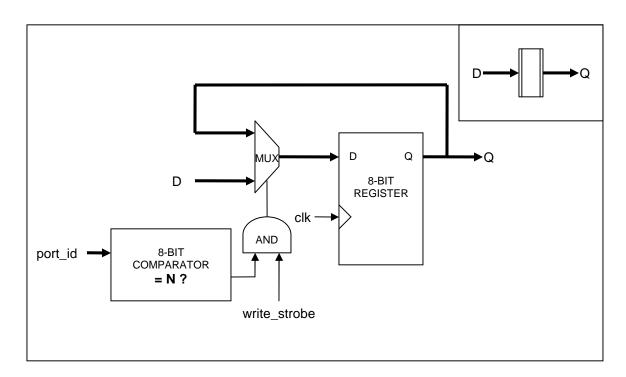

Due to the addressable nature of the I/O, special care is taken to create output registers that only capture PicoBlaze's output based on the port\_id address. Shown below is the construction of a data output register:

Fig. 4: OMICRON data output register

In a data output register, the port\_id signal is checked to determine when it is appropriate to capture the incoming byte. An extra precaution is taken by only allowing a byte to be captured when there is a write strobe indicating a write operation. This is analogous to the operation of a data bus. The data bus is indicated by the out\_port signal in Figure 2.

On the input side, a multiplexer is responsible for selecting which input byte to read. The selection is determined by the port\_id signal. With the exception of the UART (Universal Asynchronous Receiver-Transmitter) modules, the read strobe is not utilized by OMICRON. This is because most of the incoming bytes originate from non-queued sources.

In Figure 2, output registers are used for control signals of the datapath. It is also used to send data to various peripherals. For the sake of keeping the figure concise, not all peripherals are listed. Likewise, the list of connected peripherals on the input side is shortened as indicated by the triple dots.

### (3) Instruction ROMs

An assembler is provided with the PicoBlaze source files to compile assembly programs into synthesizable VHDL ROM modules. Each ROM module is allows 1024 x 18-bit instructions to be stored.

Unfortunately, OMICRON requires more than 1024 assembly instructions for its operation. For this reason, two extra instruction ROMs were created to supplement the main program ROM. The entire OMICRON program is partitioned into three instruction ROMs as follows:

### § Main program ROM

The main ROM contains the root program execution for OMICRON. This includes code for the menu interface as well as the handling of RS232 terminal and non-terminal modes. This also includes a majority of the code for testing on-board devices (known as "devtests" or device tests). Devtests for the LEDs, pushbuttons, LCD, serial port, SDRAM, and EEPROM are found in this ROM.

# **§** Auxiliary program ROM

The auxiliary ROM contains subroutines to construct and display strings on the RS232 terminal or the LCD. It also contains various subroutines for LCD operations such as displaying characters and clearing the display.

# § Testbench program ROM

The testbench ROM contains subroutines that define the operations of the cycleaccurate hardware testbench debugger. It also provides code space for custom subroutines that build upon OMICRON's existing subroutines using the PicoBlaze instruction set. Devtests for the user I/O, PS/2 port, and IR transreceiver are found in this ROM.

OMICRON extends the number of program instructions beyond 1024 by means of a soft switch [31] to switch seamlessly between the three instruction ROMs while the root program is still in execution. The outputs from the three ROMs are fed into a multiplexer. One of the outputs is then selected as the current instruction by a control signal originating from a data output register.

#### (4) Data ROM

OMICRON utilizes a single 2048-byte ROM as its data ROM. The data ROM is used to provide OMICRON with its vocabulary of words. The words were compressed by hand and stored as most-used syllables to save on storage space. This allows OMICRON to efficiently generate over 140 English words from only 256 bytes used. The remaining 1792 bytes are left for future use by students.

A Perl script was written to generate data ROM modules as synthesizable VHDL macros. The script data2rom.pl takes a text file as an input and parses its content by performing an ASCII (American Standard Code for Information Interchange) to hex conversion. The result is filled into the form file dataROM\_form.vhd to generate the macro.

### (5) <u>Testbench vector ROMs (optional)</u>

Optional testbench vector ROMs can be plugged into OMICRON as a source of test vectors for the hardware testbench debugger. A more detailed explanation is provided in Chapter 5.

### (6) <u>UART modules</u>

UART transmit and receive modules provided with the PicoBlaze package [32] are used to facilitate RS232 communications for the serial port. They provide the functionality of a simple UART transmitter and receiver with these fixed characteristics:

- o 1 start bit

- 8 data bits (least significant bit first)

- o No parity

- $\circ$  1 stop bit

This pair of macros are highly optimized for Xilinx FPGAs. Both the macros occupy approximately 2% of the XC3S200 device capacity.

### (7) SPI core

An SPI core is required to provide the interface between OMICRON and the EEPROM. The core will operate as the master in SPI mode 3 whereby the data is ordered most significant bit first. The main clock of 100MHz is divided down by 8 to produce a 12.5MHz SPI clock that is well within the requirements of the EEPROM.

### (8) <u>Clock divider (not shown in Figure 2)</u>

The signal from the auxiliary oscillator is fed through a clock divider to produce a 38kHz frequency signal. This is required as a carrier frequency for testing the IR transceiver. The 38kHz signal is achieved by dividing a 607kHz clock signal generated by the oscillator by 16.

# (9) Testbench output registers

These registers facilitate the output functionality of the hardware debugger. A more detailed explanation is provided in Chapter 5.

# 4.2.2 How OMICRON performs tests on FPGA board

Theoretically, module testing involves the application of test vectors to a tested component in order to induce an observable result. That result is then used to assess whether or not the test was successful. In a self-testable system, the core (assumed to be fully functional) is responsible for testing the components around it. However, for that core to receive the results of its tests, some sort of result feedback mechanism must be employed.

In the case of the FPGA board, most of its components provide some means of feeding signals back into OMICRON. For instance, the user I/O pins can be connected in pairs to form feedback loops. On the other hand, the IR transceiver can be used to send and then receive an IR signal. Some components require human feedback for test confirmation. For example, a pushbutton test relies on the user to push the button and visually confirm an actuated result.

In the list below, we shall describe the methods used by OMICRON to test each peripheral of the FPGA board. The entire implementation that was laid out in the previous section 4.2.1 enables OMICRON to probe traces and to execute test algorithms on components that are external to the FPGA.

#### (1) Serial port test

The transmit and receive capabilities of the serial port is tested by means of a serial communication between OMICRON and a computer running an RS232-capable terminal.

To test the transmission of data, a simple ASCII string is sent to the terminal by OMICRON. The user would have to visually confirm that the string was successfully sent, indicating that the TX (transmit) trace is good.

To test the receiving of data, OMICRON will continously listen for any incoming serial transmission from the computer. In this test, anything that is typed on the keyboard will be sent via the terminal to OMICRON. Incoming bytes will be displayed on the LCD as they are received, indicating that the RX (receive) trace is good. During this time also, LEDs would alternately flash as an additional indicator, providing backup for a faulty LCD.

Of course, if commands can be issued and information can be received via the terminal in the first place, then the serial port is in full working order.

### (2) LCD test

To test the LCD, a range of ASCII characters is displayed for every character of every line on the LCD. This will test the integrity of the LCD interface traces. Block characters can also be displayed to detect dead pixels on the LCD. Visual confirmation of the test is required by the user. At any time, the LCD can be cleared for a new test.

The serial port data receive test can also be used to test the LCD. Characters sent from the keyboard are displayed on the LCD, allowing the user to enter custom messages.

## (3) LEDs test

A binary counter is activated on LEDs to flash them in an incremental manner. Visual confirmation is required by the user.

The serial port data receive test can also be used to test LEDs. The LEDs will toggle flash whenever a byte is received from the keyboard.

### (4) <u>Pushbuttons test</u>

Pushbuttons will be tested for button push events. Whenever a push is made, a message to indicate which button was pushed will either appear on the terminal or the LCD, depending on the mode of operation (see next section 4.2.3). LEDs will also toggle accordingly. Visual confirmation is required by the user.

### (5) <u>IR transceiver test</u>

The IR transceiver is tested by first transmitting a signal via the transmitter, and then receiving it with the receiver. This action forms a feedback mechanism between the two devices that allows OMICRON to test both devices simultaneously. OMICRON is able to determine the success of this test on its own. User feedback is not required.

A valid IR signal is distinguised from other signals, which exist naturally in the environment, by its carrier frequency. The 38kHz carrier signal provided by the clock divider (see previous section 4.2.1) is used to modulate a valid signal. This signal is continously pulsed in bursts of 16 periods with a 37.5% duty cycle. On the receiver side, the incoming signal is verified at critical points to ensure that the original signal is correctly received.

It is advisable to avoid testing the IR transceiver under direct exposure of fluorescent light that can drown the signal. It is also advisable to provide a reflective surface, such as a sheet of paper, to reflect the IR signal back to the receiver.

#### (6) User I/O test

The 64 general I/O pins available on-board are grouped into 2 virtual ports of 32 pins each. These virtual ports are physically connected together in pin-wise pairs to form feedback loops to the FPGA.

To test the user I/O, each virtual port takes its turn to become an input and an output. While one virtual port acts an input with pull-ups activated, the other port act as an output that drives the former input port low. When the entire input port is detected as being driven low, the test is successful for one way. Then, the virtual ports interchange their input/output roles and this process is repeated again. OMICRON reports that the whole test passes only when it is successful for both ways.

### (7) $\underline{PS/2 \text{ port test}}$

This test is similar to the user I/O test except that it only involves 2 pins. First, the clock and data lines are physically connected together to form a feedback loop. Then, with pull-ups activated, each line takes its turn to become an input and an output. The current line acting as an output will try to drive the input line with a low signal, and vice versa. If low signals are detected both ways, the test is successful.

## (8) SDRAM test

The process of testing the SDRAM involves writing some data to a memory address location, and then immediately reading the data back from the same address location. If the data sent and received do not match, OMICRON will report the failure by displaying data value and address location where it failed. This process is repeated until the end of every test stage.

There are two stages for the SDRAM test. The first stage is to test the data bus. This is achieved by first fixing the memory address location to 0. Then, the data lines are tested with walking-ones and walking-zeroes configurations. With these configurations, it is easy to point out which data bus lines are faulty once errors do occur.

| 0000001  | 11111110 |

|----------|----------|

| 00000010 | 11111101 |

| 00000100 | 11111011 |

| 00001000 | 11110111 |

| 00010000 | 11101111 |

| 00100000 | 11011111 |

| 01000000 | 10111111 |

| 1000000  | 01111111 |

|          |          |

Fig. 5: 8-bit walking-ones/zeroes example

The second stage is to test the address bus. For this stage, an exhaustive test is performed on every memory address location with pseudo-random data values. It is important to cover every address location to confirm the operation of all memory cells.

### (9) <u>EEPROM test</u>

The testing process for the EEPROM is the same as for the SDRAM. It uses the same SDRAM first stage to test the data bus. However, it uses a different approach to test the address bus. Unlike the SDRAM, exhaustive testing for every address location is not recommended for the non-volatile EEPROM due to its limited number of allowable rewrites. Instead, walking-ones and walking-zeroes configurations are used in place of the SDRAM exhaustive approach to select the address locations. Those locations are then tested with pseudo-random data.

# 4.2.3 OMICRON modes of operation

Tests performed by OMICRON are manually executed by the user. Once a test is performed, OMICRON will return the results of the test to the user and await further instructions. OMICRON offers two modes of operation to interact with the user:

#### (1) <u>Terminal (TERM) mode</u>

For this mode, a serial cable connection between the FPGA board and a computer is required. Communication is established to OMICRON by opening a serial link using an RS232-capable terminal on the computer. The communication setting of the serial link is configured at a baud rate of 38400.

Once communication is established, the user is provided with a CLI (Command Line Interface) to issue commands to OMICRON and receive results on the terminal. On the CLI, a menu interface is provided to organize the various test commands. At any point, the user can view the current menu and its list of commands by issuing a question mark "?" as the command. To go back a menu level, a "G" command can be issued.

Fig. 6: OMICRON terminal menu hierarchy

With the exception of the TESTBENCH menu, all tests are executed with one-letter commands for simplicity. From the figure above, the alphabet indicated before each test is the CLI command for that particular test. For example, to test the SDRAM, a user currently in the TOP menu would perform this series of keystrokes:

- (i) Type "M" and hit <Enter> to get into the MEMORY menu

- (ii) Type "S" and hit <Enter> to start the SDRAM test